# WAFER-LEVEL PACKAGING FOR ENVIRONMENT-RESISTANT MICROINSTRUMENTS

by

Sang-Hyun Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2009

#### **Doctoral Committee:**

Professor Khalil Najafi, Chair Professor Kensall D. Wise Associate Professor Katsuo Kurabayashi Research Fellow Sangwoo Lee Assistant Professor Michel M. Maharbiz, U. C. Berkeley © Sang-Hyun Lee All rights reserved 2009 To my family: Your love and dedication made this possible

# **Table of Contents**

| 7.1. AT 1.1                                                                                                                                                                                                                                                                                                                            |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                         | XV               |

| List of Appendices                                                                                                                                                                                                                                                                                                                     | xvii             |

| Abstract                                                                                                                                                                                                                                                                                                                               | xviii            |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                 | 1                |

| 1.1 MEMS Packaging                                                                                                                                                                                                                                                                                                                     | 6                |

| 1.1.1 Role of MEMS Packaging                                                                                                                                                                                                                                                                                                           | 6                |

| 1.1.2 MEMS Packaging Procedures                                                                                                                                                                                                                                                                                                        | 7                |

| 1.1.3 MEMS Packaging Requirements                                                                                                                                                                                                                                                                                                      | 11               |

| 1.2 Environment-Resistant MEMS Package                                                                                                                                                                                                                                                                                                 | 13               |

| 1.3 Contributions                                                                                                                                                                                                                                                                                                                      | 16               |

| 1.4 Thesis Organization                                                                                                                                                                                                                                                                                                                | 16               |

|                                                                                                                                                                                                                                                                                                                                        |                  |

| Chapter 2 Development of Key Technologies for the Environment                                                                                                                                                                                                                                                                          |                  |

| Package                                                                                                                                                                                                                                                                                                                                | 17               |

| Package                                                                                                                                                                                                                                                                                                                                | 17               |

| Package                                                                                                                                                                                                                                                                                                                                |                  |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package                                                                                                                                                                                                 |                  |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design                                                                                                                                                         | 1719192232       |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation                                                                                                                               | 1719192232       |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation  2.2.1 Vibration Isolation                                                                                                    | 1719223238       |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation  2.2.1 Vibration Isolation  2.2.2. Shock Protection                                                                           | 171922323838     |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation  2.2.1 Vibration Isolation  2.2.2. Shock Protection.  2.3 Device Transfer/Assembly Techniques                                 | 17192232383842   |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation  2.2.1 Vibration Isolation  2.2.2 Shock Protection  2.3 Device Transfer/Assembly Techniques  2.3.1 Device Transfer Techniques | 1719             |

| Package  2.1 Thermal Isolation  2.1.1 Thermal Resistance of the Environment-Resistant Package  2.1.2 Heat Dissipation in Micro-package  2.1.3 Thermal Isolation Package Design  2.2 Mechanical Isolation  2.2.1 Vibration Isolation  2.2.2. Shock Protection.  2.3 Device Transfer/Assembly Techniques                                 | 1719323838424343 |

|         | 2.4 Wafer-level Vacuum Encapsulation                               | 51  |

|---------|--------------------------------------------------------------------|-----|

|         | 2.4.1 MEMS Wafer-level Encapsulation Approach                      | 51  |

|         | 2.4.2 Wafer-to-Wafer Bonding                                       | 54  |

|         | 2.4.3 Vacuum Encapsulation                                         | 60  |

|         | 2.5 Vertical Feedthroughs                                          | 62  |

|         | 2.5.1 Feedthroughs in MEMS packaging                               | 62  |

|         | 2.5.2 Vertical Feedthroughs for the Environment-Resistant Package  | 63  |

|         | 2.6 Summary                                                        | 64  |

| Chapter | r 3 Generic Environment-Resistant Package with Meandering          |     |

|         | 3.1 Package Design                                                 | 66  |

|         | 3.1.1 Package Concept                                              | 66  |

|         | 3.1.2 Packaging Process                                            | 68  |

|         | 3.1.3 Chapter Overview                                             | 69  |

|         | 3.2 Meandering Metal Isolation Suspension                          | 70  |

|         | 3.2.1 Meandering Metal Isolation Suspension                        | 70  |

|         | 3.2.2 Enforced Metal Isolation Suspension                          | 77  |

|         | 3.2.3 Electroplated Metal Suspension                               | 82  |

|         | 3.3 Sacrificial Layers                                             | 86  |

|         | 3.3.1 Photoresist and Polyimide Sacrificial Layer                  | 86  |

|         | 3.3.2 Thermally Decomposing Sacrificial Layer: Unity <sup>TM</sup> | 88  |

|         | 3.4 MEMS Device Transfer                                           | 91  |

|         | 3.4.1 Wafer-level Device Transfer Technique                        | 91  |

|         | 3.4.2 Issue in Wafer-level Transfer Bonding                        | 94  |

|         | 3.5 Vertical Feedthroughs on Glass Wafer                           | 95  |

|         | 3.6 Thermal Resistance of the Package                              | 97  |

|         | 3.6.1 Test Platform Fabrication                                    | 97  |

|         | 3.6.2 Thermal Resistance Measurement Results                       | 99  |

|         | 3.7 Summary                                                        | 102 |

| Chapte | r 4 Generic Environment-Resistant Package with Glass                   |                          |

|--------|------------------------------------------------------------------------|--------------------------|

|        | Batch Die-level Device Transfer Technique                              | 104                      |

|        | 4.1 Introduction                                                       | 104                      |

|        | 4.2 Environment-Resistant Package Design                               | 105                      |

|        | 4.2.1 Package Design Overview                                          | 105                      |

|        | 4.2.2 Isolation Suspension Design                                      | 107                      |

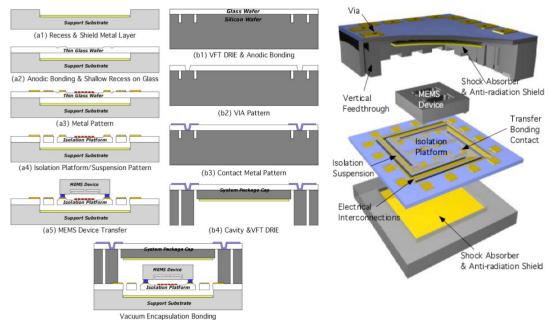

|        | 4.3 Fabrication                                                        | 110                      |

|        | 4.3.1 Platform Substrate Fabrication                                   | 111                      |

|        | 4.3.2 Generic Batch Die-level Transfer Technique                       | 117                      |

|        | 4.3.3 Wafer Bonding and Vertical Feedthrough                           | 124                      |

|        | 4.4 Test Results                                                       | 127                      |

|        | 4.4.1 Thermal Resistance Measurement                                   | 128                      |

|        | 4.4.2 Vacuum-level Measurement                                         | 129                      |

|        | 4.4.3 MEMS Gyroscope Packaging                                         | 131                      |

|        |                                                                        |                          |

|        | 4.5 Summary                                                            | 134                      |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P                  | ackage 136               |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage 136               |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage 136<br>136<br>137 |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage 136<br>136<br>137 |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | 5.1 Introduction                                                       | 136                      |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | 5.1 Introduction                                                       | ackage                   |

| Chapte | 7 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage       136         |

| Chapte | r 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage                   |

| Chapte | 7 5 Low-Power Oven-Controlled Environment-Resistant P 5.1 Introduction | ackage       136         |

| Chapter 6 Conclusion                                      | 160 |

|-----------------------------------------------------------|-----|

| 6.1 Summary                                               | 160 |

| 6.2 Future Work                                           | 163 |

| 6.2.1 Generic Packaging                                   | 163 |

| 6.2.2 Optimization of the Package and Oven-Control System | 165 |

| 6.2.3 Extended Applications                               | 166 |

|                                                           |     |

| Appendices                                                | 167 |

| Bibliography                                              | 180 |

# **List of Figures**

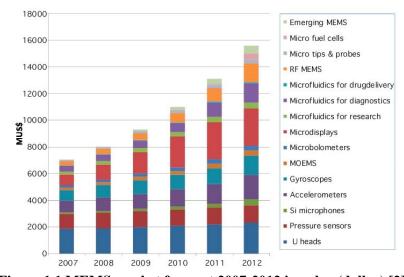

| Figure 1.1 MEMS market forecast 2007-2012 in value (dollar) [2].                                                                                                                                                                                                                                                           | 1           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

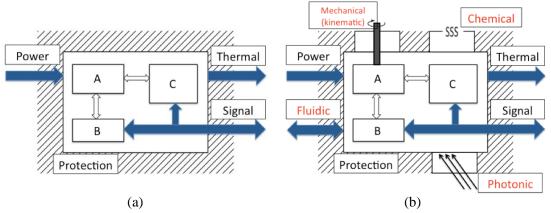

| Figure 1.2 Functions of packaging: (a) traditional: IC, (b) MEMS packaging [9].                                                                                                                                                                                                                                            | 6           |

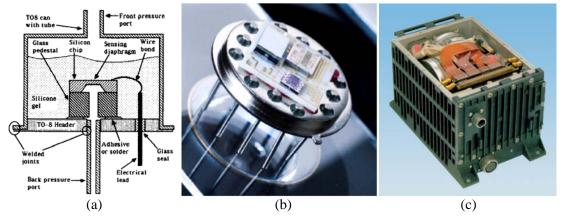

| Figure 1.3 Examples of higher level MEMS packages: (a) Conceptual drawing of a typical T (Transistor Outline-8) pressure sensor package for differential pressure [10], Accelerometer assembled on a hybrid substrate and packaged in a TO can [11], (c) (Inertial navigation system for launch and reentry vehicles [12]. | (b)<br>GPS- |

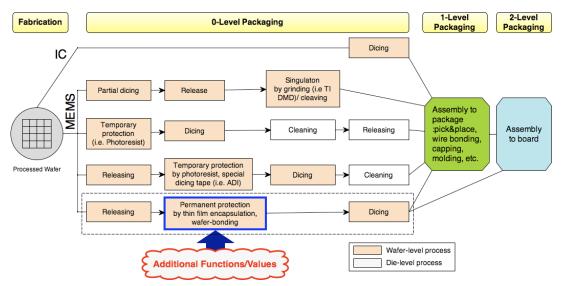

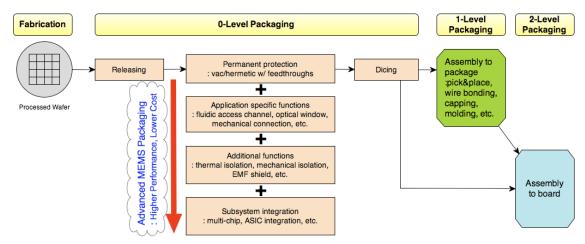

| Figure 1.4 Typical packaging processes: 0-, 1-, and 2-level packaging.                                                                                                                                                                                                                                                     | 9           |

| Figure 1.5 Advanced MEMS packaging technology.                                                                                                                                                                                                                                                                             | _ 11        |

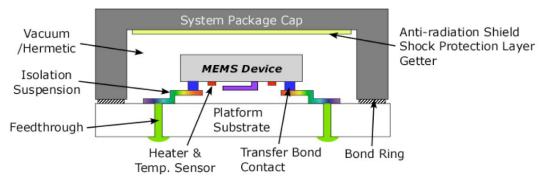

| Figure 1.6 Illustration of the generic environment-resistant package concept.                                                                                                                                                                                                                                              | _ 14        |

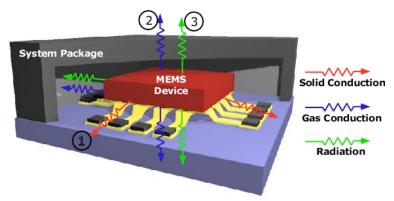

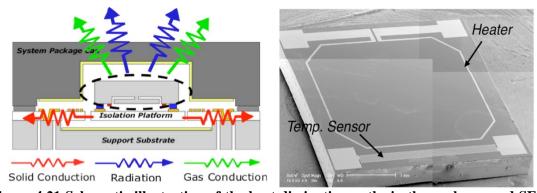

| Figure 2.1 Major heat dissipation modes: (1) solid conduction, (2) gas conduction, and radiation.                                                                                                                                                                                                                          |             |

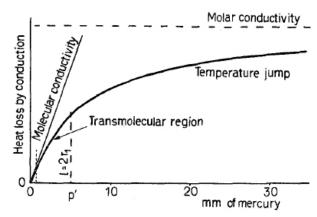

| Figure 2.2 Heat loss in air of a 0.01 mm wire placed inside a wide tube. At p', the mean free equals the diameter of the wire [44].                                                                                                                                                                                        |             |

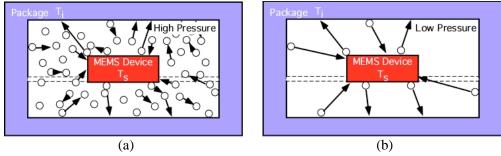

| Figure 2.3 Schematic illustration of gas conduction mechanism at (a) high pressures, and (b) pressures.                                                                                                                                                                                                                    |             |

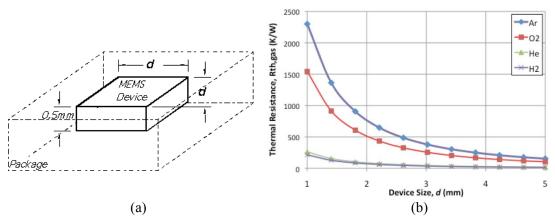

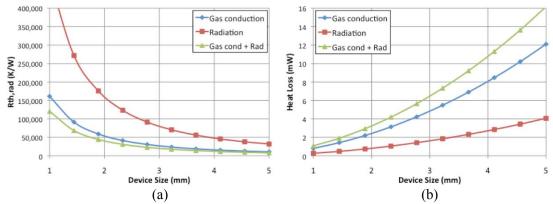

| Figure 2.4 (a) Definition of a device size in the environment-resistant package. The thickne the device is assumed 0.5mm. (b) Thermal resistance of gas conduction at atmospheressure and at 0 °C. The gap between the device and package wall is assumed 150 µm                                                           | heric       |

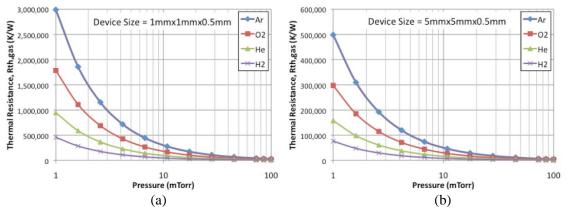

| Figure 2.5 Thermal resistance of gas conduction in a vacuum package at 0 °C. It is a function pressure and device size. The accommodation coefficient, α, is assumed 0.9.                                                                                                                                                  |             |

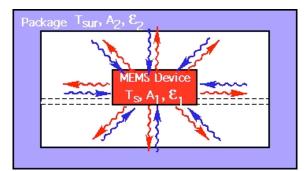

| Figure 2.6 Radiation in environment-resistant package.                                                                                                                                                                                                                                                                     | _ 30        |

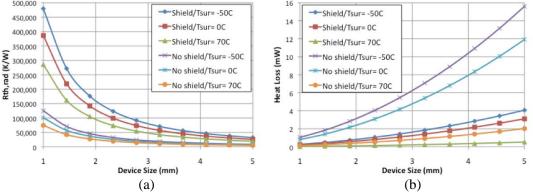

| Figure 2.7 (a) Thermal resistance and (b) heat loss by radiation with varying the packaged size in the environment-resistant package. The emissivity of the shield material assumed 0.1.                                                                                                                                   |             |

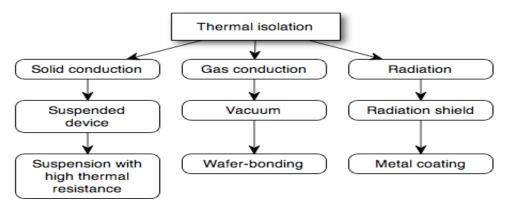

| Figure 2.8 Key approaches to achieve thermal isolation in environment-resistant package.                                                                                                                                                                                                                                   | _ 33        |

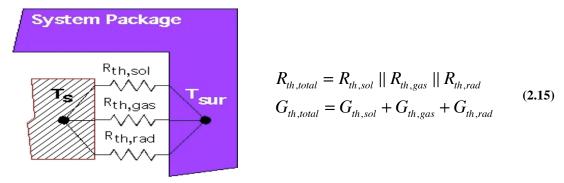

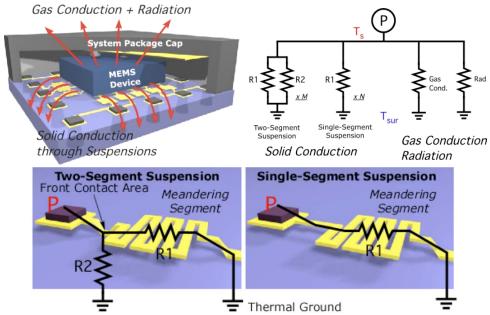

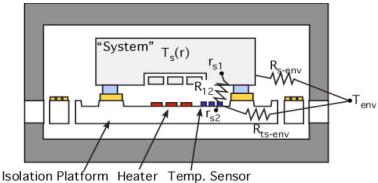

| Figure 2.9 A lumped thermal circuit model for the environment-resistant package.                                                                                                                                                                                                                                           | _ 33        |

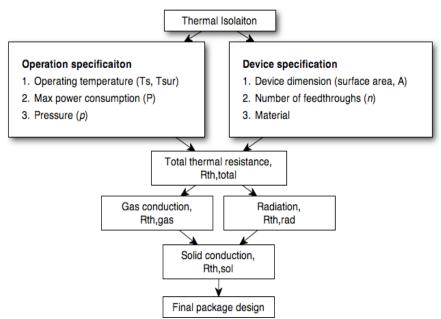

| Figure 2.10 Design procedure for thermally isolated package.                                                                                                                                                                                                                                                               | 34          |

| rigure | resistance or heat loss of solid conduction can be obtained from the total thermal budget. Assumption: $\alpha$ =0.9, O <sub>2</sub> , p=10mTorr, gap btw device and package=150 $\mu$ m, T <sub>s</sub> =80 °C, and T <sub>sur</sub> = -50 °C.                                                                                                                                           |

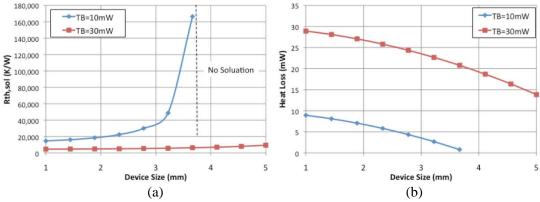

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2.12 (a) Minimum necessary thermal resistance and (b) heat loss through solid conduction under the total thermal budget (TB) of 10 mW and 30 mW. In TB= 10 mW case, there is no budget left for solid conduction when the device size is larger than $3.7\times3.7\times0.5$ mm <sup>3</sup> , because the heat loss by gas conduction and radiation is already larger than $10$ mW 36    |

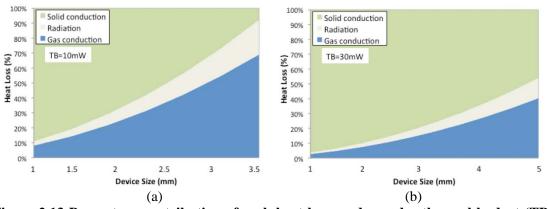

| Figure | 2.13 Percentage contribution of each heat loss modes under thermal budget (TB) of (a) 10 mW and (b) 30 mW. As the device size becomes large, gas conduction and radiation become important. Assumed $\alpha$ =0.9, p=10 mTorr, Ts=80 °C, $T_{sur}$ =0 °C, $\varepsilon_1$ =0.52, and $\varepsilon_2$ =0.1.                                                                                |

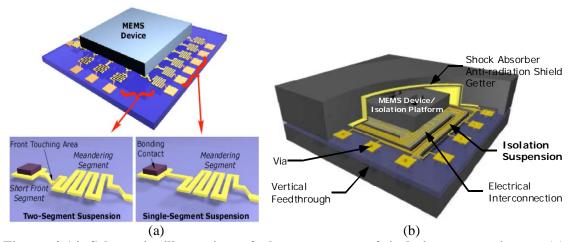

| Figure | 2.14 Schematic illustration of the two types of isolation suspensions. (a) Meandering metal isolation suspensions (Chapter 3), (b) Glass isolation suspensions (Chapter 4) 37                                                                                                                                                                                                             |

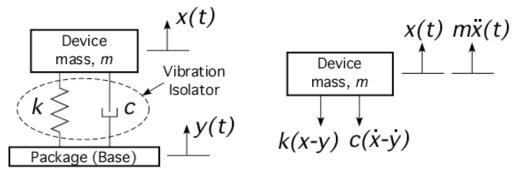

| Figure | 2.15 Modeling of the base excitation problem [46]. The motion of the device (mass, m) is excited by prescribed harmonic displacement of the package (base) through the spring and damper.                                                                                                                                                                                                 |

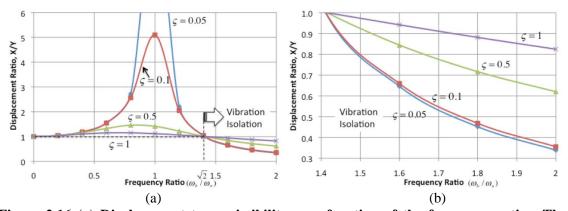

| Figure | 2.16 (a) Displacement transmissibility as a function of the frequency ratio. The dimensionless deflection $X/Y$ is less than unity when the frequency ratio of the package vibration is larger than $\sqrt{2}$ , where the vibration isolation occurs. (b) Magnification of the isolation area.                                                                                           |

| Figure | 2.17 (a) Force transmissibility as a function of the frequency ratio for $\zeta$ = 0.01, 0.05, 0.1, 0.5 and 1.0. (b) A comparison between force transmissibility and displacement transmissibility for a damping ration of $\zeta$ =0.01 on a semi-log plot41                                                                                                                             |

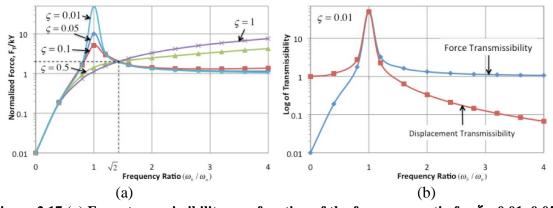

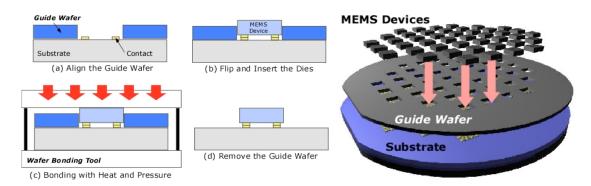

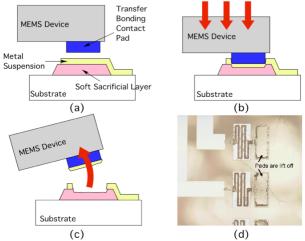

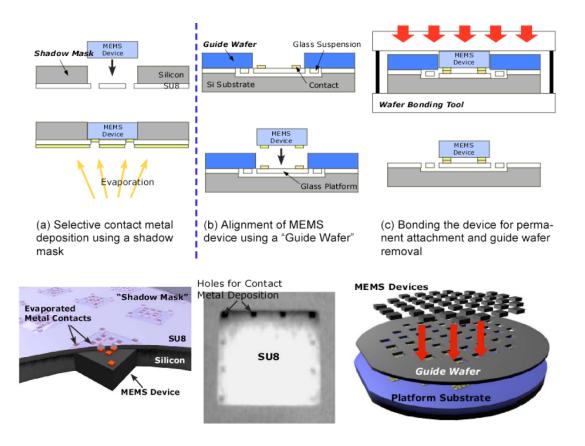

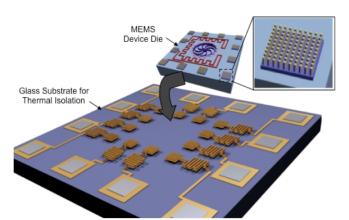

| Figure | 2.18 Procedure of wafer-level device transfer and DRIE isolation technique. (a) Device wafer and platform wafer are aligned by a commercial wafer bonding machine. On the device wafer, MEMS structure is patterned and backside DRIE etch mask is formed. (b) Two wafers are bonded. Bonding contacts form mechanical and electrical connection. (c) Each die is isolated by DRIE etch49 |

| Figure | 2.19 Illustration of the batch die-level transfer technique 49                                                                                                                                                                                                                                                                                                                            |

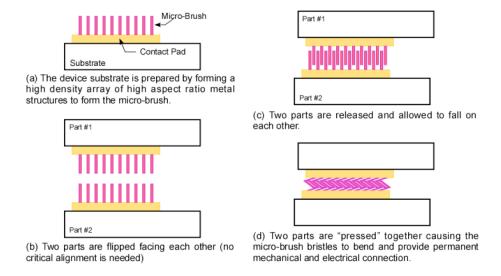

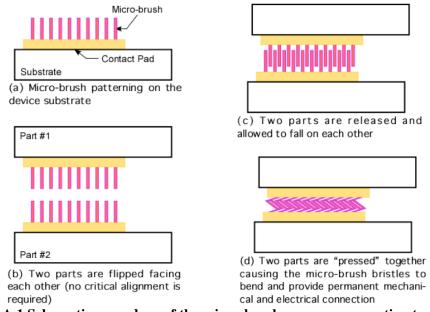

| Figure | 2.20 Schematic views of the micro-brush press-on connection technique 50                                                                                                                                                                                                                                                                                                                  |

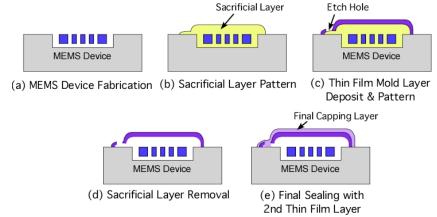

| Figure | 2.21 MEMS device encapsulation using surface micromachining 52                                                                                                                                                                                                                                                                                                                            |

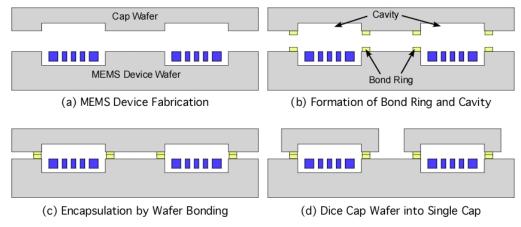

| Figure | 2.22 MEMS packaging using bulk micromachining (wafer bonding) 52                                                                                                                                                                                                                                                                                                                          |

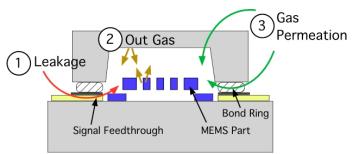

| Figure | 2.23 Major sources of vacuum degradation. 60                                                                                                                                                                                                                                                                                                                                              |

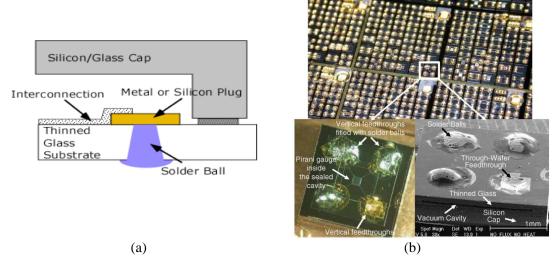

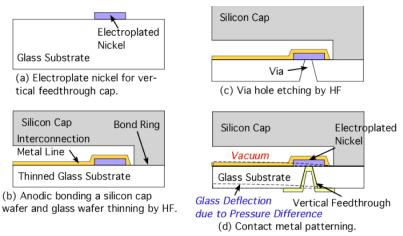

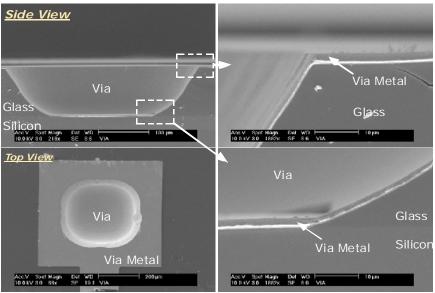

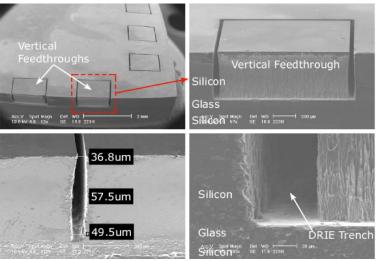

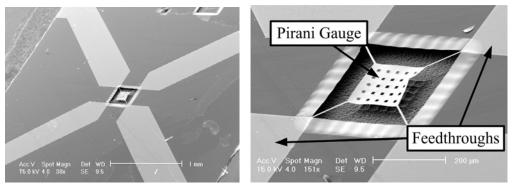

|        | 2.24 (a) Schematic view of the vertical feedthroughs in a thinned glass substrate. (b) Optical and SEM photos of vertical feedthroughs through a glass substrate. A MEMS Pirani gauge is vacuum packaged for measuring a pressure level inside the package [135].                                                                                                                         |

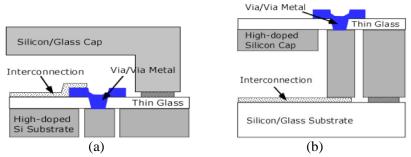

| Figure 2.25 Schematics of the proposed vertical feedthroughs in thin glass/silicon wafer. (a Bottom feedthrough located in the platform substrate, (b) Top feedthrough located in the cap substrate.                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

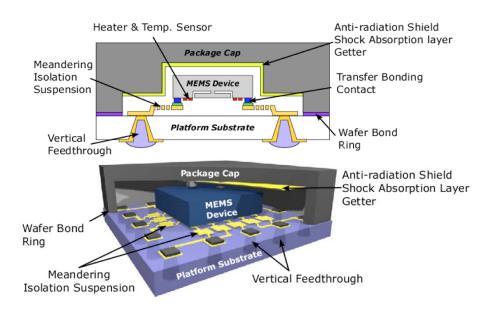

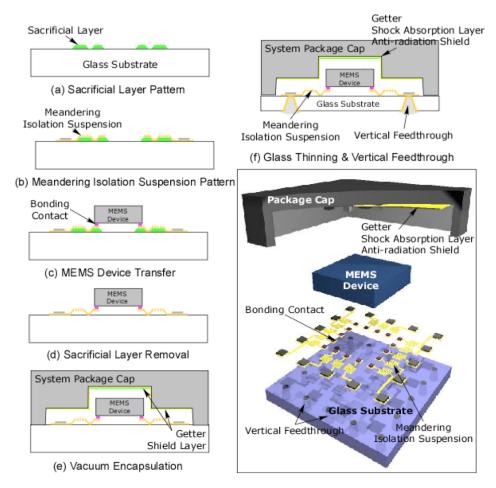

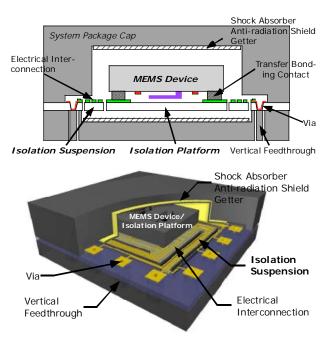

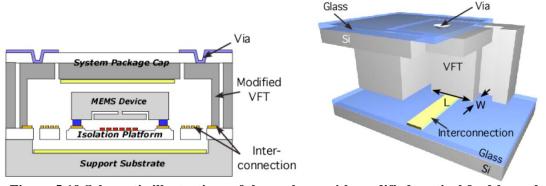

| Figure 3.1 Schematic illustration of the generic environment-resistant package with meandering metal suspensions. The MEMS device is flip-chip transferred on the meandering isolation suspensions, and vacuum encapsulated                                                                                           |

| Figure 3.2 Illustration of the fabrication procedure and exploded view of the package68                                                                                                                                                                                                                               |

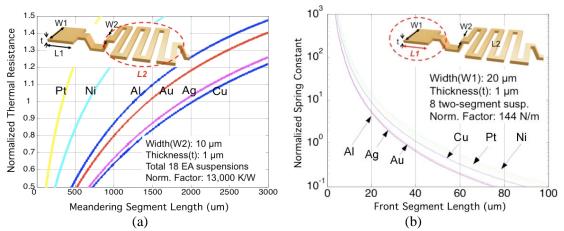

| Figure 3.3 Schematic illustration of the two types of isolation suspensions. Two-segment suspension (left) provides mechanical support, and the single-segment suspension (right enhances the thermal resistance                                                                                                      |

| Figure 3.4 Schematic illustration of the thermal loss paths, and the lumped thermal circuit mode in the package                                                                                                                                                                                                       |

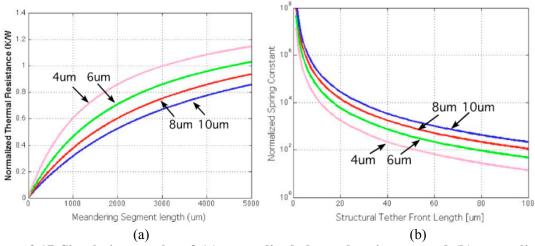

| Figure 3.5 Simulation results of normalized total thermal resistance and spring constant with varying the length of the isolation suspension and suspension materials                                                                                                                                                 |

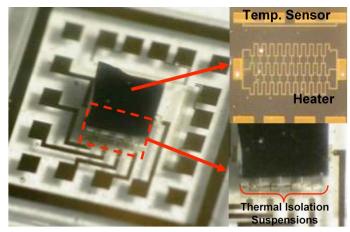

| Figure 3.6 Picture of a package die before encapsulation. A silicon test chip with integrated heater and temperature sensor is attached on the meandering isolation suspensions 76                                                                                                                                    |

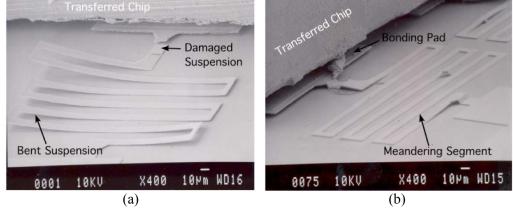

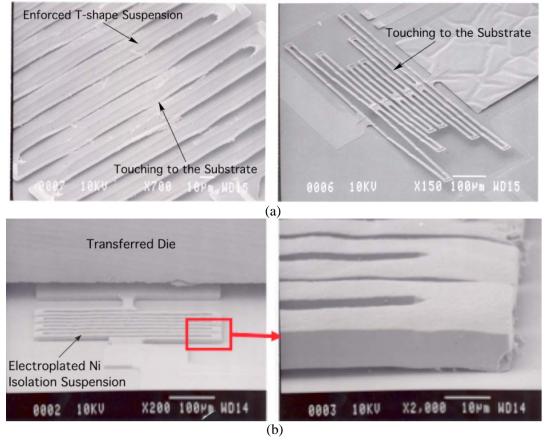

| Figure 3.7 SEM pictures of the isolation suspension made out of evaporated gold. The suspension suffers damage, bending and stiction after sacrificial layer removal 76                                                                                                                                               |

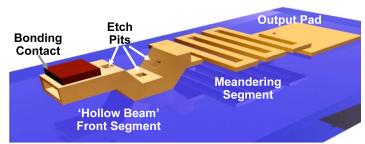

| Figure 3.8 Schematic illustration of the hollow beam suspension. The front hollow beam enhances the stiffness                                                                                                                                                                                                         |

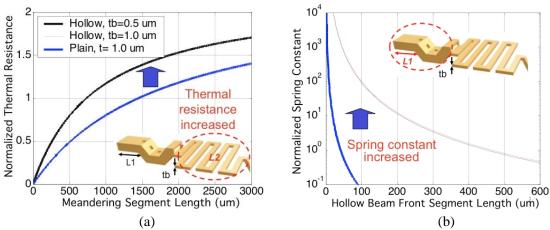

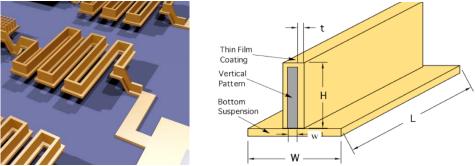

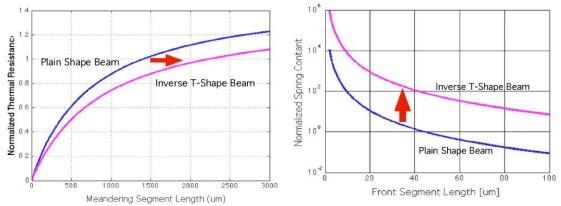

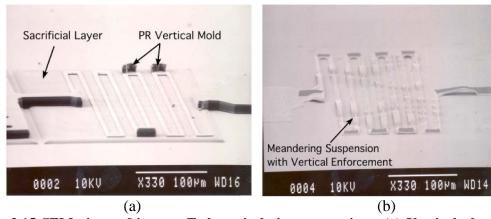

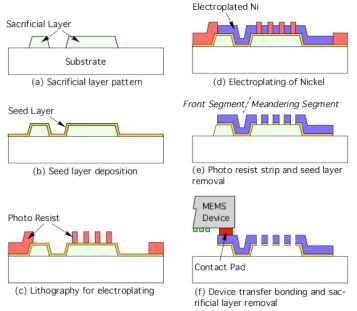

| Figure 3.9 Process procedure for the hollow beam suspension 78                                                                                                                                                                                                                                                        |

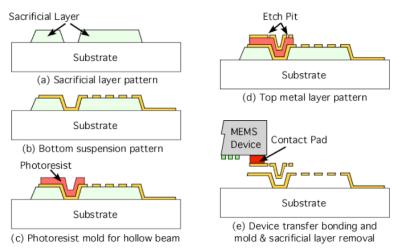

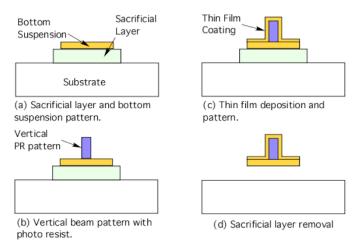

| Figure 3.10 Simulation results of (a) normalized thermal resistance and (b) normalized spring constant for the hollow beam suspension made out of gold                                                                                                                                                                |

| Figure 3.11 Schematic illustration of the inverse T-shape suspension 80                                                                                                                                                                                                                                               |

| Figure 3.12 Process procedure for the inverse T-shape metal suspension 80                                                                                                                                                                                                                                             |

| Figure 3.13 Simulation results of normalized thermal resistance and spring constant for the inverse T-shape suspensions made out of gold. The thermal resistance includes radiation and gas conduction. H=10 $\mu$ m, t=0.2 $\mu$ m, w=4 $\mu$ m, and W=20 $\mu$ m. Other modeling parameters are shown in Table 3.2. |

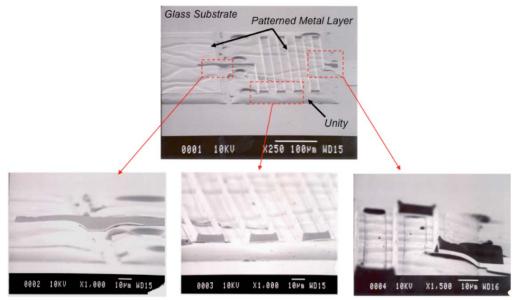

| Figure 3.14 SEM views of the inverse T-shape isolation suspension made of thin film gold Sacrificial layer of Unity <sup>TM</sup> is not removed.                                                                                                                                                                     |

| Figure 3.15 SEM views of inverse T-shape isolation suspension. (a) Vertical photoresist pattern is damaged, and (b) meandering suspension is stuck down to the substrate after removing the sacrificial layer of Unity <sup>TM</sup> .                                                                                |

| Figure 3.16 Process flow of the electroplated metal suspension 84                                                                                                                                                                                                                                                     |

| constant of the electroplated nickel suspensions with varying the suspension thickness.  The thermal resistance includes radiation and gas conduction. Modeling parameters are shown in Table 3.285                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

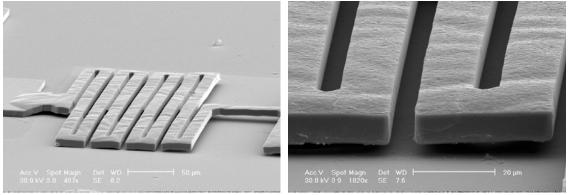

| Figure 3.18 SEM view of the nickel electroplated suspension after sacrificial layer removal 85                                                                                                                                                                                                                                  |

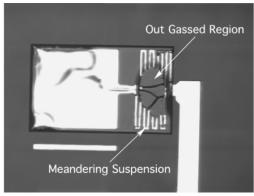

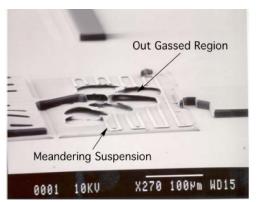

| Figure 3.19 Pictures of photoresist sacrificial layer with meandering metal suspension.  Outgassing has damaged the photoresist pattern causing large voids under the meandering suspension. 87                                                                                                                                 |

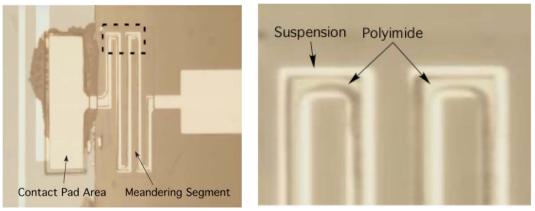

| Figure 3.20 View from the back side (through glass substrate) after oxygen plasma etch for the polyimide sacrificial layer removal. The width of the meandering suspension is 20 μm. 88                                                                                                                                         |

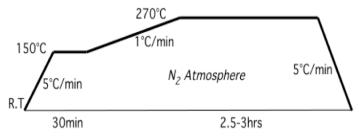

| Figure 3.21 Oven temperature profile for the thermal decomposition of the Unity <sup>TM</sup> 89                                                                                                                                                                                                                                |

| Figure 3.22 Released isolation suspensions after thermal decomposition of Unity <sup>TM</sup> . (a) Inverse T-shape suspension, (b) electroplated nickel suspension 90                                                                                                                                                          |

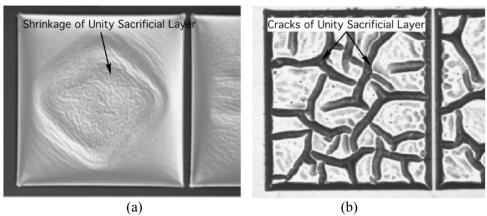

| Figure 3.23 Picture of the Unity <sup>TM</sup> (Top views) (a) after oxygen plasma RIE for 45 min with etch mask of Ti (700 Å), and then (b) sputtering of Cr/Au seed layer for the nickel electroplating. The sacrificial layer suffers shrinkage and cracking of the surface during the processes with elevated temperature91 |

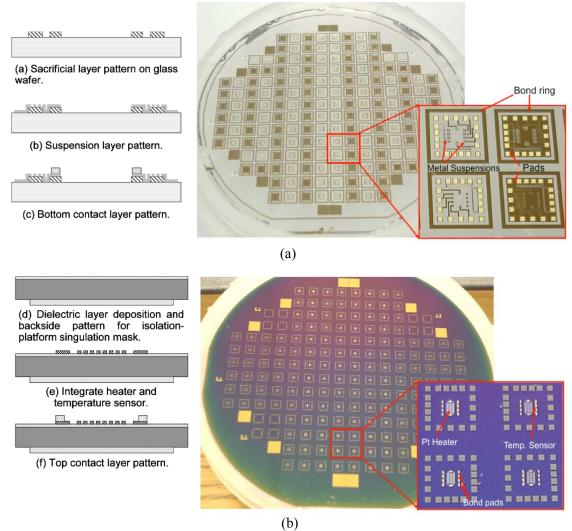

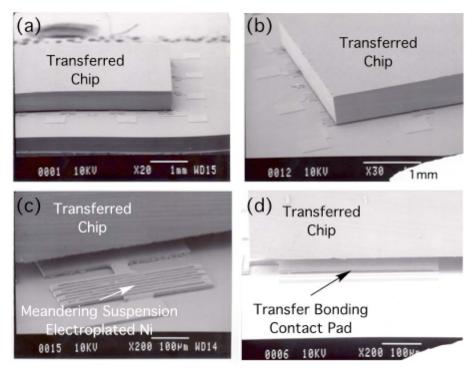

| Figure 3.24 Wafer-level views of (a) glass platform wafer with isolation suspensions and (b) device wafer. Temperature sensor and heater are formed on the device part for a thermal characteristics measurement. On each side, bond pads made out of gold are patterned for Au-Au thermocompression bonding92                  |

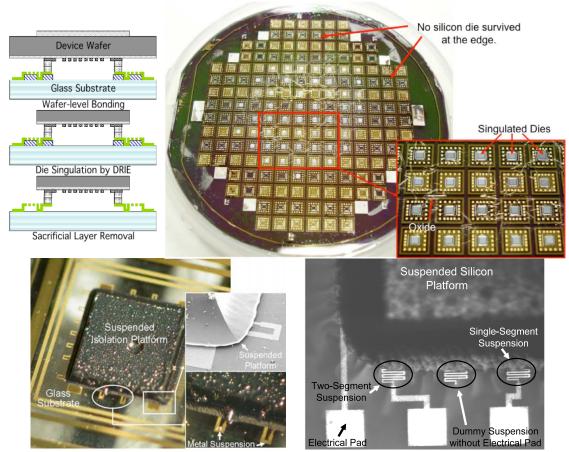

| Figure 3.25 Wafer-level views after the device transfer and singulation processes. Au-Au thermocompression bonding is used for the die attachment93                                                                                                                                                                             |

| Figure 3.26 (a-c) Schematic illustrations for the mechanism of the suspension damage during the transfer bonding. (d) Picture of the damaged suspension after the device transfer process.  94                                                                                                                                  |

| Figure 3.27 Process flow of vertical feedthroughs on the thin glass substrate using wet etching. 96                                                                                                                                                                                                                             |

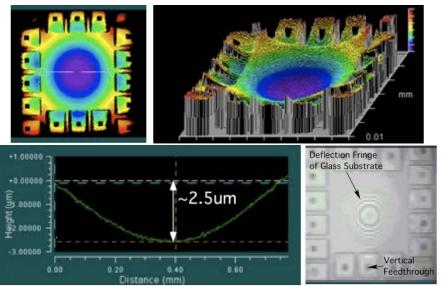

| Figure 3.28 Zygo measurement of the vacuum encapsulated package die. The thin glass substrate is deflected inside due to the pressure difference 97                                                                                                                                                                             |

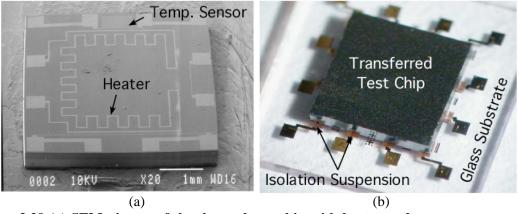

| Figure 3.29 (a) SEM picture of the thermal test chip with heater and temperature sensor, and (b) picture of the thermal test platform for measuring thermal resistance. The thermal test chip is transferred on the meandering isolation suspensions made out of electroplated nickel98                                         |

| Figure 3.30 SEM views of the thermal test platform. The electroplated nickel isolation suspensions support the chip above the glass substrate99                                                                                                                                                                                 |

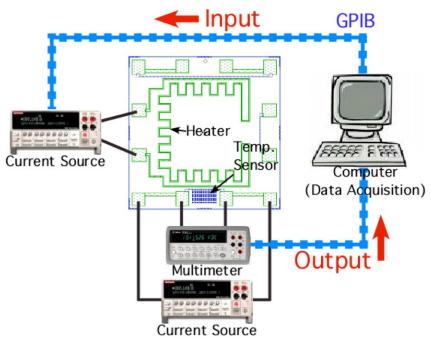

| Figure 3.31 Schematic test setup for measuring the thermal resistance of the thermal platform. 100                                                                                                                                                                                                                              |

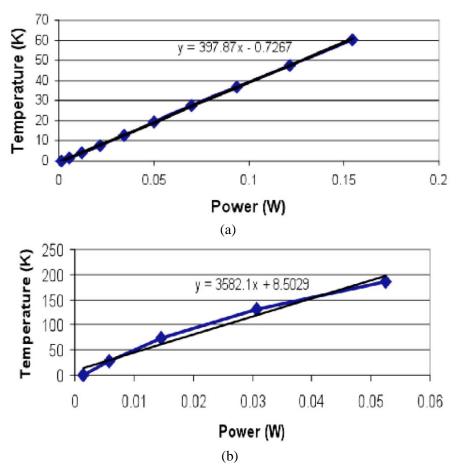

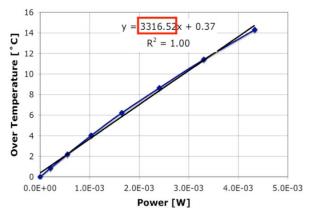

| Figure 3.32 Thermal resistance measurement results: (a) before releasing the thermal platform (397.87 K/W) and (b) after releasing the thermal platform (3582.1 K/W) 101                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

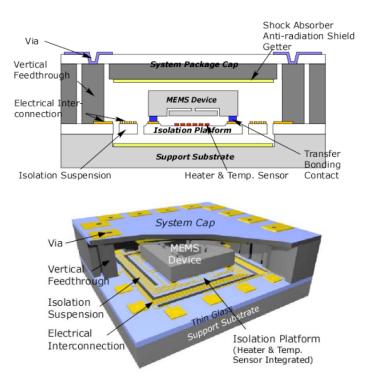

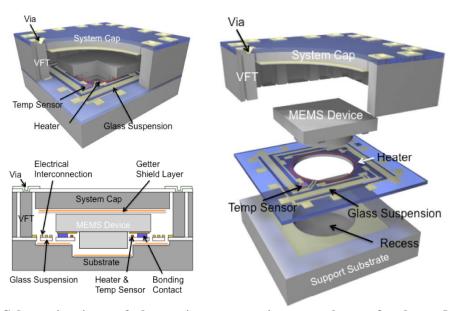

| Figure 4.1 Schematic illustrations of the environment-resistant package with glass isolation platform/suspensions 106                                                                                                                                                             |

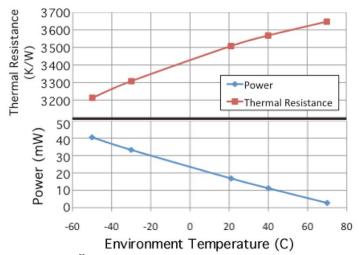

| Figure 4.2 MATLAB® simulation results. (Top) Thermal resistance and (Bottom) power consumption versus environment temperature. The device is assumed to be heated at 80 °C108                                                                                                     |

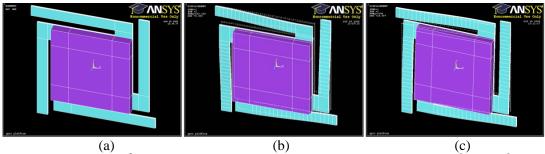

| Figure 4.3 ANSYS® simulation results. (a) Modeling, (b) 1st mode, (c) 2nd and 3rd modes 110                                                                                                                                                                                       |

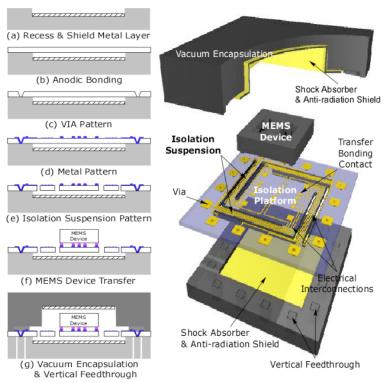

| Figure 4.4 Fabrication procedure and exploded view of the environment-resistant package 111                                                                                                                                                                                       |

| Figure 4.5 SEM views of via hole in the glass with metallization 112                                                                                                                                                                                                              |

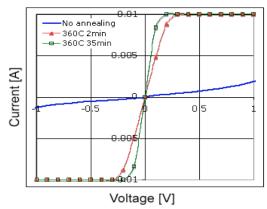

| Figure 4.6 I-V curve of the via contacts. Two connected contacts are measured 113                                                                                                                                                                                                 |

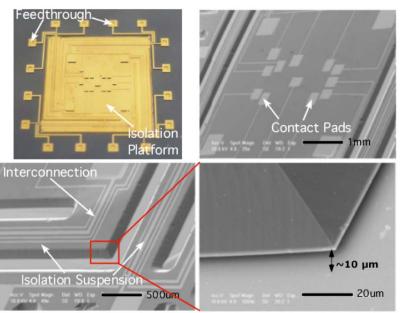

| Figure 4.7 Pictures of the glass isolation platform and suspensions. Bonding contact pads for the device flip-chip transfer are formed on the glass platform. The platform is suspended over the substrate by $\sim 10~\mu m$ .                                                   |

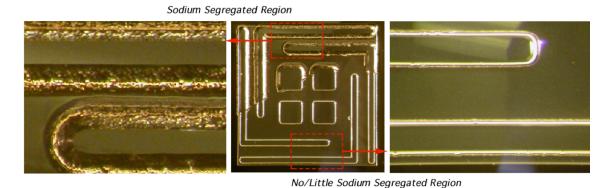

| Figure 4.8 Glass etching profile difference with and without sodium segregation (100 $\mu m$ -thick Pyrex 7740, 49% HF etching for $\sim\!\!15$ min, masking material of Cr/Au/photoresist, 1000 Å/4000 Å/25 $\mu m$ ) 116                                                        |

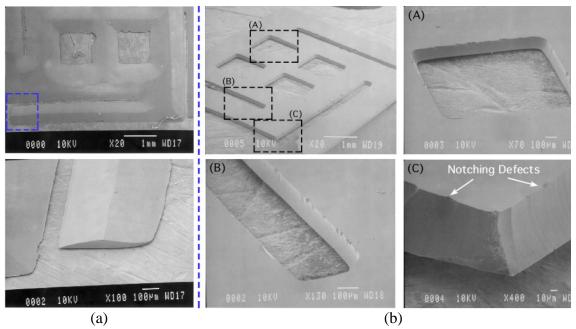

| Figure 4.9 SEM views of etched glass (a) without and (b) with BHF pre-etching for 5 min before the deep glass wet etching. (100 $\mu$ m-thick Pyrex 7740, 49% HF etching for ~15 min masking material of Cr/Au/photoresist, 1000 Å/4000 Å/25 $\mu$ m) 117                         |

| Figure 4.10 Schematic flow of the generic batch die-level transfer technique. (a) Selective pactor material deposition, and (b-c) batch device transfer bonding 118                                                                                                               |

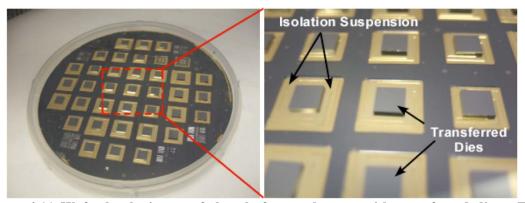

| Figure 4.11 Wafer-level picture of the platform substrate with transferred dies. The transferred dies are permanently bonded on the glass isolation platform, and suspended over the substrate                                                                                    |

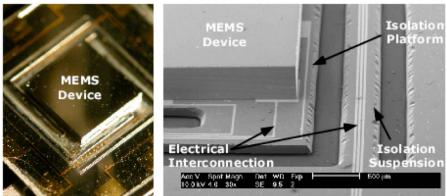

| Figure 4.12 Picture of the isolation platform/suspensions with transferred device. The isolation platform is suspended over the substrate by $\sim 10~\mu m$ .                                                                                                                    |

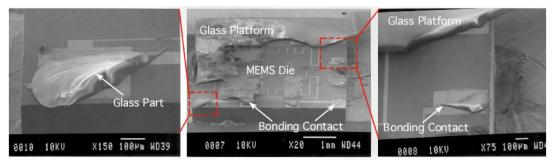

| Figure 4.13 SEM pictures of the transfer bonded die on the glass platform. The glass platform is torn-apart for testing the mechanical strength of the In-Au TLP bonded contacts. Glass parts on the glass platform are ripped-off and transferred onto the MEMS device side. 121 |

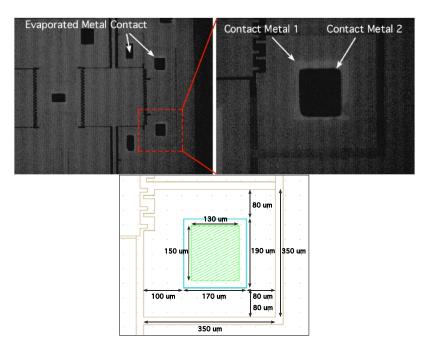

| Figure 4.14 Picture of the gyroscope die with selective pad materials deposited using the shadow mask (Top). Layout and dimensions of the contact pad                                                                                                                             |

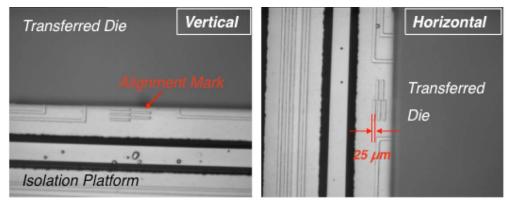

| Figure 4.15 Alignment marks for measuring misalignment. The width of each alignment bar is $25 \ \mu m$ .                                                                                                                                                                         |

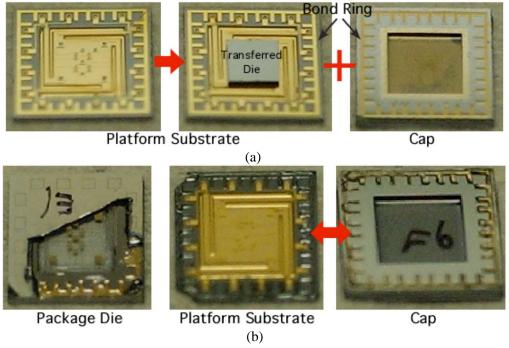

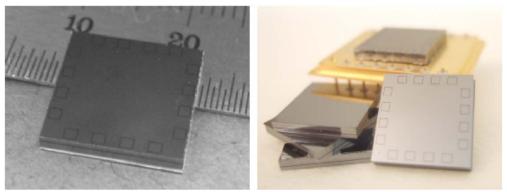

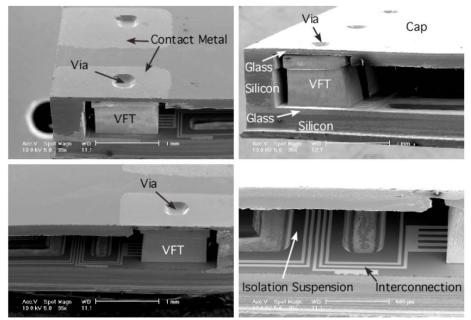

| Figure 4.16 (a) Pictures of the platform substrate die and encapsulation cap die. (b) Pictures of the complete package which is torn apart for the visual inspection 125                                                                                                          |

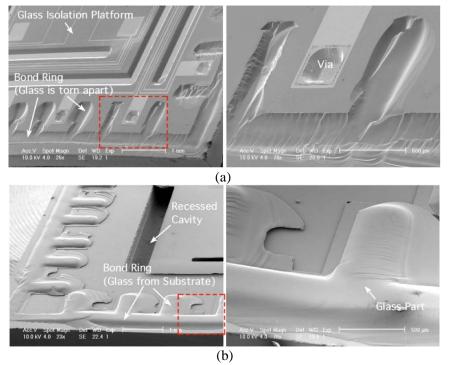

| Figure 4.17 SEM pictures of the Au-Si eutectic bonded package. (a) Platform substrate, an encapsulation cap. Package is torn apart for the visual inspection. The glass part of bond ring is ripped off from the platform substrate. | n the         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Figure 4.18 SEM pictures of the silicon vertical feedthroughs.                                                                                                                                                                       | _ 126         |

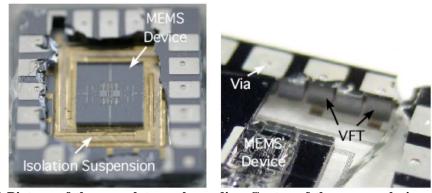

| Figure 4.19 Pictures of the complete package die                                                                                                                                                                                     | _ 127         |

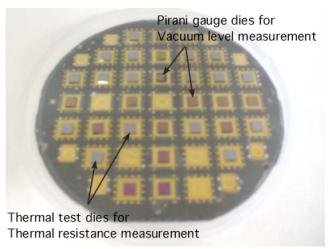

| Figure 4.20 Wafer-level view of the platform substrate with transferred thermal test diese Pirani gauge dies.                                                                                                                        |               |

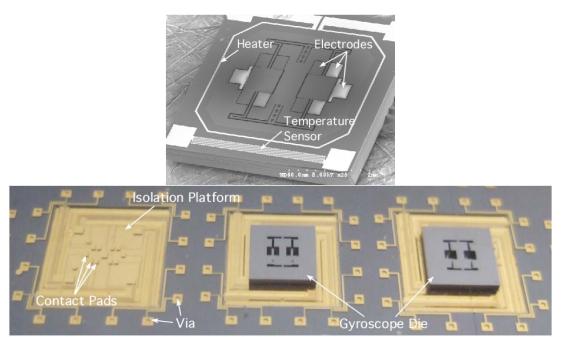

| Figure 4.21 Schematic illustration of the heat dissipation paths in the package, and SEM proof the thermal test die with the heater and temperature sensor.                                                                          |               |

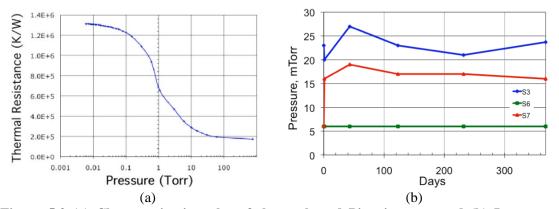

| Figure 4.22 Thermal resistance measurement result. The slope of the data curve shows K/W of thermal resistance.                                                                                                                      |               |

| Figure 4.23 SEM views of the Pirani gauge die and closed-up view of the suspended Pt h [83]                                                                                                                                          |               |

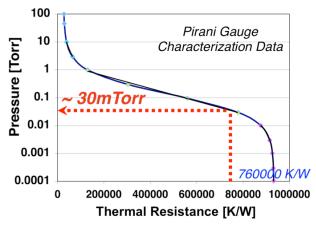

| Figure 4.24 Characterization data of the Pirani gauge. The vacuum packaged Pirani gauge s 760000 K/W which corresponds to ~ 30 mTorr of base pressure inside the package                                                             |               |

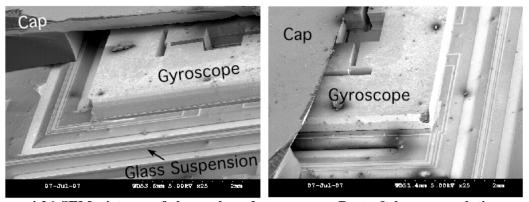

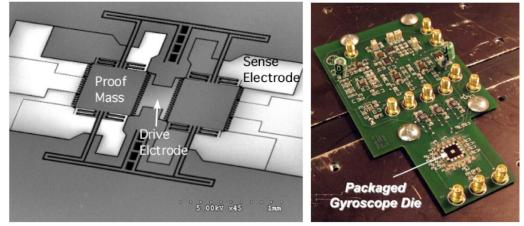

| Figure 4.25 SEM picture of the gyroscope with integrated heater and temperature sensor ( Picture of the isolation platforms with and without transferred gyroscope (Bottom)                                                          | -             |

| Figure 4.26 SEM pictures of the packaged gyroscope. Part of the encapsulation cap is torn for the visual inspection                                                                                                                  |               |

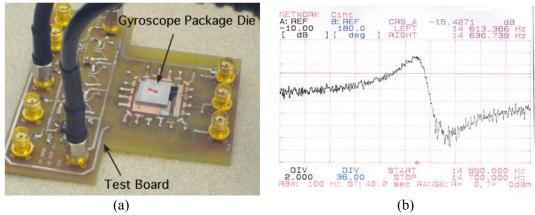

| Figure 4.27 (a) Test board with the gyroscope package die. (b) Gyroscope gain analysis Center frequency is ~14,600 Hz, and Q factor is ~ 700.                                                                                        |               |

| Figure 5.1 Schematic illustrations of the modified package.                                                                                                                                                                          | _ 137         |

| Figure 5.2 Package process flow and exploded view.                                                                                                                                                                                   | _ 140         |

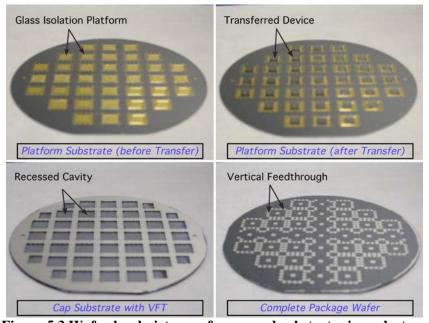

| Figure 5.3 Wafer-level pictures of processed substrates in each step.                                                                                                                                                                | _ 141         |

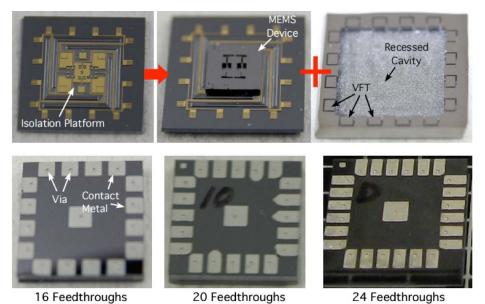

| Figure 5.4 Die-level views of the packaging sequence (Top). Complete package with different feedthrough numbers (Bottom).                                                                                                            |               |

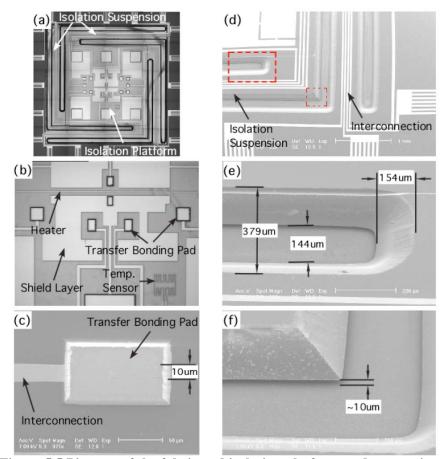

| Figure 5.5 Pictures of the fabricated isolation platform and suspensions                                                                                                                                                             | _ 142         |

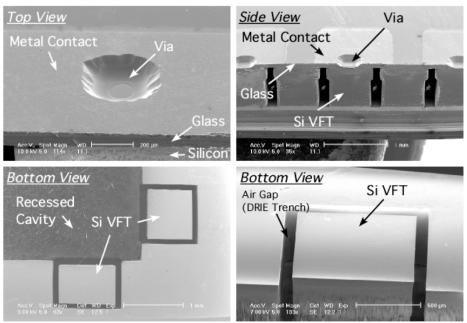

| Figure 5.6 SEM pictures of the feedthroughs in the cap wafer                                                                                                                                                                         | _ 143         |

| Figure 5.7 SEM pictures of the complete package. The package chip is diced across the d the visual inspection.                                                                                                                       |               |

| Figure 5.8 Picture of the complete package die. Center of the encapsulation cap is torn apa                                                                                                                                          | rt for<br>144 |

| Figure | 5.9 (a) Characterization plot of the packaged Pirani gauge, and (b) Long-term vacuum measurement data of the packaged Pirani gauge145                                                                                                                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 5.10 (a) SEM picture of the gyroscope die, and (b) test circuit board for the packaged gyroscope operation. (Georgia Institute of Technology)146                                                                                                                                                                                                                                                                                       |

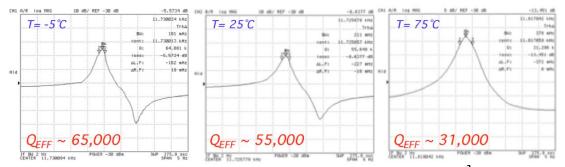

| Figure | 5.11 High-Q mode-matched operation of the vacuum packaged M <sup>2</sup> -TFG prototype at -5 °C, 25 °C, and 75 °C of environment temperature. (Tested at Georgia Institute of Technology)147                                                                                                                                                                                                                                          |

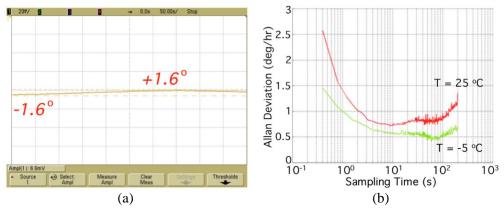

| Figure | 5.12 (a) Response to 0.01 deg/s (36 deg/hr) sinusoidal input rotation signal at $T = 0$ °C, (b) Root Allan variance plot of the vacuum packaged $M^2$ -TFG prototype at $T = 25$ °C and $-5$ °C. (Tested at Georgia Institute of Technology)                                                                                                                                                                                           |

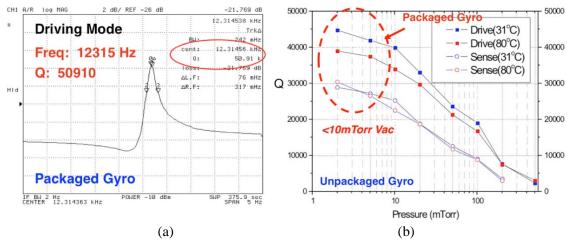

| Figure | 5.13 (a) Drive frequency response of the packaged gyroscope at 25 °C, and (b) quality factor of the unpackaged gyroscope with varying environment pressure level. High quality factor of the packaged gyroscope indicates that the vacuum level inside the package is less than 10 mTorr149                                                                                                                                            |

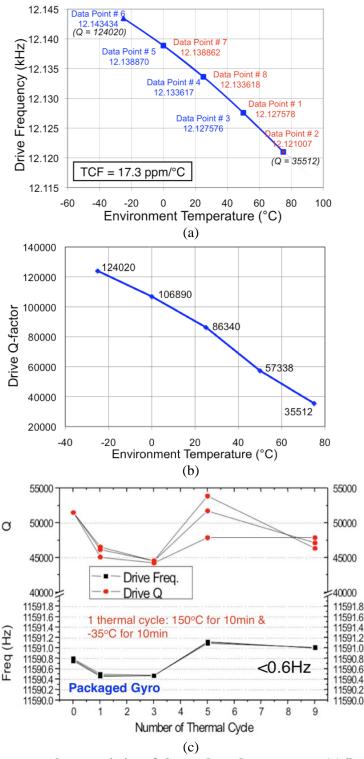

| Figure | 5.14 Temperature characteristics of the packaged gyroscopes. (a) Drive frequency variation with environment temperature cycling from -30°C to 70°C (Tested at Georgia Institute of Technology). (b) Drive quality factor versus environment temperature. (c) Drive frequency and quality factor measurement data after thermal cycling test. The package experiences 150 °C for 10 min and -35 °C for 10 min during one thermal cycle. |

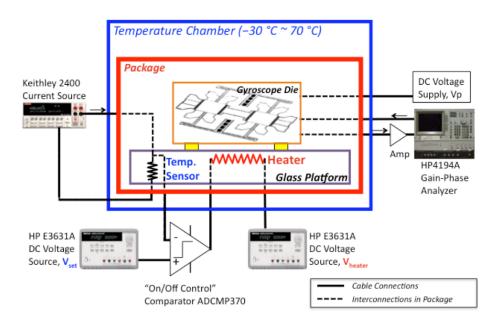

| Figure | 5.15 Schematic diagram for the oven-controlled gyroscope package test 152                                                                                                                                                                                                                                                                                                                                                              |

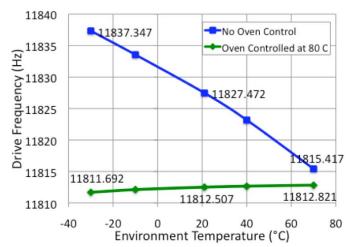

| Figure | 5.16 Drive frequency change with varying environment temperature (-30 °C ~ +70 °C).                                                                                                                                                                                                                                                                                                                                                    |

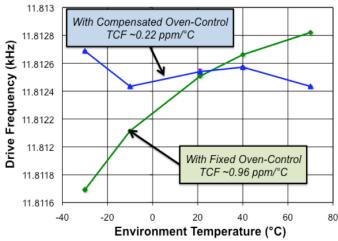

| Figure | 5.17 Drive frequency change with varying environment temperature (-30 °C ~ +70 °C) utilizing fixed oven-control and compensated oven-control 154                                                                                                                                                                                                                                                                                       |

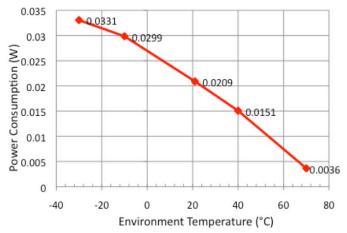

| Figure | 5.18 Measured power consumption for the oven-control with varying the external temperature 154                                                                                                                                                                                                                                                                                                                                         |

| Figure | 5.19 Schematic illustrations of the package with modified vertical feedthrough 155                                                                                                                                                                                                                                                                                                                                                     |

| Figure | 5.20 Schematic view of temperature measurement process in the environment-resistant package 158                                                                                                                                                                                                                                                                                                                                        |

| Figure | 6.1 Schematic views of the environment-resistant package of a large MEMS device 163                                                                                                                                                                                                                                                                                                                                                    |

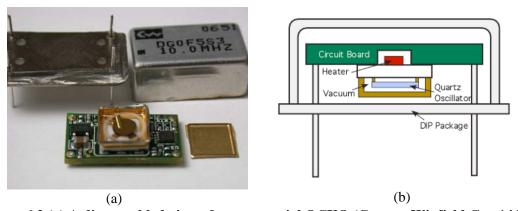

| Figure | 6.2 (a) A disassembled view of a commercial OCXO (Connor-Winfield Co., 14 PIN DIP 5.0V Stratum 3 HCMOS OCXO), and (b) a schematic illustration 164                                                                                                                                                                                                                                                                                     |

| Figure | 6.3 Package applications. (a) Transparent packaging: CMOS image sensors, IR sensors. (b) Package with outlet: Pressure sensors, Microphones. (c) Multiple MEMS packaging.  166                                                                                                                                                                                                                                                         |

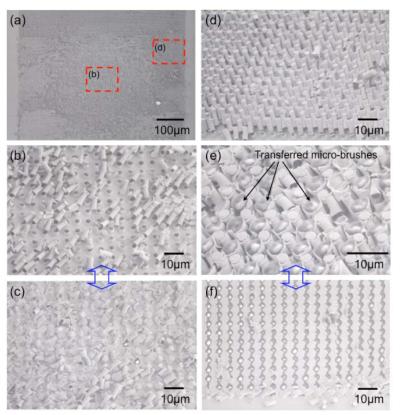

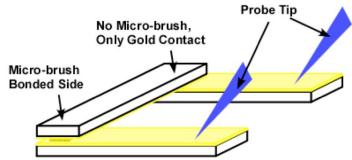

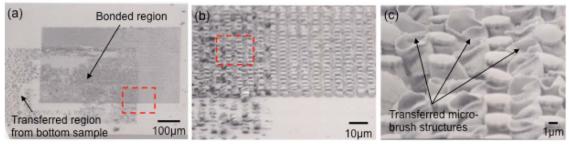

| Figure A.1 Schematic procedure of the micro-brush press-on connection technique                                                                                                                    | 169                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

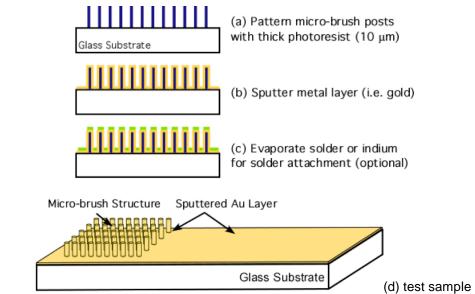

| Figure A.2 Process flow of the micro-brush structures, and a schematic illustratio sample.                                                                                                         |                    |

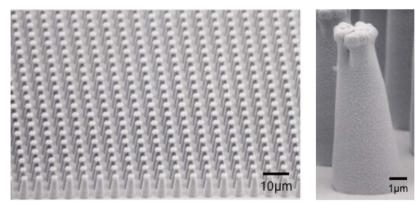

| Figure A.3 SEM pictures of the fabricated micro-brush structures.                                                                                                                                  | 171                |

| Figure A.4 SEM pictures of micro-brush surface after separation. (a) Whole micro-brush surface. (c) Counter part surface of (b). (e) Magnified view of a part of (d). part surface of (d) and (e). | (f) Counter        |

| Figure A.5 A schematic illustration of an electrical resistance measurement test.                                                                                                                  | 173                |

| Figure A.6 SEM pictures of an upper micro-brush sample after being forced apart                                                                                                                    | 173                |

| Figure A.7 A schematic view of a MEMS device transfer on a substrate using the nate technique.                                                                                                     | nicro-brush<br>174 |

## **List of Tables**

| Table 1.1 Environmental factors impacting MEMS devices [3].                                    | 2    |

|------------------------------------------------------------------------------------------------|------|

| Table 1.2 MEMS applications and their specific interface requirements.                         | 6    |

| Table 1.3 IC and MEMS packaging hierarchy [13].                                                | 8    |

| Table 1.4 Key technological requirements in packaging microsystems [8].                        | _ 12 |

| Table 2.1 Key challenges in environment-resistant package.                                     | _ 18 |

| Table 2.2 Temperature stabilization techniques in MEMS                                         | _ 19 |

| Table 2.3 Thermal conductivity, $k_{gas}$ (W/mK), for some gases at T = 0 °C [43].             | _ 25 |

| Table 2.4 Values of molecular heat conductivity [43].                                          | _ 27 |

| Table 2.5 Summary of variables for each thermal mode.                                          | _ 32 |

| Table 2.6 MEMS device transfer techniques.                                                     | _ 46 |

| Table 2.7 MEMS device transfer bonding techniques.                                             | _ 47 |

| Table 2.8 Comparison of two different MEMS packaging approaches [83].                          | _ 53 |

| Table 2.9 Summary of common wafer bonding technologies [98]                                    | _ 56 |

| Table 2.10 Summary of vertical feedthrough techniques for the MEMS packaging application.      | . 62 |

| Table 3.1 Design parameters for the isolation suspension design.                               | _ 72 |

| Table 3.2 Modeling parameters for the isolation suspension design                              | _ 75 |

| Table 3.3 Design parameters of the isolation package for thermal resistance measurement        | _ 98 |

| Table 3.4 Summary of key challenges in developing the environment-resistant package technology | 102  |

| Table 4.1 Design parameters of the isolation package for thermal resistance measurement        | 105  |

| Table 4.2 Summary of parameters for thermal analysis using MATLAB <sup>®</sup>                 | 108  |

| Table 4.3 Summary of ANSYS® simulation for mechanical analysis                                 | 110  |

| Table 4.4 Misalignment measurement data.                                                       | 123  |

| Table 4.5 Summary of Chapter 4.                                                          | 134   |

|------------------------------------------------------------------------------------------|-------|

| Table 5.1 Summary of major modifications in the new package design.                      | 138   |

| Table 5.2 Drive mode frequency measured after major packaging step.                      | 151   |

| Table 5.3 Summary of parameters for oven-control test                                    | 152   |

| Table 6.1 Summary of the environment-resistant package using glass isolation suspensions | . 162 |

| Table B.1 Cost calculation of the package in chapter 3.                                  | 176   |

| Table B.2 Cost calculation of the package in chapter 4.                                  | 177   |

| Table B.3 Cost calculation of the package in chapter 5.                                  | 177   |

# **List of Appendices**

| Appendix A Micro-Brush Press-On Contact: A New Technique for Room Te | emperature Electrical |

|----------------------------------------------------------------------|-----------------------|

| and Mechanical Attachment                                            | 168                   |

| Appendix B Process Cost Analysis                                     | 176                   |

**Abstract**

WAFER-LEVEL PACKAGING FOR ENVIRONMENT-RESISTANT

**MICROINSTRUMENTS**

by

Sang-Hyun Lee

Chair: Khalil Najafi

A generic wafer-level packaging technology for high-performance MEMS

devices, operating under harsh external conditions is developed. This technology not

only provides physical protection from the surroundings, but also provides thermal and

mechanical isolation to enhance device performance. The wafer-level encapsulation and

generic assembly approach accommodate a wide range of MEMS devices with minimal

process lead-time and manufacturing cost. To realize this environment-resistant package,

thermal isolation, mechanical isolation, generic device transfer/integration, wafer-level

vacuum packaging, and feedthroughs have been developed.

xviii

The environment-resistant package consists of two substrates: a platform substrate providing thermal and mechanical isolation, and a package cap wafer providing vacuum encapsulation. Thermal stabilization is provided by oven-controlling the device at a temperature higher than the maximum environment temperature utilizing a heater and a temperature sensor located on the platform or the MEMS device. The heated structure is thermally isolated from the environment by isolation suspensions, anti-radiation shield, and vacuum encapsulation to minimize heat loss. The isolation suspensions are designed with high thermal resistance for minimal heat loss, sufficient stiffness for mechanical support, and flexibility for rejecting environmental vibrations. The package cap seals the MEMS device in vacuum. Vertical feedthroughs for a signal delivery are formed on the platform substrate or the cap wafer. These vertical feedthroughs save area and allow direct attachment to circuit boards. Shock absorption layers, and a getter layer for achieving and maintaining high vacuum are deposited on the inside wall of the package.

Performance is evaluated by packaging Pirani gauges and mode-matched tuning fork gyroscopes. The package size is  $1.2 \times 1.2 \times 0.17 \text{ mm}^3$ , and the packaged device size is  $4.5 \times 4.5 \times 0.5 \text{ mm}^3$ . The package has maintained vacuum pressure of ~6 mTorr for ~1 year. A packaged gyroscope shows a high-Q mode-matched operation (Q ~65,000) at a constant temperature of -5 °C. Allan variance analysis displays an estimated angle random walk (ARW) of 0.012 °/ $\sqrt{h}$ r and a bias instability value of 0.55 °/hr at a constant -5 °C. Drive frequency stability of 0.22 ppm/°C is obtained using a compensated ovencontrol approach. Low power consumption of 33 mW for oven-control at 80 °C is demonstrated when the environment temperature is -30 °C. The temperature control accuracy is  $\pm 0.2$  °C.

## **Chapter 1**

## Introduction

MEMS (Micro-Electro Mechanical System) devices such as micromachined sensors, actuators, and microinstruments have made significant progress since the first commercial products (i.e. pressure sensor) were demonstrated in the 1980's [1]. In recent years, the MEMS business has grown significantly. It is expected to reach almost \$8 Billion by the end of 2008, and double that amount by 2012 with strong growth in the consumer, automotive, medical and industrial sectors (Figure 1.1) [2].

Figure 1.1 MEMS market forecast 2007-2012 in value (dollar) [2].

As the MEMS industry grows, demand for high-performance MEMS devices has also increased. These precision instruments are needed for gas and chemical analysis, environmental and health monitoring, all of which are critical elements of many emerging applications. They often require specific environmental conditions including controlled surrounding atmosphere (i.e. vacuum/hermetic), temperature isolation, and mechanical isolation.

Environmental conditions have a profound impact on the performance of precision micromachined instruments (Table 1.1). External conditions such as temperature, humidity, vibration, and shock can easily corrupt the output of an instrument, and can induce undesirable long-term effects that are not correctable using electronics. The need for protection against environmental conditions becomes more pronounced as the performance levels are increased. Therefore, to realize the potential of high-performance MEMS, it is critical that the environment surrounding the instrument be protected or controlled.

Table 1.1 Environmental factors impacting MEMS devices [3].

| Mechanical | Chemical  | Physical     |

|------------|-----------|--------------|

| Stress     | Gases     | Temperature  |

| Vibration  | Humidity  | Pressure     |

| Shock      | Corrosion | Acceleration |

Typically, the environmental protections of precision MEMS devices have been provided by a package, which has been and will continue to be a significant challenge in the MEMS area. Although the electronics manufacturing industry has a robust and viable infrastructure, direct application of electronics packaging techniques to most MEMS parts is not feasible due to the complexities of their operational structure and domain. Unlike ICs, most MEMS devices interact with the environment or other components

directly or indirectly through electrical, mechanical, thermal, chemical or optical interfaces [4]. For that reason, the MEMS package needs to comply with the requirements of traditional protections as well as provide application-specific elements such as gas access holes in pressure sensors or optical windows in MOEMS devices [5].

Because of the inherent difficulties in packaging MEMS devices, MEMS developers face many challenges in yield, size, standardization, process lead-time and cost. To accommodate the application specific elements in packaging, specially designed packages have typically been employed for housing MEMS devices. These customized packages often require chip-scale handling and assembly processes that are not desirable in mass production. This chip-scale process increases the probability of damage and loss of the device, and the size of the external package is sometimes too large to assemble into small system level products.

Unlike the IC industry, standardization of the packaging technology is not widely available in the MEMS industry. This absence of standard results from the diversity of MEMS applications and operational requirements. Most customized packaging solutions cannot be translated from one specific application to another. This causes long lead-time in developing MEMS, and cost increase.

The cost of single-chip packaging processes, utilizing customized packages, is usually too high to meet the market's needs [6]. Like the IC industry, MEMS developers also have tried to shrink the size of the bare MEMS device to reduce the manufacturing cost. However, this effort alone is not sufficient to maximize the return on investment, because the packaging of small devices increases costs and effort. This size reduction

approach also cannot be applied in some applications such as high-performance inertial sensors due to their inherent physical and operational limitation.

Recently most MEMS development efforts have been focused on reducing size and cost through utilizing wafer-level packaging [7]. A typical wafer-level packaging approach encapsulates the MEMS device before it is singulated from its host wafer. This approach reduces cost as well as protects the device during back-end processes, including dicing and die handling. By encapsulating the device, one can also provide hermetic or vacuum environments, which is often required in stable operation of many sensors, including resonant sensors and infrared detectors.

Furthermore, the MEMS package not only provides the traditional benefits such as simple protections and selective environmental interfaces, but also can be an integral part for improving the performance of the product itself. In other words, in addition to the MEMS specific packaging elements, the package can provide additional functions. For example, by adding thermal and vibration isolation, the packaged MEMS device can be more effectively protected from the environment, and provide higher performance. Typically, these additional functions have been implemented using specially designed large-scale enclosures or board-level system assemblies. This traditional approach requires die-level or chip-scale handling which is not an effective manufacturing approach. It is desirable to integrate these functions during the wafer-level packaging processes before die separation.

Developing a standard, or generic, packaging technology is a desirable feature of future microsystems packaging. This means that different devices with different applications or fabrication processes can be packaged without developing a completely

new set of packaging technology. To realize this approach, the packaging technology needs to be compatible with a variety of device types, and amenable to re-use and reconfiguration.

In summary, a desirable goal in developing MEMS packaging technology is to develop a cost-effective generic wafer-level packaging approach that can preserve and enhance device performance. To fulfill this goal, several key technological challenges in device encapsulation/protection, interconnections/feedthroughs, and device integration/assembly are required to be resolved [8]. The MEMS package should protect the enclosed MEMS device with selective access to the external environment. The package also needs to provide long-term stable, small, and low parasitic feedthroughs. It is also desirable to have a standard, modular assembly technology that can be applied to a wide range of MEMS applications.

The goal of this thesis is to offer generic wafer-level MEMS packaging technologies that provide environmental-resistance functions including thermal and mechanical isolation. In order to fulfill these objectives, a new environmentally isolated wafer-level package technology and a generic device transfer/assembly method for the integration of monolithic and hybrid MEMS into the package have been developed. To evaluate this packaging technology, high-performance gyroscopes, Pirani gauges and test chips have been packaged.

The rest of this chapter introduces typical MEMS packaging processes and requirements. Then, a wafer-level environment-resistant package concept for packaging high-performance MEMS devices will be presented. To close the chapter, the contributions and organization of the thesis are outlined.

## 1.1 MEMS Packaging

#### 1.1.1 Role of MEMS Packaging

Figure 1.2 Functions of packaging: (a) traditional: IC, (b) MEMS packaging [9].

In general, packaging provides four key functions including power delivery, signal mapping/redistribution, thermal management, and environmental protection, as illustrated in Figure 1.2 (a) [9]. Power delivery and signal transport are necessary for the operation of electronics or devices within the package. However, in MEMS packaging, additional interfaces/functions need to be involved (Figure 1.2 (b)).

Table 1.2 MEMS applications and their specific interface requirements.

| Application     | Interface Requirement       |

|-----------------|-----------------------------|

| Pressure sensor | Physical access hole        |

| Inertial sensor | Vacuum/hermetic environment |

|                 | Room for moving parts       |

| IR sensor       | IR access window            |

| Actuator        | Room for moving part        |

| Bio MEMS        | Fluid access hole           |

| Gas sensor      | Gas access hole             |

These interfaces are, directly or indirectly, related to the application, and MEMS has a large number of diverse applications. As a result, a variety of functional interfaces

such as optical, RF, thermal (radiation, conduction, and convection), fluidic (liquids or gases), mechanical (body or surface loadings) and others (Table 1.2), are needed.

Figure 1.3 shows typical MEMS packages of a pressure sensor and inertial sensors. These packages provide not only physical protection but also allow for operational interfaces (Figure 1.3 (a)), hybrid integration with circuitry (Figure 1.3 (b)), or subsystems (Figure 1.3 (c)).

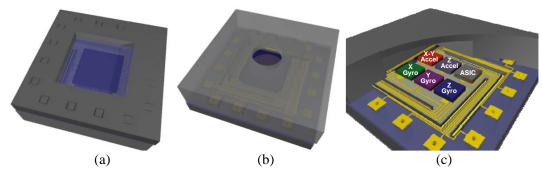

Figure 1.3 Examples of higher level MEMS packages: (a) Conceptual drawing of a typical TO-8 (Transistor Outline-8) pressure sensor package for differential pressure [10], (b) Accelerometer assembled on a hybrid substrate and packaged in a TO can [11], (c) GPS-Inertial navigation system for launch and reentry vehicles [12].

### 1.1.2 MEMS Packaging Procedures

As mentioned before, the packaging of MEMS devices is application dependent, and typically imposes a number of additional requirements compared to standard IC packaging. Packaging can be categorized under five hierarchical levels (Table 1.3) [13]. MEMS devices usually consist of delicate moving structures, and require free space with special environments or selective access holes. Once the moving structure is released, it is susceptible to physical disturbances. Therefore, 0-level packaging or protection is an important step on the path to 1-level packaging.

Table 1.3 IC and MEMS packaging hierarchy [13].

| Level                        |                                 | IC                                                                                 | MEMS                                                                           |

|------------------------------|---------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                              | Element                         | Transistor within IC                                                               | MEMS structure                                                                 |

| 0                            | Interconnected /Encapsulated by | IC metallization                                                                   | Conductive feedthroughs Thin film / shell (temporary or permanent)             |

| 1                            | Element                         | ICs, discrete components                                                           | Discrete MEMS die                                                              |

| "Chip-to-<br>Package"        | Interconnected by               | Package leadframes (single-<br>chip) or multichip module<br>interconnection system | Package leadframes 3D multichip module system Direct flip-chip interconnection |

| 2                            | Element                         | Single- and multi-chip packages                                                    |                                                                                |

| "Package-<br>to-<br>Package" | Interconnected by               | Printed wiring boards                                                              |                                                                                |

| 3                            | Element                         | Printed wiring boards                                                              |                                                                                |

| "Board-to-<br>Board"         | Interconnected by               | Connectors / backplanes (busses)                                                   |                                                                                |

| 4                            | Element                         | Chassis or box                                                                     |                                                                                |

| "System"                     | Interconnected by               | Connectors / cable harnesses                                                       |                                                                                |

After finishing wafer-level fabrication of the MEMS structures, the MEMS dies are singulated with proper 0-level protection. Typically, these dies are separated by a dicing saw tool with a diamond blade while passing a coolant stream over the device wafer. This dicing procedure can damage released MEMS structures unless they are properly protected. The cooling water stream can break and cause stiction of the released structures. Debris or particles generated during this process can prevent operation.