# THE UNIVERSITY OF MICHIGAN INDUSTRY PROGRAM OF THE COLLEGE OF ENGINEERING

COMPUTER COMPONENTS DEVELOPMENT

D. C. Ray H. L. Garner

This report results from research carried out by the Engineering Research Institute under sponsorship of the Department of Defense

September, 1957.

IP-248

The present report has been compiled and edited by D. C. Ray from Report No. 2452-1-P by H. L. Garner, K. R. Monroe, and R. A. Carlsen; Report No. 2452-2-P by R. T. Denton, W. P. Brown, and W. K. Kilmer; Report No. 2452-3-P by R. A. Carlsen, D. C. Ray, and H. L. Garner; and Report No. 2452-4-P by K. R. Monroe and H. L. Garner. Authors of the present report also include H. Ruston and C. Wickman.

## TABLE OF CONTENTS

|     |                                                           | Page |

|-----|-----------------------------------------------------------|------|

| LI  | ST OF ILLUSTRATIONS                                       | V    |

| AB  | STRACT                                                    | viii |

| OB. | JECTIVE                                                   | ix   |

| DES | SIGN PHILOSOPHY                                           | х    |

| 1.  | PULSE AMPLIFIER                                           | 1    |

|     | 1.1 Theoretical Analysis of Pulse Amplifiers              | 1    |

|     | 1.1.1. Qualitative discussion of a pentode, tetrode, or   |      |

|     | cascode triode pulse amplifier                            | 1    |

|     | 1.1.2. Qualitative discussion of a triode pulse amplifier | 14   |

|     | 1.1.3. Linear circuit analysis of possible amplifier      |      |

|     | configurations                                            | 14   |

|     | 1.1.4. Graphical circuit analysis                         | 12   |

|     | 1.2. Experimental Results and Circuits                    | 25   |

|     | 1.2.1. 437A cascode circuit                               | 25   |

|     | 1.2.2. 436A circuit                                       | 27   |

|     | 1.3. Conclusions                                          | 31   |

| 2.  | GATING CIRCUITRY                                          | 32   |

|     | 2.1. Operation of Gating Structure                        | 32   |

|     | 2.2. Gate Requirements for Ideal Diodes                   | 33   |

|     | 2.3. Application of Nonideal Diodes to Gating Circuits    | 34   |

|     | 2.3.1. Diode characteristics                              | 35   |

|     | 2.3.2. Diode specification                                | 7+7+ |

|     | 2.4. Gate Structure Performance                           | 51.  |

|     | 2.4.1. Specification of levels and currents               | 52   |

|     | 2.4.2. Gate performance                                   | 54   |

|     | 2.4.3. Effect of grid current on grid wave-shape          | 57   |

|     | 2.4.4. Upper limit of performance                         | 58   |

|     | 2.5. Summary                                              | 59   |

| 3.  | PULSE TRANSFORMER                                         | 94   |

|     | 3.1. Pulse-Amplifier Analysis                             | 94   |

|     | 3.1.1. General qualitative analysis                       | 94   |

|     | 3.1.2. Resonant-transformer analysis                      | 97   |

|     | 3.1.3. Nonresonant-transformer analysis                   | 98   |

|     | 3.1.4. Summary                                            | 99   |

## TABLE OF CONTENTS (Concluded)

|     |                     |                                                                                                                                                                                                                                                                          | Page                                                 |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|     | 3.2                 | Pulse Transformer Investigation 3.2.1. Core 3.2.2. Equivalent circuit 3.2.3. Winding 3.2.4. General transformer design procedure                                                                                                                                         | 100<br>100<br>106<br>107<br>111                      |

| 4.  | 4.1.<br>4.2.<br>4.3 | ERCONNECTION AND DELAY LINES Interconnection Problem Interconnection Through n Terminated Cables Interconnection Through Singly Terminated Cable 4.3.1. 200 $\Omega$ load 4.3.2. 470 $\Omega$ load 4.3.3. 560 $\Omega$ load 4.3.4. Resistor-diode load The Delay Network | 112<br>112<br>115<br>118<br>120<br>120<br>123<br>125 |

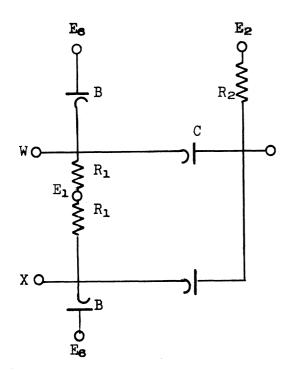

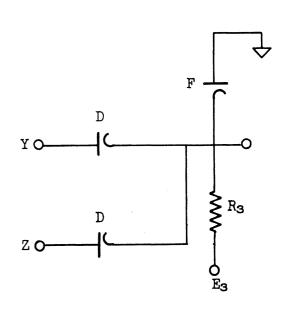

| 5.  | 5.1.<br>5.2.        | TIONAL CIRCUITRY Introduction Incorporation of the Basic Package into Functional Computer Units Standard Package                                                                                                                                                         | 127<br>127<br>127<br>137                             |

| APF | ENDIX               |                                                                                                                                                                                                                                                                          |                                                      |

|     | A                   | THEORETICAL COMPARISON OF VACUUM TUBES                                                                                                                                                                                                                                   | 140                                                  |

|     | В                   | TRIODE INPUT CAPACITANCE                                                                                                                                                                                                                                                 | 141                                                  |

|     | С                   | ANALYSIS OF STEADY-STATE MAGNETIZING CURRENT IN A TUNED, CRITICALLY DAMPED TRANSFORMER                                                                                                                                                                                   | 145                                                  |

|     | D                   | ANALYSIS OF RESONANT-TRANSFORMER PULSE RESPONSE                                                                                                                                                                                                                          | 146                                                  |

|     | E                   | ANALYSIS OF LIMITATIONS ON RESONANT-TRANSFORMER LOAD CURRENT<br>DUE TO RISE-TIME REQUIREMENTS                                                                                                                                                                            | 149                                                  |

|     | F                   | ANALYSIS OF LIMITATIONS ON HIGH-INDUCTANCE TRANSFORMER LOAD CURRENT DUE TO RISE-TIME REQUIREMENTS                                                                                                                                                                        | 151                                                  |

|     | G                   | DERIVATION OF THE REFLECTION EQUATION                                                                                                                                                                                                                                    | 153                                                  |

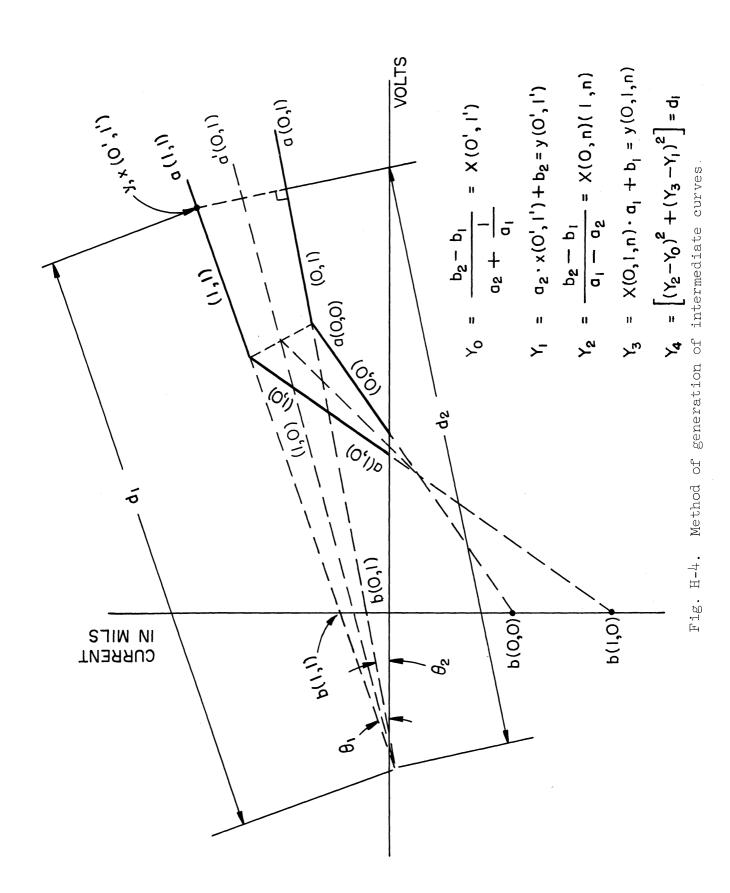

|     | H                   | GRAPHICAL CIRCUIT ANALYSIS EMPLOYING THE IBM 650 DIGITAL COMPUTER                                                                                                                                                                                                        | 156                                                  |

| REF | ERENC               | ES                                                                                                                                                                                                                                                                       | 162                                                  |

#### LIST OF ILLUSTRATIONS

| F'igure                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|                                                                                                                                                                             | 1. Pulse Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

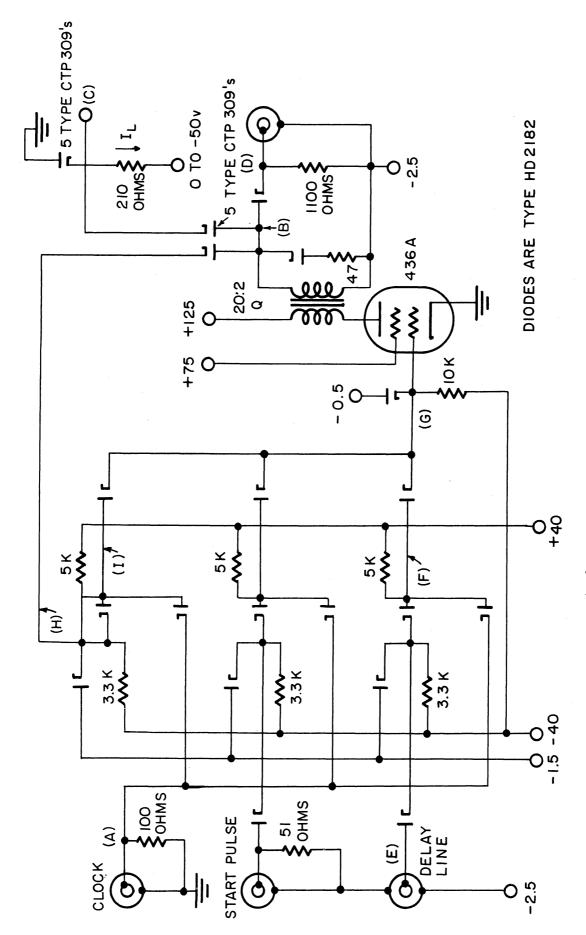

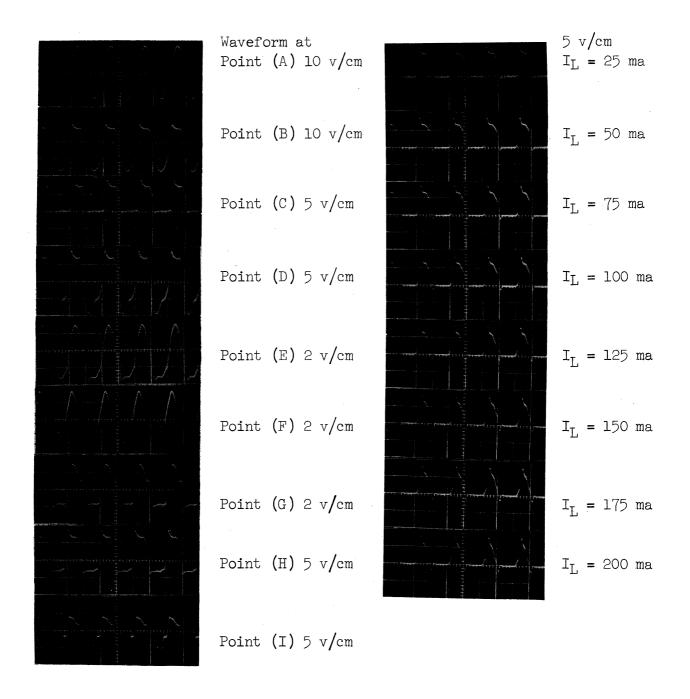

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10<br>1.11<br>1.12<br>1.13<br>1.14<br>1.15<br>1.16<br>1.17<br>1.18<br>1.19<br>1.20<br>1.21<br>1.22<br>1.23 | Pentode operating path. Pentode waveforms. Triode operating path. Triode waveforms. Triode test circuit. Waveforms for the triode circuit. Pentode-triode pulse amplifier. The cascode circuit. Cascode equivalent circuit. Variation of number of gate drives with frequency. Approximate transformer equivalent circuit. Approximate plate load presented by the transformer and its load. Approximation of a waveform by steps. The problem arising from a step grid voltage. Cascode circuit used in the graphical analysis example. Input signal. Plate characteristics for graphical analysis. Results of the graphical analysis example. Experimental waveforms. Cascode 437A dynamic flip-flop for 5-Mc operation. Waveforms for the 437A dynamic flip-flop. 436A dynamic flip-flop for 5-Mc operation. Waveforms for 436A dynamic flip-flop. | 2 3 4 5 7 8 8 9 10 3 14 15 16 18 19 4 25 6 28 29 30 |

| Table 1.1 1.2 1.3 1.4                                                                                                                                                       | Figure of Merit of Cascode Triodes with an Overall Gain of 20 Results of the Graphical Analysis Example Variation of Tube Currents with Load Current for Cascode 437A's Variation of Tube Currents with Load Current for the 436A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11<br>20<br>27<br>27                                |

|                                                                                                                                                                             | 2. Gating Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

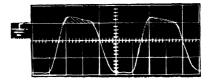

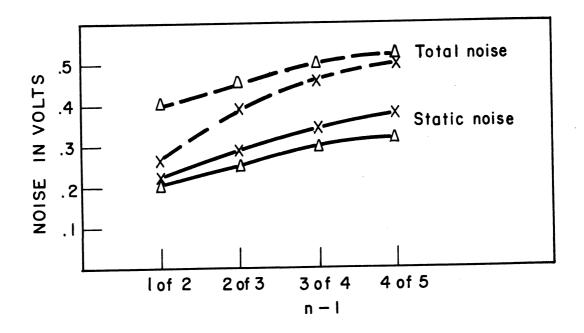

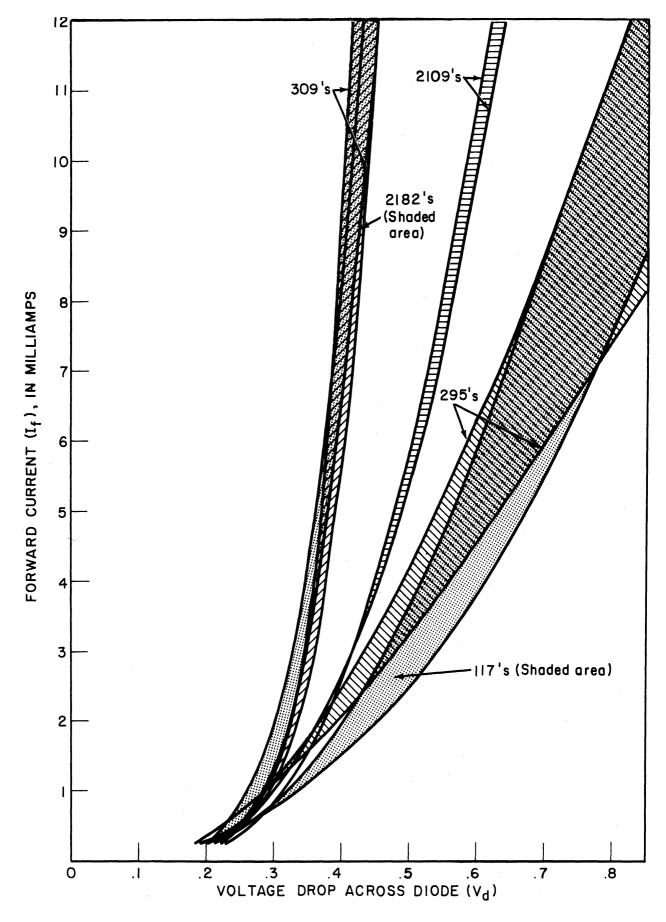

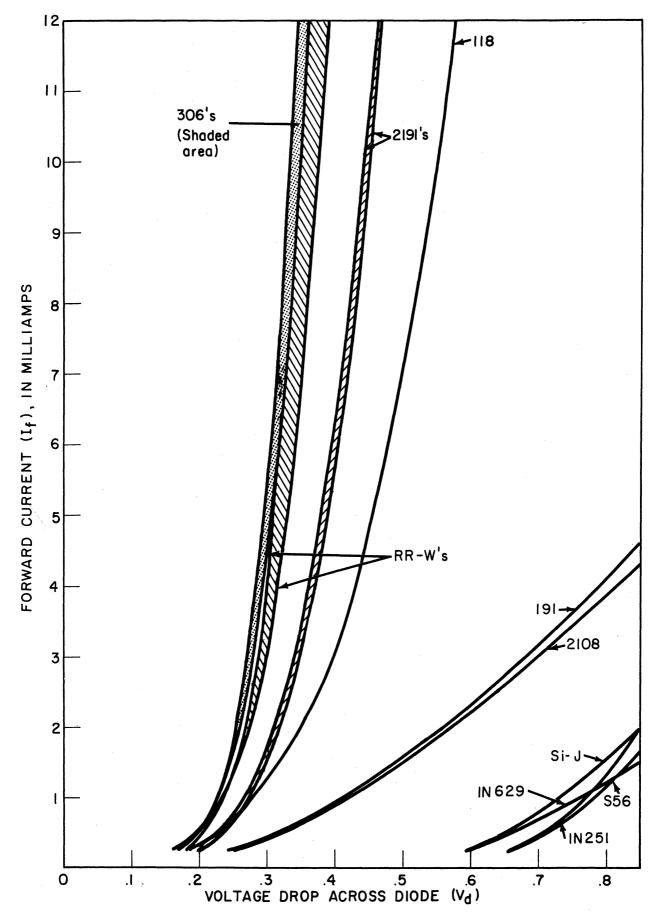

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                                                                                                             | Effect of back bias on back recovery.  Effect of circuit series resistance R' on back recovery.  Back recovery at a 10 Mc repetition rate.  Noise as a function of the number of gates pulsed.  Static characteristics of representative diodes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61<br>62<br>63<br>64<br>65                          |

## LIST OF ILLUSTRATIONS (Continued)

| Figure |                                                                           | Page |

|--------|---------------------------------------------------------------------------|------|

| 2.6    | Deviation of static characteristics.                                      | 66   |

| 2.7    | Static characteristics of additional diodes tested.                       | 67   |

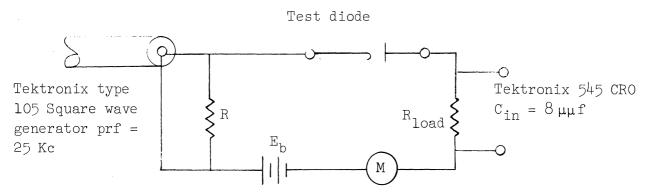

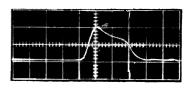

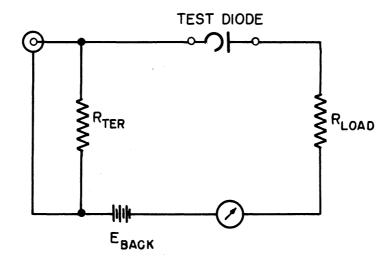

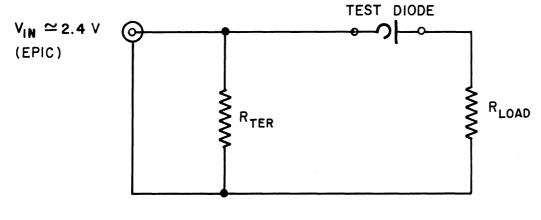

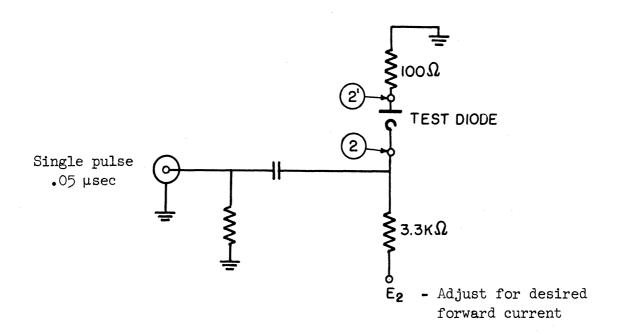

| 2.8    | Back transient test circuit at 25 Kc.                                     | 68   |

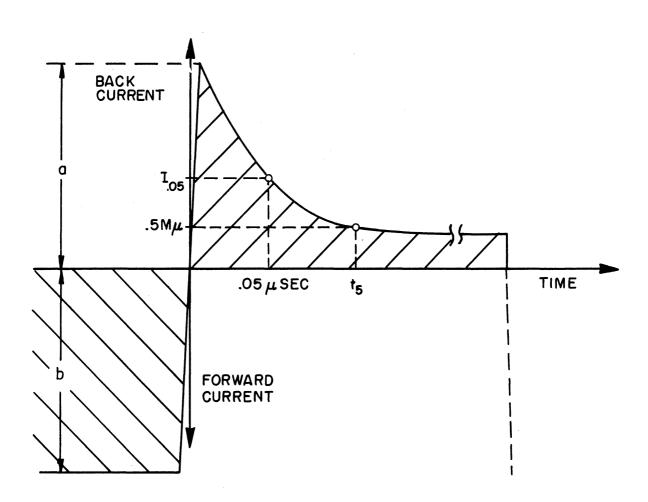

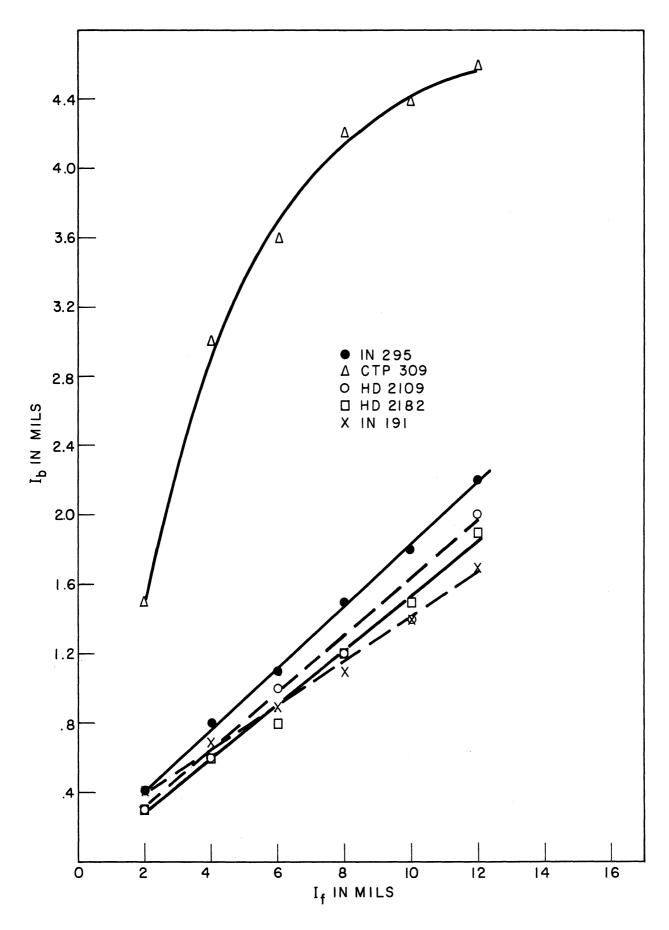

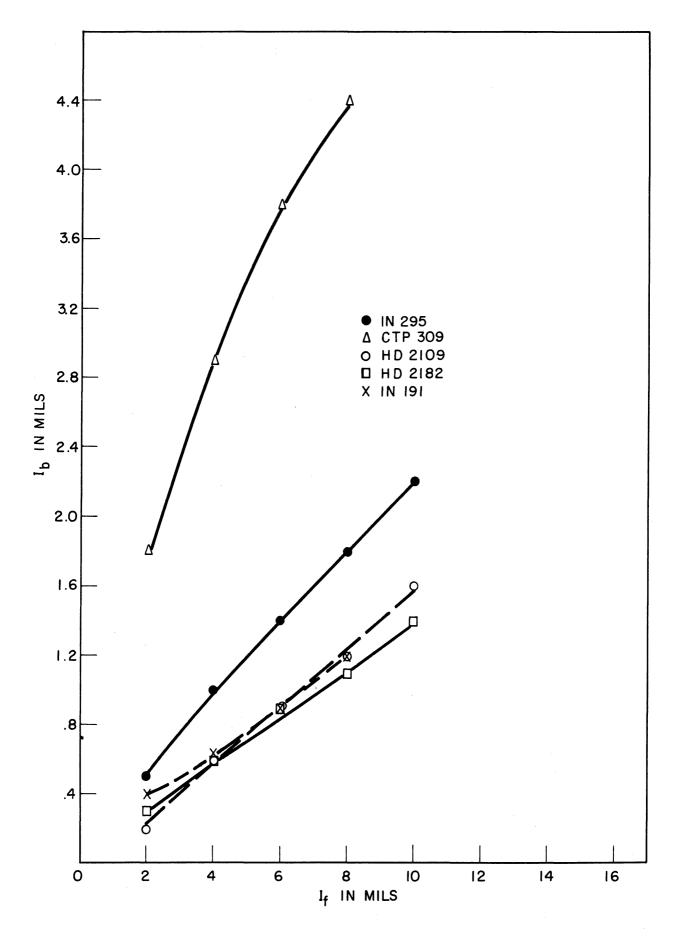

| 2.9    | Current at t = .05 $\mu$ sec vs forward current, $E_b$ = -1.5 v.          | 69   |

| 2.10   | Current at $t = .05 \mu sec$ vs forward current, $E_b = -3.0 \text{ v}$ . | 70   |

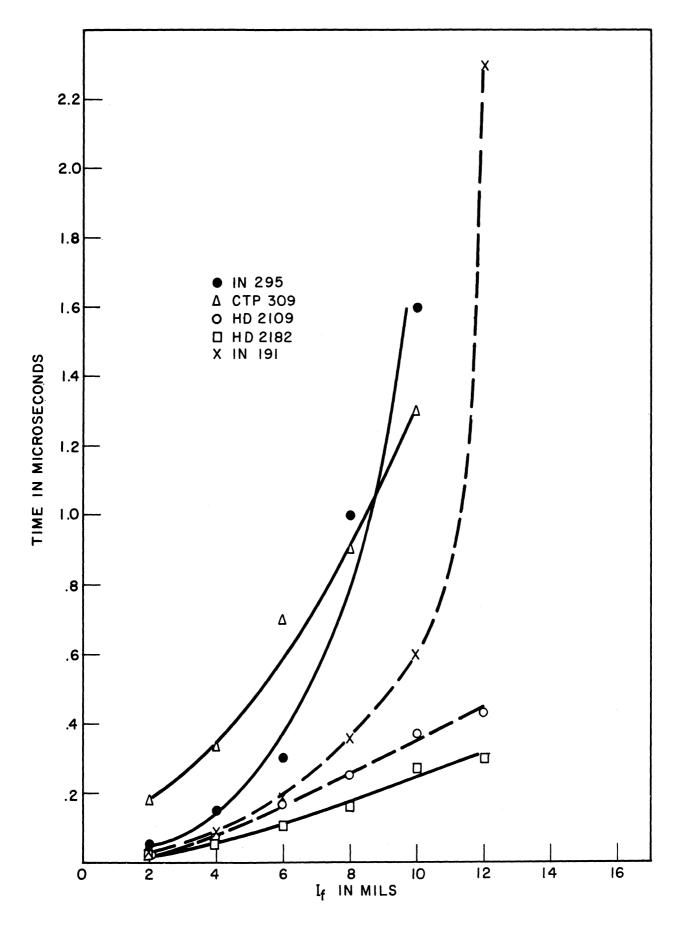

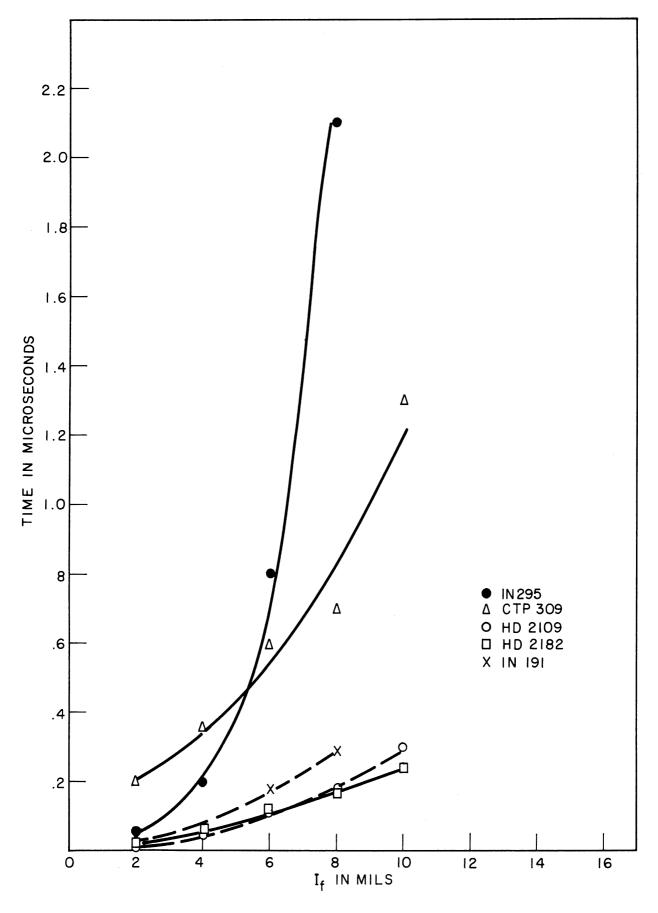

| 2.11   | Time at $I_b = .5$ mil vs forward current, $E_b = -1.5$ v.                | 71   |

| 2.12   | Time at $I_b = .5$ mil vs forward current, $E_b = -3.0$ v.                | 72   |

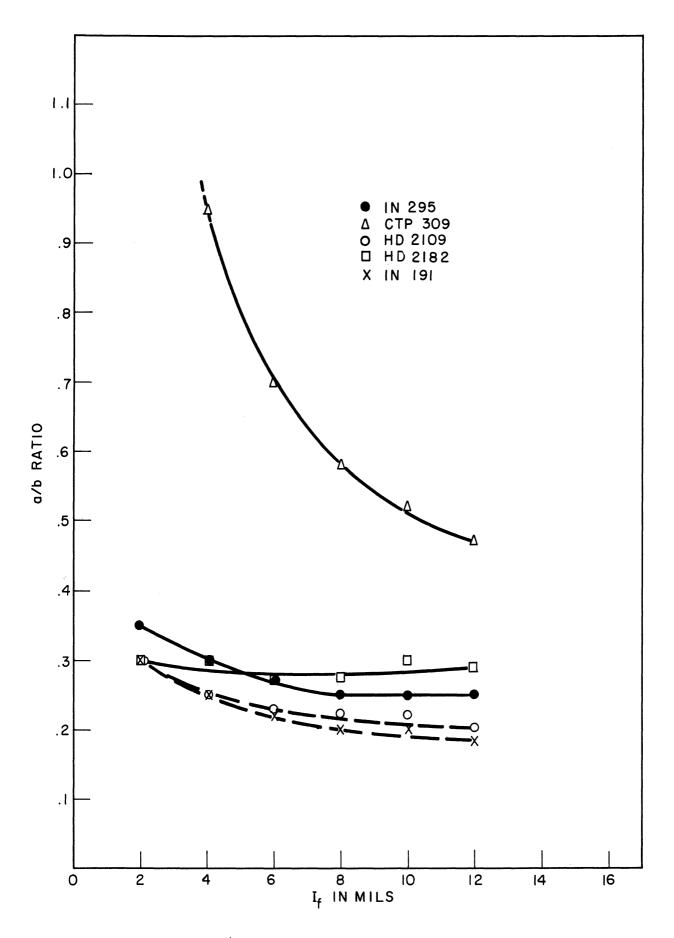

| 2.13   | a/b ratio vs forward current, $E_b = -1.5 \text{ v}$ .                    | 73   |

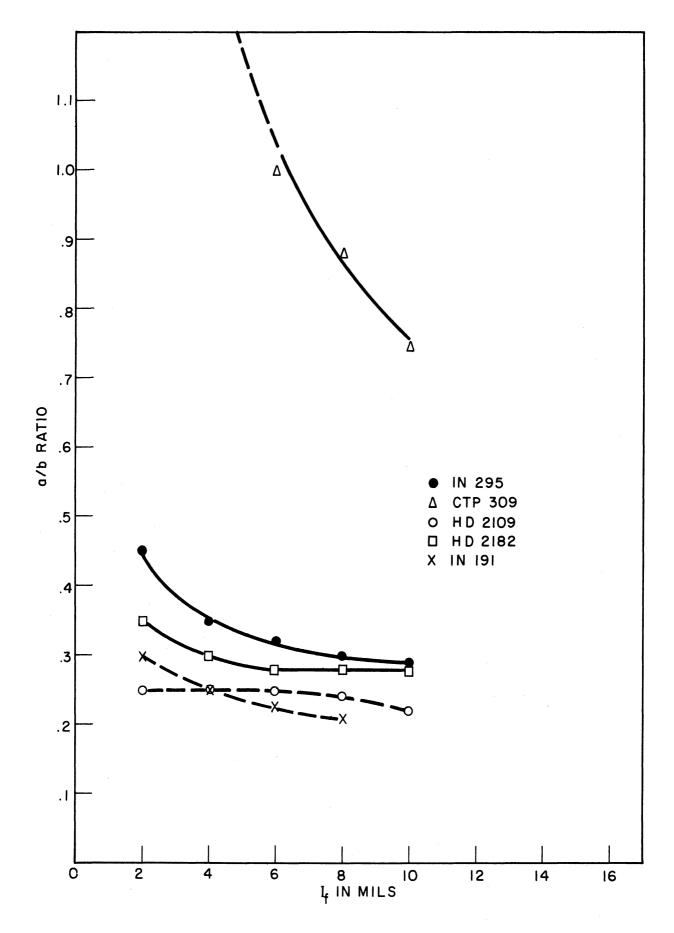

| 2.14   | a/b ratio vs forward current, $E_b = -3.0 \text{ v}$ .                    | 74   |

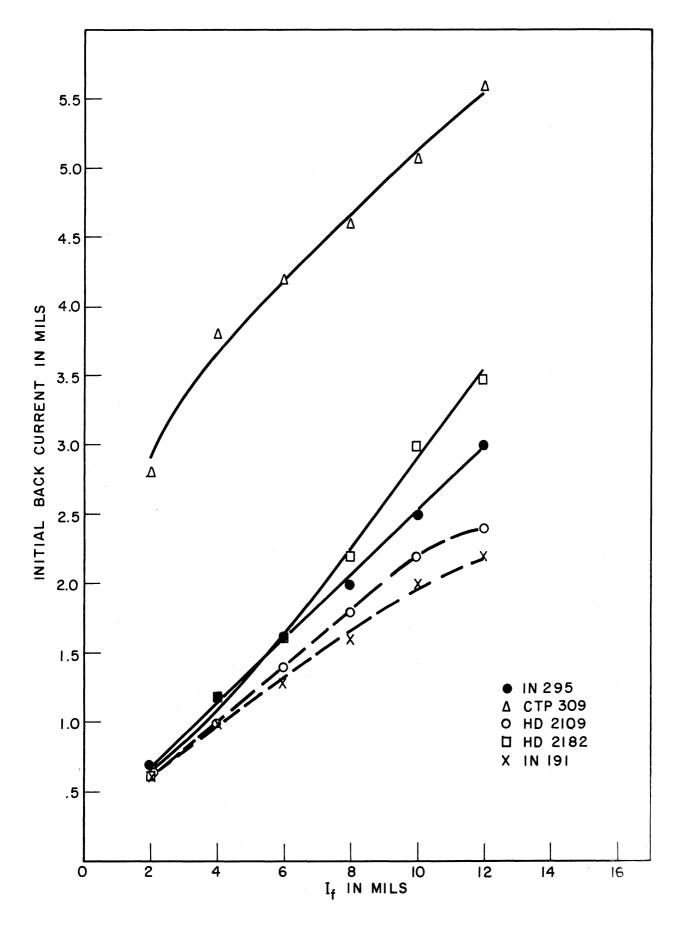

| 2.15   | Initial back current vs forward current, $E_b = -1.5 \text{ v}$ .         | 75   |

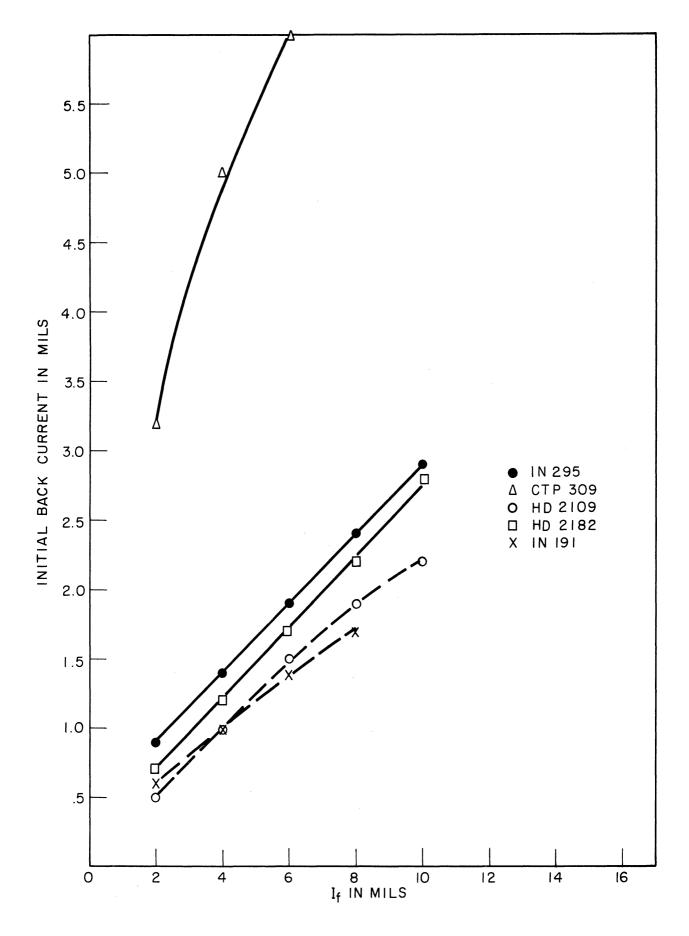

| 2.16   | Initial back current vs forward current, $E_b = -3.0 \text{ v}$ .         | 76   |

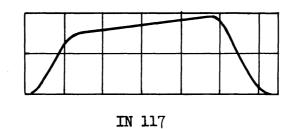

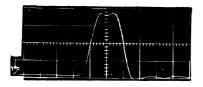

| 2.17   | Forward transients.                                                       | 77   |

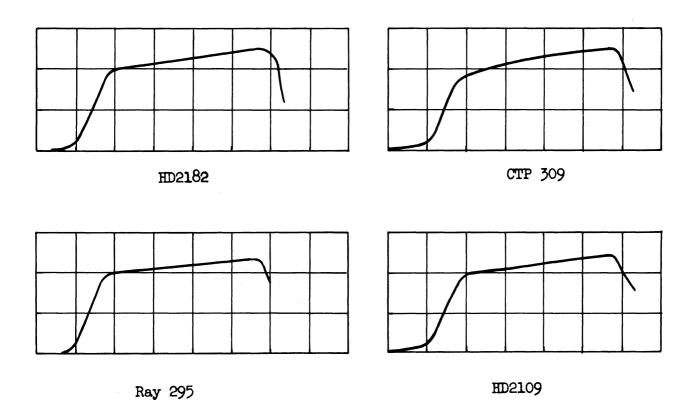

| 2.18   | Determination of the best clip diode (G).                                 | 78   |

| 2.19   | Effect of static characteristics on wave shape.                           | 79   |

| 2.20   | Experimental determination of the best grid-clamp diode.                  | 80   |

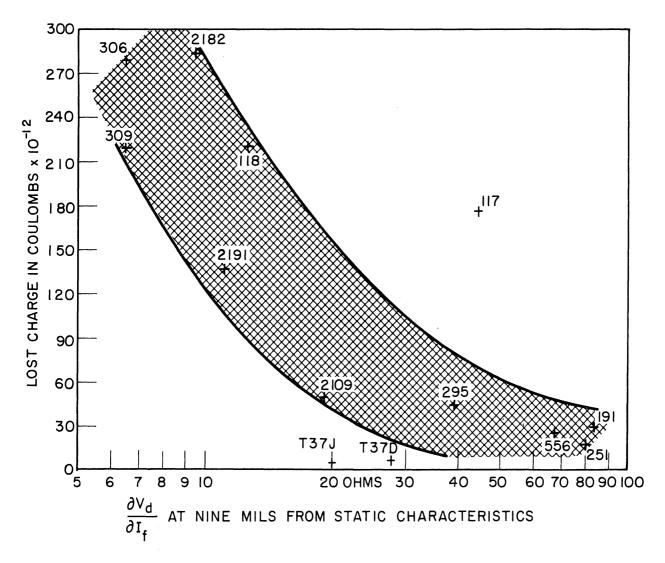

| 2.21   | Experimental correlation between static characteristics and               |      |

|        | lost charge.                                                              | 81   |

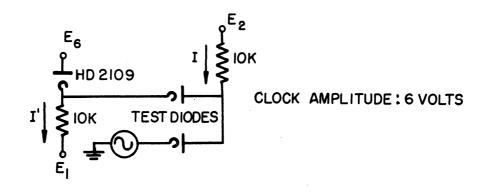

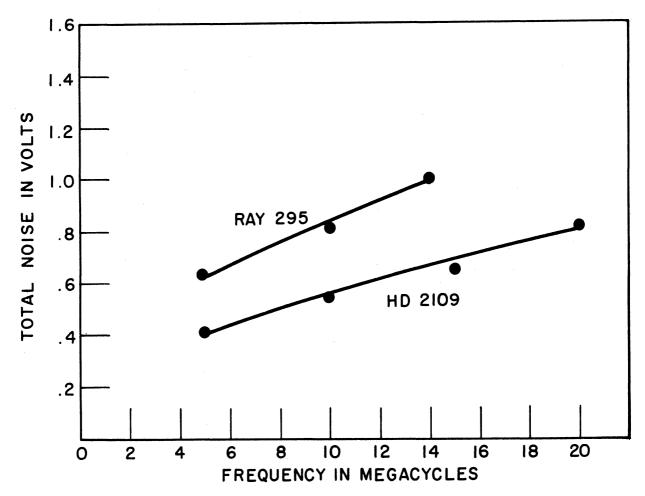

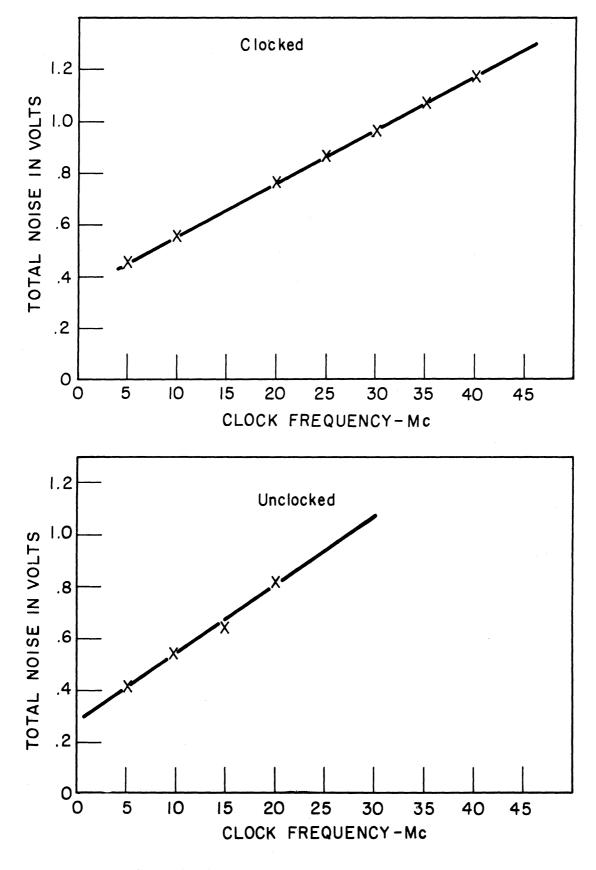

| 2.22   | Noise variation with frequency.                                           | 82   |

| 2.23   | 10 Mc experimental package.                                               | 83   |

| 2.24   | 5 Mc experimental package.                                                | 84   |

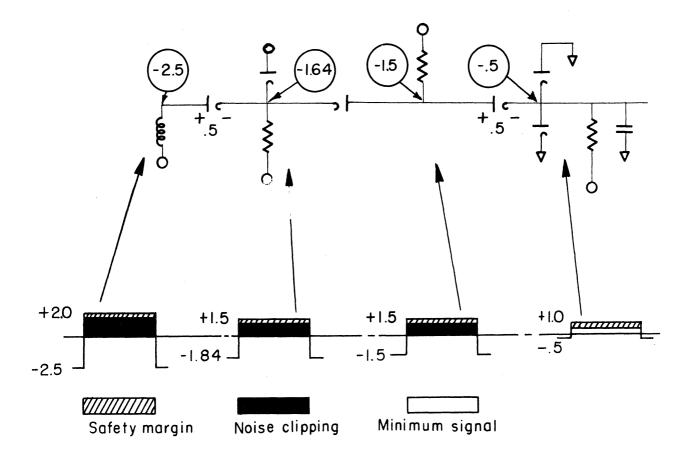

| 2.25   | 10 Mc gate performance.                                                   | 85.  |

| 2.26   | 10 Mc gate performance.                                                   | 86   |

| 2.27   | 5 Mc gate performance.                                                    | 87   |

| 2.28   | 5 Mc gate performance.                                                    | 88   |

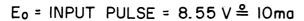

| 2.29   | Upper limit of performance.                                               | 89   |

| Table  |                                                                           |      |

| 2.1    | Back Recovery as a Function of Forward Current                            | 90   |

| 2.2    | Experimental Determination of the Best "And" Diode                        | 92   |

| 2.3    | Secondary Factors Affecting Noise                                         | 93   |

|        |                                                                           |      |

|        | 3. Pulse Transformer                                                      |      |

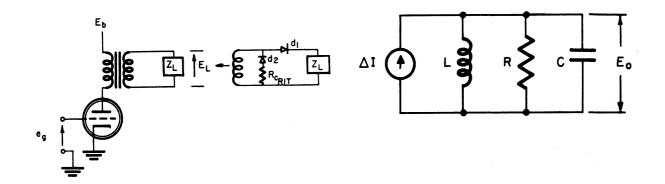

| 3.1a   | Typical pulse-amplifier configuration.                                    | 95   |

| 3.1b   | Equivalent circuit for pulse amplifier.                                   | 95   |

| 3.2    | Vacuum-tube plate characteristics.                                        | 95   |

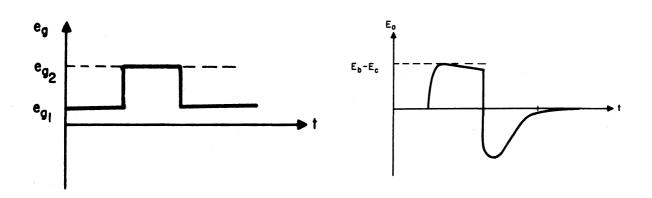

| 3.3a   | Input signal to grid.                                                     | 95   |

| 3.3b   | Transformer output voltage.                                               | 95   |

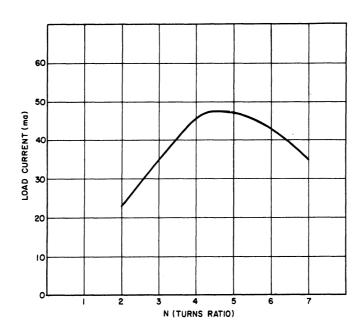

| 3.4    | Relationship of load current to turns ratio for nonresonant               |      |

|        | transformer.                                                              | 99   |

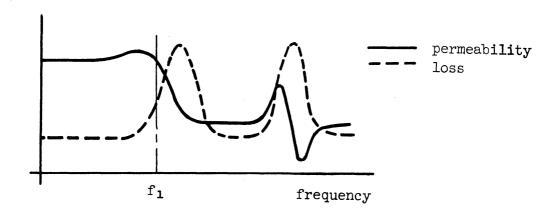

| 3.5    | Frequency characteristics of ferrite materials.                           | 103  |

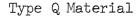

| 3.6    | Open circuit damping characteristics.                                     | 103  |

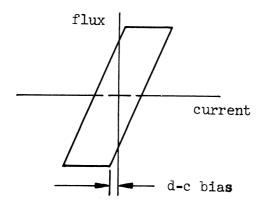

| 3.7    | Idealized hysteresis loop.                                                | 104  |

## LIST OF ILLUSTRATIONS (Concluded)

| Figure       |                                                           | Page |

|--------------|-----------------------------------------------------------|------|

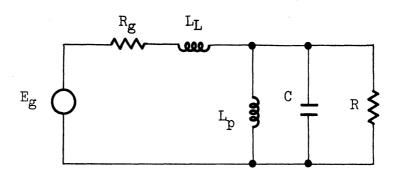

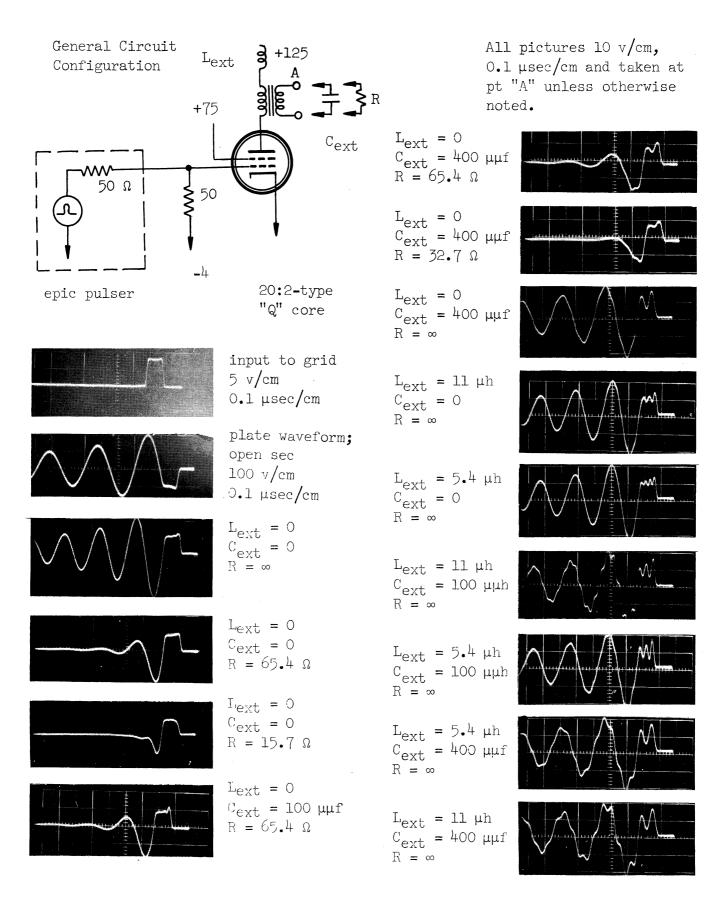

| 3.8          | Transformer equivalent circuit.                           | 106  |

| <b>3.</b> 9  | Pulse response when the magnitude of the stray parameters |      |

|              | is increased.                                             | 108  |

| 3.10         | Final winding form.                                       | 109  |

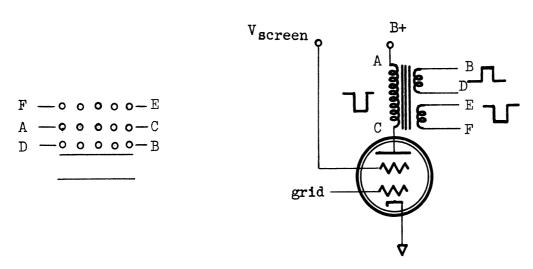

| 3.11         | Winding configurations.                                   | 110  |

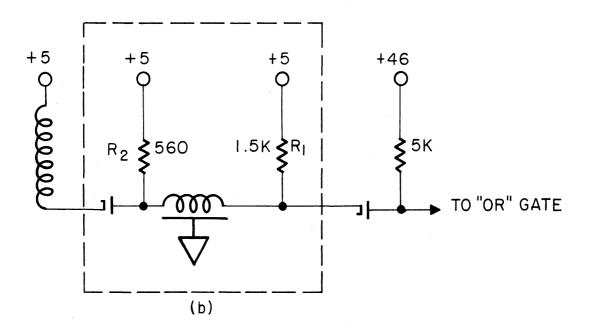

| <b>3.1</b> 2 | Circuit for measurement of dynamic capacitance.           | 110  |

|              | 4. Interconnection and Delay Lines                        |      |

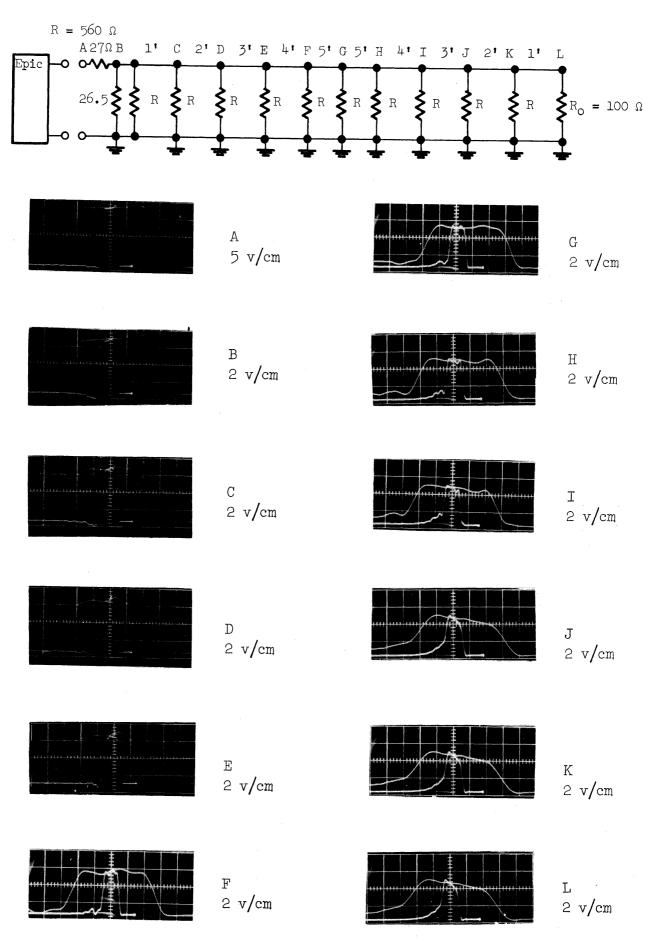

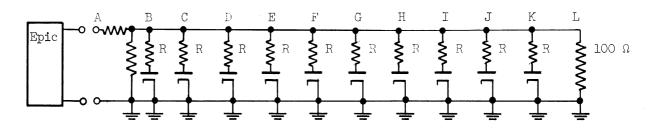

| 4.1          | Interconnection through n terminated cables.              | 112  |

| 4.2          | Interconnection through singly terminated cable.          | 113  |

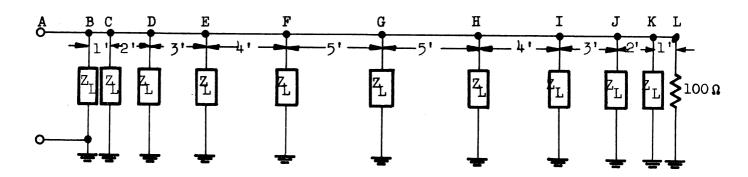

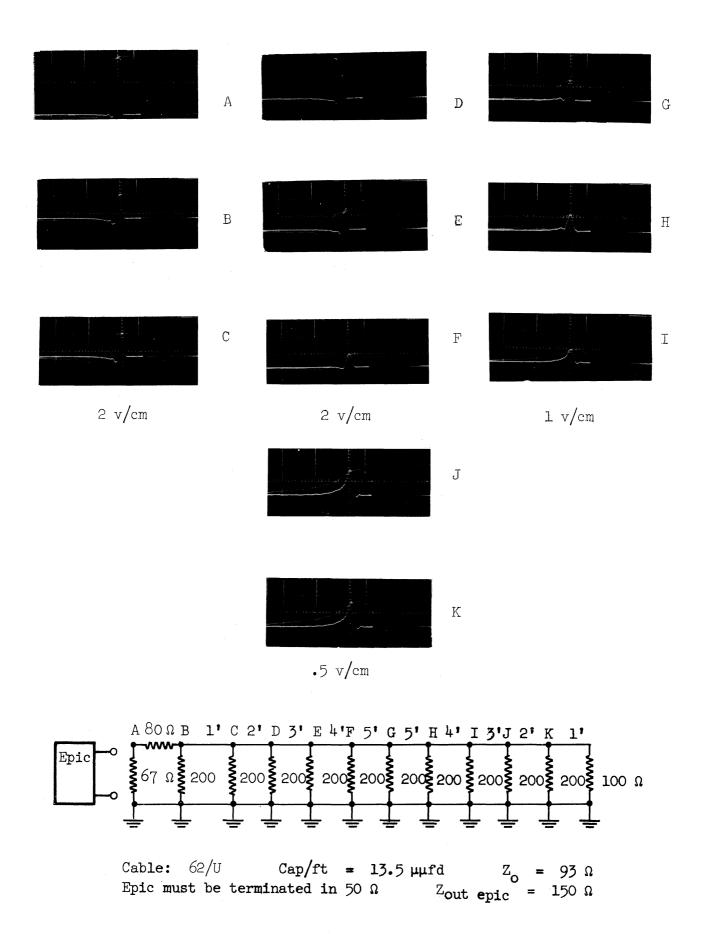

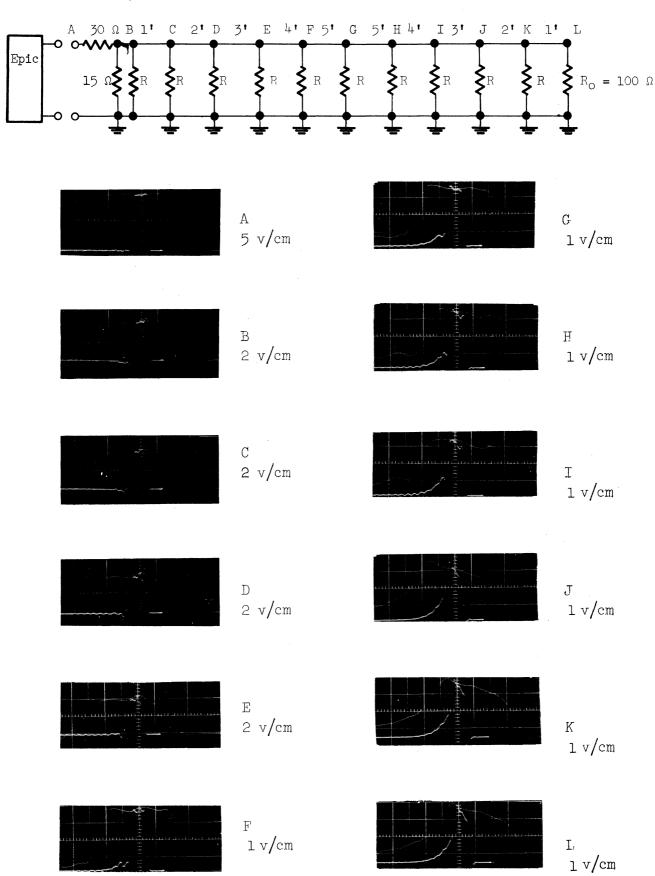

| 4.3          | Experimental model for reflection study.                  | 118  |

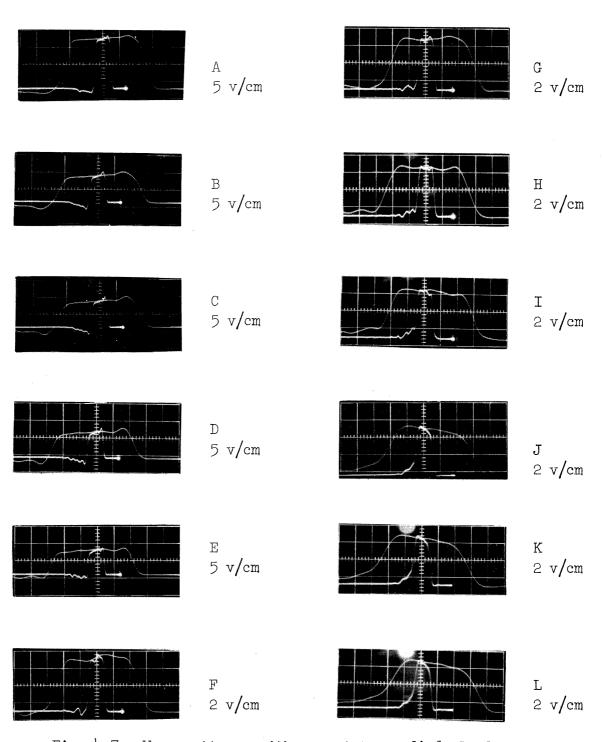

| 4.4          | Wave patterns with a 200 $\Omega$ load.                   | 119  |

| 4.5          | Wave patterns with a 470 $\Omega$ load.                   | 121  |

| 4.6          | Wave patterns with a 560 $\Omega$ load.                   | 122  |

| 4.7          | Wave patterns with a resistance-diode load.               | 124  |

| 4.8          | Delay network patterns for 100 musec delay.               | 126  |

| Table        |                                                           |      |

| 4.1          | Attenuation for 200 $\Omega$ Load                         | 120  |

| 4.2          | Attenuation for 470 $\Omega$ Load                         | 123  |

| 4.3          | Attenuation for 560 $\Omega$ Load                         | 123  |

| 4.4          | Attenuation for Resistance-Diode Load                     | 125  |

|              |                                                           |      |

|              | 5. Functional Circuitry                                   |      |

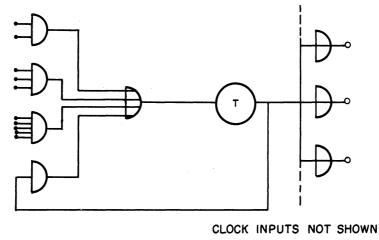

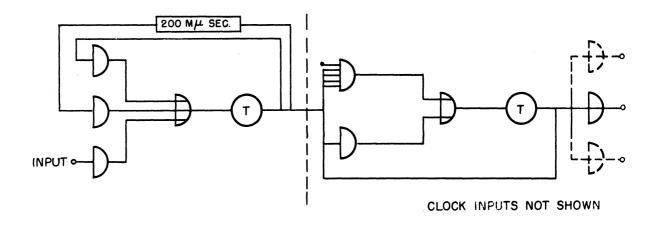

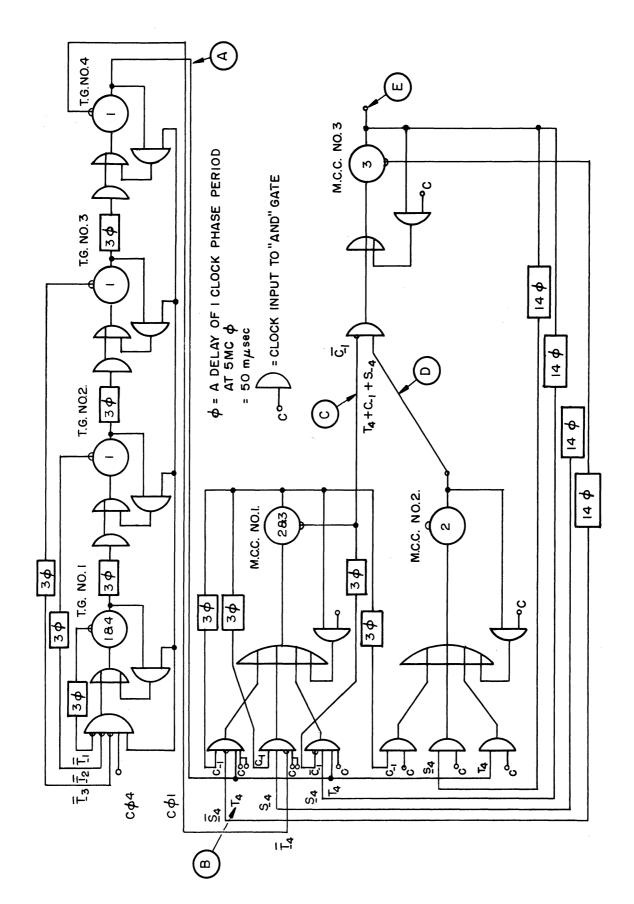

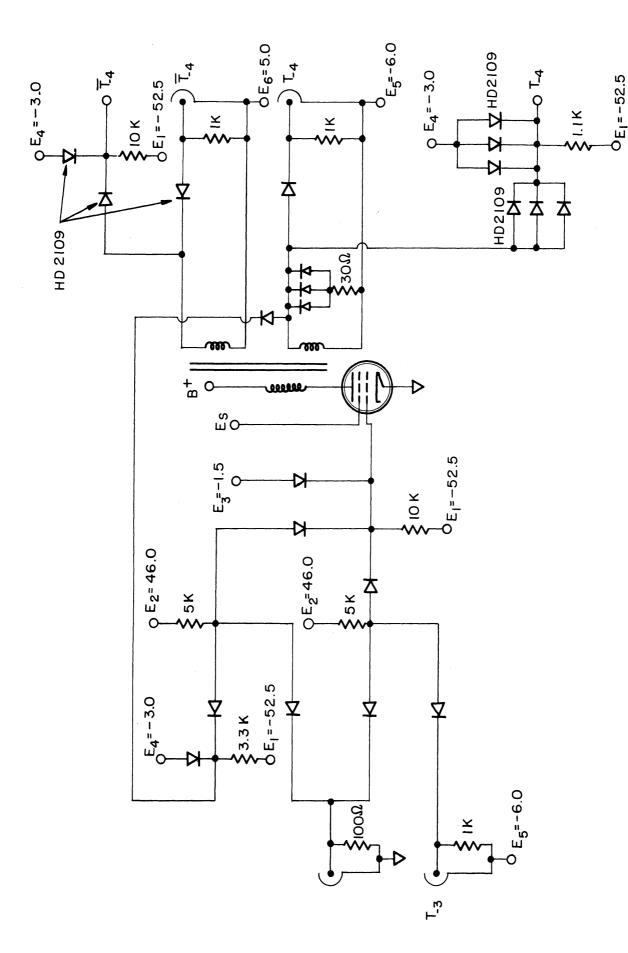

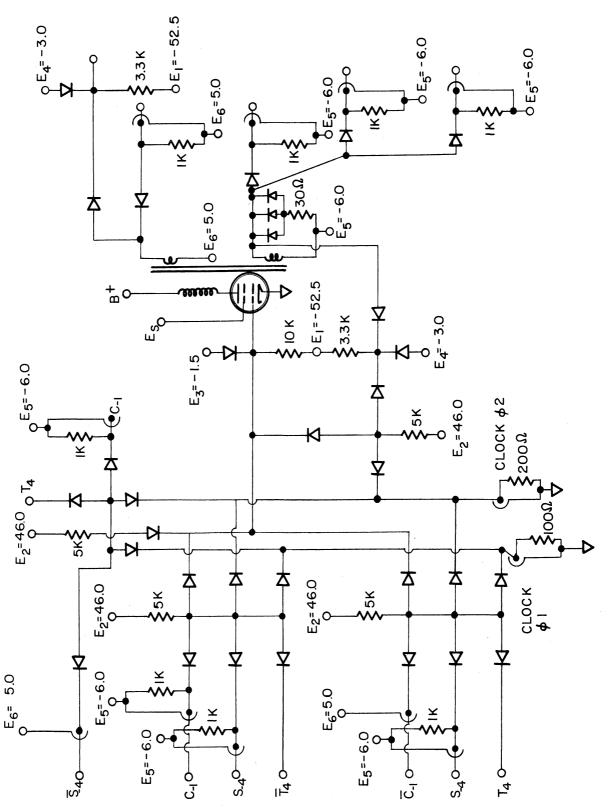

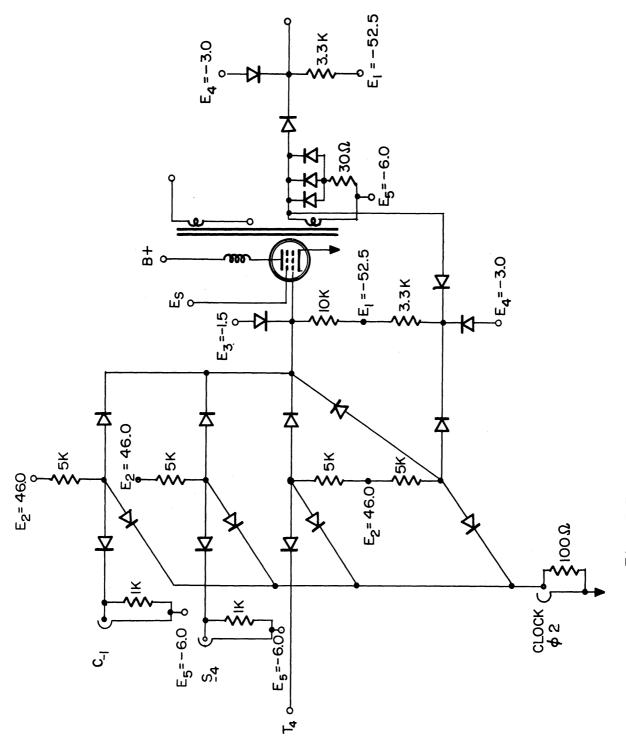

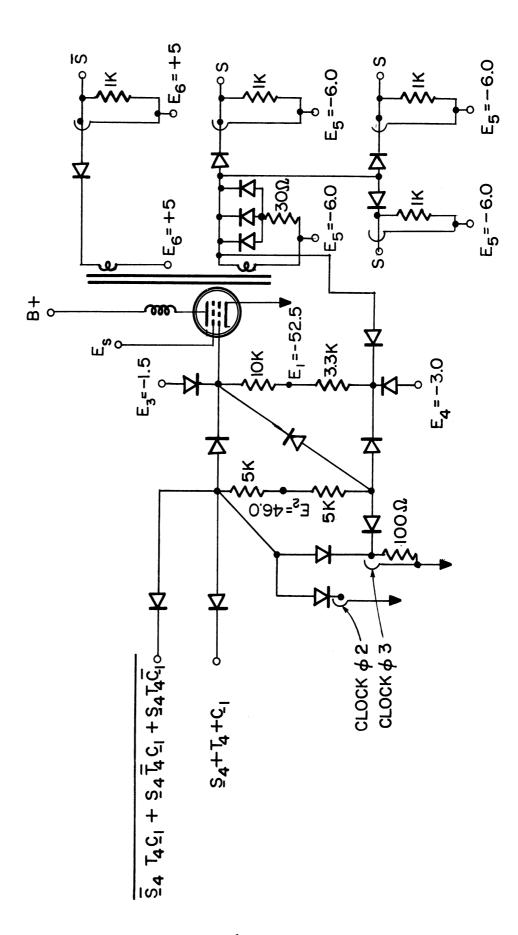

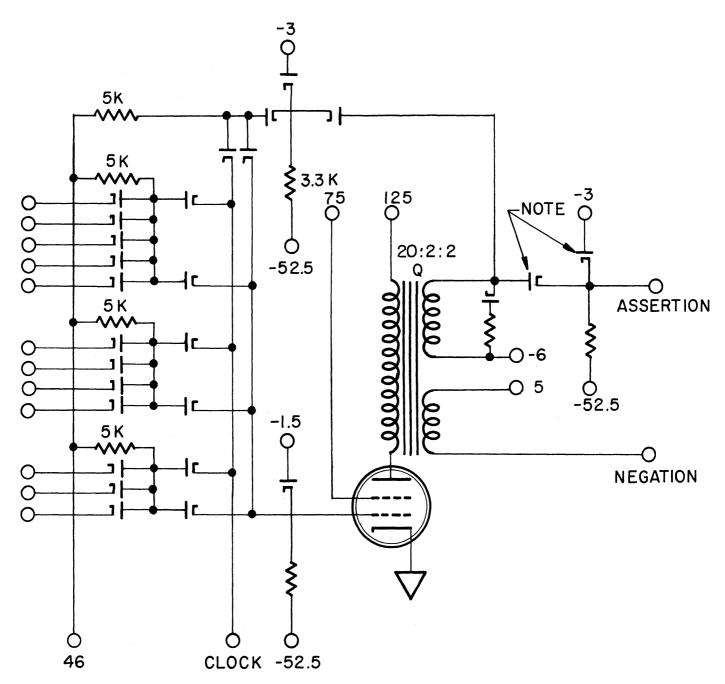

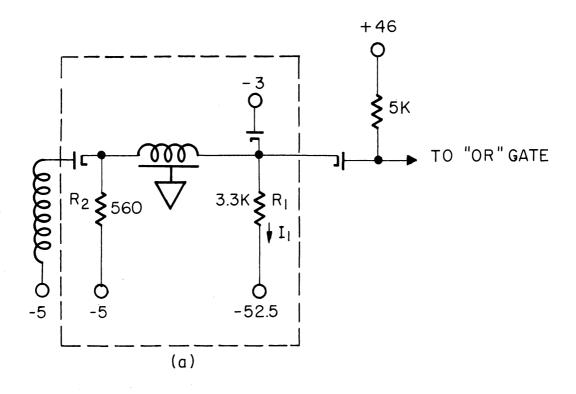

| 5.1          | ${f T_4}$ timing generator and minor cycle counter.       | 129  |

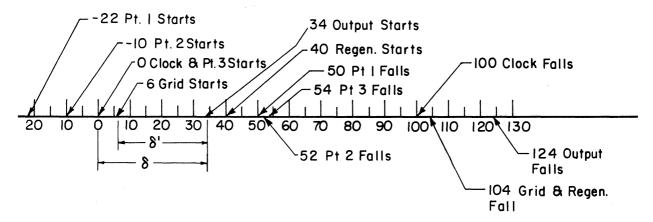

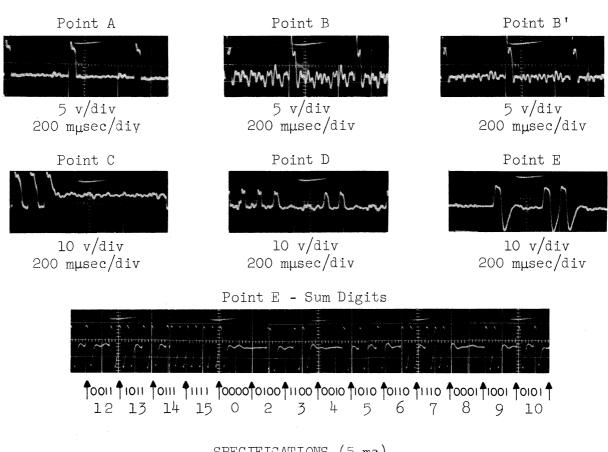

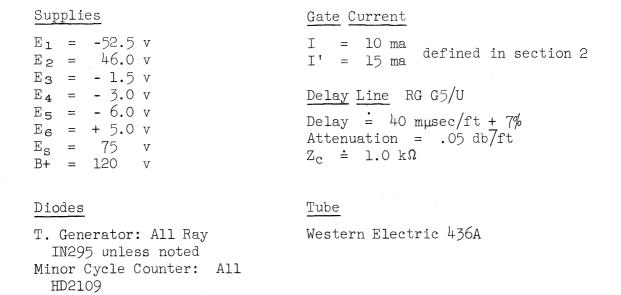

| 5.2          | Waveforms and specifications.                             | 130  |

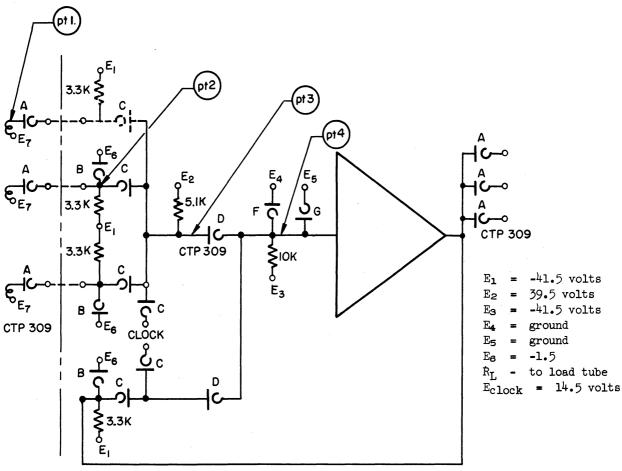

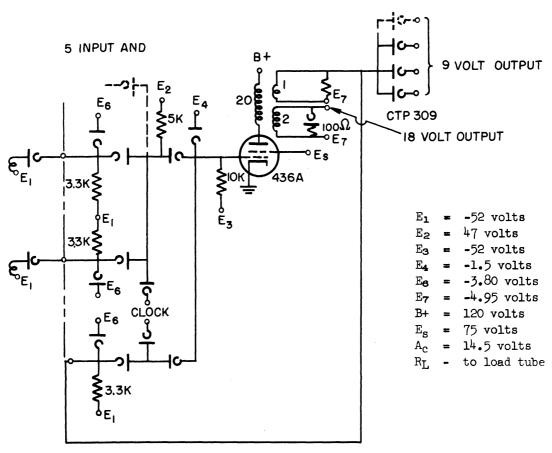

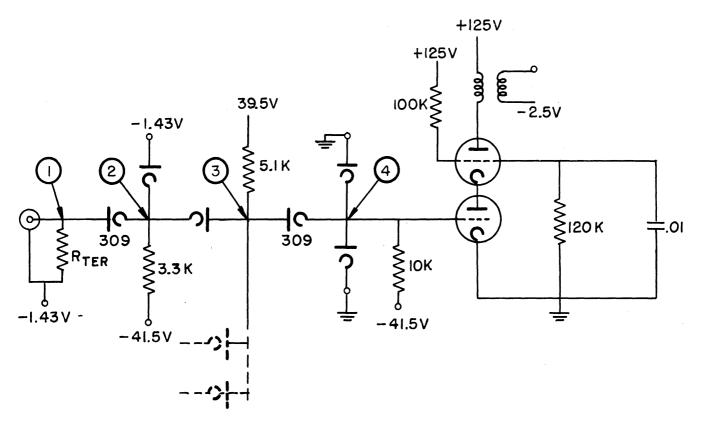

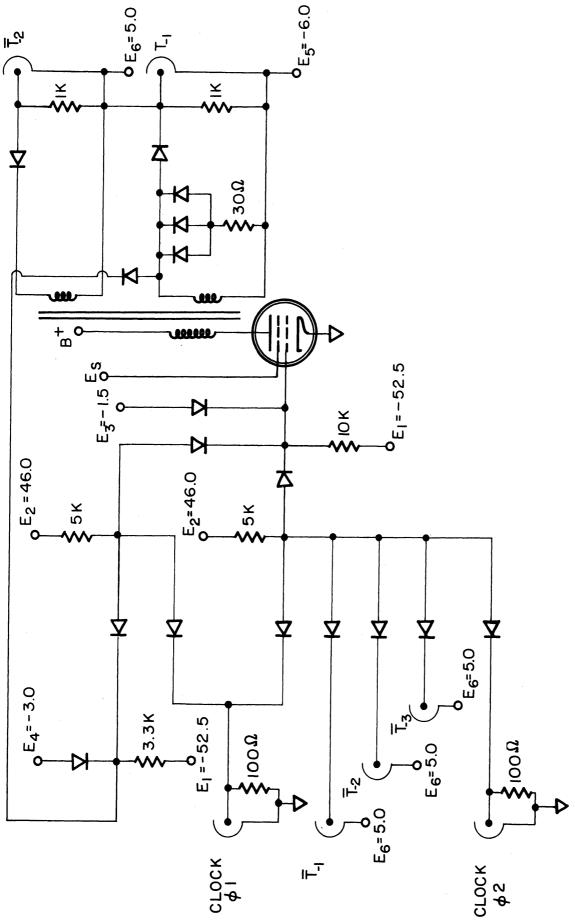

| 5.3          | Timing generator Package No. 1.                           | 131  |

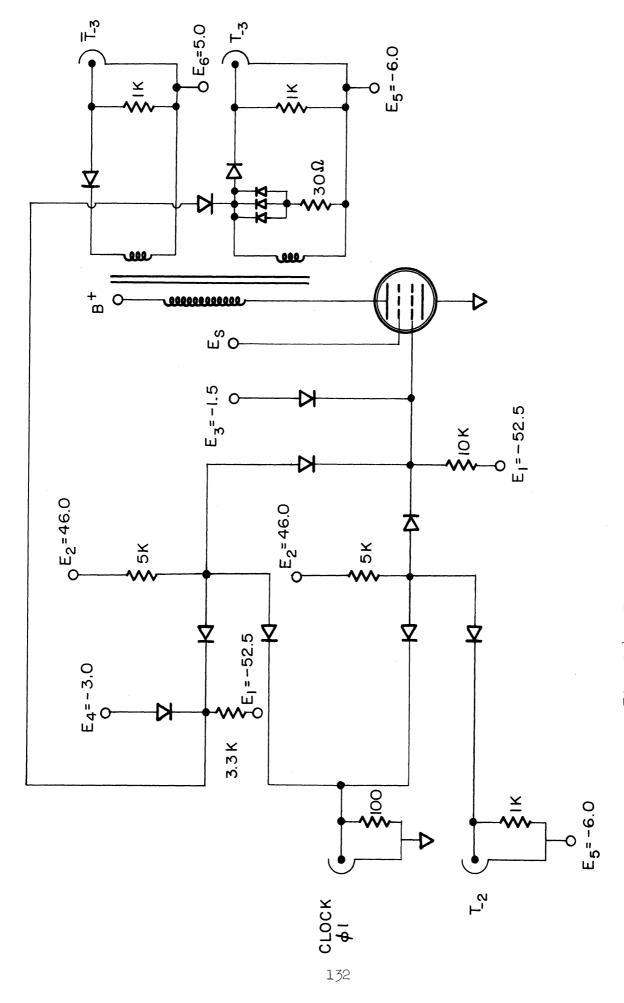

| 5.4          | Timing generator Package Nos. 2 and 3.                    | 132  |

| 5.5          | Timing generator Package No. 4.                           | 133  |

| 5.6          | Minor cycle counter Package No. 1.                        | 134  |

| 5.7          | Minor cycle counter Package No. 2.                        | 135  |

| 5.8          | Minor cycle counter Package No. 3.                        | 136  |

| 5.9          | Standard package.                                         | 138  |

| 5.10         | Delay terminations.                                       | 139  |

#### ABSTRACT

The objective of the program was the development of a basic set of switching elements which could be used to fabricate certain logical configurations. It was also desired that the basic limitations of the component parts of the circuitry be determined and clarified. A natural breakdown of the problem led to research into four distinct regions of existing component development.

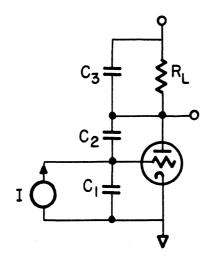

In Chapter 1, an analysis is made of a pulse amplifier of the type employed in the SEAC computer gating package. There are two ways of investigating the performance of a given circuit. The first of these is a theoretical analysis of the circuit, and the second is experimentation. The theoretical work, unless grossly inapt assumptions are made, will give the investigator at least an order-of-magnitude feeling for values of circuit parameters and frequencies of operation. In this chapter, linear circuit analysis and a graphical method of analysis are used, and the results are compared with experimental results. Agreement between the theoretical and experimental results is reasonable on the basis of the assumptions made.

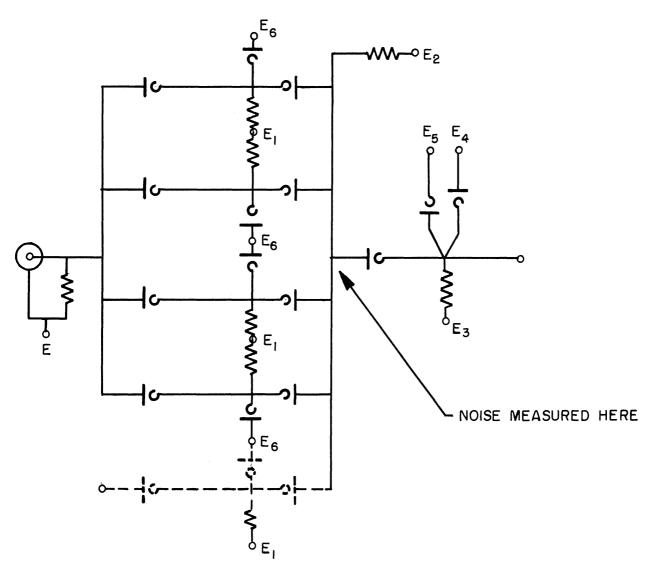

In Chapter 2, the gating circuitry is studied, and it is found that the speed of operation of a diode gating structure is limited by 1) the amount of noise which can be tolerated in the circuit, and 2) the magnitude of current required per gate input. Both of these limiting factors are dependent on the reverse transient properties of the semiconductor diodes used in the gate structure. As the frequency of operation is increased, the reverse transient is accentuated by the required increase in gate current. This chapter is a study of the effect of various diode parameters on over-all gate performance.

Chapter 3 presents design information for a pulse transformer applicable to the pulse amplifier circuitry and an analysis of the frequency limitations and circuit characteristics of the transformer independent of its circuit environment.

The first section is an investigation of the effects of tube, transformer, and external circuit parameters on the output characteristics of tube-transformer pulse amplifiers. A simplified low-frequency equivalent circuit for the transformer is assumed in this section. Equations are derived which relate the maximum available load current to the circuit parameters, and it is shown that a resonant transformer design will allow maximum load current.

The second section is a study of the limitations on circuit operation imposed entirely by the transformer characteristics. The effects of core material, core size and shape, and winding geometry on transformer characteristics are indicated, and some measurements of these effects are presented.

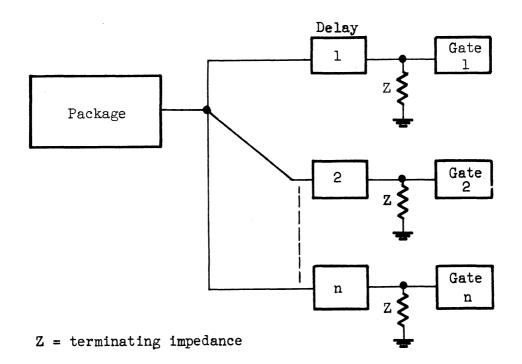

In Chapter 4, two possible configurations for interconnection between a package output and gate inputs are considered. The first one employs n cables,

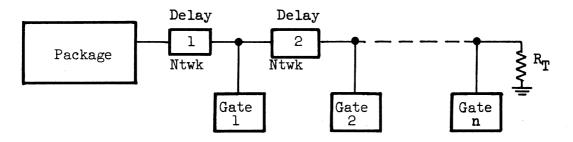

each terminated at the gate input. It is found that this interconnection necessitated equality between the gate impedance and the characteristic impedance of the cable if no power loss is to be permitted. The second configuration consisted of a singly terminated cable with each gate input tapped off at n different points of the cable. This interconnection requires that the gate impedance be much larger than the characteristic of the cable to minimize reflections. This type of interconnection is more desirable and experimental data prove this out.

The operation of delaying pulse trains for proper time phasing at the gate inputs is also considered in Chapter 4. It was found that a delay network manufactured by Advance Electronics Laboratories (8-T-300a) would operate satisfactorily at the desired frequency.

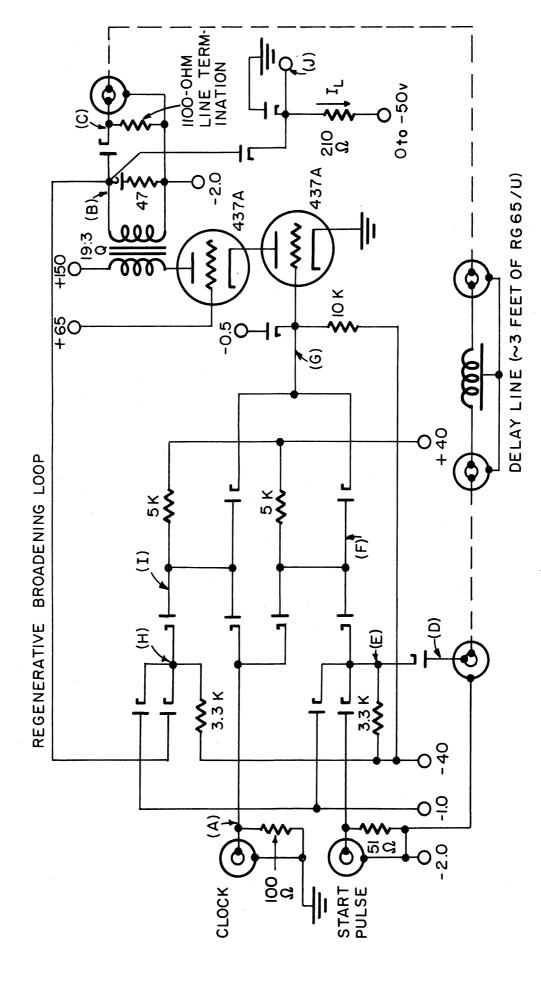

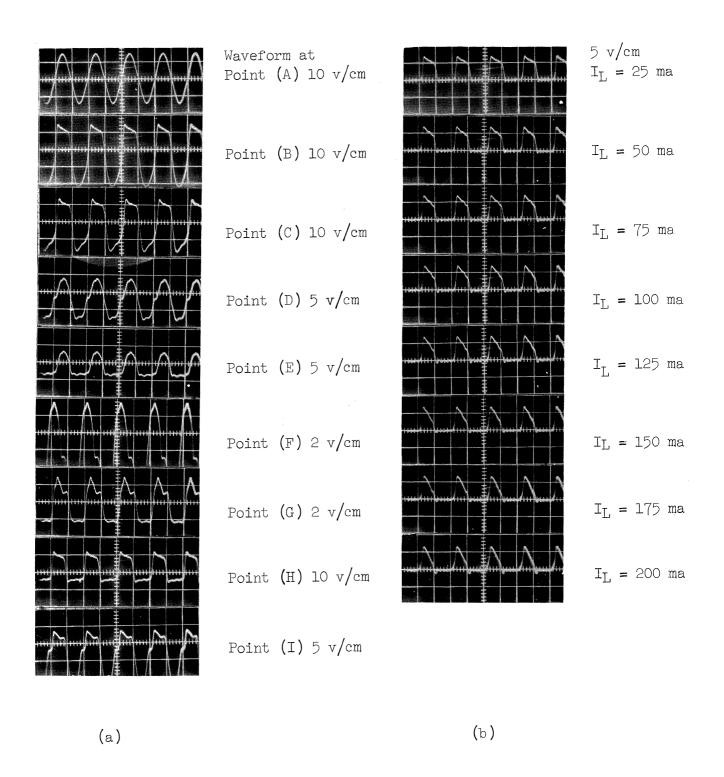

In Chapter 5, the research on gating circuitry, pulse amplifiers, transformers, and interconnection are utilized in the design of a standard package. A modified form of the standard package is then used in fabricating a  $\mathbf{T_4}$  pulse generator and a minor cycle counter. Experimental results show that the components will allow 5 Mc operation and possibly higher. It should be emphasized that throughout the different phases of research work for this project, rectangular pulses were assumed and employed whenever possible. With less stringent requirements on the pulse wave shape, it is feasible that higher speeds of operation could be realized.

#### OBJECTIVE

The object of this program has been the engineering development of a basic set of switching elements. It was desired that the circuitry developed be capable of operating at switching rates an order of magnitude greater than rates presently employed in conventional digital switching circuits. This implies that the circuitry must operate effectively at a switch rate of  $\sim 10$  Mc/sec. Another objective of the program has been the determination and clarification of basic limitations of the component parts of the circuitry.

#### DESIGN PHILOSOPHY

It is almost impossible to design high-speed switching circuitry on a hit-or-miss basis. This is due primarily to the inadequacies or limitations of the basic elements. None of the basic elements—diodes, tubes, transformers, etc.—is perfect. The successful circuit design must function correctly in spite of these basic difficulties. The task of the circuit designer is the optimization of the circuit design so that the best possible performance is obtained. In other words, the designer must be acutely aware of the limitations of the basic component, and the design must account for these limitations.

Component limitations are the primary factors governing the specification of the basic design philosophy. Let us then begin the discussion of design philosophy with a short explanation of the component limitations.

Perhaps the worst limitation arises from the capacitance associated with the basic components. All components such as tubes and diodes have shunt capacitance between elements. There also exists additional capacitance in the form of stray capacitance due to wiring. To produce a voltage pulse at a given point, it is necessary first to charge the capacitance at that point. An examination of a typical dynamic circuit configuration would reveal that capacitance is charged from three components, diode gates, tubes, or transformers. The gates and the tubes will approximate constant current generators, while the output from the transformers approximates a constant voltage generator. With a constant current generator the effect of capacitance is obtained from the following equations:

$$e = 1/C \int_{0}^{t} i dt$$

if  $i = 0, t < 0$

$$i = 1, t \ge 0$$

then

$$\Delta e = I/C \Delta t$$

.

The ratio of  $\Delta e/\Delta t$  is determined by the ratio of I/C.

As a base, consider the standard one megacycle dynamic circuitry used in the SEAC, MIDAC, and various other computers. The goal is to increase the operation speed of this basic circuit by at least a factor of ten. Can the ca-

pacitance at the various critical points be decreased by a factor of ten? The answer is obviously no. It is apparent that the capacitance which presently exists cannot be substantially reduced. Some small reduction of capacitance is obtainable if more direct wiring is employed. However, this reduction may be nullified if the tube selected for the power amplifier has greater interelectrode capacitances than the 6AN5.

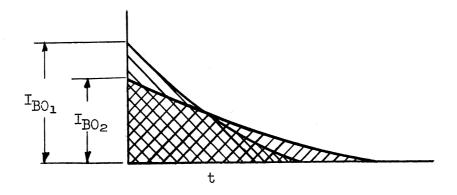

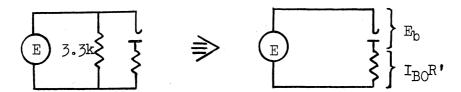

Next let us consider the effects obtained if the circuit action is speeded up by increasing the available charging current I. If perfect diodes were available, this would be a feasible solution, except from the viewpoint of power dissipation. However, presently available diodes suffer undesirable transient effects during the switching interval. In particular, the transient recovery of diodes from conduction to nonconduction must be given serious study. The diode does not recover instantly, due to the existence of the minority carriers in the diode at the time of switching. The diode is not switched until these carriers have diffused out of the active diode region. The number of carriers found in the diode at the time of switching is proportional to the magnitude of the forward current. Thus, for any given diode the fastest recovery time is obtained with the minimum forward current. The recovery time will roughly increase in proportion to an increase in forward current. Preliminary studies have indicated that back recovery effects are not as serious as might first be expected. Even so, it is still important to obtain fast recovery times. This means that only small increases in charging current can be obtained. The increase in charging current will never approach an order of magnitude.

One consideration remains. If the voltage  $\Delta e$  is reduced, a faster operation can be achieved. This means that a gate designed to give a 10-v pulse at 1 Mc/sec should function adequately at 10 Mc if the voltage swing is reduced to 1 v. This is the desired low-current gate. The reduction of the gate-voltage swing must be accompanied by a proportional increase in the  $g_m$  of the power amplifier tube. In the MIDAC 1 Mc/sec circuits the 6AN5 tube has an effective  $g_m$  of about 7000  $\mu$ mhos. A MIDAC gate structure operating at 10 Mc/sec requires a pentode-type tube with a  $g_m$  of 70,000  $\mu$ mhos. It is possible with existing tubes to achieve a  $g_m$  of 50,000  $\mu$ mhos.

Let us now examine in somewhat more detail the effects of  $\mathbf{g}_{m}$  and gate-voltage changes on the performance of a dynamic switching circuit.

A transformer of optimum design will deliver a secondary current of magnitude

$$I_{s} = \frac{I_{p}^{2} T}{4E_{o} C_{p}} \qquad I_{g} N = I_{s}$$

where

$\mathbf{I}_{\mathbf{p}}$  is the primary current,

$\mathbf{C}_{\mathbf{p}}$  is the capacitance seen at the primary,

$\mathbf{E}_{\mathrm{O}}$  is the magnitude of the pulse from the secondary,

T is the rise time desired,

$\mathbf{I}_{\mathbf{g}}$  is the current required for one gate drive, and

N is the maximum permissible number of gate drives.

Now

$$I_p = g_m E_g$$

,

where  $\mathbf{E}_{g}$  is the grid swing.

The loss occurring in the gating can be accounted for by setting

$$E_g = A E_O \qquad A < 1$$

.

$\mathbf{E}_{\mathbf{g}}$  may also be expressed in terms of current and capacitance:

$$E_{g} = \frac{B I_{g} T}{C_{\sigma}},$$

where

$\mathbf{C}_{\mathbf{g}}$  is the capacitance seen by the output of the gating circuit, and

B is the efficiency of the gating configuration.

Combining the previous formulae yields

$$N = \frac{g_{\rm m}^2 T^2 AB}{4C_{\rm p} C_{\rm g}}$$

or

$$N = \frac{M^2 T^2 E}{4} ,$$

where

$$M = \frac{g_m}{\sqrt{C_p C_g}}$$

, a figure of merit, (see Appendix A) and

E = AB, the gate efficiency defined as the product of the gatestructure current and voltage-transfer ratios. For the purpose of illustration assume

$T = 10^{-8} \sec,$

E = 1/25, and

$M = 5 \times 10^9 \text{ rad/sec.}$

For the above values N=25. It is noted that a rather inefficient gate structure was assumed. Also, the formula does not account for transformer losses which certainly are not negligible at 10 Mc/sec. In spite of various losses which have been neglected, the above calculation is important. It indicates that 10-Mc dynamic circuitry, which will provide an adequate number of gate drives, can be achieved.

Little has been said about the transformer design. The ultimate efficiency of a transformer at high frequencies is primarily dependent on the core material. To be sure, different methods of construction produce better transformers, but at high frequencies the core material remains the dominant factor. The choice of a core material must be a compromise between permeability and core losses.

In brief, the design philosophy adopted seeks to minimize the gating currents and the gate-voltage swing. The power-amplifier design effort is directed toward a circuit having a very high  $g_{m}$  and an excellent figure of merit.

#### 1. PULSE AMPLIFIER

#### 1.1 Theoretical Analysis of Pulse Amplifiers

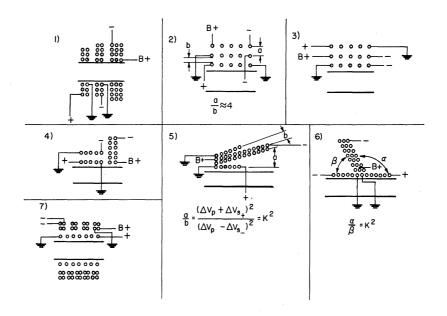

## 1.1.1 QUALITATIVE DISCUSSION OF A PENTODE, TETRODE, OR CASCODE TRIODE PULSE AMPLIFIER

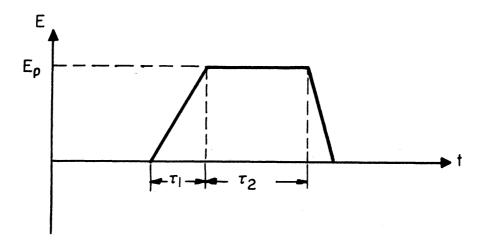

If the amplifying component is a vacuum tube, then a pulse transformer is required to match the tube to the lower impedance of the gating structure. The tube and transformer then comprise a pulse amplifier. Operation of such a pulse amplifier is best understood by consideration of three different phases of the pulse: the rise, the flat top or duration, and the fall or decay.

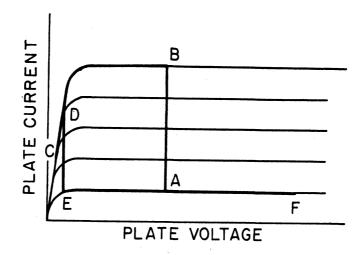

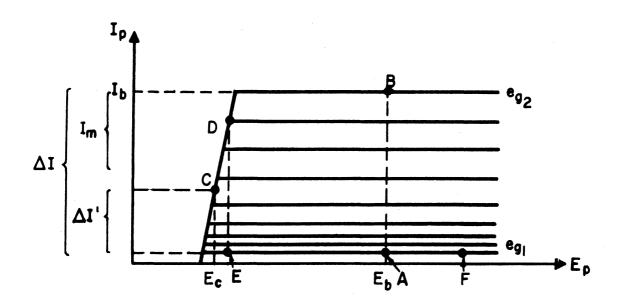

- 1.1.1.1 The Rise.—Initially the pulse amplifier has on its grid a voltage  $e_{g_1}$ , which keeps the tube in a low-conduction state. The plate voltage is the supply voltage since there is negligible d-c drop in the transformer. This quiescent point corresponds to point A of Fig. 1.1. When a pulse is applied by the gating structure, the grid is suddenly raised to the positive value  $e_{\rm g2}$ . Since there is plate-circuit shunt capacitance, the plate voltage cannot change instantly; hence, the plate characteristics are traversed to point B. The tube is now drawing much more current than previously, the capacitance begins to charge, and the plate voltage begins to fall. The plate characteristics are traversed along the  $\mathbf{e}_{\mathrm{g}_{2}}$  curve towards zero plate volts, and the voltage across the transformer increases. This process continues until the current in the transformer secondary is in equilibrium with the plate current. At the equilibrium point, the capacitance is charged (draws zero current at this instant) and no further increase in transformer voltage will occur. This point is where the line of the load resistance, referred to the primary, intersects the  $e_{\rm g2}$  curve, and it marks the end of the rise-time response of the pulse amplifier. This point is marked C on the figure, and it occurs where the tube is "bottomed." Bottomed operation is desirable since the plate voltage in the bottomed condition changes very little as the tube ages. 1 Hence, the amplitude of the output pulse should remain near the standard value over the useful life of the tube.

- 1.1.1.2 The Duration.—The rise time is so short that the transformer primary inductance does not have time to begin drawing a great deal of current. However, once the capacitance is charged, the transformer has an almost constant voltage impressed and magnetizing current will begin to build up comparatively rapidly. The point of operation on the plate characteristics will move away from point C back up the  $e_{\rm g2}$  curve toward the knee. This means that the plate voltage is increasing, the transformer voltage is falling, and the output pulse is drooping. The magnitude of the droop will depend upon the primary inductance, the

Fig. 1.1. Pentode operating path.

pulse duration, and the plate resistance of the tube in the bottomed condition. If the transformer inductance could be made large, then the magnetizing current and output pulse droop could be kept small. However, as will be seen in the next section, the amount of transformer inductance that may be used at a given repetition rate is fixed by factors other than magnetizing current.

1.1.1.3 The Fall.—At the end of the pulse, the increased magnetizing current has increased the total tube current up to point D on the curves. At this time, the grid is again switched suddenly to  $e_{g_1}$ , and again, because of plate shunt capacitance, the voltage cannot change instantly and the plate characteristics are traversed to point E. At this time we have essentially a parallel RLC circuit with an initial charge on the capacitance and with an initial current in the inductance. The R is the load resistance referred to the primary side of the transformer. As the capacitor discharges, the operating point travels along  $e_{g_1}$  to A, at which point a critical damping resistance is switched in and the load resistance is switched out by diodes. The current in the inductance then decays and produces a back voltage out to point F and finally back to point A before the next pulse comes along. Rough sketches of important waveforms during a pulse period are shown in Fig. 1.2.

In "speeding up" SEAC-type circuitry, an important factor is plate-circuit shunt capacitance. If the transformer is to recover after one pulse before the next one comes along, the resonant frequency of the transformer primary inductance and the plate-circuit shunt capacitance must be equal to or greater than the desired repetition rate. This means that the allowable transformer inductance is fixed by the tube and stray capacitances so that the magnetizing current and pulse-top droop which result from this amount of inductance must simply be tolerated. If the inductance is made lower than is necessary to allow sufficiently fast recovery, and/or if the load resistance is made too small, the magnetizing current will carry the path of operation back around the knee of the curve where a very small further increase in magnetizing current will cause the plate voltage to rise quickly to the supply voltage and the load current and

Fig. 1.2. Pentode waveforms.

voltage to fall to zero before the grid pulse is over. That is, the amplifie will not "hold up" a pulse of the width being amplified. This condition indicates that the limit to which the circuit may be loaded has been exceeded.

The same circuit may be loaded more heavily if the grid is driven positive so that the knee to which the magnetizing current must creep is the extent to which this may be carried is limited by either the current dissipation ratings of the tube employed. Usually the plate dissipation since high plate current occurs only at low plate voltage and vice versa type of amplifier. Consequently, the limit is set by screen dissipation cathode current, according to which rating is reached first.

#### 1.1.2 QUALITATIVE DISCUSSION OF A TRIODE PULSE AMPLIFIER

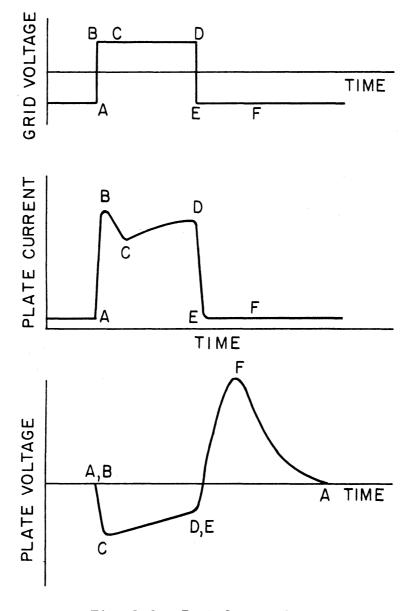

From the considerations similar to the preceding, we see that the path of operation on triode plate characteristics is ABCDEFA, as shown in Fig. 1.3. The waveforms are sketched in Fig. 1.4. These waveforms are similar to the pentode case, except that the plate current increases during the transformer backswing where the plate voltage rises above the supply voltage. This additional current may become a significant part of the average plate current, which is undesirable because, in the case of a triode, the tube rating which is likely to be exceeded first is that of average cathode current. The current increase may be eliminated by using a large quiescent bias or possibly by feedback. The first of these would require a large grid swing to drive the tube into heavy conduction, and this is undesirable. Hence, the solution appears to be feedback which would bias the grid more negative as the plate swings positive. This feedback can presumably be derived from the regular package output which is swinging negative at the required time. Further discussion of a triode amplifier is given in section 1.1.3.1.

Fig. 1.3. Triode operating path.

#### 1.1.3 LINEAR CIRCUIT ANALYSIS OF POSSIBLE AMPLIFIER CONFIGURATIONS

1.1.3.1 <u>General Discussion.</u>—It is the purpose of this section to develop formulae to be used to estimate the number of gate drives that may be expected from several amplifier configurations. In Appendix D it is shown that the maximum load current from a tube-transformer pulse amplifier is given by

$$I_{L_{max}} = \frac{23}{140\pi^2} \frac{\Delta I^2}{C_p f E_s} - \frac{35\pi^2}{23} f E_s C_s$$

(1.1)

Fig. 1.4. Triode waveforms.

#### where:

$\Delta I$  = pulse-plate current

C<sub>p</sub> = primary shunt capacitance

$E_{S}^{r}$  = secondary voltage

$C_s$  = secondary shunt capacitance

f = frequency of operation

#### If we assume:

(1) that a linear analysis is valid; i.e., that  $I = g_m e_g$ , where  $g_m$  is the tube transconductance and  $e_g$  is the grid voltage change,

- (2) that one volt of noise clipping is necessary and there is a drop of 2 volts in the diode logic so that  $E_S = e_g + 3$ , and

- (3) that secondary capacitance may be neglected,

then Eq. (1.1) may be rewritten as

$$I_{L_{\text{max}}} = \frac{23}{140\pi^2} \frac{g_{\text{m}}^2 e_{\text{g}}^2}{C_{\text{p}} f (e_{\text{g}} + 3)} . \qquad (1.2)$$

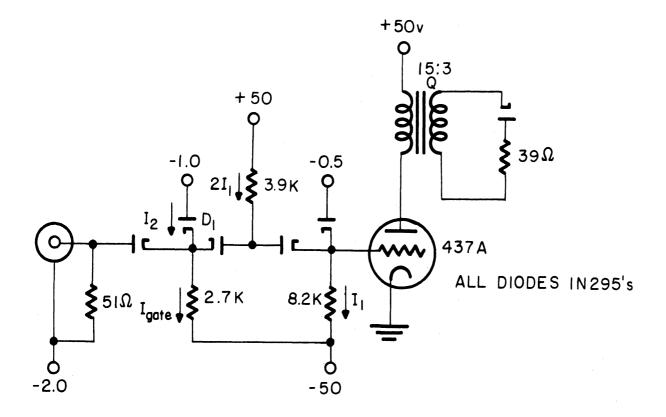

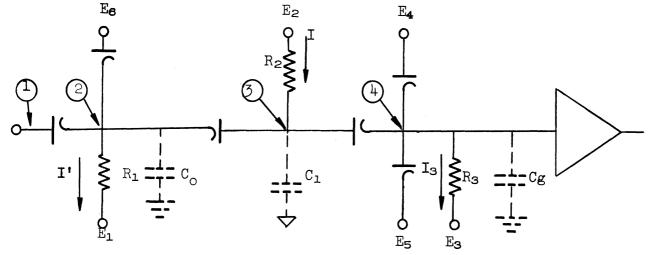

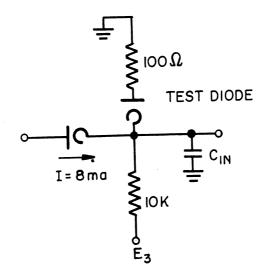

The current required per gate is calculated by considering the circuit of Fig. 1.5. A current  $I_1$  is required to charge and discharge the input capacitance of the pulse amplifier; hence, a current of  $2I_1$  is required in the "and" pull-up resistor. From noise considerations it is necessary to have a current  $I_2$  flowing in clamp diode  $D_1$ . Hence, the input gate current,  $I_{\rm gate}$ , is

$$I_{gate} = 2I_1 + I_2$$

(1.3)

The current  $I_1$  is given by

$$I_1 = \frac{C_g e_g}{0.1 \text{ T}} = 10f C_g e_g$$

, (1.4)

where T = 1/f = pulse repetition period.

The number of gates that may be driven by a gating package is then

$$N = \frac{I_{L_{max}}}{I_{gate}} = \frac{\frac{23}{140\pi^2} \frac{g_m^2 e_g^2}{C_p f (e_g + 3)}}{20 f C_g e_g + I_2}$$

(1.5)

Eq. (1.5) applies only as long as none of the ratings of the tube employed are exceeded.

Within the ratings of the tube employed, Eq. (1.5) applies to several amplifier configurations provided the proper input and output capacitances and  $g_m$ 's are used. Capacitances for several configurations are as follows:

- (a) If a pentode or tetrode tube is used, the input capacitance may be taken as the capacitance from the control grid to the cathode and to the screen grid plus stray wiring capacitance. The output capacitance is the capacitance from the plate to the cathode and to the screen and suppressor grids plus transformer and stray capacitances. These input and output capacitances, except for the stray components, are ordinarily published by tube manufacturers.

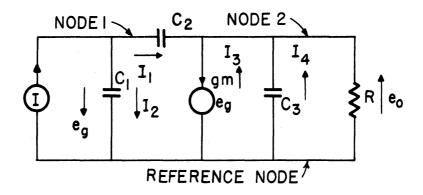

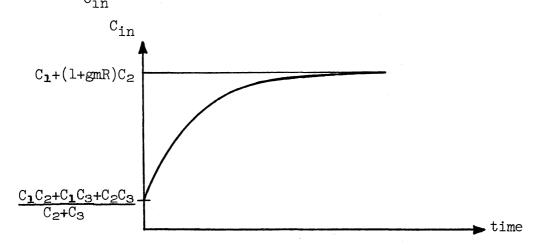

- (b) In a triode the Miller Effect capacitance becomes the dominating part of the input capacitance. This capacitance has a transient and a steady-state component. However, as shown in Appendix B, the steady-state value is

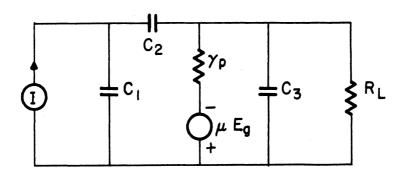

Fig. 1.5. Triode test circuit.

reached in such a short time that the transient may be neglected for operation at frequencies equal to or less than 10 mcps. The input capacitance is then effectively given by

$$C_g = C_{gk} + (1 - A) C_{ng}$$

(1.6)

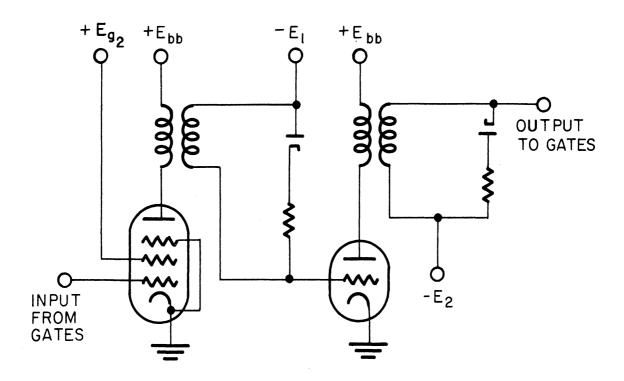

Some experimentation has been performed with the 437A triode to illustrate the Miller Effect. The circuit used was the same as that shown in Fig. 1.5. Results of the experiment are shown in Fig. 1.6. Fig. 1.6(a) shows the grid waveform with the plate supply turned off. In this case the capacitance at the grid is just the grid-to-cathode capacitance and the stray capacitance. The gate pullup and pull-down currents are large enough to charge and discharge the grid capacitance. In Fig. 1.6(b) the plate supply voltage is turned on, the tube has gain, and the Miller capacitance, which is now present, is large enough to require a comparatively long time to charge and discharge. Presumably it is possible to increase gate currents to the point where they would be able to charge and discharge even the large Miller capacitance in a sufficiently short time. However, such large gate currents would have adverse effects upon the transients in the gating diodes and would require a greater amount of noise clipping. Also, a given triode would be able to drive only a very small number of such high-current gates. It should be possible to drive the input capacitance of the triode by a rather low-power pentode as in Fig. 1.7, whose small input capacitance could be driven by comparatively low-current gates. The backswing of the pentode's transformer

(a) 0.1  $\mu$ sec/major division 2.0  $\nu$ /major division (b) 0.1  $\mu$ sec/major division 2.0  $\nu$ /major division

Fig. 1.6. Waveforms for the triode circuit.

would then tend to keep the triode biased off during its transformer's backswing, thereby reducing the triode average plate current. However, if the rise time of the pulse is not to deteriorate too drastically in this cascade pulse amplifier, then the rise time of the pentode stage and of the triode stage must be the same as for a single-stage amplifier. Since rise times of cascaded stages, with rise times  $T_1$ , and  $T_2$ , add in the square root according to the formula

$$T = \sqrt{(T_1^2 + T_2^2)}, \qquad (1.7)$$

the rise-time requirements on the individual stages become more stringent. In fact, each stage must now rise in only 0.707 of the time that a single-stage pulse amplifier would be allotted.

Fig. 1.7. Pentode-triode pulse amplifier.

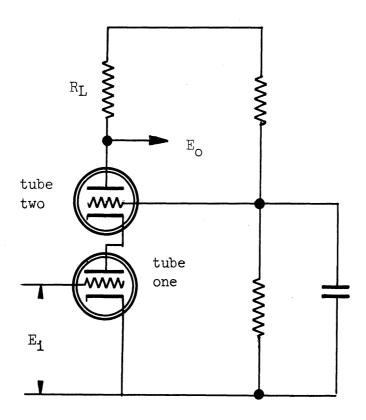

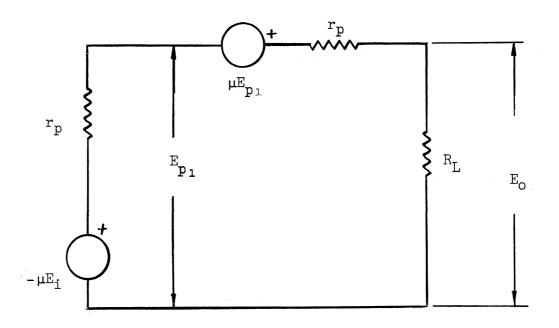

(c) The cascode circuit of Fig. 1.8 represents an approach which reduces the input capacitance due to the Miller effect. A high figure of merit is

Fig. 1.8. The cascode circuit.

thereby obtained from the very-high- $g_m$  triodes (see Appendix A). The Miller effect in this circuit depends on the gain to the plate of tube one,  $K_1$ ;  $K_1$  is small because the plate load for tube one is the impedance looking into the cathode of tube two, which is a small impedance approximately equal to  $1/g_m$ .

Thus we may write

$$C_g = C_{gk} + (1 - K_1) C_{pg}$$

(1.8)

To determine the input capacitance, one must first determine the impedance  $R_{\rm e}$  looking into the cathode of tube two.  $R_{\rm e}$  may be found from a consideration of the equivalent circuit of Fig. 1.9. The following equations are written by inspection of the equivalent circuit:

$$I_{p} = \frac{-\mu (E_{g} - E_{pl})}{2r_{p} + R_{L}}$$

(1.9)

$$E_{p1} = -\mu E_g - I_p r_p$$

(1.10)

Substituting (1.10) into (1.9) and simplifying, one obtains

$$I_{p} = \frac{-\mu E_{g} (\mu + 1)}{(\mu + 2) r_{p} + R_{L}}$$

(1.11)

Fig. 1.9. Cascode equivalent circuit.

Substituting (1.11) into (1.10), one has

$$E_{p1} = \mu E_g + \frac{\mu E_g (\mu + 1) r_p}{(\mu + 2) r_p + R_L}$$

(1.12)

The impedance we desire is evidently the ratio of voltage to current at that point:

$$R_e = \frac{E_{p1}}{I_p}$$

(1.13)

Substituting (1.11) and (1.12) into (1.13), one has finally

$$R_{e} = \frac{r_{p} + R_{c}}{\mu + 1} (1.14)$$

The gain  $K_1$  is that of a triode with plate load  $R_e$ :

$$K_{1} = \frac{-\mu R_{e}}{r_{p} + R_{e}}$$

$$= \frac{-\mu (r_{p} + R_{L})}{(\mu + 2) r_{p} + R_{L}}.$$

(1.15)

Therefore, from (1.8) the input capacitance is

$$C_g = C_{gk} + \left[ \frac{\mu(r_p + R_L)}{(\mu + 2) r_p + R_L} + 1 \right] C_{gp}$$

(1.16)

If  $R_{\rm L} <<$  ( $\mu$  + 2)  $r_{\rm p}\text{,}$  this may be simplified to

$$C_g = C_{gk} + (2 + R_L/r_p) C_{gp}$$

(1.17)

The figure of merit of the cascode circuit is also dependent on the output capacitance, which is evidently the capacitance plate-to-grid plus some fraction of the capacitance plate-to-cathode since this latter capacitance does not have the full output voltage impressed. The effect of  $\mathtt{C}_{pk}$  will be that of a capacitance whose size is  $\mathtt{C}_{pk}$  multiplied by the ratio of the voltage impressed on  $\mathtt{C}_{pk}$  to the total output voltage. Thus

$$C_p = C_{pg} + \frac{K_2 - K_1}{K_2} C_{pk}$$

(1.18)

where  $K_2$  = overall gain.

The gain K2 is

$$K_2 = E_0/E_i = (R_I I_D)/E_i$$

(1.19)

Substituting  $I_p$  from (1.15), one has

$$K_2 = \frac{-\mu(\mu + 1) R_L}{(\mu + 2) r_p + R_L} . \qquad (1.20)$$

If  $R_{\rm L} <\!\!<$  ( $\mu$  +2)  $r_{\rm p}$  , this reduces to

$$K_2 \doteq - (\mu/r_p) R_L = - g_m R_L$$

(1.21)

Substituting the values for  $K_1$  and  $K_2$  into the formula for output capacitance, one has

$$C_{p} \doteq C_{pg} + \frac{\mu(\mu + 1) R_{L} - \mu (r_{p} + R_{L})}{\mu(\mu + 1) R_{L}} C_{pk}$$

$$= C_{pg} + \left[1 - 1/(g_{m} R_{L})\right] C_{pk} . \qquad (1.22)$$

The figures of merit for particular tubes in a cascode configuration with an overall gain of 20 are presented in Table 1.1. Of these tubes, the 416A is evidently the best. A test circuit using the 437A triode has been studied experimentally to study the feasibility of the cascode circuit.

TABLE 1.1

FIGURE OF MERIT OF CASCODE TRIODES WITH AN OVERALL GAIN OF 20

|                      | 417A | 437A | 416A   |

|----------------------|------|------|--------|

| C <sub>g</sub> (μμf) | 13.5 | 20.1 | 8      |

| C <sub>p</sub> (μμf) | 3.28 | 4.4  | 2      |

| gm (ma/volt)         | 24   | 45   | 50     |

| M(rad/µsec)          | 3600 | 4780 | 12,500 |

#### 1.1.3.2 Predicted Gate Drives for Particular Tubes and Configurations. -

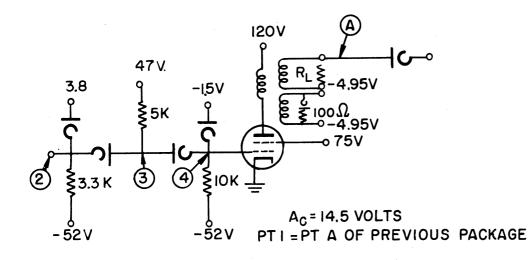

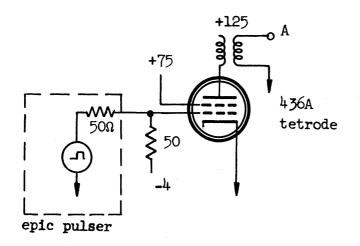

#### 1.1.3.2.1 436A Tetrode.

The current  $I_2$  of Eq. (1.3) has been determined experimentally to be about 4 ma. Allowing 5 pF for grid-circuit stray capacitance and a voltage gain of 40, the input capacitance for the 436A is calculated to be 23 pF. The output capacitance with the transformer in place was calculated from the undamped transformer ringing frequency to be about 10 pF. The transconductance is 30 millimhos. Hence, Eq. (1.5) may be rewritten as

$$N = \frac{23}{140\pi^2} \frac{(30)^2 (10^{-6}) e_g^2}{f (e_g + 3) 10^{-11}} \frac{1}{20(23)(10^{-12}) f e_g + 4 \times 10^{-3}} . \qquad (1.23)$$

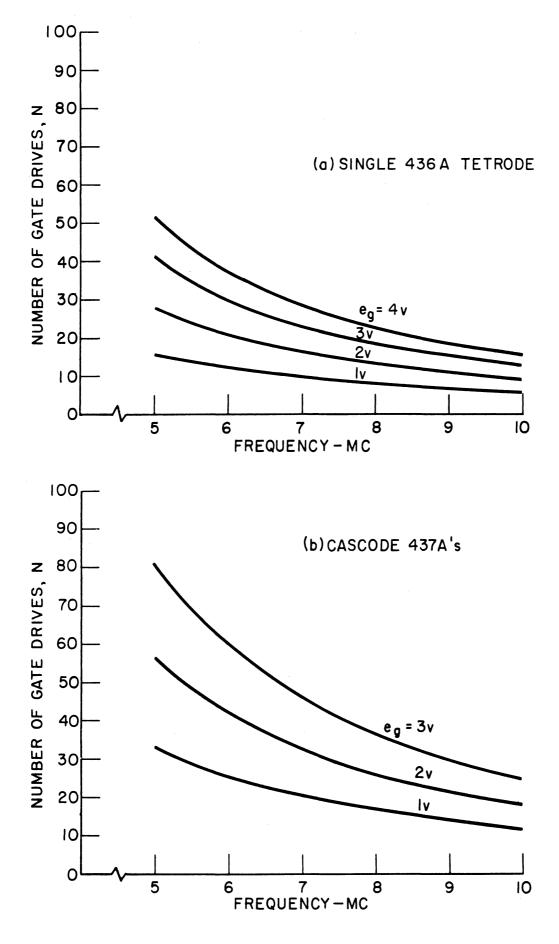

This equation is plotted as a function of frequency with grid swing as a parameter in Fig. 1.10(a).

#### 1.1.3.2.2 Cascode 437A.

Again assuming a voltage gain of 40, the input capacitance of 437A's in cascode is calculated to be 27.5 pF. The output capacitance is about 10 pF and the transconductance is 45 millimhos, so that Eq. (1.5) is evaluated to be

$$N = \frac{23}{140\pi^2} \frac{(45)^2 (10^{-6}) e_g^2}{f (e_g + 3) 10^{-11}} \frac{1}{20 f (27.5)(10^{-12}) e_g + 4(10^{-3})} . \qquad (1.24)$$

and is plotted in Fig. 1.10(b).

#### 1.1.4 GRAPHICAL CIRCUIT ANALYSIS

Linear circuit analysis is useful in analyzing this type of pulse amplifier in an approximate manner. It tells one the tube parameters which are important and gives one the ability to estimate with very little calculation the number of gate drives that may be expected from a particular amplifier configuration. If a more precise description of the pulse waveform is desired, one can resort to a graphical analysis of the pulse amplifier.

1.1.4.1 <u>General Discussion</u>.—If the grid signal waveform is assumed to be known, then from the plate characteristics of the tube and a known RLC load, the output-voltage waveform may be plotted. From the same set of calculations, the magnetizing current, the capacitive current, the load current, and the total tube current and voltage may be plotted. If the tube has a screen grid, and if the screen-grid characteristics are available, then a plot of screen-grid current may also be obtained by reading the screen current, point by point, for the previously calculated pairs of values of plate voltage and control-grid voltage.

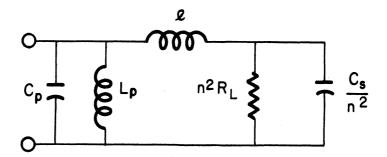

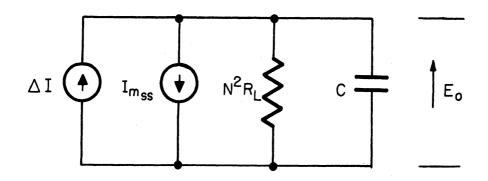

The transformer and its load may be approximated by the circuit of Fig. 1.11. The leakage inductance is small<sup>3</sup> and may be neglected without serious error.

Fig. 1.10. Variation of number of gate drives with frequency.

$\ell$  = Transformer leakage inductance  $L_p$  = Transformer primary inductance  $C_p$  = Primary shunt capacitance  $C_s$  = Secondary shunt capacitance  $R_L$  = Secondary load resistance

n = Step-down turns ratio

Fig. 1.11. Approximate transformer equivalent circuit.

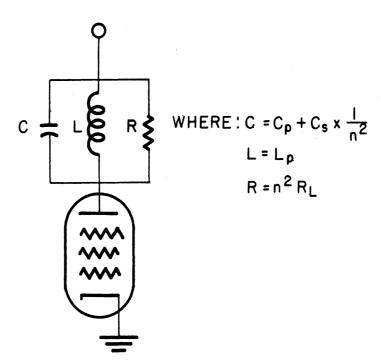

In this case, the plate load for the tube reduces to a parallel RLC circuit as in Fig. 1.12.

Fig. 1.12. Approximate plate load presented by the transformer and its load.

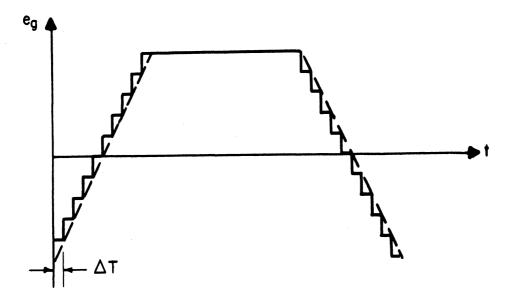

The essence of the analysis is that the grid waveform may be approximated by true step functions occurring at regular intervals of time as in Fig. 1.13. The approximation becomes more accurate as the number of steps is increased and the time between steps is decreased. The approximation becomes exact in the

Fig. 1.13. Approximation of a waveform by steps.

limit as the number of steps tends to infinity and the time between steps tends to zero.

The steps of voltage at the grid will result in steps of current through the tube. The tube current-step increase may flow through any of the three paths: R, L, or C. However, a true step increase will flow through C at the initial instant of application, and, if sufficiently short times,  $\Delta t$ , are used, then it is approximately true that the capacitor current will not change appreciably during one time interval. Hence, the voltage across the capacitor will increase during the first interval, and during the second interval this voltage will begin to force current through the resistive load according to Ohm's Law and will begin to change the current in the inductance according to Lenz's Law. Note that an error has been introduced: actually some resistive current will flow as soon as the capacitor has acquired the most minute charge, and also the inductive current will begin to change. However, if the time interval is taken quite small, then the error will be small.

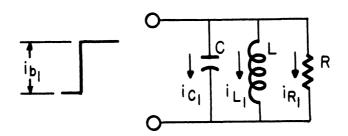

Before the pulse is applied, the grid is at some steady potential, there is some steady flow of plate current, and all this current flows through the primary of the transformer, which is a d-c short circuit. Hence, initially, there is no output voltage  $\mathbf{e}_p$  and there is no current in either the capacitor or the resistor. Then at t = 0+, the grid voltage is suddenly increased and causes a sudden increase in the plate current of  $\mathbf{i}_{b_1}$ . The problem to be solved then is as illustrated in Fig. 1.14.

For times  $t \ll RC$ , the currents may be shown to be approximately

$$i_{R_1} = i_{b_1} \frac{t}{RC} \left( 1 - \frac{t}{2 RC} \right)$$

(1.25)

Fig. 1.14. The problem arising from a step grid voltage.

$$i_{L_1} = i_{b_1} \left(\frac{t}{2 RC}\right)^2 \tag{1.26}$$

$$i_{c_1} = i_{b_1} \left( 1 - \frac{t}{2 RC} \right)^2 , \qquad (1.27)$$

provided that the circuit is critically damped. Presumably the increase in plate current  $i_{b_1}$  is not known. However, it is known that the output voltage is given by

$$e_{P_1} = E_{bb} - e_{b_1}$$

, (1.28)

and it is also known that the output voltage must be given by

$$e_{P_1} = \frac{1}{C} \int i_{C_1} dt = i_{R_1}R = L \frac{di_{L_1}}{dt}$$

(1.29)

If we now apply the approximation that the capacitive current is a constant for short times, we have

$$e_{P_1} = i_{c_1} \frac{t}{C} \text{ for } t \ll RC$$

(1.30)

and at the end of the first interval we have

$$i_{c_1} \frac{\Delta t}{C} = E_{bb} - e_{b_1}$$

, (1.31)

where

t =  $\Delta t$ - (just before the second grid step), and  $e_b$  = the plate voltage at t =  $\Delta t$ - and is unknown.

But ic, is given by

$$i_{c_1} = i_{b_1} - i_{R_1} - i_{L_1}.$$

(1.32)

Therefore,

$$\left(i_{b_{1}} - i_{R_{1}} - i_{L_{1}}\right) \frac{\Delta t}{C} = E_{bb} - e_{b_{1}}$$

(1.33)

This last equation may be rewritten in the form of a load line, drawn on the plate characteristics, and  $e_{b_1}$  and  $i_{b_1}$  read off. Given  $e_{b_1}$  and  $i_{b_1}$ , the currents  $i_{c_1}$ ,  $i_{c_1}$ , and  $i_{c_1}$  may be calculated. This procedure may be generalized to the following recursion formulae:

$$E_{j} = E_{bb} + (i_{r_{j-1}} + i_{r_{j-1}}) \Delta t/C - e_{p_{j-1}}$$

(1.34)

$$e_{b_{j}} = E_{j} - (\Delta t/C)i_{b_{j}}$$

(1.35)

$$e_{p_{\mathbf{j}}} = E_{bb} - e_{b_{\mathbf{j}}} \tag{1.36}$$

$$i_{r_j} = e_{p_j}/R \tag{1.37}$$

$$i_{L_{j}} = i_{L_{j-1}} + e_{p_{j}}(\Delta t/L)$$

(1.38)

$$i_{c_{j}} = i_{b_{j}} - i_{R_{j}} - i_{L_{j}}$$

(1.39)

From these equations, known initial conditions, given grid waveform, and the plate characteristics of the tube used, a complete solution may be obtained.

1.1.4.2 A Specific Example of Graphical Analysis.—The discussion of the preceding section and the method of applying the formulae to a particular situation can probably be clarified by consideration of a particular example.

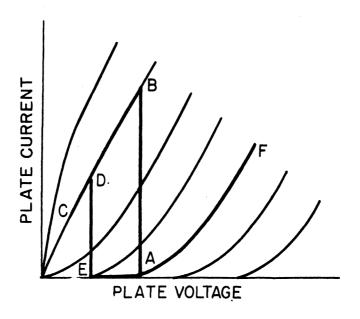

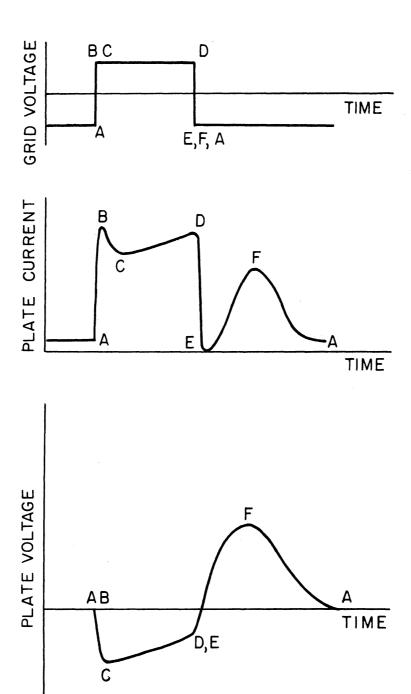

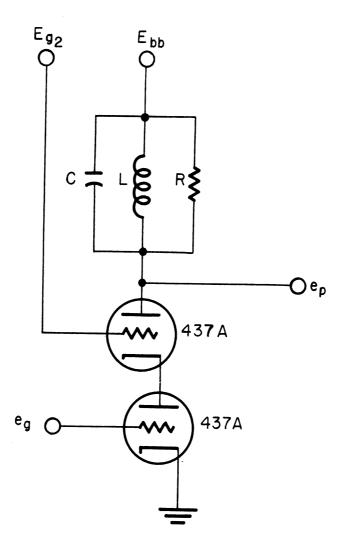

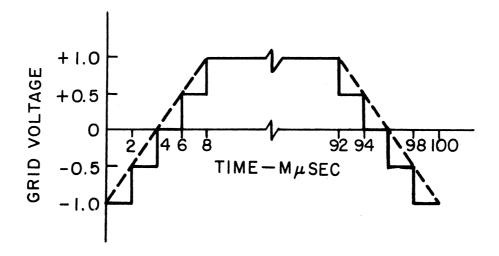

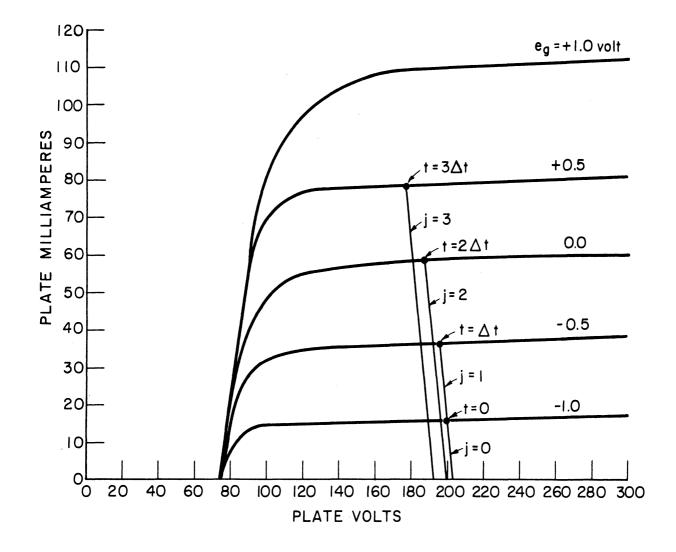

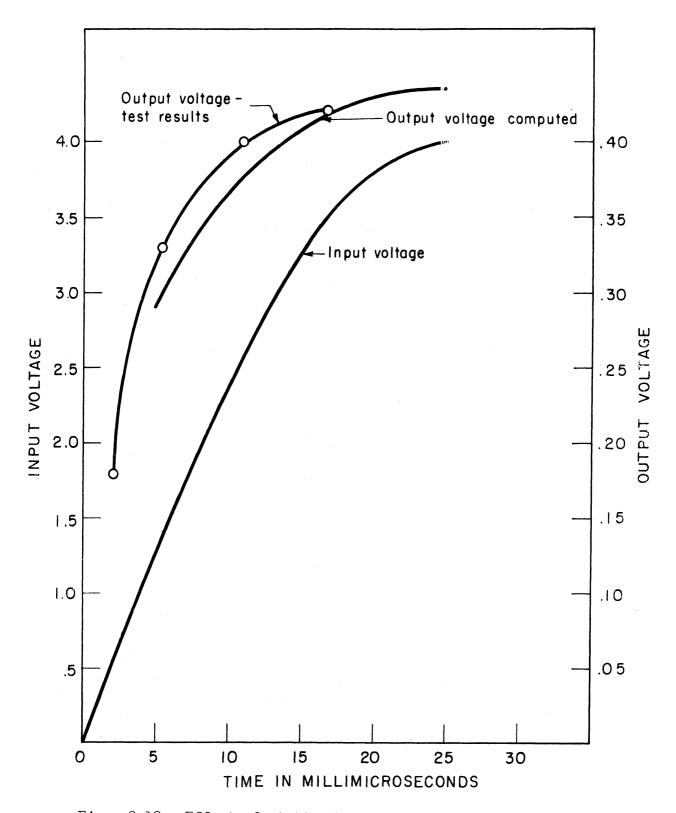

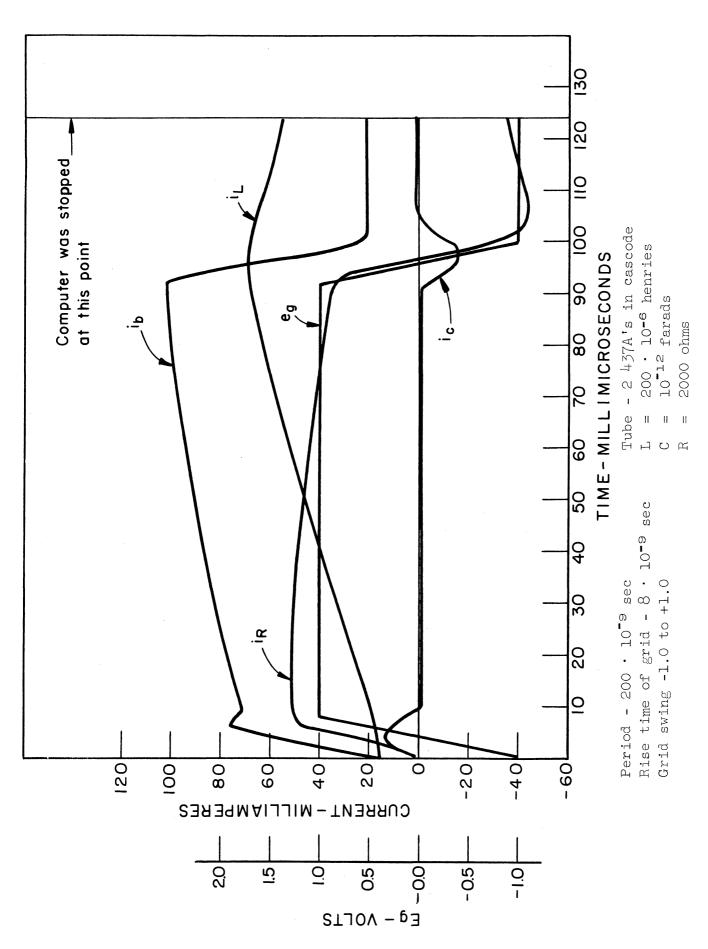

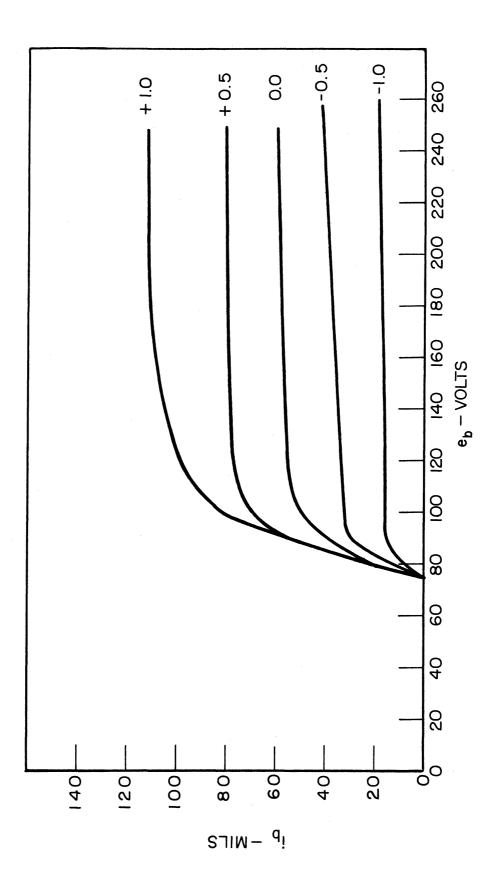

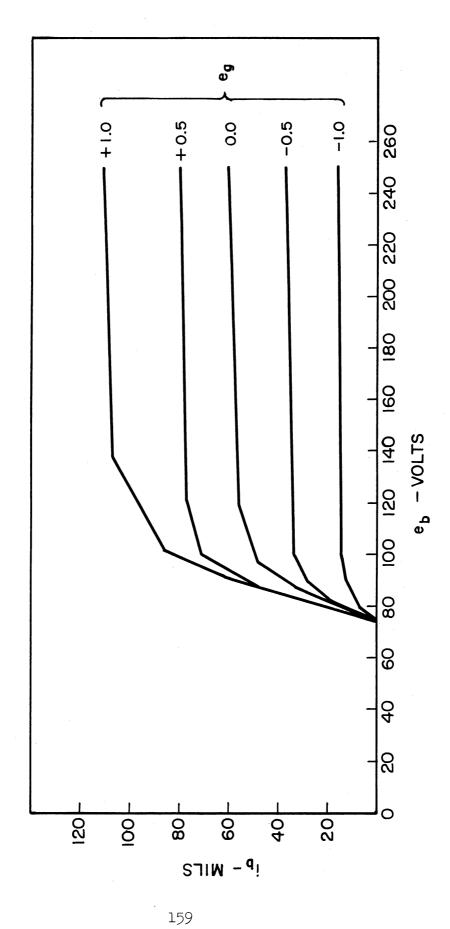

Consider the cascode 437A circuit of Fig. 1.15 with input grid signal as in Fig. 1.16 and plate characteristics as in Fig. 1.17. Assume a transformer primary inductance of 200  $\mu$ hy, a shunt capacitance of 10 pF, and a load resistance referred to the primary of 2k (this value of resistance slightly overdamps the circuit). The plate supply voltage will be taken as 200 volts and the upper grid supply as 75 volts.

Assuming that there has been no input pulse for a sufficiently long time for all transients to have died out, all the plate current will flow through the inductance, and there will be no output voltage and no resistive or capacitive component of current. The grid voltage will be -1.0 volt. Evaluating Eq. (1.34) for these conditions gives  $E_O = 203.2$  volts and substituting into Eq. (1.35) gives

$$e_{b_0} = 203.2 - 200 i_{b_0}$$

(1.40)

This load line is the j = 0 line of Fig. 1.17, and at the intersection with the  $e_g$  = -1.0-volt curve, one can read  $e_b$  and  $i_b$  to be 200 volts and 16 ma, respectively. From Eq. (1.36) through (1.39), one calculates  $e_{p_0}$  = 0,  $i_r$  = 0,  $i_{L_0}$  = 16 ma, and  $i_{C_0}$  = 0, respectively. This concludes the first iteration.

For the second iteration, j=1,  $t=\Delta t=2$  m $\mu$  sec, and the grid voltage has increased to -0.5 volt, as in Fig. 1.16. Equation (1.34) is again evaluated to be

$$E_1 = 203.2 \text{ volts}$$

(1.41)

Fig. 1.15. Cascode circuit used in the graphical analysis example. C = tube interelectrode capacitance, plus stray capacitance = 10 pF; L = 150  $\mu hy$ ; R = 2K.

Fig. 1.16. Input signal.

Fig. 1.17. Plate characteristics for graphical analysis.

Therefore, Eq. (1.35) is again

$$e_{b_1} = 203.2 \div 200 i_{b_1}$$

(1.42)

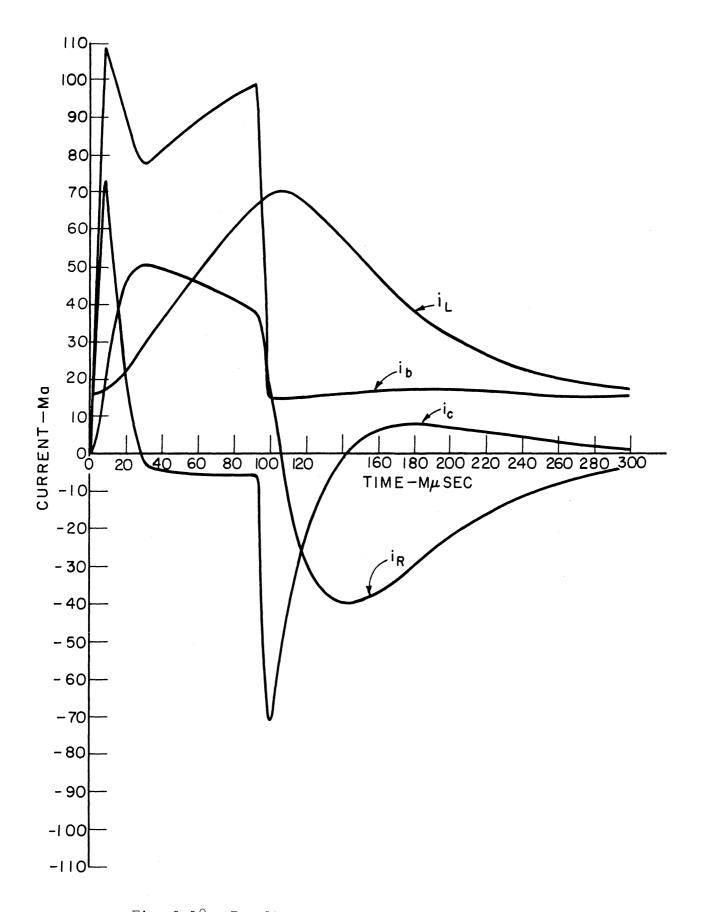

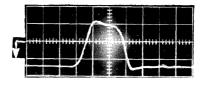

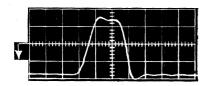

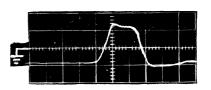

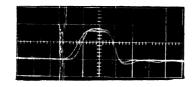

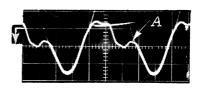

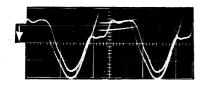

From the intersection of this j = l load line with the  $e_g$  = 0.5-volt curve,  $e_{b_1}$  and  $i_{b_1}$  are read as 196 volts and 36 ma, respectively. From Eq. (1.36) through (1.39), one calculated, respectively,  $e_{p_1}$  = 4 volts,  $i_{r_1}$  = 2 ma,  $i_{L_1}$  = 16.05 ma, and  $i_{c_1}$  = 18 ma. The second iteration is now ended. Further iterations may be performed similarly with the results being as shown in Table 1.2. These results are presented graphically in Fig. 1.18. Experimental results using the same voltages and circuit parameters are presented for comparison in the photograph of plate voltage in Fig. 1.19.

The graphical method of analysis yields results which agree quite well with experimental results. However, it is a very time-consuming method and, therefore, does not lend itself to an investigation of the effects of varying circuit parameters if calculations are performed by hand. Therefore, the problem

TABLE 1.2

RESULTS OF THE GRAPHICAL ANALYSIS EXAMPLE

|       |                  |                  | •            | _                | •               | •                 | •                           | *              |    |

|-------|------------------|------------------|--------------|------------------|-----------------|-------------------|-----------------------------|----------------|----|

| j<br> | e <sub>gj</sub>  | e <sub>b</sub> j | ibj          | e <sub>P</sub> j | <sup>i</sup> Rj | <sup>i</sup> Lj   | <sup>i</sup> C <sub>j</sub> | Ej             | t  |

| 0     | -1               | 200              | 16           | 0                | 0               | 16.00             | 0                           | 203.2          | 0  |

| 1     | <b>-</b> 0.5     | 1 <b>9</b> 6     | . 36         | 4                | 2               | 16.05             | 18                          | 203.2          | 2  |

| 2     | 0.0              | 188              | 58           | 12               | 6               | 16.21             | 35.8                        | 1 <b>9</b> 9.6 | 4  |

| 3     | +0.5             | 178              | 79           | 22               | 11              | 16.50             | 51.5                        | 192.44         | 6  |

| 4     | +1.0             | 162              | 109          | 38               | 19              | 16.90             | 73.1                        | 183.5          | 8  |

| 5     | +1.0             | 149              | 106          | 51               | 25.5            | 17.58             | 63                          | 16 <b>9.</b> 2 | 10 |

| 6     | +1.0             | 138              | 104          | 62               | 31              | 18.4              | 54.6                        | 157.6          | 12 |

| 7     | +1.0             | 128              | 100          | 72               | 36              | 19.36             | 44.6                        | 147.7          | 14 |

| 8     | +1.0             | 120              | 97           | 80               | 40              | 20.42             | 36                          | 139            | 16 |

| 9     | +1.0             | 114              | 93           | 86               | 43              | 21.56             | 29.4                        | 132.1          | 18 |

| 10    | +1.0             | 108              | 90           | 92               | 46              | 22.8              | 21.2                        | 126.9          | 20 |

| 11    | <del>+</del> 1.0 | 105              | 86           | 95               | 47.5            | 24.06             | 14.4                        | 121.8          | 22 |

| 12    | +1.0             | 102              | 83           | 98               | 49              | 25.36             | 8.6                         | 119.3          | 24 |

| 13    | +1.0             | 100              | 80           | 100              | 50              | 26.69             | 3 <b>.</b> 3                | 116.9          | 26 |

| 14    | +1.0             | 99'.5            | 79           | 100.5            | 50.25           | 28.03             | 0.72                        | 115.3          | 28 |

| 15    | +1.0             | 98.6             | 77.5         | 101.4            | 50.7            | 29.38             | <b>-</b> 2 <b>.</b> 58      | 114.2          | 30 |

| 16    | +1.0             | 99               | 78           | 101              | 50.5            | <b>30.7</b> 2     | - 3.22                      | 114.6          | 32 |

| 17    | +1.0             | 99.5             | 79           | 100.5            | 50.25           | 32.06             | - 3.31                      | 115.24         | 34 |

| 18    | +1.0             | 100              | 80           | 100              | 50              | 33 <b>.</b> 39    | <b>-</b> 3.39               | 116            | 36 |

| 19    | +1.0             | 100.6            | 80.7         | 99.4             | 49.7            | 34.71             | <b>-</b> 3.7                | 116.7          | 38 |

| 20    | +1.0             | 101.1            | 81.2         | 98.9             | 49.5            | 36.03             | <b>-</b> 4.33               | 117.5          | 40 |

| 21    | +1.0             | 101.8            | 82.1         | 98.2             | 49.1            | 37.3 <sup>4</sup> | <b>-</b> 4.34               | 118.2          | 42 |

| 22    | +1.0             | 102.4            | 83           | 97.6             | 48.8            | 38.64             | - 4.44                      | 119.1          | 44 |

| 23    | +1.0             | 103              | 84           | 97               | 48.5            | 39 <b>.</b> 94    | - 4.44                      | 119.9          | 46 |

| 24    | +1.0             | 103.8            | 84.7         | <b>9</b> 6.2     | 48.1            | 41.32             | <b>-</b> 4.72               | 120.67         | 48 |

| 25    | +1.0             | 104.5            | 85.3         | <b>9</b> 5.5     | 47.8            | 42.59             | <b>-</b> 5.09               | 121.7          | 50 |

| 26    | +1.0             | 105.3            | 86.1         | 94.7             | 47.35           | 43.85             | - 5.1                       | 122.6          | 52 |

| 27    | +1.0             | 106              | 87           | 94               | 47              | 45.10             | - 5.1                       | 123.54         | 54 |

| 28    | +1.0             | 106.8            | 87 <b>.9</b> | 93.2             | 46.6            | 46.34             | - 5.04                      | 124.42         | 56 |

| 29    | +1.0             | 107.7            | 88.6         | 92.3             | 46.15           | 47.57             | <b>-</b> 5.12               | 125.4          | 58 |

| 30    | +1.0             | 108.4            | 89.2         | <b>9</b> 1.6     | 45.8            | 48.79             | <b>-</b> 5.39               | 126.4          | 60 |

| 31    | +1.0             | 109.1            | 90           | 90.9             | 45.45           | 50.00             | - 5.45                      | 127.32         | 62 |

| 32    | +1.0             | 110              | 90.4         | 90               | 45              | 51.20             | - 5.80                      | 128.2          | 64 |

| 33    | +1.0             | 111              | 91.2         | 89               | 44.5            | 52.38             | - 5.68                      | 129.24         | 66 |

| 34    | +1.0             | 112              | <b>9</b> 2   | 88               | 44              | 53.55             | - 5.55                      | 130.38         | 68 |

TABLE 1.2 (Continued)

| j    | e<br>gj      | e <sub>b</sub> j | îb<br>j | e <sub>P</sub> j  | <sup>i</sup> Rj    | <sup>i</sup> Lj | <sup>i</sup> C <sub>j</sub> | Ej             | t   |

|------|--------------|------------------|---------|-------------------|--------------------|-----------------|-----------------------------|----------------|-----|

| 35   | +1.0         | 112.9            | 92.9    | 87.1              | 43.55              | 54.71           | <del>-</del> 5.36           | 131.51         | 70  |

| 36   | +1.0         | 113.8            | 93.4    | 86.2              | 43.1               | 55.86           | <b>-</b> 5.56               | 132.55         | 72  |

| 37   | +1.0         | 114.6            | 94      | 85.4              | 42.7               | 57.00           | <b>-</b> 5.70               | 133.59         | 74  |

| 38   | +1.0         | 115.7            | 94.7    | 84.3              | 42.15              | 58.12           | - 5.57                      | 134.54         | 76  |

| 39   | +1.0         | 116.7            | 95.1    | 83.3              | 41.65              | 59.23           | <del>-</del> 5.78           | 135.8          | 78  |

| 40   | +1.0         | 117.7            | 95.9    | 82.3              | 41.15              | 60.31           | - 5.56                      | 136.9          | 80  |

| 41   | +1.0         | 118.5            | 96.3    | 81.5              | 40.75              | 61.40           | <del>-</del> 5.85           | 138.0          | 82  |

| 42   | +1.0         | 119.7            | 97      | 80.3              | 40.15              | 62.47           | <b>-</b> 5.62               | 138.9          | 84  |

| 43   | +1.0         | 120.6            | 97.6    | 79.4              | 39.7               | 63.53           | - 5.63                      | 140.2          | 86  |

| 44   | +1.0         | 121.6            | 98      | 78.4              | 39.2               | 64.57           | - 5.77                      | 141.25         | 88  |

| 45   | +1.0         | 122.7            | 98.6    | 77.3              | 38.65              | 65.60           | <del>-</del> 5.65           | 142.35         | 90  |

| 46   | +1.0         | 123.7            | 99      | 76.3              | 38.15              | 66.61           | - 5.76                      | 143.35         | 92  |

| 47   | +0.5         | 129.1            | 77      | 70.9              | 35.45              | 67.55           | -26                         | 144.65         | 94  |

| 48   | 0.0          | 138.3            | 56      | 61.7              | 30.85              | 68.37           | -43.22                      | 149.7          | 96  |

| 49   | <b>-</b> 0.5 | 151              | 35      | 49                | 24.5               | 69.02           | <del>-</del> 58.52          | 158.14         | 98  |

| 50   | -1.0         | 166.6            | 15.1    | 33.4              | 16.7               | 69.46           | -71.06                      | 169.7          | 100 |

| 51   | -1.0         | 179.8            | 15.1    | 20.2              | 10.1               | 70.33           | <del>-</del> 65.33          | 182.83         | 102 |

| 52   | -1.0         | 192.7            | 15.4    | 7.3               | 3.65               | 70.43           | <b>~</b> 58.68              | 1 <b>9</b> 5.9 | 104 |

| 53   | -1.0         | 204.4            | 15.7    | - 4.4             | - 2.2              | 70.37           | -52.47                      | 207.5          | 106 |

| 54   | -1.0         | 214.0            | 15.9    | <del>-</del> 14.0 | <b>-</b> 7.0       | 70.28           | -47.38                      | 217.0          | 108 |

| 55   | -1.0         | 223.5            | 16.0    | <b>-</b> 23.5     | -11.75             | 69.96           | <b>-</b> 42.21              | 226.7          | 110 |

| 56   | -1.0         | 231.8            | 16.0    | -31.8             | <del>-</del> 15.9  | 69.54           | -37.64                      | 235.1          | 112 |

| 57   | <b>-1.0</b>  | 239.3            | 16.0    | -39.3             | -19.65             | 69.02           | <del>-</del> 33.37          | 242.5          | 114 |

| 58   | -1.0         | 246              | 16.0    | <b>-</b> 46       | -23                | 68.41           | -29.41                      | 249.2          | 116 |

| 59   | -1.0         | 252              | 16.1    | <b>-</b> 52       | <b>-</b> 26        | 67.72           | <b>-</b> 25. <b>7</b> 2     | 255.1          | 118 |

| 60   | -1.0         | 257              | 16.2    | <del>-</del> 57   | <del>-</del> 28.5  | 66 <b>.9</b> 6  | -22.26                      | 260.3          | 120 |

| 61   | -1.0         | 261.3            | 16.2    | <b>-</b> 61.3     | <del>-</del> 30.65 | 66.14           | -19.29                      | 264.7          | 122 |

| 62   | -1.0         | 265.1            | 16.3    | <b>-</b> 65.1     | <del>-</del> 32.55 | 65.27           | -16.42                      | 268.4          | 124 |

| 63   | -1.0         | 268.1            | 16.3    | -68.1             | <del>-</del> 34.05 | 64.36           | -14.01                      | 271.6          | 126 |

| 64   | -1.0         | 270.9            | 16.4    | -70.9             | -35.45             | 63.42           | -11.57                      | 274.2          | 128 |

| 65   | -1.0         | 272.1            | 16.5    | -72.1             | <del>-</del> 36.05 | 62.46           | - 9.91                      | 275.5          | 130 |

| . 66 | -1.0         | 274.0            | 16.6    | <b>-</b> 74       | <del>-</del> 37    | 61.48           | <b>-</b> 7.88               | 277.3          | 132 |

| 67   | -1.0         | 275.7            | 16.6    | -75.7             | <b>-</b> 37.85     | 60.47           | <b>-</b> 6.02               | 278.9          | 134 |

| 68   | -1.0         | 276.9            | 16.6    | -76.9             | <b>-</b> 38.45     | 59.45           | - 4.4                       | 280.2          | 136 |

| 69   | -1.0         | 277.9            | 16.7    | <del>-</del> 77.9 | <del>-</del> 38.95 | 58.44           | - 2.79                      | 281.1          | 138 |

| 70   | -1.0         | 278.7            | 16.7    | -78.7             | <del>-</del> 39.35 | 57.39           | - 1.34                      | 281.9          | 140 |

| 71   | -1.0         | 279.0            | 16.7    | -79.0             | <del>-39.</del> 5  | 56.34           | - 0.14                      | 282.3          | 142 |

| 72   | -1.0         | 279.1            | 16.7    | -79.1             | -39.55             | 55.2 <b>9</b>   | + 0.96                      | 282.4          | 144 |

| 73   | -1.0         | 278.8            | 16.7    | <b>-</b> 78.8     | -39.4              | 54.24           | + 1.86                      | 282.1          | 146 |

TABLE 1.2 (Continued)

| j   | e <sub>gj</sub> | е <sub>ъ</sub> ј | <sup>i</sup> bj | e <sub>P</sub> j             | i <sub>R</sub> j           | <sup>i</sup> L  | <sup>i</sup> C <sub>j</sub> | Ej     | t            |

|-----|-----------------|------------------|-----------------|------------------------------|----------------------------|-----------------|-----------------------------|--------|--------------|

| 74  | -1.0            | 278.5            | 16.7            | <b>-</b> 78.5                | -39.25                     | 53.20           | + 2.75                      | 281.8  | 148          |

| 75  | -1.0            | 278.0            | 16.7            | <b>-</b> 78.0                | <del>-</del> 39            | 52.16           | + 3.54                      | 281.3  | 150          |

| 76  | -1.0            | 277.3            | ` 16.7          | <b>-</b> 77.3                | <del>-</del> 38.65         | 51.13           | + 4.22                      | 280.6  | 152          |

| 77  | -1.0            | 276.5            | 16.6            | <del>-</del> 76.5            | <del>-</del> 38.25         | 50.11           | 4.74                        | 279.8  | 154          |

| 78  | -1.0            | 275.7            | 16.6            | <del>-</del> 75.7            | <del>-</del> 37.85         | 49.10           | 5.35                        | 278.9  | 156          |

| 79  | -1.0            | 274.8            | 16.6            | <del>-</del> 74.8            | -37.4                      | 48.11           | 5.89                        | 277.95 | 158          |

| 80  | -1.0            | 273.7            | 16.6            | <del>-</del> 73.7            | <b>-</b> 36.85             | 47.13           | 6.32                        | 276.94 | 160          |

| 81  | -1.0            | 272.5            | 16.5            | <del>-</del> 72.5            | <b>-</b> 36.25             | 46.17           | 6 <b>.</b> 58               | 275.8  | 162          |

| 82  | -1.0            | 271.2            | 16.5            | -71.2                        | <del>-</del> 35.6          | 45.22           | 6.88                        | 274.5  | 164          |

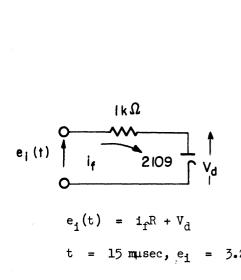

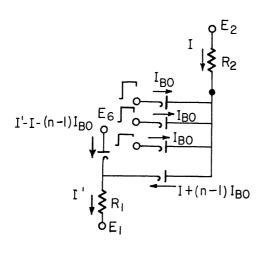

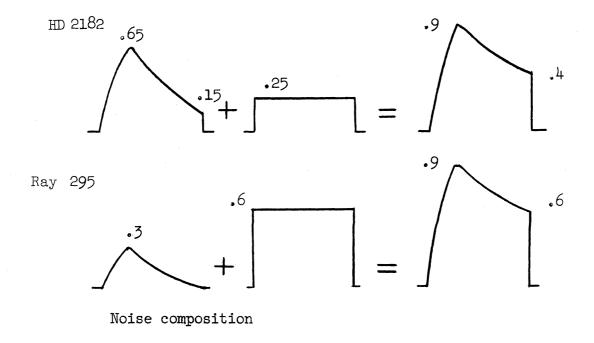

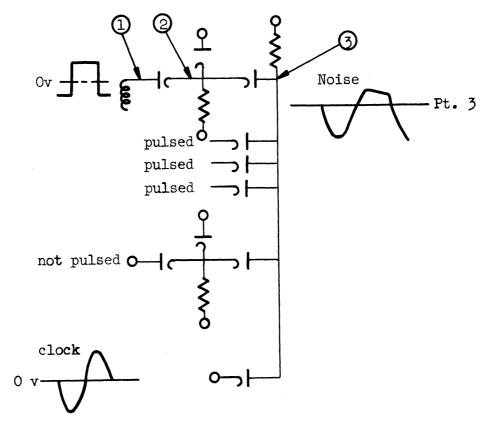

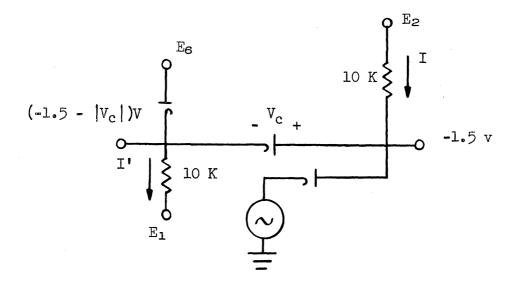

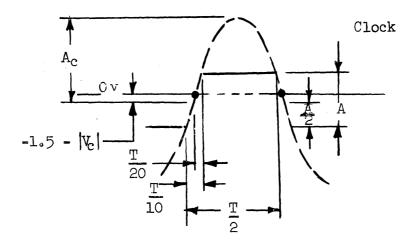

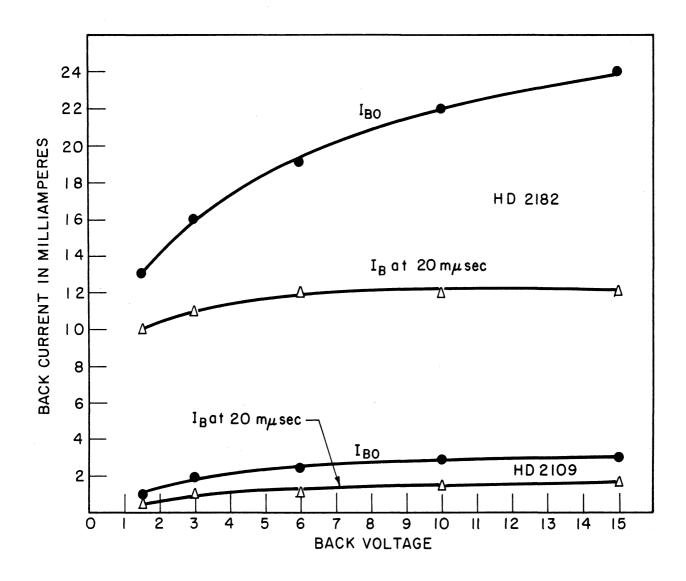

| 83  | -1.0            | 270.0            | 16.5            | <del>-</del> 70.0            | <del>-</del> 35            | 44.28           | 7.22                        | 273.1  | 166          |