# THIN FILM ELECTRONICS BASED ON ZNO AND ZNO/MGZNO HETEROJUNCTIONS

by

## Willie Eugene Bowen

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Associate Professor Jamie Dean Phillips, Chair Professor Fred L. Terry, Jr. Assistant Professor A. John Hart Assistant Research Scientist Becky Lorenz Peterson To my beloved father and my mother

#### **ACKNOWLEDGEMENTS**

In affirmation of my faith, I give all glory and praise to my Savior, the Lord Jesus Christ, who continues to strengthen and uplift my spirit. I am humbled and exceedingly joyful as a witness to his countless blessings.

Throughout my years at the University of Michigan, I have had the opportunity of meeting some wonderful people. And now, I will take a moment to thank those that have made this dissertation possible. Enormous gratitude and sincere thanks are extended to my research advisor and committee chairman, Prof. Jamie D. Phillips, for his respected guidance, supportive encouragement and the opportunity to contribute to the scientific community through doctoral research. I also thank my other committee members, Prof. Fred Terry, Prof. A. John Hart, and Dr. Becky Peterson for devoting their time to review this dissertation and offering constructive suggestions. Special thanks to Prof. Jasprit Singh and Prof. Fred Terry for the valuable mentoring discussions, encouragement, and advice.

The contributions from my past and current research group members, Dr. Ding-Yuan Chen, Tim Murphy, Dr. Kaveh Moazzami, Dr. Pierre Yves-Emelie, Weiming Wang, Emine Cagin, Jeffrey Siddiqui, Albert Lin, Jinyoung Hwang, and Anne Itsuno are to be acknowledged. It was a great pleasure and an inspiring experience to work with each of you.

During the course of my research, I have benefited from the technical suggestions, friendly conversations, and listening ear of many, including Dr. Andre Taylor, Dr. Jian Xu, Dr. Jun Yang, Brandon Lucas, Dr. Sanghyun Seo, Dr. Xinen Zhu, Cedric Whitney, Tim Brock, Dr. Sandrine Martin, Dr. Pilar Herrera-Fierro and others on the Solid State Electronics Laboratory staff, Dr. Wei Guo, Meng Zhang, Debashish Basu, Dr. Taeil Jung, Luke Lee, Min Kim, Dr. Tao Li, Victor Lee, and Tze-Ching Fung.

I have had the opportunity to benefit from the listening ear and encouragement of Beth Stalnaker and Becky Turanski. These women have been great to me throughout my entire time at the university. There are so many others at the university and outside of its surroundings who have shaped my experience. I do not believe that personal relation, triumphs, nor trials occur by accident. Rather, these occurrences are nothing more than a snapshot of the portrait planned for my life.

Finally, I am continually sustained by the loving memory of my father. And among other feelings of gratitude, I am immeasurably thankful for the loving support, encouragement, and understanding from both he and my mother.

# TABLE OF CONTENTS

| DEDICATION                                                           | ii   |

|----------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                     |      |

| LIST OF FIGURES                                                      | vii  |

| LIST OF TABLES                                                       |      |

| ABSTRACT                                                             | xiii |

| Chapter I                                                            | 1    |

| INTRODUCTION                                                         | 1    |

| 1.1 Thin-Film Transistors for Display Electronics                    | 3    |

| 1.2 Zinc Oxide Thin-Film Transistors                                 |      |

| 1.3 Complementary Electronics using Zinc Oxide Thin-Film Transistors | 8    |

| 1.4 Objective and Organization of this Dissertation                  |      |

| Chapter II                                                           | 13   |

| PULSED LASER DEPOSITION OF ZNO THIN FILMS                            |      |

| 2.1 General Introduction of ZnO Properties                           | 13   |

| 2.2 Basic Aspects of Pulsed Laser Deposition                         | 17   |

| 2.3 Material Characterization                                        | 20   |

| 2.3.1 Structural Characterization                                    | 21   |

| 2.3.2 Optical Characterization                                       | 25   |

| 2.3.3 Electrical Characterization                                    |      |

| 2.4 Conclusion                                                       | 30   |

| Chapter III                                                          |      |

| THE N-CHANNEL ZNO THIN FILM TRANSISTOR IN STATIC OPERATION           | 31   |

| 3.1 Introduction                                                     |      |

| 3.2 ZnO TFT Regions of Operation                                     | 32   |

| 3.2.1 Depletion of Charge                                            |      |

| 3.2.2 Accumulation of Charge                                         |      |

| 3.3 Two-Dimensional ZnO TFT Device Simulation                        | 39   |

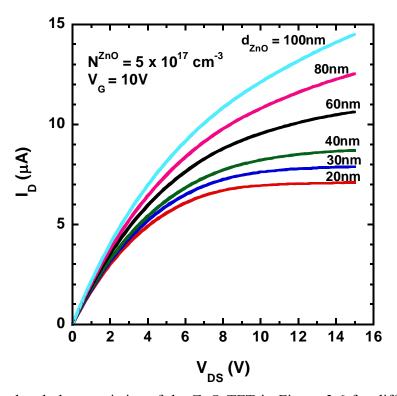

| 3.3.1 Effect of the ZnO Channel Thickness                            | 41   |

| 3.3.2 ZnO Carrier Concentration Dependence                           | 44   |

| 3.4 Conclusion                                                       | 48   |

| Chapter IV.                                                          | 49   |

| FABRICATION AND DC CHARACTERISTICS OF ZNO TFT DEVICE                 | 49   |

| 4.1 Introduction                                                     | 49   |

| 4.2 ZnO TFT Fabrication                                              | 49   |

| 4.3 ZnO TFT Electrical Characteristics                               | 50   |

| 4.3.1 Influence of Active Channel Thickness                          | 54   |

| 4.3.2 Influence of Carrier Concentration                             | 56   |

| 4.4 Non-idealities of Polycrystalline TFTs                           |      |

| 4.4.1 Mobility Dependence on Gate Bias                               |      |

| 4.4.2 Threshold Voltage by Power Law Extraction                                     | 63    |

|-------------------------------------------------------------------------------------|-------|

| 4.5 Conclusion                                                                      | 68    |

| Chapter V                                                                           | 70    |

| PLD GROWTH AND CHARACTERIZATION OF ZNO/MGZNO                                        |       |

| HETEROJUNCTIONS AND APPLICATION TO BURIED-CHANNEL ZNO TI                            | FT 70 |

| 5.1 MgZnO Material Properties                                                       | 71    |

| 5.2 ZnO/ Mg <sub>x</sub> Zn <sub>1-x</sub> O Quantum Well Fabrication               | 74    |

| 5.3 Single Quantum Well Characterization                                            | 75    |

| 5.3.1 Structural Characteristics                                                    |       |

| 5.3.2 Optical Characteristics                                                       | 78    |

| 5.3.3 Polarization and Carrier Localization Effects                                 | 82    |

| 5.4 Buried-Channel ZnO/MgZnO TFT Device                                             | 89    |

| 5.4.1 Simulation of ZnO Buried-Channel TFT                                          |       |

| 5.4.2 Buried-Channel TFT DC Characteristics                                         | 93    |

| 5.5 Conclusion                                                                      | 96    |

| Chapter VI                                                                          |       |

| COMPLEMENTARY INVERTER BASED ON N-CHANNEL ZNO AND                                   |       |

| P-CHANNEL ZNTE TFTS                                                                 | 98    |

| 6.1 ZnTe Characterization and TFT Device Fabrication                                | 99    |

| 6.1.1 Characterization of Thin-Film ZnTe                                            |       |

| 6.1.2 ZnTe TFT Fabrication Process                                                  | 100   |

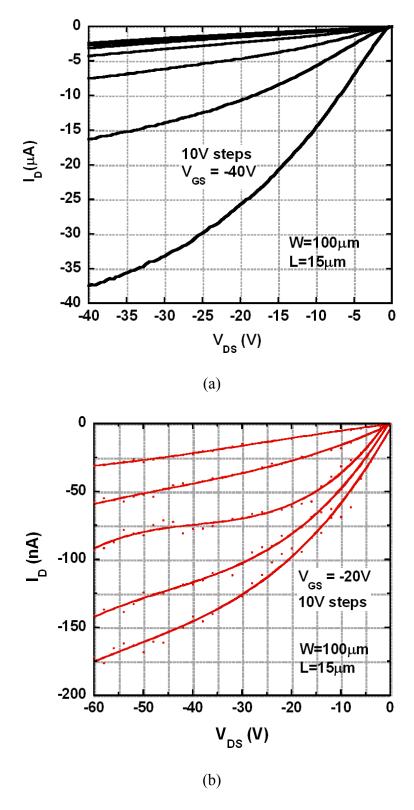

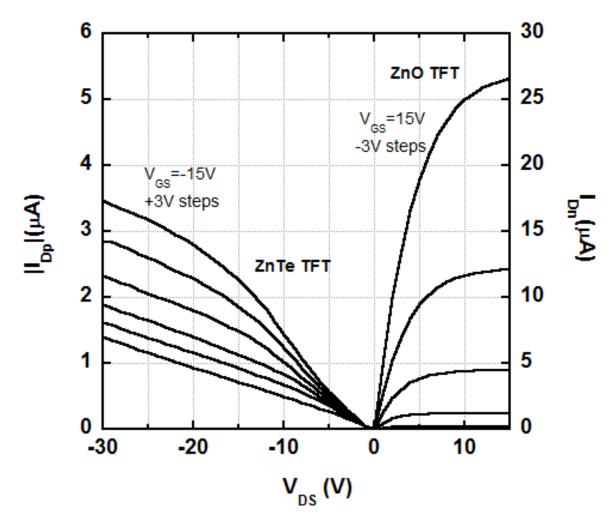

| 6.2 ZnTe TFT DC Charcateristics                                                     | 102   |

| 6.3 Inorganic Inverter Based on <i>n</i> -channel ZnO and <i>p</i> -channel ZnTe    | 108   |

| 6.3.1 CMOS Inverter                                                                 |       |

| 6.3.2 Voltage Transfer Characteristics of <i>n</i> -ZnO and <i>p</i> -ZnTe Inverter | 111   |

| 6.4 Conclusion                                                                      |       |

| Chapter VII                                                                         |       |

| CONCLUSIONS AND FUTURE WORK                                                         |       |

| 7.1 Conclusions                                                                     |       |

| 7.2 Future Work                                                                     |       |

| BIBLIOGRAPHY                                                                        | 119   |

# LIST OF FIGURES

| Figure 3.4 Schematic of a ZnO thin-film transistor illustrating the development of a depletion zone near the drain contact. For $V_{DS} > V_{GS}$ , pinch-off of the entire channel thickness occurs near the drain                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

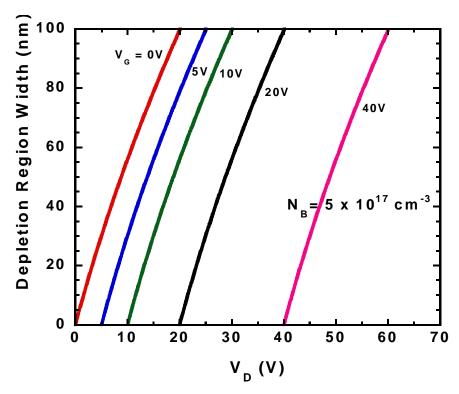

| Figure 3.5 Depletion region width allowing TFT channel pinch-off as a function of $V_{DS}$ and $V_{GS}$ for a background concentration of $N_B$ =5x10 <sup>17</sup> cm <sup>-3</sup> 37                                                         |

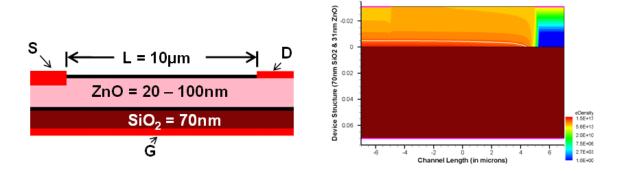

| Figure 3.6 ZnO TFT device structure and example of electron density profile40                                                                                                                                                                   |

| Figure 3.7 Simulated characteristics of the ZnO TFT in Figure 3.6 for different channel layer thickness                                                                                                                                         |

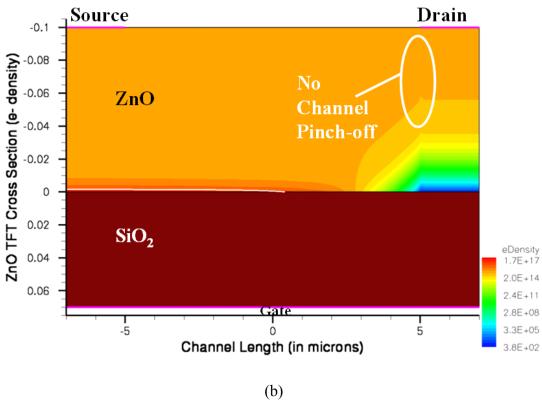

| Figure 3.8 Distribution of electron concentration contour lines for (a) 20nm and (b) 100nm ZnO TFTs                                                                                                                                             |

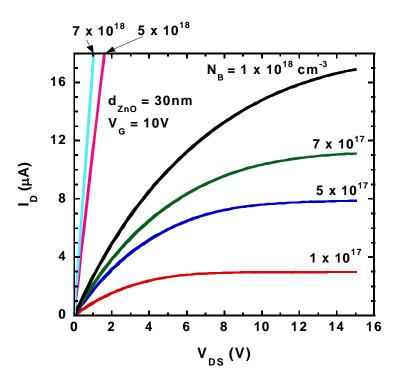

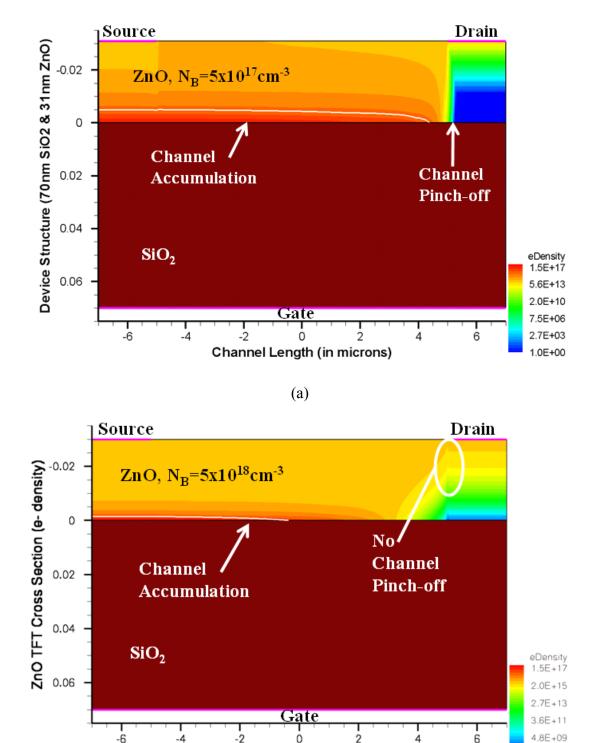

| Figure 3.9 Simulated characteristics of the ZnO TFT in Figure 3.6 for different background carrier concentration                                                                                                                                |

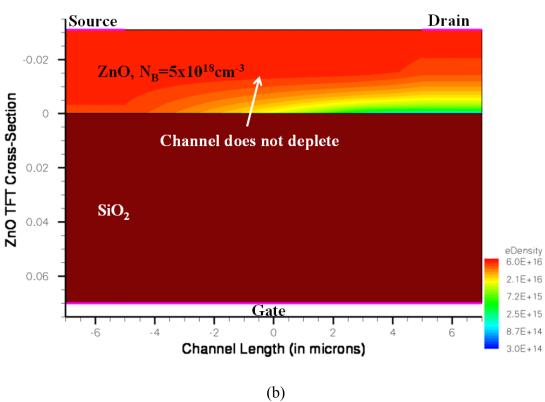

| Figure 3.10 Distribution of electron concentration contour lines for 30nm ZnO TFT with (a) $N_B = 5x10^{17} \text{cm}^{-3}$ and (b) $N_B = 1x10^{18} \text{ cm}^{-3}$ . Pinch-off (current saturation) observed for lower carrier concentration |

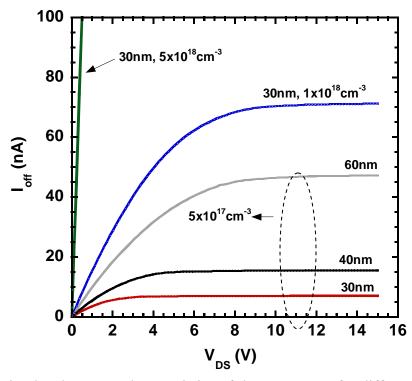

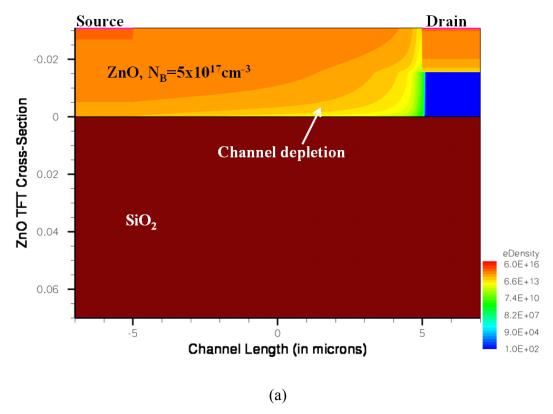

| Figure 3.11 Simulated I <sub>off</sub> -V <sub>DS</sub> characteristics of the ZnO TFTs for different background carrier concentrations and ZnO thickness                                                                                       |

| Figure 3.12 Distribution of the electron density in the off-state for a (a) $N_B = 5x10^{17} cm^{-3}$ and (b) $N_B = 5x10^{18} cm^{-3}$ ZnO TFT with a 31nm thick channel                                                                       |

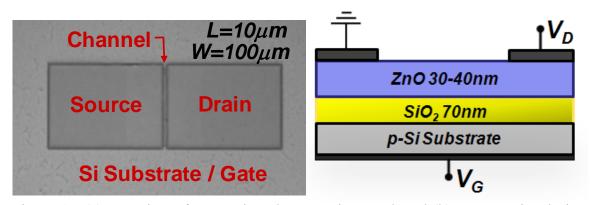

| Figure 4.1 (a) Top view of a scanning electron micrograph and (b) cross-sectional view of a L=10 $\mu$ m (W/L = 10:1) ZnO TFT50                                                                                                                 |

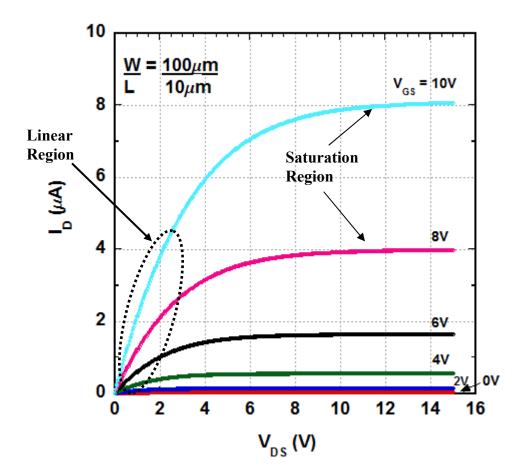

| Figure 4.2 Measured current-voltage, I <sub>D</sub> -V <sub>DS</sub> , characteristics of a ZnO TFT for a 30nm thick channel                                                                                                                    |

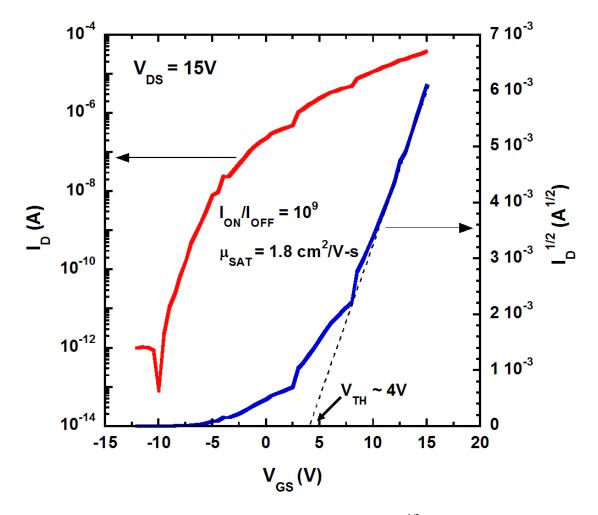

| Figure 4.3 Measured transfer characteristics, $I_D$ - $V_{GS}$ and $ I_D ^{1/2}$ - $V_{GS}$ , of a ZnO TFT with 31nm channel thickness                                                                                                          |

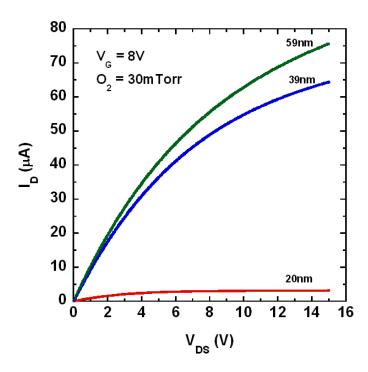

| Figure 4.4 Output characteristics of ZnO TFTs as a function of active channel thickness deposited under similar growth conditions                                                                                                               |

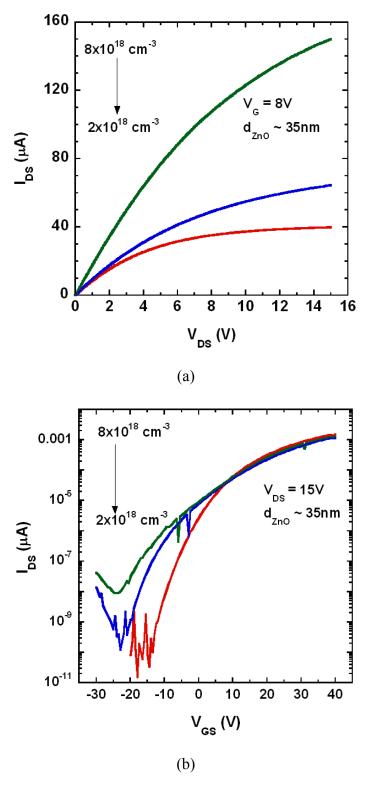

| Figure 4.5 Output characteristics of ZnO TFTs as a function of carrier concentration deposited under similar conditions                                                                                                                         |

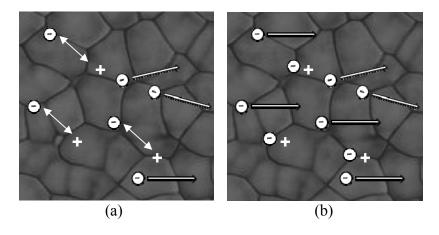

| Figure 4.6 Effect of carrier transport in the ZnO TFT channel region (a) by scattering and trapping mechanisms and (b) "screened" fixed charge from polycrystalline grain boundaries for higher channel charge   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

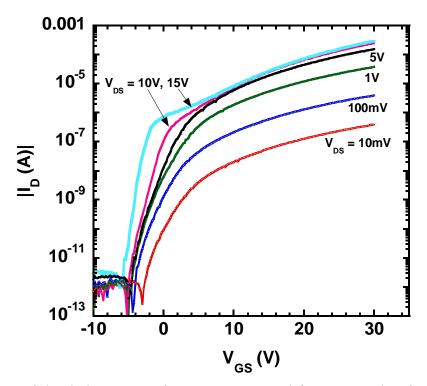

| Figure 4.7 Set of, $\log  I_D $ - $V_{GS}$ , transfer curves measured for $V_{DS}$ ranging from 10mV to 15V illustrating operation in the linear and saturation region60                                         |

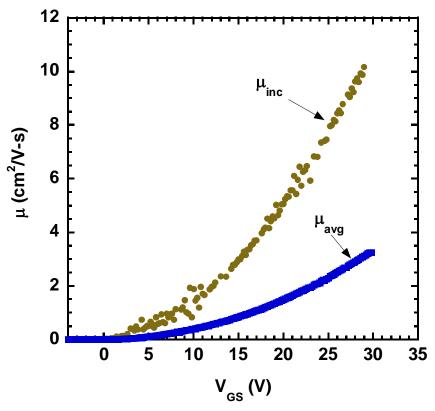

| Figure 4.8 Average mobility, $\mu_{avg}$ , and incremental mobility, $\mu_{inc}$ , dependence on gate bias                                                                                                       |

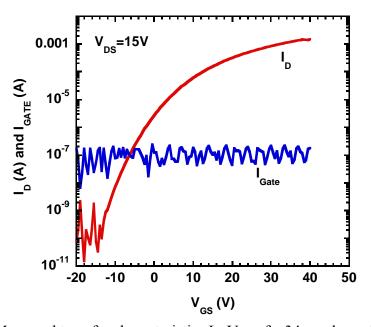

| Figure 4.9 Measured transfer characteristics $I_D$ - $V_{GS}$ of a 34nm channel ZnO TFT64                                                                                                                        |

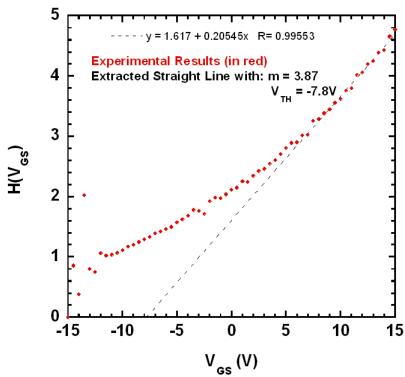

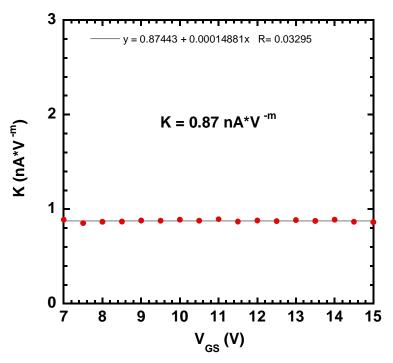

| Figure 4.10 Extracted $V_{TH}$ and empirical parameter, m, from the analytical approximation of $H(V_{GS})$ - $V_{GS}$                                                                                           |

| Figure 4.11 Extracted threshold voltage from the analytical approximation of H(V <sub>GS</sub> )-V <sub>GS</sub>                                                                                                 |

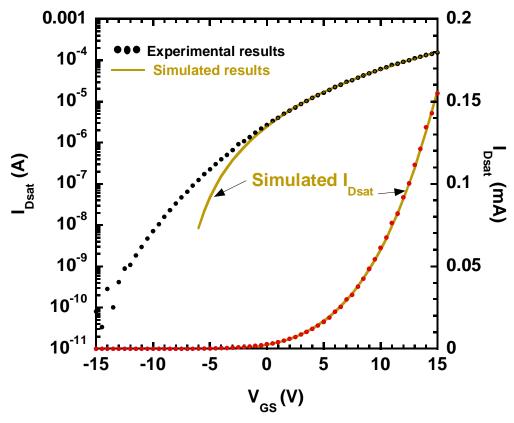

| Figure 4.12 Experimental and simulated transfer characteristics of a ZnO TFT operated in saturation                                                                                                              |

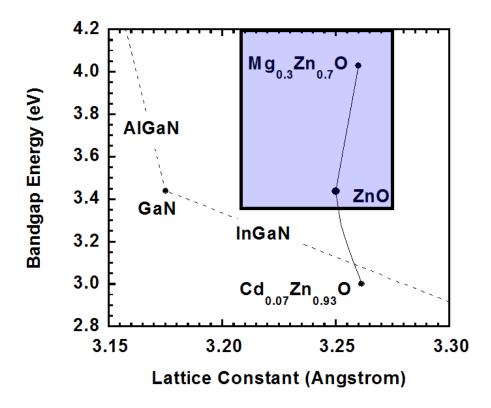

| Fig. 5.1 Bandgap energy versus the a-axis lattice constant of representative II-VI oxide binary compounds                                                                                                        |

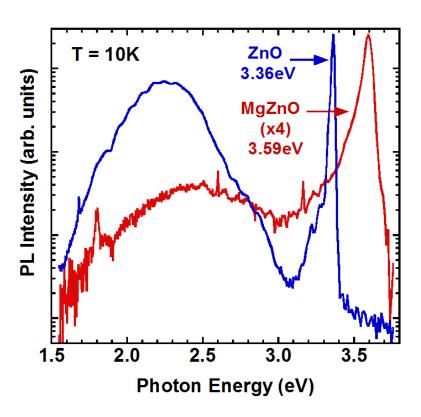

| Fig. 5.2 Low-temperature PL spectra of $Mg_xZn_{1-x}O$ (x=0-0.17) layers with a thickness of 300-nm. A small blueshift in the PL peak position as a function of the photon energy is observed                    |

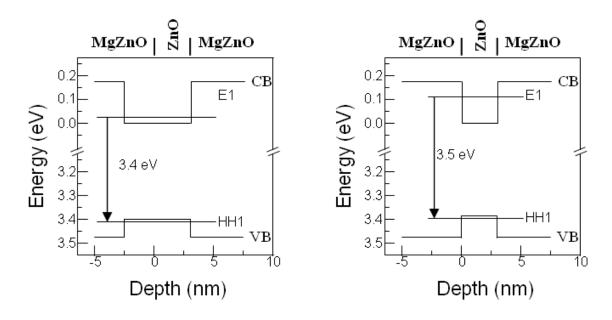

| Figure 5.3 Band profile of a ZnO quantum well demonstrating a blueshift in energy with decreasing well width                                                                                                     |

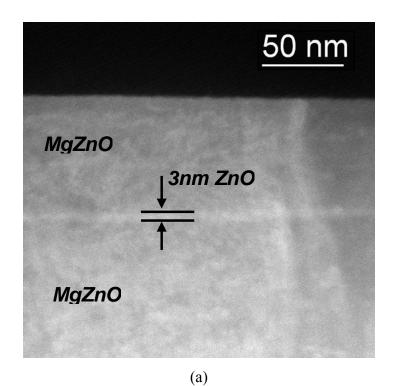

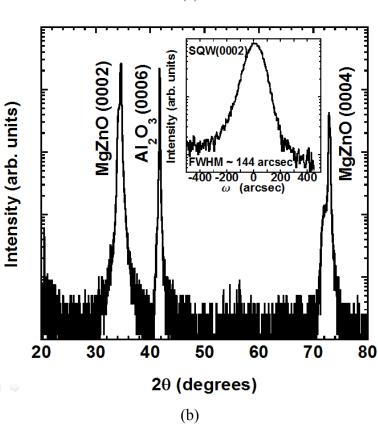

| Fig. 5.4 (a) Cross-sectional TEM image and (b) θ-2θ XRD spectra with rocking curve showing the (0002) diffraction peak of the ZnO(3.0±0.2nm)/Mg <sub>0.17</sub> Zn <sub>0.83</sub> O SQW on a sapphire substrate |

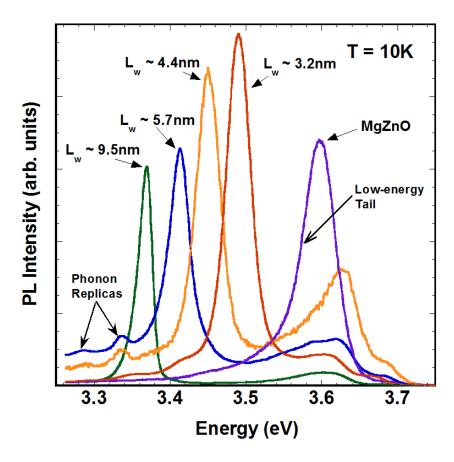

| Fig. 5.5 PL spectra of ZnO/MgZnO SQWs illustrating an excitonic blueshift with decreasing well thickness                                                                                                         |

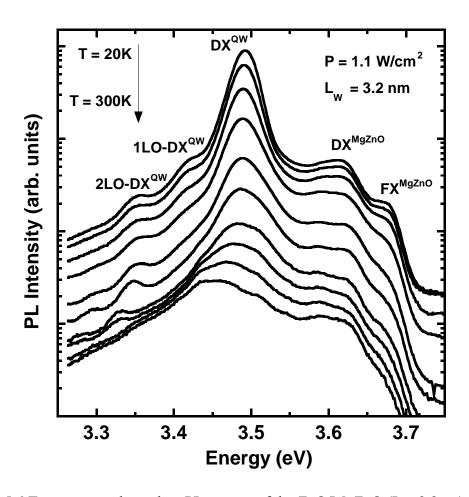

| Fig. 5.6 Temperature-dependent PL spectra of the ZnO/MgZnO ( $L_w \sim 3.2 nm$ ) SQW80                                                                                                                           |

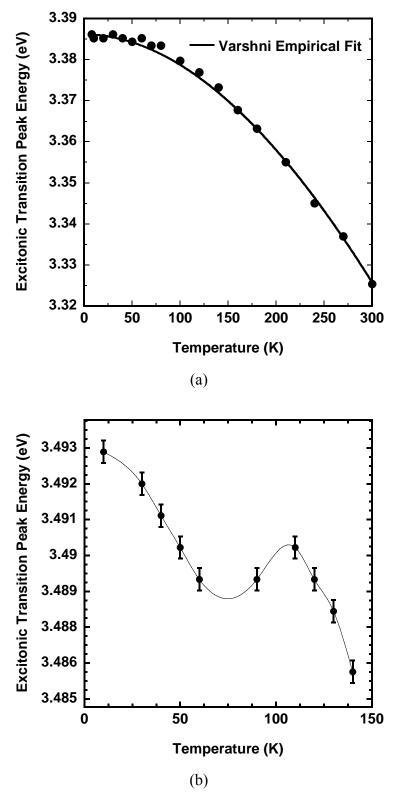

| Fig. 5.7 PL peak energy as a function of temperature for (a) the 5-period ZnO/MgZnO MQW and (b) the ZnO/MgZnO ( $L_w\sim3.2$ nm) SQW exhibiting a red- then blue-shift emission between 20-100K                  |

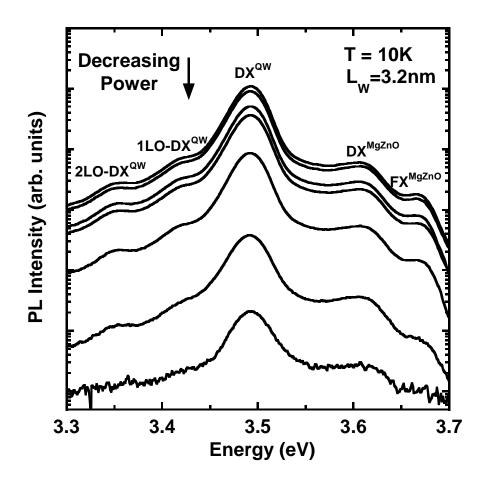

| Fig. 5.8 Excitation-power density dependent PL spectra of a SQW measured at 10K. There is no apparent blueshift with increasing intensity                                                                        |

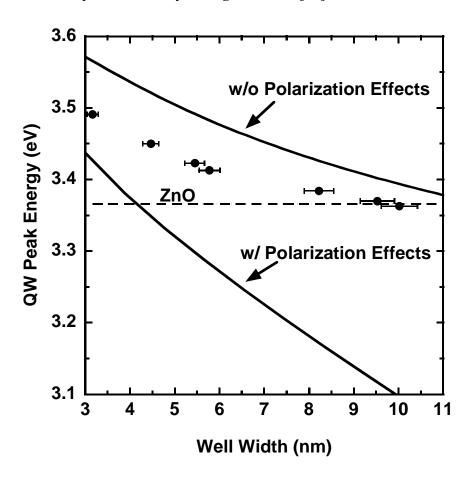

| Fig. 5.9 PL peak emission energy for c-plane SQWs as a function of the well width. The calculated ground state transition taking the exciton binding energy into account is plotted with and without the presence of polarization effects. SQW peak energy redshifts below the ZnO bandedge for well widths above 9.5nm                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

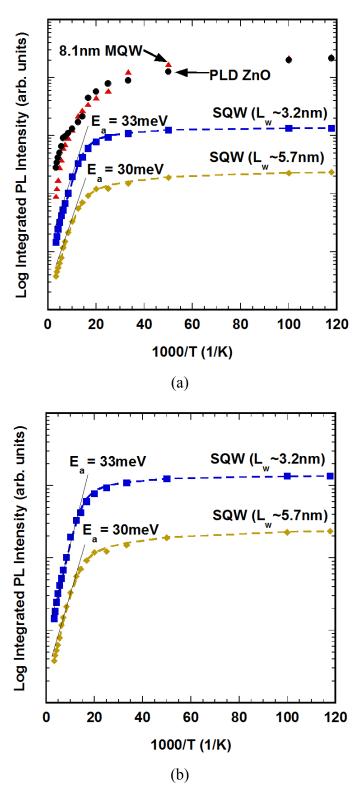

| Fig. 5.10 (a) Integrated PL intensity as a function of temperature for ZnO/MgZnO SQWs (L <sub>w</sub> of 3.2 and 5.7nm), 5-period ZnO/MgZnO MQW and a 530nm thick ZnO epitaxia layer. (b) Arrhenius plot fitted to the SQWs with the activation energy indicated by the slope in the high temperature region                                                                                                                                                                                                                                                      |

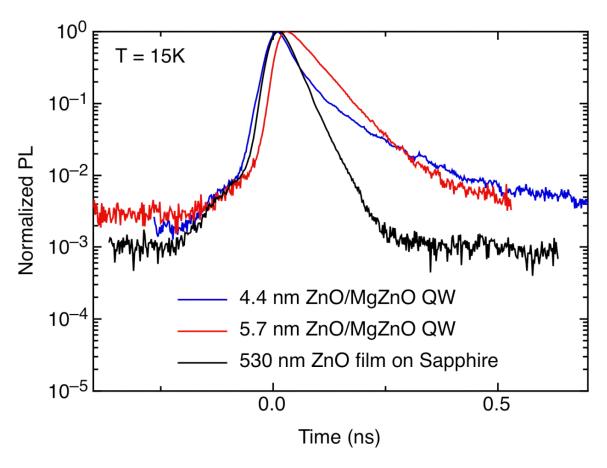

| Fig. 5.11 Time-resolved PL intensity as a function of ZnO/MgZnO SQW width (L <sub>w</sub> of 4.4 and 5.7nm) and a 530nm thick ZnO epitaxial layer                                                                                                                                                                                                                                                                                                                                                                                                                 |

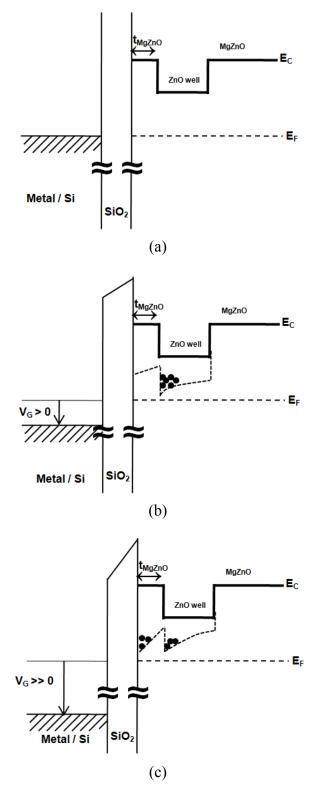

| Fig. 5.12 ZnO/Mg <sub>0.17</sub> Zn <sub>0.83</sub> O SQW forming the channel region of a TFT (a) at flat-band (b) with the accumulation of electrons in the ZnO well region at small $V_{GS}$ and (c) with the accumulation of electrons at the $SiO_2/Mg_{0.17}Zn_{0.83}O$ interface along with that in the well region at higher $V_{GS}$                                                                                                                                                                                                                      |

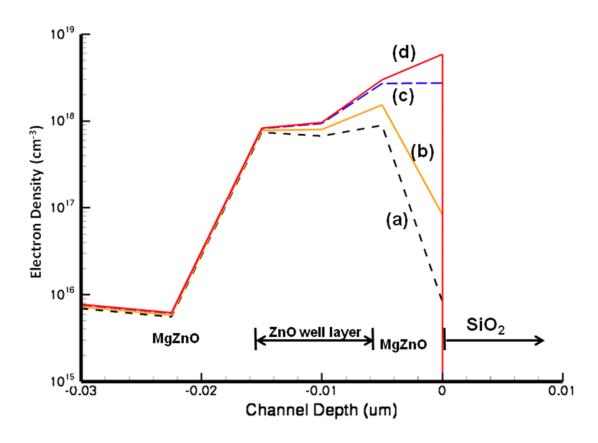

| Fig. 5.13 ZnO/Mg <sub>0.17</sub> Zn <sub>0.83</sub> O SQW forming the buried-channel region of a TFT with spatial distribution of electron accumulation for four different gate bias conditions (a accumulation 5-15nm from SiO <sub>2</sub> at $V_{GS}$ =5V, b: increased accumulation of electrons near the ZnO/MgZnO interface at $V_{GS}$ =10V, c: electron accumulation at the ZnO/MgZnO interface equals that at the SiO <sub>2</sub> /MgZnO interface at $V_{GS}$ =25V, and d: surface accumulation along the SiO <sub>2</sub> interface at $V_{GS}$ =30V) |

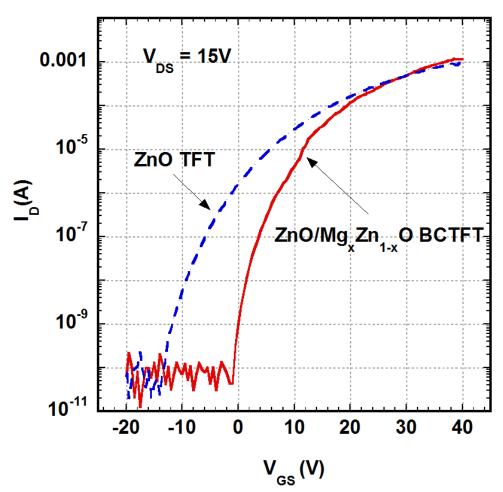

| Fig. 5.14 Transfer characteristics for a ZnO-Mg <sub>0.17</sub> Zn <sub>0.83</sub> O buried-channel TFT and a surface channel ZnO TFT operated in saturation, $V_{DS}$ =15V. The BCTFT has a much steeper subthreshold slope                                                                                                                                                                                                                                                                                                                                      |

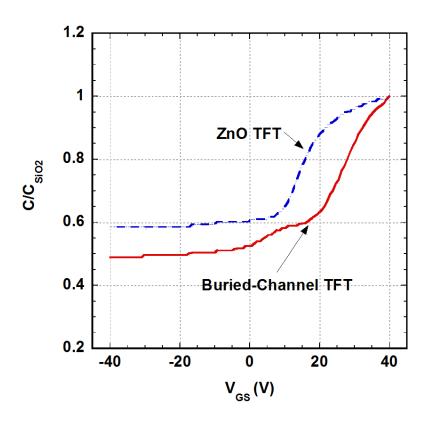

| Fig. 5.15 Capacitance-voltage (C-V) relation for a buried-channel and surface channel ZnO TFT of comparable thickness. The plateau in the C-V for the BCTFT denotes electron confinement in the buried channel ZnO layer at $V_{GS}$ =15V94                                                                                                                                                                                                                                                                                                                       |

| Fig. 5.16 Transfer characteristics for a ZnO-Mg <sub>0.17</sub> Zn <sub>0.83</sub> O buried-channel TFT a $V_{DS}$ =15V. The increase in the calculated field-effect mobility demonstrates a significant contribution due to isolation of the ZnO channel                                                                                                                                                                                                                                                                                                         |

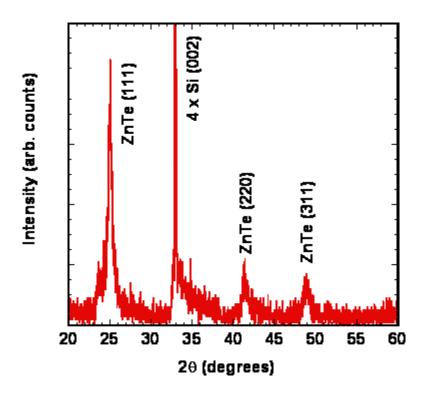

| Figure 6.1 X-ray diffraction of the ZnTe film grown on a SiO <sub>2</sub> /Si substrate101                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

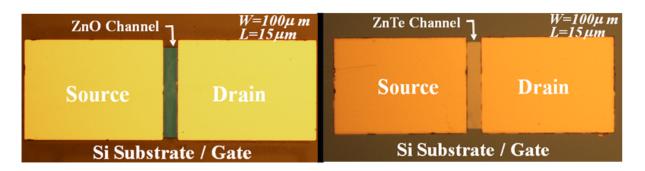

| Figure 6.2 Top-view optical microscope image of the bottom-gate ZnO and ZnTe TFT devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 6.3 Drain current-voltage (I <sub>D</sub> -V <sub>DS</sub> ) characteristics of a representative ZnTe TFT with the active channel layer deposited by (a) MBE and (b) PLD103                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 6.4 Drain current-voltage (I <sub>D</sub> -V <sub>DS</sub> ) characteristics of a representative ZnTe (left) and ZnO (right) TFT                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

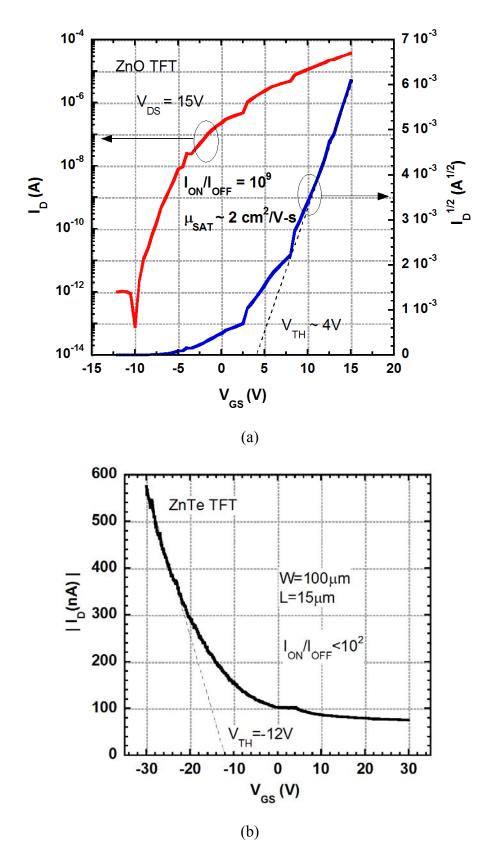

| Figure 6.5 Transfer ( $I_D$ - $V_{GS}$ ) characteristics for the (a) ZnO and (b) ZnTe TFTs107                                                                                                                 |

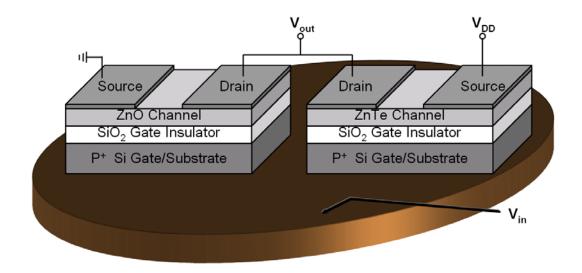

| Figure 6.6 Schematic (3-D) view of the bottom-gate n-channel ZnO and p-channel ZnTe based inverter. The conducting stage of the DC test station serves to apply V <sub>in</sub> between the two gate contacts |

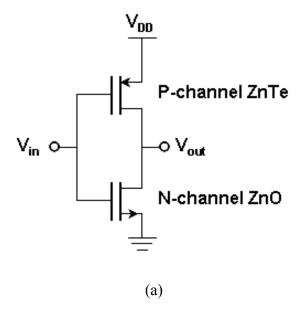

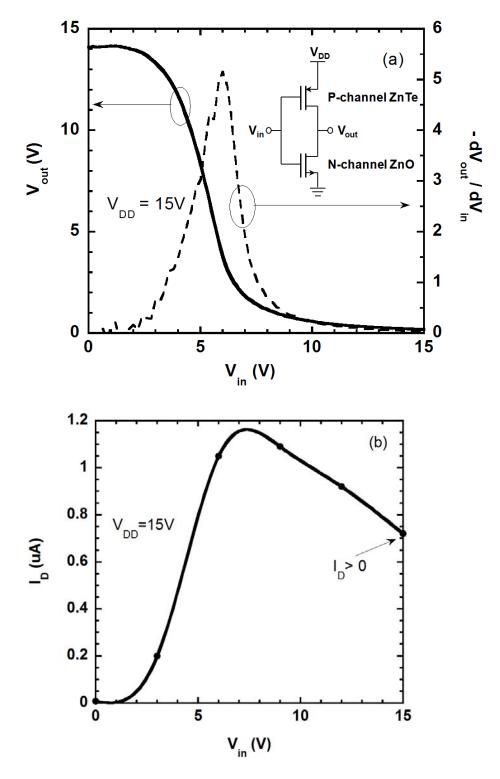

| Figure 6.7 (a) Circuit diagram and (b) idealized voltage transfer characteristic of complementary p-channel ZnTe and n-channel TFT inverter                                                                   |

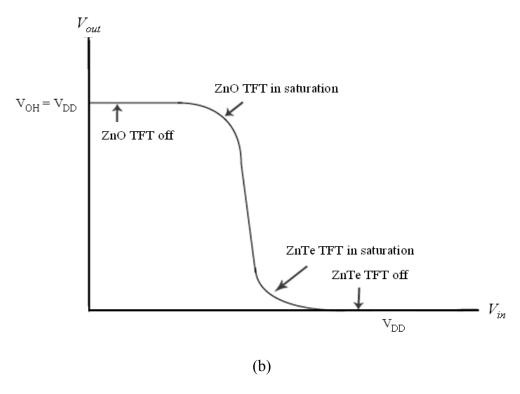

| Figure 6.8 Load line analysis and mapping on measured voltage transfer characteristic (VTC) curve for (a) voltage output low, $V_{OL}$ , and (b) voltage output high, $V_{OH}$ 112                            |

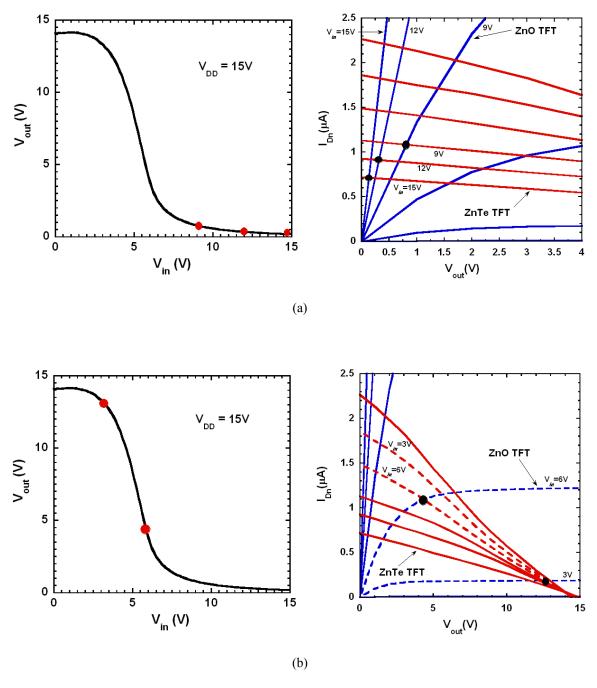

| Figure 6.9 Measured voltage transfer characteristic and corresponding voltage gain (a) with switching current (b) of the complementary thin-film transistor inverter with p-ZnTe/n-ZnO channels               |

# LIST OF TABLES

| Table 2.1 Comparison of material properties of ZnO with that of other wide band semiconductors           | 0 1 |

|----------------------------------------------------------------------------------------------------------|-----|

| Table 5.1 FWHM of the excitonic line broadening for the ZnO/MgZnO SQWs function of increasing well width |     |

#### **ABSTRACT**

The ZnO TFT (Thin Film Transistor) has demonstrated improved electron mobility over entrenched, *a*-Si, technologies and is receiving considerable attention as an alternative TFT technology due to high transparency in the visible region and potential for flexible electronics on conformal substrates. This work studied the material properties of ZnO thin films deposited by pulsed laser deposition, provided a qualitative discussion of TFT operation, applied the buried-channel approach to enhance channel mobility, and demonstrated a complementary logic inverter circuit based on an *n*-channel ZnO TFT and a *p*-channel ZnTe TFT.

The material study in this work focused on optimal deposition conditions needed to realize low-resistivity ZnO thin films. Various techniques were used to illustrate the effect of decreasing polycrystalline ZnO grain size on carrier mobility and background carrier concentration as a function of thickness. Building on these results, discussion of TFT operating principles concentrated on explaining its dependence on carrier concentration and active-channel thickness. The resulting performance of surface-channel ZnO TFTs demonstrated saturation mobility of  $\mu_{SAT} = 1.8 \text{cm}^2/\text{Vs}$ , current on/off ratio of  $I_{ON}/I_{OFF} > 10^9$ , and off current of  $I_{OFF} = 10 \text{pA}$ .

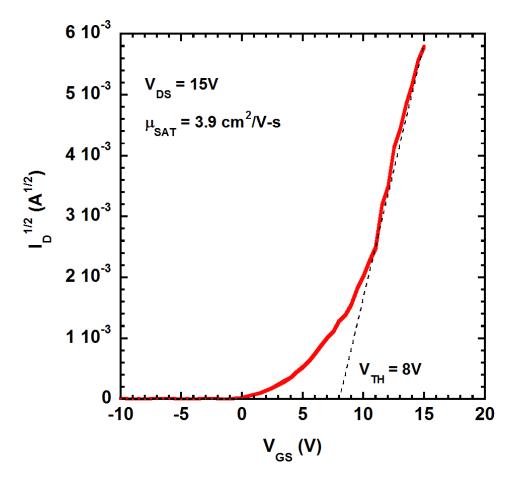

A buried-channel approach to suppress the effect of electron trapping on carrier transport by isolating the ZnO active channel was presented. Quantum confined

structures, such as quantum wells, enhance speed of electronic devices due to carrier confinement. Quantum wells based on the  $ZnO/Mg_xZn_{1-x}O$  ( $x\leq0.3$ ) material system have been grown on c-plane sapphire substrates. Luminescent properties characterized by low-temperature photoluminescence revealed quantum confinement with a systematic blueshift as a function of decreasing ZnO well width in the range from 3nm to 10nm. An enhancement in saturation mobility of  $3.9cm^2/V$ -s was achieved by utilizing the ZnO/MgZnO heterojunctions to fabricate a buried-channel TFT.

Finally, incorporation of a ZnTe TFT, exhibiting relatively high hole mobility ( $\sim$ 5cm²/Vs), and ZnO TFTs in a complementary logic inverter circuit demonstrated reasonable transfer characteristics. Inverter behavior is demonstrated, with a high output voltage of  $V_{OH} > 14V$  and low output voltage of  $V_{OL} < 0.2V$  are observed for a supply voltage of 15V. The small signal gain for the transfer characteristic is found to be  $-dV_{out}/dV_{in} > 5$  at  $V_{in} = 6V$ .

## Chapter I

#### INTRODUCTION

The modern era of semiconductor electronics owes its existence to the rapid expansion of the metal-oxide semiconductor field-effect transistor (MOSFET), first proposed in 1930 by Lilienfield [1] and developed for practical use in 1960 by Kahng and Atalla [2]. It offered more miniaturization, cost reduction, and longer operating lifetime than the vacuum tube. It is the most important device for very-large scale integrated circuits (ICs) used in logic and semiconductor memory devices. One distinct characteristic of IC technology is its complex integration of many thousands of active and passive devices made primarily in a single wafer of silicon, thus enabling new applications for electronics in communication, control, and data processing not possible with discrete components.

The first all thin-film integrated circuit for scanning an image sensor containing CdSe thin-film transistors (TFTs) was produced in 1965 by Weimer [3]. This allowed for fabrication of transistors and other passive devices on insulating substrates which reduces parasitic losses associated with embedded silicon substrates. Historically, the patent invention by Lilienfield [1] describing the flow of current varied by electrostatic influence from an insulated gate electrode in a semiconductor of minute thickness

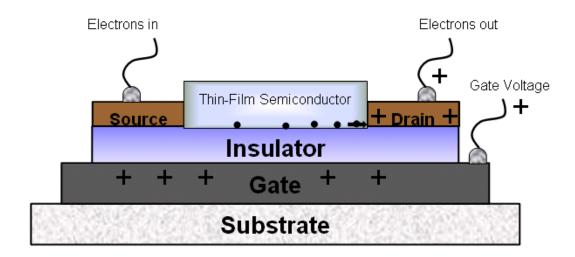

actually describes the first thin-film field effect transistor. A typical TFT under normal operating conditions is shown in Figure 1.1. The application of a positive-bias to the gate electrode induces the accumulation of electrons in the case of an *n*-type semiconductor. At the same time, the positive input voltage at the drain leads to the flow of current as electrons flow from source to drain (reverse electrode voltages for a p-type semiconductor).

Figure 1.1 Typical TFT under normal operation conditions with electrodes marked.

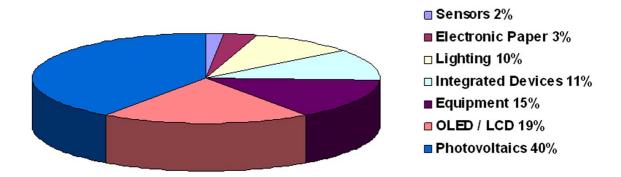

Because of established processing techniques for silicon technology, MOSFETs developed more rapidly than TFTs. However, a new field of macroelectronics is emerging for thin-film, flexible, large area electronics and systems enabling TFTs. These applications include integrated displays, photovoltaics, embedded power sources, sensing devices, smart labels, lighting, and integrated logic devices. Figure 1.2 projects the emerging distribution of predicted growth forecasts for commercially accessible markets employing TFTs and thin-film electronics [4]. This includes inorganic and organic devices, semiconducting and printed, on rigid and flexible substrates.

Figure 1.2 Distribution of predicted growth forecasts for various emerging applications enabling TFT development.

## 1.1 Thin-Film Transistors for Display Electronics

Electronic display technology once limited to the bulky, rugged cathode ray tube (CRT) has matured into an expansive area of industrial commercial development and academic research. Whereupon plasma displays are commercially available for large size television monitors, active-matrix liquid crystal displays (LCDs) and active-matrix organic light-emitting diodes (OLEDs) are the leading technologies for portable display of information. LCDs which preceded OLEDs as the dominant mobile flat-panel display technology is a passive type of display which requires either front (reflective) or rear (transmissive) illumination. However, OLEDs are emissive devices which generate light at the display surface without the need for an external source of illumination. Typically both devices are fabricated on glass substrates, though use of glass substrates poses the undesirable characteristic of being rigid and fragile. Applications including electronic books (e-books), foldable cell phone displays, wearable displays, and compact military display systems are driving the growth for flexible electronic display technology. Flexible displays along with the integrated back-plane electronics compel the need for plastic or

thin metal foil substrates that are unbreakable, rollable, lightweight, and flexible. The back-plane electronics providing the active-matrix switching rely on thin-film transistors (TFTs).

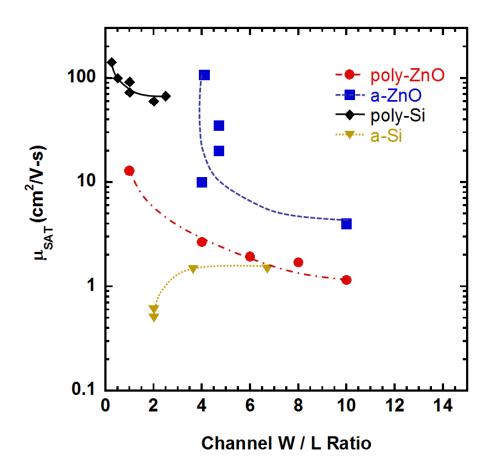

Hydrogenated amorphous silicon (a-Si:H) and polycrystalline silicon (poly-Si) TFTs are the industry standard for the switching and drive circuitry of monolithic active matrix LCD and OLED technology. Overwhelming advantages in favor of poly-Si TFTs are motivated by the need to address low electron field-effect mobility (< 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) associated with a-Si TFTs, and enabling integrated complementary metal oxide semiconductor (CMOS) circuits with high performance n- and p-channel poly-Si TFT devices [5]. However, undesirable large OFF-state leakage current (> 10<sup>-10</sup> A) and high processing temperature are challenges in poly-Si TFT device development. The large leakage current limits charge switching between ON and OFF states. Suppression of high leakage current is concentrated on modification of the device structure or pixel circuit architecture [6]. There has been mounting interest in the use of oxide thin-film transistors (TFTs) as electronic back-plane switching devices for the next generation of large-area flat-panel display applications. Zinc oxide (ZnO) is receiving considerable attention as an alternative TFT technology due to high transparency in the visible region, high ON-to-OFF state switching ratio, and improved mobility over opaque a-Si. A snapshot comparison of the saturated channel mobility as a function of channel width/length (W/L) for various technologies is shown in Figure 1.3. Decreasing mobility with increasing W/L is consistent with all technologies presented. This is due to effects associated with contact resistance and fringing electric-field effects [7].

Figure 1.3 Comparison of saturated channel mobility of various TFT active channel material as a function of W/L [8-24].

#### 1.2 Zinc Oxide Thin-Film Transistors

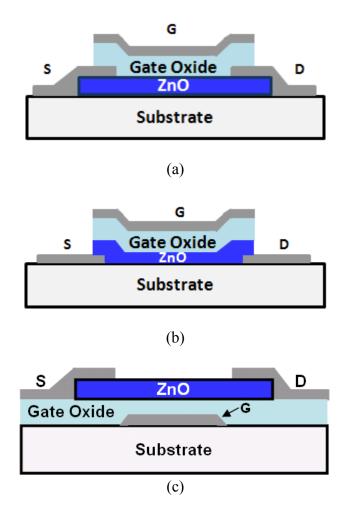

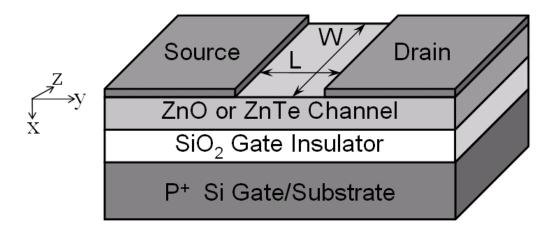

The first reported ZnO insulated-gate field-effect transistor fabricated in a coplanar configuration was demonstrated by Boesen and Jacobs in 1968 [25]. The wide band-gap (E<sub>g</sub>=3.37eV at 300K) of ZnO prohibits device degradation due to carrier photo-generation with exposure to light. This intrinsic property alleviates the need for external shielding during device operation. In this work, polycrystalline ZnO TFT devices are fabricated and the effect of material properties on its DC operating characteristics is discussed. While the coplanar configuration is widely used with the conventional MOSFET device structure, there are essentially three types of TFT configurations: the coplanar, staggered

(top-gate), and inverted-staggered (bottom-gate) structures. The difference in configuration is defined by the position of the gate and source/drain electrodes with respect to the gate insulator and semiconductor layer. The coplanar structures have all three electrodes on one side of the semiconductor layer; whereas, the staggered structures have the gate electrode and the source/drain electrodes on opposite sides of the semiconductor layer [26]. Figure 1.4 depicts a schematic cross-section of the coplanar, top-gate, and bottom-gate ZnO TFTs. Because the bottom-gate TFT is the most extensively reported ZnO device of those previously mentioned, we will concentrate on its formation.

Processing of thin film transistors are composed of four key parts: the gate electrode, the gate insulator, the ZnO active channel region, and the source/drain ohmic contacts. Since the channel region-gate insulator interface is where carrier transport predominately takes place, considerable attention has been devoted to its development. Fixed interface charges (surface states) at the ZnO-gate insulator interface impede carrier flow due to scattering and are detrimental to carrier mobility along the ZnO channel region. As a result, the choice of gate dielectric and pre-ZnO layer surface preparation plays an important role in interface quality. Silicon dioxide, SiO<sub>2</sub>, possesses the attributes of being an extremely good insulator and is the predominant gate dielectric as evidenced in the literature [9,27,28]. Experiments have been reported on the influence of different gate dielectrics on ZnO TFT properties. The use of high-k dielectrics (ε<sub>r</sub>>3.9) allows for thicker gate dielectrics resulting in reduced gate leakage and increased capacitive coupling between the ZnO layer and the gate dielectric. This will make available stable operation of transistors with high operating currents at low operating voltages. There

Figure 1.4 The schematic cross-section of the (a) coplanar; (b) staggered (top-gate); and (c) typical inverted-staggered (bottom-gate) TFT structures.

have been several reports on promising alternatives such as  $Si_3N_4$  [8],  $SiN_x$  ( $\epsilon_r$ =6) [11], (Ba,Sr)TiO<sub>3</sub> ( $\epsilon_r$ =16-500) [29-31], Al<sub>2</sub>O<sub>3</sub> ( $\epsilon_r$ =7) [12], HfO<sub>2</sub> ( $\epsilon_r$ ~30) [32], and Bi<sub>1.5</sub>Zn<sub>1.0</sub>Nb<sub>1.5</sub>O<sub>7</sub> ( $\epsilon_r$ ~51) [33]. Unfortunately, the use of high-k dielectrics does not alleviate electrical degradation caused by carrier trapping at the gate dielectric-active layer interface.

From these studies, it is clear that accumulation of carriers forming the conducting channel for a thin film transistor have to be physically separated in order to minimize

interface trapping and enhance device performance. One way that this can be achieved is by inserting a thin higher-gap material, MgZnO, adjacent to the gate insulator interface with carrier confinement in the lower-gap material, ZnO, thereby forming a buried-channel layer for carrier transport experiencing less scattering and surface interface trapping [34].

#### 1.3 Complementary Electronics using Zinc Oxide Thin-Film Transistors

Flexible electronics that can be subjected to deformation, including twisting, bending, and stretching will provide for interesting applications. These applications include artificial sensor skin, radio frequency identification tags, and wearable electronics on the human body that can be used for computation, information storage, and sensing. Semiconducting oxides including polycrystalline ZnO and amorphous indium gallium zinc oxide (IGZO) have recently emerged as important candidates for thin film transistors intended for flexible electronics due to their relatively high carrier mobility (~10cm<sup>2</sup>/Vs) and ability for low deposition temperature. These flexible transistors can be utilized in applications requiring flexible logic circuitry. Digital logic and related electronic circuitry would benefit tremendously from a complementary device technology in semiconducting oxides. However, these materials are all intrinsically n-type and have not demonstrated a reliable means for obtaining p-type thin films. Alternatively, polycrystalline ZnTe thin films are intrinsically p-type and exhibit relatively high hole mobility (~5cm<sup>2</sup>/Vs) at low deposition temperatures (~200°C). In this work, ZnO and ZnTe thin film transistors (TFTs) are fabricated and characterized. After electrically connecting the TFTs in the appropriate configuration, complementary logic inverters are demonstrated.

## 1.4 Objective and Organization of this Dissertation

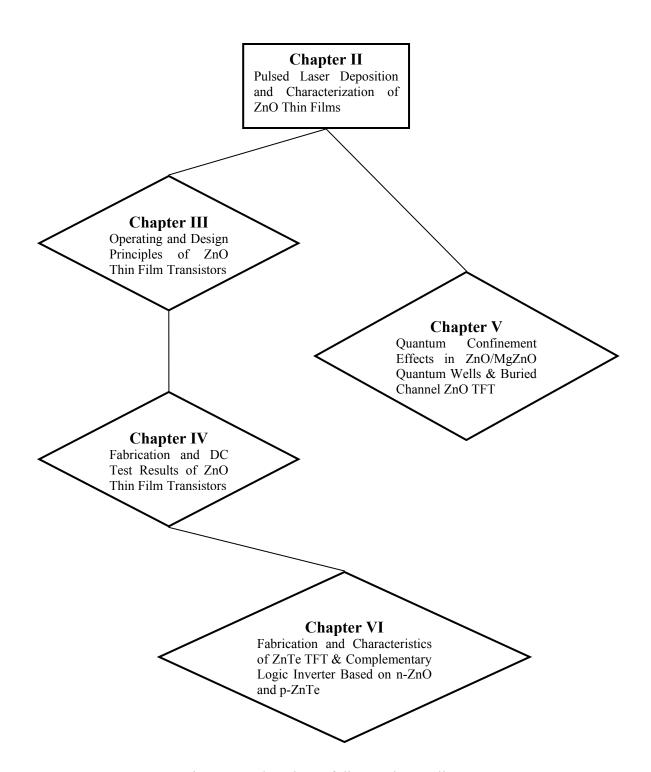

The purpose of this dissertation is to develop a buried-channel technique, based on the polycrystalline ZnO/MgZnO material system, for improved thin film transistor performance and demonstration of a complementary logic inverter based solely on inorganic thin film transistor technology. Electron trapping near the gate dielectric/ZnO interface of conventional surface-channel ZnO TFTs significantly impacts carrier transport and thus limits device performance, specifically the field-effect mobility. Since electron accumulation with appropriate biasing occurs in close vicinity of the interface, typically on the order of 10nm or less, the fabrication of TFTs where conduction takes place in the higher quality ZnO material away from the gate dielectric interface is extremely beneficial. Tradeoffs with the thickness and conduction band offset for the higher energy gap, MgZnO, material are therefore critical to maintaining electron accumulation in the buried-channel. Afterwards p-channel ZnTe TFTs are demonstrated, and the integration of these devices with buried-channel n-channel ZnO TFTs for a complementary inverter circuit are shown to exploit this technologies' relevance for enabling logic integrated circuits (ICs). Figure 1.5 shows a flowchart of the dissertation outline.

Chapter II discusses material growth and characterization of polycrystalline ZnO thin films. Basic aspects of growth by pulsed laser deposition (PLD) are reviewed. The structural, optical, and electrical properties of thin film material are characterized by X-ray diffraction (XRD), transmission electron microscopy (TEM), photoluminescence, and Hall-effect measurement. These characterization techniques are later used to characterize

the grain size, orientation, optical energy gap, and alloy effects of the II-VI semiconductor, zinc telluride (ZnTe), and the alloy, magnesium zinc oxide (MgZnO).

Chapter III presents the operating and design principles of the TFT device. Qualitative description of conventional TFT operation and its dependence on the undoped background carrier concentration (N<sub>B</sub>) and thickness (t<sub>ZnO</sub>) of the active channel layer are reviewed. A two-dimensional numerical model of the TFT device assuming homogenous material is used to illustrate the effect of N<sub>B</sub> and t<sub>ZnO</sub> on the TFT semiconducting channel and output characteristics. Non-idealities of polycrystalline TFTs, such as field-effect mobility and threshold voltage extraction, introduce a certain degree of ambiguity. Mobility dependence on gate bias and threshold voltage by power law extraction gives insight into the transport characteristics' dependence on scattering and trapping mechanisms at the gate dielectric interface.

Chapter IV discusses the fabrication and static DC test results of ZnO TFTs. To avoid confusion associated with the use of different techniques, conventional square-law theory is used to extract the threshold voltage and field-effect mobility of the TFTs. The experimental dependence of  $N_B$  and  $t_{ZnO}$  on output characteristics are presented, and the results are used for developing reproducible TFTs and convey the need for active-channel layer tailoring to achieve increased mobility.

Chapter V presents the optical properties of  $ZnO/Mg_xZn_{1-x}O$  (x=0.17) quantum wells (QWs) grown on c-plane sapphire substrates by pulsed laser deposition are presented. A blueshift in the low-temperature photoluminescence of the QWs illustrate quantum confinement effects as a function of ZnO well widths in the range from 3nm to 10nm. This demonstration of quantum confinement is suitable for fabricating buried-

channel TFTs with the lower energy gap ZnO layer and electron accumulation physically separated from carrier trapping effects at the gate dielectric interface.

Chapter VI discusses the fabrication and device characteristics of ZnTe TFTs. The ZnTe films exhibiting p-type carrier concentration form the active channel layer of the p-channel device. ZnTe layers were deposited by ablation of a ZnTe pressed target using PLD under vacuum (10<sup>-6</sup> Torr). Despite the inferior transistor behavior of the ZnTe device, incorporation of the ZnTe and ZnO TFTs in a complementary logic inverter circuit demonstrates reasonable transfer characteristics. Static operation of the complementary thin-film inverter circuit is characterized and the results analyzed.

Chapter VII summarizes the obtained results and presents proposed directions for future work. Further studies on the introduction of high-k gate dielectrics for higher drive currents at lower operating bias are discussed. Exploration of device process techniques for a buried-channel ZnO TFT is suggested. Finally, further improvement of the ZnTe thin films are addressed for optimized static operation of purely inorganic complementary logic inverters.

Figure 1.5 Flowchart of dissertation outline.

#### **Chapter II**

#### PULSED LASER DEPOSITION OF ZNO THIN FILMS

#### 2.1 General Introduction of ZnO Properties

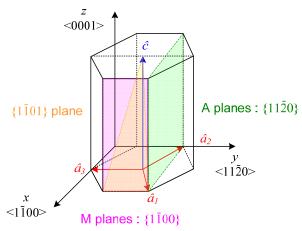

II-VI compounds giving rise to semiconducting materials cover a considerable part of the light spectrum; from near infrared (CdTe) into the ultraviolet (ZnS) region. In addition to the established II-VI wide band-gap compounds ZnS, ZnSe, ZnTe, CdS, and CdSe and other direct band-gap materials such as GaN and SiC, zinc oxide is a wide, direct gap semiconductor (ZnO,  $E_g = 3.4 \text{eV}$  at 300K) which has garnered the focus of intense materials research and device development. Distinguishing advantages of ZnO include: (i) the availability of large area native substrates [35], (ii) highly transparent in the visible region, (iii) an exciton binding energy of 60meV which ensures excitonic emission at temperatures above room temperature ( $k_BT = 26$ meV), (iv) its resistance to high energy radiation damage which enables application in hostile environments [36]; and (v) its susceptibility to wet chemical processing [37]. The comparison of material properties for ZnO and other wide band-gap compounds is given in Table 1. ZnO crystallizes in the wurtzite structure with a hexagonal lattice as shown in Figure 2 and is similar in energy gap to GaN. Furthermore with a lattice mismatch less than 1.8%, it is suitable as an alternative substrate for growth of high-quality GaN epilayers and its alloys [38]. ZnO, which has a tendency to grow with c-plane (0001) preferential orientation, has

| Materials | Crystal    | Bandgap     | Lattice C    | onstants    | <b>Exciton Binding</b> |

|-----------|------------|-------------|--------------|-------------|------------------------|

|           | Structure  | Energy (eV) | <u>a (Å)</u> | <u>c(Å)</u> | Energy (meV)           |

| ZnO       | Wurtzite   | 3.4         | 3.25         | 5.21        | 60                     |

| ZnS       | Wurtzite   | 3.8         | 3.82         | 6.26        | 39                     |

| ZnSe      | Zincblende | 2.7         | 5.67         |             | 20                     |

| GaN       | Wurtzite   | 3.4         | 3.19         | 5.19        | 21                     |

| 6H-SiC    | Wurtzite   | 2.9         | 3.08         | 15.1        |                        |

TABLE 2.1 Comparison of material properties of ZnO with that of other wide band gap semiconductors.

Figure 2.1 Wurtzite lattice for ZnO illustrating a-plane, c-plane, and m-plane.

been shown to exhibit m-plane ( $10\overline{1}0$ ) orientation on cubic MgO substrates [39] and a-plane ( $11\overline{2}0$ ) orientation on r-plane sapphire [40]. Though the natural structure of ZnO is wurtzite resulting in the existence of polarization along the c-axis, growth along these alternative orientations provide for nonpolar epitaxial ZnO.

Additional advantages associated with ZnO and other wide band-gap semiconductors are its thermal stability which facilitates high-temperature operation and the high breakdown voltage making it ideal for high-power switching devices. While the electron drift velocity of GaN and ZnO are comparable, the peak electric field for ZnO is

about 100kV/cm higher than GaN [41]. Its direct band-gap and large exciton binding energy make it attractive for optoelectronic devices such as ultraviolet (UV) photodetectors and blue-UV light emitters, such as light-emitting diodes (LEDs) and laser diodes (LDs). Other applications include surface acoustic wave devices [40], gas sensors [42], and transparent conducting films for solar cells [43]. The tremendous potential of ZnO and novel devices based on the II-VI material is further broadened by band-gap engineering. Alloying with CdO and MgO allows for modulation of the bandgap from 3.0eV (CdyZn<sub>1-y</sub>O) to 4.0eV (Mg<sub>x</sub>Zn<sub>1-x</sub>O). Heterojunctions based on the II-VI oxide semiconductor and its ternaries make possible the fabrication of such devices as high electron mobility transistors (HEMTs) [44] and tunable wavelength optoelectronic devices.

Realization of a homogeneous ZnO optoelectronic device requires n- and reliable p-type ZnO, which has been problematic. This is analogous to the p-type conductivity limitations that once hindered other wide band-gap II-VI materials such as ZnS, ZnSe, and GaN; similarly, there is an n-type doping limitation in the case of ZnTe. There have been reports on p-type ZnO material with the group V elements N [45], P [46], As [47], Sb [48], and Bi [49], though stability and reproducibility are controversial. With smaller ionic radii than that of O, N is the most promising dopant though P doping has resulted in the lowest resistivity p-ZnO material with  $\rho$ =0.6  $\Omega$ -cm [50,51]. Nonetheless, several authors have reported on the fabrication of ZnO homojunction light emitting devices [52]. In the absence of p-ZnO, high-quality heterostructure LED devices are possible and have been fabricated using p-GaN [53].

The shallow donor naturally occurring in n-type ZnO is attributed to native point defects associated with zinc and oxygen vacancies, interstitials, and antisites [54]. The equilibrium concentration of the defect affects the electrical and optical properties of the metal oxide. Using first-principle calculations of defect formation energy as a function of the Fermi energy, the two most abundant defects in Zn-rich material were shown to be zinc (V<sub>Zn</sub>) and oxygen (V<sub>O</sub>) vacancies which act as donors. Because V<sub>O</sub> has lower formation energy than zinc interstitials (Zn<sub>i</sub>), it is expected to occur in higher concentration. Though under O-rich conditions, V<sub>Zn</sub> is the main native point defect. For both the Zn-rich and O-rich material, the transition from the -1 to -2 charge state of V<sub>Zn</sub> occurs at approximately 0.8eV above the valence band. This is a possible mechanism for the pronounced broad-band green luminescence commonly observed at approximately 2.4eV by radiative transition between shallow donors and acceptors (Vzn) [55,56]. However, recent density functional theory calculations have shown that hydrogen is the likely origin of native donor activity. Because hydrogen (H) is unavoidable in most growth environments, it was concluded that compensating effects due to H act to make ptype doping difficult [57,58].

Although high quality ZnO substrates have better structural, optical, and electrical properties, growth of ZnO single-crystal or polycrystalline thin films allow for variation of the film properties and incorporation of dopants by control of deposition conditions. ZnO thin films have been grown by various growth techniques, such as: sol gel, rf sputtering, metal-organic chemical vapor deposition (MOCVD) [59], molecular beam epitaxy (MBE) [39], and pulsed laser deposition (PLD) [60]. In this thesis, PLD is used for polycrystalline growth of c-axis oriented ZnO thin films on sapphire (c-Al<sub>2</sub>O<sub>3</sub>)

substrates for optically characterized quantum well structures and on thermally oxidized silicon substrates for eventual fabrication of thin film transistors.

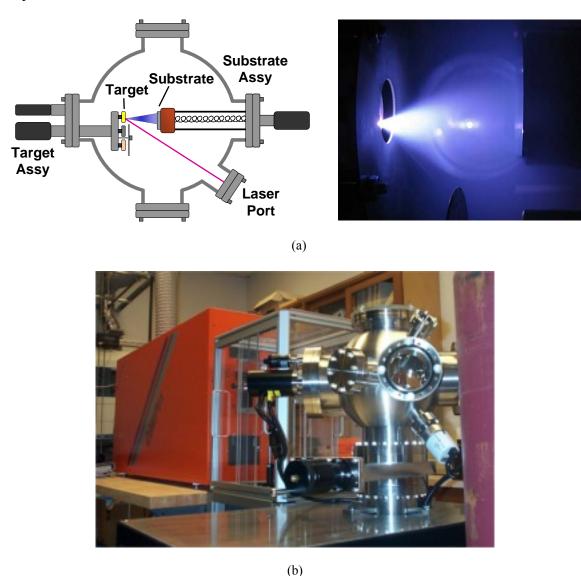

### 2.2 Basic Aspects of Pulsed Laser Deposition

Pulsed-laser deposition (PLD) is defined as the formation of thin films and multilayer structures on a substrate by a plume of evaporated material created when an external pulsed laser source with sufficiently high-energy density ablates a flat target surface. The highly energetic plume of ablated species is forward-directed normal to the target surface and condenses on a substrate located opposite the target. The substrate is bonded to a substrate heater thus allowing good adhesion and making certain epitaxial quality for the deposited material. For deposition of metal oxide epitaxial films such as ZnO, oxygen (O<sub>2</sub>) at high ambient gas pressures in the 10<sup>-4</sup> to 10<sup>-2</sup> Torr range are easily pumped into the chamber using a gas inlet valve and regulated with a mass flow controller thus enabling control of oxygen stoichiometry.

PLD offers the following advantages over competing thin-film growth techniques such as sputtering, molecular beam epitaxy (MBE), or metal-organic chemical vapor deposition (MOCVD): a) simple and versatile experimental setup with economical start-up cost; b) high-quality film growth at moderate substrate temperatures (typically ~600°C) with uniformities better than ± 0.5%; c) fast laser pulses giving rise to high peak energies which is advantageous for oxide thin films with high melting points [61]; and d) easily formed in-situ multilayer structures by target manipulation into and out of the beam of the energy source, laser. A schematic diagram of the PLD chamber illustrating the cone-shaped plume of target material directed at the heated substrate is shown in Fig. 2.2(a). Figure 2.2(b) displays the multilayer PLD system used in this thesis. The entire

system consists of three primary components: laser source, external optics, and deposition chamber.

Figure 2.2 (a) Schematic diagram of a pulsed-laser deposition chamber illustrating expansion of the plume profile and (b) the multilayer PLD system with KrF ( $\lambda$  = 248 nm) laser, focusing optics, and chamber.

Laser wavelengths between 200-nm and 400-nm are required of the external laser source due to the strong absorption exhibited for most materials in this range. As laser emission approaches 200-nm, the absorption coefficient of the target material tends to

increase and the penetration depth into the target are reduced [62]. This results in a thinner layer of the target material surface being ablated and a lower laser fluency threshold for ablation. The excimer laser, a gas laser system, emits its radiation directly in the UV and is generally the laser of choice for PLD work. Of the active excimer molecules used for commercial laser systems, KrF with an operating wavelength of 248-nm has the advantage of being a high gain system which also delivers sufficiently high output pulse energies. The KrF excimer laser with pulse duration of 25nsec used in this work was manufactured by Lambda Physik, Inc.

Between the laser source and the deposition chamber, optical elements are used to collect the radiation from the laser and focus it to a point on the target. Because the laser energy density (in J/cm²) incident on the target is one of the factors which determines crystal quality and preserves composition of the ablated material during growth, significant care is taken to align the cylindrical collimating lenses. Once the laser beam profile on the target is optimized by way of lens ordering, the laser energy is then set for a desired minimum threshold fluence needed to ablate the target material.

After the laser beam passes through the optical elements, it passes through the laser window on the deposition chamber. Thus, the laser window must be periodically cleaned and unobstructed so that the desired laser fluence on the target is realized. The spherical PLD chamber manufactured by Neocera, Inc. contains the ZnO ceramic target 99.999% pure, substrate holder and heater assembly, and variable background gas (i.e. oxygen) which enables control of crystalline stability. The ability to adjust the target-to-substrate distance, S, is desirable in so far as it allows for adjustment of the growth rate. While a smaller S allows for lower laser energy, it also allows for undesired impurities which can

be as much as several microns in size being deposited within the thin film during growth. However, highly dense targets help reduce the generation of those unwanted impurities. Rotating the disk-shaped target attached to a target mount along its rotation axle allows for uniform erosion during deposition. As the evaporated target material condenses on the substrate, thermal distribution across the substrate surface (1-2.5 cm²) becomes significant. Bonding the substrate to the substrate heater with an appropriate adhesive improves temperature uniformity. Silver paint, commonly used during microscopy sample preparation, is used for bonding due to its thermal conductivity, strong mechanical bond, and ease of substrate removal. With a basic foundation of PLD, the influence of growth conditions on structural and electrical properties of ZnO thin films are discussed next.

#### 2.3 Material Characterization

ZnO thin films were grown on single-side polished sapphire (0001) and preoxidized silicon (100) substrates by pulsed laser deposition. The rotating singlecrystalline ZnO target (99.999% pure) was placed at a distance of 4cm from the substrate and ablated using a KrF excimer laser (248nm, 6 Hz, 25 nsec) with a fluence on the target of 1.5 J/cm<sup>2</sup>. The films were grown at an optimized substrate temperature of  $600^{\circ}$ C in ultra-pure oxygen (99.999%) ambient gas pressure of  $p(O_2)=30x10^{-3}$  Torr. Under the above PLD conditions, the resulting deposition rate is on the order of ~3 Å/sec.

The as-grown ZnO films were characterized using various techniques as necessary for optimizing growth conditions and gaining insight on details of material quality. Material surface morphology and crystalline texture are studied by atomic force microscopy (AFM) and x-ray diffraction (XRD), respectively. Film thickness is measured

using optical reflectance, and the band-gap of the ZnO layers is gathered from the peak wavelength of the near-band-edge signal using low-temp photoluminescence (PL). Intrinsic electrical characteristics of the layer are studied by Hall effect measurement. The material characterization techniques used in this study are reported below together with the corresponding results. A detailed discussion on the structure and optical properties of single quantum well structures based on the ZnO/MgZnO material system using transmission electron microscopy (TEM) and PL, respectively, are found in Chapter 5.

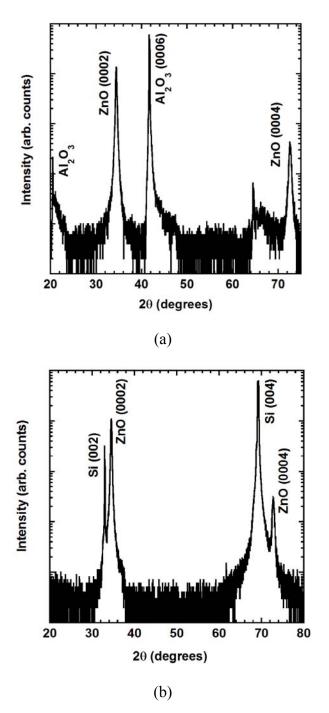

#### 2.3.1 Structural Characterization

The XRD technique is commonly used to determine the crystalline quality and preferential orientation of the ZnO films. All the  $\theta$ -2 $\theta$  XRD results shown in this work were obtained using a Rigaku X-ray diffractometer with Cu  $K\alpha$  radiation ( $\lambda$ =1.5406 Å). Figure 2.3 (a) & (b) show  $\theta$ -2 $\theta$  spectra of polycrystalline thin films having wurtzite-type structure and strong growth orientation along the (000ℓ) on Al<sub>2</sub>O<sub>3</sub> (0001) and SiO<sub>2</sub>/Si (100) substrates, respectively. The 2 $\theta$  diffraction angle occurred at 34.44° for ZnO/Al<sub>2</sub>O<sub>3</sub> and at 34.5° for the ZnO/SiO<sub>2</sub>/Si thin film. Based on the peak position of the (0002) diffraction, the lattice constant c was calculated using Bragg's law to be 5.204 Å for ZnO thin film on the Al<sub>2</sub>O<sub>3</sub> substrate and 5.195 Å for that on the SiO<sub>2</sub>/Si substrate. The full width at half maximum (FWHM) of the (0002) peak was measured to be 0.26° and 0.28° for Fig. 2.3 (a) and Fig. 2.3 (b), respectively. The crystalline grain size is calculated using the Scherrer formula given in Eq. 2.1:

$$D = \frac{0.89\lambda}{B\cos\theta} \tag{2.1}$$

where D is the crystallite grain size,  $\lambda$  the X-ray wavelength,  $\theta$  the Bragg diffraction angle, and B the peak width at half maximum (FWHM). Whereas the grain size for a 300nm thick ZnO film on Al<sub>2</sub>O<sub>3</sub> was 73nm, the grain size for a 90nm thick film on the

Figure 2.3 X-ray diffraction patterns for the ZnO thin films grown on (a)  $Al_2O_3$  (0001) and (b)  $SiO_2/Si$  (100) substrates.

SiO<sub>2</sub>/Si substrate was 68nm. It has been shown that the FWHM of the (0002) diffraction peak from XRD data decreases and the corresponding film grain size increases with an increase in ZnO thickness [63]. In this work the growth of ZnO thin films on amorphous SiO<sub>2</sub>/Si substrates for application in thin-film transistors is expected to result in reduced stress in the film [64].

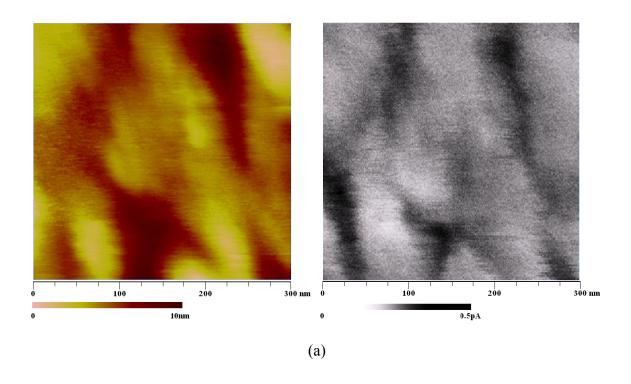

The surface topography of ZnO thin film ( $\sim$  90 nm) by PLD on SiO<sub>2</sub>/Si substrates with a substrate temperature of 600°C were studied by atomic-force microscopy (AFM). An average surface roughness less than 3nm and grain size of approximately 10nm were observed in the as-grown film. Figure 2.4(a) shows the surface image and conduction mapping of the film over a  $2 \times 2 \mu m^2$  area. The average surface roughness of the relatively smooth poly-ZnO film is about 1.5 nm as shown in Fig. 2.4(b). The film surface showed large crystals with good correlation between the topography and electrical mapping at a bias of 5V. This confirms good conduction through the thin film without the formation of 2D island growth.

Figure 2.4 (a) AFM surface image and conduction mapping and (b) surface roughness of poly-ZnO grown on  $SiO_2/Si$  (100) substrates.

## 2.3.2 Optical Characterization

When light with sufficient energy is incident onto a sample, absorbed photons impart excess energy to electrons within the material. This photo excitation causes electrons within the material to move into permissible excited states. These excited electrons eventually relax to their ground state. With radiative and nonradiative relaxation of the electrons, the emission of light called photoluminescence occurs. The most common radiative transition in semiconductors is between states in the conduction and valence bands. Hence, photoluminescence can be used to determine the band-gap. Thus, photoluminescence (PL) is the spontaneous emission of light from a material under optical excitation. PL spectroscopy is a nondestructive technique requiring very little sample manipulation that is used to optically characterize various material parameters. It is a selective and extremely sensitive probe of electronic states of a sample and is usually acquired at a temperature between 8K and 300K. This provides access to the energy level structure of a system. Features of the emission spectrum can be used to gauge surface quality and analysis of structural interfaces. Information gained from the PL peak position can be used to evaluate the band-edge emission, peak linewidth to spatial uniformity of the band-gap throughout the material, and peak intensity gives a measure of the radiative and nonradiative mechanisms present at material surfaces and interfaces.

The photoluminescence characterization in this work was performed using a Kimmon He-Cd ( $\lambda = 325$ nm) continuous wave laser source with a maximum output of 35mW. The spontaneous emission from the sample after being excited with the cw-laser is then collected and focused on a SPEX 500M spectrometer input slit. Inside the spectrometer, photoluminescence with different spectral components is separated at

different angles by an optical grating. Finally, the output slit of the spectrometer is connected to a photo-diode so that the luminescence signal intensities at different wavelengths can be recorded as the optical grating scans through a designated angular range. A lock-in amplifier detects and amplifies the small AC signal from the spectrometer. It then uses a phase sensitive detection technique at a specific reference frequency and phase to reject noise signals other than the reference frequency. A spinning chopper is used to synchronize the light from the continuous laser source with the lock-in amplifier. Background noise associated with the detected signal is therefore attenuated using this standard lock-in technique resulting in an optimized signal-to-noise ratio.

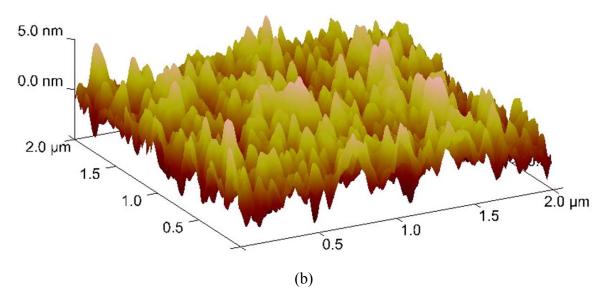

Energy band gap of ZnO (MgZnO will be discussed in Chapter 5) are thus determined by corresponding PL peaks. PL spectrum measured at low temperature for PLD ZnO material grown at 600°C is shown in Figure 2.5. Radiative transitions in semiconductors also involve localized defect levels. Assignment of the emission peak at 3.36 eV is attributed to the neutral donor-bound exciton (D°X). As mentioned previously, D°X energy is 60meV in ZnO thus the actual band-gap is 3.42eV at T=10K. The intensity of the green luminescence (GL) band, centered around 2.3 eV, is used as a measure of the deep-level defects (i.e. V<sub>O</sub> and Zn<sub>i</sub>) commonly associated with bulk and epitaxial ZnO.

Figure 2.5 Photoluminescence spectra measured at low temperature for ZnO material grown at 600°C.

#### 2.3.3 Electrical Characterization

A result of considerable stress due to the lattice mismatch ( $\sim$ 18%) between the deposited ZnO film and the Al<sub>2</sub>O<sub>3</sub> substrate is an array of threading dislocations forming nanocrystalline grains separated by grain boundaries in the thin film. There is a high density of defects associated with the grain boundaries, which along with the point defects ( $V_O$  and  $Zn_i$ ) cause an increase in the n-type background (undoped) concentration of polycrystalline ZnO. The grain boundaries also have a significant influence on electrical conductivity. Electrical conductivity parallel to the grain boundary is higher than the lateral conductivity. In practical application, carrier transport normal to the grain

boundaries is detrimental for high-performance transistors. Hence, post-annealing is used to decrease the dense number of grain boundaries thus improving the crystallinity of the ZnO thin film. Additionally, growth with low  $p(O_2)$  has the largest number of oxygen vacancies, the electron concentration and conductivity is higher than ZnO at higher pressure. The stoichiometry improves with increasing oxygen supply, because the number of oxygen vacancies will decrease. With fewer oxygen vacancies, the resulting ZnO has a lower background concentration and higher resistivity.

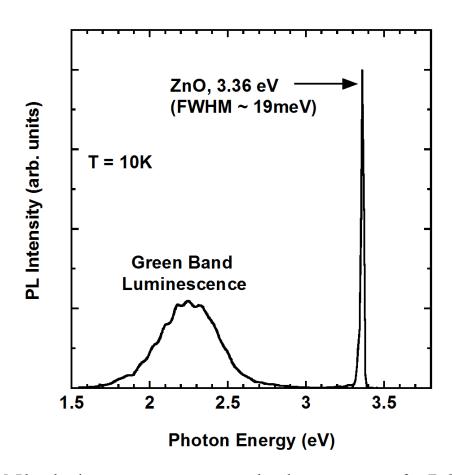

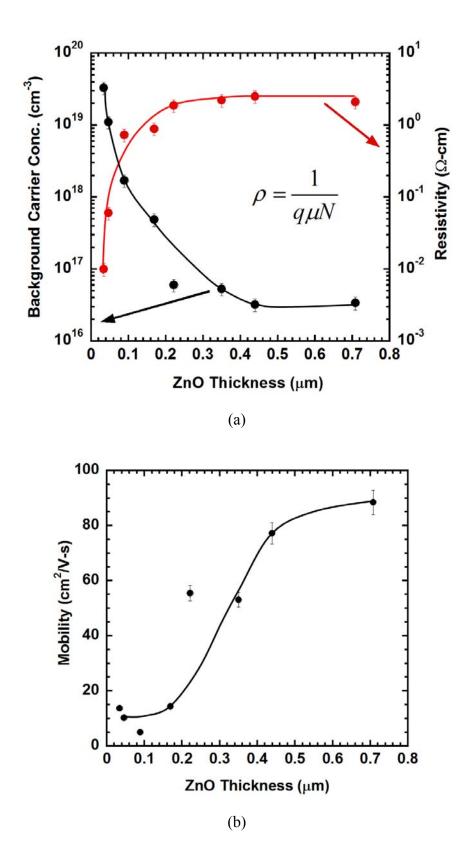

It was found that the electrical properties of ZnO films on c-plane  $Al_2O_3$  were dependent upon its thickness. Hall-effect measurements were used to characterize the films all grown under the same (i.e. temperature, pressure, laser fluence) conditions. The van der Pauw technique was used to determine the background carrier concentration  $(N_B)$ , resistivity  $(\rho)$ , and Hall mobility  $(\mu)$  as a function of the ZnO thickness, as shown in Fig. 2.5 (a) & (b). Relaxation of stress in the ZnO film occurs with thicker films resulting in the increased crystallite grain size and fewer grain boundaries. Less the number of grain boundaries, the electrons experience less scattering and enhanced transport mobility. As will be shown in Chapter 3 and 4, ZnO TFTs are limited to channel thicknesses less than 60nm for current saturation due to channel "pinch-off". This presents a challenge because  $N_B$  increases for thinner films, likewise  $\rho$  decreases.

Figure 2.6 (a) The background concentration and resistivity and (b) carrier mobility of polycrystalline ZnO deposited on c-plane  $Al_2O_3$  as a function of film thickness.

#### 2.4 Conclusion

In conclusion, ZnO thin films can be grown by various physical deposition technologies. PLD offers the advantage of an economical experimental setup for growth of films at moderate substrate temperatures. Careful selection of the laser power density and appropriate beam profile of the excimer laser used to ablate pressed targets, along with manipulation of the PLD growth conditions (i.e. temperature, partial pressure, and gas flow rate), are analyzed to reduce particulate formation and 2D nucleation in favor of promoting unit-cell layer transport in ZnO thin films. A technique is developed for optimized growth of ZnO thin films to serve as active channel layers of a TFT based on these studies. The material study on ZnO material was characterized by XRD, AFM, PL, and Hall measurement. The studies provided valuable information concerning the structural, optical, and electrical properties of ZnO. From the electrical characterization, it was concluded that growth of thin films (30 – 50 nm) with background concentrations less than 10<sup>18</sup> cm<sup>-3</sup> for eventual fabrication of a thin-film transistor would be a challenge.

## **Chapter III**

#### THE N-CHANNEL ZNO THIN FILM TRANSISTOR IN STATIC OPERATION

#### 3.1 Introduction

As discussed in Chapter II, lower carrier concentrations are observed with increasing polycrystalline ZnO film thickness, resulting from the increase in the grain size [65]. However, ZnO TFT channel thicknesses are usually on the order of 40nm to ensure current saturation at low operating bias. This chapter provides qualitative details of the device structure and the basic theory of operation on which the TFT is based. Further, the simulated dependence of ZnO carrier concentration and channel layer thickness on TFT DC characteristics is discussed. Basic steps of TFT fabrication will be given in Chapter IV along with the device experimental DC characteristics.

The structure of TFTs differ from the conventional metal-oxide-semiconductor field-effect transistor (MOSFET) in so far as the typical n-channel MOSFET (NMOS) consist of two n+ regions diffused into a p-type substrate forming the source and drain contacts. Conversely for the n-channel TFT in the bottom-gate configuration, ohmic contacts with low specific contact resistance on the undoped ZnO semiconductor surface form the source and drain electrodes. This simplified structure of the n-channel TFT distinguishes the device from the NMOS and its normal mode of operation.

## 3.2 ZnO TFT Regions of Operation

A cross-sectional view and basic features of the ZnO TFT with an adjoining coordinate system is shown in Fig 3.1. The basic device dimensions are the channel length L in the y-direction, the channel width W in the z-direction, and the ZnO channel depth  $d_{ZnO}$  in the x-direction. TFTs are field-effect transistors which operate as majority carrier devices in the accumulation regime. In the device of Fig. 3.4, positive bias applied to the gate electrode with respect to the grounded source electrode induces an excess (or accumulation) of negative charge in the proximity of the ZnO-SiO<sub>2</sub> interface. These electrostatically induced electrons form a conducting channel and allows current to flow from the drain to the source. It is important to note that the source and drain contacts are ohmic with minimal resistance; furthermore unlike in a MOSFET, no depletion region forms between the source and drain contacts to isolate the conducting channel from the remaining ZnO surface. As a result, switching the TFT from its off-state (no conducting channel) to its on-state (conducting channel) is solely limited by the conductivity of the ZnO thin film. In principle, the absence of a depletion region suggests that the threshold voltage (V<sub>TH</sub>), the minimum gate voltage required to induce a conducting channel, should be zero. However, a measurable V<sub>TH</sub> is observed for TFTs and depends on the quality of the ZnO-SiO<sub>2</sub> interface. Initial electrostatic induction of electrons at low gate bias (subthreshold regime) suffers from surface state trapping at the ZnO-SiO2 interface. This has a detrimental effect on carrier transport along the ZnO channel layer and therefore negligibly small drain-to-source current flow. With further increase in gate voltage, the traps are eventually filled resulting in the formation of a conducting channel. The gate voltage at the onset of the conducting channel is defined as the turn-on voltage, V<sub>on</sub>.

Figure 3.1 Cross-section of a typical ZnO bottom-gate TFT device.

Beyond this point, the channel becomes increasingly conducting in keeping with accumulative electron charge having increased carrier mobility. This carrier mobility dependence on gate bias will be discussed further in Chapter 4.

# 3.2.1 Depletion of Charge

When a negative bias is applied to the gate electrode, carriers in the n-type semiconductor are withdrawn and a depletion region forms at the gate-insulator surface. The extent of the depletion region is related to increasing negative gate bias. Thus, the depletion region widens as more electrons are withdrawn. The TFT is said to be in its *off*-state (no conducting channel). Fig 3.2 shows the schematic of a ZnO TFT operated in depletion. For wide band gap materials with overwhelming inherent n-type conduction such as ZnO, the bands are bent upward however the valence band is not closer to the Fermi level than the conduction band.

Figure 3.2 Schematic of ZnO TFT operation in depletion.

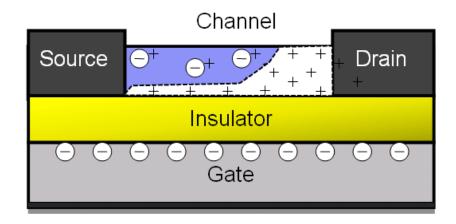

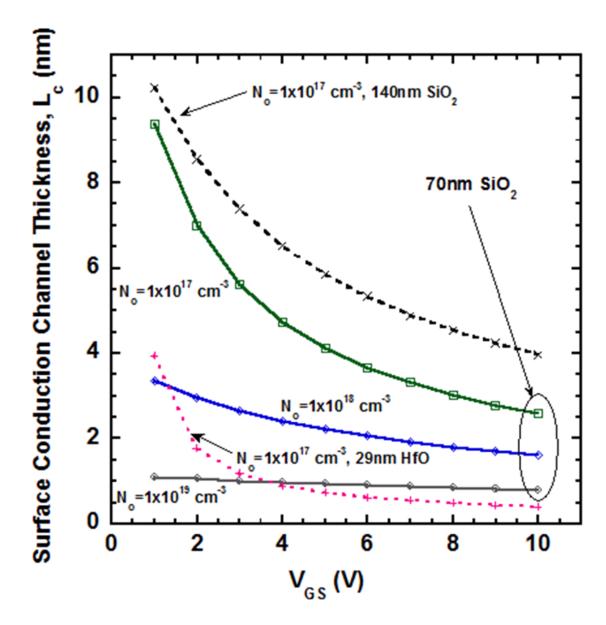

## 3.2.2 Accumulation of Charge

With a small positive drain bias, a negligibly small drain current will flow due to leakage currents and the conductivity of the thin film. Increasing the gate bias above zero  $(V_{GS} > V_{DS} > 0)$  results in the accumulation of charge at the ZnO-SiO<sub>2</sub> interface. The charge adjacent to the interface surface is now larger than that uniformly distributed throughout the remaining semiconductor volume and the thickness of this resulting surface accumulation layer is given by [66]

$$L_C = \frac{V_S}{E_S} \tag{3.1}$$

where  $V_S$  is the semiconductor surface potential and  $E_S$  the surface field. Fig. 3.3 shows the surface accumulation layer thickness as a function of  $V_{GS}$  for a ZnO TFT while varying carrier concentration in the semiconductor and use of different gate dielectric (SiO<sub>2</sub>) thickness. The thickness of this layer is small on the order of 40Å and decreases with an increase of the electric field at the surface.

Figure 3.3 Surface accumulation layer thickness as a function of  $V_{GS}$  for a ZnO TFT with varying carrier concentration in the semiconductor, different gate dielectric (SiO<sub>2</sub>) thickness, and a HfO gate dielectric.

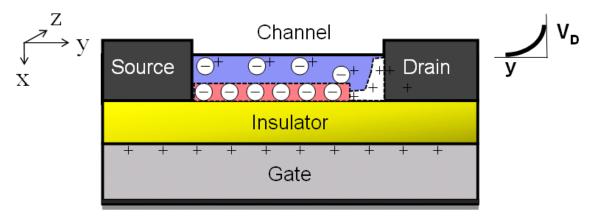

A schematic of the ZnO TFT illustrating the accumulation of negative charge in the vicinity of the ZnO-SiO<sub>2</sub> interface is shown in Fig. 3.4. Hence, the device operates in the linear region and behaves like a voltage- controlled resistor with a small drain current. At some point along the channel where the drain bias equals the gate bias ( $V_{DS}=V_{GS}$ ), a depletion zone (i.e. absent of free charge) begins to develop near the drain contact. Once the drain bias is increased above the gate bias ( $V_{DS} > V_{GS} > 0$ ), the depletion zone width increases thus effectively reducing  $d_{ZnO}$ . The depletion zone eventually extends across the entire thickness of the ZnO layer near the drain contact resulting in the onset of pinch-off,

Figure 3.4 Schematic of a ZnO thin-film transistor illustrating the development of a depletion zone near the drain contact. For  $V_{DS} > V_{GS}$ , pinch-off of the entire channel thickness occurs near the drain.

and the drain current saturates. The depletion zone width,  $W_{depl}(y)$ , at a distance y from the source is given by [67]

$$W_{depl}(y) = \frac{\varepsilon_{ZnO}}{C_{ins}} \left[ \sqrt{1 + \frac{2C_{ins}^2 \left[ V(y) - V_{GS} \right]}{q N_B \varepsilon_{ZnO}}} - 1 \right]$$

(3.2)

where  $\varepsilon_{ZnO}$  is the ZnO dielectric constant,  $C_{ins}$  is the capacitance of the gate dielectric, and V(y) is the drain voltage variation as a function of distance y along the semiconducting channel. Therefore, current saturation is determined by device geometry and material

properties. Fig. 3.5 gives the ZnO TFT maximum depletion zone width as a function of  $V_{DS}$  and  $V_{GS}$ . The figure suggests pinch-off for the entire thickness of the ZnO layer at a  $V_{GS}$ =10V and  $V_{DS}$ =15V for a ZnO TFT device with <40nm channel thickness ( $N_B$ =5x10<sup>17</sup> cm<sup>-3</sup>).

Figure 3.5 Depletion region width allowing TFT channel pinch-off as a function of  $V_{DS}$  and  $V_{GS}$  for a background concentration of  $N_B$ =5x10<sup>17</sup>cm<sup>-3</sup>.

Calculation of the device current-voltage characteristic consists of considering a differential drain voltage for an elemental section *dy* of the conducting channel, given by [68]

$$dV = \frac{I_D dy}{\mu W |Q_{acc}(y) + Q_{bulk}|}$$

(3.3)

where  $\mu$  represents constant carrier mobility,  $Q_{acc}(y)$  is the total accumulated charge per unit area induced at a position y along the channel, and  $Q_{bulk}$  is the bulk charge for n-type ZnO at equilibrium. Consistent with field-effect transistor operation, the drain voltage  $V_{DS}$  drop is a function of its position along the channel from (y = 0, V(y) = 0) at the source to  $(y = L, V(y) = V_{DS})$  at the drain contact. At low drain bias,  $Q_{acc}$  is uniformly distributed over the entire channel and  $Q_{bulk}$  is a constant given by

$$Q_{bulk} = -qN_B d_{ZnO} (3.4)$$

where q is the elemental charge with the sign of the majority carrier,  $N_B$  is the background concentration of ZnO, and  $d_{ZnO}$  is the thickness of the ZnO film. The total charge induced in the ZnO thin film forming the accumulation layer is given by

$$Q_{acc} = -C_{ins} |V_{GS} - V_{fb} - V(y)|$$

(3.5)

where  $V_{GS}$  is the gate-to-source voltage,  $V_{fb}$  is the flat-band voltage which accounts for the work-function difference between the ZnO material and the gate electrode, and V(y)is the drain voltage drop along the channel. Under ideal conditions,  $V_{fb}$  is considered to be negligible. Substituting Eq. (3.4) and (3.5) into Eq. (3.3) yield

$$I_D \int_0^L dy = \mu W \int_0^{V_D} \left[ C_{ins} \left( V_{GS} - V(y) \right) + q N_B d_{ZnO} \right] dV.$$

(3.6)

The drain current as a function of the drain voltage at any point along the channel can now be obtained from Eq. (3.6). Drain current-voltage characteristics are derived for the linear and saturation regions of operation, as will be discussed in Chapter 4. It is worth noting that the expression for  $Q_{bulk}$  in Eq. (3.4) is no longer a constant value and now becomes

$$Q'_{bulk} = -qN_B (d_{ZnO} - W_{devl}(y)). (3.7)$$

The depletion zone which forms near the drain contact will eventually cover the entire ZnO layer thickness near the drain contact; thus, the *pinched off* channel is now free of accumulated charge and the drain current saturates.

### 3.3 Two-Dimensional ZnO TFT Device Simulation