# The Electrical Characteristics and Device Applications of Metal Oxide Nanowires

by

### Eric Neil Dattoli

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

# **Doctoral Committee:**

Assistant Professor Wei Lu, Chair Professor Xiaoqing Pan Assistant Professor Zhaohui Zhong Assistant Research Scientist Becky Lorenz Peterson

# **Table of Contents**

| List of Figuresiv |         |                                                                                                                                    |    |  |  |  |  |  |  |

|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| Lis               | t of Ta | ıbles                                                                                                                              | vi |  |  |  |  |  |  |

| Glossary          |         |                                                                                                                                    |    |  |  |  |  |  |  |

|                   |         |                                                                                                                                    |    |  |  |  |  |  |  |

| 1                 | Intr    | oduction                                                                                                                           | 1  |  |  |  |  |  |  |

| 2                 | Nan     | owire Growth                                                                                                                       | 3  |  |  |  |  |  |  |

|                   | 2.1     | Overview                                                                                                                           | 3  |  |  |  |  |  |  |

|                   | 2.2     | Important Aspects related to VLS Nanowire Growth                                                                                   |    |  |  |  |  |  |  |

|                   |         | 2.2.1 Nanoparticle Catalysts                                                                                                       |    |  |  |  |  |  |  |

|                   |         | 2.2.2 Nanoscale Eutectic Temperature                                                                                               |    |  |  |  |  |  |  |

|                   |         | 2.2.3 Nucleation of Nanoparticles                                                                                                  | 12 |  |  |  |  |  |  |

|                   |         | 2.2.4 Nanowire Sidewall Deposition                                                                                                 |    |  |  |  |  |  |  |

|                   |         | 2.2.5 Nanowire Growth Rates                                                                                                        |    |  |  |  |  |  |  |

|                   |         | 2.2.6 Nanowire Heterostructures                                                                                                    |    |  |  |  |  |  |  |

|                   | 2.3     | Nanowire Growth Setups                                                                                                             |    |  |  |  |  |  |  |

|                   |         | 2.3.1 CVD Nanowire Growth                                                                                                          |    |  |  |  |  |  |  |

|                   |         | 2.3.2 Vapor-Transport Metal Oxide Nanowire Growth                                                                                  |    |  |  |  |  |  |  |

|                   | 2.4     | Metal Oxide Nanowire Vapor-Phase Growth                                                                                            |    |  |  |  |  |  |  |

|                   |         | 2.4.1 VLS Growth of Metal Oxide Nanowires                                                                                          |    |  |  |  |  |  |  |

|                   |         | 2.4.2 VSS Growth of Metal Oxide Nanowires                                                                                          |    |  |  |  |  |  |  |

|                   |         | <ul><li>2.4.3 Self-Catalytic Growth of Metal Oxide Nanowires.</li><li>2.4.4 Vapor-Solid Growth of Metal Oxide Nanowires.</li></ul> |    |  |  |  |  |  |  |

|                   |         | 2.4.5 Experimental Results for Vapor-Transport Growth of SnO <sub>2</sub> Nanowires                                                |    |  |  |  |  |  |  |

|                   | 2.5     | Summary                                                                                                                            |    |  |  |  |  |  |  |

| 3                 | Nan     | owire-based Transistors Overview                                                                                                   | 36 |  |  |  |  |  |  |

|                   | 3.1     | Nanowire-based FET Overview                                                                                                        | 36 |  |  |  |  |  |  |

|                   | 0.1     | 3.1.1 JFET approach to analysis of NW-FET Operation                                                                                |    |  |  |  |  |  |  |

|                   |         | 3.1.2 MOSFET approach to analysis of NW-FET Operation                                                                              |    |  |  |  |  |  |  |

|                   | 3.2     | Schottky Contacts                                                                                                                  |    |  |  |  |  |  |  |

|                   | -       | 3.2.1 Overview                                                                                                                     |    |  |  |  |  |  |  |

|                   |         | 3.2.2 Effect on Nanowire-based FETs                                                                                                |    |  |  |  |  |  |  |

|                   | 3.3     | Transistor Analysis                                                                                                                |    |  |  |  |  |  |  |

|     |             | 3.3.1 NW-FET Gate Capacitance Estimation                      | 53       |

|-----|-------------|---------------------------------------------------------------|----------|

|     |             | 3.3.2 FET Parameter Extraction                                |          |

|     |             | 3.3.3 RF Characterization                                     |          |

|     | 3.4         | Summary                                                       | 62       |

| 4   | Nan         | owire Transfer                                                | 63       |

|     | 4.1         | Transfer Overview                                             | 63       |

|     | 4.2         | Contact Printing Optimization                                 | 67       |

|     | 4.3         | Gate Capacitance Considerations for Nanowire Arrays           | 70       |

|     | 4.4         | Summary                                                       | 74       |

| 5   | Sing        | gle Nanowire Device Characterization                          | 75       |

|     | 5.1         | SnO <sub>2</sub> Nanowire FET Devices                         |          |

|     |             | 5.1.1 Defect-induced Carriers in Metal Oxide Semiconductors   |          |

|     |             | 5.1.2 Experimental Method and Results                         |          |

|     | 5.2         | Degenerately Doped Metal Oxide Nanowires                      |          |

|     |             | 5.2.1 Sb-doped SnO <sub>2</sub> Nanowires                     |          |

|     |             | 5.2.2 Sn-doped In <sub>2</sub> O <sub>3</sub> (ITO) Nanowires |          |

|     | 5.3         | Summary                                                       | 90       |

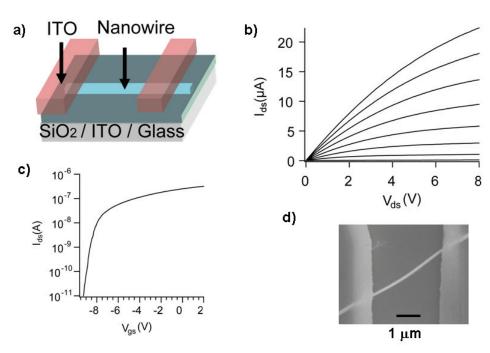

| 6   |             | nsparent n-type, SnO <sub>2</sub> NW-TFTs                     |          |

|     | 6.1         | Overview                                                      |          |

|     | 6.2         | Electrical characterization: DC and RF                        |          |

|     | 6.3         | NW-TFT Optimization and Circuit Applications                  | 98       |

|     | 6.4         | Summary                                                       | 108      |

| 7   | p-ty        | pe, Ge-based NW-TFTs                                          | 110      |

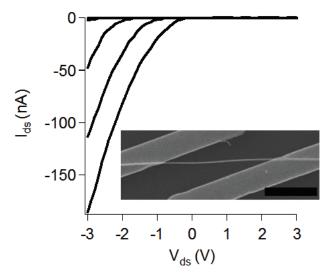

|     | 7.1         | Ge/Si Core-Shell TFTs                                         | 110      |

|     | 7.2         | B-doped Ge NW-TFTs                                            | 115      |

|     | 7.3         | Summary                                                       | 116      |

| 8   | Conclusion1 |                                                               | 118      |

|     | 8.1         | Comparison of NW-TFT to other materials for flexible and tra  | nsparent |

|     | elect       | tronics                                                       | 119      |

|     | 8.2         | Future Work                                                   | 123      |

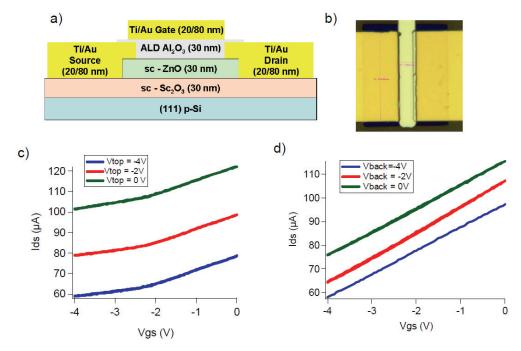

| Ap  | pendix      | x A: Single-crystalline ZnO TFT                               | 125      |

| Rik | nlingra     | nhy                                                           | 134      |

# **List of Figures**

| Fig. 2.1. Schematic of the VLS process                                                   | 4  |

|------------------------------------------------------------------------------------------|----|

| Fig. 2.2 Before and After Silicon Nanowire Growth                                        | 5  |

| Fig. 2.3 Annealed 2 nm thick Au thin film                                                | 10 |

| Fig. 2.4 Theoretical Calculations of the Nanoscale Eutectic temperature for the Au-Ge    |    |

| system                                                                                   | 11 |

| Fig. 2.5 Nucleation (or lack thereof) of nanoparticle catalysts                          | 12 |

| Fig. 2.6 A tapered nanowire.                                                             | 13 |

| Fig. 2.7 Ge Nanowire Growth Scheme                                                       | 14 |

| Fig. 2.8 The Stoppage and Resumption of Nanowire Growth                                  | 15 |

| Fig. 2.9 Nanowire Heterostructure Configurations                                         | 17 |

| Fig. 2.10 CVD Setup for Ge Nanowire Growth                                               | 18 |

| Fig. 2.11 Vapor-Transport Apparatus for Nanowire Growth                                  |    |

| Fig. 2.12 Model for Metal Oxide Nanowire VLS growth                                      | 22 |

| Fig. 2.13 Model for Self-Catalytic VLS growth of a SnO <sub>x</sub> Nanobelt             | 24 |

| Fig. 2.14 Schematic for VLS grown SnO <sub>2</sub> NWs                                   | 28 |

| Fig. 2.15 SEM Images of Diameter-Controlled VLS Grown SnO <sub>2</sub> NWs               | 29 |

| Fig. 2.16 Schematic for self-catalytic VLS grown SnO <sub>2</sub> NWs                    | 32 |

| Fig. 2.17 SEM Images of Self-Catalytic VLS grown SnO <sub>2</sub> Nanowires              | 33 |

| Fig. 2.18 Histogram of Self-Catalytic Grown SnO <sub>2</sub> Nanowire Diameters          | 34 |

| Fig. 3.1 Field-Effect Operation of a NW-FET                                              |    |

| Fig. 3.2 Diagram of a Bottom-Gated Nanowire-based FET using JFET assumptions             |    |

| Fig. 3.3 NW-FET in Depletion and Accumulation                                            |    |

| Fig. 3.4 Diagram of a Bottom-Gated Nanowire-based FET using MOSFET assumptions           | 44 |

| Fig. 3.5 Equilibrium diagram of Schottky M-S junction                                    |    |

| Fig. 3.6 Effect of Bias on Schottky Junction                                             | 49 |

| Fig. 3.7 Ohmic M-S Junction.                                                             |    |

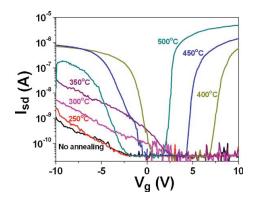

| Fig. 3.8 Annealing Effect on NW-FET Performance                                          | 52 |

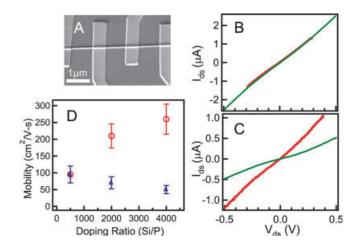

| Fig. 3.9 Effect of Doping Level on SiNW FET Contacts                                     |    |

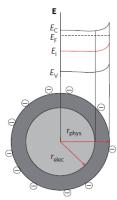

| Fig. 3.10 Schematic of Dopant Depletion at Nanowire Surfaces                             |    |

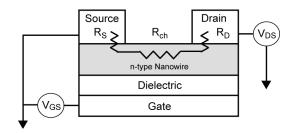

| Fig. 3.11 NW-FET Model with Contact Resistances Included                                 |    |

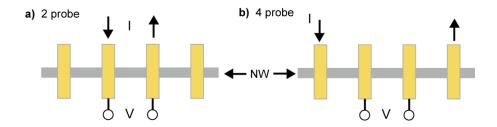

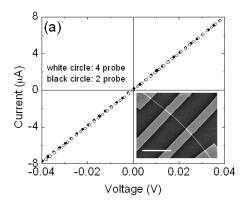

| Fig. 3.12 Four-Probe Test Structure                                                      |    |

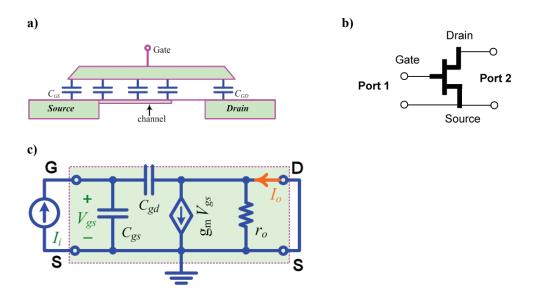

| Fig. 3.13 AC Models of a FET                                                             |    |

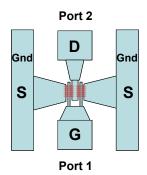

| Fig. 3.14 Ground-Signal-Ground NW Device Structure                                       |    |

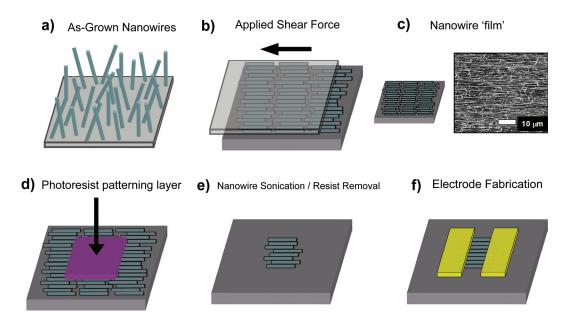

| Fig. 4.1 Nanowire Contact Printing and TFT fabrication                                   |    |

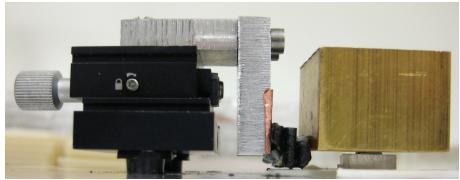

| Fig. 4.2 Experimental Contact Printing Setup                                             |    |

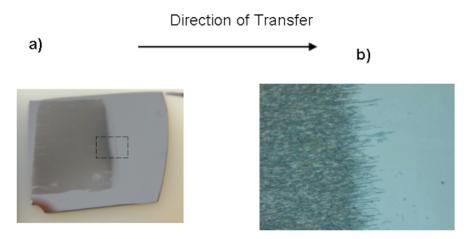

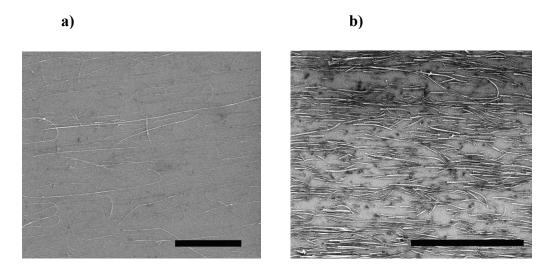

| Fig. 4.3 Images of Transferred Nanowires                                                 |    |

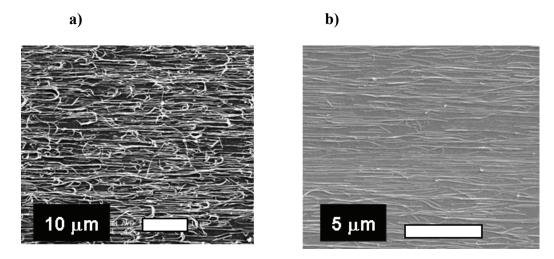

| Fig. 4.4 Effect of Pressure on Contact Printing                                          |    |

| Fig. 4.5 Optimal Contact Printing Conditions for Nanowire Transfer                       |    |

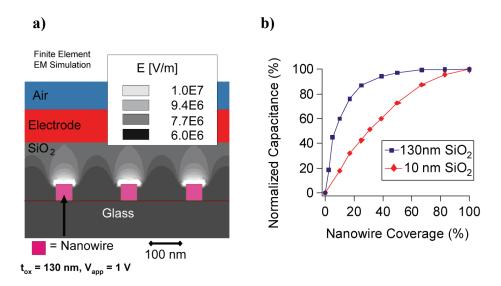

| Fig. 4.6 EM Simulations of a NW-TFT                                                      |    |

| Fig. 4.7 E-M Simulations of a Low-Density NW-TFT                                         |    |

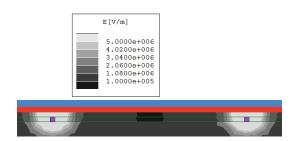

| Fig. 5.1 Images of as-grown SnO <sub>2</sub> nanowires                                   | 80 |

| Fig. 5.2 Transfer characteristics of a back-gated Ta-doped SnO <sub>2</sub> nanowire FET | 81 |

| Fig. | 5.3 | Extraction of Average Mobility                                                           | 82  |

|------|-----|------------------------------------------------------------------------------------------|-----|

| Fig. | 5.4 | Electrical characterization of a typical undoped SnO <sub>2</sub> nanowire device in air | 82  |

| Fig. | 5.5 | Back-gated Ta-doped SnO <sub>2</sub> nanowire FET fabricated on glass with ITO contacts  | 85  |

| Fig. | 5.6 | Degenerately Doped TAO NWs                                                               | 88  |

| Fig. | 5.7 | Electrical Characteristics Degenerately Doped TAO NWs                                    | 88  |

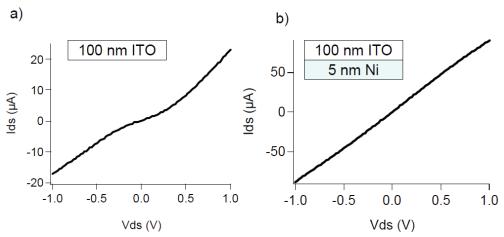

| Fig. | 5.8 | ITO Nanowires                                                                            | 90  |

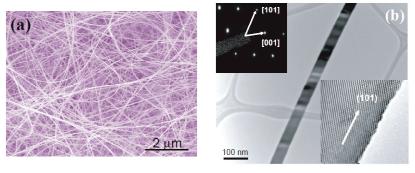

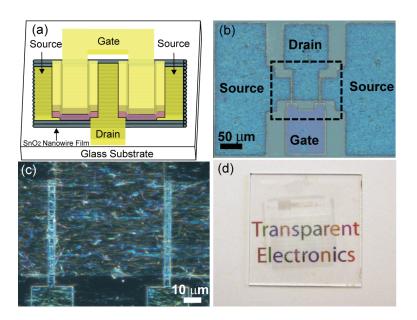

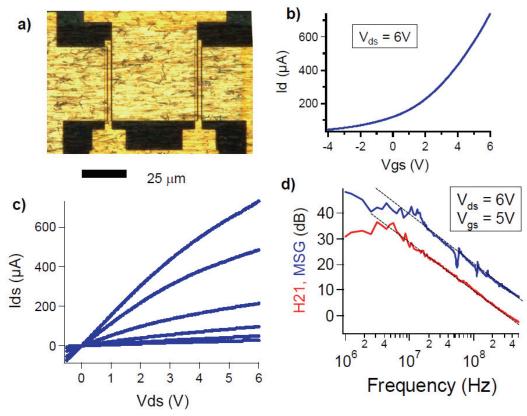

| Fig. | 6.1 | Overview of NW-TFT                                                                       | 92  |

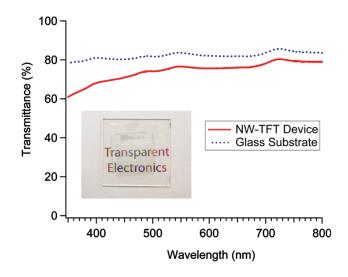

| Fig. | 6.2 | Transmittance Measurements of the NW-TFTs                                                | 93  |

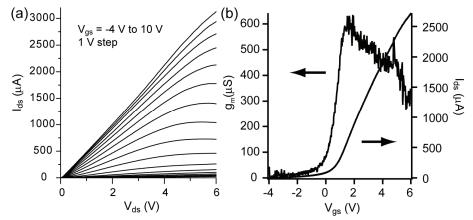

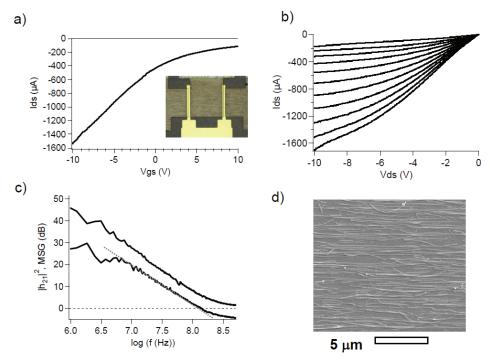

| Fig. | 6.3 | DC Characteristics of a Transparent SnO <sub>2</sub> NW-TFT                              | 95  |

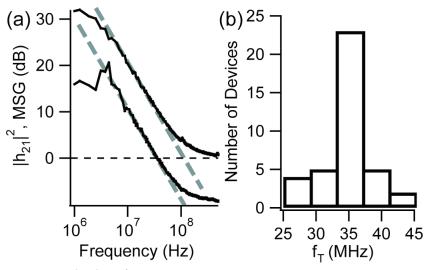

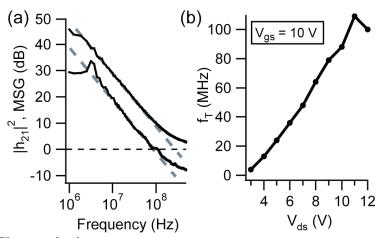

| Fig. | 6.4 | RF characterization of transparent NW-TFTs.                                              | 96  |

| Fig. | 6.5 | RF Characterization, cont.                                                               | 97  |

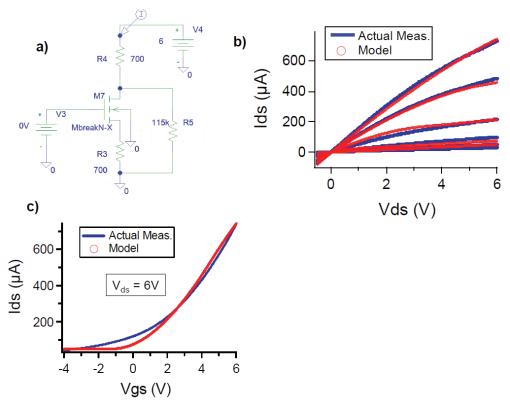

| Fig. | 6.6 | SnO <sub>2</sub> NW-TFT With Optimized PECVD Dielectrics                                 | 02  |

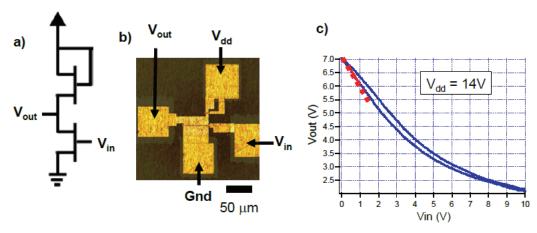

| Fig. | 6.7 | N-type SnO <sub>2</sub> NW-TFT Inverter1                                                 | 03  |

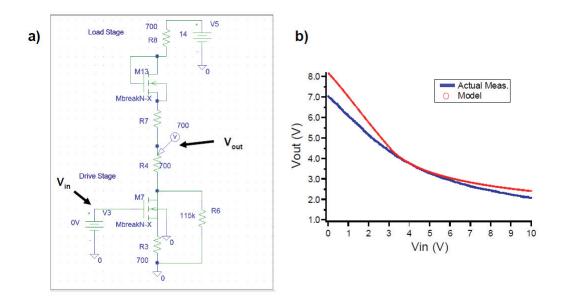

| Fig. | 6.8 | Spice Simulation of SnO <sub>2</sub> NW-TFT                                              | 107 |

| Fig. | 6.9 | Spice Simulation of SnO <sub>2</sub> NW-TFT Inverter                                     | 08  |

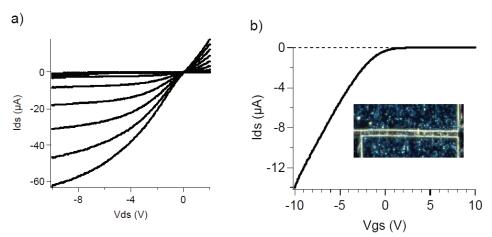

| Fig. | 7.1 | Ge/Si Core-shell NW-TFT                                                                  | 112 |

| Fig. | 7.2 | Transparent Contacts to Ge/Si NWs                                                        | 114 |

| Fig. | 7.3 | Ge NW-TFT testing                                                                        | 116 |

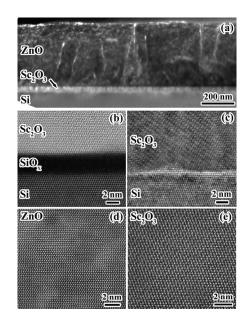

| Fig. | A.1 | TEM image of ZnO film stack                                                              | 26  |

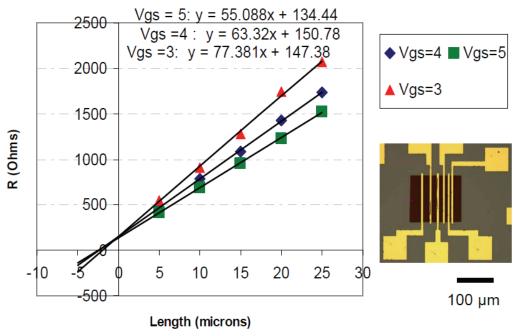

| Fig. | A.2 | TLM measurements of ZnO film                                                             | 127 |

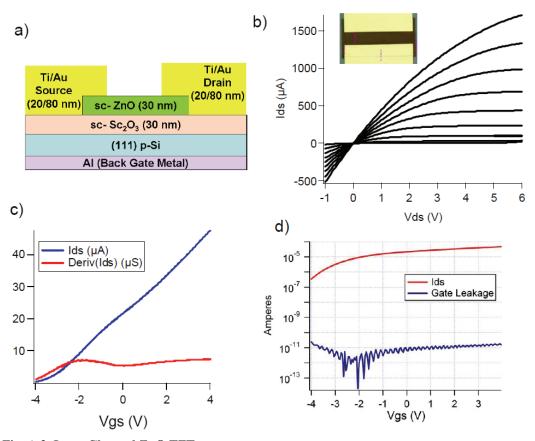

| Fig. | A.3 | Long-Channel ZnO TFT                                                                     | 129 |

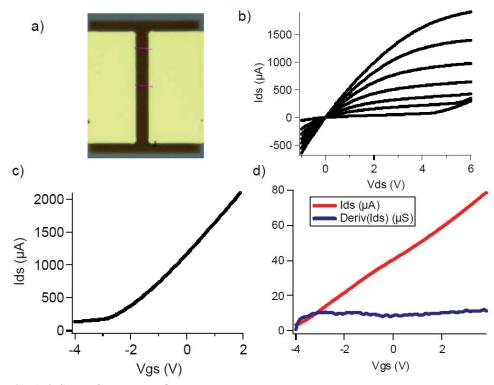

|      |     | Short Channel ZnO TFT                                                                    |     |

| Fig. | A.5 | Top-gated ZnO TFT                                                                        | 132 |

|      |     |                                                                                          |     |

# **List of Tables**

| Table 4.1 | Optimal Contact Printing Conditions | 69 |

|-----------|-------------------------------------|----|

|           | SPICE Model for NMOS Component      |    |

|           | ZnO TLM Measurement Results         |    |

# Glossary

$\mu$  mobility (cm<sup>2</sup>/V•s)

C<sub>gd</sub> capacitance between gate and drain (F/cm)

$C_{gs}$  the coupling capacitance between the gate electrode and the FET

or TFT channel (F/cm<sup>2</sup>)

C<sub>gs</sub> capacitance between gate and source (F/cm)

C<sub>i</sub> the coupling capacitance between the gate electrode and the

NW-FET channel (F/cm)

E<sub>c</sub>, E<sub>v</sub> conduction band, valence band edge (eV)

E<sub>F</sub> equilibrium Fermi level (eV)

E<sub>i</sub> intrinsic level (eV)

f<sub>max</sub> power gain cutoff frequency (Hz)

f<sub>T</sub> unity current gain cutoff frequency (Hz)

g<sub>m</sub> transconductance (S)

I current (A)

I<sub>DS</sub> channel current in a FET, from drain to source (A)

J current density (A/cm<sup>2</sup>)

L length of a transistor, distance between the source and drain

contacts (cm)

MSG Maximum Stable Gain

$Q_{ch}(x)$  amount (magnitude) of charge at a certain location, x, of the NW

channel (C)

S subthreshold slope (mV/decade)

V<sub>a</sub> applied voltage (V)

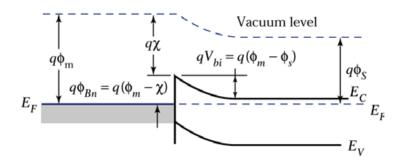

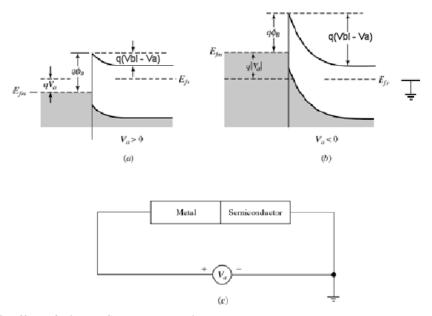

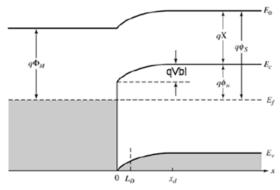

$V_{bi}$  built-in contact potential,  $\phi_m - \phi_s(V)$

$V_{ch}(x)$  is the voltage value that the channel possesses at a location (V)

V<sub>DS</sub> drain voltage with respect to source (V)

$V_{GS}$  gate voltage with respect to source (V)

V<sub>T</sub> FET threshold voltage (V)

$\epsilon, \epsilon_r, \epsilon_0$  permittivity, relative dielectric constant, permittivity of free

space;  $\varepsilon = \varepsilon_r \cdot \varepsilon_0 (F/cm)$

φ work function potential (V)

φ<sub>B</sub> Metal-semiconductor barrier height (V)

$\phi_{m}$  metal work function (V)

$\phi_s$  semiconductor work function (V)

$\phi_{S}$  surface potential (V)

$\chi$  electron affinity (V)

#### **Abstract**

Metal oxide and semiconductor nanowires have shown great potential as the basis for electronic devices which are compatible with a wide range of device substrates, including transparent or flexible substrates. The development of such nanowire-based devices, however, currently presents several outstanding challenges. Besides the various issues related to the growth of nanowires, the commercial applications of these materials depend critically on the development of scalable methods for achieving nanowire assembly and integration. In order to address such manufacturability issues, a thin-film transistor (TFT) based upon metal oxide nanowires is characterized in order to show that it is possible to fabricate nanowire devices which offer both high-performance levels and compatibility with transparent and flexible device substrates.

Instead of directly depositing semiconductor materials on glass or plastic as with typical TFT designs, in this work the low-temperature requirements of glass and plastic substrates are satisfied by employing a contact printing process to transfer synthesized nanowires from their growth substrate directly onto the device substrate. This method was shown to effectively achieve the isolation of the high-temperature processes required by single-crystalline material growth from the low-temperature conditions mandated by the device substrate.

Semiconductor nanowires, such as metal oxide SnO<sub>2</sub> or Ge-based nanowires, were

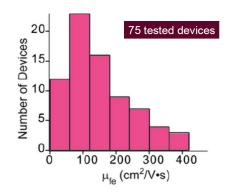

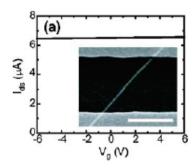

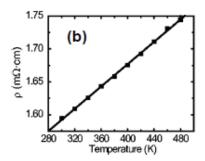

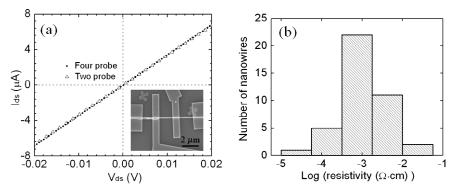

employed as the TFT channel material. Optimization of the growth process of these nanowires is discussed. For instance, the diameter controlled growth of 30 nm diameter SnO<sub>2</sub> nanowires is examined. Electrical characterization results of such SnO<sub>2</sub> nanowires showed that they possess field-effect mobilities that averaged 156 cm<sup>2</sup>/V•s. Moreover, by properly controlling the amount of extrinsic dopants during the nanowire growth, the conductivity of the nanowires may be adjusted from semiconducting to metallic.

Although the DC performance of nanowire-based transistors has been extensively examined; in circuit applications, the high frequency characteristics of the nanowire-based transistors are more relevant. In order to demonstrate their suitability for high frequency circuit applications, direct RF measurements are carried out on nanowire-based TFTs fabricated on glass. Operational speeds in excess of 300 MHz were reached. Additionally, the suitability of these TFTs in logic circuits is demonstrated with the fabrication and successful operation of a two-transistor inverter.

# Chapter 1

#### Introduction

The nascent field of nanowire (NW) research has made a great deal of progress in broadening the field of knowledge related to nanowire growth mechanisms and their associated electrical properties. So far, the main focus of this research has been on single nanowire device structures [1]. Although these simple structures are useful for probing the intrinsic physical properties of NWs, they are not applicable to commercial or real-world applications. A practical NW-based electronic device must be able to be fabricated in sizable quantities and in an affordable fashion while maintaining a good uniformity in performance among different devices. The purpose of this thesis work is to demonstrate nanowire growth and fabrication methods which could help make NW-based electronic devices a practical reality.

The bright prospects related to NW-based electronics can be attributed to the unique physical properties of nanowires. As a result of their growth mechanism, nanowires may be synthesized in an independent step and later be transferred (post-growth) to device substrates of interests. Moreover, the nanowires to be discussed also possess a single-crystalline structure which allows for higher speed electronic carrier transport as compared to poly-crystalline or amorphous materials.

The device structure to be presented that can take advantage of these properties in a practical manner is the nanowire-based thin-film transistor (NW-TFT). The main

novelty of a NW-TFT as compared to other electronic devices is that the switching element, i.e. semiconductor channel material, is made up of an array of a large number of aligned nanowires. Such NW arrays may be transferred onto a wide variety of substrates, like glass, in a controlled fashion by a contact printing method. Following the nanowire transfer to the substrate of interest, device fabrication can be carried out using established semiconductor processing methods. The fabrication of NW-TFTs on transparent substrates like glass opens up the possibility of achieving transparent electronic devices. The operation of a transparent NW-TFT and a two-transistor inverter will be examined.

For practical circuit applications, both p- and n-type transistors are required. To this end, p- and n-type NW-TFTs were fabricated separately in this work and both their DC and RF electrical properties will be detailed. The semiconductor SnO<sub>2</sub> was utilized as the n-type material, while Ge-based nanowires were explored as the p-type material. A future goal will be to fabricate both structures on the same chip with the aim of creating low-power, complementary logic circuits.

Lastly, the electrical characterization of a single-crystalline ZnO TFT on a Si substrate will be examined in Appendix A. Although not a nanowire-based device, the ZnO TFT shares many structural similarities with NW-TFTs, and serves as a useful performance comparison. Thanks to its epitaxial deposition on Si, the structure of the examined ZnO TFT could one day be useful in integrating ZnO devices alongside Si-based devices.

# Chapter 2

#### Nanowire Growth

#### 2.1 Overview

The bottom-up growth of nanowires may be achieved by a variety of methods [1-3], such as solution-phase or template-directed deposition. This work will, however, exclusively focus on the vapor-based growth of nanowires and specifically via the vapor-liquid-solid (VLS) process. The VLS process was first demonstrated in the 1960s by Wagner with the growth of silicon whiskers (wire-like structures 100s of nm to microns in diameter) [4]. The name for the VLS process was coined to describe the step-by-step phase changes of the reactant molecules as they proceed through the entire crystal growth process. It is important to note that the VLS growth process possesses many different characteristics as compared to plasma or thermal chemical vapor deposition (CVD) processes. Whereas traditional CVD relies upon the thermal (or plasma) activated decomposition of gaseous reactants, the VLS process utilizes a metal catalyst to facilitate the deposition of the gaseous reactants. Typically, VLS depositions may occur at lower temperatures and produce products with a greater crystalline quality than low-temperature thermal or plasma-CVD processes.

The role of the metal catalyst will first be examined. Two requirements for this metal catalyst are: a) that the metal be able to alloy with the desired reactant element, and b) that the metal catalyst forms an eutectic alloy with the reactant element. An eutectic

alloy is defined as an alloy such that at some alloy composition ratio, the melting point of the alloy is less than both of the individual pure elements [5]. Not necessarily all alloys are eutectic.

As a generality in VLS growth, the diameter of the metal catalyst particle roughly determines the diameter of the grown nanowire. For example, if large catalyst particles are used (i.e. micron sized metal particles), then large, micron-sized whisker structures will be obtained from VLS growth, as was first established by Wagner in the 1960s [4]. Metal nanoparticles may be deposited directly onto a growth substrate. The diameter and density of the deposited nanoparticles directly influences these same properties of the grown nanowire forests. If growth in only certain areas is desired, the nanoparticles may be patterned via means such as photolithography [6].

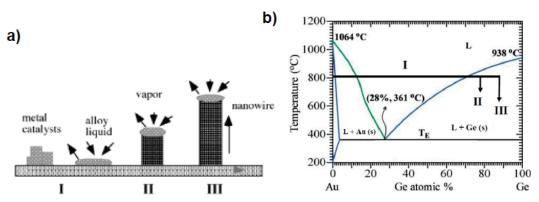

Fig. 2.1. Schematic of the VLS process

a) Diagram of the VLS Process. The steps to this process are: alloy droplet formation (I), nanowire nucleation (II), nanowire axial growth (III). Adapted with permission from [7]. Copyright 2001 American Chemical Society. b) Binary Phase Diagram of the Au/Ge alloy. The green line is the Au liquidus line, and the blue line is the Ge liquidus line. The eutectic point of the system is marked by an arrow. The solidus line (horizontal) is in black at the eutectic temperature. Adapted from [8]. Reprinted with permission from AAAS.

The VLS process will now be examined sequentially according to Fig. 2.1 which diagrams the growth of a Ge nanowire using an Au catalyst [7-8]. The VLS growth of a nanowire can be summarized into three steps: (I) liquid alloy droplet formation, (II)

nanowire nucleation, and (III) nanowire elongation (i.e. growth). This process is displayed schematically in Fig. 2.1a. In addition, the process may also be plotted on a phase diagram for the alloy system (Fig. 2.1b). This phase diagram is specifically known as a binary eutectic phase diagram, where the independent variables are the alloy compositional percentage and the temperature; the experimental data (data of interest) is the phase of matter of the materials.

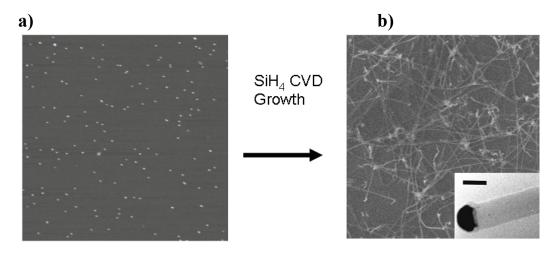

Fig. 2.2 Before and After Silicon Nanowire Growth a) AFM image of 10 nm Au nanoparticles on a growth substrate. b) SEM image of Si nanowires grown after CVD VLS process. Inset, the solidified alloy droplet can be seen at the end of the nanowire when imaged post-growth. The sides of both images are 4  $\mu$ m. Reprinted with permission from [9]. Copyright 2001, American Institute of Physics.

To go into more detail about the phase diagram, one can notice from Fig. 2.1b that the Au/Ge alloy is eutectic, where the melting point of Au and Ge is 1064 °C and 938 °C, respectively. The eutectic point for an eutectic alloy system is defined as the temperature and compositional gradient at which the alloy has its lowest melting point. The eutectic point is important since the liquid and solid phases of the material system are all allowed to exist simultaneously at these conditions. The eutectic point for the bulk Ge/Au system is 28% Ge atomic percentage, 361 °C. The green and blue lines on the plot are the Au and Ge, respectively, liquidus lines. They represent the boundary above which these

materials are liquid, and below which are solid. The solidus line (black, horizontal) line occurs at the eutectic temperature (361 °C) and represents the temperature below which the alloy must be solid.

Fig. 2.1 illustrates the VLS growth process of a Ge nanowire at ~800 deg C as examined in ref. [7]. This temperture was chosen by the experimenters due to constraints in their experimental setup. Ge nanowire VLS growth may occur at temperatures between the melting point of Ge (938 °C) and the eutectic temperature of the Ge/Au alloy. It is important to note that Ge nanowire VLS growth has been observed at temperatures down to ~270 °C [10] due to reasons that will be discussed later.

In step I, liquid Ge/Au alloy droplet formation, the Au catalyst sites are heated up in the presence of a vapor source of Ge (typically GeH<sub>4</sub>). Liquid droplets will start to form above the eutectic temperature for the nanoscale alloy system. Note that without the presence of gaseous Ge molecules, the Au catalyst sites will not liquefy at the eutectic temperature. Direct TEM observation of Au nanoparticles heated up to 900 °C in a vacuum (without any gaseous Ge source) revealed that the Au did not liquefy [7]. The diffusion of Ge atoms into the Au cluster sites is required for the Ge/Au alloy droplet formation. When CVD reactants are used (i.e. GeH<sub>4</sub>), the temperature is a crucial factor for the dissociation of the reactant precursor molecule and the subsequent absorption of the Ge atoms. GeH<sub>4</sub> readily dissociates at low temperatures (i.e. ~270 °C) at metal catalyst sites while other CVD precursors (i.e. SiCl<sub>4</sub>) require high temperatures (i.e. 800 °C or above) for reactant dissociation when carrying out Si nanowire VLS growth [6].

During droplet formation, the metal nanoparticle site serves as a catalyst for the decomposition of the reactant molecules by lowering the thermodynamic energy barrier

required for reactant dissociation and subsequent crystal (nanowire) formation. Due to this energy barrier lowering, materials may preferentially deposit at these catalyst sites and cause nanowire growth while leaving the rest of the growth substrate free of any deposition, as evidenced in Fig. 2.2.

It was originally suggested by Wagner [4] that a reason for this catalytic activity of the metal catalyst particle was due to the high sticking coefficient that a liquid droplet presents to a gaseous reactant (like SiH<sub>4</sub>) as compared to the solid, bare growth substrate. A sticking coefficient is defined as the probability that an impingent molecule attaches to a certain surface upon collision. It is true that silanes have a larger sticking coefficient on liquids catalysts as compared to typical growth substrates, however this phenomenon cannot explain all VLS growth processes, especially when the growth material is not a reactant molecule, but rather evaporated from a solid source [11]. Although the exact source for the catalytic activity of the metal nanoparticle is still under debate, under typical VLS growth conditions the metal nanoparticle's catalytic properties allow for it to act as a sink for gaseous material sources and for the exclusive incorporation of these materials for nanowire growth as opposed to substrate or sidewall deposition.

As the VLS process proceeds, the adsorption of the growth material (Ge) and its incorporation into the liquid alloy droplet will cause the alloy to increase the saturation ratio of Ge in the originally 100% Au nanoparticle. It is illustrative to examine an isothermal line (at 800 °C) for this specific saturation of Ge into the Au nanoparticle as shown in Fig. 2.1b. It is thermodynamically allowed for the Ge incorporation to continue into the droplet along the horizontal isothermal line until one reaches the Ge atomic concentration rate which intersects the Ge liquidus line (blue). Beyond this concentration

of Ge, any further increase in Ge percentage in the liquid alloy is defined as supersaturation. Although the condition of supersaturation is not thermodynamically favored, it may exist in a state of unstable equilibrium due to the fact that the way to resolve this unfavored state, which is crystal nucleation, requires a certain energy input to initiate [8]. As time goes on and Ge continues to incorporate into the droplet, a critical supersaturation ratio is reached where the unstable equilibrium can no longer be maintained, and nucleation of the nanowire will occur (step II). Nucleation is defined here as the formation of a crystal phase.

Subsequent to the nanowire nucleation, further incorporation of the Ge species will cause nanowire elongation (i.e. axial growth, step III). It is explained that this additional supersaturation of Ge species causes additional Ge crystal precipitation (i.e. nanowire growth) as opposed to additional nucleation events due to the fact that less energy is needed for crystal growth as compared to additional nucleation events in the droplet.

Nanowire growth continues as long as a sufficient partial pressure of gaseous Ge material is present or the temperature is sufficient. As soon as these conditions cease, the alloy droplet expels the supersaturated portion of the Ge via the nanowire growth mechanism and the liquid alloy droplet will be left at an eutectic alloy concentration.

# 2.2 Important Aspects related to VLS Nanowire Growth

#### 2.2.1 Nanoparticle Catalysts

The choice of metal catalyst for VLS growth plays a critical role. As previously mentioned, the metal catalyst must be able to form an eutectic liquid alloy with the certain nanowire growth species. Moreover, the solid solubility of the catalyst in the final single-crystalline material must be low so as to minimize crystal defects. For instance,

Au is commonly used to catalyze Si nanowire VLS growth, and the maximum solid solubility of Au in Si is just  $\sim 2x10^{-4}$  at.% at 1280 °C [12], making it an appropriate choice.

Another important consideration is whether the metal catalyst can alternatively perform nanowire growth via the vapor-solid-solid (VSS) process. VSS growth proceeds similarly to the VLS process, a catalytic metal nanoparticle acts as a growth site for a nanowire single-crystal. Unlike the VLS process, VSS growth proceeds with the metalrich catalyst particle remaining in a solid state throughout the entire growth process [13]. One notable feature of the VSS process is that it can take place far below the eutectic temperature of the catalyst and crystal material alloy. For instance, Si nanowire growth with Cu catalysts has been demonstrated via the VSS mechanism at ~400 °C while the eutectic temperature of the system is ~800 °C [13]. Moreover, the VSS nanowire growth typically proceeds 10-100x slower as compared to VLS growth under comparable conditions [14]. Both VLS and VSS growth have been observed occurring at the same time in a single growth chamber [8]; therefore in order to maintain good control over nanowire growth it necessary to properly control and choose the appropriate growth mechanism. Au is often chosen as the alloy for VLS growth due to the fact that it possesses a low eutectic temperature in most alloys that it forms, suppressing the likelihood of VSS growth.

The density and morphology of the metal nanoparticles are a critical determinate of nanowire growth. Since VLS grown nanowires roughly take on the diameter of the metal catalyst nanoparticle, the presence of a wide distribution of nanoparticle sizes will produce nanowires possessing the same large size distribution [15]. To mitigate these

effects, the most popular method of placing metal catalysts on a substrate is the dispersion of metal liquid colloids (i.e. colloidal Au). These liquid colloids consist of metal nanoparticles stabilized in a liquid suspension [9]. As seen in Fig. 2.2, the nanowires produced using such nanoparticles are of a very uniform diameter. Clumping of the deposited nanoparticles on the substrate must be avoided, however, in order to ensure that the nanoparticle catalysts do not combine together under the high temperatures of VLS growth. Since the nanoparticles become liquid alloys under VLS growth, in such conditions they may readily combine with other physically adjacent nanoparticles. The appropriate choice of nanoparticle density is known to reduce the chance of this occurring.

Fig. 2.3 Annealed 2 nm thick Au thin film

Reprinted with permission from [11]. Copyright 2001, American Institute of Physics.

Another widely used method for creating metal nanoparticles is through the annealing of metal thin films. These metal thin films are typically deposited in thicknesses of ~1 nm to ~100 nm. The metal thin film may be annealed at appropriate temperatures (i.e. ~500 °C for Au thin films [11], Fig. 2.3) to cause the film to ball up into separate islands of metal with a non-uniform size distribution [16]. It is clearly noted in Fig. 2.3, that there are nanoparticles of a large diameter (greater than 100 nm) on the substrate. After

carrying out Ge nanowire growth, the authors measured the diameters of the synthesized nanowires in the range of 20-180 nm.

#### 2.2.2 Nanoscale Eutectic Temperature

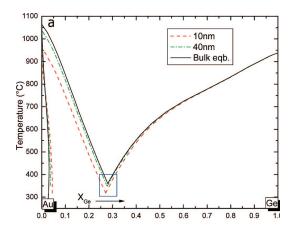

${\bf Fig.~2.4~Theoretical~Calculations~of~the~Nanoscale~Eutectic~temperature~for~the~Au-Ge~system}$

Adapted with permission from [17]. Copyright 2007 American Chemical Society.

For nanoscale systems (i.e. metal nanoparticles or thin films), it has been widely noted that an alloy's eutectic temperature is typically suppressed [18] from the well-known bulk values. This effect contributes to the reduction of the minimal temperature necessary for nanowire VLS growth. For instance, as displayed in Fig. 2.4, the eutectic temperature of 10 nm diameter Au nanoparticles in the presence of Ge species experiences a much lower eutectic temperature (~300 °C) as compared to the bulk system (~360 °C). In addition to the eutectic temperature lowering due to size-related effects, the supersaturation of the alloy droplets with high Ge concentration during VLS growth is also hypothesized to keep the Ge/Au alloy in the liquid state even further below the bulk eutectic temperature [8, 17], allowing for Ge nanowire VLS growth at temperatures as low as ~260 °C.

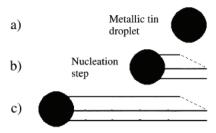

### 2.2.3 Nucleation of Nanoparticles

Although ideally in VLS growth there should be a 100% nucleation rate of each catalyst nanoparticle to initiate the growth of an individual nanowire, this does not always happen under practical conditions. As displayed in Fig. 2.5, it is possible for a single metal catalyst nanoparticle to either: (a) not nucleate nanowire growth at all, (b) nucleate a single nanowire growth, or (c) nucleate multiple nanowire growth fronts. The most important factors that were found to determine these effects were the growth temperature and the partial pressure of the reactants [10]. Under higher growth temperatures and higher partial pressures of the growth reactants, more nucleation events occurred.

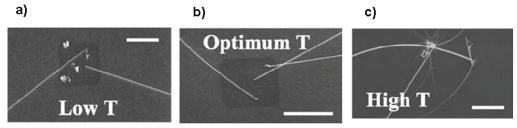

Fig. 2.5 Nucleation (or lack thereof) of nanoparticle catalysts SEM images of Ge nanowire growth under different conditions (only temperature is varied). a) less than 100% nucleation of Ge nanowires, b) one-to-one nucleation of Ge nanowires from Au nanoparticle catalysts, c) multiple nanowire growths from Au catalyst sites. Scale bar is 5  $\mu$ m for a and b and 1  $\mu$ m for c. Reproduced with permission from [10, 19]. Copyright Wiley-VCH Verlag GmbH & Co. KGaA.

#### 2.2.4 Nanowire Sidewall Deposition

In the idealized VLS nanowire growth mechanism, deposition of material on the grown nanowire sidewalls is assumed not to occur. However, under certain conditions this may in fact take place, leading to the growth of tapered nanowires (Fig. 2.6).

Tapered nanowires feature a wide base and narrow top (the end where axial growth ceases). This morphology is due to the fact that sidewall deposition is typically homogenous and occurs at a uniform rate on a nanowire; thus, the oldest grown segments of the nanowire experience the most deposition and the newly grown sections of a

nanowire will experience the least amount of total sidewall deposition.

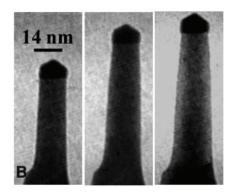

Fig. 2.6 A tapered nanowire.

TEM image of the growth of a tapered Ge nanowire. From left to right, is an image of the same Ge nanowire as the growth proceeds. Adapted from [8]. Reprinted with permission from AAAS.

Various strategies for reducing or eliminating sidewall deposition have been demonstrated. Two parameters known to play a large role in uncatalyzed deposition are growth temperature and the partial pressures of reactants. Increasing either parameter will increase the amount of thermal decomposition of material species on grown nanowires and the substrate itself [10]. To carry out proper nanowire growth, these two parameters must be properly adjusted to address the two important needs of: (1) high yield nanowire nucleation, and (2) the prevention of sidewall deposition.

Ge nanowire growth provides a good example of the rational choice of the growth temperature in order to address these two simultaneous needs. It has been established that Ge nanowires grown from GeH<sub>4</sub> are particularly susceptible to uncatalyzed sidewall deposition if grown near the bulk eutectic temperatures on Ge and Au (~360 °C) [17]. A successful method to achieve both high nucleation rates and uniform nanowire diameters is through the use of a two-step growth process as displayed in Fig. 2.7. A higher temperature is used initially in the VLS growth process in order to cause the nucleation of a large percentage of the alloy nanopaticle droplets. Then, once high yield nucleation is

achieved, the temperature is ramped down to a lower level to prevent sidewall deposition while simultaneously providing sufficient nanowire axial elongation growth rates.

Another strategy involves the use of an appropriate carrier gas to functionalize the grown nanowire surfaces with the correct functionalization group which prevents sidewall deposition. This was demonstrated with the use of H<sub>2</sub> as a carrier gas in order to H- terminate silicon nanowires during VLS growth [20]. Additionally, the use of local substrate heaters (as opposed to hot-wall chambers) has been shown to reduce the amount of unwanted thermal decomposition of CVD reactants and thus reduce nanowire sidewall deposition [20].

**Fig. 2.7 Ge Nanowire Growth Scheme**Two temperature VLS growth process where first high yield nanowire nucleation is achieved at a high temperature, followed by axial elongation and no sidewall deposition at a lower temperature. Reprinted with permission from [21]. Copyright 2004, American Institute of Physics.

#### 2.2.5 Nanowire Growth Rates

Another essential parameter for nanowire growth is the rate of axial elongation of the nanowire. Depending on deposition conditions, this rate can be drastically altered. For instance, the CVD reactant Si<sub>2</sub>H<sub>6</sub> was found to produce nanowires at growth rates over 100x as great as compared to SiH<sub>4</sub> [22]. It was reasoned that Si<sub>2</sub>H<sub>6</sub> more readily decomposes as compared to SiH<sub>4</sub>. Besides the choice of reactant species, other

parameters which play a critical role are the temperature and partial pressure of the reactance species [23]. Increasing either of these parameters will also increase the nanowire growth rate.

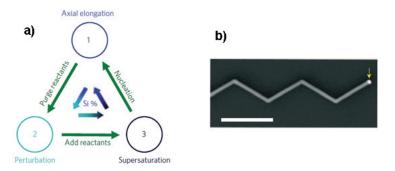

Specifically, it has been shown that the amount of supersaturation of the crystal growth material in the liquid alloy nanoparticle is directly influenced by the partial pressure of the gaseous reactants. This amount of supersaturation is what directly effects nanowire growth rates. Thus, it has been observed that typically a higher partial pressure of the reactants leads to higher growth rates [24]. This can be most dramatically seen in Fig. 2.8, where nanowire growth can be repeatedly stopped and restarted by simply purging and reflowing gaseous reactants into the growth chamber. Completely purging the chamber lowers the amount of supersaturation of the alloy droplet causing growth to cease. When reactants are again flowed in, high supersaturation levels are restored in the droplet, and a new nucleation event occurs, followed by the continuation of nanowire growth. The evidence of these additional nucleation steps can be evidently seen in the kinks (abrupt ends) of the nanowire.

**Fig. 2.8** The Stoppage and Resumption of Nanowire Growth

a) Schematic of a cyclical method to stop and restart nanowire growth. During nanowire growth (1), reactants may be purged from the growth chamber, ceasing growth (2). Growth may be restarted by flowing in reactants again (3). b) SEM image of a kinked Si nanowire. Scale bar is 1 μm. Reprinted by permission from Macmillan Publishers Ltd: Nature [24] copyright 2009.

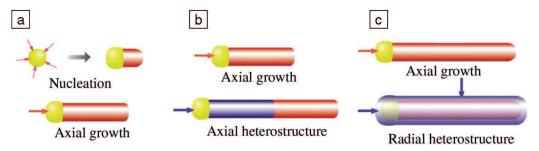

#### 2.2.6 Nanowire Heterostructures

Another benefit that the bottom-up growth of nanowires provides is that different materials may be incorporated into a single nanowire in a heterogeneous configuration during growth. A schematic of the possible configurations of the heterogeneous nanowire material structure is shown in Fig. 2.9. The base case (starting point) to heterogeneous nanowire growth is the VLS growth of a single material nanowire (Fig. 2.9a). The VLS growth process has already been extensively covered earlier in this chapter. By modifying the reactant gases during VLS growth, axial or radial material nanowire heterostructures may be obtained. An axial heterostructure (Fig. 2.9b), where the material varies along the long axis of the nanowire, can be achieved by varying reactants during the axial elongation phase of VLS growth.

Radial heterostructures (Fig. 2.9c), where the material composition varies symmetrically along the radial cross-section of a nanowire, are synthesized by performing sidewall (i.e. homogeneous) deposition of a new material after axial elongation of the nanowire is ceased. A two-material radial heterostructure, as depicted in Fig. 2.9c, is typically termed a core-shell nanowire, where the core comprises of the starting nanowire material, and the shell is made up of the later, homogeneously deposited exterior material. The limit to the amount of shells capable of being deposited is in theory unlimited, but the practical limit is determined by the specific material system being deposited.

**Fig. 2.9 Nanowire Heterostructure Configurations**Description given in text. Arrow denotes preferential site for reactant adsorption. Reprinted with permission from [25]. Copyright 2003, Materials Research Society.

## 2.3 Nanowire Growth Setups

#### 2.3.1 CVD Nanowire Growth

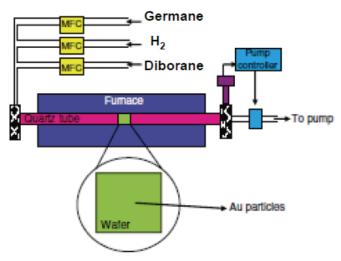

One of the most common setups used to carry out the VLS growth of nanowires is in a low-pressure CVD, i.e. LPCVD, apparatus (Fig. 2.10). Typically, the setup comprises of a two-ended quartz tube placed in a ceramic-encased resistive element furnace. One end of the tube (the inlet side) is hooked up to mass flow controllers (MFCs) which regulate the input flow of compressed process gases. Besides the main process gas (i.e. SiH<sub>4</sub> or GeH<sub>4</sub>), there may be also be dopant gases or dilutant gases (i.e. H<sub>2</sub> or Ar) fed into the growth chamber. The other end of the tube (outlet side) is hooked up to a vacuum pump via an adjustable vacuum throttle valve. The nanowire growth substrates are placed in the center of the tube furnace where temperature uniformity is the highest.

The nanowire growth is typically run at low to medium vacuum (~1 to 760 torr) and this is controlled by properly adjusting the inlet flow of the gases as well as the strength of the vacuum pump via its throttle valve connection to the outlet of the tube. Similar to conventional LPCVD systems, the major reason for low-pressure depositions is to increase uniformity across the deposition substrates [26]. Additionally it is important to

be able to adjust the process pressures for VLS nanowire growth, since these parameters directly affect all aspects of nanowire growth (as detailed earlier).

Fig. 2.10 CVD Setup for Ge Nanowire Growth

Reprinted by permission from Macmillan Publishers Ltd: Nature Protocols [15] copyright 2004.

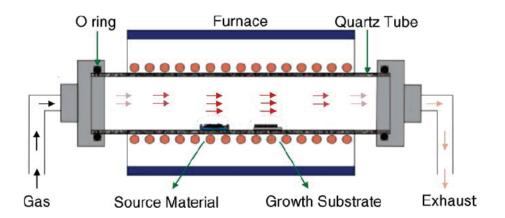

## 2.3.2 Vapor-Transport Metal Oxide Nanowire Growth

An alternative method for nanowire growth via the VLS method relies upon the vapor transport of evaporated source materials from a solid source (typically in powder form). This method is schematically similar to the CVD growth method outlined earlier, with the one difference being that the source materials are supplied via thermal evaporation rather than compressed gas sources. A typical setup for this process is depicted in Fig. 2.11. As before with CVD systems, the setup comprises of a two-ended quartz tube placed in a ceramic-encased resistive element furnace. One end of the tube (the inlet side) is hooked up to mass flow controllers (MFCs) which regulate the input flow the compressed carrier/process gases. The other end of the tube (outlet/exhaust side) is hooked up either to an exhaust or a vacuum pump depending on whether atmospheric pressure or vacuum is desired. Inside the quartz tube is first placed the source material and then downstream

is placed the growth substrate.

Regardless of the process pressure of the tube (either atmospheric or vacuum), a carrier gas is supplied at the inlet end of the tube via a MFC in order to direct the transport of the evaporated source species to the downstream growth substrate. This carrier gas is typically either Ar or  $N_2$ ; the carrier gas species and flow rate are important parameters for nanowire growth [27].

Near the middle of the tube lies the source material. During process, this area of the furnace is heated up to a high temperature so as to create a partial pressure of the species by thermal evaporation. This partial pressure is determined by the evaporation rate and vapor pressure (for a certain temperature) of the source material. Downstream of the source material is placed the growth substrate. The growth substrate is typically heated either to the same temperature or a lower one as compared to the source material (depending on process requirements). Additionally, the distance between the source material and growth substrate is an important parameter which affects the amount of material species that reach the growth substrate.

**Fig. 2.11 Vapor-Transport Apparatus for Nanowire Growth** Reprinted from [2] with permission from Elsevier.

The previously described vapor transport growth using evaporated source materials method can grow a wide variety of nanowires, including even Si or Ge [11] nanowires, however its use in the growth of metal oxide nanowires will be explored in detail. Metal oxide semiconductor nanowires; such as SnO<sub>2</sub>, ZnO, or In<sub>2</sub>O<sub>3</sub>; are a class of materials that readily lend themselves to be grown by the vapor transport growth method. In order to synthesize oxide nanowires with this method, two options are available: either the semiconductor oxide material may be evaporated directly (i.e. SnO<sub>2</sub>, ZnO, or In<sub>2</sub>O<sub>3</sub> powder), or a pure metal powder (i.e. Sn, Zn, or In) may be evaporated in the presence of  $O_2$  in the growth tube. The gaseous  $O_2$  may be supplied either via a MFC after pumping out residual atmospheric O<sub>2</sub> from the process tube; or instead, trace amounts of atmospheric O<sub>2</sub> that either leak into the tube or which are residual quantities may be utilized. This amount of  $O_2$  is a critical parameter of nanowire growth, it not only influences the volatility of the source material (due to competitive oxidation of the metallic atoms) but also influences the yield, morphology, and growth rate of the nanowires.

# 2.4 Metal Oxide Nanowire Vapor-Phase Growth

Metal oxide nanowires (i.e. SnO<sub>2</sub>, ZnO, or In<sub>2</sub>O<sub>3</sub>) may be grown using vapor-phase, metal catalyzed methods which are widely assumed to be similar to the previously detailed VLS method for Si and Ge nanowires. However, the exact growth mechanism of metal oxide nanowires is still under much debate in the literature. The main uncertainty lies in discerning the role of the metal catalyst during growth. The following four separate theories on metal oxide nanowire growth will be presented: (1) VLS growth, (2) VSS growth, (3) self-catalytic VLS growth, and (4) VS growth.

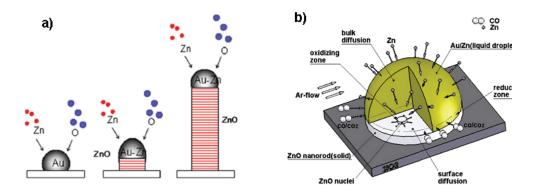

#### 2.4.1 VLS Growth of Metal Oxide Nanowires

The theorized VLS growth process for a ZnO nanowire will now be described. ZnO is chosen arbitrarily for this discussion, the process is applicable to any metal oxide nanowire. It is proposed that the VLS growth proceeds from a binary alloy droplet of the vapor phase Zn material and the chosen catalyst (i.e. Au). Upon sufficient supersaturation of the droplet, Zn precipitates from the droplet at the liquid-solid interface of the droplet and the ZnO nanowire. Oxygen is claimed not to be present in the alloy droplet (experimental data is cited in [28]), and the makeup of the Zn/Au alloy droplet is hypothesized to follow Wagner's original VLS theory of a binary eutectic alloy droplet. Gaseous oxygen atoms are next presumed to diffuse towards the Zn metal interfacial region (but not through the Au-Zn droplet bulk) and then carry out the oxidation of the Zn atoms into ZnO and thus elongate the nanowire [28-30].

It is important to note that the authors derived the above theory from experimental ZnO nanowire growth that took place near the melting temperature of Zn (~420 °C) [29, 31]. This theory however does not properly explain (seemingly-VLS) ZnO nanowire growth at temperatures far above Zn's melting temperature, i.e NW growth has been demonstrated at ~800 °C [32]. At such high temperatures, any precipitated Zn metal would quickly reliquefy which invalidates the previous model. A less widely cited proposal may explain such high temperature growths. It hypothesizes that oxygen diffuses into the alloy droplet during growth, causing supersaturation of the metal oxide inside the droplet, thus bringing about precipitation of the metal oxide and nanowire growth [33]. Moreover, the self-catalytic nanowire growth process may also play a role and will be covered in this chapter.

Fig. 2.12 Model for Metal Oxide Nanowire VLS growth

a) a proposed model for the VLS growth of a ZnO nanowire. The vapor phase Zn atoms are presumed to form an alloy with the Au catalyst nanoparticle. Nanowire growth proceeds via the precipitation of Zn from the droplet which then forms ZnO by oxidation by oxygen atoms present in the chamber. Reprinted from [34] with permission from Elsevier. b) a more detailed schematic of this model. Oxidative species (i.e. CO/CO2 in this figure) oxidize the precipitating Zn atoms at the liquid-solid interface of the catalytic droplet and growing nanowire. Reprinted from [28] with permission from Elsevier.

In addition to ZnO, Au-catalyzed VLS growth has been used to grow many other metal oxide nanowires, including SnO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> nanowires [35].

#### 2.4.2 VSS Growth of Metal Oxide Nanowires

An alternative explanation for metal nanoparticle catalyzed ZnO nanowire growth relies upon the vapor-solid-solid (VSS) growth mechanism. It is important to note that this theory was derived from experimental measurements on ZnO nanowire growths that were conducted at ~850 °C and does consistently explain growth at this high temperature [36]. The basis for their theory is attributed to XRD measurements taken on a ZnO nanowire forest after growth which reveal that no Zn was present in the Au catalyst nanoparticle tips. This finding leads the authors to suggest that VSS growth occurred rather than the more widely cited VLS method. The authors propose that the growth does not proceed via a supersaturation-nucleation process, but rather that the Au nanoparticles act as preferential adsorption sites for Zn species which then are incorporated in the growing ZnO nanowire by surface diffusion along the Au nanoparticle.

#### 2.4.3 Self-Catalytic Growth of Metal Oxide Nanowires

In the previous two methods, a separate catalyst metal (i.e. Au) was used in order to catalyze the growth of metal oxide nanowires. An alternative approach to metal oxide nanowire growth instead relies upon the self-catalytic NW growth properties of the metal species of metal oxide nanowires. For instance, it has been shown that ZnO nanowires have been selectively grown from Zn isolated metal islands without the use of any additional metal catalyst by simple oxidation annealing [37-38]. Since in both references, the reaction takes place above the melting point of Zn (~500 °C), it is hypothesized that Zn liquid originating on the Zn islands act as a catalyst to ZnO nanowire growth [39].

The vapor-phase growth of ZnO nanowires has been demonstrated on completely bare surfaces (i.e. SiO<sub>2</sub> or alumina) by the thermal evaporation of either Zn metal in the presence of O<sub>2</sub> or ZnO powder [34, 40]. Moreover, a similar synthesis has also been demonstrated with SnO<sub>2</sub> nanowires [41-42]. The mechanism for such nanowire growth is explained by two hypotheses: either self-catalytic VLS or vapor-solid (VS) growth. For both methods, source materials are evaporated at high temperature (usually in a tube furnace) into a vapor state and transported via carrier gas.

In self-catalytic VLS growth, the vapor phase species reaches the deposition substrate while still in the high temperature zone, and proceeds to coalesce onto the growth substrates to form liquid droplets. In particular, a requirement for self-catalytic VLS growth is that the deposition substrate temperature be above the melting point of the metal species to allow for liquid droplet formation. An example of this growth process for a SnO<sub>x</sub> nanobelt is shown in Fig. 2.13. One theory proposed to explain the self-catalytic growth process is that liquid metal droplets are formed which then catalyze nanowire growth as a result of the supersaturation of metal oxide in the droplet [43]. An

alternative theory surmises that instead of metal oxide supersaturation in the droplet, gaseous oxygen reacts at the surface of the droplet (not in the bulk of droplet) to form the metal oxide nanowire [37]. Importantly, Au-catalyzed VLS growth and self-catalytic VLS growth may proceed simultaneously. Branched SnO<sub>2</sub> nanowires have been grown from Au catalysts due to the self-catalysis of branched nanowire formation from adsorbed Sn droplets on the nanowire surface [33].

Fig. 2.13 Model for Self-Catalytic VLS growth of a  $SnO_x$  Nanobelt ) Sn droplet formation via the coagulation of vapor Sn atoms, b) nucleation of the  $SnO_x$  nanobelt after the Sn droplet becomes supersaturated with  $SnO_x$ , c) axial elongation of the nanobelt via precipitation of supersaturated  $SnO_x$ , similar to the VLS mechanism. Adapted with permission from [43]. Copyright 2006 American Chemical Society.

#### 2.4.4 Vapor-Solid Growth of Metal Oxide Nanowires

An alternative hypothesis to the self-catalytic formation of metal oxide nanowires is the VS growth process, whereby metal oxide vapor directly deposits onto the growth substrate in solid form. As a distinction to the VLS process, there is no intermediate liquid phase present. Crystal nucleation occurs directly as vapor metal oxide species condense (and solidify) onto a growth substrate. Nanowire growth proceeds due to the fact the nanowire growth front presents a thermodynamically favorable place for additional vapor phase species to solidify. Notably, the VS process is able to cohesively explain the self-catalytic growth of metal oxide [44] and even metal [45] nanowires on

deposition substrates held at temperatures lower than the melting point of the metal species. Furthermore, the VS process has also been deduced to operate at temperatures above the metal melting point [46] due to the fact that metal oxides typically possess melting temperatures greater than the metal element itself. A disadvantage of the VS process is that it is difficult to control the morphology of the grown nanowires (i.e. diameter) since no separate metal catalyst is required.

#### 2.4.5 Experimental Results for Vapor-Transport Growth of SnO<sub>2</sub> Nanowires

#### 2.4.5.1 Diameter-Controlled Vapor-Liquid-Solid SnO<sub>2</sub> NW Growth

The diameter-controlled growth of vapor-liquid-solid grown SnO<sub>2</sub> nanowires will be detailed in this section. Although such growth was only demonstrated in a small area (< 1 mm<sup>2</sup>) on a growth substrate which was not sufficient for device fabrication purposes, the demonstration does illustrate that such growths are in principle feasible. As described in section 2.4.1, nanoparticle-nucleated vapor-liquid-solid growth of nanowires is observable only under certain proper conditions, i.e. certain gaseous precursor vapor pressures and appropriate growth temperatures. At improper conditions, VLS nanowire growth will not be observed, but rather other material depositions will occur such as homogeneous material deposition which will be detailed in section 2.4.5.2.

#### Experimental Conditions

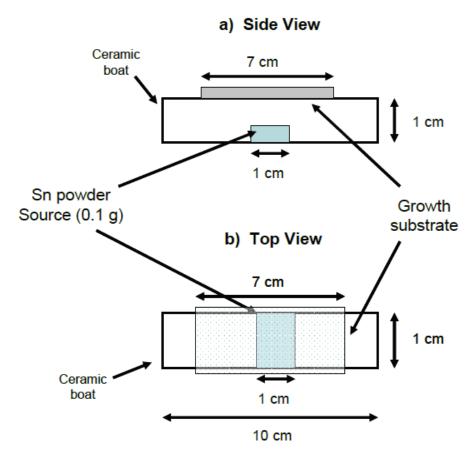

We were able to achieve a sufficient control over the deposition parameters and in turn VLS SnO<sub>2</sub> nanowire growth by utilizing the growth setup shown in Fig. 2.14. Growth was carried out in a single-zone horizontal tube furnace with tube inner diameter of 2 1/8 inches and length of 40 inches. The temperature ramp rates were fixed at 10 °C/min. A

Sn powder precursor, procured from Sigma Aldrich, 99.8% pure, was used as the Sn precursor source and was placed in the center of an alumina ceramic boat, the dimensions of the boat and weight of the Sn powder are described in Fig. 2.14.

The nanowires were grown on a Si substrate ( $7x1 \text{ cm}^2$ ) in which Au nanoparticles were deposited onto. Au nanoparticles colloidal solutions were procured from Ted Pella and diluted to a concentration of  $\sim 10^{10}$  particles/mL. Poly-I lysine functionalization of the Si surface was utilized in order to promote Au nanoparticle adhesion. The obtained nanoparticle deposition density was in the range of 1-5 nanoparticles /  $\mu m^2$ . 20 nm diameter Au nanoparticles were used for the growth process described in this section.

As shown in Fig. 2.14, the growth substrates were placed directly on top of the Sn powder source and let to lie flat on the top of the ceramic boat. The growth substrates were placed such that their nanoparticle-functionalized surfaces were orientated downwards closest to the Sn powder source. By only using a small amount of Sn powder (0.1 g) confined to a 1 cm long region in the center of the 10 cm long ceramic boat, a Sn vapor gradient was able to be produced during the high-temperature growth conditions. Specifically, during the growth process the Sn vapor pressure was highest in the volume of space contained by the ceramic boat directly closest to the Sn powder precursor. This Sn vapor pressure then monotonically decreased in the ceramic boat in a proportion that was directly related to the distance away from the center of the boat where the Sn powder precursor was situated.

The growth process proceeded as follows. The ceramic boat with Sn powder and with the Si growth substrate situated on top of the boat was placed in the center of the tube furnace. An Ar gas flow, acting as the carrier gas, of 0.7 SCFH was made to flow

through the tube using metered flows and at atmospheric pressure. The tube was allowed to heat up to 900 °C and was held there for 25 min. After this time elapsed, the furnace was opened and the ceramic boat was pulled out from the center of the furnace using a stainless steel rod while the furnace was still at the process temperature and let to cool at the end of the ceramic tube.

### Results

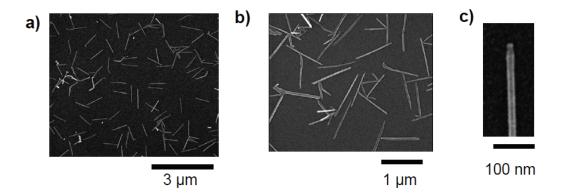

Following growth, SEM imaging of the growth substrate at an area situated 1.5 cm downstream from the center of the growth substrate showed diameter-controlled VLS SnO<sub>2</sub> nanowire growth (Fig. 2.15). The images show ~30 nm diameter SnO<sub>2</sub> nanowires growing from 20 nm Au gold nanoparticles, see Fig. 2.15c. It can be clearly seen that nanowire growth only occurred via a nanoparticle nucleated mechanism since nanowire growth occurred at commensurate densities as the Au nanoparticle deposition densities, i.e. the growth substrate is bare of deposition in areas where there is no nanoparticle present. In addition, a spherical Au nanoparticle was observed at the end of each asgrown nanowire which is a common characteristic of the nanoparticle nucleated VLS nanowire growth process. Although there are clearly some nanowires present in the SEM images that possess a diameter larger than 20-30 nm, this may be explained by clumping of the Au nanoparticles during nanoparticle deposition.

Self-catalytic VLS SnO<sub>2</sub> nanowire growth was also observed in areas on the growth substrate that were situated closer to the Sn powder source (< 1.5 cm away). Experimental descriptions of such self-catalytic growths will be described in the next section, but observance of such growth can be described by the higher Sn vapor

concentration in the closer regions and in turn the greater amount of Sn condensation on the growth substrate.

Fig. 2.14 Schematic for VLS grown SnO<sub>2</sub> NWs (not drawn to scale) a) Side view of the growth setup for achieving the VLS growth of SnO<sub>2</sub> NWs. A gradient of Sn vapor pressure is created (high to low) between the center of the ceramic boat and the boat edges. b) top view.

**Fig. 2.15 SEM Images of Diameter-Controlled VLS Grown SnO<sub>2</sub> NWs**a) As-grown SnO<sub>2</sub> nanowires on a Si substrate from 20 nm diameter Au nanoparticles. b) higher magnification image. c) Zoomed in image of an individual SnO<sub>2</sub> NW, clearly showing the Au nanoparticle at its tip.

## 2.4.5.2 Self-Catalytic VLS grown SnO<sub>2</sub> Nanowires

As opposed to the nanoparticle-nucleated SnO<sub>2</sub> nanowires described in the last section, the self-catalytic, Sn-catalyzed, growth of SnO<sub>2</sub> nanowires will now be detailed.

### Experimental Conditions

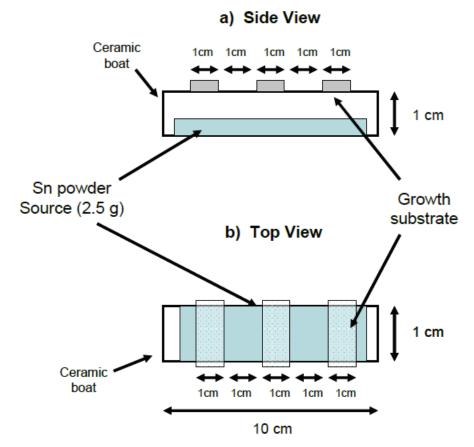

Details for the nanowire growth to be discussed in this section are closely similar to those conditions described in 2.4.5.1. All details for the nanowire growth procedure can be assumed to be the same as in that section unless otherwise noted. The growth setup is pictured in Fig. 2.16, please note that the amount of Sn powder precursor and distance of the growth substrates is different than in section 2.4.5.1. In particular, the amount of Sn powder precursor is larger, 2.5 g vs 0.1 g, and the 3 growth substrates (each 1x1 cm<sup>2</sup> in areal dimensions) are placed directly above this powder source. The effective result of these differences in the setup is to ensure a high and relatively constant Sn vapor pressure during nanowire growth. The practical result for this setup as will be detailed is to cause

a relatively large amount of Sn vapor condensation on the growth substrates (as compared to the section 2.4.5.1) and as a result a large amount of self-catalytic  $SnO_2$  nanowire growth.

Two separate growth runs were conducted with the setup pictured in Fig. 2.16: run A was performed at a process temperature of 900 °C for 10 min and run B was conducted at 900 °C for 25 min.

#### Results

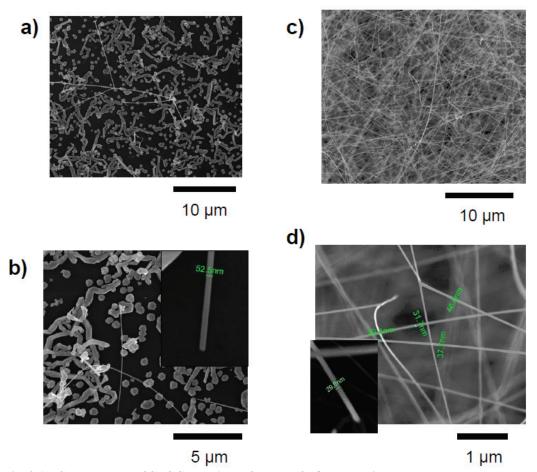

SEM images of the growth substrates were taken after the separate growth runs, A and B, were conducted. Fig. 2.17 (parts a and b) depict the growth results for run A (process conducted at 900°C for 10 min). SnO<sub>x</sub> microstructures can be discerned on the growth substrate which can be assumed to be a result of uncatalyzed, homogeneous deposition of SnO<sub>x</sub> materials. Although Au nanoparticles were utilized on the growth substrate, these SnO<sub>x</sub> microstructures are observed in areas where there is visually no Au nanoparticles present on the growth substrate. Careful imaging of the substrate can discern a few SnO<sub>2</sub> nanowires growing from certain microstructures on the surface. Close-up imaging of these nanowires, Fig. 2.17b, reveals that a spherical Au nanoparticle is not present on the nanowire tip. The lack of a presence of such a spherical nanoparticle leads one to conclude that self-catalytic VLS growth of the SnO<sub>2</sub> nanowire occurred. As discussed in section 2.4.3, such growth occurs when a liquid Sn droplet carries out the catalyzation of nanowire growth. It can be assumed that after cool down following nanowire growth that the Sn droplet is incorporated into the SnO<sub>2</sub> nanowire body and is unable to be discerned by SEM imaging. Such a result is consistent with publications cited in section 2.4.3.

The imaging results for growth run B (process conducted at 900°C for 25 min) is shown in Fig. 2.17 (parts c and d). Growth run B differs from run A only by a longer process duration time. The images reveal that a large amount of self-catalyzed SnO<sub>2</sub> nanowires are present on the growth substrate following the growth process. It is important to note that such features as: branching of the nanowires, lack of presence of a nanoparticle catalyst at the nanowires' tips, and lack of a tight nanowire diameter control lead one to conclude that self-catalytic VLS SnO<sub>2</sub> nanowire growth occurred. It is apparent from comparing growth runs A and B, that the presence of large SnO<sub>x</sub> microstructures on the growth substrates effectively acted as the originating source of growth for voluminous forests of branching and self-catalyzed VLS grown SnO<sub>2</sub> nanowires.

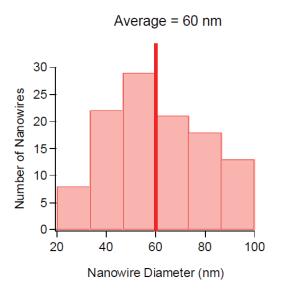

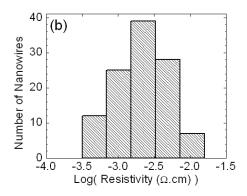

A histogram of the measured SnO<sub>2</sub> nanowire diameters from a similar growth run (see Fig. 2.18) show that there is a large variance of the nanowire diameters which contrasts with the diameter control which is a typical feature of nanoparticle-nucleated VLS nanowire growth. The nanowire diameters were measured by SEM and were chosen at random. Self-catalyzed growth is also suggested by presence of nanowire growth on the walls of alumina ceramic boats used during these two growth processes.

Fig. 2.16 Schematic for self-catalytic VLS grown SnO<sub>2</sub> NWs (not drawn to scale) a) Side view of the growth setup for achieving the self-catalytic VLS growth of SnO<sub>2</sub> NWs. A relatively high Sn vapor pressure is produced for all three nanowire growth substrates along nearly the entire ceramic boat length. b) top view.

Fig. 2.17 SEM Images of Self-Catalytic VLS grown SnO<sub>2</sub> Nanowires

a) SEM image of nanowire growth conducted for 10 min at 900 °C. b) zoomed in image of part a. Inset, shows image of a  $SnO_2$  nanowire with no spherical nanoparticle apparent at its end. c) SEM image of nanowire growth conducted for 25 min at 900 °C. d) Zoomed in image of part c. Inset shows  $SnO_2$  nanowire with no spherical nanoparticle at its growth end.

Fig. 2.18 Histogram of Self-Catalytic Grown SnO<sub>2</sub> Nanowire Diameters

Nanowire Diameter distribution of 111 measured SnO<sub>2</sub> nanowires grown via the self-catalytic VLS process.

# 2.5 Summary

In this chapter, a theoretical overview of the vapor transport growth of nanowires was presented. Two closely related processes, the vapor-liquid-solid (VLS) and the self-catalyzed VLS growth methods, were examined in the greatest detail. The key feature of such VLS-based growth methods are that they are able to achieve the growth of single-crystalline nanowires comprising a wide range of growth materials.

In order to examine their role in the growth of a type of nanowire of interest in this thesis work, both of these processes were demonstrated for the purpose of growing  $SnO_2$  nanowires. Utilizing a nanoparticle-nucleated VLS process, the diameter-controlled growth of  $\sim 30$  nm diameter  $SnO_2$  nanowires was presented. Moreover, large volume, self-catalyzed VLS growth of  $SnO_2$  nanowires was demonstrated using a growth condition consisting of a higher Sn vapor concentration. The nanowires synthesized by

this method were shown to consist of branched nanowires with a lesser degree of diameter consistency.

## Chapter 3

### Nanowire-based Transistors Overview

### 3.1 Nanowire-based FET Overview

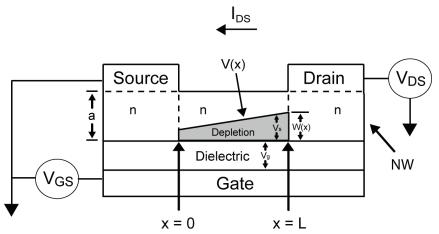

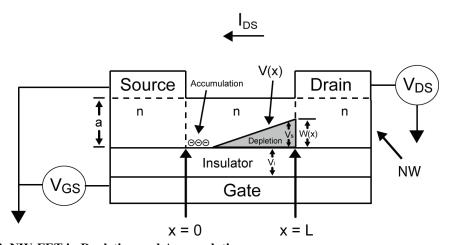

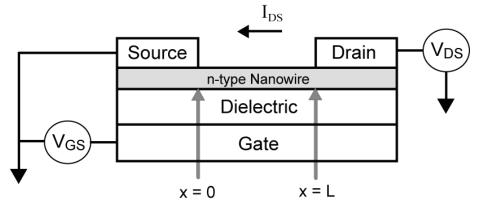

The electrical characteristics of a nanowire-based field-effect transistor (NW-FET) will now be discussed. The term field-effect transistor denotes a three-terminal device where the transverse electric-field imparted by the gate electrode controls the resistance of a semiconductor channel between the source and drain terminals. A diagram of a back-gated, single nanowire FET is shown in Fig. 3.2, where the source and drain metal electrodes of the device lay on top of the nanowire. Although geared towards NW-FETs, the following discussion also applies to thin-film transistors (TFTs) with a few substitutions in the analysis.

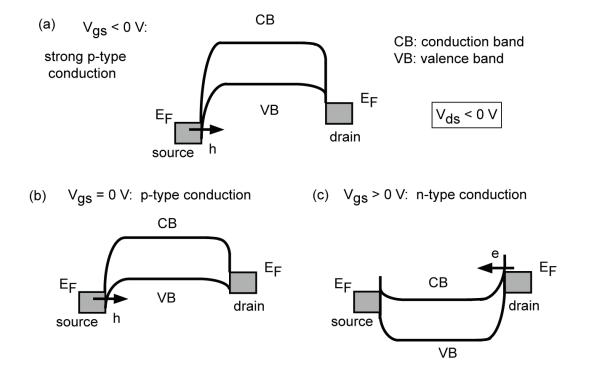

It is important to note that the NW-FET structure possesses some differences as compared to the widely studied MOSFET (metal oxide semiconductor) devices. In a NW-FET, the source and drain regions (which are in contact with the channel) are comprised of metal electrodes. This differs from the MOSFET case, where the source and drain regions are made up of degenerately doped semiconductor. This leads to the possibility of ambipolar conduction as shown in Fig. 3.1 which is not present in MOSFETs. Ambipolar behavior in FETs is defined as both n- and p-type conduction in a single device at the appropriate gate bias conditions. To simplify the discussion in this section, only the typical case of majority carrier conduction will be considered in the

Fig. 3.1 Field-Effect Operation of a NW-FET

Schematic of the effect of a transverse electric field (arising from a gate voltage) on the conduction and valence bands of an intrinsically p-type NW-FET, (a) strong p-type conduction is observed when  $V_{gs} < 0 \text{ V}$ . (b) p-type conduction (due to hole injection from the source metal electrode) occurs when  $V_{gs} = 0 \text{ V}$ . (c) at a bias such that  $V_{gs} > 0 \text{ V}$ , sufficient band bending occurs in the nanowire to favor electron injection from the drain electrode and thereby n-type conduction.

#### NW-FET under examination.

An additional property of NW-FETs to consider is that generally the nanowire is uniformly doped along its axial length. This contrasts with modern-day MOSFETs which typically feature varying dopant profiles along the channel in order to improve performance. A uniform doping level of the nanowire will be assumed in this discussion.

Another major difference is the device geometry, whereas a MOSFET is a planar device, the channel of an NW-FET can be approximated as a cylinder. As will be discussed later, capacitance estimates of the NW-FET structure must consider this difference.

To analyze an NW-FET, a model for carrier conduction in the NW channel must first be considered. The term  $Q_{ch}(x)$  will be used to represent the amount (magnitude) of

carrier charge at a certain location, x, of the NW channel. Since an NW-FET is a field-effect device, a transverse electric field emanating from the gate electrode will be used to modulate the carrier concentration in the NW channel. Specifically, the applied electric field from the gate causes a change in the position and shape of the conduction and valence bands of the NW as shown in Fig. 3.1. Such band bending can modulate regions of the nanowire channel into depletion and/or accumulation of carriers and this concept is the basis for the operation of the NW-FET.

Two different approaches will be examined for modeling NW-FET operation: a JFET-like approach where the nanowire region is treated as a bulk volume of charge, and a MOSFET-like approach where the nanowire channel is treated as a thin sheet of charge. In the following discussion pertaining to these two approaches, an n-doped nanowire will be assumed.

## 3.1.1 JFET approach to analysis of NW-FET Operation

Although a NW-FET is typically treated using MOSFET equations, a careful examination of the NW-FET structure shows that there is a major difference: the NW can conduct current via both a MOSFET-like surface channel and a JFET-like bulk channel. It will be shown that this is particularly relevant near the on-off transition when  $V_{\rm GS}$  is low so that the accumulation surface charge is not formed.

A three-dimensional (3-D) model will be used to examine NW-FET operation where the channel will be approximated as a 3-D rectangular volume. Fig. 3.2 displays a schematic of a cross-sectional view of this model. Let the channel geometry of the NW-FET be represented by the following variables: a is the height of the 2-D cross-section of the nanowire, L is the length of the channel region, and Z is the width of the channel.