# Broadening the Scope of Multi-Objective Optimizations in Physical Synthesis of Integrated Circuits

by David Anthony Papa

A dissertation submitted in partial fulf llment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Associate Professor Igor L. Markov, Chair Professor David T. Blaauw Professor Karem A. Sakallah Professor Dennis M. Sylvester Charles J. Alpert, International Business Machines Corporation  $\odot$  David Anthony Papa 2010 All Rights Reserved

#### **ACKNOWLEDGEMENTS**

This dissertation would not have been possible without the immeasurable self-sacrif ce of my perfect wife, Amy. She has worked day and night by my side for years to make our home and family prosperous. I love you very much. Our two beautiful sons George and Victor have brought me indescribable joy and gave me hope for the future when it seemed all was lost. I love you two in ways I never thought possible. I am eternally grateful to her for the faith she has placed in me. I will do everything I can to reward her investment.

I am also deeply indebted to her parents Ren Fang Zhang and Yue Xia Gong who have come from their home in China to live with us and help raise our babies. Without them, I don't know how it would be possible for me to balance graduate school, a full-time job, and a new family. I will be sorry when they return home.

My advisor, Professor Igor Markov, has also poured an incredible amount of work into training me to be capable of writing this dissertation. He has defended me when it was not convenient, supported me when it seemed hopeless, and never gave up on me until the task was complete. I am grateful for all of his efforts as well as all of the opportunities and second chances he has given me. I truly hope it has been as worth it for him as it has been for me.

I also want to thank all of the people at IBM Austin Research Lab, especially my manager Chuck Alpert and my mentor Gi-Joon Nam. Chuck's approach to industrial research is truly unique and I feel very fortunate to have worked with him during graduate school. Gi-Joon has seen my value from the very start and stuck his neck out for me when

it mattered most. I hope he feels proud of his judgment. I have also made many friendships here, and this research group is an amazing place to work. Zhuo Li, Jarrod Roy, Cliff Sze, Natarajan Viswanathan, Mehmet Yildiz and Nancy Zhou are brilliant people who have all had their impact on this dissertation. Working with these people on a topic I love has truly made it a pleasure to come to work each day. I also want to thank Anne Gattiker for accompanying me on so many occasions while I burned the midnight oil to f nish this thesis. John Keane and Vipin Sachdeva have also been close friends that enriched my life a lot during our time together at IBM.

I also have to thank all of my friends from igroup who have stayed close despite long distances and made life bearable. Jarrod Roy has been an especially close friend, and he is not so far away today. Smita Krishnaswamy has been my friend for even longer, and still brainstorms with me daily. Aaron may have left igroup a long time ago, but he is still making me laugh every day. George Viamontes has moved on to greener pastures, but he is always willing to lend good advice when its needed. Esha Krishnaswamy was never a member of igroup, but she has been there for moral support when I wanted it. Jin Hu has been a good friend and helped me with this thesis and been my boots on the ground in Michigan. And while I haven't been in Michigan for the current group of graduate students, Myung-Chul Kim, and Dong-Jin Lee, and Hector Garcia have all been good friends during my visits.

I also want to thank the other friends I have managed to keep over the years despite everyone being spread all over the country. Brandon Hanson has been by my side through a lot of interesting adventures, and would be there again if I needed him. Jason Feyers has been a really close friend and showed me a lot about life. Sid Bottoms and his family have always been good to me, and he is a really great guy. Max Mass taught me a lot of things and I have to thank him for that. Ryan Park has always been fun and I wish I stayed in

better touch with him now.

Last but not least, I want to thank my parents George and Maureen who gave everything they had to support me, as well as my sister and brothers Crystal, Mitchell and Evan, who look up to me and give me motivation to carry on. I love you all very much. I could not have been successful without the foundation they built. I expect my family's future to be bright thanks to their support and sacrif ces.

## TABLE OF CONTENTS

| ACKNOW    | LEDGEMENTS                                                     |

|-----------|----------------------------------------------------------------|

| LIST OF I | FIGURES                                                        |

| LIST OF T | TABLES                                                         |

| ABSTRAC   | CT                                                             |

| PART I    | Introduction and Prior Art                                     |

| Chapte    | r I. Timing Closure for Multi-Million-Gate Integrated Circuits |

| 1.1       | Challenges in Physical Synthesis                               |

| 1.2       | Our Contributions                                              |

| 1.3       | Organization of the Dissertation                               |

| Chapte    | r II. State of the Art in Physical Synthesis                   |

| 2.1       | Progression of a Modern Physical-Synthesis Flow                |

| 2.2       | The Controller / Transformation Approach                       |

| 2.3       | Circuit Delay Estimation                                       |

| 2.4       | Current Trends in Physical Synthesis                           |

| PART II   | Local Physical Synthesis and Necessary Analysis Techniques     |

| Chapte    | r III. Buffer Insertion During Timing-Driven Placement         |

| 3.1       | Introduction                                                   |

| 3.2       | Background                                                     |

| 3.3       | The RUMBLE Timing Model                                        |

| 3.4       | Timing-Driven Placement with Buffering                         |

| 3.5       | The RUMBLE Algorithm                                           |

| 3.6       | Empirical Validation                                           |

| 3.7       | Conclusions                                                    |

| Chapte   | r IV. Bounded Transactional Timing Analysis                     | . 58  |

|----------|-----------------------------------------------------------------|-------|

| 4.1      | Introduction                                                    | . 59  |

| 4.2      | Background                                                      | . 62  |

| 4.3      | Transactional Timing Analysis                                   | . 70  |

| 4.4      | Empirical Validation                                            | . 77  |

| 4.5      | Conclusions                                                     | . 80  |

| Chapte   | r V. Gate Sizing During Timing-Driven Placement                 | . 82  |

| 5.1      | Introduction                                                    | . 83  |

| 5.2      | Background                                                      | . 87  |

| 5.3      | Problem Formulation                                             | . 88  |

| 5.4      | Our Simultaneous Placement and Gate-Sizing Algorithm            | . 93  |

| 5.5      | Empirical Validation                                            | . 101 |

| 5.6      | Conclusions                                                     | . 101 |

| PART III | <b>Broadening the Scope of Circuit Transformations</b>          |       |

| Chanta   | r VI. Physically-Driven Logic Restructuring                     | . 103 |

| Спарис   | 1 VI. Thysicany-Driven Logic Restructuring                      | , 103 |

| 6.1      | Introduction                                                    |       |

| 6.2      | Background and Preliminaries                                    |       |

| 6.3      | Fast Timing-Driven Gate Cloning                                 |       |

| 6.4      | Empirical Validation                                            |       |

| 6.5      | Extensions                                                      |       |

| 6.6      | Conclusions                                                     | . 132 |

| Chapte   | r VII. Logic Restructuring as an Aid to Physical Retiming       | . 135 |

| 7.1      | Introduction                                                    | . 135 |

| 7.2      | Background, Notation and Objectives                             |       |

| 7.3      | Joint Optimization for Physical Synthesis                       |       |

| 7.4      | Empirical Validation                                            |       |

| 7.5      | Extensions                                                      | . 159 |

| 7.6      | Conclusions                                                     | . 160 |

| Chapte   | r VIII. Broadening the Scope of Optimization using Partitioning | . 161 |

| 8.1      | Introduction                                                    | . 161 |

| 8.2      | Background                                                      |       |

| 8.3      | Forming Subcircuits using Top-Down Netlist Partitioning         |       |

| 8.4      | Trade-offs in Window Selection                                  |       |

| 8.5      | Empirical Validation                                            |       |

| 8.6      | Conclusions                                                     |       |

| 0.0      |                                                                 |       |

| 9.1     | Introduction                             |

|---------|------------------------------------------|

| 9.2     | Background                               |

| 9.3     | Disruptive Changes in Physical Synthesis |

| 9.4     | A Graceful Physical-Synthesis Flow       |

| 9.5     | Empirical Validation                     |

| 9.6     | Conclusions                              |

|         | X. Conclusions and Future Work           |

| Chaptei | A. Conclusions and Future Work           |

| •       | Summary of Results                       |

| 10.1    |                                          |

# LIST OF FIGURES

| <b>Figure</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

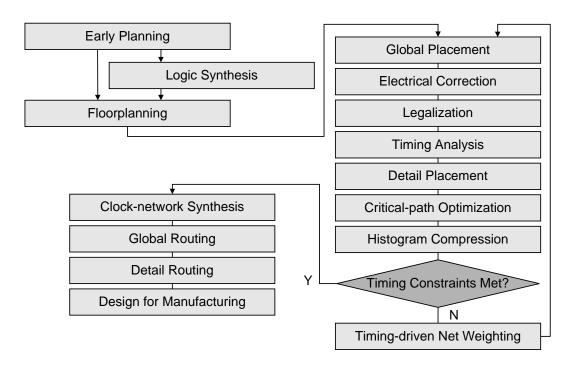

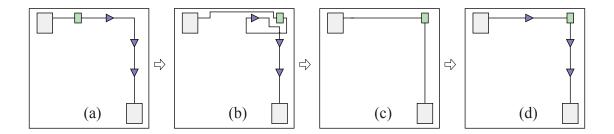

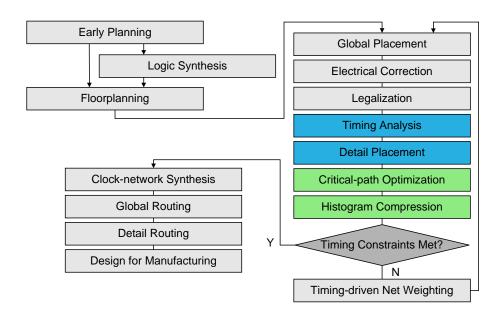

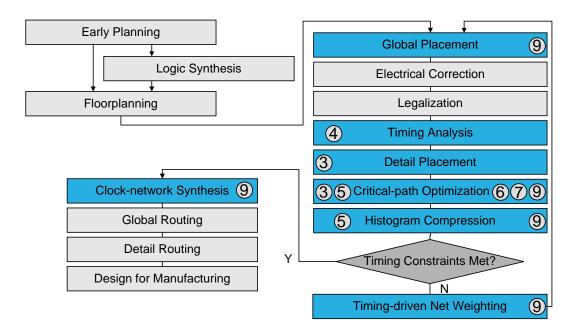

| 2.1           | Major stages of physical design include f oorplanning and logic synthesis, followed by physical synthesis beginning with global placement, and f nishing with routing and design for manufacturing. Physical synthesis can be iterated with modif ed parameters to improve the result, however, this f ow does not always converge to an acceptable solution                                                                                                                                                                                                                                                                                                         | 12 |

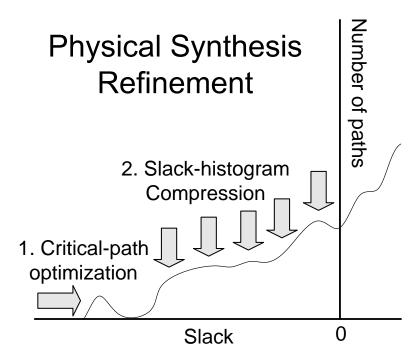

| 2.2           | During physical synthesis ref nement, optimization is f rst applied to most-critical paths, then different optimizations are used to reduce the total number of critical paths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14 |

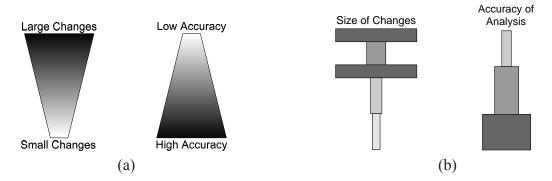

| 2.3           | In physical synthesis f ows, the amount of change to the design is large in early phases and reduces quickly in later phases. Timing models become more accurate as the f ow progresses. This trade-off is necessary because using the highest accuracy of analysis while making large changes to the design is too expensive. (a) An ideal physical synthesis f ow that gradually reduces the size of changes as it increases accuracy. (b) A more realistic example f ow with two global placement steps that move every gate in the design, and ref nement stages that apply local optimizations to one object at a time. Accuracy is increased in discrete steps | 15 |

| 3.1           | The contributions in this chapter improve the state of the art in critical path optimization and timing-driven detailed placement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

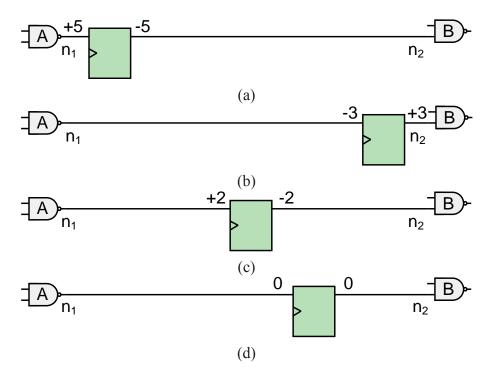

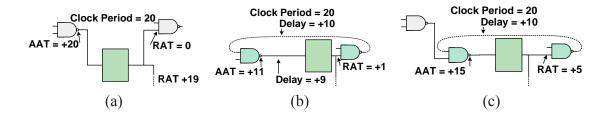

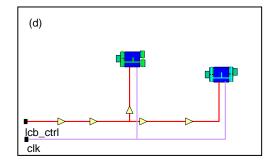

| 3.2           | The placement of a pipeline latch impacts the slacks of both input and output paths. A wirelength objective does not capture the timing effects of this situation, and with equal net weights a placer may choose the configuration in (a). In trying to f x this path, timing-driven net weighting would increase the weight on net $n_2$ , and placement would then choose the configuration in (b). Placing the latch in the center as in (c) is also not an optimal approach. There may be only a single optimal location as shown in (d)                                                                                                                        | 25 |

| 3.1           | early phases and reduces quickly in later phases. Timing models become more accurate as the f ow progresses. This trade-off is necessary because using the highest accuracy of analysis while making large changes to the design is too expensive. (a) An ideal physical synthesis f ow that gradually reduces the size of changes as it increases accuracy. (b) A more realistic example f ow with two global placement steps that move every gate in the design, and ref nement stages that apply local optimizations to one object at a time. Accuracy is increased in discrete steps                                                                             |    |

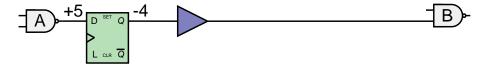

| 3.3 | A poorly-placed latch with buffered interconnect. In this case, the buffer must be moved or removed in order to have the freedom to move the latch far enough to f x the path.                                                                                                                                                                                                                                                                                                                                               | 29 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

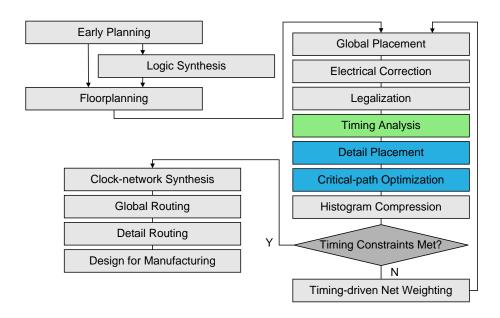

| 3.4 | The layout in (a) has a poorly-placed latch, and existing critical path optimizations do not solve the problem. Repowering the gates may improve the timing some in (b), but if it cannot fx the problem, the latch must be moved. Moving the latch up to the next buffer, shown in (c), does not give optimization enough freedom. If we move the latch but do not re-buffer in (d), timing may degrade. Figure 3.12(d) shows the ideal solution to this problem.                                                           | 30 |

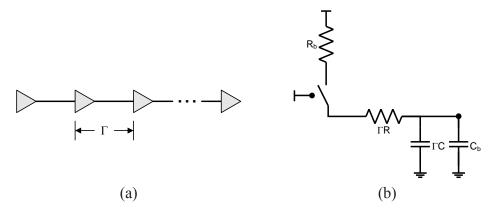

| 3.5 | (a) A model for buffered interconnect. $\Gamma$ describes the optimal distance between buffers on a two-pin net. (b) A corresponding $RC$ -network of a single buffer driving a wire segment. $R_b$ and $C_b$ represent the intrinsic resistance and gate capacitance of the buffer while $R$ and $C$ represent the per-unit resistance and capacitance of a metal wire.                                                                                                                                                     | 31 |

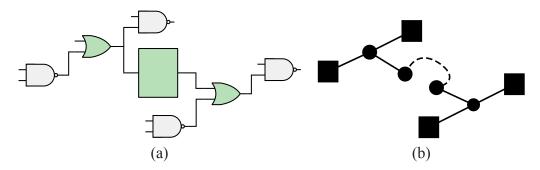

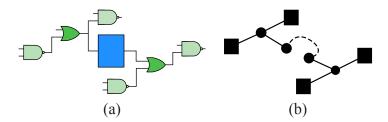

| 3.6 | (a) An example subcircuit and (b) corresponding timing graph used in RUMBLE. The AATs or RATs of unmovable objects (squares) are considered known. STA is performed on movable objects (round shapes).                                                                                                                                                                                                                                                                                                                       | 33 |

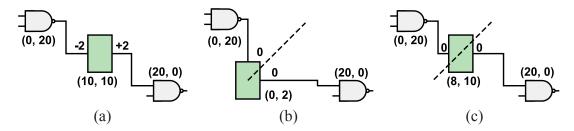

| 3.7 | In many subcircuits there are multiple slack-optimal placements. In RUMBLE we add a secondary objective to minimize the displacement from the original placement. This helps to maintain the timing assumptions made initially and reduces legalization issues. (a) shows the initial state of and example subcircuit, (b) a slack-optimal solution commonly returned by LP solvers, all optimal solutions lie on the dotted line and (c) a solution given by RUMBLE that maximizes worst-slack then minimizes displacement. | 34 |

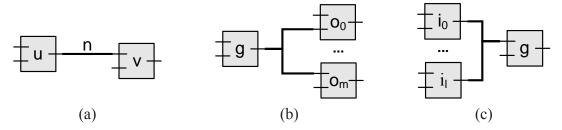

| 3.8 | (a) A timing arc $n_{u,v}$ connecting an arbitrary gate $u$ to an arbitrary gate $v$ . (b) The RAT of a gate $g$ is the minimum of RATs of the outputs of $g$ . (c) The AAT of a gate $g$ is the maximum of AATs of the inputs of $g$                                                                                                                                                                                                                                                                                        | 35 |

| 3.9 | (a) An example subcircuit with an imbalanced latch whose worst-slack cannot be improved. Nevertheless, it is possible to improve timing of the latch while maintaining slack-optimality. By including a TNS component in the objective, the total negative slack can be reduced, as shown in (b).                                                                                                                                                                                                                            | 38 |

| 3.10 | Modeling feedback paths within logic requires a new type of gate. Pseudomovable gates have timing values that depend on the timing values of neighboring gates, but they cannot be moved. (a) Ignoring the presence of feedback paths is overly pessimistic, and it appears that the timing of the latch cannot meet its constraints. (b) Making the fixed gates along a feedback path pseudomovable allows the latch to meet its timing constraints, but doing only this can lead to the wrong placement. (c) Including all gates connected to pseudomovables as fixed timing points properly models the problem as a convex subcircuit. | 43  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.11 | Subcircuit selection transparently skips buffers when building a neighborhood of movable gates, and requires detection of <i>pseudomovables</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44  |

| 3.12 | The RUMBLE algorithm proceeds by (a) selecting a subcircuit to work on. An LP is formulated and solved, with movable gates being relocated as shown in (b). Existing repeater trees are no longer appropriate, and are subsequently removed in (c). Finally, the nets are re-buffered, forming                                                                                                                                                                                                                                                                                                                                            | 1.6 |

|      | the f nal subcircuit shown in (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46  |

| 3.13 | The RUMBLE algorithm for moving one latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48  |

| 4.1  | The contributions in this chapter improve the results of timing analysis as it is used in physical synthesis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59  |

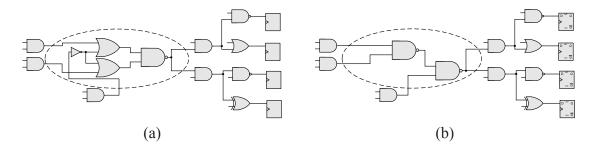

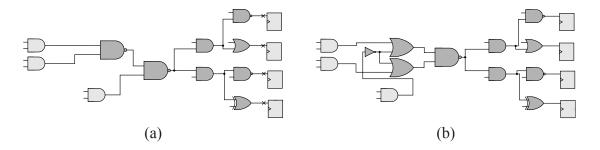

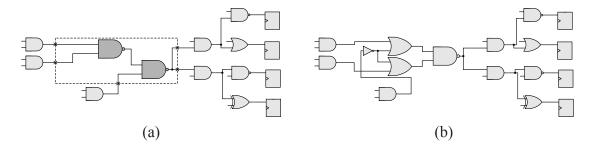

| 4.2  | A physical synthesis transformation improves the subcircuit in (a) by resynthesizing the logic, resulting in the circuit shown in (b). The traditional way of evaluating the timing impact of such transformations can be improved considerably.                                                                                                                                                                                                                                                                                                                                                                                          | 63  |

| 4.3  | Evaluating the timing impact of the physical synthesis transformation in Figure 4.2 (output side only). (a) Traditional static timing analysis with lazy evaluation will mark the fanout cone of the change dirty. (b) If the change is found to have a negative impact on timing, it will be reversed. This reversal will be treated as another change, and the fanout cone will be marked dirty for a second time.                                                                                                                                                                                                                      | 68  |

| 4.4  | Evaluating the timing impact of the physical synthesis transformation in Figure 4.2 (output side only). (a) Bounded transactional timing analysis will not propagate the change outside of a specified window. (b) In the event of a reversion, gates with dirty timing will have their timing data                                                                                                                                                                                                                                                                                                                                       |     |

|      | restored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71  |

| 4.5 | One possible implementation of transactional timing analysis. The functions Propagate-Forward and Propagate-Backward shown here using recursion for brevity are best implemented without recursion                                                            | 74  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | The contributions in this chapter improve the results of the critical path optimization and slack-histogram compression stages of physical synthesis.                                                                                                         | 83  |

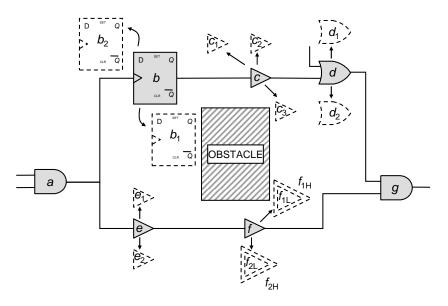

| 5.2 | Gates $a$ and $g$ are f xed. Alternate candidate locations for movable gates $b$ , $c$ , $d$ , $e$ , and $f$ have been determined. Gate $f$ also has two candidate power levels.                                                                              | 88  |

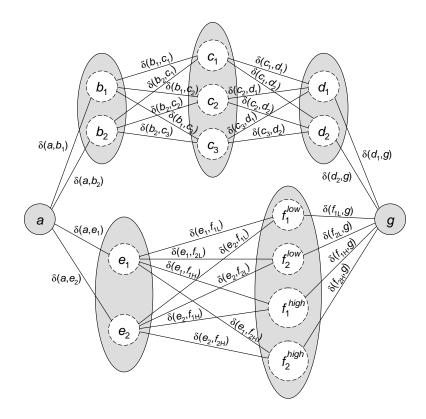

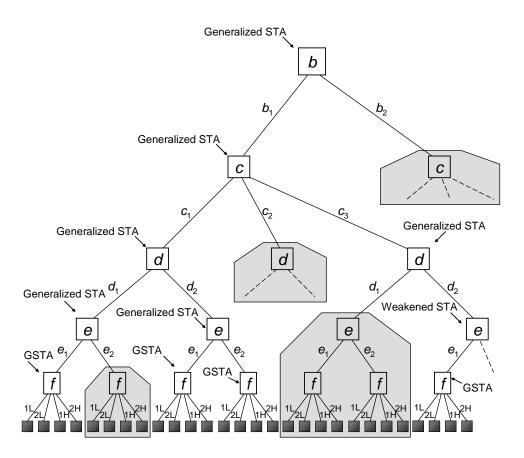

| 5.3 | The <i>disjunctive timing graph</i> for our running example. Each timing arc between a pair of candidate assignments has a distinct value; the actual arc between any two meta-nodes in a complete solution depends on the candidates chosen.                 | 92  |

| 5.4 | Branch-and-bound computes an upper bound on the worst negative slack at every node in search. Any partial solution that cannot improve upon the best known is pruned                                                                                          | 94  |

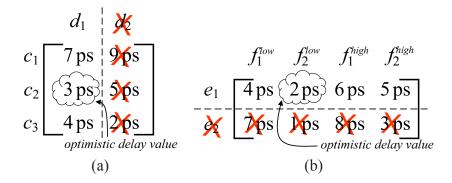

| 5.5 | The delay functions $\delta(c,d)$ and $\delta(e,f)$ . Here we show the case where the partial solution $S$ includes the decisions $(d \leftarrow d_1)$ and $(e \leftarrow e_1)$ . The weakened delay values are $\delta_S(c,d)=3$ ps and $\delta_S(e,f)=2$ ps | 96  |

| 5.6 | Pseudocode for the RATCHET algorithm                                                                                                                                                                                                                          | 97  |

| 6.1 | Example of interconnect-driven cloning. The arrival times of $F_1$ and $F_2$ are 0. The required arrival times of $S_1$ and $S_2$ are 5. For simplicity, this example uses gate delays of 0                                                                   | 106 |

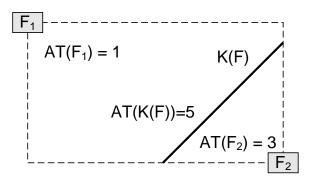

| 6.2 | An example of arrival time arc $K(F)$ . $dis(F_1, K(F)) = 4$ , $dis(F_2, K(F)) = 2$ , $\tau = 1$                                                                                                                                                              |     |

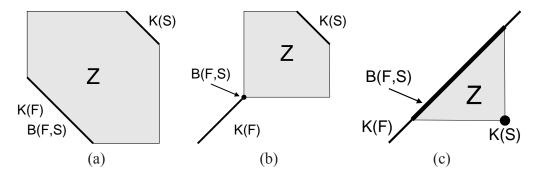

| 6.3 | Examples of the region $Z$ . (a) Both $K(F)$ and $K(S)$ are $-45^{\circ}$ line segments; (b) $K(F)$ is a $45^{\circ}$ line segment and $K(S)$ is a $-45^{\circ}$ line segment; (c) $K(F)$ is a $45^{\circ}$ line segment and $K(S)$ is a single point         | 116 |

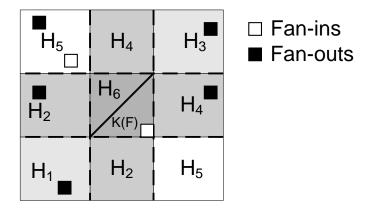

| 6.4 | The region division for the arrival time arc $K(F)$                                                                                                                                                                                                           | 118 |

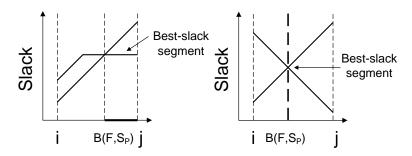

| 6.5 | The slack vs. $K(F)$ curves for each region                                                                                                                                                                                                                   | 119 |

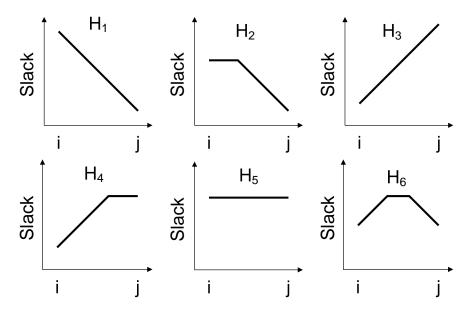

| 6.6 | Examples of Best Slack Segment.                                                                                                                                                                                                                               | 120 |

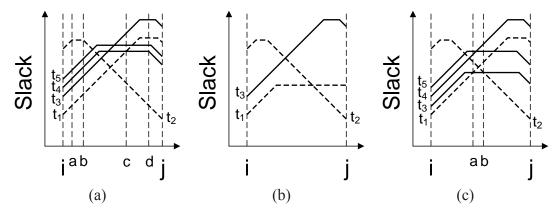

| 6.7  | gate duplication; (b) an example in which the rightmost and leftmost segments do not intersect; (c) an example that does not need gate duplication.                                                                                                                                                                                                                                                                                                                                            | 122 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.8  | Our simultaneous cloning and placement algorithm for a movable gate.                                                                                                                                                                                                                                                                                                                                                                                                                           | 125 |

| 6.9  | Our simultaneous cloning and placement algorithm for a f xed gate                                                                                                                                                                                                                                                                                                                                                                                                                              | 126 |

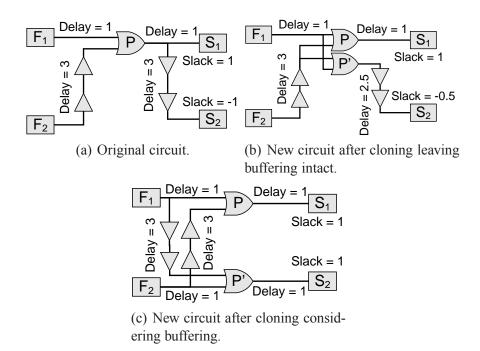

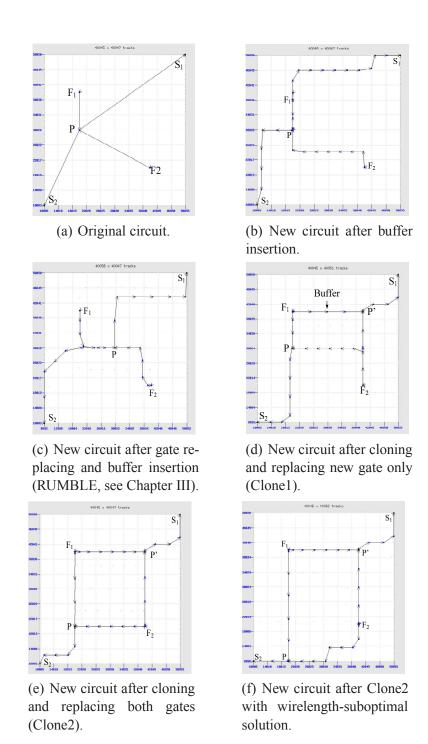

| 6.10 | Examples of different optimizations, including buffering, RUMBLE and cloning. $F_1$ and $F_2$ are fan-ins with same arrival time and $S_1$ and $S_2$ are fan-outs with same required arrival time. $P$ is the original gate, and $P'$ is the new duplicated gate.                                                                                                                                                                                                                              | 133 |

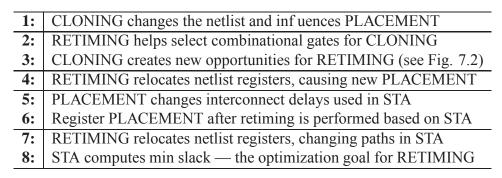

| 7.1  | Interactions in SPIRE's joint optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137 |

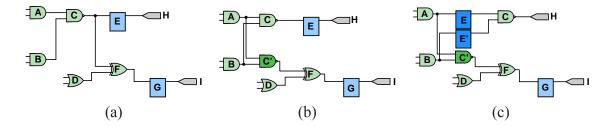

| 7.2  | Retiming and gate cloning to improve slack: (a) Register $E$ cannot be moved past gate $C$ because of fanout $E$ - $F$ . (b) If the NAND gate $C$ is cloned, creating a new gate $C'$ to drive its two sinks, it is possible to retime the top register without changing the logic function. (c) The final result with register $E$ retimed.                                                                                                                                                   | 140 |

| 7.3  | A circuit (a) and its timing graph (a). The square objects have f xed AATs or RATs. STA is performed only on circular movable objects                                                                                                                                                                                                                                                                                                                                                          | 140 |

| 7.4  | An LP for minimum-area retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142 |

| 7.5  | An LP for min-area, period-constrained retiming                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142 |

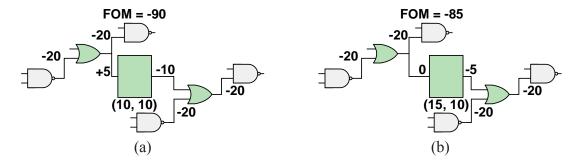

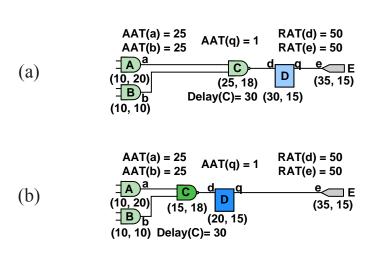

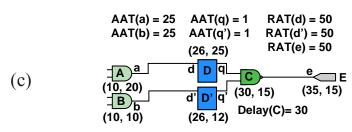

| 7.6  | Advantages of performance-driven retiming with simultaneous re-placeme Timing values of labeled pins are given, and physical locations of gates and ports are shown as (x, y) pairs. In the original circuit (a), the timing path feeding the input of the register has negative slack. Moving the gate and register in (b) improves the slack, but movement alone does not allow the path to meet timing constraints. Only by retiming and movement can all timing constraints be met in (c). | nt. |

| 7.7  | Finding minimum slack using LP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 146 |

| 7.8  | Max-slack retiming with STA embedded.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 149 |

| 7.9  | Optimal register location relative to adjacent gates                                                                                                                                                                                                                                                                                                                                                                                                                                           | 150 |

| 7.10 | Max-slack retiming with relocation of registers.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 151 |

| 7.11 | Gate cloning in max-slack retiming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 152 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.12 | Our SPIRE f ow proceeds in phases. First the MILP that represents only static timing analysis is solved without design changes. The values of relevant variables are saved and passed to the next stage which runs an MILP that incorporates retiming and cloning. The retiming variables are saved and f xed in an MILP that allows latches to move. Finally, with known values for latch locations and retiming variables we run the complete linear program.                                                                                                                                                                                                                                                                                                                                    | 156 |

| 8.1  | A generic iterative improvement physical synthesis algorithm that applies a transformation to a window based on bottom-up clustering. The performance of this algorithm can be tuned through the choice of clustering strategy, the selection of a controller and transformation pair, and through the runtime solution quality trade-off controlled by $S$ . Chapter III explores using an $n$ -hop clustering strategy and Chapter V was applied to windows selected in most-critical-f rst order                                                                                                                                                                                                                                                                                                | 163 |

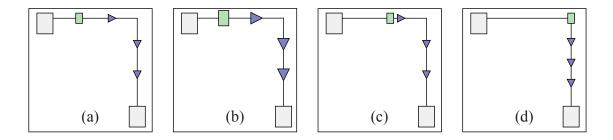

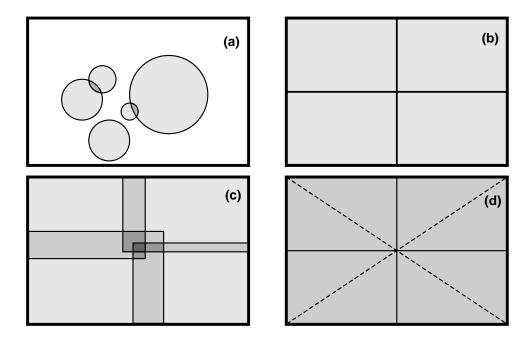

| 8.2  | Venn diagrams illustrating different window selection techniques. The outer rectangle in each image represents the entire design while shaded regions inside represent clusters or partitions. (a) Clustering grows windows around a seed object and typically creates overlapping windows that do not cover the circuit. (b) Partitioning divides the entire circuit into windows of approximately equal size that do not overlap. (c) The windows formed by partitioning can be expanded to deliberately create overlaps between adjacent partitions. (d) Partitioning can be performed multiple times to f nd orthogonal partitioning solutions. In (d) two independent 4-way partitioning solutions are overlaid, the solution from (b) is augmented by an additional one with dashed cutlines | 169 |

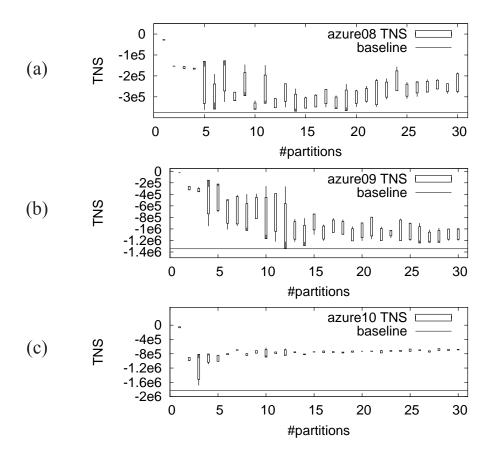

| 8.3  | An illustration of SPIRE's effect on $\mathcal{T}$ (TNS) versus the number of approximately equal-size partitions of three industrial microprocessor design blocks generated by the hMETIS partitioner [43]. (a) azure08 (b) azure09 (c) azure10. The horizontal axis indicates the number of partitions $k$ . The vertical bars extend to $+$ /- one standard deviation from the mean value of $\mathcal{T}$ . The wicks of candlesticks extend from the min to the max value of $\mathcal{T}$ . The baseline indicates the value of $\mathcal{T}$ without changes to the circuit.                                                                                                                                                                                                                | 172 |

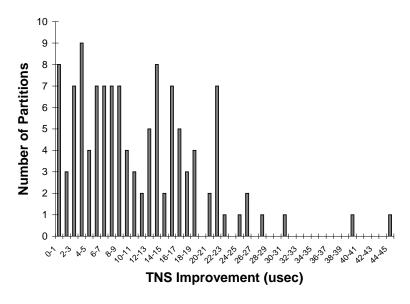

| 8.4  | A histogram of TNS improvement in partitions of a large ASIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 174 |

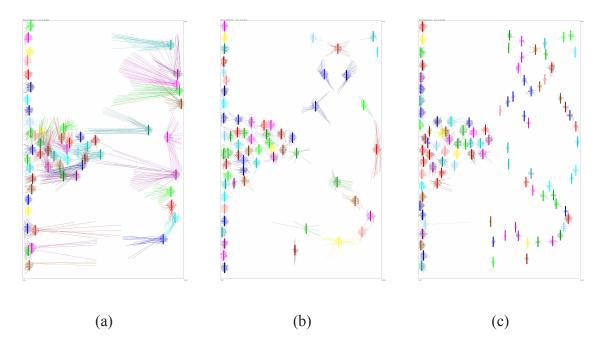

| 9.1 | The locations of cells during force-directed placement at the clockopt placement stage. (a) After one iteration of quadratic programming followed by cell spreading, a graceful spreading of cells can be observed. (b) The final placement resulting from repeating these iterations to convergence, followed by detailed placement and legalization                                                                                                                                                                                                                                                                                                                                                                                                               | 180 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

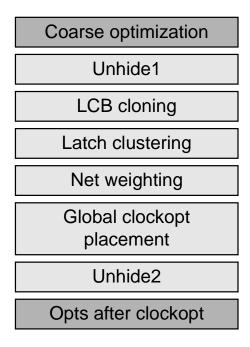

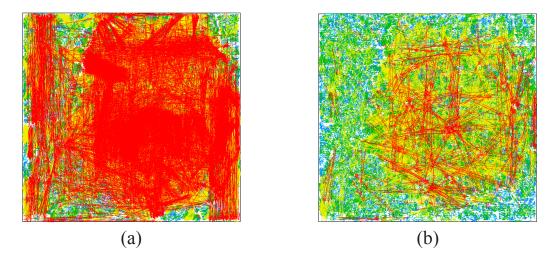

| 9.2 | The preexisting clock optimization f ow exhibits several disruptive features. During Unhide1, the last level of the clock network is exposed to timing analysis, but the latches are not yet optimized. LCB cloning creates additional LCBs to limit the fanout of each LCB and latch clustering determines which LCB will drive each latch. Global clockopt placement ignores existing locations when determining a new location for each gate. Timing is reasserted after placement in Unhide2. Finally, additional coarse optimization is performed based on new timing conditions.                                                                                                                                                                              | 182 |

| 9.3 | Our next-generation clock optimization f ow uses careful ordering of steps to avoid the largest degradations. LCB cloning creates additional LCBs to limit the fanout of each LCB and latch clustering determines which LCB will drive each latch, this is now done before clock timing is exposed. After many new LCBs are inserted, the control signals that drive them are traveling over an unoptimized high-fanout net. We optimize these control signals paths in LCB fanin opt. Incremental clockopt placement moves gates as little as possible when ensuring that latches are placed close to LCBs. Clocks timing is only exposed after the LCB to latch load is reduced to acceptable levels. Finally, coarse optimization based on mercury is performed. | 187 |

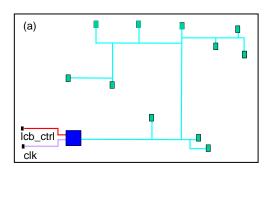

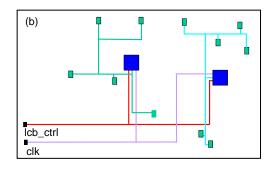

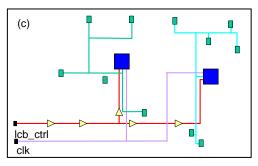

| 9.4 | An illustration of the f ow in Figure 9.3. At the beginning of clock optimization in (a) the clock is still idealized and latches are placed around the chip. In (b) local clock buffers (LCBs) are cloned and used to drive several latches each. To accommodate the timing impact of all the new LCBs, LCB control signals are optimized in (c). Global placement then moves latches close to LCBs in (d). Finally, leaf-level clock networks are inserted and clocks are unidealized.                                                                                                                                                                                                                                                                            | 188 |

| Adding LCBs (shown by vertical bars) reduces the maximum latch displacement (thin lines). This behavior is controlled by two parameters $(i)$ maximum increase in the number of LCBs, as a percentage of the minimum number $(ii)$ maximum latch displacement, with $(i)$ taking precedence over $(ii)$ . (a) The minimum number of LCBs is 56 and the maximum latch displacement is high. (b) By limiting parameter $(i)$ to 12.5% we get a maximum of 63 LCBs, and this noticeably reduces the maximum latch displacement. (c) We limit the maximum latch displacement to a tight limit using parameter $(ii)$ but relax parameter $(ii)$ and end up with low latch displacement and 100 LCBs. | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| An algorithm for length-constrained latch clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

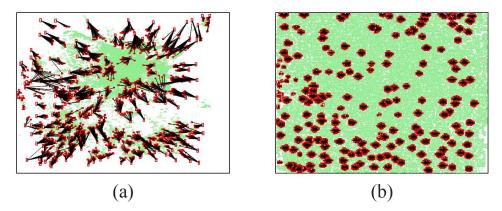

| Using incremental clockopt placement signif cantly reduces the disruption of the clockopt placement step. In each plot, a vector indicates the movement of a cell during the clockopt phase. Red vectors indicate displacements by over 500 tracks. Yellow, green and blue indicate 200, 100 and 50 tracks respectively. (a) Displacement vectors for all cells resulting from traditional force-directed placement. (b) Incremental placement reduces the number of red vectors drastically. Nearly all of the red vectors in this plot are due to latches which must be moved far to get to the nearest LCB.                                                                                   | 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

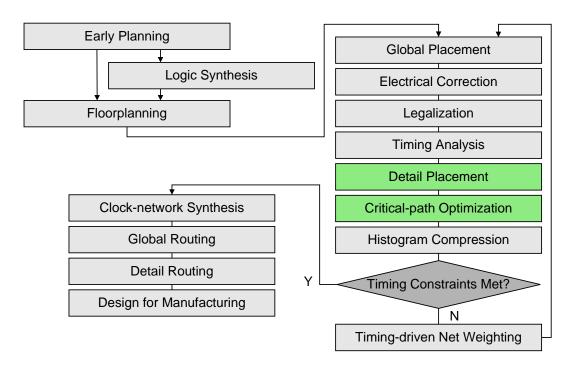

| The optimizations in this dissertation improve nearly every stage of a state-of-the-art physical synthesis f ow. For example, we illustrate that Chapter IV deals with Timing Analysis by a adding a circled 4 to that step in the f ow.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | placement (thin lines). This behavior is controlled by two parameters (i) maximum increase in the number of LCBs, as a percentage of the minimum number (ii) maximum latch displacement, with (i) taking precedence over (ii). (a) The minimum number of LCBs is 56 and the maximum latch displacement is high. (b) By limiting parameter (i) to 12.5% we get a maximum of 63 LCBs, and this noticeably reduces the maximum latch displacement. (c) We limit the maximum latch displacement to a tight limit using parameter (ii) but relax parameter (i) and end up with low latch displacement and 100 LCBs.  An algorithm for length-constrained latch clustering.  Using incremental clockopt placement signif cantly reduces the disruption of the clockopt placement step. In each plot, a vector indicates the movement of a cell during the clockopt phase. Red vectors indicate displacements by over 500 tracks. Yellow, green and blue indicate 200, 100 and 50 tracks respectively. (a) Displacement vectors for all cells resulting from traditional force-directed placement. (b) Incremental placement reduces the number of red vectors drastically. Nearly all of the red vectors in this plot are due to latches which must be moved far to get to the nearest LCB.  The optimizations in this dissertation improve nearly every stage of a state-of-the-art physical synthesis f ow. For example, we illustrate that |

# LIST OF TABLES

| <u>Table</u> |                                                                                                                                                                                                                                                                                                                             |     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1          | Keeping buffers instead of removing and reinserting them degrades RUM-BLE's performance                                                                                                                                                                                                                                     | 49  |

| 3.2          | The RUMBLE model accurately predicts the solution quality improvements in the reference timing model                                                                                                                                                                                                                        | 50  |

| 3.3          | Comparison of RUMBLE's LP to a slack-weighted center-of-gravity technique.                                                                                                                                                                                                                                                  | 52  |

| 3.4          | RUMBLE simultaneously moving a <i>one-hop</i> neighborhood compared to iteratively moving the same gates individually                                                                                                                                                                                                       | 52  |

| 3.5          | RUMBLE simultaneously moving a <i>two-hop</i> neighborhood compared to iteratively moving the same gates individually                                                                                                                                                                                                       | 53  |

| 3.6          | RUMBLE deployed in a physical design f ow on circuits that have pipeline latch placement problems. ckt1 has 2.92M objects and 629k latches and ckt2 has 4.74M objects and 247k latches. "old" reports values before RUMBLE "new" reports results after and "diff" reports their difference. FOM is reported in nanoseconds. | 55  |

| 4.1          | Types of transformations with embedded retraction. Illustrative values in the "Undo frequency" column suggest that some cases require many more retractions that other cases.                                                                                                                                               | 70  |

| 4.2          | Empirical results of bounded transactional timing analysis, with and without lazy evaluation                                                                                                                                                                                                                                | 77  |

| 5.1          | Path Smoothing Benchmarks                                                                                                                                                                                                                                                                                                   | 100 |

| 5.2          | Experimental Results on a large industrial design with a 2.2ns clock                                                                                                                                                                                                                                                        | 100 |

| 6.1          | Experimental results comparing cloning to other optimization techniques for the circuit shown in Figure 6.10.                                                                                                                                                                                                               | 129 |

| 6.2 | Experimental results comparing cloning to other optimization techniques for 100 circuits. Buffering refers to timing-driven buffering. RUMBLE refers to timing-driven gate placement followed by buffering. Clone1 refers to gate duplication with the original gate f xed. Clone2 refers to gate duplication with the original gate movable.                                                   | 134 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1 | Minimum slack $(\mathcal{M})$ and total negative slack $(\mathcal{T})$ improvement during simultaneous retiming+placement on macros of a 45nm microprocessor (see Eqns. VII.1-VII.2). Maximal $\mathcal{T}$ improvement (100%) is reached when design closes on timing. These cases are indicated in bold. $\%\mathcal{M}$ is computed as described in Equation VII.14 with $\mathcal{P}=174ps$ | 158 |

| 7.2 | Total thresholded slack $(\Theta_T)$ improvement through simultaneous retiming, cloning and placement (see Eqn. VII.3). Cloning also improved $\mathcal{M}$ on azure by 3.5%, while on remaining testcases the most-critical paths were not affected.                                                                                                                                           | 158 |

| 8.1 | Previously reported transformations and the maximum reported size of subcircuit to which they are applied                                                                                                                                                                                                                                                                                       | 162 |

| 8.2 | A comparison between window selection techniques                                                                                                                                                                                                                                                                                                                                                | 170 |

| 9.1 | Large-block synthesis benchmark characteristics. The FINAL #GATES column shows the range of possible gate counts using data from experiments presented in Tables 9.2 and 9.3.                                                                                                                                                                                                                   | 194 |

| 9.2 | The impact of individual components in the graceful f ow. TIME is the runtime of physical synthesis in seconds. WORSTSLACK is slack of the worst path in the circuit in picoseconds. $\Phi$ is calculated as in Equation IX.1 and is expressed in picoseconds. WL is the sum of half-perimeter wirelengths and is expressed in routing tracks                                                   | 196 |

| 9.3 | The impact of our graceful f ow on key design parameters. TIME is the runtime of physical synthesis in seconds. WORSTSLACK is slack of the worst path in the circuit in picoseconds. $\Phi$ is calculated as in Equation IX.1 and is expressed in picoseconds. WL is the sum of half-perimeter wirelengths and is expressed in routing tracks.                                                  | 197 |

ABSTRACT

Broadening the Scope of Multi-Objective Optimizations

in Physical Synthesis of Integrated Circuits

by

David Anthony Papa

Chair: Igor L. Markov

In modern VLSI design, physical synthesis tools are primarily responsible for satisfy-

ing chip-performance constraints by invoking a broad range of circuit optimizations, such

as buffer insertion, logic restructuring, gate sizing and relocation. This process is known

as timing closure. Our research seeks more powerful and efficient optimizations to im-

prove the state of the art in modern chip design. In particular, we integrate timing-driven

relocation, retiming, logic cloning, buffer insertion and gate sizing in novel ways to create

powerful circuit transformations that help satisfy setup-time constraints.

State-of-the-art physical synthesis optimizations are typically applied at two scales: i)

global algorithms that affect the entire netlist and ii) local transformations that focus on

a handful of gates or interconnections. The scale of modern chip designs dictates that

only near-linear-time optimization algorithms can be applied at the global scope — typi-

cally limited to wirelength-driven placement and legalization. Localized transformations

can rely on more time-consuming optimizations with accurate delay models. Few tech-

niques bridge the gap between fully-global and localized optimizations. This dissertation

xviii

broadens the scope of physical synthesis optimization to include accurate transformations operating between the global and local scales. In particular, we integrate groups of related transformations to break circular dependencies and increase the number of circuit elements that can be jointly optimized to escape local minima.

Integrated transformations in this dissertation are developed by identifying and removing obstacles to successful optimizations. Integration is achieved through mapping multiple operations to rigorous mathematical optimization problems that can be solved simultaneously. We achieve computational scalability in our techniques by leveraging analytical delay models and focusing optimization efforts on carefully selected regions of the chip. In this regard, we make extensive use of a linear interconnect-delay model that accounts for the impact of subsequent repeated insertion. Our integrated transformations are evaluated on high-performance circuits with over 100,000 gates.

Integrated optimization techniques described in this dissertation ensure graceful timingclosure process and impact nearly every aspect of a typical physical synthesis f ow. They have been validated in EDA tools used at IBM for physical synthesis of high-performance CPU and ASIC designs, where they signif cantly improved chip performance.

# **PART I**

# **Introduction and Prior Art**

#### **CHAPTER I**

# Timing Closure for Multi-Million-Gate Integrated Circuits

Sophisticated integrated circuits (ICs) can be classif ed as processors (CPUs), application-specif c integrated circuits (ASICs) or systems-on-a-chip (SoCs), which embed CPUs and intellectual property blocks into ASICs. Mass-produced on silicon chips, these circuits fuel consumer and industrial electronics, maintain national and international computer networks, coordinate transportation and power grids, and ensure the competitiveness of military systems. The design of new integrated circuits requires sophisticated optimization algorithms, software and methodologies — collectively called Electronic Design Automation (EDA) — which leverage synergies between Computer Science, Computer Engineering and Electrical Engineering. From the algorithmic perspective, a number of NP-hard problems need to be solved quickly in practice, while their instances grow year after

year with Moore's law. From the software perspective, multiple optimizations must operate on sophisticated design databases and coordinate to ensure consistent results over a large variety of chip designs. Electrical-engineering aspects of EDA emphasize physical characteristics of integrated circuits, such as speed-of-light limitations observed in large, high-speed chips manufactured at sub-65nm technology nodes.

### 1.1 Challenges in Physical Synthesis

State-of-the-art automated IC design f ows begin at a planning stage with rough estimates of chip performance and cost. During this stage, a block-level layout or *floorplan* of the chip is determined. Next, designers describe the function of the chip using a hardware description language (HDL), such as Verilog or VHDL. A logic synthesis tool is run on the HDL code to create a mapped netlist that implements the design in the target standard-cell library. Timing analysis can then calculate crude, optimistic estimates of chip performance, and the HDL code can be improved until it passes this sanity check.

The physical synthesis stage begins after logic synthesis produces a gate-level netlist that meets agreed performance targets under optimistic timing conditions. A physical synthesis tool reads the netlist, creates an overlap-free placement of gates, and proceeds to optimize circuit performance. During physical synthesis, the availability of gate locations enables more accurate interconnect-delay modeling in timing analysis. Common physical synthesis operations include inserting or removing buffers and inverters, resynthesizing small windows, increasing and decreasing gate sizes, as well as relocating gates. When a design meets its performance constraints, it is said to *have closed on timing*. When physical synthesis is unable to achieve timing closure, designers must study the tool's logs and

the optimized circuit then manually generate additional constraints to guide the optimization process. More substantial timing-closure difficulties can cause an expensive return to the logic synthesis stage, necessitate f oorplanning changes or even require changes in the HDL code.

Designs that have passed timing checks during physical synthesis, transition into the routing stage, where more accurate timing models are available and new timing-closure problems may arise. Failure to route or meet timing constraints at this stage can again cause a return to earlier stages and further iterations. Finally, post-routing optimizations address any timing-closure issues that remain after routing, such as changing wire layers to reduce variability, moving detailed routes to reduce cross-talk, or adding redundant vias to improve manufacturing yield.

Challenges. Aggressive scaling of transistor dimensions according to Moore's Law has historically driven performance improvements of CMOS-based integrated circuits (ICs). This trend has been so successful that now the greater part of critical path delay is no longer in the transistors that compose logic gates — delay through signal nets and repeaters now dominates [101]. As a result, logic synthesis can no longer estimate design performance effectively without physical information. A relatively recent solution, physical synthesis optimization algorithms employ a complex, multi-phase process that combines netlist optimization, placement, routing and timing analysis [7,8,112]. Physical synthesis optimization algorithms are primarily designed to achieve timing closure, but there are other important objectives such as reducing wirelength, area and power consumption while maintaining routability.

Another consequence of technology scaling trends gives IC designers more transistors at their disposal, which leads to increased design size and complexity. Today's ICs have tens of millions of gates and each design has its own performance requirements, which include reducing power consumption, satisfying area bounds and increasing manufacturing yield. A physical synthesis tool must accommodate these requirements as well as ensure that basic physical constraints are met, such as producing a legal, routable placement. As a result, throughout the physical synthesis f ow *multiple objectives* are always present and must be optimized simultaneously.

Several prior publications formulate non-linear, multi-objective optimization problems and solve them with some success [109], but these algorithms typically exhibit superlinear runtime complexity and do not scale well enough to optimize an entire modern VLSI design at once. Other approaches focus on a handful of gates, and apply more time-consuming algorithms to relocate several gates at once, increase drive strength, or insert buffers to improve performance [10,112,114]. However, these approaches are limited in scope and only near-linear-time algorithms such as *wirelength-driven placement* can be applied at a truly global scope. For example, the scope of *timing-driven gate relocation* is typically limited to f nding new positions for a handful of gates so as to improve the delay of incident paths. Few techniques are available between the global and local scopes, but resynthesis is a notable exception. While logic synthesis techniques are applied to more than a few gates at once, the delay estimations considered at that scale do not typically utilize all of the physical information available and are therefore less accurate [87]. Con-

<sup>&</sup>lt;sup>1</sup>This is in contrast to *timing-driven placement*, which in previous literature usually refers to the application of net weights during placement that are based on timing information. Here we are referring to the detailed placement of a small number of gates while interacting incrementally with a timing analysis engine.

sequently, in state-of-the-art physical synthesis tools there is a large gap between the scope of accurate, local transformations and coarse, global transformations.

More recently, a trend toward integration of such *point optimizations* as repowering, buffering, and timing-driven detailed placement has gained strength. Increasing the scope of such *compound transformations* to close the aforementioned gap while maintaining acceptable runtime and accuracy remains a challenging research problem. It is unclear *a priori* if established techniques based on static timing analysis and single-objective optimizations remain sufficient in the context of physical synthesis for sub-45nm ICs. To this end, Chapter IX reports successful experiments with 32nm and 22nm designs.

#### 1.2 Our Contributions