# Delivering Affordable Fault-tolerance to Commodity Computer Systems

by

Shuguang Feng

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2011

### **Doctoral Committee:**

Associate Professor Scott Mahlke, Chair Professor David Blaauw Professor Trevor N. Mudge Professor Dennis M. Sylvester Assistant Professor Thomas Wenisch Pradip Bose, IBM T.J. Watson © Shuguang Feng 2011

All Rights Reserved

To my parents Jinan and Pinfang.

#### **ACKNOWLEDGEMENTS**

Over the last few years there have been many moments when I felt that this dissertation would never be written. The fact that I can now place the finishing touches on this document means that there is no shortage of people to whom I owe a great debt of gratitude. Since I cannot possibly list all those that have blessed my time in Ann Arbor, I encourage everyone that I have omitted to track me down, so that I might apologize over a meal the next time we meet.

First I would like to thank my advisor, Scott Mahlke. His expert guidance and passion for his work were crucial to my success. The existence of this dissertation owes itself, in large part, to Scott's drive and unshakable optimism, which on many occasions resurrected research directions I had already resigned to abandon. Although we often disagreed, his eagerness to debate ideas and willingness to entertain dissent left an indelible mark on my approach to problem solving.

I also want to thank Jason Blome and Eric Karl who played an instrumental role in the early months of my graduate career. Their advice and guidance as I took my initial steps into academic research was invaluable.

Next, I would like to thank Shantanu Gupta and Amin Ansari. Having endured countless hours of meetings, and endless rounds of paper revisions, these two have become more than simply co-authors. Collaborating on nearly all of our work, we have witnessed each others' failures as well as shared in each others' successes.

I would also like to thank the members (and honorary members) of the CCCP research group. I have often felt that graduate school was as much about maintaining one's sanity as it was about conducting innovative research. Whether it was our infamous coffee breaks, or seemingly random office discussions ranging from Middle East politics to Russell Peters, my labmates provided plenty of much-needed distractions.

I am also grateful to the amazing friends I made through Harvest and Knox. It is hard for me to imagine being able to survive the last few years without these friendships to remind me that there does actually exist a world outside of the office. I would especially like to thank Greg ("Magnum Opus") Davidson, Erik Kim, Manoj Cheriyan, and Matthew Remy for sharing their Ph.D. experiences with me, and showing me that, despite what trials may come, it is always possible to remember who holds tomorrow.

I also want to thank Grace Hwang for putting up with me for the last four years. Despite not seeing each other for weeks, sometimes months, at a time, she has been an encouragement throughout this Ph.D. journey. Her patience with me during particularly stressful weeks was a wonderful comfort, allowing me to selfishly vent over the phone while keeping things in perspective. Although never ideal, Grace made juggling a long-distance relationship as painless as I had any right to hope for.

Finally, I would like to thank my parents. They have sacrificed so much for me and my sister. I may never truly appreciate, much less acknowledge, the extent of their love and commitment to us. The chance to write this thesis is simply one in a long series of opportunities afforded to me because of their sacrifice.

# TABLE OF CONTENTS

| <b>DEDICATION</b> |                                                    |

|-------------------|----------------------------------------------------|

| ACKNOWLED         | GEMENTS                                            |

| LIST OF FIGU      | RES viii                                           |

| LIST OF TABL      | ES xii                                             |

| ABSTRACT          |                                                    |

| CHAPTER           |                                                    |

| I. Introd         | uction                                             |

| 1.1               | Dependable Computing for the Masses                |

| 1.2               | Reliability Taxonomy                               |

|                   | 1.2.1 Threats to Reliable Computing                |

|                   | 1.2.2 Anatomy of Fault-tolerant Computing 5        |

| 1.3               | Conventional Solutions                             |

| 1.4               | Contributions                                      |

| II. Self-ca       | dibrating Online Wearout Detection                 |

| 2.1               | Introduction                                       |

| 2.2               | Device-level Wearout Analysis                      |

|                   | 2.2.1 Gate Oxide Breakdown                         |

|                   | 2.2.2 HSPICE Analysis                              |

| 2.3               | Microarchitecture-level Wearout Analysis           |

|                   | 2.3.1 Microprocessor Implementation                |

|                   | 2.3.2 Power, Temperature, and MTTF Calculations 22 |

|                   | 2.3.3 Wearout Simulation                           |

| 2.4               | Wearout Detection                                  |

|                   | 2.4.1 Online Delay Profiling                       |

|                   | 2.4.2 Failure Prediction Algorithm                 |

|            | 2.4.3 Implementation Details                                     | 31         |

|------------|------------------------------------------------------------------|------------|

| 2.5        | Experimental Analysis                                            |            |

|            | 2.5.1 Overhead and Accuracy                                      |            |

|            | 2.5.2 Dynamic Variations                                         | 37         |

| 2.6        | Related Work                                                     | 39         |

| 2.7        | Summary                                                          | 41         |

|            |                                                                  |            |

| III. Maest | ro: Orchestrating Lifetime Reliability in Chip Multiprocessors . | 42         |

| 3.1        | Introduction                                                     | 42         |

| 3.2        | Scheduling for Damaged Cores and Dynamic Workloads               | 45         |

|            | 3.2.1 Failure Mechanism Review                                   | 46         |

|            | 3.2.2 Existing Scheduling Schemes                                | 47         |

|            | 3.2.3 Workload Variation                                         | 50         |

|            | 3.2.4 Implications for Mean Time to Failure                      | 53         |

| 3.3        | System Design                                                    | 54         |

|            | 3.3.1 Health Monitoring                                          | 54         |

|            | 3.3.2 Maestro Virtualization Layer                               | 55         |

| 3.4        | Evaluation and Analysis                                          | 64         |

|            | 3.4.1 Adaptive Lifetime Simulation                               | 65         |

|            | 3.4.2 Lifetime Throughput Enhancement                            | 67         |

|            | 3.4.3 Failure Distributions                                      | 69         |

|            | 3.4.4 Sensitivity to System Utilization                          | 71         |

|            | 3.4.5 Sensitivity to Sensor Noise                                | 72         |

|            | 3.4.6 Sensor Selection                                           | 73         |

| 3.5        | Summary                                                          | 74         |

|            |                                                                  | , .        |

| IV. Shoest | ring: Probabilistic Soft Error Reliability on the Cheap          | 75         |

| 4.1        | Introduction                                                     | 75         |

| 4.2        | Background and Motivation                                        |            |

|            | 4.2.1 Soft Error Rate                                            | 78         |

|            | 4.2.2 Solution Landscape and Shoestring                          | 80         |

| 4.3        | System Design                                                    | 83         |

|            | 4.3.1 Compiler Overview                                          | 86         |

|            | 4.3.2 Preliminary Classification                                 | 87         |

|            | 4.3.3 Vulnerability Analysis                                     | 89         |

|            | 4.3.4 Code Duplication                                           | 94         |

| 4.4        | Experimental Methodology                                         | 96         |

| 1. 1       | 4.4.1 Fault Model and Injection Framework                        | 97         |

|            | 4.4.2 Outcome Classification                                     | 99         |

|            |                                                                  | رر<br>100  |

| 4.5        | Evaluation and Analysis                                          |            |

| 7.3        | 4.5.1 Preliminary Fault Injection                                |            |

|            | , , , , , , , , , , , , , , , , , , ,                            | 102<br>104 |

|           | 4.5.3      | Overheads and Fault Coverage             |     |

|-----------|------------|------------------------------------------|-----|

| 4.6       |            | Vork                                     |     |

| 4.7       | Summary    |                                          | 112 |

| V. Encore | e: Low-cos | t, Fine-grained Transient Fault Recovery | 114 |

| 5.1       | Introducti | on                                       | 114 |

| 5.2       | Recoverir  | ng from Transient Faults                 | 118 |

|           | 5.2.1      | Recovery with Fine-grained Re-execution  | 119 |

|           | 5.2.2      | The Role of Idempotence                  | 122 |

| 5.3       | Encore .   |                                          | 123 |

|           | 5.3.1      | Identifying Inherent Idempotence         | 125 |

|           | 5.3.2      | Instrumentation                          | 131 |

|           | 5.3.3      | Region Formation                         | 132 |

|           | 5.3.4      | Encore Heuristics                        | 134 |

| 5.4       | Experime   | ntal Methodology                         |     |

|           | 5.4.1      | Compilation Framework                    | 137 |

|           | 5.4.2      | Recoverability Coverage Model            | 137 |

|           | 5.4.3      | Performance Modeling                     |     |

| 5.5       | Evaluation | n and Analysis                           | 139 |

|           | 5.5.1      | Region Idempotence                       |     |

|           | 5.5.2      | Dynamic Execution Breakdown              |     |

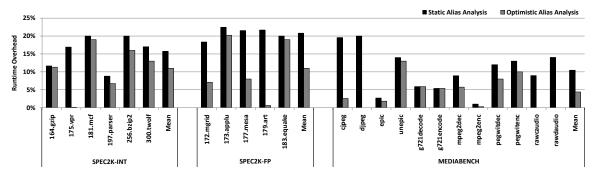

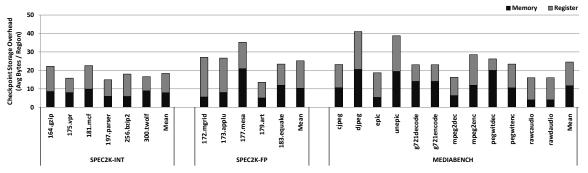

|           | 5.5.3      | Overheads                                | 142 |

|           | 5.5.4      | Full-system Reliability                  |     |

| 5.6       | Related V  |                                          |     |

|           | 5.6.1      | Fault Detection                          | 146 |

|           | 5.6.2      | System Recovery                          | 146 |

| 5.7       | Summary    |                                          | 148 |

| . Conclu  | ısion      |                                          | 150 |

|           |            |                                          |     |

| CRAPI     | IV         |                                          | 153 |

# LIST OF FIGURES

| <b>Figure</b> |                                                                                                                                                                                                                                                                                                                                  |    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

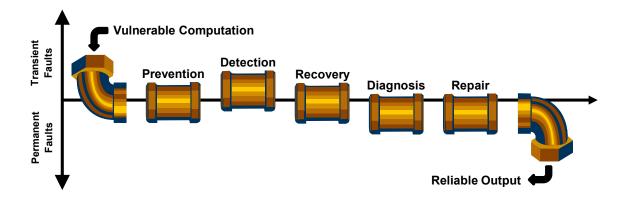

| 1.1           | A "reliability pipeline" depicting the different pieces of a comprehensive reliability strategy. The relative location of each component to the transient-permanent boundary represents the extent to which recent research into transient (wearout-induced permanent) faults has studied that particular aspect of reliability. | ć  |

| 2.1           | Impact of OBD-induced oxide leakage current on standard cell propagation delays.                                                                                                                                                                                                                                                 | 17 |

| 2.2           | HSPICE simulation traces for inverter with degraded PMOS (slowdown).                                                                                                                                                                                                                                                             | 18 |

| 2.3           | HSPICE simulation traces for inverter with degraded PMOS (speedup)                                                                                                                                                                                                                                                               | 19 |

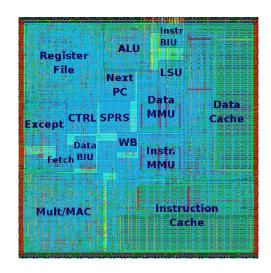

| 2.4           | OpenRisc1200 embedded microprocessor                                                                                                                                                                                                                                                                                             | 22 |

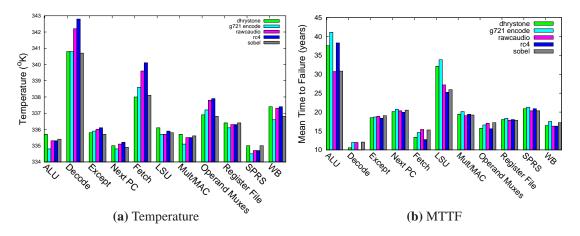

| 2.5           | Derived workload-dependent steady state temperature and MTTF for the OR1200 CPU core. An ambient temperature of 333 <i>K</i> was used for Hotspot.                                                                                                                                                                               |    |

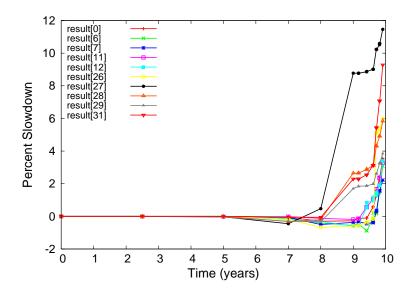

| 2.6           | The observed slowdown of signals from the ALU result bus as a result of OBD effects over the lifetime of one instance of an OR1200 processor core.                                                                                                                                                                               | 26 |

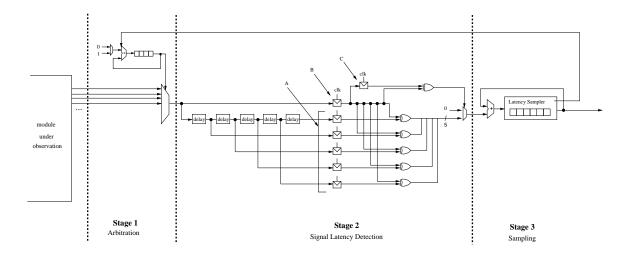

| 2.7           | Online delay profiling unit                                                                                                                                                                                                                                                                                                      | 28 |

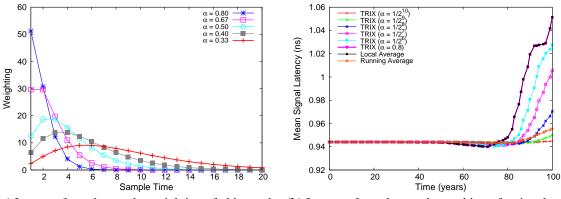

| 2.8           | Sensitivity analysis of TRIX parametrization.                                                                                                                                                                                                                                                                                    | 31 |

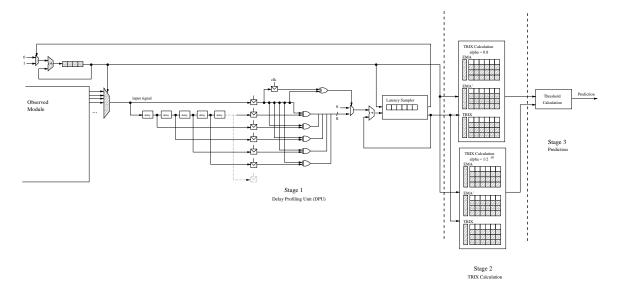

| 2.9           | Design and organization of the wearout detection unit                                                                                                                                                                                                                                                                            | 32 |

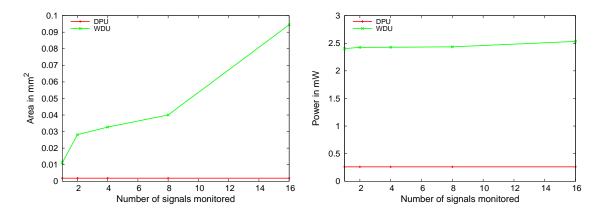

| 2.10          | Scaling of the WDU and DPU area and power as the number of signals                                                                                                                                                                                                                                                               |    |

|               | monitored scales                                                                                                                                                                                                                                                                                                                 | 35 |

| 2.11          | Analysis of TRIX analysis efficacy in predicting failure                                                                                                                                                                                                                                                                         | 36 |

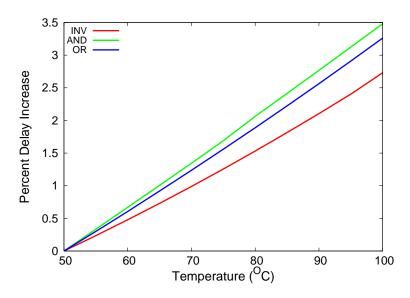

| 2.12          | Impact of temperature on logic gate delay                                                                                                                                                                                                                                                                                        | 38 |

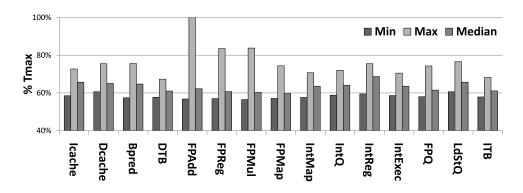

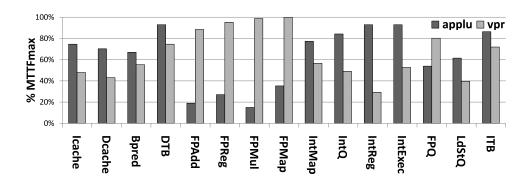

| 3.1           | Variation of module temperatures across SPEC2000 workloads. All temperatures are normalized to $T_{max}$ , the peak temperature seen across all                                                                                                                                                                                  |    |

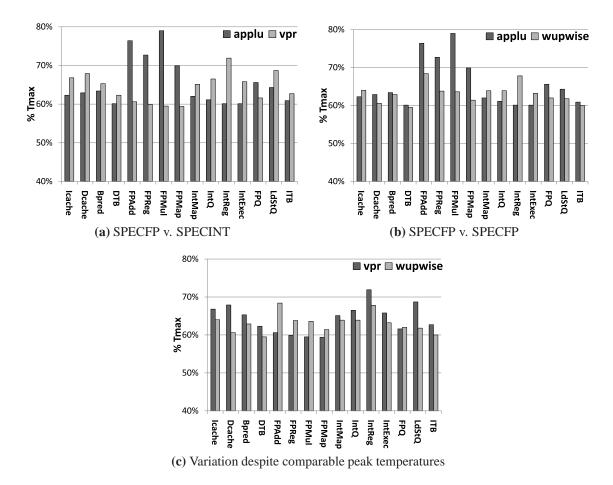

| 3.2           | benchmarks and modules (83°C)                                                                                                                                                                                                                                                                                                    | 51 |

| 3.2           | wise (SPECFP). No one benchmark in (a), (b), or (c) strictly dominates                                                                                                                                                                                                                                                           |    |

|               | the other (with respect to temperature) across all modules                                                                                                                                                                                                                                                                       | 52 |

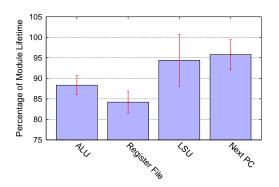

| 3.3           | Projected core lifetime based on execution of <i>applu</i> and <i>vpr</i> as a function of the module identified as the weakest structure. Values are normalized                                                                                                                                                                 |    |

|               | to the best achievable MTTF                                                                                                                                                                                                                                                                                                      | 54 |

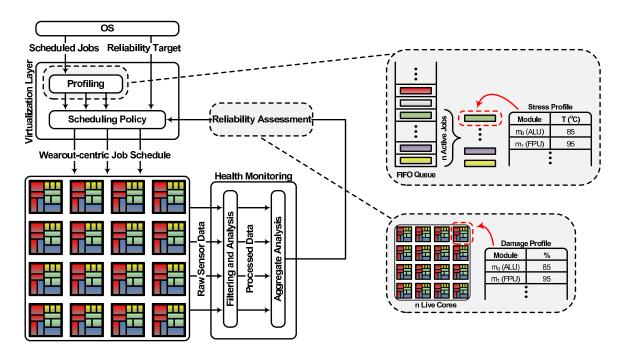

| 3.4  | A high-level block diagram of the Maestro introspective reliability management system. Dynamic monitoring of sensor feedback and detailed characterization of workload behavior enables Maestro to improve lifetime system reliability with wearout-centric scheduling                                                                                                                                                                                                | 56       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

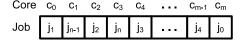

| 3.5  | Chromosome structure                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

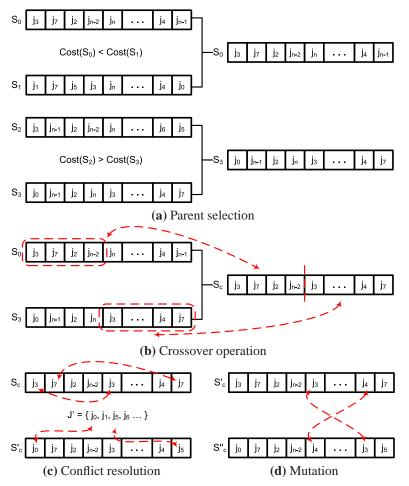

| 3.6  | Steps involved in reproduction. $S_0, S_1, S_2, S_3$ are the parental candidates. $S_c$ is the resulting child chromosome after initial crossover. $S'_c$ and $S''_c$ are the states of the child chromosome after conflicts resolution and mutation respectively                                                                                                                                                                                                     |          |

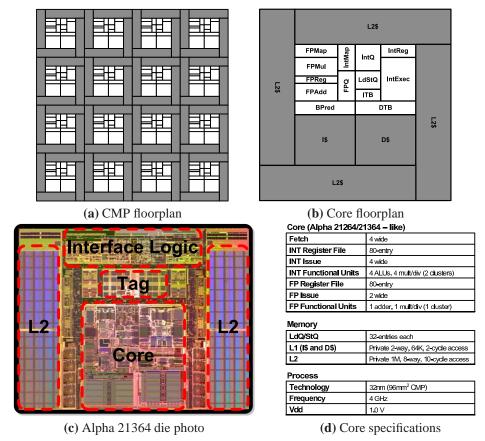

| 3.7  | CMP details. All simulation results, unless otherwise stated, are presented for a CMP configured with 16 cores.                                                                                                                                                                                                                                                                                                                                                       | 65       |

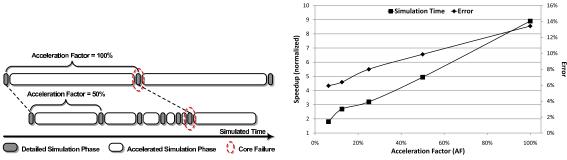

| 3.8  | The adaptive simulation used to accelerate lifetime reliability simulations while incurring minimal experimental error.                                                                                                                                                                                                                                                                                                                                               | 67       |

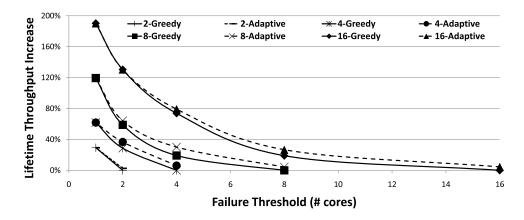

| 3.9  | Performance of wearout-centric scheduling policies verses CMP size and failure threshold.                                                                                                                                                                                                                                                                                                                                                                             | 68       |

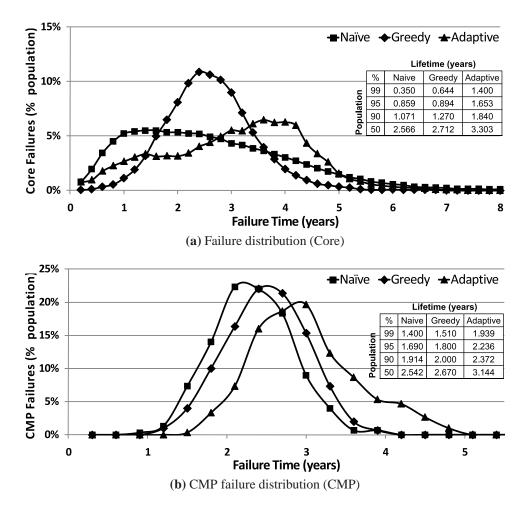

| 3.10 | Failure distributions for individual cores and the 16-core CMP with a failure threshold of 8 cores and 100% utilization. Trendlines are added (between morters) to improve readability.                                                                                                                                                                                                                                                                               | 70       |

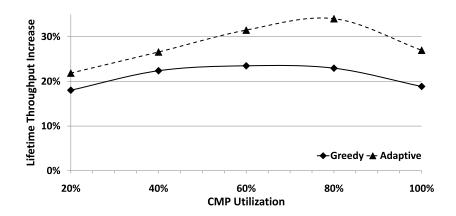

| 3.11 | (between markers) to improve readability                                                                                                                                                                                                                                                                                                                                                                                                                              | 70<br>71 |

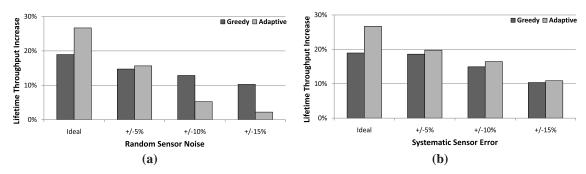

| 3.12 | Sensitivity to sensor noise. Although random sensor noise can be removed with the appropriate filtering, systematic error due to manufactur-                                                                                                                                                                                                                                                                                                                          | /1       |

|      | ing tolerances is more problematic                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73       |

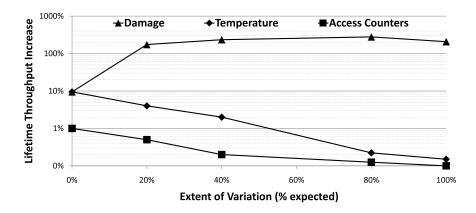

| 3.13 | Performance of wearout-centric scheduling with different sensors. Results are shown for a failure threshold of 1 core to favor the temperature sensor and access counter based approaches                                                                                                                                                                                                                                                                             | 73       |

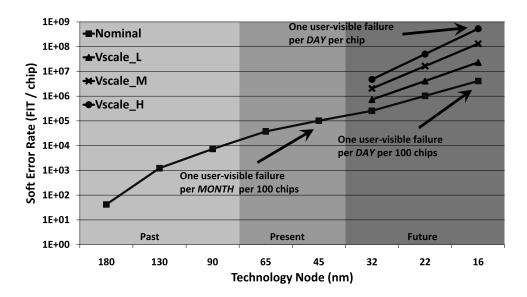

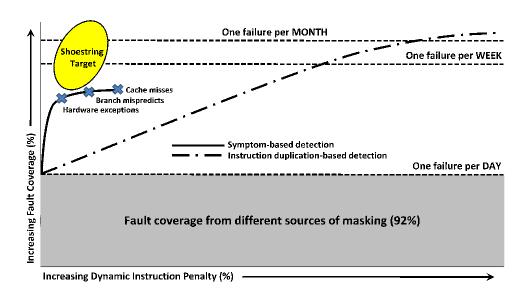

| 4.1  | The soft error rate trend for processor logic across a range of silicon technology nodes. The <i>Nominal</i> curve illustrates past and present trends while the <i>Vscale_L</i> , <i>Vscale_M</i> , and <i>Vscale_H</i> curves assume low, medium and high amounts (respectively) of voltage scaling in future deep submicron technologies. The user-visible failure rates highlighted at $45 nm$ and $16 nm$ are calculated assuming a 92% system-wide masking rate |          |

| 4.2  | Fault coverage versus dynamic instruction penalty trade-off for two existing fault detection schemes: symptom-based detection and instruction duplication-based detection. Also indicated is the region of the solution space targeted by Shoestring. The mapping of fault coverage to uservisible failure rate (dashed horizontal lines) is with respect to a single chip in a $16  nm$ technology node with aggressive voltage scaling (Vscale_H).                  | 81       |

| 4.3  | A representative example of performance optimized code (loop unrolled).                                                                                                                                                                                                                                                                                                                                                                                               | 84       |

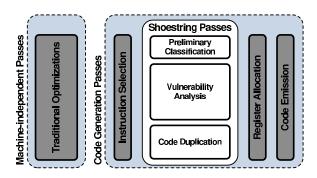

| 4.4  | A standard compiler flow augmented with Shoestring's reliability-aware code generation passes.                                                                                                                                                                                                                                                                                                                                                                        | 85       |

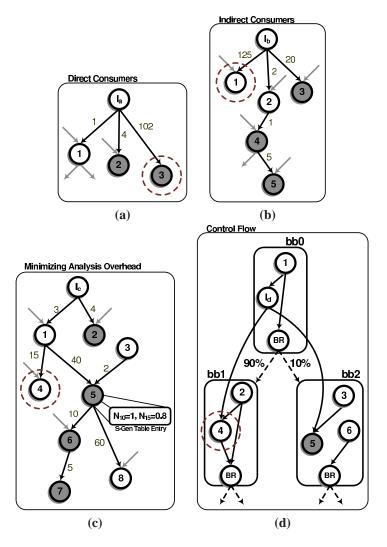

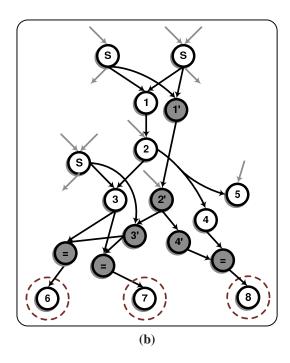

| 4.5  | Example data flow graphs illustrating Shoestring's vulnerability analysis.  The data flow edge numbers represent the distance between two instructions in the statically scheduled code. Shaded nodes represent symptom-generating instructions and dashed circles highlight high-value instructions. Dashed edges in (d) represent control flow                           | 00 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

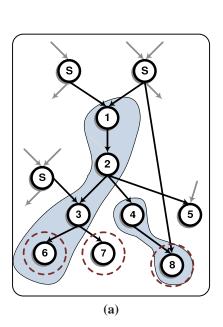

| 4.6  | Example data flow graph illustrating Shoestring's code duplication pass. Nodes labeled with an "S" represent safe instructions and dashed circles highlight high-value instructions. In (a) the shaded portions of the graph represent code duplication chains. (b) shows the new DFG with all duplicated instructions inserted as shaded nodes. Nodes labeled with an "=" |    |

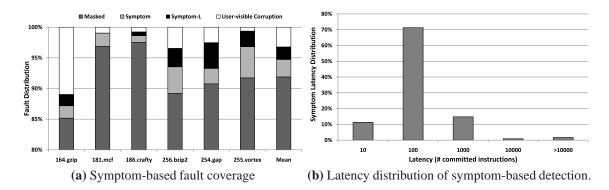

| 4.7  | represent checker instructions                                                                                                                                                                                                                                                                                                                                             | 13 |

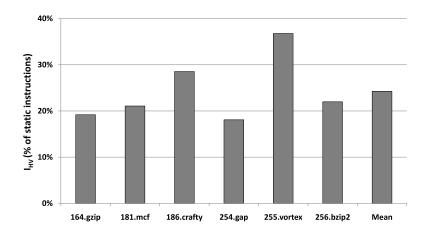

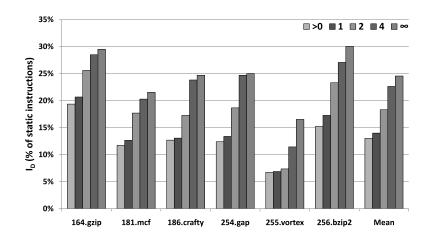

| 4.8  | Percentage of static instructions classified as high-value $(I_{HV})$ 10                                                                                                                                                                                                                                                                                                   |    |

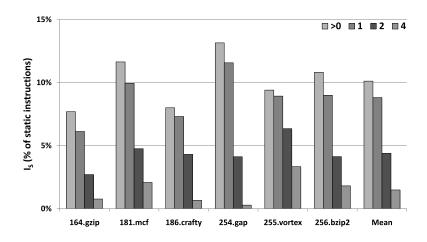

| 4.9  | Percentage of static instructions classified as safe as $S_t$ is varied $(I_S)$ 10                                                                                                                                                                                                                                                                                         |    |

| 4.10 | Percentage of static code duplication performed by Shoestring as $S_t$ is varied $(I_D)$                                                                                                                                                                                                                                                                                   |    |

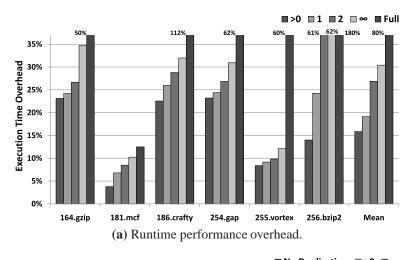

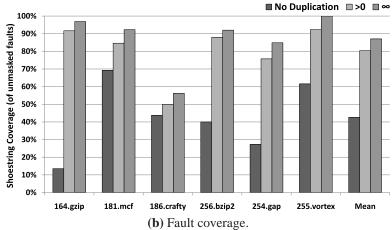

| 4.11 | Fault coverage and runtime performance overheads for Shoestring as a                                                                                                                                                                                                                                                                                                       |    |

| 4.10 | function of $S_t$                                                                                                                                                                                                                                                                                                                                                          | /  |

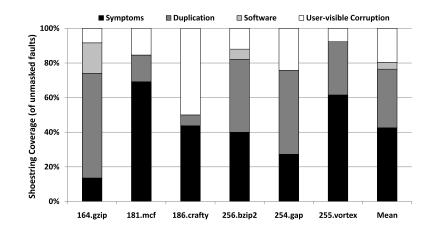

| 4.12 | Detailed coverage breakdown for Shoestring configured with $S_t$ fixed at $>010$                                                                                                                                                                                                                                                                                           | 8  |

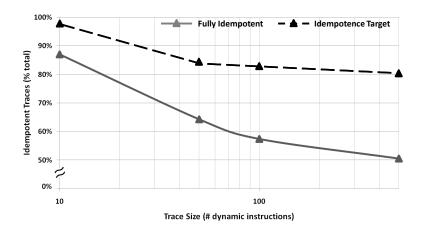

| 5.1  | Percentage of dynamic instruction traces that are inherently idempotent as a function of size. The execution traces were extracted from an assortment of SPEC2K and Mediabench workloads. The <i>Idempotence Target</i> curve illustrates Encore's goal of exposing, and exploiting, even greater degrees of idempotence through intelligent compiler analysis and trans-  |    |

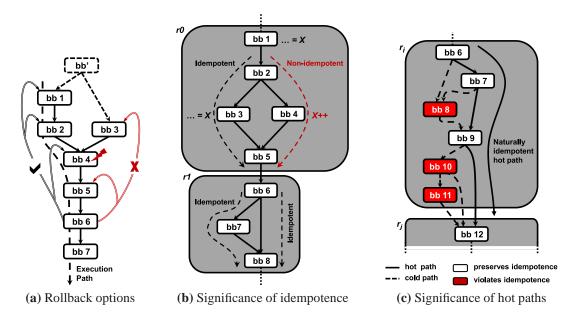

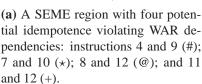

| 5.2  | formations                                                                                                                                                                                                                                                                                                                                                                 | 6  |

|      | ist when leveraging fine-grained re-execution to achieve fault recovery. (a) enumerates potential rollback destinations that execution can be redirected to once a fault, striking at $bb_4$ is detected, at $bb_6$ . Ideally $bb_1$ and                                                                                                                                   |    |

|      | $bb_3$ would share a common predecessor $bb'$ that could serve as the rollback destination for all faults that are detected within the region. (b) highlights                                                                                                                                                                                                              |    |

|      | how idempotence violating instructions might constrain which code re-                                                                                                                                                                                                                                                                                                      |    |

|      | gions can actually be efficiently recovered. (c) depicts how otherwise<br>non-idempotent regions can still frequently exhibit idempotent behavior                                                                                                                                                                                                                          |    |

|      | along their hot paths. The region shown in (c) is taken from the CFG corresponding to the dominant hot function in <i>175.vpr</i>                                                                                                                                                                                                                                          | 0  |

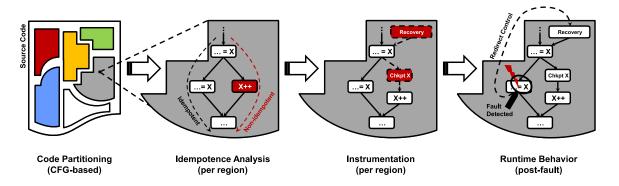

| 5.3 | High-level Encore vision. At compile-time, application code is partitioned into SEME regions that are subsequently analyzed and instrumented to enable low-cost rollback recovery from transient faults. Flexible heuristics enable Encore to refine the partitioning and instrumentation.                                                                                                                                                                                                                                                    |       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | tion passes, customizing their behavior to achieve the desired tradeoff between reliability and performance overheads                                                                                                                                                                                                                                                                                                                                                                                                                         | . 124 |

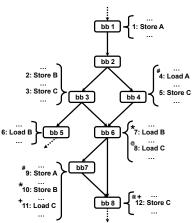

| 5.4 | Example illustrating Encore's idempotence analysis. Only the relevant instructions within each basic block are shown in (a). (b) shows how the data structures in Equation 5.1 and Equations 5.2-5.3 are populated dur-                                                                                                                                                                                                                                                                                                                       | . 121 |

|     | ing the in-order traversal and reverse in-order traversal of the subgraph, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 128 |

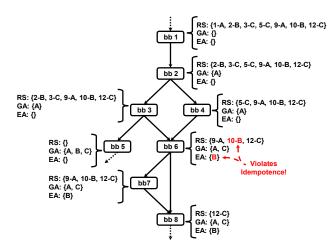

| 5.5 | Inherent region idempotence as a function of $P_{min}$ . From left to right, the columns illustrate the fraction of regions within each application that is inherently idempotent for different values of $P_{min} \in \{\emptyset, 0.0, 0.1, 0.25\}$ . With $P_{min} = \emptyset$ , the left-most column for each application depicts the idempotence breakdown when no dynamically-dead code is pruned from the analysis. The $Unknown$ segments correspond to portions of the application source code that could not be analyzed by Encore |       |

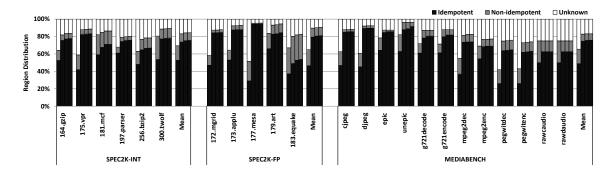

| 5.6 | Breakdown of dynamic execution time. For each application the stacks represent the fraction of execution time spent within regions of the code that were inherently idempotent, non-idempotent but instrumented with selective checkpointing by Encore, and non-idempotent but too costly to                                                                                                                                                                                                                                                  |       |

|     | checkpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 5.7 | Encore runtime and storage overheads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 143 |

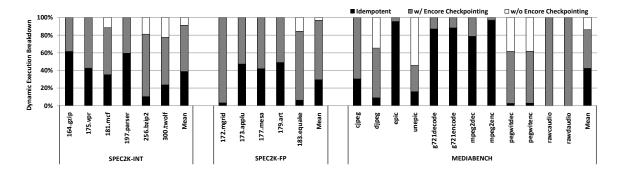

| 5.8 | Full-system fault coverage for a low-cost commodity system using Encore for rollback recovery and fault detection schemes with different latencies. From left to right, the columns represent the % of all transient fault events that can be effectively tolerated given a system with detection latencies of 1000, 100, and 10 instructions.                                                                                                                                                                                                | . 144 |

## LIST OF TABLES

####

5.1

**ABSTRACT**

Delivering Affordable Fault-tolerance to Commodity Computer Systems

by

Shuguang Feng

Chair: Scott Mahlke

To meet an insatiable consumer demand for greater performance at less power, silicon tech-

nology has scaled to unprecedented dimensions. This aggressive scaling has provided de-

signers with an ever increasing budget of cheaper and faster transistors. Unfortunately, this

trend has also been accompanied by a decline in individual device reliability as transistors

have become increasingly susceptible to a host of threats.

With each new technology generation the challenges associated with process variation,

wearout, and transient faults gain greater prominence. We are quickly approaching a new

era where fault-tolerance is becoming a first-order design constraint, no longer a luxury

reserved exclusively for high-reliability, mission-critical domains. Even commodity mi-

croprocessors used in mainstream computing will require protection.

However, just as the reliability needs of NASA and Apple differ dramatically, so does

their ability to absorb the costs necessary to ensure fault-tolerance. Viable solutions tar-

xiii

geting commodity systems must not only recognize this fact, but must embrace it. Simply stripping down techniques developed for enterprise servers may not result in the most appropriate designs for your laptop or cellphone. The best solutions will exploit the relaxed reliability constraints of commodity systems, judiciously sacrificing a small degree of fault-tolerance to achieve far greater reductions in overhead costs.

This thesis proposes a collection of works that can be selectively mixed and matched to assemble reliability solutions tailor-fit for the commodity systems community. Although the works presented address a variety of different issues from wearout to transient faults and prevention to detection, they were all motivated by the same observation—that much of the overhead costs associated with conventional fault tolerance mechanisms are spent in pursuit of the last few "nines" of reliability. This conclusion gave rise to the philosophy permeating the chapters of this work, that summarily dismissing techniques that cannot supply *mission-critical* fault tolerance is no longer acceptable. In presenting concrete solutions to a few of the more interesting challenges—proactive wear-leveling orchestrated through intelligent job scheduling and software-only transient fault detection and recovery that exploits intrinsic computational patterns within applications—we establish fundamental principles that can be applied more broadly to formulate a comprehensive reliability strategy.

## **CHAPTER I**

## Introduction

Given the recent news coverage of the high-profile Toyota recalls and similar articles chronicling Apple's antenna woes on their newly released iPhone, the reliability, or perhaps more appropriately the *unreliability*, of computer systems has taken center stage. Although culpability in these headlining stories may not rest solely on the shoulders of faulty microprocessors, the public response to these events has highlighted the frustration that can arise when computers, and the systems they are associated with, do not function as advertised.

# 1.1 Dependable Computing for the Masses

With hundreds, sometimes thousands, of dollars being spent on the latest piece of consumer electronics the computers that power them are expected to perform tasks not only quickly, but also reliably. Whether they are trading stocks from a laptop or watching the latest YouTube video on an iPhone, users expect their experience to be fault-free. Although the occasional dropped call or "blue screen of death" may be overlooked, the average con-

sumer has grown accustomed to the (nearly) fault-free enjoyment of their electronic devices.

Unfortunately, the course of aggressive technology scaling being undertaken by industry is exposing new sources of unreliability and exacerbating old ones. Whether we are talking about manufacturing defects resulting in chips that are dead-on-arrival, process variation leading to dynamic heterogeneity, wearout constraining device lifetimes, or soft-errors periodically corrupting computation, the reliability threats faced by modern microprocessors are as diverse as they are challenging.

Microarchitects who were once able to defer reliability concerns to lower level circuit and process engineers are now responsible for their share of the heavy lifting. With wearout and transient faults knocking at the door of even commodity processors, microarchitects must devise new methods to ensure consumer-visible failure rates still remain imperceptibly small, without noticeably degrading performance or cutting into shrinking profit margins.

Traditionally, reliability research has focused largely on the high-performance server market. The historical gold standards in this space have been the IBM S/360 (now Z-series servers) [95] and the HP NonStop systems [14], which rely on large scale modular redundancy to provide fault tolerance. Other researchers have focused on providing fault protection using redundant multithreading [80, 74, 59, 38, 90] or specialized hardware checkers [114, 19, 55].

These simple yet elegant techniques, having served those in the mission-critical server arena for decades, are not typically practical outside this niche domain. The overheads associated with these conventional solutions are prohibitively expensive for budget-conscious

systems with less demanding reliability requirements. Although reliability cannot be completely ignored in lower-end systems, they are not usually designed to provide the "five-nines" of fault tolerance capable of sending someone safely to the moon.

In the commodity computing space, area and power are primary considerations. Consumers are not willing to pay the additional costs (in terms of hardware price, performance loss, or reduced battery lifetime) for conventional fault-tolerance schemes. At the same time, they do not demand "five-nines" of reliability, tolerating the occasional dropped phone calls, glitches in video playback, and crashes of their desktop/laptop computers (commonly caused by software bugs). The key challenge facing the consumer electronics market in future deep submicron technologies is providing just enough fault-tolerance to ensure that the effective fault rate remains at the level to which people have become accustomed. Examining how this minimal, yet *sufficient*, coverage can be achieved "on the cheap" is the goal of this thesis.

# 1.2 Reliability Taxonomy

The purpose of this section is to set the stage for the remainder of the thesis by providing some preliminary background. Additional, supplemental information is supplied within subsequent chapters as needed. Given the vast amount of reliability works in the literature, this section hopes to minimize potential confusion by introducing the manner in which some fundamental terms and concepts will be used within the context of this document. Although other, presumably more formal texts, may present alternatives to these defini-

tions, our intent was to embrace the most popular definitions when possible for the sake of readability, drawing distinctions and specializing terms only when absolutely necessary.

### 1.2.1 Threats to Reliable Computing

For the purposes of this thesis, faults are separated into two broad categories, *transient* and *permanent*. Membership in one of these two categories, although not always a hard-and-fast rule, is generally decided based on the frequency and duration of the fault event. A transient fault is typically a "rare" event that causes an error that generally does not persist, whereas a permanent fault, once it has evolved, is almost assured to manifest as frequent consistent errors. Within permanent faults this thesis is particularly interested in those faults that are caused by device *wearout*—the process by which transistors, which are fully functional at manufacture time, degrade and eventually fail over a lifetime.

Transient Faults: Probably the better understood of the two categories, transient faults, also known as soft-errors, can be caused by a variety of phenomena. Historically, the two major sources have been neutrons from cosmic radiation and alpha particles released from packaging impurities. Whatever their origin, these high-energy particles deposit additional charge when they strike that can cause a transistor to erroneously switch. In addition to these environmental culprits, transient faults can also result from an array of other sources including crosstalk and voltage and current fluctuations. Furthermore, recent proposals for high-performance, low-power designs that employ aggressive frequency scaling and even timing speculation are also emerging as prominent causes of transient faults.

**Permanent Faults:** Traditionally viewed as a process and manufacturing concern, permanent faults (also known as "hard faults") have caught the attention of microarchitects in

recent years. In addition to the expected manufacturing defects, designers are now faced with the prospect of in-field wearout. This most recent threat has captured significant interest because it is closely coupled with the aggressive technology scaling trend being pursued by industry. As CMOS feature sizes scale to smaller dimensions, the inability of operating voltage to scale accordingly results in dramatic increases in power and current density. Consequently, areas of high power density increase local temperatures leading to hot spots on the chip. Since most wearout mechanisms, such as gate oxide breakdown and negative bias temperature instability are all highly dependent on temperature, the occurrence of wearout-induced failures will become increasingly common in future technology generations.

## 1.2.2 Anatomy of Fault-tolerant Computing

Figure 1.1 is an abstract illustration of the major components of a comprehensive reliability strategy. Each of these aspects of reliability must be addressed, at least to some degree, in order to ensure fault-tolerant operation. For example, simply detecting a fault is insufficient if no mechanism is in place to recover from it. However, not all components in Figure 1.1 require complex, sophisticated solutions. In some situations, like when a transient fault is detected, an adequate recovery response may simply be to discard the affected instructions.

The relative position of each component with respect to the transient-permanent fault boundary represents the degree to which recent state-of-the-art research publications aimed at transient (permanent) faults has focused on that particular aspect of reliability. For example, papers proposing diagnosis and system repair (reconfiguration) solutions have gen-

**Figure 1.1:** A "reliability pipeline" depicting the different pieces of a comprehensive reliability strategy. The relative location of each component to the transient-permanent boundary represents the extent to which recent research into transient (wearout-induced permanent) faults has studied that particular aspect of reliability.

erally been targeted toward permanent faults, mainly because transient faults typically do not damage the underlying hardware, leaving nothing to be repaired.

This thesis concentrates primarily on the first three stages in this "reliability pipeline." The first half presents techniques to monitor (detection) and proactively manage (prevention) the effects of device wearout. The later half of the dissertation tackles the challenges of transient fault detection and recovery, capitalizing on detailed program analysis to reign in overhead costs.

## 1.3 Conventional Solutions

As previously alluded to, processor reliability is by no means a new area of research. In as early as 1956 von Neumann formally presented the principles behind modular redundancy [63], principles that have evolved into the fault-tolerance solution of choice for nearly all application domains that have historically demanded high-reliably. In its simplest form, n-modular redundancy (nMR) relies on performing multiple instances of the same compu-

tation and employing an arbitration mechanism (typically majority voting) that can identify the correct, error-free, result from n potentially different outcomes. The archetypal fault-tolerant systems of the past have all embraced some variant of this elegant, yet effective technique [95, 11, 14].

Possibly the biggest attraction of nMR solutions is that they can nearly address all aspects of reliability (see Figure 1.1). By design they fulfill both the detection and recovery requirements, and in a simple triple-modular implementation fault diagnosis is also naturally provided (assuming a single fault model). Furthermore, given the inherent redundancy in an nMR design, even temporary repair can be easily achieved by simply ignoring the outputs of components that have been identified as faulty <sup>1</sup>.

Yet despite the strengths of these early systems, the advent of multithreaded and multicore architectures motivated researchers to develop ways of accomplishing nMR without having to explicitly design redundancy into the hardware. Rotenberg's seminal paper on AR-SMT [80] was the first comprehensive microarchitectural-level paper on modular redundancy, introducing the concept of redundant multithreading on simultaneous multithreaded cores. Whether redundantly executing on separate cores within a CMP (spatial redundancy) or managing redundant threads running within multiple software contexts on the same hardware (temporal redundancy), later proposals like those by Vijaykumar [38, 37, 107] and Falsafi [70, 90, 91] attempted to improve upon the performance of AR-SMT by exploiting the redundant, and often idle, resources of modern superscalar CMPs.

<sup>&</sup>lt;sup>1</sup>Clearly, depending on the needs of the system the faulty components would ultimately need to be replaced or the reductions in redundancy would eventually degrade reliability.

Relative to these coarse-grained redundancy approaches, the techniques proposed in this thesis incur considerably less overheads. They are not dependent on the abundance of idle processors or hardware resources. In scenarios where systems are not significantly overprovisioned, the overheads of traditional nMR are considerably greater than the few percentage points of performance degradation regularly reported in research papers. The additional resources required to enable redundant execution (i.e., additional cores and threads) must also be accounted for, resources that can no longer be allocated to other waiting tasks, adversely impacting their performance.

In contrast, the solution we propose for transient fault detection and recovery only imposes a modest performance degradation, limited to just the application being protected, without any modifications to commodity hardware. Similarly, although our wearout proposals do involve microarchitectural additions, they do not require that entire cores be reappropriated for continuous fault monitoring. Furthermore, unlike nMR solutions that can only react to failures, the wearout management techniques in this thesis are preventative and can actually proactively avoid failures.

Of course, the body of reliability literature is not solely devoted to nMR. The considerable research effort devoted toward further reducing the overheads of fault-tolerant computing has resulted in many innovative solutions that span the spectrum of the software-hardware stack. They range from compiler-directed instruction duplication [75] and specialized hardware checkers [55] for transient fault detection to adaptive body biasing and voltage scaling [105, 85] to keep wearout at bay. However, as less conventional solutions that typically only target a single component of the "reliability pipeline" (Figure 1.1) they will be discussed separately within the appropriate chapters. A more extensive treatment

of the latest advances in fault-tolerant architecture can also be found in Sorin's recent synthesis lecture [93].

### 1.4 Contributions

This thesis is built upon two central principles: 1) that the majority of consumer devices do not lie at either extreme of the reliability spectrum, necessitating the need for not just "low-cost" but genuinely affordable fault-tolerance, and 2) that with the appropriate analysis, the inherent computational patterns within programs can be leveraged to reap dramatic reductions in the cost of dependable computing.

With these themes in mind we make the following contributions:

- We demonstrate that the progressive nature of prominent silicon wearout mechanisms

makes them amenable to low-cost, in-situ monitoring, proposing a microarchitecturallevel sensor capable of tracking the evolution of wearout.

- We present a proactive reliability-aware scheduler that leverages continuous health monitoring to orchestrate application-driven wear-leveling to maximize lifetime reliability.

- We develop a commodity-grade (adequate coverage at ultra-low cost) transient fault detection mechanism that relies on reliability-aware compiler analyses to direct selective instruction duplication of vulnerable computations.

- Lastly, we present a software-only, fine-grained rollback recovery mechanism targeted at low-end commodity processors lacking native hardware recovery support.

### **CHAPTER II**

# **Self-calibrating Online Wearout Detection**

### 2.1 Introduction

Traditionally, microprocessors have been designed with worst case operating conditions in mind. To this end, manufacturers have employed burn in, guard bands, and speed binning to ensure that processors will meet a predefined lifetime qualification, or mean time to failure (MTTF). However, projections of current technology trends indicate that these techniques are unlikely to satisfy reliability requirements in future technology generations [18]. As CMOS feature sizes scale to smaller dimensions, the inability of operating voltage to scale accordingly results in dramatic increases in power and current density. Areas of high power density increase local temperatures leading to hot spots on the chip [88]. Since most wearout mechanisms, such as gate oxide breakdown (OBD), negative bias temperature instability (NBTI), electromigration (EM), and hot carrier injection (HCI), are highly dependent on temperature, power, and current density, the occurrence of wearout-induced failures will become increasingly common in future technology generations [41].

Though the reliability of individual devices is projected to decrease, consumer expectations regarding system reliability are only likely to increase. For example, some business customers have reported downtime costs of more than \$1 million per hour [4]. Further, a recent poll conducted by Gartner Research demonstrated that more than 84% of organizations rely on systems that are over five years old, and more than 50% use machines that are over ten years old [1]. Given the requisite long life expectancies of systems in the field and the high costs of in-field replacement, any technique for mitigating the amount of downtime experienced due to failed systems will prove invaluable to businesses.

In order to maintain availability in the presence of potentially unreliable components, architects and circuit designers have historically employed either error detection or failure prediction mechanisms. Error detection is used to identify failed or failing components by locating (potentially transient) pieces of incorrect state within the system. Once an error is detected, the problem is diagnosed and corrective actions may be taken. The second approach, failure prediction, supplies the system with a failure forecast allowing it to take preventative measures to avoid, or at least minimize, the impact of expected device failures.

Historically, high-end server systems have relied on error detection to provide a high degree of system reliability. Error detection is typically implemented through coarse grain replication. This replication can be conducted either in space through the use of replicated hardware [95, 14], or in time by way of redundant computation [80, 74, 70, 107, 90, 37, 75, 71]. The use of redundant hardware is costly in terms of both power and area and does not significantly increase the lifetime of the processor without additional cold-spare devices. Detection through redundancy in time is potentially less expensive but is generally limited to transient error detection unless redundant hardware is readily available.

Failure prediction techniques are typically less costly to implement, but they also face a number of challenges. One traditional approach to failure prediction is the use of canary circuits [56], designed to fail in advance of the circuits they are charged with protecting, providing an early indication that important processor structures are nearing their end of life. Canary circuits are an efficient and generic means to predict failure. However, there are a number of sensitive issues that must be addressed to deploy them effectively. For instance, the placement of these circuits is extremely important for accurate prediction, because the canary must be subjected to the same operating conditions as the circuit it is designed to monitor.

Another technique for failure prediction is the use of timing sensors that detect when circuit latency is increasing over time or has surpassed some predefined threshold [31, 15, 2]. The work presented here extends upon [15] which presented the idea of failure prediction using timing analysis and identifying degrading performance as a symptom of wearout in semiconductor devices.

Recent work by Srinivasan [98] proposes a predictive technique that monitors the dynamic activity and temperature of structures within a microprocessor in order to calculate their predicted time to failure based on analytical models. This system can then be used to swap in cold-spare structures based on these predictions. This work pioneered the idea of dynamically trading performance for reliability in order to meet a predefined lifetime qualification. Although this technique may be used to identify structures that are likely to fail in the near future, it relies on accurate analytical device wearout models and a narrow probability density function for effective predictions.

Research into the physical effects of wearout on circuits has shown that many wearout mechanisms for silicon devices are progressive over time. Further, many of these wearout mechanisms, such as EM, OBD, HCI, and NBTI, have been shown to have a negative impact on device performance [7, 51, 119, 23]. For example, a device subject to hot carrier injection (HCI) will experience drive current degradation, which leads to a decrease in switching frequency [7]. The recognition of progressive performance degradation as a precursor to wearout-induced failures creates a unique opportunity for predictive measures, which can forecast failures by dynamically analyzing the timing of logic in situ.

The work presented here proposes an online technique that detects the performance degradation caused by wearout over time in order to anticipate failures. Rather than aggressively deploying duplicate fault-checking structures or relying on analytical wearout models, an early warning system is presented that identifies the performance degradation symptomatic of wearout. As a case study, and to derive an accurate performance degradation model for subsequent simulations, detailed HSPICE simulations were performed to determine the impact of one particular wearout mechanism, OBD, on logic gates within a microprocessor core. Research of other progressive wearout mechanisms such as HCI and EM, indicates that similar effects are likely to be observed as a result of these phenomenon.

The results of this analysis are used to motivate the design of an online latency sampling unit, dubbed the wearout detection unit (WDU). The WDU is capable of measuring the signal propagation latencies for signals within microprocessor logic. This information is then sampled and filtered by a statistical analysis mechanism that accounts for anomalies in the sample stream (caused by phenomenon such as clock jitter, and power and temperature fluctuations). In this way, the WDU is able to identify significant changes in the

latency profile for a given structure and predict a device failure. Online statistical analysis allows the WDU to be self-calibrating, adapting to each structure that it monitors, making it generic enough to be reused for a variety of microarchitectural components.

Traditional studies of wearout mechanisms have focused primarily on their effects on transistor and circuit level performance, without analyzing the microarchitectural impact.

To the best of our knowledge, the experiments presented in this chapter were the first such attempt in this direction. Specific contributions include:

- An HSPICE-based characterization of OBD-induced wearout

- A microarchitectural analysis of the performance impact of OBD on microprocessor logic

- A detailed simulation infrastructure for modeling the impact of wearout on an embedded processor core

- A self-calibrating WDU capable of monitoring path latencies

- A demonstration of how the WDU can be deployed to extend processor lifetime

# 2.2 Device-level Wearout Analysis

Though many wearout mechanisms have been shown to progressively degrade performance as transistors age [7, 119, 23], as a case study, this work focuses on the effects of one particular mechanism, gate oxide breakdown (OBD), to demonstrate how performance degradation at the device level can affect processor performance at the microarchitectural level. Due to the lack of microarchitectural models for the progressive effects of wearout, it was necessary to first model the effects at the circuit level in order to abstract them up to

the microarchitecture. The results of the modeling and abstraction are presented within this section. While this section is useful in understanding the nature of progressive wearout, readers unfamiliar with device physics may want to simply note the high-level abstraction of OBD effects presented in Figure 2.1 and move on to section 2.3.

The remainder of this section describes the transistor degradation model for OBD, based on empirical data from researchers at IBM. This section also presents an HSPICE characterization of the effects of OBD on gates in a 90 nm standard cell library from a major technology vendor.

#### 2.2.1 Gate Oxide Breakdown

OBD, also known as time dependent dielectric breakdown (TDDB), is caused by the formation of a conductive path through the gate oxide of a CMOS transistor. The progression of OBD causes an increasing leakage current through the gate oxide of devices that eventually leads to oxide failure, rendering the device unresponsive to input stimuli [100, 57, 51]. Sune and Wu showed that there is a significant amount of time required for the OBD leakage current to reach a level capable of affecting circuit performance [100]. This suggests that there is a window of opportunity to detect the onset of OBD before oxide leakage levels compromise the operation of devices and cause timing failures.

The modeling of OBD conducted in this work is based upon the experimental results of Rodriguez et al. [78]. The change in gate oxide current resulting from OBD is modeled by the power-law expression in Equation 2.1:

$$\Delta I_{qate} = K(V_{qd})^p \tag{2.1}$$

The change in gate-to-drain (gate-to-source) current is represented as a function of a linear scaling factor K, the gate-to-drain (gate-to-source) voltage  $V_{gd}$  ( $V_{gs}$ ), and a power-law exponent, p. Both fitting parameters K and p vary depending on the amount of degradation experienced by the transistor in question. However, for much of the empirical data collected in [78], selecting a p=5.0, while still allowing K to track the degree of degradation, resulted in a consistent fit. This is the model for device degradation used in this work.

#### 2.2.2 HSPICE Analysis

To facilitate modeling the effects of OBD-induced degradation in HSPICE, the BSIM4 gate leakage model [13] for gate-to-drain and gate-to-source oxide leakage is modified to accommodate the scaling factor from Equation 2.1. Using this leakage model, an HSPICE testbench was created to simulate the effects of OBD on propagation delay within logic circuits. The testbench consists of an ideal voltage source driving an undegraded copy of the gate under test, which drives the gate under test, which drives another undegraded copy of the gate under test. This testbench allows the simulations to capture both the loading effects a degraded device presents to nodes on the upstream path, as well as the ability of downstream nodes to regenerate a degraded signal.

For each type of logic gate within the cell library, one transistor at a time is selected from the gate and its leakage model is replaced with the modified BSIM4 model. For each transistor that is being degraded, all input to output transistions are simulated so that for every gate characterized, propagation delays corresponding to all possible combinations of degraded transistor, input to output path, and initial input states are captured. For each

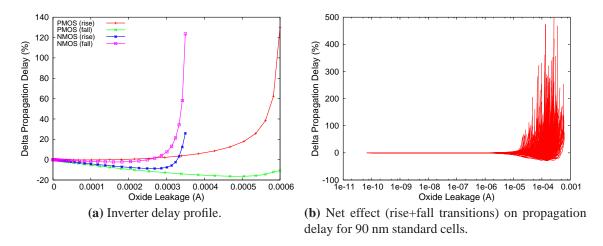

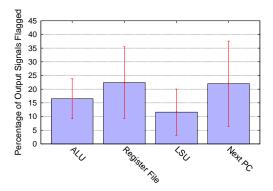

**Figure 2.1:** *Impact of OBD-induced oxide leakage current on standard cell propagation delays.*

simulation run, the amount of degradation experienced by the degraded transistor (as modeled by the oxide leakage) is slowly increased until the gate ceases to function (outputs no longer switch).

The results of the timing characterization are shown in Figure 2.1. Figure 2.1a shows the changes in propagation delay for an average size inverter. The plot highlights the different effects that OBD has on propagation delay depending on the transition direction and location/type of the degraded transistor. Note that for the case when the PMOS (the analogous story is true for the NMOS) is degraded, rising transitions expressed increases in delay while falling transitions showed decreases in delay. A detailed discussion of this phenomenon follows in the next paragraph. Although there are complex dependence relationships affecting the performance impact on rise and fall propagation delays, as a simplifying assumption, the net effect is used in this work. Figure 2.1b presents the net effect (rising transition + falling transition) of OBD on gates within the cell library. For a given gate a separate curve is shown for each of its transistors. Note that the "net" change in

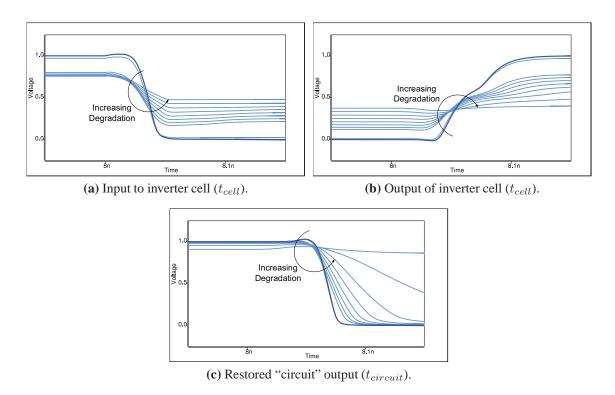

**Figure 2.2:** *HSPICE simulation traces for inverter with degraded PMOS (slowdown).*

propagation delay is categorically increasing near the end of life for gates within this cell library, irrespective of which internal transistor is degraded.

An examination of Figure 2.1a reveals that in the case where the PMOS experiences OBD, the rising transition expresses more than a doubling of its nominal delay before the inverter fails to transition. The primary source of this increase in delay is the interaction with the previous stage, a non-degraded inverter, which is subjected to driving the leaky PMOS oxide. Figures 2.2 and 2.3 show the voltages at the nodes of interest during the rising and falling transitions of the degraded inverter. The bold traces show the voltage transitions under nominal conditions while the lighter curves are the result of increasing amounts of wearout.

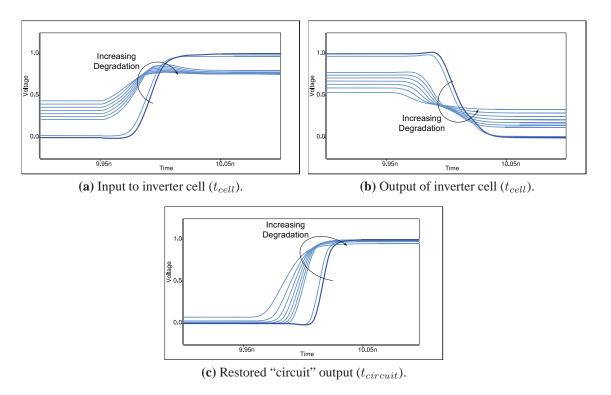

**Figure 2.3:** *HSPICE simulation traces for inverter with degraded PMOS (speedup).*

When the input to the inverter under test begins to fall (Figure 2.2a), the gate-to-source oxide leakage,  $I_{gs}$ , through the PMOS device provides additional current to the input node, prolonging the discharge time of the gate through the NMOS of the preceding stage. The gate-to-drain oxide leakage,  $I_{gd}$ , initially aids the rising transition, helping to charge up the inverter output. However, as the transition continues and the output begins to rise, this  $I_{gd}$  leakage also provides an additional current to the gate node. As with the  $I_{gs}$  current, this too increases the time required to drain the remaining charge on the gate. Note also that with large amounts of degradation the input voltage range compresses due to  $I_{gs}$  and  $I_{gd}$  oxide leakage. Unable to switch from rail-to-rail, the on-currents sustainable by the PMOS and NMOS are significantly reduced, which ultimately contributes to the increase in overall propagation delay (Figure 2.2c).

Perhaps more surprising is the behavior of the propagation delay during a falling transition of the inverter output (Figure 2.3). With increasing oxide degradation, the delay of the inverter actually decreases until just prior to functional failure. This behavior is caused by the  $I_{gs}$  and  $I_{gd}$  leakage currents that help in charging their own gate node, resulting in an earlier rising transition on the input. As a result, despite the degraded on currents due to the compressed gate voltage swing, because the inverter actually "sees" the input transitioning sooner, the net effect is a decrease in the overall propagation delay of the inverter itself  $(t_{cell})$  and ultimately the circuit  $(t_{circuit})$ .

In summary, at moderate values of oxide degradation, the input voltage on the gate node swings roughly rail-to-rail, allowing normal operation of the inverter. However, during the final stages of oxide OBD, the input voltage range compresses due to  $I_{gs}$  and  $I_{gd}$  leakage (Figures 2.3a and 2.2a), and the current conducted by the PMOS and NMOS devices in the inverter are significantly altered. The significantly reduced output range eventually results in functional failure when the device is no longer capable of driving subsequent stages. Note however, that prior to circuit failure, the stage immediately following the inverter under test is able to completely restore the signal to a full rail swing (Figures 2.2c and 2.3c), irrespective of the switching direction.

# 2.3 Microarchitecture-level Wearout Analysis

This section describes how the transistor-level models from the previous section are used to simulate the effects of OBD over time on an embedded microprocessor core. The section begins by describing the processor core studied in this work along with the synthesis

flow used in its implementation and thermal analysis. This is followed by a discussion of MTTF calculations and a description of the approach used to conduct Monte Carlo simulations of the effects of OBD. A discussion of OBD's impact on propagation delay at the microarchitectural level concludes the section.

## 2.3.1 Microprocessor Implementation

The testbed used to conduct wearout experiments was a Verilog model of the Open-RISC 1200 (OR1200) CPU core [65]. The OR1200 is an open-source, embedded-style, 32-bit, Harvard architecture that implements the ORBIS32 instruction set. The microprocessor contains a single-issue, 5-stage pipeline, with direct mapped 8KB instruction and data caches, and virtual memory support. This microprocessor core has been used in a number of commercial products and is capable of running the  $\mu$ Clinux operating system.

The OR1200 core was synthesized using Synopsys Design Compiler, with a cell library characterized for a 90 nm process and a clock period of 2.5 ns (400 MHz). Cadence First Encounter was used to conduct floorplanning, cell placement, clock tree synthesis, and routing. This design flow provided accurate timing information (cell and interconnect delays) and circuit parasitics (resistance and capacitance values) for the entire OR1200 core. The floorplan along with details of the implementation is shown in Figure 2.4. Note that although the OR1200 microprocessor core shown in Figure 2.4 is a relatively small design, it's area and power requirements are comparable to that of an ARM9 microprocessor. The final synthesis of the OR1200 appropriates a timing guard band of 250 ps (10% of the clock cycle time) to mimic a commodity processor and to ensure that the wearout simulations do not prematurely cause timing violations.

| OR1200 Core            |                    |

|------------------------|--------------------|

| Area                   | $1.0 \text{ mm}^2$ |

| Power                  | 123.9 mW           |

| Clock Frequency        | 400 MHz            |

| Data Cache Size        | 8 KB               |

| Instruction Cache Size | 8 KB               |

| Logic Cells            | 24,000             |

| Technology Node        | 90 nm              |

| Operating Voltage      | 1.0 V              |

- (a) Implementation details for the OR1200 microprocessor.

- **(b)** Overlay of the OR1200 floorplan on top of the placed and routed implementation of the CPU core.

**Figure 2.4:** OpenRisc1200 embedded microprocessor.

#### 2.3.2 Power, Temperature, and MTTF Calculations

The MTTF due to OBD is dependent on many factors, the most significant being oxide thickness, operating voltage, and temperature. To quantify the MTTF of devices undergoing OBD, this work uses the empirical model described in [97], which is based on experimental data collected at IBM [117]. This model is presented in Equation 2.2.

$$MTTF_{OBD} \propto (\frac{1}{V})^{(a-bT)} e^{\frac{(X+\frac{Y}{T}+ZT)}{kT}}$$

(2.2)

where,

- V =operating voltage

- T = temperature

- k = Boltzmann's constant

- a, b, X, Y, and Z are all fitting parameters based on [97]

In order to calculate the MTTF for devices within the OR1200 core, gate-level activity data was generated by simulating the execution of a set of benchmarks<sup>1</sup> running on a synthesized netlist using Synopsys VCS. This activity information, along with the parasitic data generated during placement and routing, was then used by Synopsys PrimePower to generate a per-benchmark power trace. The power trace and floorplan were in turn processed by HotSpot [88], a block level temperature analysis tool, to produce a dynamic temperature trace and a steady state temperature for each structure within the design.

Once the activity and temperature data were derived, the MTTF for each logic gate in the design was calculated using Equation 2.2 with the temperature and activity data for each benchmark. A per-module MTTF is calculated by identifying the minimum MTTF across all logic gates within each top-level module of the OR1200 core. These per-module MTTF values are later used to parametrize the statistical distribution of failures used in Monte Carlo simulations of OBD effects. Figure 2.5 presents the steady state temperatures and MTTF values of different structures within the CPU core for the five benchmarks.