# **Correct Communication in Multi-core Processors**

by

#### Andrew Whitehouse DeOrio

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2012

**Doctoral Committee:**

Associate Professor Valeria M. Bertacco, Chair Professor Todd M. Austin Professor Scott Mahlke Professor Stephen J. Rush Raj Yavatkar, Intel Corporation © Andrew Whitehouse DeOrio

All Rights Reserved 2012

To my family

### Acknowledgments

I would like to thank my advisor Professor Valeria Bertacco, who introduced me to research. Her willingness to let me explore new ideas has been a wonderful freedom, and our discussions of engineering trade-offs have improved my work. Moreover, my writing and presentation skills have grown significantly as a result of her mentoring and her careful eye.

I am also grateful for my committee members. Professor Todd Austin has been a consistent source of valuable feedback throughout my studies. I am appreciative of Professor Scott Mahlke's contributions, and our friendly interactions at the north campus gym track. My musical tastes have expanded as a result of my relationship with Professor Stephen Rush. He introduced me to the pyrophone [75], and to the saints of free jazz. Dr. Raj Yavatkar has been a mentor to me in the professional world, as well as the academic world, supporting my work at Intel Corp. and at the University.

Early in my graduate school career, I was fortunate to work with Ilya Wagner – he taught me the ropes of being a graduate student. I am grateful for Joseph Greathouse and Andrea Pellegrini for our illuminating discussions and colorful experiences. I am also appreciative of the people I have collaborated with on many projects: Adam Bauserman, Debapriya Chatterjee, Ilya Wagner, Rawan Abdel-Khalek, Ritesh Parikh, Daya Khudia, Jialin Li, Qingkun Li, Matt Burgess, Jin Hu, Gregory Chen, Kostantinos Aisopos, David Fick, and Professors Li-Shiuan Peh, Dennis Sylvester, and David Blaauw.

Finally, I would like to thank my family: for my mom, for many Thursday night dinners with Dad, and for my siblings Allison and Scott.

### Preface

Computer chips, the most complex artifacts ever made by man, are susceptible to problems with correct functionality due to their intricacy. Incorrect operation of silicon chips has lasting, and sometimes devastating, effects on computer systems and their manufacturers: from incorrect computation results, to security vulnerabilities affecting end users, to financial impact on the vendors. Furthermore, new chips are increasingly fragile, liable to break as the transistors that comprise them become small enough to be measured in atoms.

A typical modern computer usually includes a single chip where many processors are connected by a communication medium. This communication medium, a new feature in modern chips, provides many opportunities for catastrophic errors, as it is a complex, unpredictable, unique component.

The goal of this dissertation is to provide a new solution to ensure the correct operation of the communication medium in multicore processors, from the early stages of design to the end user. It addresses failures in several modes, and operates across the different phases of the verification process, integrating them into a cohesive framework. A key finding of this work is the synergy among verification phases, connected by a novel abstraction technique and multipurpose hardware and software. Simply put, it ensures that the design operates as intended. This approach to the development cycle accelerates, automates and extends the reach of the verification process, providing decreased occurrence of and increased resilience to — failures. With this solution, the communication system of multi-core chips can operate free from errors.

## **Table of Contents**

| Dedicat   | ion                                                                                  | ii     |

|-----------|--------------------------------------------------------------------------------------|--------|

| Acknow    | ledgments                                                                            | iii    |

| Preface   |                                                                                      | iv     |

| List of I | <b>Figures</b>                                                                       | iii    |

| List of 7 | Fables                                                                               | X      |

| Chapter   | <b>1</b> Microprocessor Errors and Opportunities to Mitigate Them Impact of Failures | 1<br>2 |

| 1.2       | Types of Errors                                                                      | 3      |

| 1.3       | Avoiding Failures and Ensuring Correctness                                           | 4      |

| 1.4       | Dissertation Overview                                                                | 6      |

| 1.5       | Dissertation Organization                                                            | 7      |

| Chapter   | 2 Verification: State of the Art                                                     | 9      |

| 2.1       |                                                                                      | 11     |

|           |                                                                                      | 11     |

|           |                                                                                      | 12     |

| 2.2       |                                                                                      | 14     |

| 2.3       |                                                                                      | 17     |

| 2.4       |                                                                                      | 19     |

| 2.5       | Verification Targets                                                                 | 19     |

| Chapter   | r 3 Addressing Functional Bugs                                                       | 21     |

| 3.1       |                                                                                      | 21     |

| 3.2       |                                                                                      | 24     |

|           |                                                                                      | 25     |

|           |                                                                                      | 28     |

|           | • •                                                                                  | 30     |

| 3.3       |                                                                                      | 30     |

|           | e                                                                                    | 31     |

|                                                          | 3.3.2 Post-silicon Failure Detection                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 3.4                                                      | Accelerating Post-Silicon Validation with Dacota                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

|                                                          | 3.4.1 Dacota Operation                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |

|                                                          | 3.4.2 Activity Logging Hardware                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                   |

|                                                          | 3.4.3 Policy Validation Algorithm                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                   |

|                                                          | 3.4.4 Evaluation                                                                                                                                                                                                                                                                                                                                                                          | 42                                                                                                                |

| 3.5                                                      | Ensuring End-to-end Correctness at Runtime with SafeNoC                                                                                                                                                                                                                                                                                                                                   | 45                                                                                                                |

|                                                          | 3.5.1 Error Detection Hardware                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                   |

|                                                          | 3.5.2 Recovery Algorithm                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                   |

|                                                          | 3.5.3 Evaluation                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

|                                                          | 3.5.4 BiPeD/SafeNoC Integration                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                   |

| 3.6                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                   |

|                                                          | -                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                   |

| -                                                        | r 4 Addressing Electrical Failures                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |

| 4.1                                                      | Electrical Failures                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                   |

| 4.2                                                      | Detecting Failures with BiPeD                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |

| 4.3                                                      | Diagnosing Failures with BPS                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                   |

|                                                          | 4.3.1 BPS Hardware                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |

|                                                          | 4.3.2 BPS Post-Analysis Software                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

|                                                          | 4.3.3 Tuning Parameters                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                   |

|                                                          | 4.3.4 Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |

| 4.4                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                                                                                |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                   |

| Chanter                                                  | r 5 Addressing Transistor Faults                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                |

| -                                                        | r 5 Addressing Transistor Faults                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

| Chapter<br>5.1                                           | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77                                                                                                                |

| 5.1                                                      | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79                                                                                                          |

| 5.1<br>5.2                                               | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81                                                                                                    |

| 5.1                                                      | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82                                                                                              |

| 5.1<br>5.2                                               | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83                                                                                        |

| 5.1<br>5.2<br>5.3                                        | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91                                                                                  |

| 5.1<br>5.2                                               | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91<br>96                                                                            |

| 5.1<br>5.2<br>5.3                                        | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97                                                                      |

| 5.1<br>5.2<br>5.3                                        | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98                                                                |

| 5.1<br>5.2<br>5.3                                        | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102                                                         |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults.5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization                                                                                                                            | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103                                                  |

| 5.1<br>5.2<br>5.3                                        | Transistor Faults                                                                                                                                                                                                                                                                                                                                                                         | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105                                           |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.4EvaluationSubstructure5.5.1Recovery — Drain5.5.1Recovery Hardware                                                                                      | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106                                    |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4Evaluation5.5.1Recovery — Drain5.5.2Recovery Algorithm                                                                  | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109                             |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4EvaluationData Recovery — Drain5.5.1Recovery Hardware5.5.2Recovery Algorithm                                            | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109<br>110                      |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4Evaluation5.5.1Recovery — Drain5.5.2Recovery Algorithm                                                                  | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109<br>110                      |

| 5.1<br>5.2<br>5.3<br>5.4                                 | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4Evaluation5.5.1Recovery — Drain5.5.2Recovery Algorithm5.5.3EvaluationSummary                                            | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109<br>110<br>114               |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.5                   | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4Evaluation5.5.1Recovery — Drain5.5.2Recovery Algorithm5.5.3EvaluationSummary                                            | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109<br>110<br>114<br>115        |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Chapter</b> | Transistor Faults5.1.1Fault ModelFault Detection — BiPeDFault Diagnosis — Vicis5.3.1Architectural Features5.3.2EvaluationNetwork Reconfiguration — Ariadne5.4.1Historical Approaches to Reliable Routing5.4.2Routing Algorithm5.4.3Timing and Synchronization5.4.4EvaluationData Recovery — Drain5.5.1Recovery Hardware5.5.3EvaluationSummaryr6BiPeD: Bridging the Phases of Verification | 77<br>79<br>81<br>82<br>83<br>91<br>96<br>97<br>98<br>102<br>103<br>105<br>106<br>109<br>110<br>114<br>115<br>115 |

|           | 6.3.1 P    | rotocol De  | etection | n.    | <br>    |     |     |       |     |       |     |   |     | <br>• | 121 |

|-----------|------------|-------------|----------|-------|---------|-----|-----|-------|-----|-------|-----|---|-----|-------|-----|

|           | 6.3.2 P    | rotocol Ex  | stractic | n.    | <br>    |     |     |       |     |       |     |   |     | <br>• | 123 |

|           | 6.3.3 T    | ransaction  | n Extra  | ction | <br>    |     |     |       |     |       |     |   |     | <br>• | 123 |

|           | 6.3.4 A    | rea Overh   | nead.    |       | <br>    |     |     |       |     |       |     |   |     | <br>• | 124 |

| 6.4       | Summary    |             |          | •••   | <br>••• | • • | • • | <br>• | ••• | <br>• | • • | • |     | <br>• | 125 |

| Chapter   | 7 Conc     | lusions .   |          |       | <br>    |     |     |       |     |       |     |   |     | <br>• | 127 |

| 7.1       | Bridging   | Verificatio | on Phas  | ses   | <br>    |     |     |       |     |       |     |   |     | <br>• | 127 |

| 7.2       | Functiona  | al Bugs .   |          |       | <br>    |     |     |       |     |       |     |   |     | <br>• | 128 |

| 7.3       | Electrical | Failures    |          |       | <br>    |     |     |       |     |       |     |   |     | <br>• | 130 |

| 7.4       | Transisto  | r Faults    |          |       | <br>    |     |     | <br>• |     |       |     |   |     | <br>• | 130 |

| 7.5       | Summary    |             |          | •••   | <br>    |     |     | <br>• | ••• | <br>• | • • | • | ••• | <br>• | 131 |

| Bibliogra | aphy       |             |          | •••   | <br>    |     |     | <br>• |     |       |     |   |     | <br>• | 132 |

# **List of Figures**

### Figure

| 1.1  | Types of errors addressed by this dissertation                              | 3  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Overview of the solution framework proposed by this dissertation $\ldots$ . | 7  |

| 2.1  | Typical design verification flow for a modern multi-core microprocessor     |    |

| 2.2  | Simulation-based pre-silicon verification for microprocessors               |    |

| 2.3  | Post-silicon validation flow                                                | 15 |

| 2.4  | Theoretical shmoo plots                                                     | 16 |

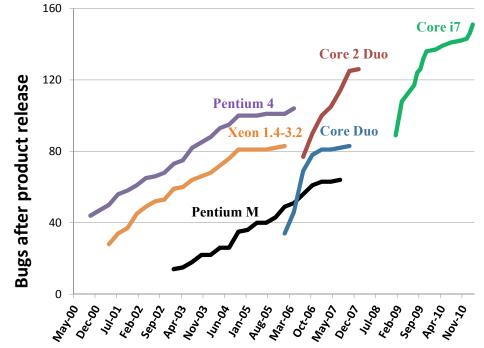

| 3.1  | Functional bugs over time                                                   |    |

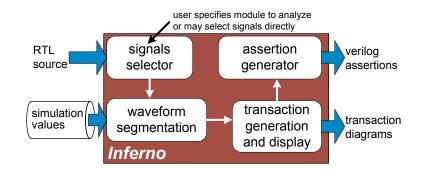

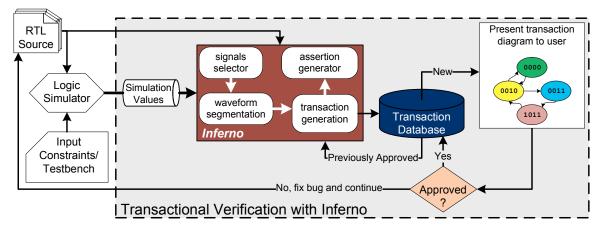

| 3.2  | Inferno architecture                                                        |    |

| 3.3  | Pseudocode for protocol diagram generation algorithm                        |    |

| 3.4  | Flowchart of Inferno's transaction extraction algorithm                     | 26 |

| 3.5  | Pseudocode for dynamic transaction extraction algorithm                     | 27 |

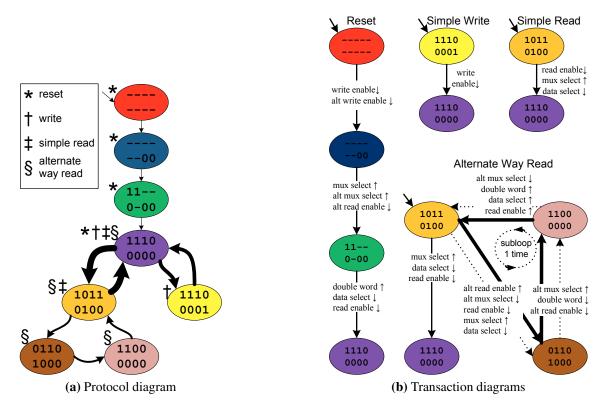

| 3.6  | Protocol and transaction diagrams from the OpenSPARC T1                     | 29 |

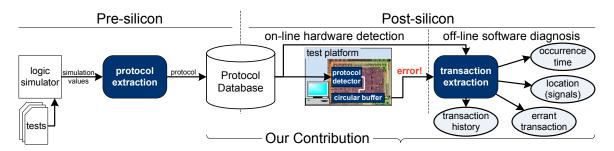

| 3.7  | Methodology overview                                                        |    |

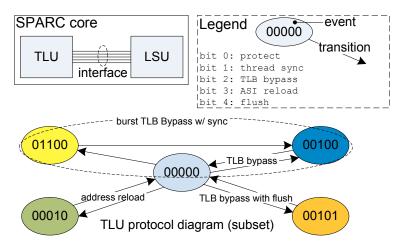

| 3.8  | Protocol subset of the OpenSPARC T2 TLU/LSU interface                       |    |

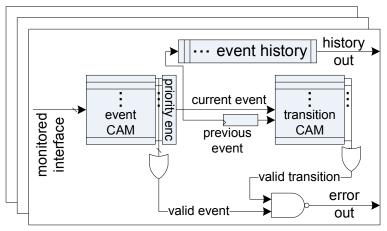

| 3.9  | Protocol detector hardware                                                  | 33 |

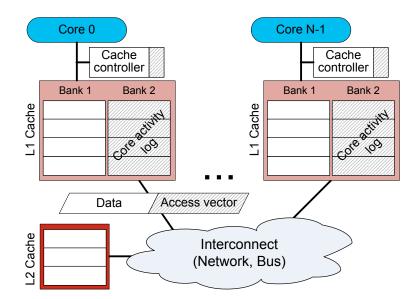

|      | CMP reconfiguration for Dacota validation                                   |    |

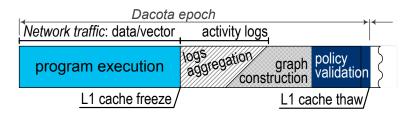

| 3.11 | Dacota execution flow                                                       | 37 |

| 3.12 | Graph construction algorithm                                                | 41 |

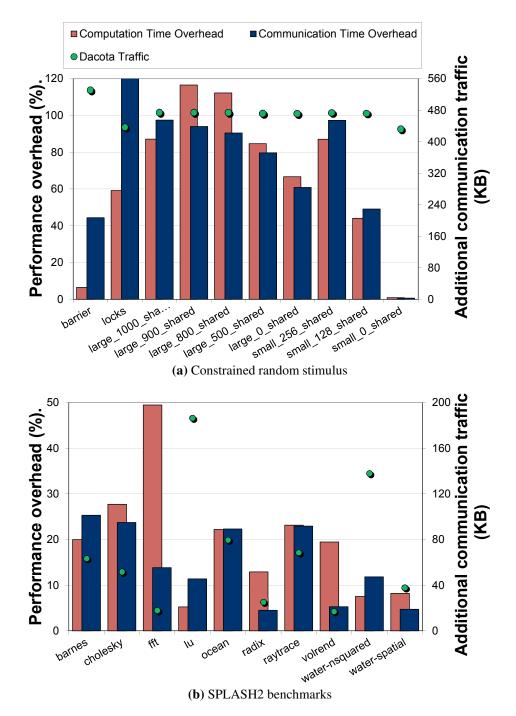

| 3.13 | Dacota performance overhead                                                 | 44 |

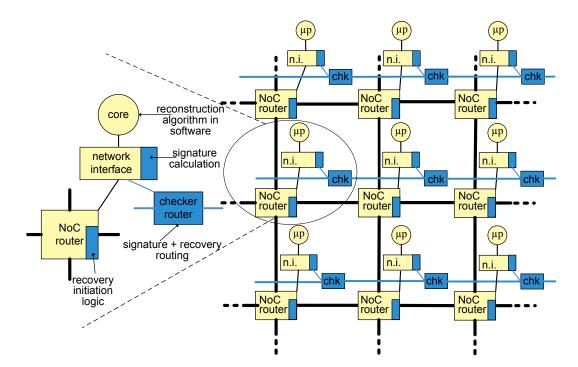

| 3.14 | High-level overview of SafeNoC                                              | 47 |

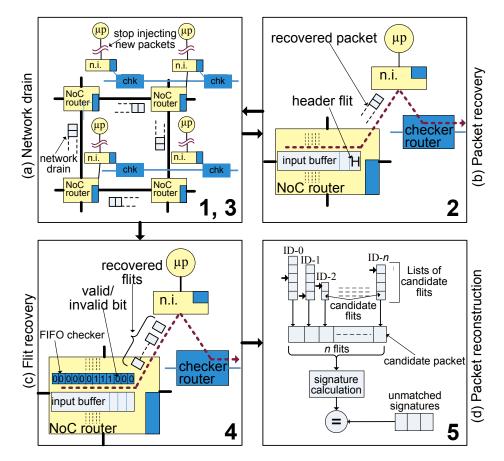

| 3.15 | SafeNoC recovery process                                                    | 49 |

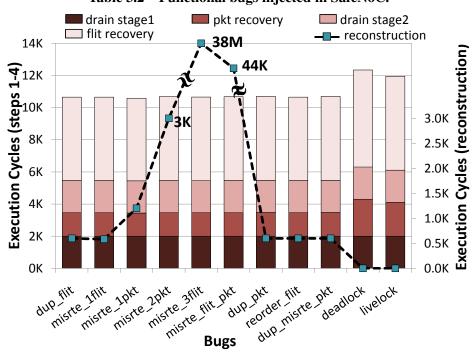

| 3.16 | SafeNoC recovery time by bug                                                | 51 |

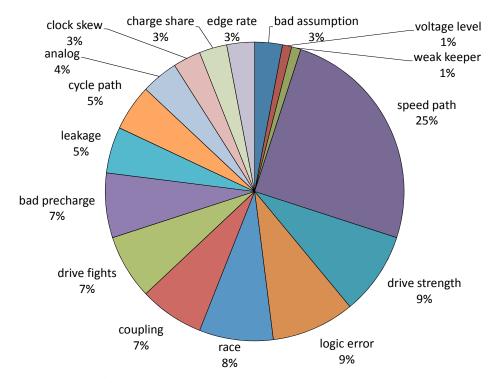

| 4.1  | Electrical failure root causes                                              | 56 |

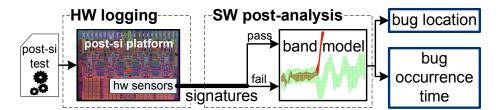

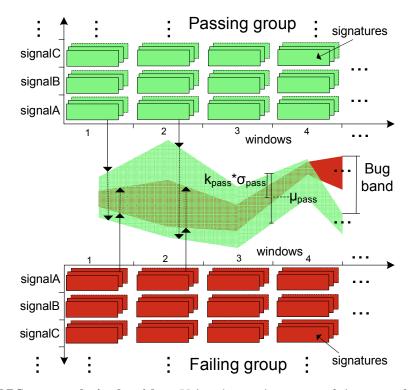

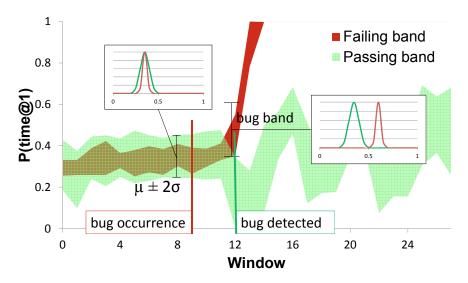

| 4.2  | BPS operation                                                               | 59 |

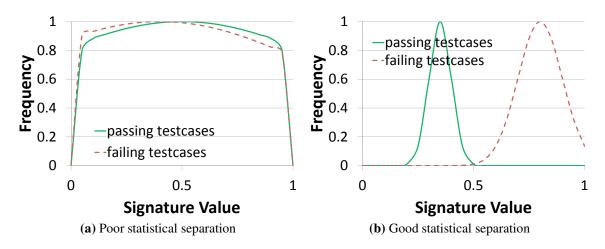

| 4.3  | Comparison of typical distributions with different signatures               | 60 |

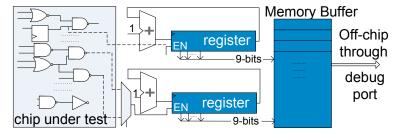

| 4.4  | BPS Hardware                                                                | 61 |

| 4.5  | BPS post-analysis algorithm                                                 |    |

| 4.6  | BPS band model                                                              |    |

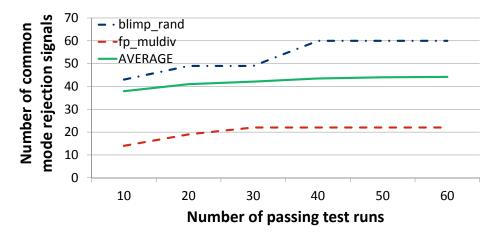

| 4.7  | Number of common mode rejection signals                                     | 64 |

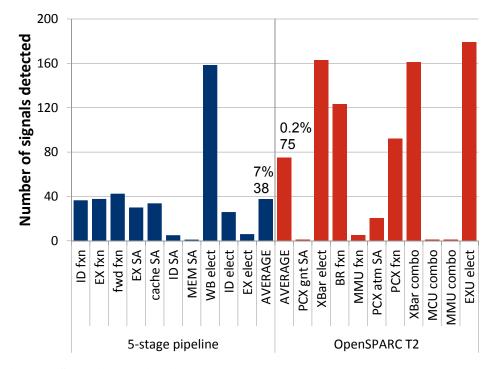

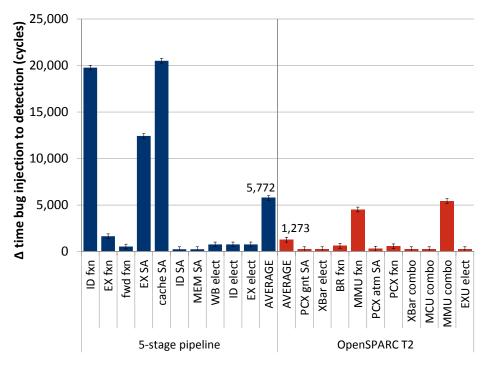

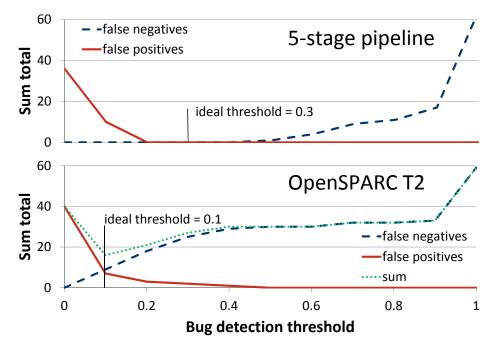

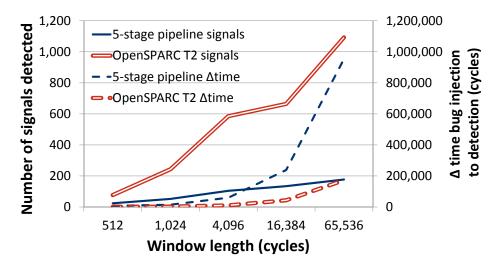

| 4.11 | BPS spatial localization69BPS temporal localization70Bug band threshold and quality of results71Population size and quality of results72Impact of window length on quality of results73 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | Transistor faults are addressed in four steps                                                                                                                                           |

| 5.2  | Wear-out mechanisms                                                                                                                                                                     |

| 5.3  | Hypothetical "bathtub curve"                                                                                                                                                            |

| 5.4  | Fault model                                                                                                                                                                             |

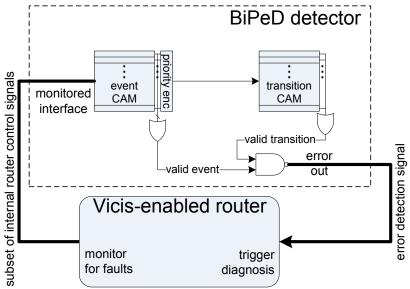

| 5.5  | BiPeD error detection connected to the Vicis architecture                                                                                                                               |

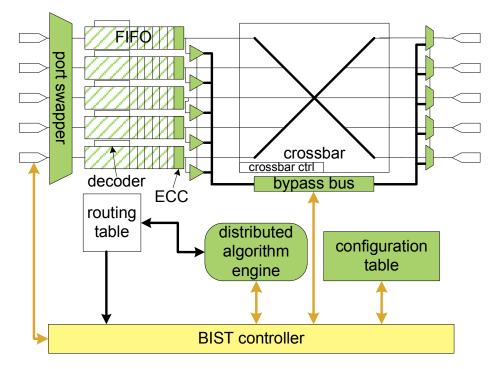

| 5.6  | Vicis router architecture                                                                                                                                                               |

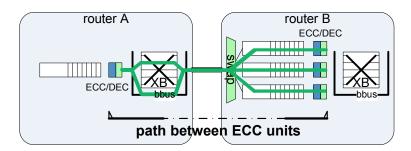

| 5.7  | Faults mitigated by ECC                                                                                                                                                                 |

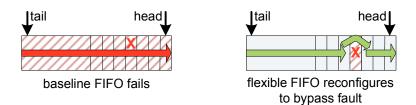

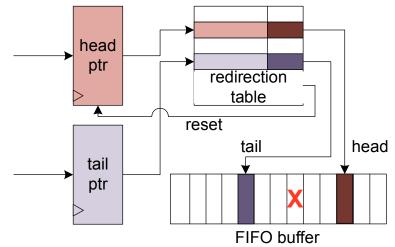

| 5.8  | Flexible FIFO design                                                                                                                                                                    |

| 5.9  | Flexible FIFO buffer logic    87                                                                                                                                                        |

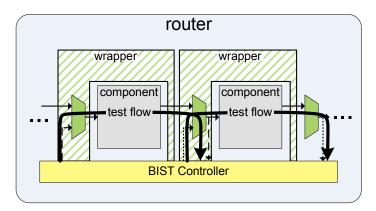

|      | Interlocking router unit wrappers                                                                                                                                                       |

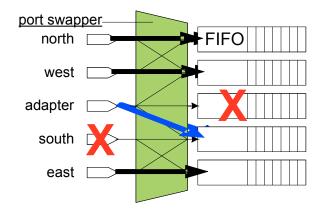

|      | Port swapping unit                                                                                                                                                                      |

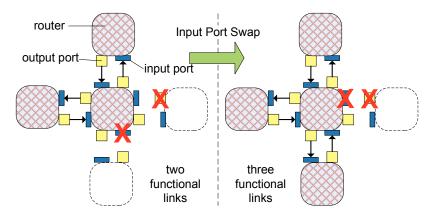

|      | Port swapping example                                                                                                                                                                   |

|      | Port-swapping algorithm pseudocode                                                                                                                                                      |

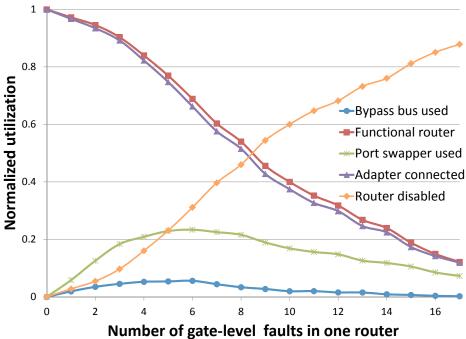

| 5.14 | Utilization of reliability features                                                                                                                                                     |

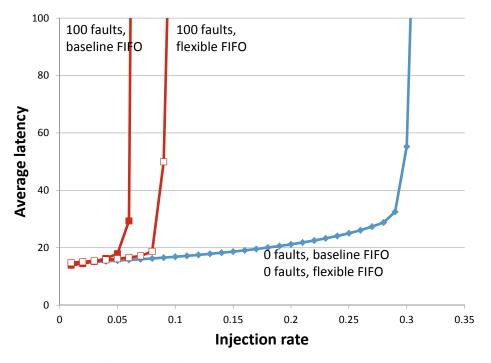

|      | Impact of flexible FIFO design                                                                                                                                                          |

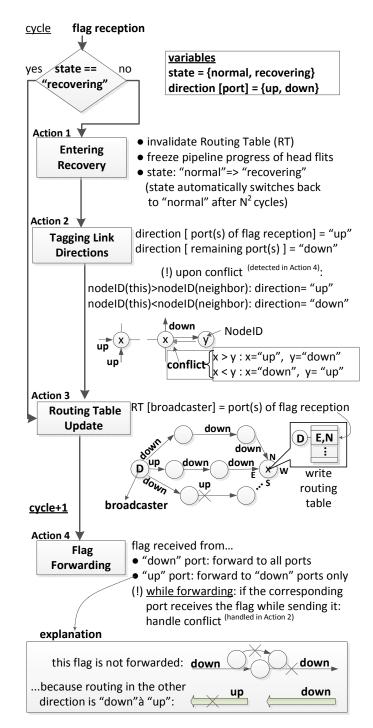

| 5.16 | Ariadne reconfiguration algorithm                                                                                                                                                       |

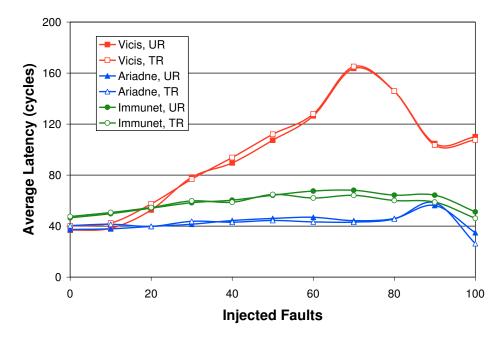

| 5.17 | Zero load latency with synthetic traffic                                                                                                                                                |

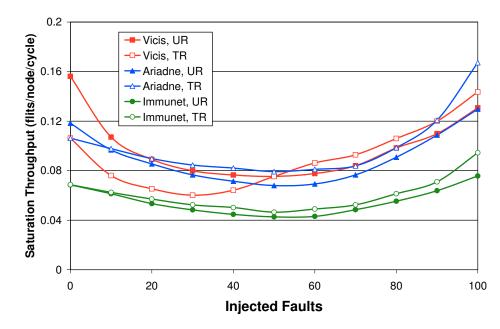

|      | Saturation throughput with synthetic traffic                                                                                                                                            |

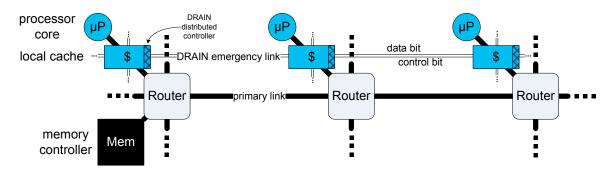

|      | Drain-enabled system                                                                                                                                                                    |

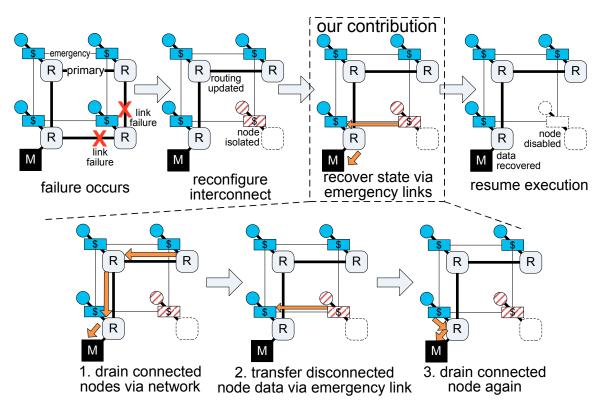

|      | Drain system operation                                                                                                                                                                  |

|      | Drain uses an emergency link                                                                                                                                                            |

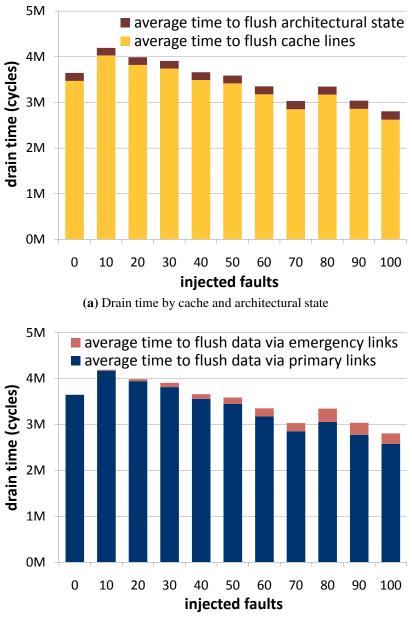

| 5.22 | Cycles to drain the entire network                                                                                                                                                      |

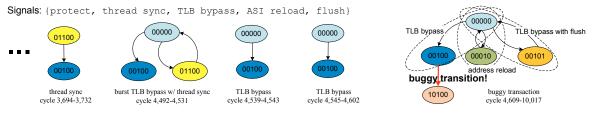

| 6.1  | Transaction history example                                                                                                                                                             |

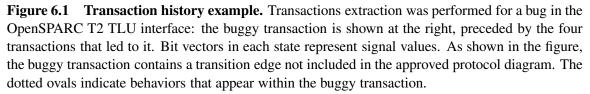

| 6.2  | Protocol extraction                                                                                                                                                                     |

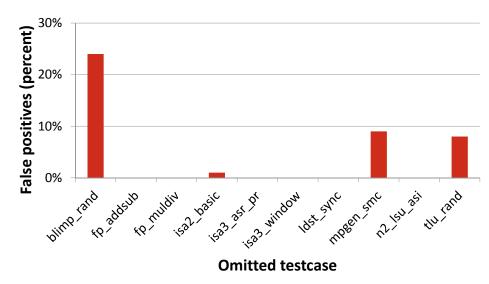

| 6.3  | Effect of leave-one-out-cross-validation                                                                                                                                                |

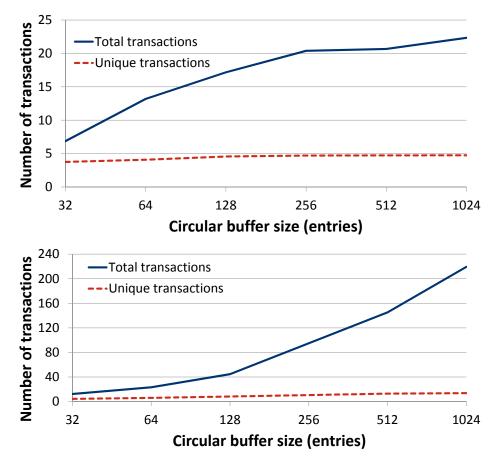

| 6.4  | Transactions extracted from the circular buffer                                                                                                                                         |

| 7.1  | Review of the solution framework proposed by this dissertation                                                                                                                          |

## **List of Tables**

#### Table

| 3.1 | Design error coverage by Dacota         |

|-----|-----------------------------------------|

| 3.2 | Functional bugs injected in SafeNoC     |

| 4.1 | Designs and modeled failures            |

| 4.2 | Workloads for both experimental designs |

| 4.3 | BPS signal localization                 |

| 5.1 | Fault model                             |

| 5.2 | Area of the baseline router             |

| 5.3 | Area breakdown of Vicis router          |

| 5.4 | Experimental setup                      |

| 5.5 | Additional gates                        |

| 6.1 | Workloads used for evaluation           |

| 6.2 | Monitored interfaces                    |

| 6.3 | Bugs injected                           |

| 6.4 | Bug detection latency                   |

| 6.5 | Area comprised by one protocol detector |

### **Chapter 1**

# Microprocessor Errors and Opportunities to Mitigate Them

We rely on unreliable devices. Digital computers are at the heart of the phones we use to communicate with each other; they run banking and stock market systems for business and commerce. Automobiles and airplanes are dependent on computer systems for engine function and navigation, and computers can even be involved in international conflict, as was the case with the STUXNET virus [49]. However, there are many challenges to the correct operation of these devices.

Modern computer chips are vastly complex systems comprised of billions of tiny transistors: they are the most complex artifact yet created by man. The doubling of the number of transistors every 18 months driven by Moore's law has moved processor designs from 2,300 transistors with the Intel 4004 in 1971 to recent Intel microprocessors with 2.6 billion transistors. Large transistor counts give rise to today's chip multi-processors, incorporating many cores on one die. Recent IBM chips, such as the POWER7 [126], contain 8 cores, and the Tilera Tile-Gx series ships with 100 cores. Intel has released two experimental chips: the 40 core Single-chip Cloud Computer (SCC) [97], as well as the 80 core Polaris [144].

As the number of cores in a single chip continues to rise, the complexity of these chips also increases. Cores must communicate in order to coordinate their efforts, and as a result, the communication subsystem becomes increasingly elaborate. This system is large, distributed and complex: thus, a large number of interactions must be verified during the design process. In 2008, a 16 core Sun chip required 100 person-years of verification [142], some Intel estimates are in the thousands of person-years [133], and estimates are rising. This daunting and incomplete verification task presents the risk of errors (bugs) escaping into final silicon. This is a prominent issue in processors, where design bugs are often detected after the release of the product, as can be noted in several processor errata documents [6, 68, 69, 67, 70].

In addition to increasingly risky bugs, shrinking transistors foment shrinking device reliability. Current microprocessors are available with transistor dimensions as small as 22nm, corresponding to less than 100 silicon atoms. With critical dimensions shrinking, only a few misplaced atoms may cause a catastrophic device failure. Thus, the possibility of transistors and wires wearing out in the field may soon become a reality.

Increasing core counts and decreasing transistor dimensions create a situation where the communication subsystem is a critical point of failure. Correct operation of this system is jeopardized by transistors susceptible to faults and latent design bugs.

### **1.1 Impact of Failures**

Design failures can have impact ranging from minor delays in a product's time-to-market, to the viability of an entire company. Failures can occur early in the development cycle, late in the cycle, or in the final product. Latent failures in the final chip can also be a security concern, opening new avenues for hackers to exploit a system.

Failures **early in the design process** are limited to problems with the functionality of the design, bugs that prevent it from working as expected. At this stage, the design is typically engineered through simulations: fixing a bug first involves understanding the issue. Then, the error can be fixed by modifying the source code. The impact of a bug caught late in this phase may be limited to a schedule delay of a few weeks or months.

Later in the design process, silicon prototypes are manufactured for fast, at-speed testing. Failures caught at this stage require re-tooling the manufacturing process for a modified design, called a re-spin. Re-spins may require several months of delay and are very expensive due to the high re-tooling cost, which can range from approximately \$3 million to \$30 million.

Following prototype testing, a new **chip can be shipped to customers**. At this late stage, failures have wide-spread and critical impact. A recall on a faulty product can take a year, at which point newer, competing products may already be available. The life of a company can be jeopardized by failures in the field. For example, the infamous Pentium FDIV bug was discovered in 1994. This bug caused some floating point division operations to compute the wrong result. Ultimately, the defective processors were recalled at a cost of \$475 million [94]. Some of the recalled processors were turned into commemorative key chains.

Transistor wear-out can also result in recalls: a recent Intel 6-Series chipset (codenamed Cougar Point) experienced a wear-out problem in the field. Prematurely aging transistors in one of the SATA controllers caused increasing errors on the link over time. The only fix was a recall in early 2011, at a cost upwards of \$1 billion.

### **1.2 Types of Errors**

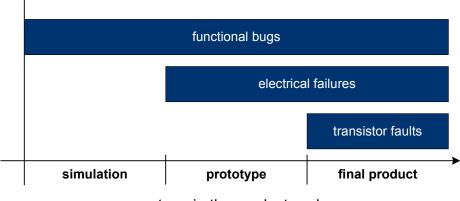

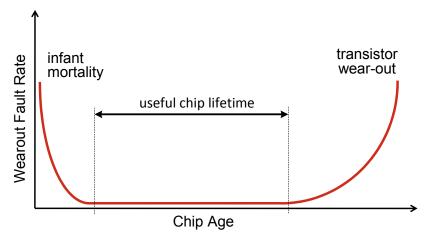

While all errors prevent the correct operation of the chip, their root causes can be different. This dissertation addresses three major categories of errors (Figure 1.1). At the highest level of abstraction, functional bugs are instances where the design does not conform to its specification. Electrical failures manifest at the circuit level, where gates do not perform as expected. Finally, at the lowest level of abstraction, transistor faults are visible as malfunctioning silicon devices or conductors.

stage in the product cycle

**Functional bugs** occur when the functionality of a design does not match its specification, or when the specification is incomplete. These failures are present in a digital design beginning with the first simulations. Functional bugs are deterministic and reproducible in simulation; however, real silicon prototypes may contain latent bugs that do not manifest deterministically due to environmental and electrical variations. An example of a functional bug is the previously mentioned Pentium FDIV bug, where some division operations produced the wrong result.

**Electrical failures** occur in circuits that do not meet voltage, current or timing constraints. This can be due to circuit design problems, as well as manufacturing defects, and occur most often in early silicon prototypes. Electrical errors include timing failures, where a signal does not reach its destination in time, and may also be due to insufficient

**Figure 1.1** Types of errors addressed by this dissertation and when they occur. Functional bugs, present from the very first design models, can be addressed in any phase of verification. Electrical failures begin to appear with the first prototypes, and transistor faults due to wear-out occur only in the final product.

drive current or voltage distribution. The end result is a circuit that fails to produce the desired output under some conditions. On-chip conditions such as temperature and voltage vary from chip to chip, as well as with the executing program. Thus, electrical failures are not always deterministic. The time-consuming, manual process of debugging electrical failures is a critical barrier in a chip's time-to-market schedule [73].

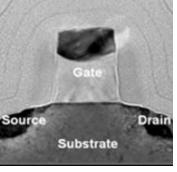

**Transistor faults** can be caused by a variety of wear-out mechanisms in highly scaled technology nodes. As transistor dimensions approach the atomic scale, oxide breakdown [136] becomes a concern, since the gate oxide tends to become less effective over time. Moreover, negative bias temperature instability (NBTI) [9] is of special concern in PMOS transistors, where increased threshold voltage occurs over time. Additionally, thin wires are susceptible to electromigration [58], because conductor material is gradually worn away during chip operation until an open circuit occurs. Since these mechanisms occur over time, traditional manufacturing tests and burn-in procedures are ineffective in detecting them. An example of a transistor failure is the Intel Cougar Point chipset recall discussed earlier.

This range of failures illustrates the variety of ways in which a digital design may err, despite the best intentions of designers and multi-billion dollar validation efforts. The goal of this work is to provide correct operation by addressing the three sub-problems of functional bugs, electrical failures and transistor faults.

#### **1.3** Avoiding Failures and Ensuring Correctness

Ensuring the correctness of a digital design spans the entirety of the design process. Beginning with abstract design models, manufacturers use simulation to conduct pre-silicon verification. Once early prototypes are available, engineers run tests on real silicon during post-silicon validation. Finally, runtime verification employs reliability-enhancing hardware features to check correctness as computation progresses. In the end, the goal of design verification is to ensure correction operation throughout the lifetime of the chip.

**Pre-silicon verification** operates on an abstract design model, and can be based on simulation or formal methods. Formal verification techniques rigorously prove that a design satisfies properties: theorem provers, model checkers and symbolic simulators are examples of formal tools. While these techniques are capable of checking the correctness of a design aspect under all possible execution situations, formal methods can only be deployed for very simple designs. With large designs, the state explosion problem occurs, due to the exponential memory requirements of formal tools. Additionally, formal verification is only as effective as the properties that are checked, a manual process susceptible to human limitations. Writing a complete set of formal properties for a large design can even require more time than the design itself. Today, formal verification is limited to abstraction versions of the design, such as the Mur $\varphi$  [44] tool.

In contrast to formal tools, simulation-based verification is the mainstream approach used in industry to validate large designs and correct any design errors. Here, a model of the design is simulated using hand-written programs or constrained-random inputs. Due to the complexity of the design state space, only a small fraction of the design's functionality can be validated within the available development time window. Bugs at this stage are easier to diagnose than in real silicon, since simulation has the advantage of being fully deterministic and fully observable. Failing testcases can be reliably reproduced to diagnose functional bugs, which in turn manifest consistently. Unfortunately, the slow speed of pre-silicon simulation limits verification to a small set of very short testcases, despite the deployment of large server farms devoted to the task.

**Post-silicon validation** begins when the first silicon prototypes become available. Here, long programs such as operating systems, as well as extensive constrained-random tests, can be executed directly on the prototypes, which are orders of magnitude faster than pre-silicon simulation. Fast execution speed enables high coverage testing at this stage. Tests outcomes are validated with a mix of hardware assertions, comparison of test outputs against a golden model, or with the aid of self-checking mechanisms. A test failure indicates an error, which can be functional, electrical (process, logic or circuit related), or due to a missed manufacturing defect. To diagnose the error, validation engineers must re-run the failed test with the support of a post-silicon validation hardware platform that provides a limited amount of control of test advancement and debugging features, such as on-chip logic analyzers and/or configurable embedded checkers [2, 110]. However, post-silicon failure diagnosis is notoriously difficult, especially when targeting tests that do not fail consistently over multiple runs. The limited observability and controllability characteristics of post-silicon further exacerbate this challenge, making post-silicon diagnosis one of the most difficult tasks of the entire validation effort.

**Runtime verification** solutions have been proposed by the research community to detect and correct failures in the final product. A common trait of these solutions is the use of on-chip checkers to detect functional bugs and transistor faults [147, 148, 14]. If an error is detected, most solutions will provide a correction mechanism, which enables the processor to overcome the errant configuration at a performance cost. Hence, the impact of an error in a hardware module protected by an online verification mechanism is limited to performance degradation, rather than incorrect results or, possibly, a system crash. Thus, a

key benefit of these runtime verification solutions is that they enable the verification team to focus its efforts on the design's execution scenarios that arise most frequently.

Furthermore, runtime approaches are the only type of solution able to handle faults caused by transistor wear-out. Since these faults only occur after substantial time and us-age, traditional burn-in and manufacturing tests at the factor are unable to mitigate wear-out related errors. Failure mechanisms such as oxide breakdown [136], negative bias temper-ature instability (NBTI) [9] and electromigration [58] all result in errors occurring later in the lifetime of the chip. Thus, runtime solutions are required to alleviate these errors. In the end, runtime verification enhances the reliability of the final chip, making it resilient to functional bugs, electrical failures, and transistor faults.

#### **1.4 Dissertation Overview**

Digital designs today face increasing complexity and decreasing reliability, which challenge the ability of the current design process to deliver a correct product that can function for years. This dissertation develops a number of solutions that work together in a novel validation framework. Called BiPeD, this framework addresses the problem of correctness within the communication subsystem of a chip multi-processor. The components of our solution are multi-pronged, leveraging opportunities in pre-silicon, post-silicon, and runtime verification. As a whole, they take on the complexity of modern designs by automating and accelerating the verification process, increasing the understanding of the design, and easing debugging. This enables increased coverage, thereby decreasing bugs in the final product. Furthermore, our approach is a long-term solution aware of the lifetime reliability challenges of fragile chips in the field.

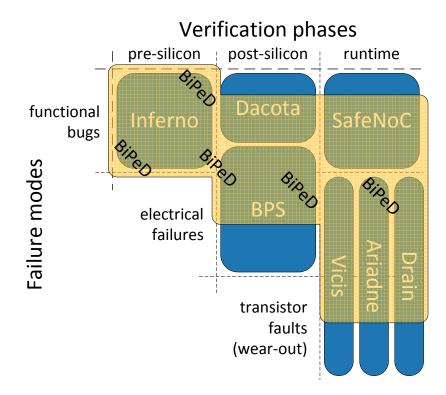

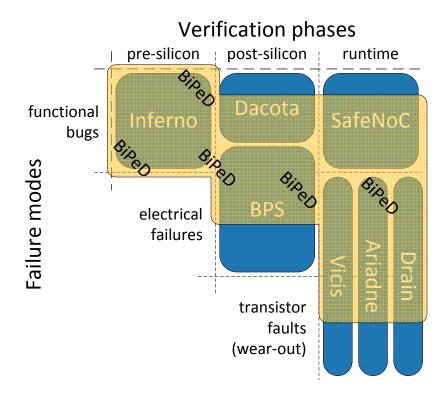

Figure 1.2 shows an overview of the solution proposed in this dissertation, which synergizes the different phases of verification to address a variety of errors. The figure divides correctness problems into three failure modes: functional, electrical and transistor (vertical axis). Electrical failures also include manufacturing defects that have escaped line testing, and transistor faults indicate errors that occur due to wear-out. Our solution leverages three verification stages to provide a comprehensive solution, beginning with pre-silicon verification (horizontal axis). Post-silicon validation allows testing of early chips, and runtime solutions enable resilience to transistor faults. The integral components of our solution are completely covered by the shaded region, while complementary parts are partially covered.

In Chapters 3 - 5, we discuss new solutions that address these errors, and how they fit into the BiPeD framework. We evaluate this framework in more detail in Chapter 6,

**Figure 1.2** Overview of the solution framework proposed by this dissertation, which synergizes the different phases of verification within the BiPeD framework to address three modes of failure: functional bugs, electrical failures and transistor faults (vertical axis). To accomplish this, it leverages opportunities in the three phases of verification, pre-silicon, post-silicon and runtime (horizontal axis). Integral component solutions to the BiPeD framework are completely shaded, while complementary solutions are partially shaded.

bringing together the different phases of verification, enabling reuse of verification effort and deploying multipurpose verification hardware.

#### **1.5** Dissertation Organization

The remainder of this dissertation is organized by error type. First, Chapter 2 presents a look at the current state of the art in verification. It describes the process by which modern microprocessors are designed and verified using pre-silicon verification, post-silicon validation, and runtime verification. The three modes of failure are addressed in Chapters 3–5, following the flow of Figure 1.2.

Chapter 3 addresses functional bugs, which may be present from the first models of the design and persist through shipment, manifesting in customers' chips. Thus, we take advantage of all three phases of verification to address functional bugs. During pre-silicon verification, we establish an abstraction that defines the correct behavior of the system protocols. This integral part of the BiPeD framework is a software tool for aiding the understanding of the complex protocols that make up the communication subsystem (Section 3.2). The protocols learned during pre-silicon verification are then leveraged by BiPeD during high-speed post-silicon validation, where flexible hardware monitors the on-chip protocols. When an error is detected, Dacota (Section 3.4) is applied to narrow down the source, targeting communication orderings, a common source of errors. Finally, we propose a solution to ensure end-to-end correctness of a network-on-chip communication infrastructure with SafeNoC (Section 3.5).

We address electrical failures in Chapter 4, which may be present beginning with the first silicon prototypes. First, flexible BiPeD hardware detects the occurrence of failures. Then, we invoke BPS, a method to debug and narrow down these difficult errors (Section 4.3) during post-silicon validation. When electrical failures escape post-silicon validation, a runtime solution can address both electrical failures and transistor faults simultaneously.

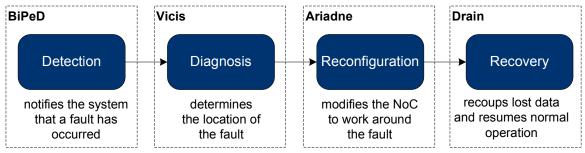

Transistor faults are discussed in Chapter 5. Runtime verification is the only chance to mitigate wear-out induced transistor faults. Our approach begins by once again leveraging BiPeD's flexible hardware to detect faults. Next, the fault location is diagnosed by Vicis (Section 5.3). Following diagnosis, Ariadne reconfigures around the faults (Section 5.4, and Drain recovers lost data (Section 5.5).

After addressing the three types of errors, we evaluate our BiPeD framework in Chapter 6, which bridges the phases of verification. BiPeD automates understanding the design during pre-silicon verification, and leverages this information to detect errors and debug during post-silicon validation. At runtime, flexible hardware previously used for postsilicon debugging is repurposed as an error detection mechanism. Finally, Chapter 7 briefly summarizes the conclusions of this dissertation.

# Chapter 2 Verification: State of the Art

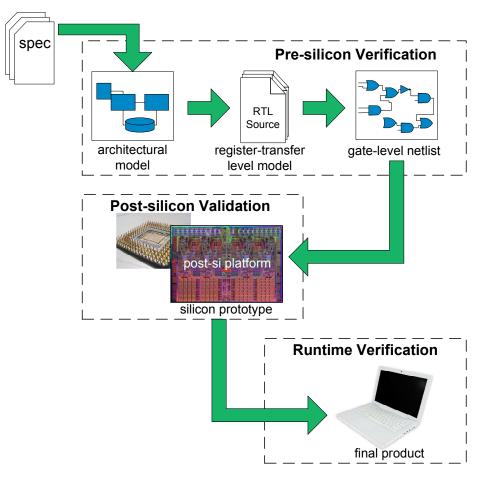

The design and manufacture of a microprocessor consists of a series of steps which transform a high-level description of the design into a physical chip. The complexity of microprocessors increases with each generation of chips, bringing new design verification challenges. A typical design verification flow for microprocessors is shown in Figure 2.1, and begins with a specification, a high-level prose description of the desired functionality. First, an architectural model is created from the specification, simulating the functional input/output behavior of the future chip. This model is often written in a high-level programming language, such as C, and is used to refine the details of the specification. It is also used as a reference model for the next steps. As the design cycle continues, a register transfer level (RTL) model is created. This detailed, cycle-accurate model describes the logic and storage that will comprise the chip, and is written in a low-level hardware description language (HDL), such as Verilog or VHDL. Pre-silicon verification is used to locate functional bugs in both the architectural model and the RTL model. This process involves running tests on both models simultaneously and comparing the results. In addition to testing the models through simulation, formal techniques are applied to prove design properties. This is used to prove the absence of certain types of errors. Unfortunately, these techniques do not scale to the size of modern designs.

The next steps transform the HDL model into a silicon prototype. When the first prototypes are available, post-silicon validation begins, where tests are run at full speed on real hardware. At this stage, it is possible to run much longer tests, which are no longer constrained by the slow execution speeds of pre-silicon simulation. Long constrained random tests, operating systems and real application workloads are examples post-silicon tests. Bugs become more difficult to pinpoint during post-silicon validation, since only a few of the design's internal signals are observable. The majority of the design's signals are inaccessible outside the chip. Errors found at this stage include functional failures that escaped pre-silicon verification, and electrical failures that manifest in the chip's circuits. When an error is found during post-silicon validation, it is typically reproduced in the pre-silicon

**Figure 2.1** Typical design verification flow for a modern multi-core microprocessor, which transforms a high level specification to a final product. Three major phases of verification are available to achieve a correct final product: pre-silicon verification is used to verify early models, followed by post-silicon validation, which is performed on silicon prototypes. Finally, runtime verification operates as part of the final product.

model, and the RTL is modified to fix the error. Finally, a new prototype is manufactured, called a re-spin.

Multiple re-spins are often required, as bugs are discovered and fixed during postsilicon validation. When the rate of bug discovery slows and stabilizes, the design is deemed ready for shipment. Because of the vast complexity of a microprocessor design, it is not possible to test every aspect. Thus, designs are shipped with latent bugs. Furthermore, as transistor dimensions shrink, transistors becoming increasingly susceptible to wear-out faults. To mitigate these problems, runtime solutions are implemented as part of the design, enabling it self-check results, and recover from errors. Runtime approaches can be used to address latent function bugs, electrical failures, and transistor faults.

The verification problem can be divided into three major approaches: pre-silicon, postsilicon and runtime. During early design phases, pre-silicon verification is performed on design models, using either formal verification, or simulation-based verification. Next, post-silicon verification works on early silicon prototypes. Runtime solutions ensure correct functionality in the shipped product. Despite these efforts, bugs still slip through the verification process. In addition to the three major approaches to hardware verification, solutions from software verification offer some insights into the verification of hardware. The next sections go into detail on each of these three verification approaches, and discuss the verification target: the communication subsystem.

#### 2.1 **Pre-Silicon Verification**

Pre-silicon verification is used to discover and fix errors in early design models. Since no prototypes are yet available, it is limited to finding functional bugs. There are two major types of pre-silicon verification, formal methods and simulation-based verification.

#### 2.1.1 Formal Methods

Formal verification methods exhaustively prove that a design satisfies properties under all conditions. It has the advantage of being able to prove that a portion of the design is bug-free, however, it has significant drawbacks that prevent it from being applied to large designs.

One of the mainstream tools used by the EDA community to analyze complex graphs is model checking, a formal verification technique used to rigorously prove properties of a hardware design. Model checking has the ability to reason about a data set using properties, which are formal descriptions of a particular functionality of a design. Properties are verified by the model checker against an internal mathematical representation of the input design. Model checking uses specialized formalisms and logics to reason about graphs. These include including computation tree logic (CTL) and linear temporal logic (LTL) [32]. Formal verification of the memory subsystem notably includes several notable approaches [3, 57, 44, 114].

The first and foremost problem with formal verification is scaling. Formal verification suffers from state space explosion, since the techniques require exponential memory to implement. Furthermore, formal verification tools require a set of properties to prove. The quality and completeness of the properties is directly related to the quality and completeness of the verification exercise. Moreover, while formal verification of abstract representations has been accomplished with success, its results are inadequate, as the implementations of these abstract models are much more complex and cannot be validated. For these reasons, formal verification is limited in practice to very small design blocks, leaving the large, system-level properties to slow, incomplete pre-silicon simulation.

#### 2.1.2 Simulation-based Verification

Logic simulation is a central aspect of the modern integrated circuit development process. It is the primary tool used to validate a wide range of design aspects, foremost among these being the correctness of the system's functionality, both in its behavioral description, as well as in its structural (gate-level) one. Most industry design flows invest the largest portion of their time and resources precisely on this task [47], in an attempt to provide the best possible guarantee that the system satisfies its original functional specification. Large server farms, comprising thousands of machines, execute billions of cycles of simulation for months at a time.

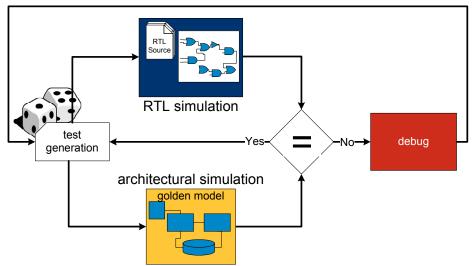

**Figure 2.2** Simulation-based pre-silicon verification for microprocessors is used heavily in industry. A constrained-random test generator produces valid, random programs, which are provided as input to both an RTL simulator and golden model. If the results match, testing continues, otherwise, the bug is fixed manually.

Simulation-based pre-silicon verification, shown in Figure 2.2, is the workhorse of modern pre-silicon verification of microprocessors. Typically, a constrained-random test generator produces input programs, which are run concurrently on an RTL model simulation, and on the architectural golden model. RTL simulations run much slower than architectural one, sometimes at slowdowns on the order of millions of times. When both simulations are complete, their outputs are compared, ensuring that final memory and architectural state match. In addition to checking results against an architectural model,

assertions augment the design under simulation, performing software checks as simulation progresses. When a check fails, the testcase stops, and the location of the failure is identified.

Despite the vast effort of time and resources, functional validation remains an incomplete task, with large portions of the design going unverified. Indeed, while common case scenarios are often checked in this process, buggy and rare corner cases frequently slip through validation, and are consequently latent in the final product, potentially causing malfunctions in the field.

#### **Logic Simulators**

Logic simulation entails evaluating the response of a design over time when subjected to a set of input stimuli, typically selected by the designer to be representative of practical use situations. For most synchronous designs the response is computed once for each cycle of simulated execution. Modern logic simulators read in a design description, then "compile" it to produce machine code emulating the same functionality as the design's primitives, and finally optimize it to minimize the amount of computation required to provide the responses that the user wishes to observe. The input stimuli are commonly provided in the form of a testbench, that is, a program describing implicitly or explicitly the set of input values for each clock cycle of simulation. The testbench may be direct, where input values are selected by a verification engineer, or pseudo-random, that is, inputs are set by a generator abiding pre-set constraints and statistical distributions.

Simulators can be grouped into two families based on their internal architecture: *oblivious* simulators compute all gates (or logic) in the system during every simulation cycle and entail a simpler software design. Oblivious simulators have the advantage of low control overhead, but can spend significant computation time unnecessarily evaluating gates over and over whose output values do not change from cycle to cycle. *Event-driven* simulators limit the amount of computation by selectively simulating in each cycle only those gates who inputs have changed since the previous cycle, and whose output may thus change in response to the switching stimulus. While the sequencing of gate evaluation in oblivious simulation can be statically determined at compile-time, event-driven simulators require a dynamic runtime scheduler, hence entail a more complex software structure. However, this latter approach is vastly more common in commercial tools because the scheduler performance overhead is largely offset by the fact that for many designs only 1 to 10% of the gates switch at each cycle, thus requiring significantly less computation.

Simulation approaches, in contrast to formal methods, are able to tackle a much larger

portion of the design. For example, Wood, *et al.* [152] leverages constrained-random simulation to boost the coverage of a design. Here, there is the additional burden of understanding the interactions within a large design occurring throughout a long simulation. A number of previous works have focused on the problem of automatically extracting properties and specifications. Hangal, *et al.* [62] have proposed a tool to extract simple "probable" properties (*e.g.*, one-hot or mutually exclusive signals) through simulation trace analysis, which can then be fed to a formal property checker for verification. In [50], the authors propose a more general approach to automatic property extraction, by evaluating a wide range of possible "time relations" between groups of signals.

#### 2.2 Post-Silicon Validation

Following pre-silicon verification, post-silicon validation begins when the first prototype chips are available, and is used primarily to validate large microprocessor designs. It is the first opportunity to test a physical implementation of the design, and thus it is able to uncover problems with the design's circuits (electrical failures). Additionally, functional bugs that evaded pre-silicon verification may be identified at this stage.

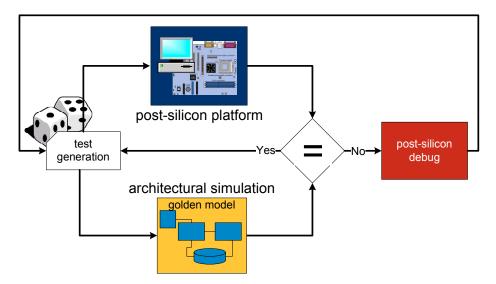

Post-silicon validation is conducted on prototype chips connected to specialized validation platforms (Figure 2.3). The platforms are used to run post-silicon tests, a mix of directed and constrained-random workloads. Upon completion of each test, the output of the silicon prototype is typically checked against an architectural simulator. When an error causes a check to fail, the debugging process begins, seeking to determine the root cause of the failure.

In industry practice, the post-silicon validation process begins when the first silicon prototypes become available. These chips are then connected to specialized validation plat-forms that facilitate running post-silicon tests, a mix of directed and constrained-random workloads. Upon completion of each test, the output of the silicon prototype is checked against an architectural simulator, or in some cases, self-checked [5, 146].

When a check fails, indicating that an error has occurred, the debugging process begins, seeking to determine the root cause of the failure. On-chip instrumentation can be used to observe intermediate signals. Techniques such as scan chains, on-chip logic analyzers [149] and flexible logging infrastructures [2] are configured to trace design signals (only a small number can usually be observed) and periodically transfer data off-chip. Traces are then examined by validation engineers to determine the root cause of the problem. This process is time-consuming and engineering intensive, and is further exacerbated by bugs

**Figure 2.3 Post-silicon validation flow** typical in industry. Like pre-silicon verification, a constrained-random test generator produces valid, random programs, which are provided as input to both the golden model and the silicon prototype. The prototype is connected to a validation platform that includes a host CPU. If the results match, testing continues, otherwise, the bug is fixed manually.

with inconsistent outcomes. Additionally, off-chip data transfers are very slow, which further hinders observability due to limited transfer time. Thus, our goal with this portion of the dissertation to reduce debugging effort, automatically diagnosing the time and location of bugs, while minimizing off-chip transfers.

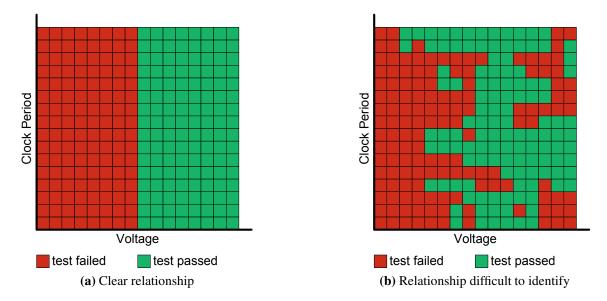

A powerful industry approach to locating electrical failures is the shmoo plot [13], which shows the relationship between chip failures and changes in environmental conditions. In a typical shmoo plot, two primary parameters are varied and assigned to the X and Y axis of the plot, respectively. For example, the parameters might be voltage and clock period. Then, a single test is run many times, with different parameter values, and the pass/fail status of the test is recorded. With some parameter value pairs, the test passes, with others, it fails. Figure 2.4 shows two theoretical examples of typical shmoo plots, with clock period and voltage as the parameters. Each cell in the plots represents the outcome of one test, with passing results in green, and failing results in red.

The debugging process of non-deterministic failures can be aided by deterministic replay mechanisms [104, 123]. However, these solutions perturb system execution which can prevent the bug from manifesting, and often incurs significant hardware and performance overheads. In addition, in an effort to automate the failure diagnosis process, methods based on formal verification techniques have been proposed [38, 77, 120, 156]. These solutions require deterministic execution and a complete golden (known-correct) model of the design for comparison. However, the limitations of formal methods discussed earlier

**Figure 2.4** Theoretical shmoo plots showing test pass/fail status as a function of two parameters, voltage and clock period. These plots are used to debug electrical failures during post-silicon validation. The left plot shows a clear relationship between the error and voltage, while the relationship in the right plot is not as clear. One goal of this dissertation is to help localize those bugs that are most difficult to reproduce.