# DESIGN TECHNIQUES FOR LOG BASED CLOSED-LOOP NEUROSTIMULATION SYSTEM-ON-CHIP

by

Hyo Gyuem Rhew

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctoral of Philosophy (Electrical Engineering) in The University of Michigan 2012

# **Doctoral Committee:**

Professor Michael P. Flynn, Chair Assistant Professor Parag G. Patil Assistant Professor David D. Wentzloff Assistant Professor Zhengya Zhang

All rights reserved

2012

To Mom, Dad, my sister and fianc éfor their endless love...

## Acknowledgements

I would like to express my sincere gratitude to my friends, colleagues, advisors and family for their care and support during my graduate study in Ann Arbor. First, I would like to thank my advisor Prof. Michael Flynn for introducing me to the research area and for guiding and encouraging me through the course of the research. I must confess that I am very fortunate to have an advisor like Prof. Flynn. Throughout the years of my graduate life he has not only been a good research advisor but also given me personal advice as a great mentor. I would also like to thank the rest of my committee members: Prof. Parag G. Patil for many discussions we had to design and refine this doctoral work, Prof. David D. Wentzloff for his invaluable feedback during all years of my graduate study and Prof. Zhengya Zhang for his interest and support for this research and helping me write a better dissertation.

I would like to thank Mr. Ram Sadhwani and Mr. Adil Kidwai from Intel for their great mentoring. I would also like to thank many people at Intel Corporation including Dr. Hasnain Lakdawala, Mr. Benjamin Jann, Mr. Sunny Sharma, Dr. Stephen Bruss, Dr. Satwik Patnaik, Dr. Ning Zhang, Dr. Thomas Brown, and Dr. Khartik Natarajan for sharing their time and expertise. I would also like to thank many people at Mediatek Incorporation including Mr. Michael Ashburn, Mr. Stacy Ho, Dr. Patrick Riehl, Dr. Jose Silva, and Dr. Ayman Shabra.

I would like to acknowledge the help of all EECS department staffs, especially Mrs. Beth Stalnaker, Mrs. Deborah Swartz and Mrs. Francis Doman. They provided tremendous amount of support while I was going through all kind of issues related to degree progress. I must express my gratitude to Joel VanLaven for supporting CAD systems. I would never be able to write these lines without their continuous support.

Much thanks must go to all of my former and current members of Prof. Flynn's group for their assistance in research and their heartfelt friendship: Dr. Sunghyun Park, Dr. Ivan Bogue, Dr. Dan Shi, Dr. JunYoung Park, Dr. Mark Ferriss, Dr. Joshua Kang, Dr. Jongwoo Lee, Dr. Shahrzad Naraghi, Andres Tamez, Dr. Chun Lee, Jorge Pernillo, Dr. David Lin, Dr. Li Li, Nick Collins, Jeffrey Fredenburg, Hyungil Chae, Mohammad Mahdi Ghahramani, Jaehun Jeong, Aaron Rocca, Chunyang Zhai, Yong Lim, and Batuhan Dayanik. I would like to thank especially Jaehun Jeong for his great work designing log-scale digital circuits. This thesis work could not be finished if it weren't for his invaluable help. I would also like to express my gratitude to my friends from all over the world I have made at Michigan for sharing their time with me which made my life in Michigan always happy and enjoyable. I would also like to thank people at the Eden Presbyterian Church of Oregon for their care and love.

I am very grateful to the Samsung Scholarship Foundation for providing me with a fellowship for my Ph.D. study. I also thank the Catalyst Foundation for supporting this work.

Most importantly, I want to say my thankfulness to my wonderful family and my fianc é My father, mother, sister, and Jiyeon believed in me with their endless love, support, encouragement and prayer. Above all I thank God for His grace and love.

# **Table of Contents**

| Dedic  | atio                        | on                                        | ii   |

|--------|-----------------------------|-------------------------------------------|------|

| Ackno  | owl                         | ledgements                                | iii  |

| List o | f Fi                        | igures                                    | vii  |

| List o | f Ta                        | ables                                     | xi   |

| List o | $\mathbf{f} \mathbf{A}_{]}$ | ppendices                                 | xii  |

| List o | f A                         | bbreviations                              | xiii |

| Abstr  | act                         | t                                         | XV   |

| Chap   | ter :                       | I                                         | 1    |

| -      | 1.                          | Introduction                              | 1    |

|        |                             | 1.1. Essential Tremor                     | 1    |

|        |                             | 1.2. Dystonia                             | 3    |

|        |                             | 1.3. Parkinson's Disease                  | 6    |

|        |                             | 1.4. Epilepsy                             | 8    |

|        |                             | 1.5. Deep Brain Stimulation (DBS)         | 10   |

|        |                             | 1.6. Closed-loop DBS                      | 13   |

|        |                             | 1.7. Dissertation outline                 | 16   |

| ,      | 2.                          | Design techniques for recording front-end | 18   |

|        |                             | 2.1. LNA                                  | 18   |

|        |                             | 2.2. Pipeline logarithmic ADC             | 24   |

| 3.            | Design techniques for a log-domain digital processing unit       | 35 |

|---------------|------------------------------------------------------------------|----|

|               | 3.1. Logarithmic digital signal process                          | 35 |

|               | 3.2. Logarithmic digital filter                                  | 38 |

|               | 3.3. Closed-loop stimulation controller                          | 41 |

| 4.            | Design techniques for a power management block                   | 44 |

|               | 4.1. RF-DC converter                                             | 45 |

|               | 4.2. LDO                                                         | 46 |

|               | 4.3. Bandgap voltage reference                                   | 48 |

| 5.            | Design techniques for other building blocks: current stimulator, |    |

|               | clock generator, and RF transceiver                              | 50 |

|               | 5.1. Current stimulator                                          | 50 |

|               | 5.2. Clock generator                                             | 52 |

|               | 5.3. RF Transceiver                                              | 54 |

| 6.            | Prototype system and performance measurements                    | 57 |

|               | 6.1. Proposed closed-loop DBS SoC architecture                   | 57 |

|               | 6.2. Prototype measurement results                               | 61 |

| 7.            | Conclusions                                                      | 70 |

|               | 7.1. Summary of the prototype performance                        | 71 |

|               | 7.2. Contributions                                               | 73 |

|               | 7.3. Future work                                                 | 74 |

| Appendi       | ces                                                              | 76 |

|               | aphy                                                             |    |

| $\mathcal{L}$ | <u>.                                     </u>                    |    |

# **List of Figures**

| Figure 1.1: A patient with essential tremor drawing the Archimedes spiral [6]           |

|-----------------------------------------------------------------------------------------|

| Figure 1.2: A person with medication induced dystonia.                                  |

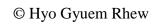

| Figure 1.3: Muhammad Ali and Michael J. Fox.                                            |

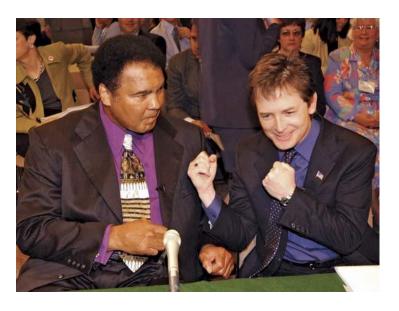

| Figure 1.4: Diminished substantia nigra in a patient with Parkinson's Disease [13]      |

| Figure 1.5: Woman with epileptic seizure.                                               |

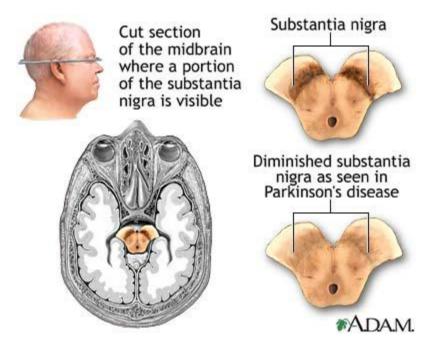

| Figure 1.6: Implantation of DBS system [23]                                             |

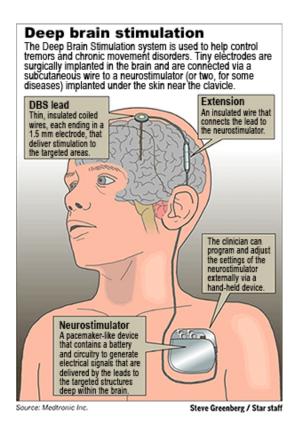

| Figure 1.7: Activa RC neurostimulator for Medtronic DBS therapy [25]                    |

| Figure 1.8: Titrating stimulation using a handheld programmer from Medtronic [28] 14    |

| Figure 2.1: A single-ended representation of the schematic of a band-pass amplifier 19  |

| Figure 2.2: Simulated frequency response of the general band-pass amplifier 20          |

| Figure 2.3: A differential representation of the schematic of a two-stage band-pass     |

| amplifier                                                                               |

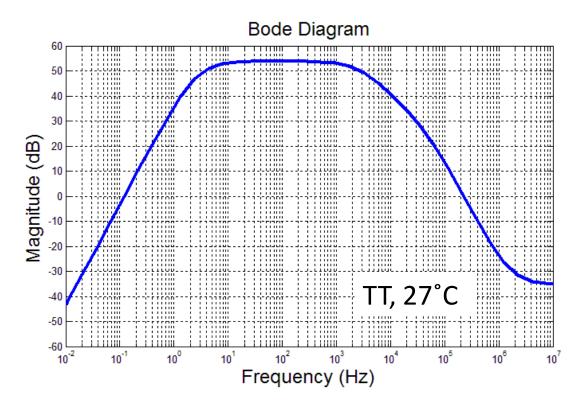

| Figure 2.4: Simulated frequency response of the designed two-stage band-pass LNA 23     |

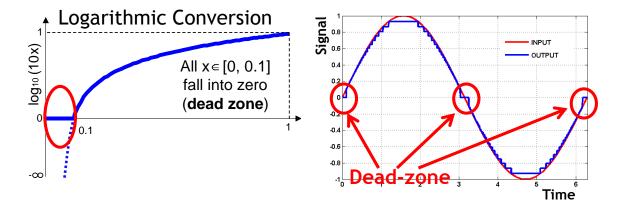

| Figure 2.5: Coding scheme of a 5-bit logarithmic ADC with $B=10$ (left) and output from |

| sinusoidal input shown with dead-zone effect (right)                                    |

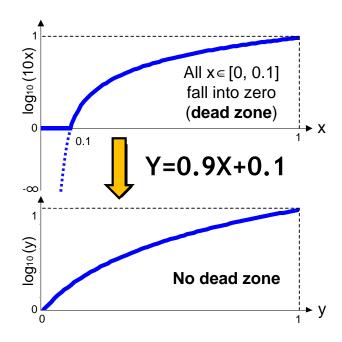

| Figure 2.6: Pre-conversion of input to eliminate the log dead-zone                      |

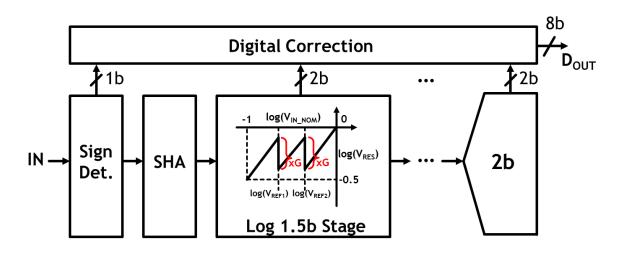

| Figure 2.7: Overall architecture of the 8-bit pipeline logarithmic ADC                  |

| Figure 2.8: Conceptual block diagram of the logarithmic 1.5-bit stage                   |

| Figure 2.9: Residue plot of the logarithmic 1.5-bit stage with $B=10$                   |

| Figure 2.10: Simplified schematic of SHA with $B=10$                                                 |

|------------------------------------------------------------------------------------------------------|

| Figure 2.11: Simplified schematic of a logarithmic 1.5-bit stage                                     |

| Figure 2.12: Schematic of bias circuits                                                              |

| Figure 3.1: Lookup table usage decision                                                              |

| Figure 3.2: Block diagram of digital logarithmic low-pass and high-pass filters 38                   |

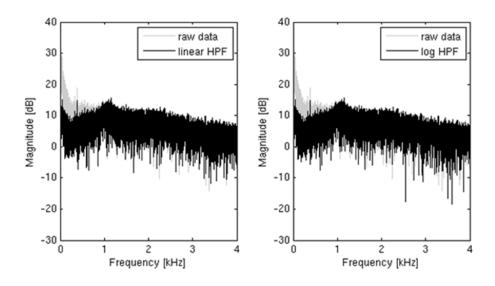

| Figure 3.3: Simulated output spectrums of the linear (left) and logarithmic (right) 15 <sup>th</sup> |

| order FIR LPF                                                                                        |

| Figure 3.4: Simulated output spectrums of the linear (left) and logarithmic (right) 15 <sup>th</sup> |

| order FIR HPF                                                                                        |

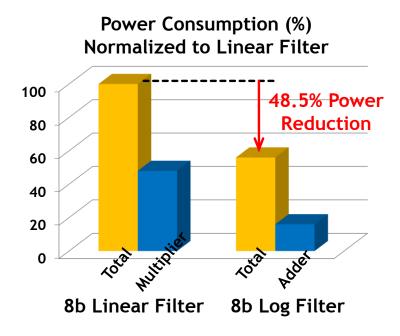

| Figure 3.5: Power consumption comparison of a linear-domain and a log-domain 10-bit                  |

| FIR digital filters                                                                                  |

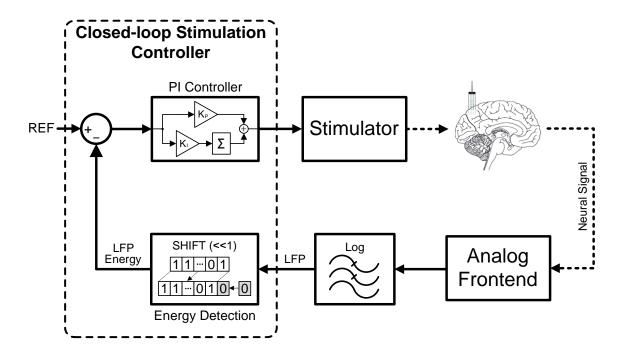

| Figure 3.6: Flow diagram of the proposed closed-loop stimulation that uses LFP energy                |

| information as a feedback indicator                                                                  |

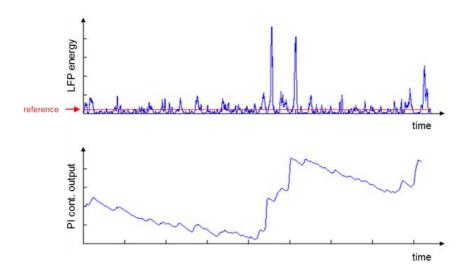

| Figure 3.7: Simulated transient input and output of the PI-controller with pre-recorded              |

| rat's neural data input                                                                              |

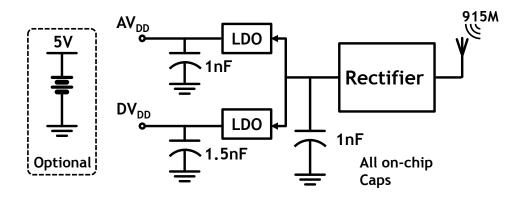

| Figure 4.1: Block diagram of the power management block of the closed-loop DBS                       |

| system that generates both analog and digital supply voltages from a 915MHz carrier 45               |

| Figure 4.2: Schematic of the full-wave rectifier that generates unregulated $V_{DD}$ of 2.2 $V_{DD}$ |

| from a 915MHz carrier                                                                                |

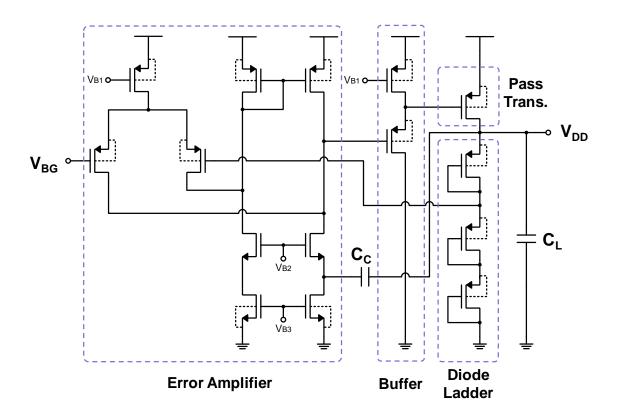

| Figure 4.3: Schematic of the LDO for analog domain voltage supply                                    |

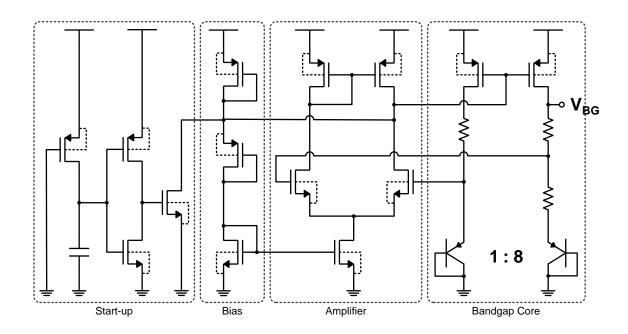

| Figure 4.4: Schematic of bandgap reference circuits                                                  |

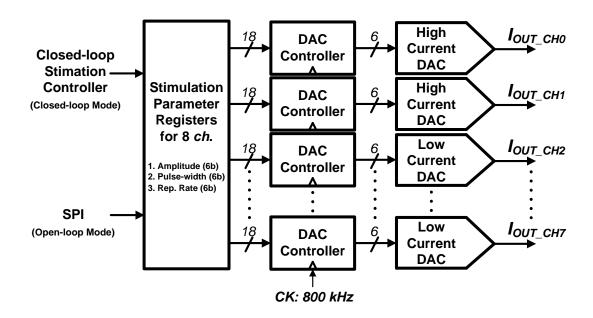

| Figure 5.1: Simplified block diagram of 8-channel current stimulator                                 |

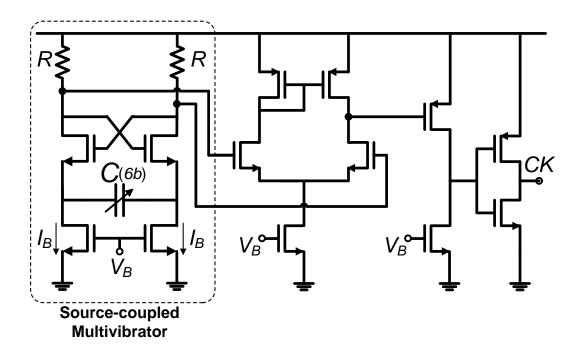

| Figure 5.2: Schematic of clock generator.                                                            |

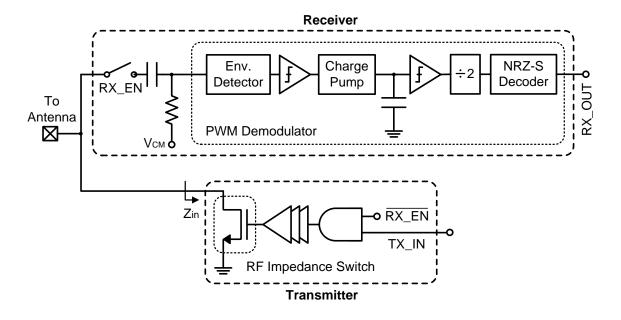

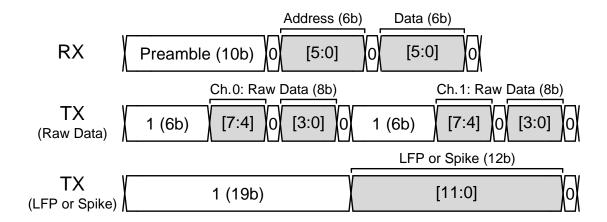

| Figure 5.3: Block diagram of RF transceiver                                                 | 55     |

|---------------------------------------------------------------------------------------------|--------|

| Figure 5.4: Communication protocol for RF telemetry.                                        | 56     |

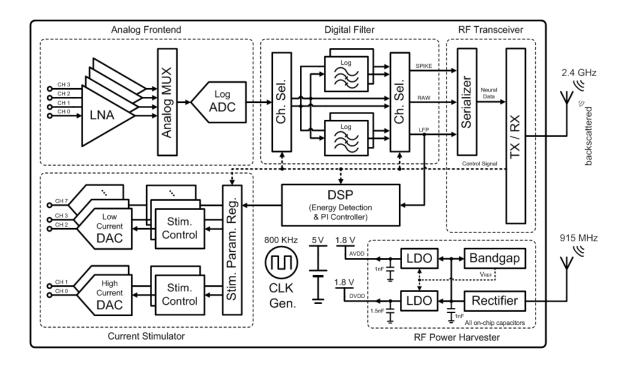

| Figure 6.1: Overall system block diagram of the proposed log-based closed-loop              | DBS    |

| system.                                                                                     | 58     |

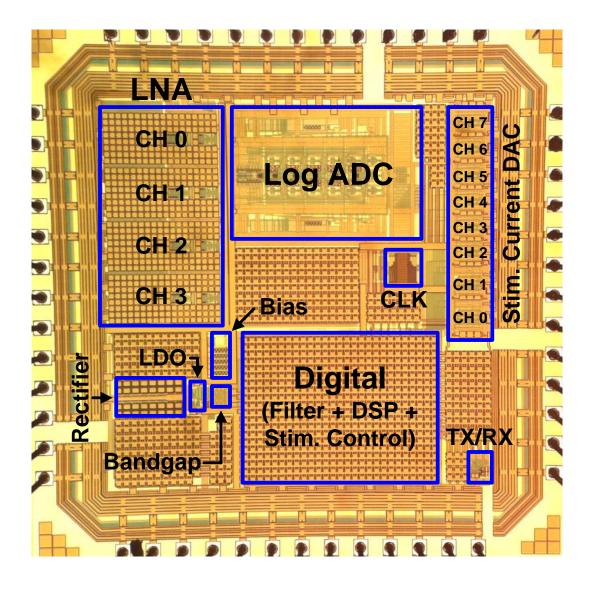

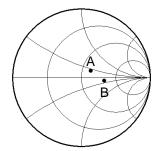

| Figure 6.2: Die micrograph of the prototype log-based closed-loop DBS system                | 60     |

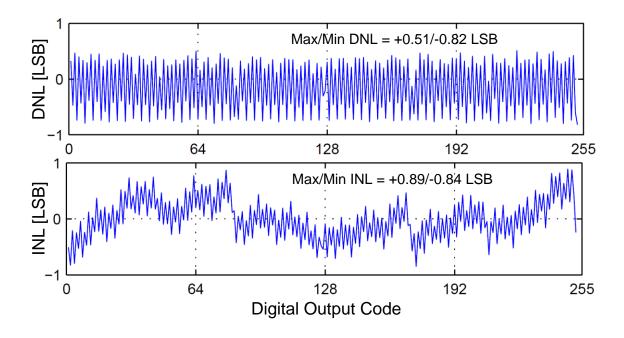

| Figure 6.3: Measured DNL and INL of the designed AFE (4-ch. LNAs + log ADC)                 | 61     |

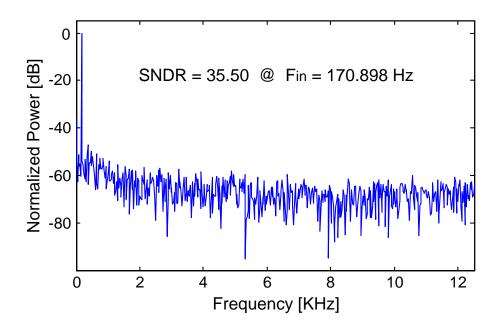

| Figure 6.4: Measured output spectrum of the designed AFE (4-ch. LNAs + log ADC)             | 62     |

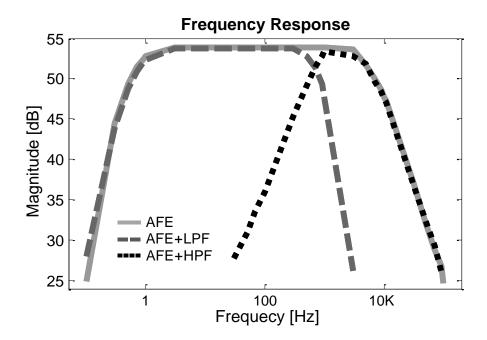

| Figure 6.5: Measured frequency response of the designed recording path (AFE + di            | gital  |

| log-filters).                                                                               | 63     |

| Figure 6.6: Recorded output of the designed recording path (AFE + digital log-fil           | lters) |

| with a pre-recorded neural signal from a rodent's brain applied as input to the system.     | 64     |

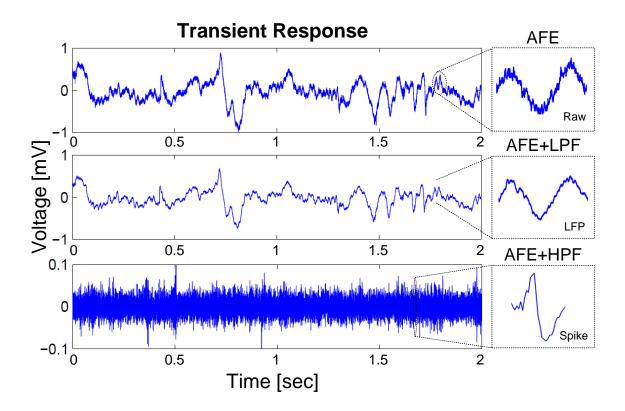

| Figure 6.7: Measured stimulation current waveforms of low-current and high-cur              | rrent  |

| stimulation channels with 6.23 $k\Omega$ and 220 $\Omega$ respectively                      | 65     |

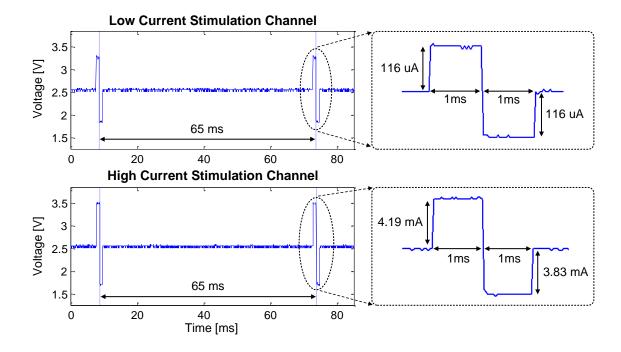

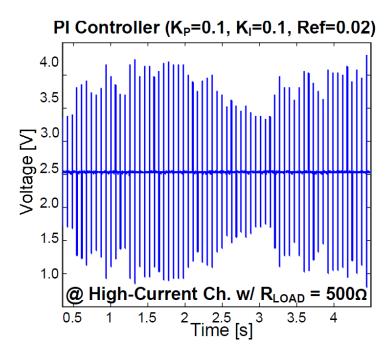

| Figure 6.8: Measured stimulation current waveforms of a high-current stimula                | ation  |

| channel in closed-loop mode using LFP energy detection with a 220 $\varOmega$ resistor load | 66     |

| Figure 6.9: Measured input impedance changed from backscatter modulation of                 | f the  |

| transceiver                                                                                 | 67     |

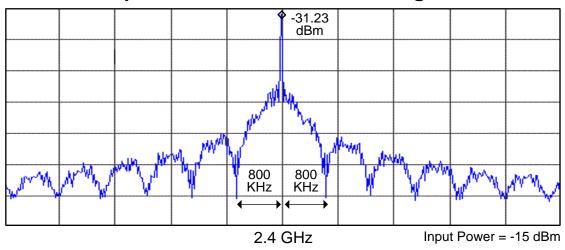

| Figure 6.10: Measured output spectrum of the backscatter transceiver                        | 68     |

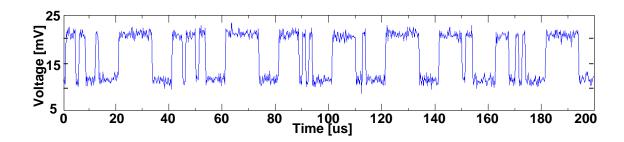

| Figure 6.11: Measured recovered data bit-stream from the backscatter transmitter            | 68     |

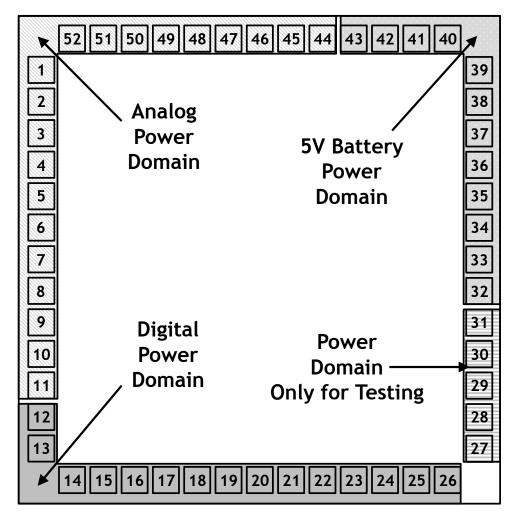

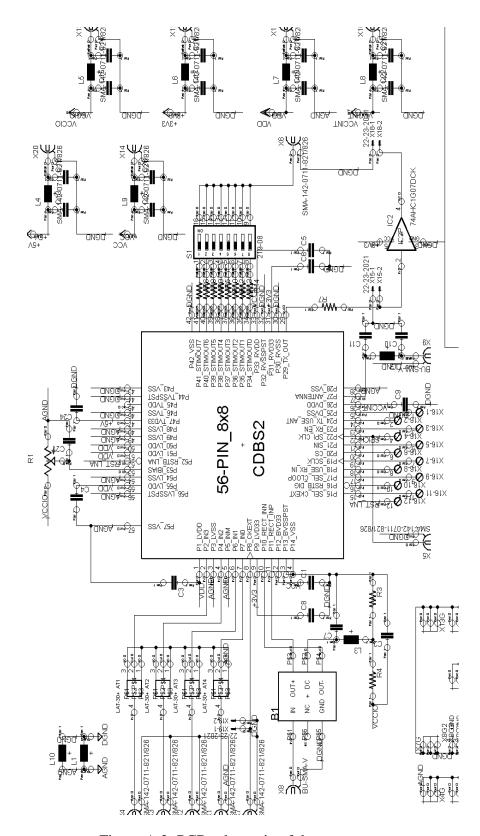

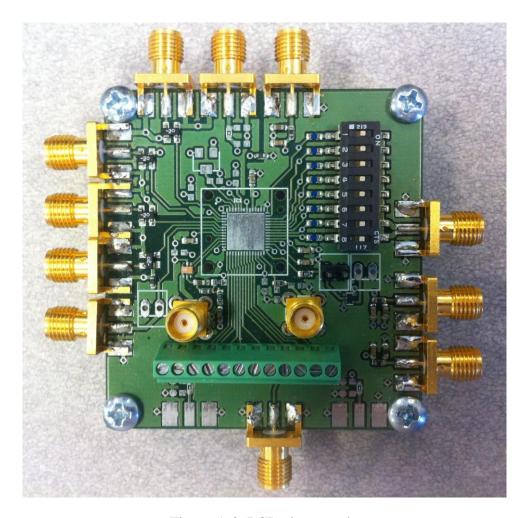

| Figure A.1: IO pad of the closed-loop neurostimulation SoC prototype                        | 78     |

| Figure A.2: PCB schematic of the prototype.                                                 | 82     |

| Figure A.3: PCB photograph.                                                                 | 84     |

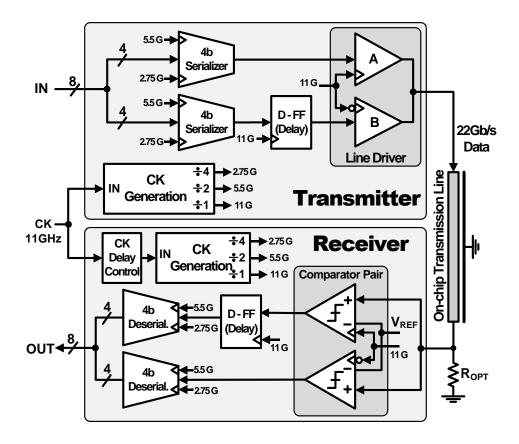

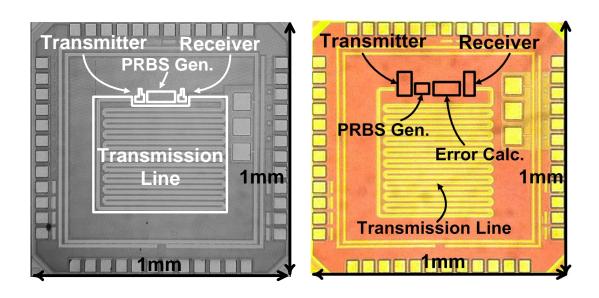

| Figure B.4: Transceiver architecture with an on-chip transmission line link terminated            |

|---------------------------------------------------------------------------------------------------|

| with optimal resistance.                                                                          |

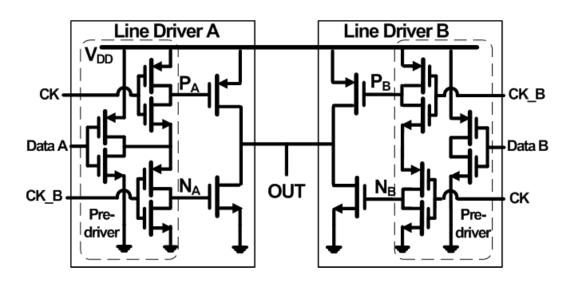

| Figure B.5: Interleaved voltage-mode line drivers: A, B                                           |

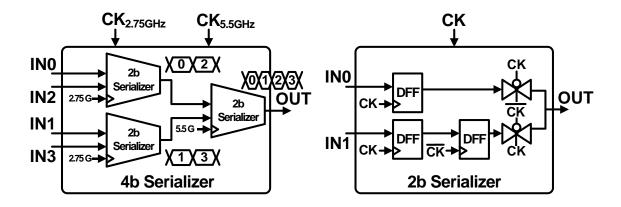

| Figure B.6: Block diagrams of 4b-to-1b serializer and 2b-to-1b serializer                         |

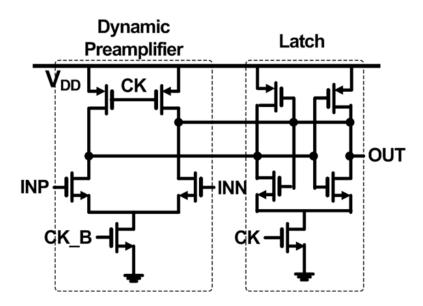

| Figure B.7: Schematic of comparator of high-speed serial link                                     |

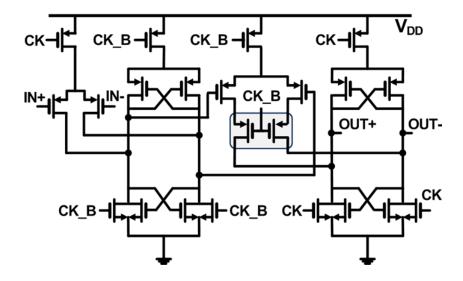

| Figure B.8: Schematic of comparator of low-power serial link                                      |

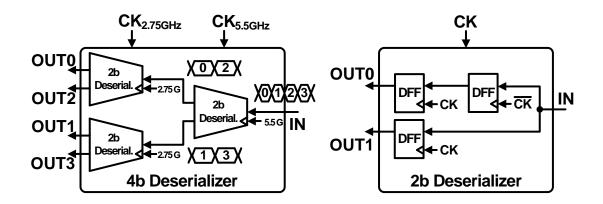

| Figure B.9: Block diagrams of 1b-to-4b deserializer and 4b-to-1b deserializer                     |

| Figure B.10: Die micrographs of low-power type serial link (left) and high-speed type             |

| serial link (right)                                                                               |

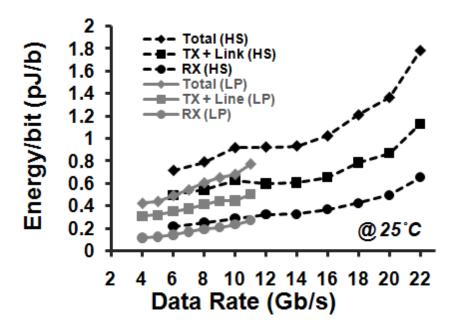

| Figure B.11: Measured energy-per-bit and data rates at 25°C                                       |

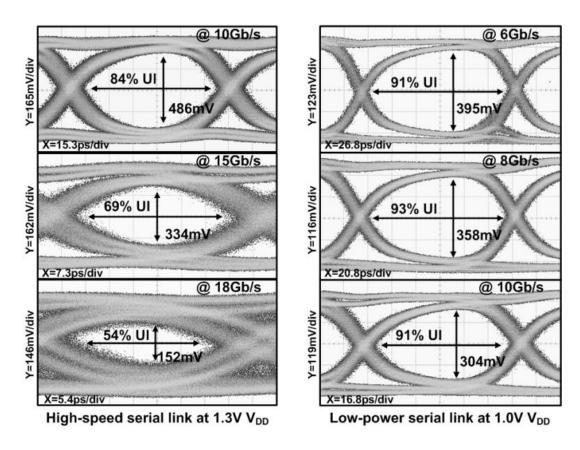

| Figure B.12: Measured eye-diagram of the receive-end of the 10mm serial link with a               |

| GSG probe at 25°C                                                                                 |

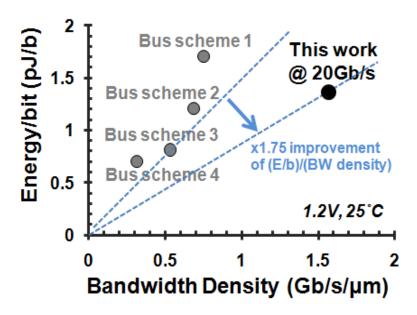

| Figure B.13: Comparison of energy efficiency over bandwidth density with conventional             |

| bus schemes that utilize the same metal level (M9) at $1.2V_{DD}$ and $25^{\circ}C$ . A crosstalk |

| coefficient of 15% is assumed for the transmission line                                           |

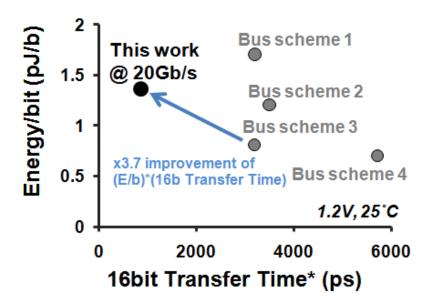

| Figure B.14: Comparison of energy efficiency over 16-bit transfer time with conventional          |

| bus schemes that utilize the same metal level (M9) at $1.2V_{DD}$ and $25^{\circ}C$               |

# **List of Tables**

| Table 1.1: Treatment for essential tremor                                           | 3      |

|-------------------------------------------------------------------------------------|--------|

| Table 1.2: Treatment for dystonia.                                                  | 5      |

| Table 1.3: Treatment for Parkinson's disease.                                       | 8      |

| Table 1.4: Treatment for epilepsy.                                                  | 10     |

| Table 2.1: Summary of the simulated performanc of the designed LNA at 40°C with     | h 1.8V |

| supply                                                                              | 24     |

| Table 2.2: Voltage reference and gain settings in the logarithmic 8-bit ADC with B= | =10.34 |

| Table 4.1: Pass transistor dimensions and load capacitance values of the LDOs       | 48     |

| Table 5.1: Summary of ranges of stimulation parameters.                             | 52     |

| Table 6.1: Power breakdown of the prototype system                                  | 69     |

| Table 7.1: Prototype performance summary                                            | 72     |

| Table A.1: IO pad information of the closed-loop neurostimulation SoC prototype     | 78     |

| Table A.2: Parts list for PCB                                                       | 83     |

| Table B.3: Designed transmission line characteristics                               | 92     |

| Table B.4: Designed transmission line characteristics                               | 97     |

| Table B.5: Performance comparison with recent works                                 | 100    |

# **List of Appendices**

| Appendix A. Printed circuit board for the closed-loop neurostimulation SoC  | 77 |

|-----------------------------------------------------------------------------|----|

| Appendix B. A 22Gb/s, 10mm On-chip Serial Link over Lossy Transmission Line | 85 |

## **List of Abbreviations**

ADC Analog-to-digital converter

AFE Analog Front-end

BER Bit error rate

CMOS Complementary metal-oxide semiconductor

CNS Central nervous system

DAC Digital-to-analog converter

dB Decibel

DBS Deep brain stimulation

DNL Differential non-linearity

DSP Digital signal processor

ENOB Effective number of bit

ET Essential Tremor

FET Field Effect Transistor

GSG Ground-signal-ground

HPF High pass filter

INL Integral non-linearity

I/O Input/Output

ISI Inter-symbol interference

LNA Low-noise neural amplifier

LPF Low pass filter

LSB Least significant bit

MOS Metal-oxide semiconductor (field-effect transistor)

MSB Most significant bit

PCB Printed circuit board

PD Parkinson's disease

PRBS Pseudo-random binary sequence

PWM Pulse width modulation

QFN Quad-flat no-leads

RF Radio frequency

ROM Read-only memory

SAR Successive approximation

SerDes Serializer/Deserializer

SHA Sample and hold

SMA Sub-miniature version A

SNDR Signal to noise-plus-distortion ratio

SoC System-on-Chip

TEM Transverse Electro-Magnetic

UI Unit interval

VGA Variable gain amplifier

#### **Abstract**

This thesis describes research on design techniques for a log-based closed-loop neurostimulation system-on-chip (SoC) for treatment of neurological disorders. Deep brain stimulation (DBS) has become one of the most effective therapies for numerous neurological disorders and epilepsy. A single-chip closed-loop neurostimulation system for treatment of neurological disorders is proposed.

The system is comprised of five major parts: a recording path, a stimulation path, a digital processing unit, a power harvester, and an RF transceiver. Unlike any previous work, the recording path and digital processing unit of this work operate entirely in the log-domain to represent neural signals effectively with fewer bits while consuming less power. The recording path incorporates four channel low-noise amplifiers (LNAs), a logarithmic 8-bit pipeline analog-to-digital converter (ADC), and two sets of a logarithmic digital low-pass filter (LPF) and high-pass filter (HPF). The stimulation path includes two high-current digital-to-analog converters (DACs), six general-purpose DACs, and dedicated stimulation controllers. The high-current DACs are capable of both electrical and optical stimulation.

Even though there has been over a decade of research on the mechanism of DBS, the algorithms of closed-loop DBS are still unclear. Recently, the energy of the local field potential (LFP) has emerged as an important and effective feedback indicator. In the proposed system, the digital processing unit detects the LFP energy and extracts optimal

stimulation parameters by analyzing the LFP energy information. The digital processing unit includes a generic PI-controller for analysis of the LFP energy.

The proposed system also includes a power harvester that converts a 915MHz RF carrier to 1.8V power supplies for the system, an RF transceiver to transmit recorded signals to an external device for further research. A backscatter scheme is chosen for the type of transmitter to minimize power consumption.

A prototype system is designed and fabricated in 180nm CMOS technology. The prototype system occupies 4 mm<sup>2</sup> and consumes  $468 \mu W$  for recording and processing neural signals, stimulation, and RF communication. The proposed closed-loop neurostimulation system utilizes the LFP energy for closed-loop stimulation and log-domain computation for the first time, and achieves a single-chip operation requiring no external circuit components.

## Chapter 1

#### Introduction

An estimated 42 million people in the United States suffer from neurological movement disorders including essential tremor, dystonia, and Parkinson's disease [1]. More than 10 million people in the United States and more than 50 million people worldwide suffer from epilepsy [2]. Deep brain stimulation (DBS) of the subthalamic nucleus with periodic, high frequency electric pulse trains has become one of the most effective therapies for epilepsy and aforementioned neurological movement.

In this chapter, we review the background of several important neurological movement disorders and epilepsy, and discuss DBS and closed-loop DBS. Following the discussion, we propose a log-based single-chip closed-loop neurostimulation system and give a brief description of the proposed system. At the end of the chapter, an outline of the dissertation is provided.

#### 1.1. Essential Tremor

Essential tremor (ET) is a progressive neurological disorder that causes a rhythmic trembling (4-12 Hz) of the hands, head, voice, legs or trunk [3]. In addition to the trembling, a variety of non-motor features appear such as anxiety, depressive symptoms and cognitive difficulty [4]. Patients with severe tremor have difficulty

performing many routine activities of daily living. ET is one of the most common neurological disorders, with a prevalence of approximately 4% of people in age 40 and older and considerably higher among people in 60s and older [5].

Although the underlying etiology is not clear yet, it is found that a genetic mutation is responsible for 50% of all cases, from observing its autosomal dominant transmission. It is estimated that the abnormal brain activity is processed through the thalamus and causes tremor. Figure 1.1 shows a patient with ET drawing the Archimedes spiral [6]. This is the most common way to diagnose ET assuming there are no other neurological or biological reasons to be found.

Figure 1.1: A patient with essential tremor drawing the Archimedes spiral [6].

The tremor tends to intensify as any physical or mental stress builds up. Other factors including fatigue, low blood sugar, caffeine, cold, and lithium salts also make tremor worse.

Table 1.1 gives summary of treatment for ET. When diagnosed with essential tremor there are several courses of action depending on the severity of the tremor. Most people with ET benefit from medication. A surgical approach to treatment is generally suggested for people with severe ET symptoms or those whose symptoms have not responded to the maximum acceptable dosages of medication.

Table 1.1: Treatment for essential tremor.

| Type       | Name        | Mechanism                                                                                | Side Effects or Complications                                                                                                                          |

|------------|-------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Medication | Propranolol | Blocks the receptor sites for Adrenaline.                                                | Dizziness, fatigue, depression, diarrhea, nausea and vomiting, changes in blood sugar levels, difficulty breathing, sinus bradycardia, or hypotension. |

| Mediculon  | Primidone   | Slows the central nervous system and helps to reduce seizure.                            | Nausea, vomiting, fatigue or sleepiness, confusion, ataxia, vertigo, unsteadiness, irritability, blurred vision, or loss of appetite.                  |

|            | Thalatomy   | A selected portion of the thalamus is ablated.                                           | Contralateral weakness, confusion or dysarthria.                                                                                                       |

| Surgery    | DBS         | High frequency electrical stimulation helps the thalamus rebalance the movement control. | Mild dysarthria, weakness on one or both sides of the body, or disequilibrium.                                                                         |

# 1.2. Dystonia

Dystonia is also a neurological movement disorder in which sustained muscle contractions cause twisting and repetitive movements or abnormal postures [7]. The movements are involuntary and sometimes painful, and may affect a single or group of muscles [8]. Dystonic spasms typically increase in intensity during stress, emotional

upset, or fatigue. Spasms tend to decrease in intensity during periods of rest or sleep. Secondary effects such as disturbed sleep patterns, mood swings, mental stress, blurred vision, digestive problems and short temper may accompany direct symptoms. Over a period of time, the symptoms may become more noticeable and widespread and be unrelenting. Figure 1.2 shows a person with medication induced dystonia. It is difficult to find a comfortable position for arms, legs, and a neck for the patient.

Figure 1.2: A person with medication induced dystonia.

Although the causes of dystonia are not known or understood, investigators believe that dystonia results from an abnormality in the basal ganglia. It is suspected that a defect in the body's ability to process neurotransmitters, environmental or disease-related damage

in the basal ganglia causes dystonia.

Unfortunately there are currently no known treatments that can reverse the course of dystonia. However, the symptoms can be reduced and managed with a combination of treatments. Table 1.2 gives summary of treatment for dystonia. Surgical intervention is generally suggested for those patients with severe dytonia or those whose symptoms have not responded to drug therapy. Recently, DBS has proven successful in many cases of severe dystonia [9].

Table 1.2: Treatment for dystonia.

| Туре       | Name                         | Mechanism                                                                                      | Side Effects or<br>Complications                                                                |

|------------|------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|            | Botulinum<br>Toxin<br>(BoNT) | Block the release of acetylcholine to decrease inappropriate or excessive muscle contractions. | Temporary muscle weakness.                                                                      |

| Medication | Benzo-<br>diazepines         | Interfere with chemical activities in the nervous system and brain.                            | Drowsiness,<br>depression or<br>psychosis.                                                      |

|            | Anti-<br>cholinergics        | Block the action of acetylcholine to decrease inappropriate or excessive muscle contractions.  | Confusion, drowsiness,<br>hallucinations,<br>forgetfulness, dry<br>mouth, or blurred<br>vision. |

|            | Thalamotomy                  | A selected portion of the thalamus is ablated.                                                 | Contralateral<br>weakness, confusion or<br>dysarthria.                                          |

| Surgery    | Pallidotomy                  | Part of the globus pallidus (GPi) is destroyed to restore balance.                             | Stroke, or cognitive impairment.                                                                |

|            | DBS                          | High frequency electrical stimulation helps the thalamus rebalance the movement control.       | Mild dysarthria,<br>weakness on one or<br>both sides of the body,<br>or disequilibrium.         |

#### 1.3. Parkinson's Disease

Parkinson's disease (PD) is a degenerative disorder of the central nervous system (CNS) and is the second most common neurodegenerative disorder after Alzheimer's disease [10]. PD affects more than 1 million people in United States and approximately 50,000 Americans are diagnosed with PD every year [11]. PD gives rise to motor types of symptoms including tremor, bradykinesia, stiffness, and postural instability as well as non-motor types of symptoms such as sensory deficits, depression, anxiety, cognitive difficulties and sleep disturbance. Figure 1.3 shows Muhammad Ali and Michael J. Fox who are celebrity patients diagnosed with PD.

Figure 1.3: Muhammad Ali and Michael J. Fox.

For most cases with PD, patients are diagnosed with idiopathic PD meaning no specific causes are known or understood, and only a very small minority of cases can be attributed to known genetic factors such as the parkin gene, alpha-synuclein, DJ-1, PINK-

1, and UCHL-1. The main pathological characteristics of PD is that cells of the substantia nigra degenerate and become incapable of producing adequate dopamine as described in Figure 1.4. Since dopamine controls movement and balance for the proper functioning of CNS, PD gives rise to the aforementioned symptoms [12].

Figure 1.4: Diminished substantia nigra in a patient with Parkinson's Disease [13].

Although there is no known cure that can stop or reverse the progress of PD, there exists treatment that can provide relief from the symptoms of PD. Several types of treatment are summarized in Table 1.3. While levodopa continues to be the most effective treatment for motor symptoms, DBS has become the most commonly used surgical treatment for patients with advanced PD for whom medication is no longer sufficient [14]. Active on-going research direction includes the studies of cell transplants and gene therapy that are still at the experimental stage.

Table 1.3: Treatment for Parkinson's disease.

| Туре       | Name                  | Mechanism                                                                                        | Side Effects or<br>Complications                                                               |

|------------|-----------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|            | Levodopa              | Converted into dopamine in the brain.                                                            | Nausea, vomiting,<br>drowsiness, orthostatic<br>hypotension, and<br>dyskinesia.                |

| Medication | Dopamine<br>Agonists  | Imitate or mimic the action of levodopa in the brain by directly stimulating dopamine receptors. | Drowsiness, sudden sleep<br>onset, nausea, orthostatic<br>hypotension, edema and<br>psychosis. |

|            | MAO-B<br>Inhibitors   | Slow the breakdown of dopamine in the brain.                                                     | Insomnia, hallucinations, and orthostatic hypotension.                                         |

|            | Anti-<br>cholinergics | Block the action of acetylcholine to decrease inappropriate or excessive muscle contractions.    | Confusion, drowsiness,<br>hallucinations,<br>forgetfulness, dry mouth,<br>or blurred vision.   |

|            | Thalamotomy           | A selected portion of the thalamus is ablated.                                                   | Contralateral weakness, confusion or dysarthria.                                               |

| Surgery    | Pallidotomy           | Part of the globus pallidus (GPi) is destroyed to restore balance.                               | Hemorrhage, stroke, or cognitive impairment.                                                   |

|            | DBS                   | High frequency electrical stimulation helps the thalamus rebalance the movement control.         | Mild dysarthria, weakness<br>on one or both sides of<br>the body, or<br>disequilibrium.        |

# 1.4. Epilepsy

Epilepsy is one of the most common neurological disorder characterized by a tendency for recurrent seizures, which is defined as a transient symptom of abnormal excessive or synchronous neuronal activity in a part of the brain, in particular the cortex [15]. The intensity of epileptic seizure differs from person to person. Although some may experience a strange sensation, some experience violent shaking and lose consciousness

as shown in Figure 1.5. Epilepsy is estimated to affect approximately 3 million Americans of all ages and ethnic groups, and about 50 million people worldwide [16-17].

Figure 1.5: Woman with epileptic seizure.

Causes of epilepsy vary from a medical condition to injury that affects the brain, or even may be unknown. Many known common causes of epilepsy include hypoxic-ischemic encephalopathy, CNS infections, congenital defects, stroke, trauma, brain tumors, cerebrovascular disease, and dementia.

Epilepsy is usually treated with medication. Anticonvulsants may reduce the number of future seizures. If a patient's condition does not improve after adequate trials of different anti-seizure drugs, that epilepsy is diagnosed to be medically refractory. For people with refractory epilepsy, surgical treatments are recommended. Even though it is not clear which brain region is affected by DBS and the mechanism is not understood at the present time, DBS is shown to be effective in many uncontrolled studies. Table 1.4 summarizes treatments of epilepsy.

Table 1.4: Treatment for epilepsy.

| Туре       | Name                    | Mechanism                                                                                | Side Effects or<br>Complications                                                        |

|------------|-------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Medication | Anticonvulsant          | Favor inhibition over excitation by modifying processes that develop a seizure.          | Mood changes,<br>sleepiness, unsteadiness<br>in gait, hepatitis, or<br>aplastic anemia. |

|            | Resection               | Removes the area of the brain that causes seizures.                                      | Paralysis, headache, nausea, or depression.                                             |

| Surgery    | Vagus nerve stimulation | Affects serotonin and norepinephrine neurotransmitters.                                  | Dyspepsia, infection,<br>nausea, paresthesia, or<br>hoarseness.                         |

|            | DBS                     | High frequency electrical stimulation helps the thalamus rebalance the movement control. | Mild dysarthria,<br>weakness on one or both<br>sides of the body, or<br>disequilibrium. |

# 1.5. Deep Brain Stimulation (DBS)

DBS is a surgical treatment that involves the implantation of battery-operated medical device which delivers electrical stimulation to specific parts of the brain, blocking the abnormal nerve signals that cause movement or affective disorders [18-19]. Despite the long history of DBS and the fact that DBS in select brain regions has provided remarkable therapeutic benefits for refractory movement and affective disorders, its underlying principles and mechanisms are still not clear and are still under research [20].

The Food and Drug Administration (FDA) approved DBS as a treatment for ET in 1997, for PD in 2002, and dystonia in 2003, and a medical technology company named Medtronic has received European regulatory approval for its DBS system for patients with refractory epilepsy [21]. Medtronic has pioneered the use of DBS therapy in the

United States, a fast growing market that has attracted the interest of competitors like St. Jude Medical, Cyberonics, Advanced Bionics, and Boston Scientific [22]. Among those many companies, Medtronic is currently the only company selling FDA-approved rechargeable DBS devices in the country, and this distinction led the third quarter neurostimulation revenues of the company to \$394 million in fiscal year 2010 [23].

Figure 1.6: Implantation of DBS system [23].

The DBS system is typically comprised of three parts implanted completely inside the body by an experienced neurosurgeons, neurologists, and neurophysiologists: the power source to the system called neurostimulator, a set of thin wires called lead covered with a protective coating, and an insulated wire called extension that connects the neurostimulator and the lead [24]. Figure 1.6 shows a placement of these components in a patient. DBS leads are placed in the target site of the brain according to the type of symptoms. The leads are placed in the ventrointermediate nucleus of the thalamus and in either the globus pallidus or subthalamus nucleus for cases with essential tremor and cases with dystonia or PD respectively. The neurostimulator is usually placed subcutaneously below the collarbone. The extension runs from the head, down the side of the neck and connects to the neurostimulator. The Activa RC neurostimulator shown in Figure 1.7, the most advanced device from Medtronic that operates with a rechargeable battery, has the size of  $54 \times 54 \times 9 \ mm$  ( $2.1 \times 2.1 \times 0.4 \ in$ ) and the weight of 40g ( $1.6 \ oz$ ).

Figure 1.7: Activa RC neurostimulator for Medtronic DBS therapy [25].

While DBS is proven to be effective to movement and affective disorders and to epilepsy, there exist potential side effects and complications. The potential side effects

commonly include stiffness or weakness of the limb, dizziness, imbalance, mood changes, and depression. These side effects are, however, usually temporary or reversible, and can be minimized by optimization of stimulation parameters in most cases. Post-operative complications include hemorrhage, and wound infection. Although the resulting complications from hemorrhage can be severe, complication rates after DBS surgery remain low when the procedure is performed by an experienced surgical team, proving that DBS is not only effective but also safe [26].

Unfortunately, complications related to hardware and its components can also occur, and these include fracture or breakage of the DBS lead or extension wire, battery failure, erosion of the device, and migration of the wire. From recent research, it has been reported that 9.8% of the patients with DBS procedure were affected by hardware related complications [27]. Improvement in powering scheme of DBS devices such as power harvesting or wireless powering that obviates the need for a large battery and an extension wire can reduce the number of incidents from hardware related complications as well as the number of surgeries only to replace a battery or a wire.

## 1.6. Closed-loop DBS

Despite over a decade of clinical experience the underlying principles of DBS are still not clear. Because of this lack of knowledge, the only effective feedback indicator currently known for the optimal selection of stimulation parameters such as amplitude, pulse-width, and repetition rate (frequency) of the electrical stimulation signals is the visual sign of symptoms. In addition, every patient has a different set of signal amplitudes,

pulse widths and repetition rates that are effective to treat their disease symptoms. Thus a post-surgery process called programming is necessary for the best result from DBS.

Figure 1.8: Titrating stimulation using a handheld programmer from Medtronic [28].

After a DBS device is surgically implanted in a patient, the stimulation parameters are adjusted by a neurologist or a trained technician to optimize symptom management with minimum adverse effects. An external component that transmits instructions wirelessly to the neurostimulator is used to noninvasively tune the parameters [29]. Figure 1.8 shows a clinician programming the stimulation parameters of a patient using a programmer from Medtronic which communicates with the neurostimulator through the skin. Initial programming may take 2-3 hours and the patient

should not leave the doctors for at least 1-2 hours after programming to allow the observation of therapeutic changes with DBS and for any fine adjustments to be made. In general, programming is performed frequently for the first 3-6 month period to achieve good results, and the patients visit a neurologist or a trained technician periodically or on need basis to ensure the best control of symptoms as a patient's condition changes over time. This type of DBS can be named open-loop DBS.

If any internal information from the brain of a patient with a neurological disorder can be obtained, then it may be possible to find the proper stimulation parameters automatically with the help of a dedicated microprocessor or even a small digital signal processor. This type of DBS is called closed-loop DBS. While open-loop DBS, the only type of DBS currently available, requires patients to visit clinicians often for fine tuning and needs an external device for programming, closed-loop DBS does not require intricate visits of patients to clinicians nor external device for programming.

Although the underlying principles of DBS is not known yet, it is believed that the strongest candidate for the closed-loop feedback signal is an abnormal pattern change in spike or local field potential (LFP) signals. In general, spike signals, also known as action potentials, are said to have bandwidths from  $100 \ Hz$  to  $10 \ kHz$  and amplitudes up to  $500 \ \mu V$  [30], and LFP signals have bandwidths from  $1 \ Hz$  to  $100 \ Hz$  and amplitudes up to  $5 \ mV$  [31]. Among them, neural spike signals have drawn more attention as a possible candidate for the feedback indicator. To this end, a biomedical multiprocessor systemon-chip (SoC) for closed-loop neuroprosthetic applications has been proposed [32]. This work performs real-time spike-sorting with principal component analysis. Another work on a closed-loop biomedical system has developed an activity-dependent intracortical

microstimulation SoC [33]. This SoC embeds a digital spike discrimination processor that triggers stimulation every time it captures a neural spike signal stronger than a preset threshold. Recently features of the LFP signals, in particular the energy of LFPs, have emerged as more effective feedback indicators for DBS [34]. An implantable closed-loop microstimulator targeted at titration therapy in DBS was proposed and developed to exploit the features of LFP signals with analog spectral analysis method [35]. The system incorporates a custom IC for recording and spectral analysis, an auxiliary microprocessor for extracting key bioelectrical signals, and an existing neurostimulator device.

#### 1.7. Dissertation outline

In this dissertation, a new architecture and new design techniques are proposed for closed-loop neurostimulation to exploit the logarithmic characteristics of neural signals, allowing efficient signal processing to extract the feedback information while operating from harvested or battery power. These techniques are verified with evaluation results from a prototype closed-loop DBS SoC. The prototype is fabricated in 180nm TSMC CMOS. The key design goals for the prototype are to implement and verify a log-based digital processing unit that receives the logarithmic output from a log-ADC directly and extracts the energy information of LFP signals, and a closed-loop feedback path that uses the energy of LFP signals, and to achieve the highest degree of integration to enable truly single-chip operation.

Design techniques for a low-power differential low-noise neural amplifier (LNA) and a pipeline log-ADC are proposed in Chapter II. These techniques include a two-stage cascade structure of band-pass amplifiers, power optimization of a folded cascode

amplifier, and elimination of a dead-zone inherent in a pipeline log-ADC structure. In Chapter III, design methods and techniques to build a digital processing unit that performs high-pass and low-pass filtering, and extracts the feedback information to set the stimulation parameters are explained. The processing unit performs calculation entirely in a logarithmic domain resulting in reduced power consumption. Circuit techniques for a power management block which incorporates a power harvester, low-dropout regulators, and bias circuitries are shown in Chapter IV. The power management block provides 1.8V supply to the whole system from a 915 MHz carrier. Design techniques for other important building blocks of the proposed system including a biphasic current stimulator, a source-coupled oscillator for clock generation, an RF transceiver based on a backscattering scheme, are described in Chapter V.

The prototype system and performance measurements are presented in Chapter VI. The dissertation concludes in Chapter VII that combination of logarithmic analog to digital conversion, logarithmic digital signal processing (DSP), and LFP energy based closed-loop DBS enables a power-efficient, fully implantable SoC for treatment of neurological disorders, and suggests some possibilities for future work to extend this research.

## Chapter 2

## **Design techniques for recording front-end**

As the extraction of accurate feedback information relies on the quality and accuracy of recorded neural signals, the performance of the recording front-end is one of the most critical specifications of closed-loop neurostimulation systems. Therefore, it is required to design the recording front-end to provide data that carry sufficient and accurate information to support the extraction of feedback indicators or to enable further analysis. In this chapter design techniques for LNAs and a log-ADC are presented to process both spikes and LFPs.

#### 2.1. LNA

Both the spikes and LFP signals carry unique information about the state of a brain [36]. Since these signals exhibit different characteristics such as bandwidth and amplitude, there have not been many IC systems that record both signals simultaneously. Due to the very different amplitude ranges of spikes and LFPs, LNAs should exhibit a high dynamic range, good noise performance, and wide bandwidth at the same time.

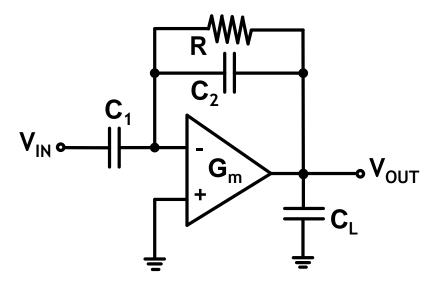

A general band-pass amplifier is shown in a single-ended fashion in Figure 2.1. Assuming the voltage gain of the op-amp is A, the transconductance of the op-amp is  $G_m$ , and the poles are far from each other, we have the following equations for the zero and

pole locations, and the pass-band gain. The frequency response of the general band-pass amplifier is shown in Figure 2.2 with the zero and pole locations assigned with the equations described below.

Figure 2.1: A single-ended representation of the schematic of a band-pass amplifier.

$$\omega_{z1} = 0 \tag{2.1}$$

$$\omega_{z2} = \frac{1}{C_2} \left( G_m - \frac{1}{R} \right) \tag{2.2}$$

$$\omega_{p1} \approx -\frac{1}{RC_2} \tag{2.3}$$

$$\omega_{p2} \approx -\sqrt{\frac{G_m}{R(C_1C_2 + C_2C_L + C_LC_1)}}$$

(2.4)

$$(Passband Gain) = \frac{C_1}{C_2}$$

(2.5)

Figure 2.2: Simulated frequency response of the general band-pass amplifier.

As can be seen from the equations, the two poles tend to move in the same direction as the values of R and  $C_2$  change, except only that the second pole moves less because of the square root operator. The pass-band gain and the first pole are determined easily from the gain requirement to match the full scale input of the ADC and from the low cutoff frequency requirement (around 1  $H_2$ ) to be able to capture low frequency LFP signals. Therefore, the transconductance of the amplifier,  $G_m$ , and the load capacitance,  $C_L$ , are determined by equation 2.4 to achieve the second pole of around 10  $kH_2$  to capture high frequency spike signals.

Given that the full scale input range of the ADC is 600 mV, as explained in section 2.2, and that the input amplitude of the LFP signals is around 1 mV and rarely higher than 1.2 mV, a pass-band gain of 500 (= 54 dB) is appropriate for the front-end LNA. Moreover the feedback resistance R is on the order of  $10^{11} \Omega$  which is described later. This level of gain and the feedback resistance makes it difficult to achieve both the first and second poles low and high enough respectively to be able to capture low-frequency LFP and high-frequency spike signals at the same time unless  $G_m$  is in the order of  $1\Omega^{-1}$ , which is not allowed in low-power biomedical applications.

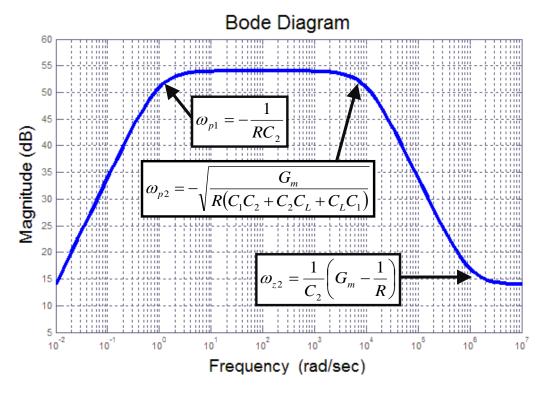

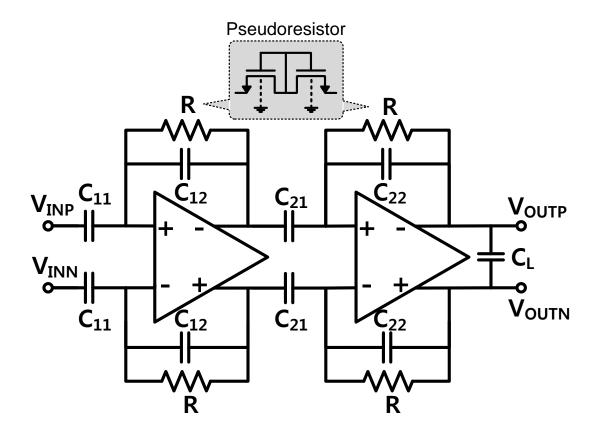

Therefore, to address the large gain issue and to achieve the bandwidth requirement with a minimum overhead in power consumption, a two-stage cascade structure is chosen for the front-end LNA. The LNA with two-stage structure is shown in Figure 2.3. This two-stage structure also suppresses out-of-band signals more than the general one-stage band-pass amplifier with the same pass-band gain. The first stage and second stage are designed to have a pass-band gain of 50 and 10 respectively. The larger gain in the first stage reduces the effect from the second stage to the input-referred noise of the entire LNA. This two-stage structure also reduce the capacitor area compared to the general one-stage approach while meeting the same mismatch requirement which is directly related to the pass-band gain.

Figure 2.3: A differential representation of the schematic of a two-stage band-pass amplifier.

The amplifiers in the first and second stages are folded cascode amplifiers with an NMOS input pair to provide an enough gain. The lengths of all MOSFETs in the signal paths are  $20\,\mu m$ , the maximum channel length allowed in the used 180nm CMOS technology, for large output resistance, since gain is a more important property than speed in this application. Since the input pair of an amplifier is the most significant source of flicker noise, the input pair of the amplifier is sized to  $W=20\,\mu m$  and  $L=20\,\mu m$  to reduce the total noise. A pseudoresistor comprised of two back-to-back diode-connected NMOSs are used to emulate high resistance as high as  $10^{11}\,\Omega$ . Compared to one used in

[37], this configuration reduces parasitic capacitance shown at the input and output nodes of the amplifier because the gates of NMOSs are connected within the pseudoresistor.

Figure 2.4: Simulated frequency response of the designed two-stage band-pass LNA.

The values of the circuit components in the LNA are chosen through calculation and simulation:  $C_{II} = 62.5 \ pF$ ,  $C_{2I} = 1.25 \ pF$ ,  $C_{I2} = C_{22} = 12.5 \ pF$ ,  $C_L = 2.5 \ pF$ , and  $R = 10^{11} \Omega$ . A simulated frequency response of the designed band-pass LNA at 40°C and 1.8V supply is shown in Figure 2.4. The simulated input-referred noise is 6.04  $\mu V_{rms}$ , which is comparable to the microelectrode noise and background cortical activity noise (5  $\mu V$ ) [38]. As the application of this system is an implant device in a human body, temperature variation is not a significant factor to affect the performance of LNA. Therefore, the

design of the system is considered at body temperature, 40°C. A summary of the simulated performance of the LNA at different process corners is given in Table 2.1.

Table 2.1: Summary of the simulated performanc of the designed LNA at 40°C with 1.8V supply.

| Process<br>Corner | Power consumption | Low 3dB cutoff frequency | High 3dB cutoff frequency |  |

|-------------------|-------------------|--------------------------|---------------------------|--|

| TT                | 12.4 μW           | 1.4 <i>Hz</i>            | 6 <i>kHz</i>              |  |

| FF                | 12.8 μW           | 6.9 <i>Hz</i>            | 6.6 <i>kHz</i>            |  |

| SS                | 12.4 μW           | 0.66 Hz                  | 5.04 <i>kHz</i>           |  |

## 2.2. Pipeline logarithmic ADC

Once neural signals are recorded from a microprobe implanted in a specific part of the brain and amplified by LNAs, the signals need to be encoded into digital domain to facilitate digital processing of the recorded signals, including further filtering to separate LFP and spike signals and to extract feedback information.

In the real world, many signals such as light intensity, audio amplitude, as well as neural signals in the brain, are better represented in a logarithmic scale than in a linear scale. These signals exhibits a high dynamic range and require high resolution analog to digital conversion when conventional linear encoding is used. However, increasing the resolution of an ADC results in larger area consumption, higher power consumption, or slower conversion speed depending on the type of ADC structure. Alternatively variable gain amplifier (VGA) can be used to expand dynamic range. However, a VGA is generally slow and cannot respond rapidly to fast varying signals [39].

Instead we propose to use a logarithmic ADC directly [40]. Although a neurostimulator system with a logarithmic ADC was proposed in our previous work [37], the compatibility of the logarithmic ADC in the system with neural signal input was not fully demonstrated. The performance of the log-ADC designed in this work is presented in a later chapter. Compatibility of the log-ADC with sample neural signals prerecorded from the brain of a rodent is also shown.

First, we briefly introduce the concept of the pipeline log-ADC. With logarithmic scale quantization, assuming an N-bit logarithmic ADC with an input voltage,  $V_{in}$ , a full scale input range,  $V_{range}$ , output digital bits  $(b_{N-1}, b_{N-2}, \dots, b_0)$ , and the base of logarithm function, B, the transfer function of the ADC is given by [40]:

$$\left[2^{N} \cdot \log_{B}\left(B \cdot \frac{V_{in}}{V_{range}}\right)\right] = b_{N-1} 2^{N-1} + \dots + b_{0},$$

(2.6)

where [x] is the maximum integer that is not larger than x. As illustrated in Figure 2.5, the LSB size increases as the input signal level increases. As the input amplitude increases, the quantization becomes coarser. The LSB size is described by:

$$LSB_{j} = V_{range} \cdot B^{\left(\frac{j}{2^{N}}-1\right)} \cdot \left(B^{\frac{1}{2^{N}}}-1\right), \text{ where } j = 0, 1, 2, \dots, 2^{N}-1.$$

(2.7)

According to equation 2.7, we also have the following equations for the maximum and minimum LSB size.

$$LSB_{\text{max}} = V_{range} \cdot \left(1 - B^{-\frac{1}{2^{N}}}\right). \tag{2.8}$$

$$LSB_{\min} = V_{range} \cdot \left( B^{\left(\frac{1}{2^N} - 1\right)} - B^{-1} \right). \tag{2.9}$$

The dynamic range (DR) is defined as the ratio of the input range to the smallest resolvable signal, and can be described with the next equation:

$$DR = \frac{V_{range}}{LSB_{\min}} = \frac{B}{B^{\frac{1}{2^{N}}} - 1}.$$

(2.10)

From this equation, it is shown that DR increases as the base of logarithmic function, B, and the resolution, N, increase. Because of this logarithmic scale coding, a log-ADC have a higher DR than a conventional linear ADC. For example, with B=10 and N=8, we get DR=61 dB and this is 13 dB larger than DR of a conventional linear ADC with 8-bit resolution.

Figure 2.5: Coding scheme of a 5-bit logarithmic ADC with B=10 (left) and output from sinusoidal input shown with dead-zone effect (right).

However, all inputs smaller than  $0.1 \times V_{range}$  result in a negative digital output and usually truncated to "0" as shown in Figure 2.5 leading to a practical DR of only 10. This logarithmic dead-zone and a technique to remove this dead-zone is briefly described in detail in Figure 2.6. Given that  $x = V_{in}/V_{range}$ , all inputs smaller than  $0.1 \times V_{range}$  are converted to a digital output 0 losing the benefit of high DR characteristic of logarithmic conversion. This problem can be overcome with a pre-conversion of input signal. With B=10, input x is pre-converted to  $y=0.9 \cdot x + 0.1$ , where, y is the input to logarithmic conversion. This pre-conversion scheme effectively eliminates the log dead-zone without losing significant DR. The pre-conversion scheme can be easily combined with the sample and hold circuits and this is explained later.

Figure 2.6: Pre-conversion of input to eliminate the log dead-zone.

Figure 2.7 shows the overall architecture of the 8-bit pipeline logarithmic ADC. Before the pre-conversion, the polarity of input signal is checked and sample and hold is performed. The output of sample and hold circuits is arranged in order to give positive inputs to the following logarithmic 1.5-bit stage, because of the nature of logarithmic function that assumes the input to be a positive number. After the sign decision with sample and hold, five logarithmic 1.5-bit stages and a 2-bit flash ADC process the signal and, finally, a digital logic block calculates out 8-bit digital output.

Figure 2.7: Overall architecture of the 8-bit pipeline logarithmic ADC.

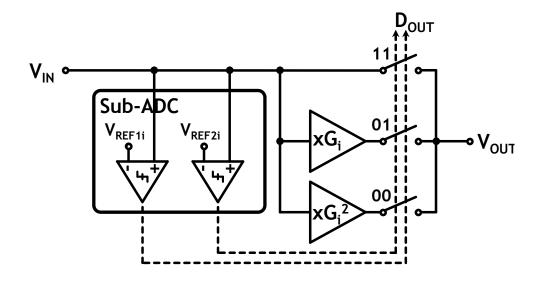

Direct logarithmic conversion of a 1.5-bit stage in linear domain requires squaring operation to replace multiplication-by-2 operation in linear domain and conditional multiplication to replace the conditional addition or subtraction in linear domain. To avoid analog squaring, the reference voltages for the comparators and the gain settings for conditional addition are scaled in order to achieve the same result [40]. A conceptual

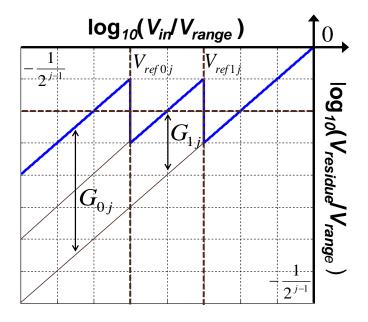

block diagram of the logarithmic 1.5-bit stage is described in Figure 2.8. The residue characteristic of the logarithmic 1.5-bit stage is also described in detail in Figure 2.9.

Figure 2.8: Conceptual block diagram of the logarithmic 1.5-bit stage.

Figure 2.9: Residue plot of the logarithmic 1.5-bit stage with B=10.

The reference voltages for a  $j^{th}$  1.5-bit stage are given by:

$$V_{ref\,0\,j} = V_{range} \cdot B^{-1.25/2^{j}},$$

$$V_{ref\,1\,j} = V_{range} \cdot B^{-0.75/2^{j}},$$

(2.11)

where  $V_{ref0j}$  and  $V_{ref1j}$  are the first and second reference voltages for a  $j^{th}$  1.5-bit stage, and  $V_{range}$  is the full scale input range. The gain settings for a  $j^{th}$  1.5-bit stage are given by [40]:

$$G_{j}(V_{in}) = \begin{cases} G_{0j} = B^{1/2^{j}}, & V_{in} \leq V_{ref0j} \\ G_{1j} = B^{1/2^{j+1}}, & V_{ref0j} < V_{in} \leq V_{ref1j} \\ G_{2j} = 1, & V_{ref1j} < V_{in} \leq V_{range} \end{cases}$$

(2.12)

where  $G_{0j}$ ,  $G_{1j}$ , and  $G_{2j}$  are gains for the first, second, and third input region for a  $j^{th}$  1.5-bit stage respectively, and  $V_{range}$  is the full scale input range. As shown from Figure 2.8, the input range of the next 1.5-bit stage is half of the current stage, and the reference voltages also scale accordingly.

For neural interface applications, an 8-bit logarithmic ADC with one sign bit and a base of 10 is implemented. A sampling rate of 100 *kSample/s* is chosen to process neural data from four recording channels simultaneously with some bandwidth margin. This configuration (7-bit resolution + 1 sign bit) provides a DR of 61 *dB*, which is high enough to cover the entire range of spike and LFP signals.

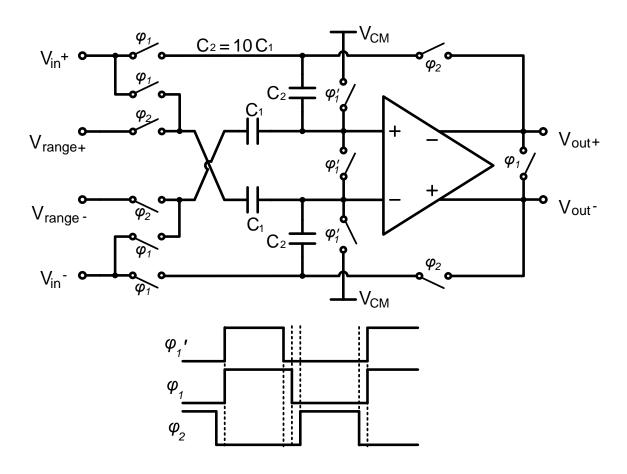

Figure 2.10 shows a fully differential sample and hold circuits that embeds the pre-conversion scheme. A common mode voltage of 800mV is chosen and used

throughout the entire ADC. Three clock signals  $\varphi_1$ ,  $\varphi_1$ , and  $\varphi_2$  control the operation of the sample and hold circuits with the help of bottom-plate sampling [41]. When  $\varphi_1$  is high, the stage input is sampled and the output is reset. When  $\varphi_2$  is high, the input is amplified and the output is set by the following equation.

$$V_{out} = 0.9 \cdot V_{in} + 0.1 \cdot V_{range}. \tag{2.13}$$

Figure 2.10: Simplified schematic of SHA with B=10.

For the op-amps in the SHA block and the 1.5-bit stages, a folded cascode amplifier topology with a PMOS input pair is chosen for its high gain and low power

consumption. The full scale input range,  $V_{range}$ , is set to 600 mV, which is the maximum achievable voltage swing that allows all MOS devices in the cascode amplifiers in saturation region. The op-amps are scaled through the stages to match the gain-bandwidth requirement.

Figure 2.11: Simplified schematic of a logarithmic 1.5-bit stage.

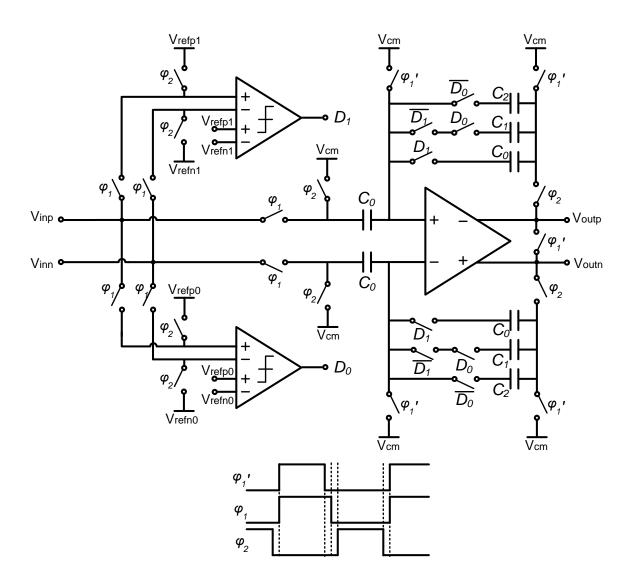

A schematic of a fully differential 1.5-bit stage of the logarithmic ADC is illustrated in Figure 2.11. Similar to the SHA block, three clock signals  $\varphi_1$ ,  $\varphi_1$ , and  $\varphi_2$  controls the operation of the sample and hold circuits with the help of bottom-plate sampling. When  $\varphi_1$  is high, the stage input is sampled and the output is reset. When  $\varphi_2$  is high, comparators decide the output bits and the residue is amplified with a gain depending on the bit decision. A two-stage regenerative comparator is used for the sign decision block and 1.5-bit stages, and the size of the input pairs of the comparators are scaled through the stages as the mismatch requirement becomes more strict due to the decrease of input range along the stages.

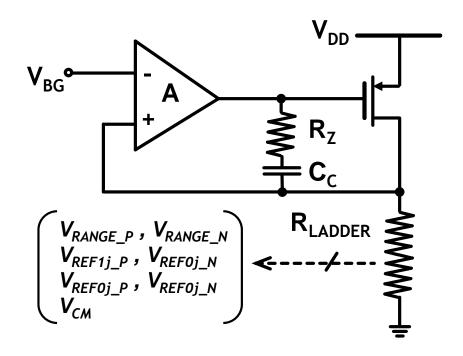

The bias circuit that generates reference voltages of the ADC is implemented entirely on-chip to enable the single-chip operation of the neurostimulation SoC. The schematic of the bias circuits is comprised of a two-stage amplifier with frequency compensation and a resistor ladder as shown in Figure 2.12. The common mode voltage and differential full scale input range voltages are generated, as well as the differential reference voltages, from the bias circuits. Reference voltage values and gains in each stage of the ADC are summarized in Table 2.2.

Figure 2.12: Schematic of bias circuits.

Table 2.2: Voltage reference and gain settings in the logarithmic 8-bit ADC with B=10.

| Stage (j)    | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | 4 <sup>th</sup> | 5 <sup>th</sup> | 6 <sup>th</sup> (2-bit<br>Flash) |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------------------|

| $V_{ref0j}$  | 142 mV          | 292 mV          | 419 mV          | 501 mV          | 548 mV          | 568 mV                           |

| $V_{ref1j}$  | 253 mV          | 389 mV          | $484 \ mV$      | 539 mV          | 568 mV          | 579 mV                           |

| $V_{ref2j}*$ | -               | -               | -               | -               | -               | 589 mV                           |

| $G_{0j}$     | 3.162           | 1.778           | 1.334           | 1.155           | 1.075           | -                                |

| $G_{lj}$     | 1.778           | 1.334           | 1.155           | 1.075           | 1.037           | -                                |

| $G_{2j}$     | 1               | 1               | 1               | 1               | 1               | -                                |

<sup>\*</sup>  $V_{ref2}$  is needed for the 6<sup>th</sup> stage because a 2-bit flash ADC needs three comparators.

## Chapter 3

# Design techniques for a log-domain digital processing unit<sup>1</sup>

To exploit the efficiency of logarithmic digitization, an analog front-end (AFE) with a logarithmic ADC is proposed in Chapter II to record neural signals with less number of bits while achieving the same DR compared to a conventional linear ADC.

We introduce complete log-domain digital filters and digital processing unit to implement closed-loop stimulation in this chapter. To further take advantage of logarithmically encoded signals, log-domain digital filtering is introduced in this work to directly process the logarithmic scale digital output from the ADC to reduce power consumption. LFP energy is also calculated efficiently from the filtered LFP signals using logarithmic arithmetic, and a programmable digital PI-controller uses the LFP energy information to set the optimal stimulation amplitude.

## 3.1. Logarithmic digital signal process

There has been ongoing research on logarithmic digital signal processing for more than three decades because of the inherent high DR of logarithmic number system and the potentially low power consumption [42]. A logarithmic number system with a sign bit is proposed in early research to represent negative numbers as well as positive numbers

<sup>&</sup>lt;sup>1</sup> The entire logarithmic digital processing unit is designed by Jaehun Jeong after the functionality and specifications of the unit are determined.

with minimal complexity, and this number system can be easily adopted in digital signal processing [43].

For a given DR requirement, fewer bits are needed for logarithmic number system compared to conventional linear number system. Furthermore, multiplication in linear-domain is equivalent to addition in logarithmic domain as described by the next equation.

$$\log(A \cdot B) = \log A + \log B \tag{3.1}$$

where A and B are positive numbers. From this equation, it is expected that power consuming multipliers can be substituted with simple adders. The combination of the elimination of multipliers and the fewer number of required bits potentially leads to lower total power consumption for a digital processing unit. Although linear-domain addition is less intuitive in log-domain, a few methods are proposed in earlier studies [44-45]. The most popular way is to use a lookup table and this method is selected in our work for its simplicity.

$$\log(A+B) = \log\left(A\left(I + \frac{B}{A}\right)\right) = \log A + \log\left(I + I0^{\log B - \log A}\right),\tag{3.2}$$

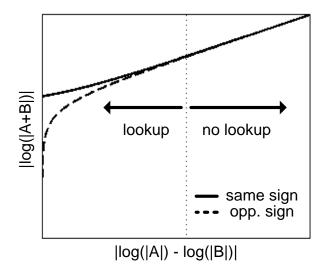

assuming B is larger than A. In equation 3.2,  $\log(1+10^{\log B-\log A})$  needs to be determined. As the value of  $\log B$ - $\log A$  increases,  $1+10^{\log B-\log A}$  approximates to  $10^{\log B-\log A}$  and, as a result,  $\log(1+10^{\log B-\log A})$  approximates to  $\log B$ - $\log A$  which means that  $\log(A+B)$  simply approximates to  $\log B$ . In the case where  $\log B$ - $\log A$  is not large enough, a lookup table is needed to find the value of  $\log(1+10^{\log B-\log A})$ . The decision to use lookup-table or not is also described in Figure 3.1. For a fixed resolution system (i.e. a fixed bit number),

there is a certain point for  $\log B$ - $\log A$  beyond which  $\log (A+B)$  and  $\log B$  are the same. Therefore, a lookup table is needed only when  $\log B$ - $\log A$  is smaller than the threshold.

Figure 3.1: Lookup table usage decision.

Logarithmic arithmetic is first used in a digital filter in [46]. The work demonstrated that the designed log-domain digital filter consumes lower power than its linear counterpart, while maintaining a high DR. In other early research, a lookup table is used to calculate the sum of two numbers [47]. Recently, a 32-bit processor core based on logarithmic arithmetic was developed for low-power 3-D graphics systems [48]. Employing log-domain arithmetic enables the work to achieve performance improvements and lower power and area consumption simultaneously compared to other earlier works. Logarithmic digital signal processing is, therefore, proven to be efficient for applications that need high dynamic range with moderate accuracy as predicted from early theoretic studies.

## 3.2. Logarithmic digital filter

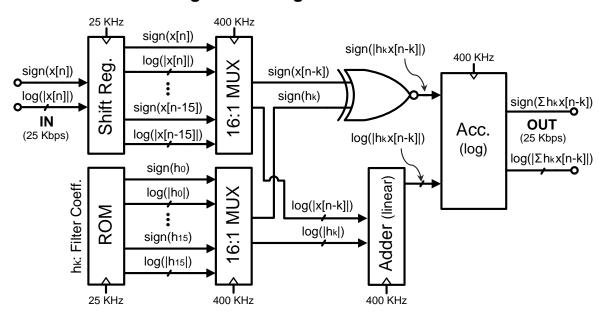

In this work, both a 15<sup>th</sup> order digital FIR low-pass filter (LPF) and a high-pass filter (HPF) are implemented in the system to separate the low-frequency LFPs and the high-frequency spikes from the digitized neural data and to provide those signals simultaneously.

# **Logarithmic Digital FIR Filter**

Figure 3.2: Block diagram of digital logarithmic low-pass and high-pass filters.

Figure 3.2 shows a block diagram of the logarithmic digital FIR filters. The entire digital filters run with a  $400 \, kHz$  clock. Both the LPF and HPF have the same 3dB cutoff frequency of  $700 \, Hz$ . As mentioned above, the log-filters do not require any multiplier since multiplication in linear-domain is equivalent to addition in log-domain. A simple linear adder multiplies the filter coefficients stored in the ROM and the input bits. A

selective look-up table method is used for logarithmic accumulation of the multiplied values of input and filter coefficients, and if the difference of the two inputs is larger than a threshold, which is 105 in this work, then the output of accumulation is approximated to the larger input, obviating the need for table look-up in this case.

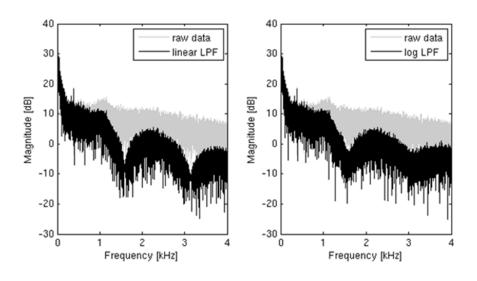

Simulated output spectrums of both a linear  $15^{th}$  order FIR LPF and a logarithmic LPF are shown in Figure 3.3. The input signal for this simulation is sample data prerecorded from a rat's brain. Both output spectrums show suppression of signals at frequency higher than  $700 \, Hz$ , though the high frequency notches are less noticeable in the logarithmic LPF than the notches in the linear LPF.

Figure 3.3: Simulated output spectrums of the linear (left) and logarithmic (right) 15<sup>th</sup> order FIR LPF.

In addition, the simulated output spectrums of both a linear  $15^{th}$  order FIR HPF and a logarithmic HPF are shown in Figure 3.4. Both output spectrums show suppression of signals at frequency lower than  $700 \, Hz$ .

Figure 3.4: Simulated output spectrums of the linear (left) and logarithmic (right) 15<sup>th</sup> order FIR HPF.

A comparison of power consumption of a 8-bit linear-domain digital filter and a 8-bit log-domain digital filter is shown in Figure 3.5. The logarithmic filter consumes 48.5% less power than the linear filter in simulation mainly due to elimination of multipliers.

Figure 3.5: Power consumption comparison of a linear-domain and a log-domain 10-bit FIR digital filters.

#### 3.3. Closed-loop stimulation controller

Neural signals such as spikes and LFPs have been considered to be the strongest candidate for an indicator of closed-loop DBS. Recently, features of the Local Field Potential (LFP), and in particular the energy of LFPs, have emerged as a more effective feedback indicator for DBS [34]. However, the mechanism of DBS for many neurological diseases is still not fully understood. Therefore, we propose a closed-loop stimulation controller embedded with a generic PI-controller to overcome the lack of understanding the DBS mechanism. The PI-controller determines stimulation parameters in order to optimally suppress abnormal activities in the brain using extracted LFP energy information.

Figure 3.6: Flow diagram of the proposed closed-loop stimulation that uses LFP energy information as a feedback indicator.

A simplified signal flow diagram of the proposed closed-loop DBS system is shown in Figure 3.6. A programmable digital PI-controller optimizes stimulation amplitude based on the energy detected in the filtered LFP signal. Instead of squaring, simple logical 1-bit left-shifting calculates the energy of the log-domain LFP signals due to the logarithmic arithmetic. To generate controller output, the product of controller constants and input is also calculated in log-domain through simple addition.

Figure 3.7 shows simulated outputs of the closed-loop stimulation controller using the LFP signals filtered from a rat's neural data sample as an input. The LFP energy of input neural signals is calculated by the energy detection block and the energy value is compared to a manually set reference value to provide input to the PI-controller. In

summary, the stimulation controller sets the stimulation amplitude depending on the neural activities and a LFP energy reference. For example, as shown in the figure, the closed-loop stimulation controller adjusts stimulation amplitudes when the controller captures LFP energy abnormally different from the reference.

Figure 3.7: Simulated transient input and output of the PI-controller with pre-recorded rat's neural data input.

#### Chapter 4

## Design techniques for a power management block<sup>2</sup>

All commercial DBS devices currently available are powered up from batteries. The battery installation inside a human body causes many problems including wire erosion, wire snapping, battery corrosion and periodic surgeries for battery replacement. To reduce the battery related risks, other means to deliver power that do not require a battery is desirable.

There has been a lot of research on delivering power wirelessly to implanted medical devices. Most research has focused to low frequency electromagnetic field in conjunction with inductive coupling to power up the implanted systems [47-51]. The power management block in these systems uses frequencies below 10 *MHz* with an intent to minimize power absorption from tissue. A few works, however, examined the range of frequencies that optimizes power transmission considering tissue absorption by modeling biological tissue as a dispersive dielectric and showed that the optimal frequency for wireless power transfer to implanted devices is in the *GHz* or sub-*GHz* range depending on the size of transmit antenna [52].

In this work, a power management unit comprised of a RF-DC converter (rectifier), two low-dropout regulators (LDOs), and a bandgap voltage generator is

<sup>&</sup>lt;sup>2</sup> The power management block is an assistive but critical part of the system since it provides power to the system. This block is designed by Jaehun Jeong after the specifications of the block is determined.

proposed. A simplified block diagram of the power management unit is shown in Figure 4.1. The power management block is designed to supply 1.8V from a 915MHz carrier to both analog and digital domains of the entire DBS system. An optional 5V battery can be used to operate high-current DACs, which is explained in section 5.1.

Figure 4.1: Block diagram of the power management block of the closed-loop DBS system that generates both analog and digital supply voltages from a 915MHz carrier.

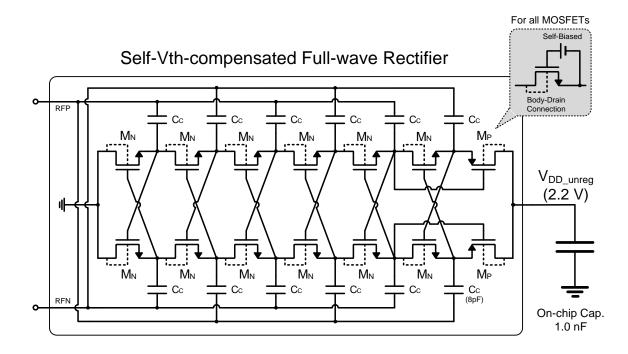

#### 4.1. RF-DC converter

An RF-DC converter is the first component of the power management block. Input of the RF-DC converter is connected to an antenna that receives a 915MHz carrier. A schematic of the RF-DC converter is illustrated in Figure 4.2. A full-wave self-threshold-compensated rectifier [53] is chosen for its higher power conversion efficiency compared to that of a half-wave rectifier. In addition compared to [53], the body of each FET is tied to the drain for both lower on-resistance and less reverse-biased leakage in this work. The rectifier generates unregulated  $V_{DD}$  of 2.2V and charges  $V_{DD}$  on an on-chip

1nF capacitor. The designed RF-DC converter exhibits a simulated power conversion efficiency of 52% when load current is  $350 \,\mu$ A.

Figure 4.2: Schematic of the full-wave rectifier that generates unregulated  $V_{DD}$  of 2.2 V from a 915MHz carrier.

#### 4.2. LDO

Two LDOs are implemented to provide analog  $V_{DD}$  and digital  $V_{DD}$  separately to minimize high frequency interference from digital circuits to analog circuits. A schematic of the LDO of the system is shown in Figure 4.3. The on-chip load capacitors,  $C_L$ , for the analog domain LDO and the digital domain are 1 nF and 1.5 nF respectively. The larger capacitance of digital domain LDO is to tolerate sharp ripples from clocks and digital