## Architecture Independent Timing Speculation Techniques in VLSI Circuits

by

#### Matthew R. Fojtik

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2013

Doctoral Committee:

Professor Dennis M. Sylvester, Chair Professor David Blaauw Associate Professor Jerome P. Lynch Professor Trevor N. Mudge

to my family

## TABLE OF CONTENTS

| DEDICA  | ΓΙΟΝ                                                                                                        | ii                                      |

|---------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| LIST OF | FIGURES                                                                                                     | vi                                      |

| LIST OF | TABLES                                                                                                      | х                                       |

| CHAPT   | RS                                                                                                          |                                         |

| 1       | <ul> <li>1.1 Sources of Delay Variation</li></ul>                                                           | 1<br>1<br>2                             |

|         | 1 0                                                                                                         | 3<br>6                                  |

|         | <ul> <li>2.1 Introduction</li></ul>                                                                         | 778890014479                            |

|         | 3.1 Retiming the Cortex-M323.2 Speculation Window Selection for the Cortex-M323.3 Implementation Circuitry2 | $\begin{array}{c}1\\1\\5\\6\end{array}$ |

|   | 3.6                                                                                                               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                                                                 |

|---|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Voltag<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                             | e Razor: Using Supply Voltage Boosting as Error Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $     \begin{array}{r}       33 \\       33 \\       35 \\       37 \\       38 \\       42 \\       42 \\       43 \\       44 \\       46 \\       \end{array} $ |

| 5 | $\begin{array}{c} \text{Transf} \\ 5.1 \\ 5.2 \\ 5.3 \\ \\ 5.3 \\ \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \end{array}$ | forming Designs With Clock Gating to Two Phase Latch Timing         Removing Functional Requirement of Clock Gating         Retiming With Clock Gating Present         5.2.1 Forward vs Backward Retiming         5.2.1 Forward vs Backward Retiming         Reassigning Gated Clocks to Negative Latches         5.3.1 Assigning Gated Clocks to Negative Latches Based on Fanout         5.3.2 Preventing Race Conditions         5.3.3 Assigning Gated Clocks to Negative Latches Based on Fanin         5.3.4 Preventing Timing Loops         5.3.5 Algorithms for Looking Forward to Assign Clocks to Negative         Latches         Clock Generation         Timing When Late Arriving EN is Falling         Metastability on GCLK         Timing Error Detection and Bubble Neighbors | $\begin{array}{c} 48\\ 49\\ 50\\ 53\\ 53\\ 54\\ 56\\ 58\\ 61\\ 64\\ 65\\ 67\\ 69\\ 69\\ 72\\ \end{array}$                                                          |

| 6 | •                                                                                                                 | ing Bubble Razor to the ARM Cortex-R4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>73</li> <li>73</li> <li>74</li> <li>77</li> <li>79</li> <li>79</li> <li>80</li> <li>82</li> <li>84</li> </ul>                                             |

|   | 7.1<br>7.2                                                                                                        | Contributions of This Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84<br>85<br>85<br>87<br>87                                                                                                                                         |

| APPENDIX     | <br> | • |  |  | • | • | • | • | • |  | • | • | • | <br>• |  | • | • | • | • | • | • | • |   | 89  |

|--------------|------|---|--|--|---|---|---|---|---|--|---|---|---|-------|--|---|---|---|---|---|---|---|---|-----|

| BIBLIOGRAPHY | <br> |   |  |  | • |   |   |   | • |  |   | • | • | <br>• |  |   |   |   |   |   | • |   | • | 102 |

## LIST OF FIGURES

### Figure

| 2.1 | By using two-phase latch based timing, minimum delay constraints are re-<br>stored to their conventional values allowing for large speculation windows. | 9  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | In a two-phase latch based system, instructions can stall without immediately                                                                           |    |

|     | being overwritten.                                                                                                                                      | 12 |

| 2.3 | Timing errors are corrected by propagating bubbles which gate off clock pulses                                                                          |    |

|     | throughout the circuit.                                                                                                                                 | 13 |

| 2.4 | Bubbles are communicated to neighboring latches. Upon error resolution,                                                                                 |    |

|     | every latch has stalled for exactly one cycle                                                                                                           | 14 |

| 2.5 | When determining where error detection is needed for a given speculation                                                                                |    |

|     | window, time borrowing can complicate analysis.                                                                                                         | 16 |

| 2.6 | Wrapper logic is placed around the SRAM such that it can be treated as a                                                                                |    |

|     | positive latch.                                                                                                                                         | 18 |

| 2.7 | Clustering was performed automatically by building two graphs based on latch                                                                            |    |

|     | connectivity. A tradeoff exists between the size of OR gates which is balanced                                                                          |    |

|     | by the choice of the number of clusters. The data shown is for a Cortex-M3                                                                              |    |

|     | processor                                                                                                                                               | 19 |

| 3.1 | Transforming the Cortex-M3 to two-phase latches can incur an $8\%$ area penalty                                                                         |    |

|     | or $7\%$ performance penalty.                                                                                                                           | 22 |

| 3.2 | The Cortex-M3 has an imbalanced path distribution as a result of retiming.                                                                              | 23 |

| 3.3 | Error checking can be added to a subset of latches, or a subset of only positive                                                                        |    |

|     | or only negative latches, yielding different area overheads. This is due to the                                                                         |    |

|     | distribution of critical path delays at the inputs of each latch.                                                                                       | 24 |

| 3.4 | Bubbles are combined using dynamic OR gates. A cluster ignores bubbles if                                                                               |    |

|     | it stalled in the previous cycle.                                                                                                                       | 25 |

| 3.5 | By running the system under nominal conditions instead of with worst case                                                                               |    |

|     | margins, performance or energy can be improved                                                                                                          | 29 |

| 3.6 | Due to only a single cycle penalty for fixing timing errors, an additional $22\%$                                                                       |    |

|     | performance gain or 17% energy reduction can be made by running beyond                                                                                  |    |

|     | the Point of First Failure.                                                                                                                             | 30 |

| 3.7 | Die photo and system information.                                                                                                                       | 32 |

| 4.1  | The boosting of VDD allows the circuit to run faster and for timing errors to recover                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2  | Boosting of VDD allows for the correction of the timing error even before VDD has stabilized and stopped ringing                                       |

| 4.3  | Block diagram of Voltage Razor test chip                                                                                                               |

| 4.4  | Standard cells comprising error detection latch                                                                                                        |

| 4.5  | With the latch clock and detection clock aligned, the latch behaves like the                                                                           |

| 4.6  | Bubble Razor latch                                                                                                                                     |

| 4.7  | Clock generation logic for Razor Core                                                                                                                  |

| 4.8  | Razor Cortex-M3 layout with clock mesh drivers around border.                                                                                          |

| 4.9  | Closeup of Razor core's corner and clock mesh drivers                                                                                                  |

| 4.10 | Allowing skew between the Bus clock and Core clock can allow for permanent time borrowing at the interface between latch and flip-flop based circuits. |

| 4.11 | Layout picture of 28nm Voltage Razor test chip                                                                                                         |

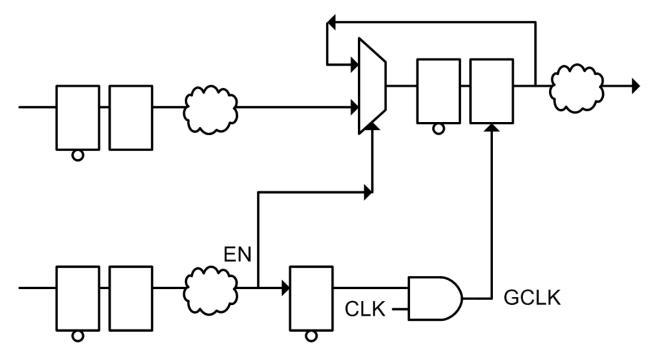

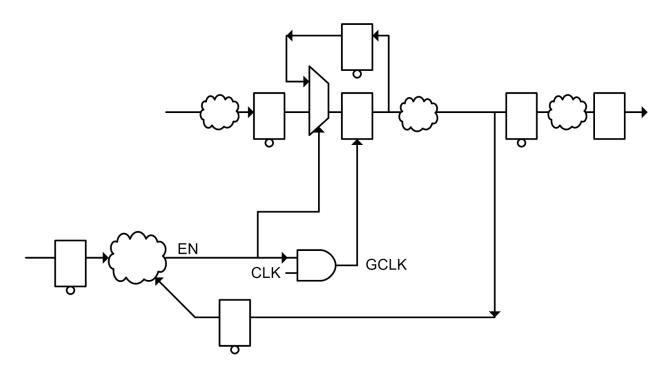

| 5.1  | Clock Gating in a conventional system where Flip-Flops are drawn as their                                                                              |

| 0.1  | constituent latches.                                                                                                                                   |

| 5.2  | Clock Gating and its equivalent redundant logic.                                                                                                       |

| 5.3  | The first step of retiming, moving the negative latch across the MUX.                                                                                  |

| 5.4  | The circuit, ready to be retimed using a commercial retiming tool.                                                                                     |

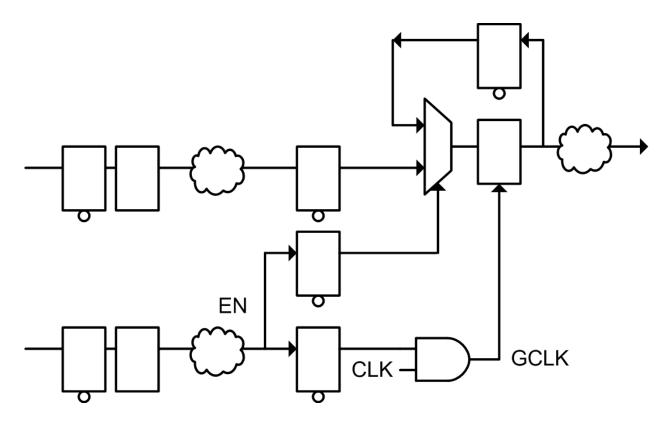

| 5.5  | When Looking Forward to Assign Clocks to Negative Latches, They Must be                                                                                |

| 0.0  | Held Open When Clock Gated                                                                                                                             |

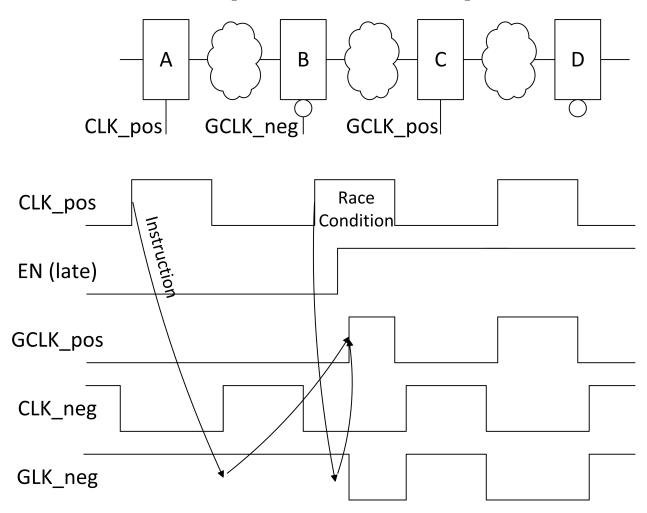

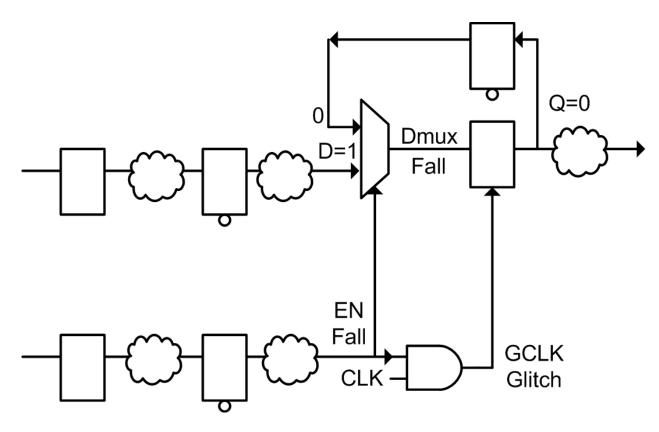

| 5.6  | Late EN causes race condition                                                                                                                          |

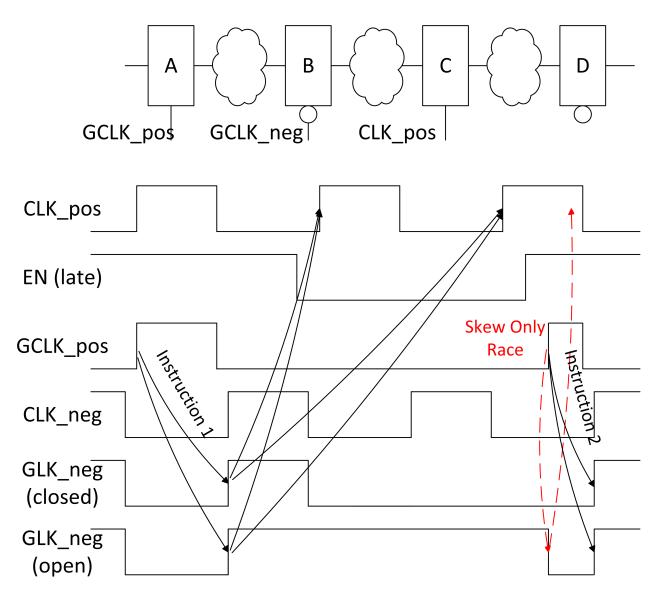

| 5.7  | When Assigning Clocks Based on Fanin, Negative Latches can Hold Open or<br>Closed when Gated                                                           |

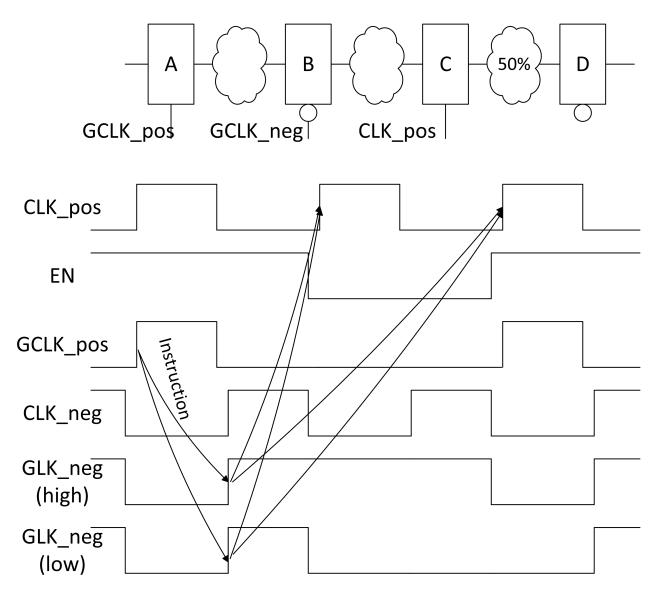

| 5.8  | Late arriving EN signals do not cause race conditions.                                                                                                 |

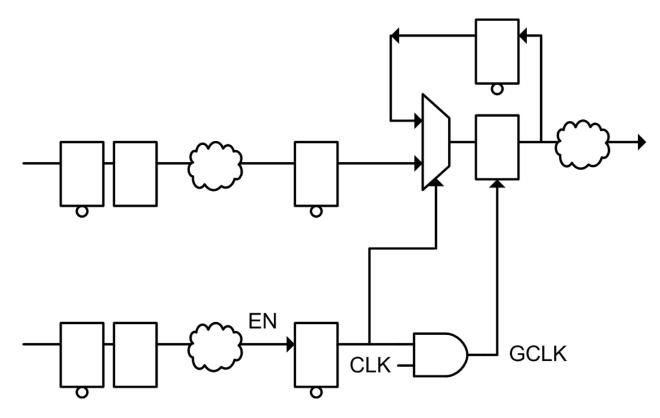

| 5.9  | After transforming to latches, and prior to retiming.                                                                                                  |

| 5.10 | Mid-retiming with negative latches moving back                                                                                                         |

| 5.11 | After retiming, if negative latches look forward to determine gated clocks, no                                                                         |

|      | timing loop exists since a clock gate is in the fanout of the moving latch                                                                             |

| 5.12 | If negative latches do not look forward to determine clock assignment, timing                                                                          |

|      | loops can be created.                                                                                                                                  |

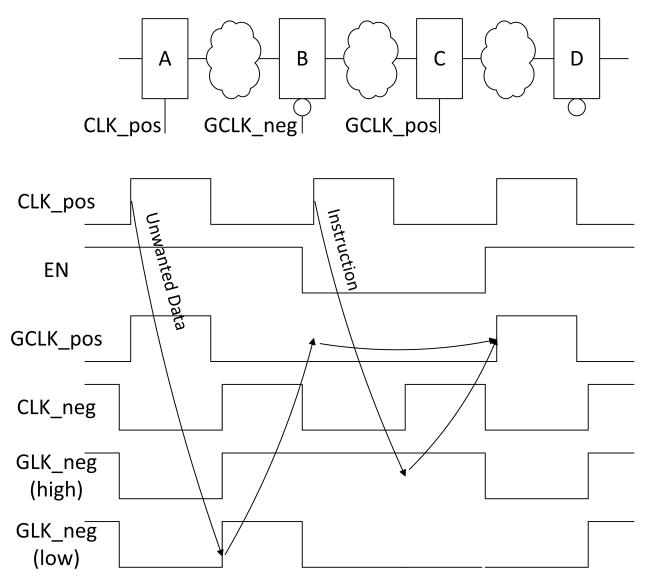

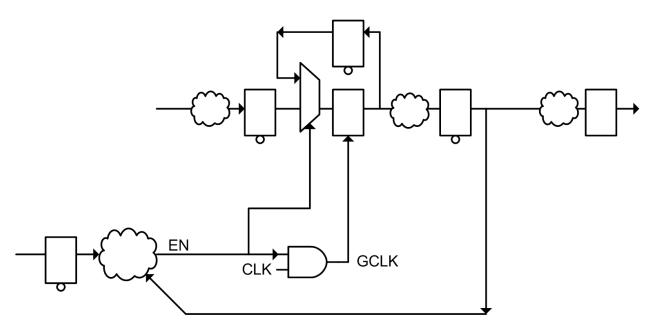

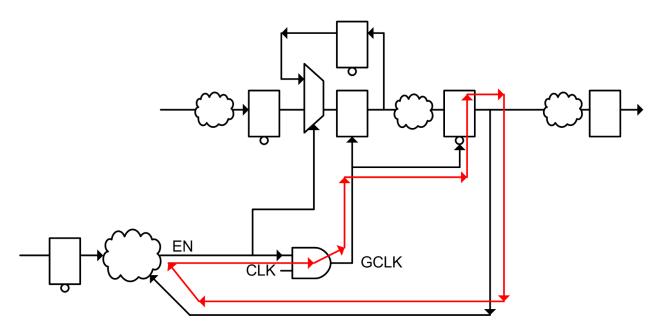

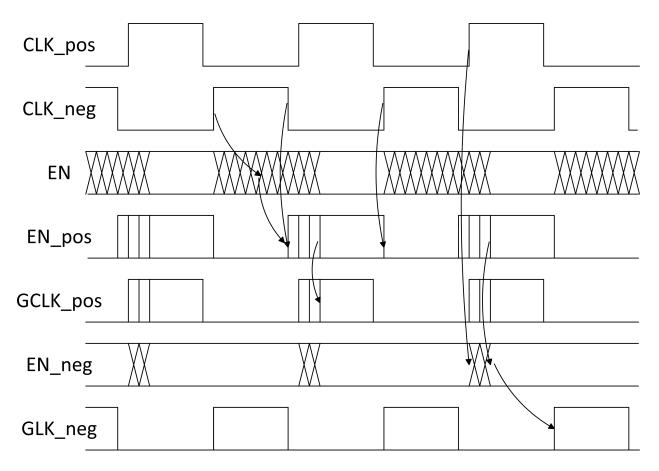

| 5.13 | Proposed Clock Timing for Latch Based Design with Clock Gating                                                                                         |

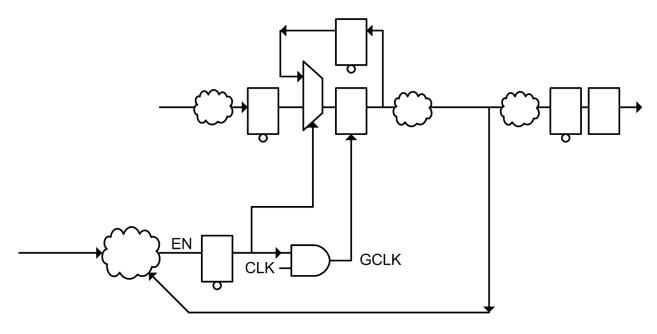

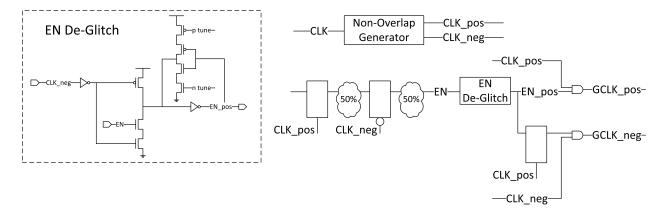

| 5.14 | Proposed Circuits for Clock Generation                                                                                                                 |

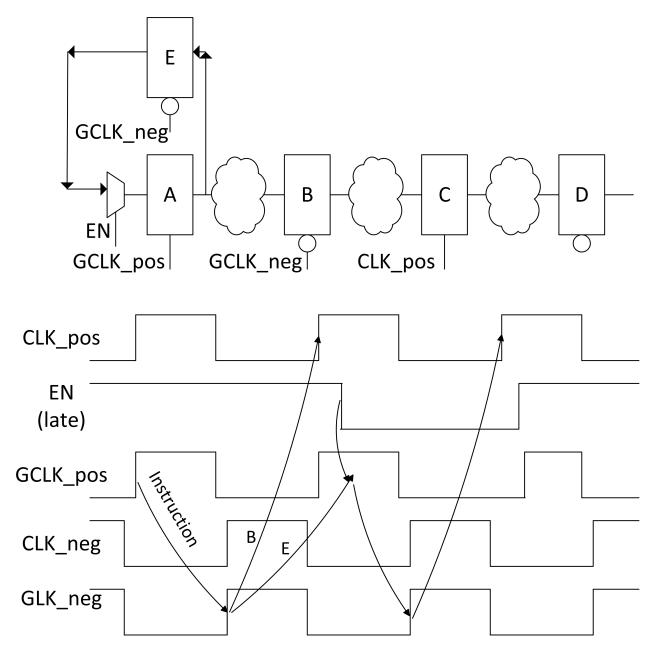

| 5.15 | The addition of latch E and the MUX allows for correct behavior when $CCLK$ around incorrectly.                                                        |

| 5 16 | $GCLK_{pos}$ opens incorrectly                                                                                                                         |

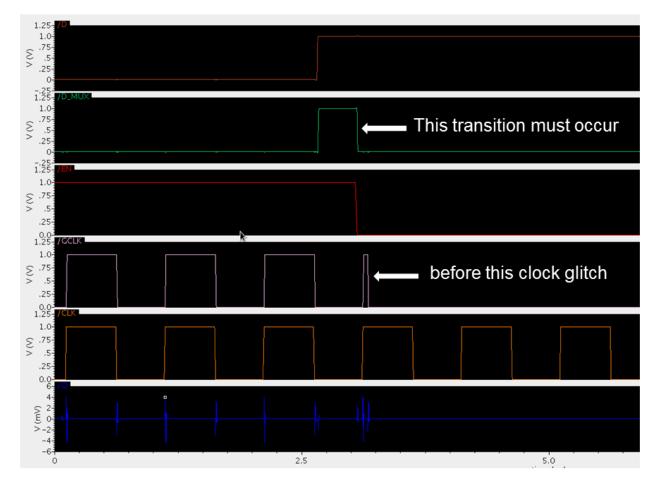

|      | EN may be sampled at a time which causes metastability on GCLK The circuit is metastability immune so long as the output of the MUX is stable.         |

| 0.17 | The circuit is metastability immune so long as the output of the MUX is stable before the glitch or bad pulse on GCLK                                  |

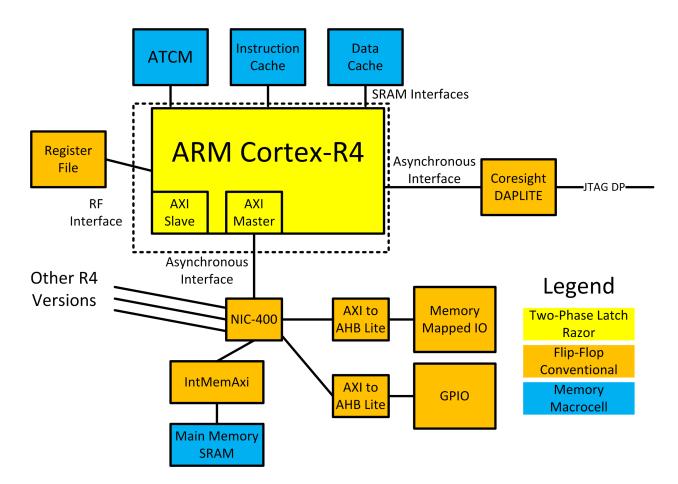

| 6.1  | Block Diagram of ARM Cortex R4 based Bubble Razor Implementation                                                                                       |

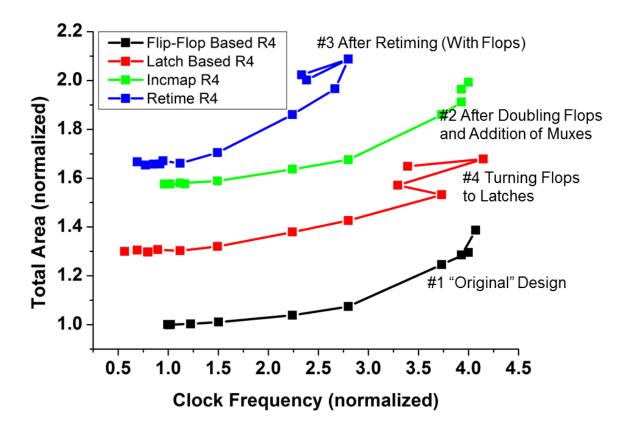

| 6.2  | Total Area of Cortex-R4 at various steps in latch transformation                                                                                       |

| 0.2  | I UTAL ALEA OF COLLEX-ITY AT VALUES STEPS III LATCH FLAUSIOFILIATION $\ldots$                                                                          |

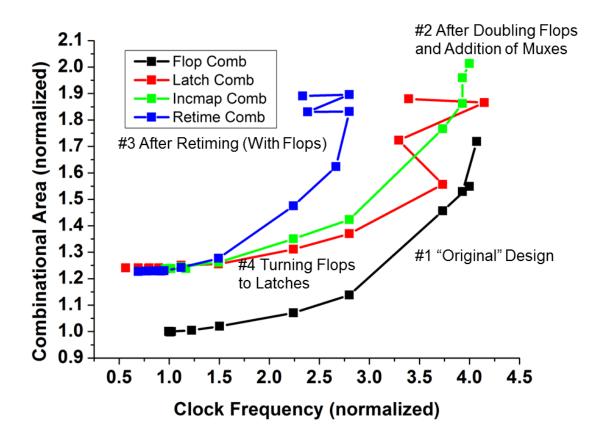

| 6.3 | Combinational Area of Cortex-R4 at various steps in latch transformation . | 76 |

|-----|----------------------------------------------------------------------------|----|

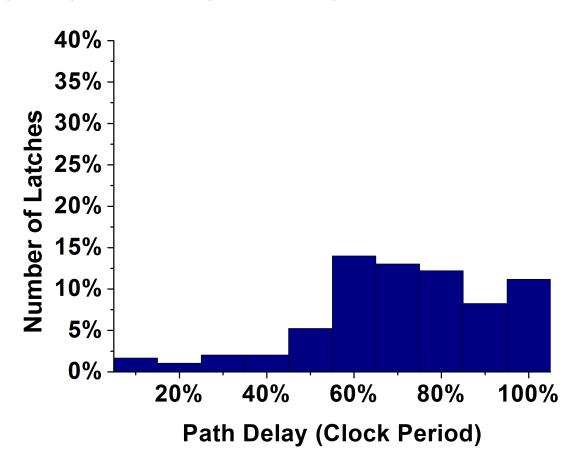

| 6.4 | Criticality of Positive Latches at Relaxed Timing Constraint               | 77 |

| 6.5 | Criticality of Positive Latches at Tight Timing Constraint                 | 78 |

| 6.6 | Bubble Razor logic for Cortex-R4 Implementation                            | 79 |

| 6.7 | The timing and interface to a conventional register file                   | 81 |

| 6.8 | The timing, interface, and wrapper to a register file with Bubble Razor    | 82 |

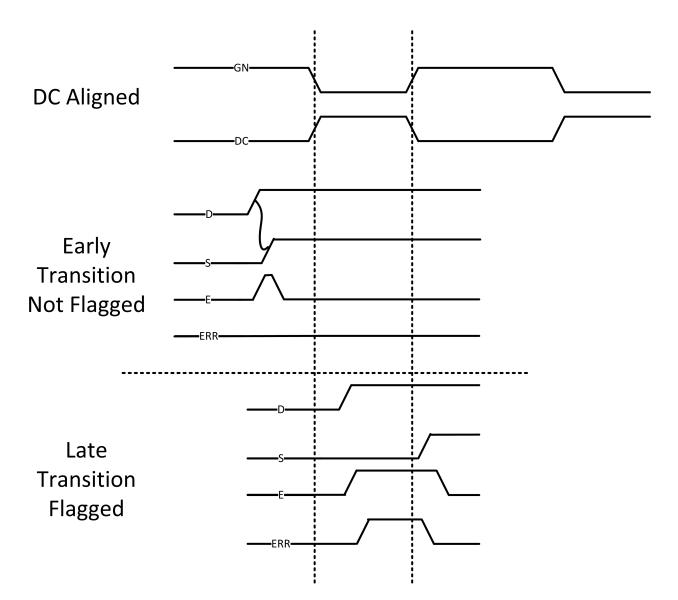

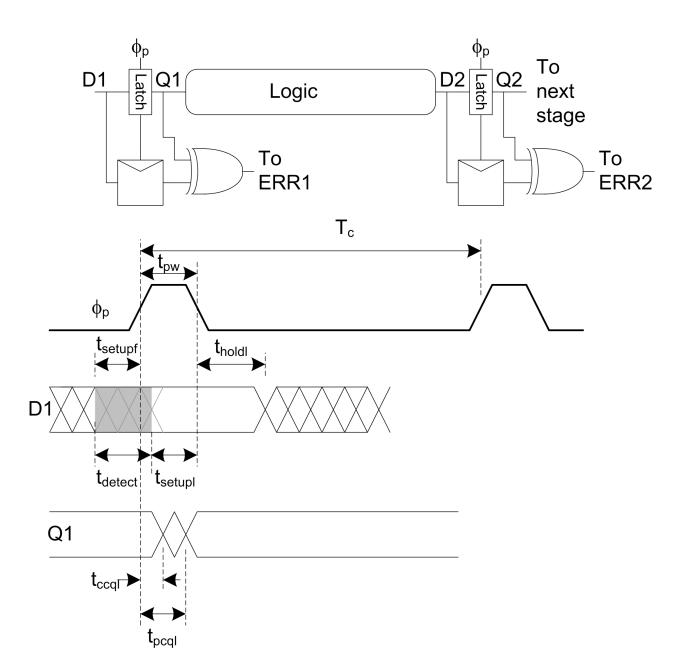

| A.1 | Timing Diagram for DSTB System                                             | 92 |

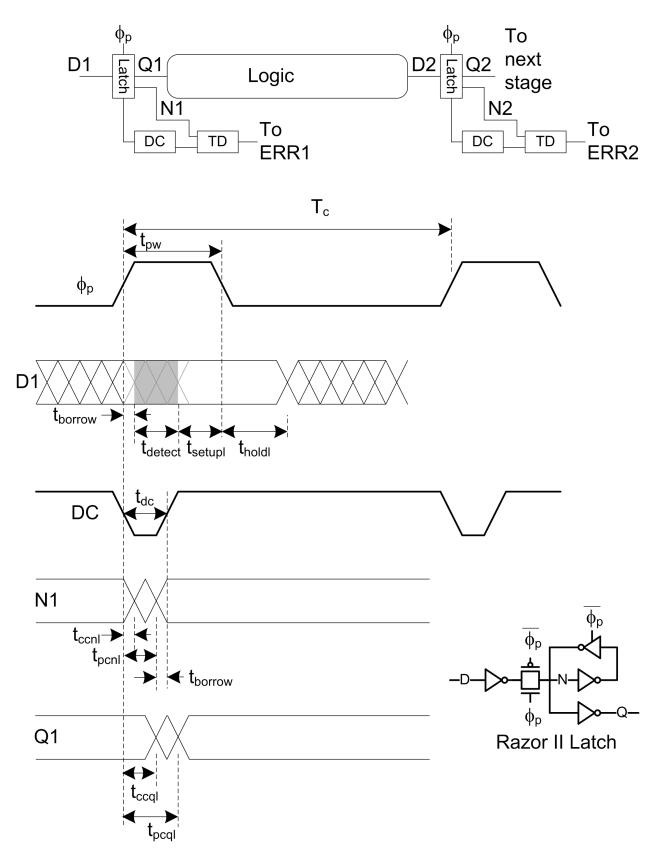

| A.2 | Timing Diagram for Razor II System                                         | 95 |

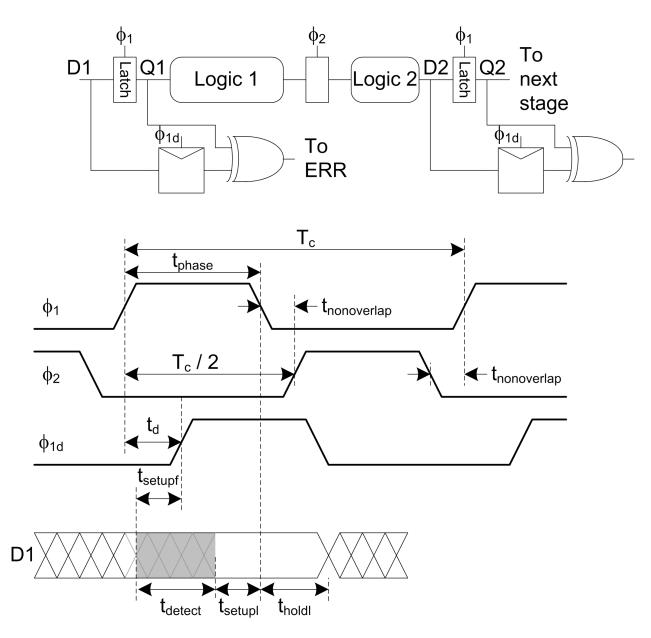

| A.3 | Timing Diagram for Bubble Razor System                                     | 98 |

|     |                                                                            |    |

## LIST OF TABLES

### Table

| 1.1 | Types of Delay Variation                                                 | 2  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Comparison of Timing Margin Reduction Techniques and Razor-Style Designs | 5  |

| 4.1 | Comparison of Three Cortex-M3 Processors                                 | 42 |

| A.1 | Terminology                                                              | 90 |

| A.2 | Timing Constraints for Conventional Systems                              | 91 |

### CHAPTER 1

### Introduction

### **1.1** Sources of Delay Variation

Conventional digital circuits must ensure correct operation throughout a wide range of operating conditions. These operating conditions can comprise process, voltage, and temperature (PVT) variation and can be static or ambient. The primary effect these variations have on digital circuits is on circuit delays, determining a circuit's maximum operating speed [1].

Static timing variation is usually a result of process corners and mismatch. Global, chipwide, variability in  $V_{th}$ , oxide thickness, or wire capacitance manifests as a static change in circuit delay that varies from chip-to-chip. Within-die, local, process variation is also present as a result of effects such as random dopant fluctiations and line edge roughness.

Ambient effects, such as supply noise and operating temperature, also affect circuit delay. These effects can also be global or local in scope. In the case of temperature, variation could be caused by global changes to the environment or local hot spots due to high power consumption of select blocks. These effects can also be classified in how quickly they change. Voltage droops can occur within a clock cycle, while temperature changes may gradually occur over thousands of cycles [1].

The final classification of delay variation is from the data being run through the circuit. The critical path in a circuit, and thus the maximum operating frequency, varies from cycle to cycle depending on the instruction being processed and the data being computed [2].

### **1.2** Conventional Approaches to Delay Variation

Microprocessor design in current CMOS technologies has become extremely challenging due to PVT variations [3, 4]. Traditionally, significant worst-case margin is added to the clock cycle to ensure that the targeted frequency is met over a wide range of PVT conditions and in the presence of fast transient timing errors (due to, e.g., fast/local supply voltage droops, soft errors, cross-coupling noise, clock jitter) [2, 5, 6]. Although this simplifies the design, the amount of margining required to achieve acceptable parametric yield has become very expensive in terms of performance and energy due to growing PVT variations. This poses a serious limit to the energy efficiency improvement in all market segments ranging from high performance (due to frequency reductions) to very low power (voltage cannot be scaled as larger margin is needed at low voltage) [7].

In recent years, a number of post-silicon techniques have been proposed to reduce design margin in microprocessors. For example, limited margin reduction has been achieved through VDD/frequency/body bias feedback compensation of slow variations that are captured through on-chip voltage/temperature sensors [5, 6, 8–11]. As an alternative, error prediction has been used through canary structures as well as lookup tables however these cannot fully capture within-die variations and still introduce some margin [7, 9, 12–14].

Table 1.1 compares several conventional approaches to addressing these types of variation. Characterization at tester time and table lookup can reduce the effect of static process variation, however speed testing all potentially critical paths can be costly. The addition of sensors to detect ambient conditions allows for slow, global ambient variation to be reduced but this comes at an even greater characterization cost. Canary circuits [12, 15–20] are a

| Technique                           | Sta    | tic   |        | Data |       |      |   |

|-------------------------------------|--------|-------|--------|------|-------|------|---|

|                                     | Global | Local | Global |      | Local |      |   |

|                                     |        |       | Slow   | Fast | Slow  | Fast |   |

| Table Lookup                        | Х      | Х     |        |      |       |      |   |

| Table & Sensors                     | X      | Х     | X      |      |       |      |   |

| Canary Circuits [12, 15–20]         | X      |       | X      |      |       |      |   |

| Razor-Style Designs $[2, 7, 21-24]$ | X      | Х     | X      | Х    | Х     | Х    | Х |

Table 1.1: Types of Delay Variation

popular approach to reducing timing margins which involve creating a replica circuit with delay matched to the critical path. This circuit tracks the operating conditions but can not respond to fast changing ambient conditions, and can not reduce local mismatch since the canary is a separate structure from the design itself.

The Razor [24] system proposed eliminating all timing margins, including those caused by data variation, by running the circuit with occasional timing errors and correcting the errors when they occur. As the checking is performed *in situ*, margins for every classification of timing variation can be eliminated. Razor Style Designs [2, 7, 21-24] allow errors to occur in order to eliminate all types of timing margins, though the methodology for detection and correction varies from scheme to scheme.

### **1.3** Comparison of Razor-Style Designs

Although all Razor-Style Designs [2,7,21–24] eliminate timing margins by running with timing errors and correcting for those errors, they differ in their correction mechanisms.

The Razor [24] system proposed two approaches to correcting errors, global stalling and counterflow pipelining. Global stalling relied on the type of double sampling error detection circuit used where, upon detection of an error, all flip-flops in the processor stalled while all Razor flip-flops in the processor reloaded their values with the correct data stored in their shadow latch. The circuit then proceeded as normal in the next cycle. This technique is architecture independent, thus it can be applied to an existing design with minimal designer effort, however it is limited in its scale. Because the technique relies on communicating an error signal to the entire processor in the same cycle, it can not be scaled to large designs with aggressive clock periods.

To address this concern, Razor also proposed counterflow pipelining, which relied on the architecture to correct for errors. When a pipeline state detected an error, it communicated a stall with its downstream stage and a flush with its upstream stage. When a flush reached the first stage, it fetched the first instruction after the failing one and continued. Although this technique eliminated the need for a global stall signal, it requires the architecture to be designed with Razor in mind and puts the correction logic in the RTL adding to the work

of the designer.

Further Razor work also used architecture specific correction mechanisms. Razor II [22] recognized that many processor architectures already support speculative execution when predicting branches. Thus, when a timing error was detected, it set a flag indicating that the instruction was in error and used the existing flushing mechanism to clear the pipeline and rerun the errant instruction. In order to ensure the failing instruction did not repeatedly fail and prevent the system from making forward progress, the instruction was rerun at half the original clock frequency. EDS [23] and ARM's Razor [21] corrected for errors in a similar way. Multiple Issue EDS [7] avoided adjusting the clock network when replaying failing instructions by issuing it multiple times in order to set up the correct values at the inputs of each pipeline stage. In these systems, it is necessary that no speculative state be written to memory or external peripherals, thus the configuration of the processor is limited to architectures with stabilization stages and write-back stages at the end of the pipeline.

Because of the architectural invasiveness of these techniques, no published Razor Style system had been applied to a complete existing commercial processor. If processor architectures are not designed with Razor in mind from the beginning, it can be difficult or impossible for a designer to adapt the system to allow Razor Style error detection and correction.

Additionally, in all conventional Razor-style systems [2,7,21–24], regardless of architecture dependence, there is a fundamental tradeoff between speculation window and short path, or minimum delay, constraints. When data arrives within the speculation window after the positive edge of a flip-flop's clock, that data must be guaranteed to be from a long path launched from the previous clock edge. In order to ensure this, all short paths must be longer than the speculation window such that no short path can falsely trigger an error. This timing constraint must also be margined for any degree of timing variation. Detailed analysis of this tradeoff is discussed in Appendix A.

| Technique                    | Eliminates | Slow      | Fast      | Scalable | Arch.  | Min Delay | Design                |

|------------------------------|------------|-----------|-----------|----------|--------|-----------|-----------------------|

|                              | Margins    | Variation | Variation | Size     | Indep. | Unchanged | $\operatorname{Cost}$ |

| Canary Circuitry [12, 15–20] |            | Х         |           | Х        | Х      | Х         | Low                   |

| Razor (Global Stall) [24]    | Х          | Х         | Х         |          | Х      |           | Low                   |

| Razor (Counterflow) $[24]$   | Х          | Х         | Х         | Х        |        |           | High                  |

| Razor II [22]                | Х          | Х         | Х         | Х        |        |           | High                  |

| EDS [23]                     | Х          | Х         | Х         | Х        |        |           | High                  |

| ARM Razor [21]               | Х          | Х         | Х         | Х        |        |           | High                  |

| Multiple Issue EDS [7]       | Х          | Х         | Х         | Х        |        |           | High                  |

| Bubble Razor (Proposed) [25] | Х          | Х         | Х         | Х        | Х      | Х         | Low                   |

| Voltage Razor (Proposed)     | Х          | Х         | Х         | Х        | Х      | Х         | Low                   |

Table 1.2: Comparison of Timing Margin Reduction Techniques and Razor-Style Designs

### **1.4** Contributions of this Work

This thesis proposes two latch based Razor Style techniques that address the architecture dependence and scalability issues of previous Razor Style systems and also break the dependence between speculation window and minimum delay constraints.

Table 1.2 compares Canary Circuitry to existing Razor Style designs and the methods proposed in this thesis. All Razor Style designs eliminate timing margins and adapt to all types of timing variation but a tradeoff exists between scalability and architecture independence. All suffer from the link between minimum delay constraints and speculation window. The proposed systems offer the benefits of prior Razor Style techniques while also providing the scalability, architecture independence, and unaffected minimum delay constraints of canary circuits. In addition, the design effort of the proposed systems are low due to their automated nature.

Chapter 2 proposes the concept of latch based Razor and presents the Bubble Razor algorithm. It also explains the process of automatically transforming an existing design to a latch based Razor style system. Chapter 3 describes the specific implementation details and measurement results of the Bubble Razor algorithm applied to an ARM Cortex-M3 processor and implemented in silicon in a 45nm SOI process. Chapter 4 discusses Voltage Razor, another latch based Razor technique that uses voltage boosting to provide the circuit speed up needed for error correction. Chapter 5 discusses transforming a flip-flop based design which uses architectural clock gating to two-phase latches in which time borrowing can be used for error correction, allowing the application of either Bubble Razor or Voltage Razor to the target design. Bubble Razor is applied to a larger processor which makes use of clock gating, the ARM Cortex-R4, in Chapter 6. Chapter 7 summarizes the contributions in this thesis and proposes some direction for future work. A thorough analysis of the timing constraints in latch based razor is discussed in Appendix A

### CHAPTER 2

# Bubble Razor: An Architectural Independent Approach to Timing Error Detection and Correction

We propose Bubble Razor, an architecturally independent approach to timing error detection and correction that avoids hold-time issues and enables large timing speculation windows. A local stalling technique that can be automatically inserted into any design allows the system to scale to larger processors.

### 2.1 Introduction

Conventional synchronous digital systems require substantial timing guard bands to ensure proper operation across manufacturing and environmental variations. While manufacturing guard bands can be reduced by testing a part after production and adjusting voltage or frequency, this process is costly and still does not eliminate the guard bands for dynamic environmental variation. Traditional approaches to reduce margining at runtime include mimicking critical path delays with "canary" circuitry and using error prediction [12,15–20] The Razor system [2,24] proposed reducing these margins by employing in-situ timing error detection latches, and dynamically tuning the supply voltage during run time to the point where the circuit is on the edge of failure. Occasional timing failures are then corrected by replaying the operation with greater margin. By always operating at the edge of failure, manufacturing and environmental guard bands are reduced to a minimum.

Multiple timing error detection techniques have been proposed, including Output Wave-

form Analysis [26], Time-Redundant Latches [27], Razor I latches [2,24], Razor II latches [22], Transition Detector with Time Borrowing (TDTB) [23], and Double Sampling with Time Borrowing (DSTB) [23]. All focus on detecting data that arrives shortly after the clock edge and flagging it as an error. The earlier references focused on SEU detection and the later on Razor-style voltage tuning to eliminate margins.

Razor II, DSTB, and TDTB provide higher performance at lower cost than the earlier work. By reducing guard bands, they have demonstrated better than 30% energy savings [22,23]. They also move metastability issues out of the datapath and into the error path, simplifying mitigation of this effect. These techniques have timing issues similar to pulsed latches in that they achieve high performance at the expense of a long hold time, increasing the risk of race failure. These significant hold time constraints are even more difficult to meet given worsening timing variability due to the link between speculation window and minimum delay. In addition, none of these methods have been applied to a complete commercial processor due to their architectural invasiveness.

To address these two issues we propose Bubble Razor, which uses a novel error detection technique based on two-phase latch timing and a local replay mechanism that can be inserted automatically in any design. The error detection technique breaks the dependency between minimum delay and speculation window, restoring hold time constraints to conventional values and allowing timing speculation of up to 100% of nominal delay. The large timing speculation makes Bubble Razor especially applicable to low voltage designs where timing varies exponentially with operating conditions.

### 2.2 Review of Prior Razor Methods

#### 2.2.1 Conventional Razor System Timing

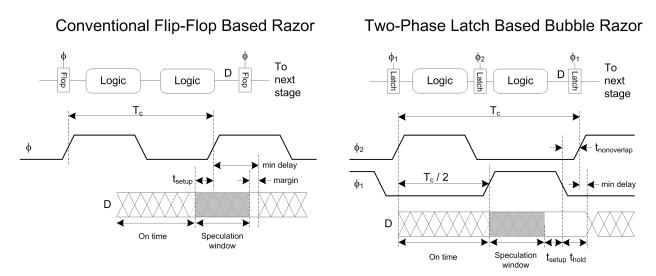

In all conventional Razor-style systems [2, 7, 21-24, 28], there is a fundamental tradeoff between speculation window and short path, or minimum delay, constraints (Fig. 2.1). In a system that allows 100ps of timing speculation, when data arrives within 100ps after the positive edge of a flip-flop or pulsed latchs clock, that data must be guaranteed to be from a long path launched from the previous clock edge. In order to ensure this, all short paths must be longer than 100ps such that no short path can falsely trigger an error. This timing constraint must also be margined for any degree of timing variation. As Razor-style systems are targeted for situations with large timing variations, this constraint can be difficult to meet and causes large area and power increases due to buffers and other delay elements that are added to lengthen short paths. Further discussion of the timing constraints of conventional Razor-style systems is included in Appendix A.

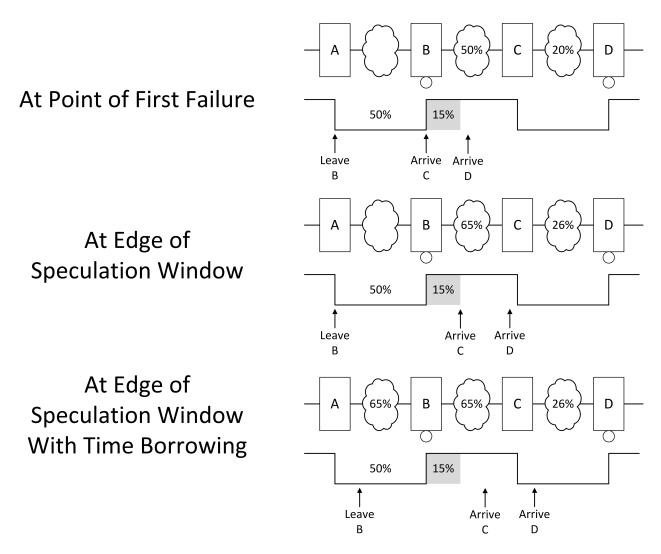

Figure 2.1: By using two-phase latch based timing, minimum delay constraints are restored to their conventional values allowing for large speculation windows.

#### 2.2.2 Conventional Razor Error Correction Schemes

Upon detection of an error, some mechanism needs to correct for that error and allow the system to continue. Razor I [2] proposes two different styles of error correction, global clock gating and counterflow pipelining. Global clock gating involves stalling the entire processor and reloading each Razor flip flop with the correct value stored in its shadow latch. Counterflow pipelining has the error detecting stage send a bubble to downstream pipeline stages and a flush to upstream stages, which was propagated throughout the circuit one stage every clock cycle. Razor II [22] proposes another local signaling technique using architectural replay to flush the processor pipeline and replay the failing instruction, similar to how mispredicted branch instructions are handled. In order to guarantee forward progress the processor must be slowed during replay to ensure the same instruction does not repeatedly cause a timing error. In both counterflow pipelining and architectural replay, the architecture is designed with Razor in mind and the correction mechanism is built into the RTL of the design.

Razor Is global clock gating technique is architecture independent, but its scale is limited to small designs without aggressive clock periods, as communicating a stall to the entire chip within one cycle can be impossible for large high performance designs. In all conventional Razor systems, if architecture independent stalling is used to correct for errors, it needs to be done at the global level. This is because the datapaths are based on edge-triggered flip-flops or pulsed latches, which have similar timing constraints to edge-triggered flip-flops. If one pipeline stage in a conventional Razor style system stalls, by gating its clock, the instruction held in the previous stage is lost, as every pipeline stage holds an instruction during every cycle and all of them update their state concurrently.

### 2.3 Proposed Bubble Razor Approach

#### 2.3.1 Bubble Razor Timing

Unlike conventional Razor style systems, Bubble Razor uses a two-phase latch based datapath instead of a flip-flop based datapath. This has two main benefits: (1) it breaks the dependency between short path constraints and speculation window, enabling large speculation windows and (2) it allows for architecture independent local correction, which can scale to large high performance systems. A flip-flop based datapath can be converted into a two-phase latch based datapath by breaking the flip-flops into their constituent master and slave latches. By using commercial retiming tools to move the latches throughout the datapath, logic delay in each phase can be balanced such that no time borrowing occurs during error-free operation. Retiming can be performed to the same timing constraints, though the number of latches in the design may change due to retiming across gates with unequal fanins and fanouts.

During normal (error-free) operation data arrives at a latch input before the latch opens

and no time borrowing occurs. If data arrives after the latch opens due to operating at the edge of failure, Bubble Razor flags an error. Unlike with flip-flop based systems, these errors are guaranteed to be caused by long paths taking more than a clock phase instead of by short paths, breaking the link between speculation window and short path constraints (Fig. 2.1). With a flip-flop based system, a flip-flop in one pipeline stage is clocked at the same time as the flip-flops in the preceding pipeline stage, creating the possibility of short paths being falsely flagged as timing errors. With two-phase latches, when one latch is opening the latches in the preceding stage are already closed. Thus, since new data is not being launched at that time, there is no possibility of short paths being falsely flagged as timing errors. The short path constraints in a Bubble Razor system are thus the same as in a conventional two-phase latch based system, which are easy to meet with non-overlapping clocks. This enables large speculation windows, up to 100% of circuit delay.

#### 2.3.2 Bubble Razor Error Correction

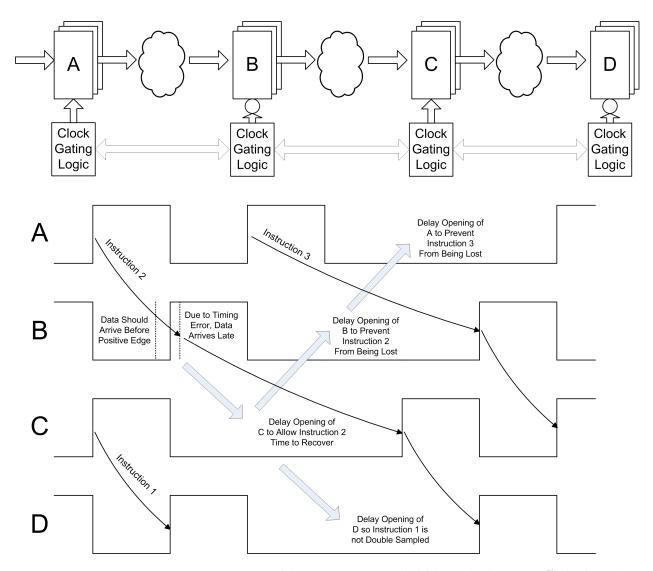

Regarding error correction, the key observation is that errors do not immediately corrupt processor state as they borrow time from later pipeline stages. A failure will occur when data arrives after a latch closes, which can arise if the time borrowing effect is not corrected and compounds through multiple stages. Upon detection of a timing error, it is critical to recover quickly before time borrowing accumulates to a point of failure. Error clock gating control signals (bubbles) are propagated to neighboring latches (Fig. 2.3). A bubble causes a latch to skip its next transparent clock phase, giving it an additional cycle for correct data to arrive.

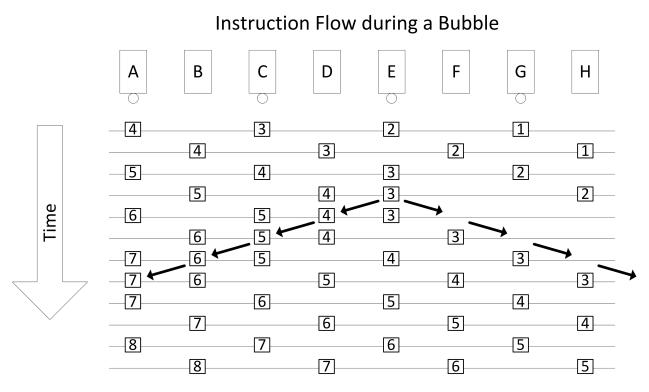

Unlike with flip-flop based systems, error correction can be accomplished by local stalling (Fig. 2.2). When a flip-flop stalls, data is immediately lost as its neighboring flip-flops transition their state at the same point in time. With two-phase latches, if a latch stalls, data is not immediately lost because its neighboring latches operate out of phase. In order to not lose data, neighboring latches must stall one clock phase later. Because of this time difference, the stalling can be distributed in time and only needs to be communicated to neighboring stages, stages with which data is already being communicated. Because stall

Figure 2.2: In a two-phase latch based system, instructions can stall without immediately being overwritten.

signals need only be distributed to neighboring stages in the same amount of time given to communicate data, the system is scalable to processors of arbitrary size.

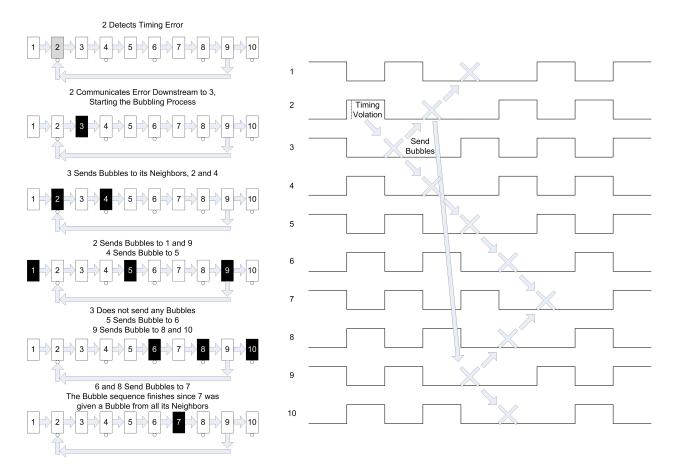

A key challenge lies in how to prevent bubbles from propagating indefinitely along loops and forwarding paths and bring the circuit back to a consistent, bubble-free state. To address this, we propose a novel bubble propagation algorithm: (1) a latch that receives a bubble from one or more of its neighbors stalls and sends its other neighbors (input and output) a bubble one half-cycle later; (2) a latch that receives a bubble from all of its neighbors stalls but does not send out any bubbles (Fig. 2.4). Despite the fact that latches stall at different times, the system maintains correct operation with every latch in the design stalling exactly once. The stalling technique is agnostic to state machine architecture or structure, allowing bubble clock gates and control logic to be automatically inserted. The only change to the external behavior of the system is an occasional single stall cycle on the inputs and outputs.

Other key questions include how the system behaves in the presence of multiple timing errors during the same cycle, the presence of multiple bubble sequences in flight at the same

Figure 2.3: Timing errors are corrected by propagating bubbles which gate off clock pulses throughout the circuit.

time, and whether forward progress is maintained during high error rates. The bubble algorithm does not need to be modified to address any of these concerns. Multiple errors during the same cycle will cause multiple bubble stalling sequences to take place at the same time, but when stall events collide they combine. The latches receiving bubbles are not aware of where the initial error occurred and they do not need to, as the stalling constraints from each error sequence overlap. It is beneficial to have multiple bubble sequences combine as multiple timing errors can be corrected by a single stall cycle, reducing correction overhead. The algorithm is also guaranteed to make forward progress as a latch will never stall indefinitely. A latch stalls when sent a bubble by one or more neighbors and then sends a bubble

Figure 2.4: Bubbles are communicated to neighboring latches. Upon error resolution, every latch has stalled for exactly one cycle.

to its other neighbors. An equivalent definition for bubble propagation is for the latch to send a bubble to all its neighbors but ignore bubbles if it stalled in the previous cycle. Since a latch will never stall two cycles in a row, it will always make forward progress. We have shown that the system operates correctly even with every latch reporting a timing error during every cycle. In this case, every latch spends exactly 50% of its cycles stalling.

### 2.4 Bubble Razor Implementation Issues

#### 2.4.1 Speculation Window Selection

A Razor-style system can be tuned such that it is running error-free but with no timing margins in order to increase system performance. At this point, the circuit is susceptible to timing errors if logic delay suddenly increases due to a voltage droop, temperature spike, or other transient event. The speculation window determines the amount this logic delay is allowed to increase such that the system can still detect and correct errors and maintain correct operation. With Bubble Razor, as with other Razor systems, the speculation window can be limited by either the technique or the amount and location of latches with error checking. The maximum allowed speculation window is a full clock phase minus the delay of the error propagation circuitry. The theoretical maximum is therefore 100% of circuit delay, meaning correct operation could be maintained even if circuit delay suddenly doubles, although in practice the error correction circuits have non-zero delay. Because of the large allowable speculation windows, it is possible to tradeoff between speculation window and allowable time borrowing. Allowing some time borrowing can improve variation tolerance due to mismatch between stages, as well as reduce area overhead by limiting the number of latches introduced by retiming.

Placing error detection on every latch in the design is very costly in terms of area and power, and is not desirable. In addition, error detection is not required on all latches; if the critical path feeding into a latch is less than 50% of a clock phase, that latch will never experience a timing error even with a doubling of circuit delay.

Because the datapath is two-phase latch based, removing error detection from certain stages could allow time borrowing to occur without generating errors, complicating speculation window analysis. Fig. 2.5 shows an example of a system with a 30% speculation window. During error-free operation near the point of first failure (PoFF), the delay from Latch B to C is a full clock phase, 50% of a clock cycle, and the delay from C to D is only 20% of a clock cycle. Due to a voltage droop or other event, circuit delay becomes 130% of its nominal value such that the design is now operating at the edge of its speculation window. In this case, data does not arrive at C before it opens, however when looking at the combined path from B to D, the delay is only 91% of a clock period and data still arrives before Latch D opens. Because of the small delay between C and D, the path from B to C is able to borrow time and the timing error corrects itself without any need for bubbles. This would imply that error detection is not needed on C or D.

However, this analysis assumes that data is launched from Latch B at its opening edge. If the delay from A to B was nominally 50% of a clock cycle, and 65% after a voltage

Figure 2.5: When determining where error detection is needed for a given speculation window, time borrowing can complicate analysis.

droop, then data arrives at B late and pushes back all the subsequent stages such that data arrives late at D. This multi-phase analysis is complex, even for the simple in-order pipeline shown. For a general finite state machine with loops and forwarding paths the analysis is substantially more complicated.

To simplify the process of determining where error detection is needed, we propose disallowing all undetected time borrowing. Thus, a latch assumes that data is launched at the opening edge of the latches preceding it, and determines that error detection is needed if its data arrives late under worst case conditions. In the above example, Latches B and C add error detection because the worst-case delay of their critical inputs paths are 65% of a clock cycle, which is greater than a clock phase. This analysis only requires looking at one path at a time, though it can produce a larger set of latches with error checking than strictly necessary.

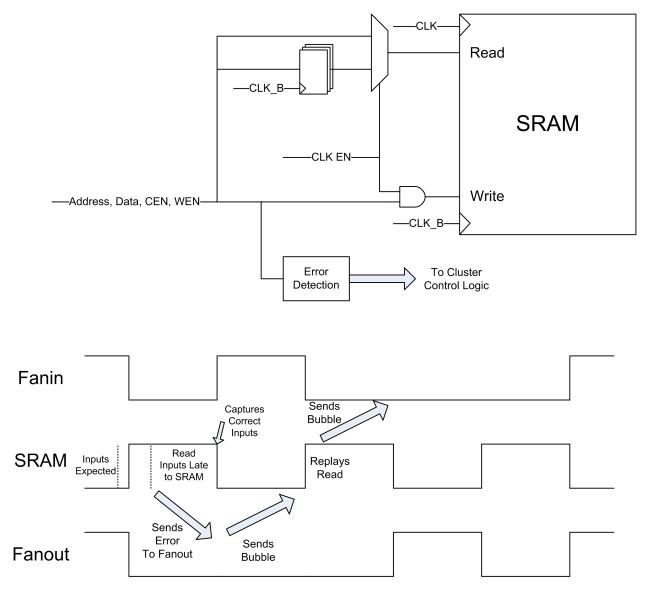

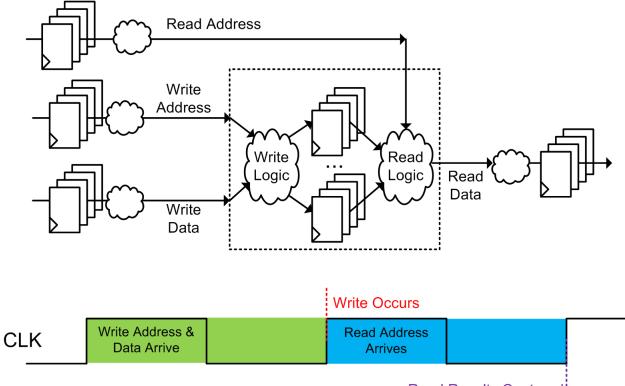

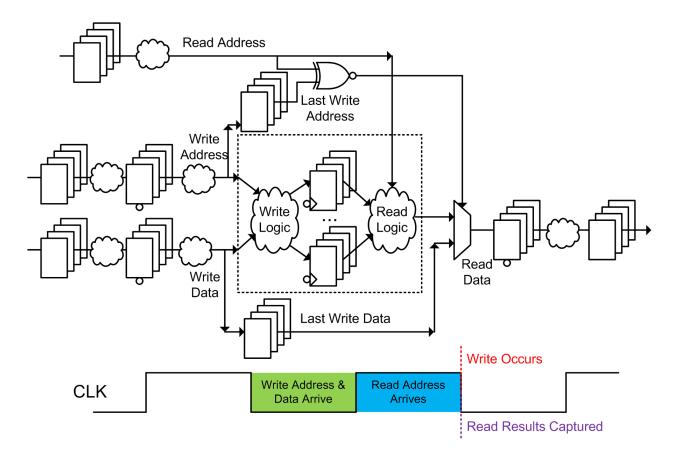

#### 2.4.2 SRAM Interface

The Bubble Razor algorithm works seamlessly for two-phase latches but adjustments need to be made when dealing with edge triggered peripherals such as SRAM. If speculative state was incorrectly written to memory that error could not be corrected for. SRAMs were treated as positive latches for the purpose of the Bubble Razor algorithm and wrapper logic was placed around SRAMs to make them behave similarly to level-sensitive latches when given a stall cycle (Fig. 2.6). In this implementation, the register file was synthesized logic and was transformed to two-phase latches along with the rest of the processor.

When retiming the design, negative latches are first placed on the outputs of the processor interface to memory such that the circuit is of legal configuration: all neighboring latches of the positive SRAM are negative latches. Assuming error checking occurs on the negative latches in the fanout of the SRAM, reads are constrained to operate in one clock phase. Depending on the configuration of the processor, this may introduce a tighter timing constraint. In a Cortex-M3 implementation timing is unaffected as SRAM is already operating in approximately 50% of a clock cycle with the other 50% of a clock cycle being used by combinational logic between the processors inputs and first flip-flops.

To avoid writing incorrect data to SRAM, the system uses a commercial two-port, highspeed SRAM that separates read and write ports. Writes are clocked on the negative edge of the clock, after the speculation window, when data is guaranteed to be error free. A single entry store buffer could alternately be used to stabilize writes. Writes are disabled when the SRAM receives a bubble.

Since reads cannot be delayed without reducing system performance, they continue speculatively at the positive edge. If the read inputs to SRAM such as address arrive late, the SRAM would capture incorrect values at the positive edge of the clock and return the wrong data. Unlike with a level sensitive latch, this error will not automatically be corrected when

Figure 2.6: Wrapper logic is placed around the SRAM such that it can be treated as a positive latch.

given more time. Fortunately, due to the nature of the Bubble Razor algorithm, in all cases where the SRAM receives late inputs it will receive a bubble during the next cycle. Upon receiving this bubble, the SRAM uses the available cycle to repeat the read with the correct inputs that were captured by a bank of flip-flops on the negative clock edge. These approaches to handling SRAM can be automatically added to any system.

#### 2.4.3 Latch Clustering

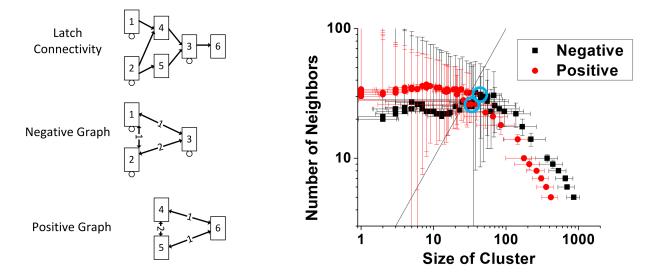

To reduce the logic area overhead of bubble propagation, latches that share neighbors were automatically grouped together into clusters. Latches in each cluster share a gated clock and combine their error signals into a common cluster error signal. A cluster then behaves as a single latch for the purpose of the Bubble Razor algorithm. It is possible for the designer to manually assign latches into clusters such as grouping together pipeline stages. Alternatively, we proposed an automated approach to assigning clusters. A positive and negative graph was extracted based on latch connectivity (Fig. 2.7). In each graph, the vertices represented the latches and the edge weights represented the number of paths through opposite polarity latches that connect the two vertices. Each latch was then assigned a cluster by inputting the graphs into a hypergraph partitioning tool [29].

Figure 2.7: Clustering was performed automatically by building two graphs based on latch connectivity. A tradeoff exists between the size of OR gates which is balanced by the choice of the number of clusters. The data shown is for a Cortex-M3 processor.

Although the assignment of clusters is performed automatically, the designer chooses the number of both positive and negative clusters. A tradeoff exists between the size of the OR gates needed to combine error signals within a cluster into a cluster error signal and the size of the OR gates needed to combine bubbles from neighboring clusters. With many clusters, the size of each cluster is small but each cluster has many neighbors. Alternatively, with few clusters each cluster has few neighbors but a large number of members.

### CHAPTER 3

# Eliminating Timing Margins in an ARM Cortex-M3 Processor with Bubble Razor

We implemented Bubble Razor on an ARM Cortex-M3 microprocessor in 45nm CMOS without detailed knowledge of its internal architecture to demonstrate the technique's automated capability. The flip-flop based design was converted to two-phase latch timing using commercial retiming tools; Bubble Razor was then inserted using automatic scripts. This system marks the first published implementation of a Razor-style scheme on a complete, commercial processor. It provides an energy efficiency improvement of 60% or a throughput gain of up to 100% compared to operating with worst case timing margins.

### 3.1 Retiming the Cortex-M3

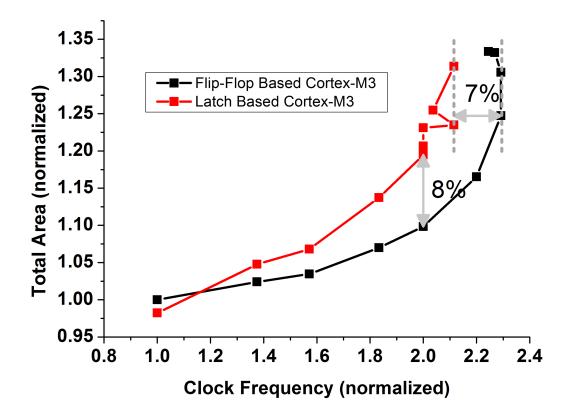

Retiming the M3 was achieved by holding the positive latches in place and moving negative latches. Under ideal circumstances, this retiming can be performed with no performance penalty without modifying the combinational logic. In practice, the additional area resulting from the changing number of latches causes a small performance penalty for the design. Fig. 3.1 shows the results of topographical synthesis performed at various timing constraints. As the synthesis and retiming software uses heuristic based optimizations on large datasets, it is possible for it to produce non-optimal outputs as well as non-monotonic results when sweeping a variable such as target clock period. This effect is more pronounced when the software is unable to meet the target clock period and is seen in the rightmost datapoints of Fig. 3.1. The maximum possible operating frequency for the latch-based M3 is 7% lower than the flip-flop based M3 due to this area increase. At a reasonable design point, the latch based M3 meets the same timing as the flip-flop based M3 but with an 8% area overhead. This operating point was chosen for further overhead analysis.

Figure 3.1: Transforming the Cortex-M3 to two-phase latches can incur an 8% area penalty or 7% performance penalty.

### 3.2 Speculation Window Selection for the Cortex-M3

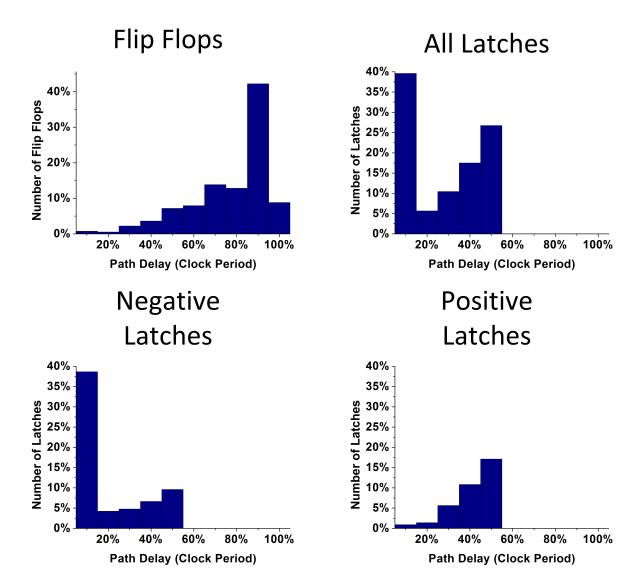

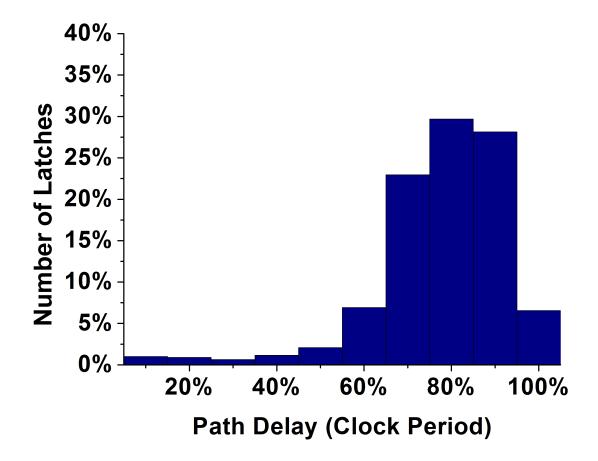

The selection of latches which require error detection can be determined by examining the critical paths at the input of each latch. Fig. 3.2 shows the distribution of critical path delays for flip-flops in the original design and latches in the retimed design. As a result of only moving negative latches, 64% of the latches in design are negative. In addition, many negative latches have very low critical path delays. These low delays result from flip-flops in the original design with critical paths below 50% of a clock period, where latches do not need to be moved to meet timing.

Figure 3.2: The Cortex-M3 has an imbalanced path distribution as a result of retiming.

We propose three different methods for selecting paths with error checking which make use of these timing characteristics: checking a subset of all latches, only positive latches, or only negative latches. When checking all latches, the maximum possible speculation window is 100%, while checking all positive or all negative latches would yield a speculation window of 50% since every other latch in a timing path has no error detection.

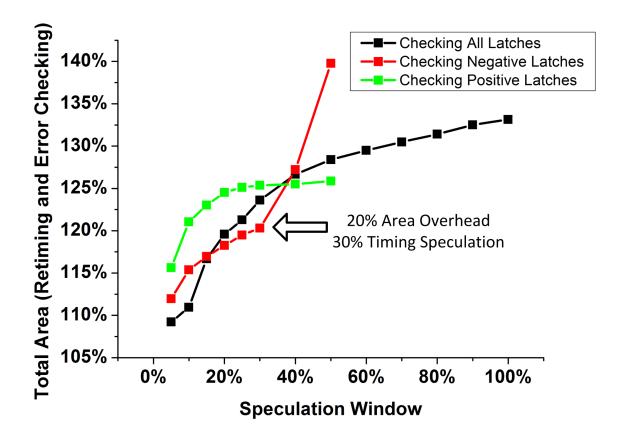

Fig. 3.3 shows the area overhead and speculation window results for these three tech-

Figure 3.3: Error checking can be added to a subset of latches, or a subset of only positive or only negative latches, yielding different area overheads. This is due to the distribution of critical path delays at the inputs of each latch.

niques when applied to the Cortex-M3. When only checking positive latches, since most latches are near critical, most of the area overhead is present with small speculation windows, but further pushing speculation window comes at low area cost. When only checking negative latches, area overhead drastically increases once the large number of latches with small critical paths require checking. Depending on the desired speculation window, either of the three techniques may be optimal. For a good design point, 30% speculation can be achieved with a retiming and error checking area overhead of 20%.

### 3.3 Implementation Circuitry

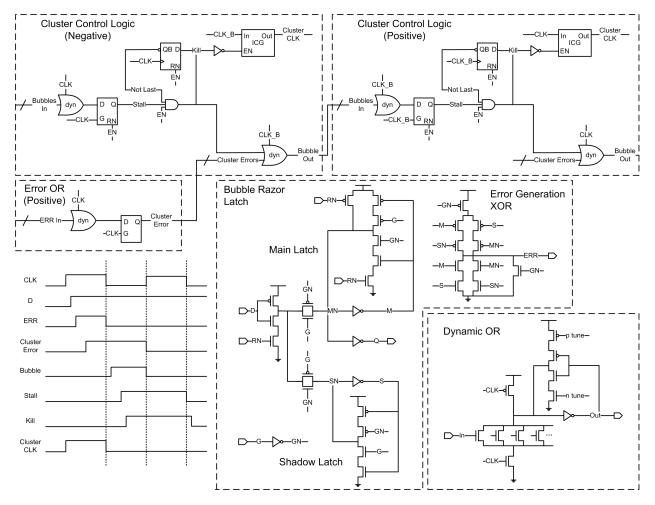

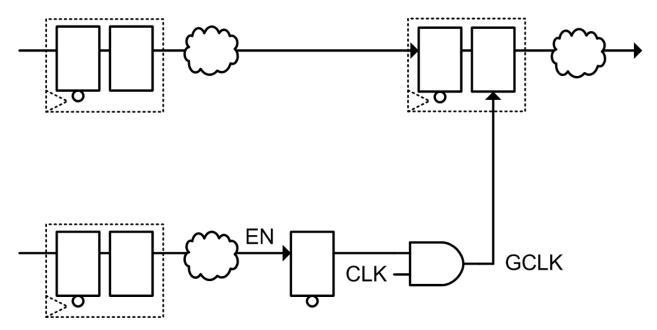

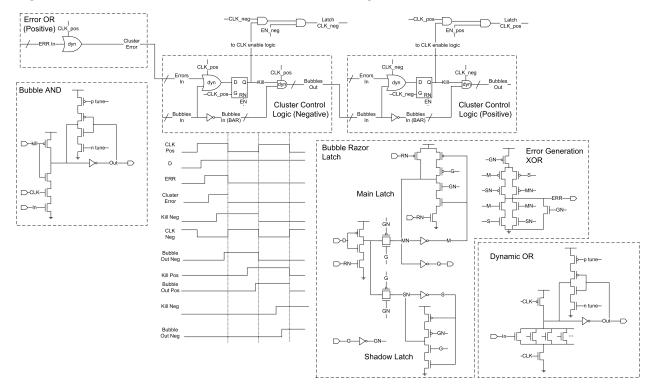

Error detection was performed using the Bubble Razor Latch, similar in design to the error detection flip-flop in [2]. A shadow latch captures data as the main datapath latch opens (Fig. 3.4). An XOR compares the two values and will flag an error if data arrives late and changes the value in the main latch. The Bubble Razor algorithm is not dependent on the type of error checking latch, and hence transition detectors based on [22] could also be used.

Figure 3.4: Bubbles are combined using dynamic OR gates. A cluster ignores bubbles if it stalled in the previous cycle.

Errors and bubbles are combined using wide dynamic OR gates, in our implementation made up of trees of 16 input dynamic ORs. Latches are used after trees of OR gates to hold the resulting values during the dynamic precharge phase. Clock gating and bubble propagation is handled by the Cluster Control Logic blocks. This logic is based on the alternate definition of the Bubble Razor algorithm: when sent a bubble by one or more neighbors: stall and send a bubble to all neighbors if and only if you did not stall in the previous cycle. By using this approach, latches do not need to store which neighbors they received bubbles from, drastically reducing implementation area. Additionally, it was noted that upon initiating the bubble propagation sequence after detecting a timing error, the first clock gating event is optional, so clock gating does not take place during the first bubble.

Although the design uses dynamic cells and latch-based timing, the models given to synthesis, placement, and routing software are fully static and edge-based. Since the dynamic ORs are always followed by more ORs or a latch, the ORs are modeled as static and the latch is modeled as a flip-flop. Latches in the datapath are modeled as flip-flops, since time borrowing during error-free operation is disallowed. The resulting design appears to the tool chain as a standard, flip-flop based design with clock gating, allowing fully automated, standard integration with no designer intervention.

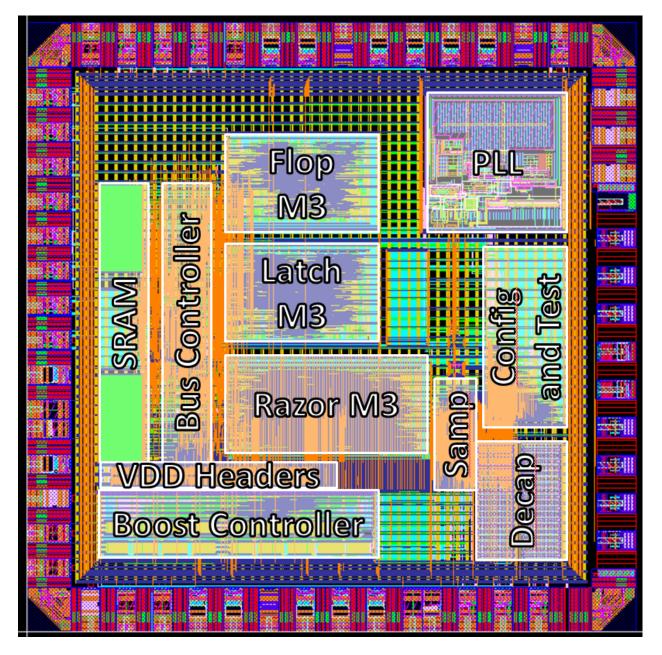

### 3.4 Silicon Test Chip

Bubble Razor was applied to the Cortex-M3 processor, a 1.25 DMIPS/MHz microcontroller [30], and implemented in a 45nm SOI process. This silicon test chip is the first published Razor-style implementation to demonstrate a transformed commercial processor operating correctly under the presence of timing errors. Several robust design decisions were made resulting in large area overheads for the silicon test chip. Timing error checking was added to all latches, even those which are not capable of failing timing, in order to allow us to find the maximum possible speculation window: one clock phase minus the propagation delay of the error detection circuits, which provides 55% timing speculation in this implementation. All latches in the design had an asynchronous reset although it is only strictly required for either all positive or all negative latches. Robust short path constraints were also put in place, and were met through buffer insertion.

These design decisions, when combined with retiming overhead, resulted in an artificially

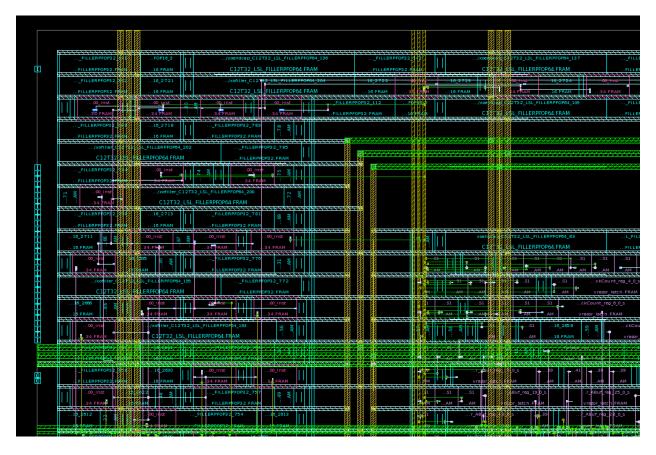

large cell area overhead of 87% for the latch based M3 compared to the original flip-flop based M3. This comprised a 21% increase in combinational logic area and a 280% increase in sequential area. The additional cluster control logic added 16% area compared to the original flip-flop design, resulting in a total area overhead over the flip-flop design of 103%. The number of gates increased from 32,805 to 36,206 when transforming to Bubble Razor, with the majority of the new cells comprising new latches as each flip-flop became an average of 3 latches after retiming. Estimated clock loading increased by 230% with 88% of the loading coming from the Razor latches and the remainder coming from flip-flops in the JTAG test harness, latches in cluster control logic, and dynamic OR gates. Reducing the number of latches with error detection would drastically reduce the increase in sequential area, additional cluster control area, total area, and clock loading.

Synthesis results since the silicon implementation are shown in Section and , which meet short path constraints with nonoverlapping clocks, only resets positive latches, and only uses Razor latches in timing critical locations. It is shown that error detection with a 30% speculation window can be achieved with 20% area overhead, which increases to approximately 25% when the additional cluster control logic is added. This area increase is for the core logic only and reduces when amortized over cache area.

### 3.5 Silicon Measurement Results

Because of the robust design decisions mentioned in Section , a silicon comparison was not made between a conventional M3 and the test chip, so the silicon test chip compares against itself operating at worst case margins when calculating performance increases and energy savings. Synthesis results show the implemented test chip can operate at the same frequency as a conventional flip-flop based Cortex-M3 when designed to the same timing constrain, however the addition of Bubble Razor will come at a cost of area and power which is highly dependent on the desired speculation window as discussed in Sections , and . Additionally, if DFT is added to a design it will come at a higher cost for the latch based Bubble Razor implementation as the scan chain will contain twice as many elements. These costs must be taken into account when calculating the energy savings from using Bubble Razor.

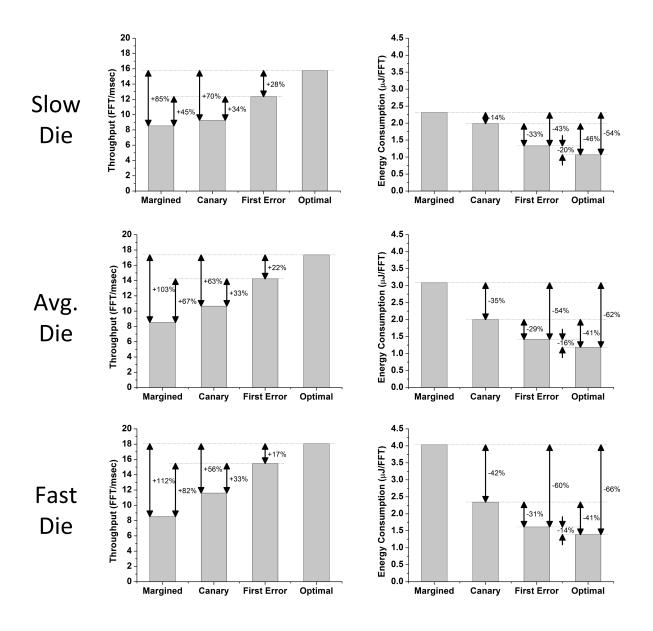

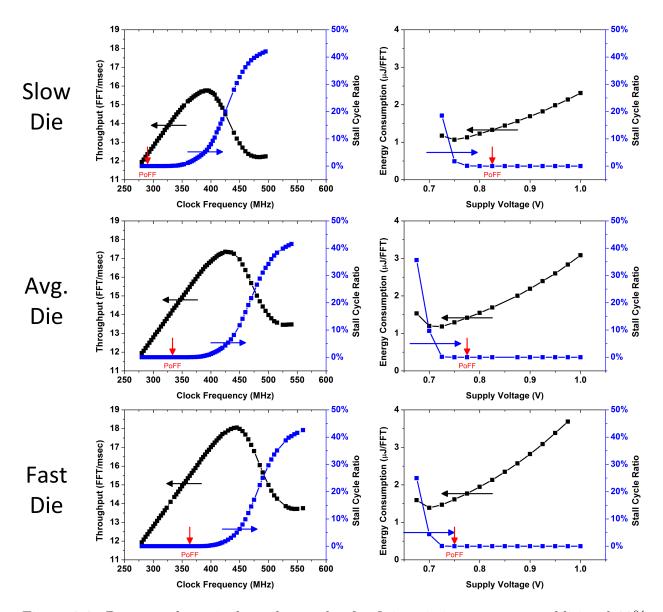

The silicon test chip was programmed to perform software FFT computations. At 85°C with 10% supply drop,  $2\sigma$  process variation, and 5% safety margin, the maximum operating frequency of the M3 design is measured as 200 MHz, setting a frequency ceiling for a conventional margined design. With Bubble Razor the design can be tuned to the point of first failure (PoFF) which was 290/333/363 MHz for three shown chips, increasing throughput by 45, 67, and 82% (Fig. 3.5). Alternatively, supply voltage can be lowered at iso-performance, reducing M3 energy consumption by 43, 54, and 60%, respectively.

Fig. 3.6 shows system behavior when sweeping frequency or voltage beyond the PoFF. As clock frequency linearly increases, throughput initially linearly increases. As timing errors become more prevalent at higher frequencies, throughput improvement slows down and eventually reverses due to stall cycles consuming a large portion of processor runtime. Similarly, voltage scaling reduces energy consumption until timing errors become too common. When running at a voltage substantially lower than the PoFF, the large number of stall cycles cause the program to take longer to execute which increases total energy consumption. If frequency or voltage is scaled too far, the system will begin operating outside of its speculation window, timing errors will not be properly corrected for, and the system will fail. All points in Fig. 3.6. represent the system executing its program correctly with the rightmost throughput and leftmost energy points representing limits of frequency and voltage scaling. Overall, an additional 22% performance or 17% energy reduction is obtained from running beyond the PoFF. This is significantly better than previous Razor approaches since only a single cycle is lost per corrected error, allowing beneficial operation at relatively high error rates. The combination of eliminating margins and running beyond the PoFF allows for a 100% throughput increase or 60% energy reduction when compared to operating with worst case timing margins.

We used ring oscillators on each chip as canary circuits to provide for a comparison of energy/performance gains from canary circuits and with Bubble Razor. Canary circuits allow some timing margins to be reduced, but cannot eliminate all margins as there may be mismatch between the canary and datapath. In addition, canary circuits can only adapt to slow changing operating conditions due to the time required to change the processor

Figure 3.5: By running the system under nominal conditions instead of with worst case margins, performance or energy can be improved.

Figure 3.6: Due to only a single cycle penalty for fixing timing errors, an additional 22% performance gain or 17% energy reduction can be made by running beyond the Point of First Failure.

clock frequency, and thus canary circuits cannot eliminate the margins for supply droop. Adding margin for  $3\sigma$  of mismatch between the canary frequency and processor frequency, a margin for 10% supply droop, and an additional 5% safety margin, the design can be tuned to 217/250/272 MHz for the three shown chips. Running with Bubble Razor at the optimal throughput point provides gains of 70%, 63%, and 56% respectively when compared to running with canary circuits. Equivalently, Bubble Razor at the optimum energy point provides gains of 46%, 41%, and 41% over canary circuits.

### 3.6 Conclusion

A novel Razor style technique was proposed that breaks the link between speculation window and minimum delay constraints, allowing large speculation windows. In addition, a local stalling technique was proposed that is independent of design architecture and scalable to designs of arbitrary size. Bubble Razor was successfully applied to the ARM Cortex-M3 microprocessor, the first Razor style implementation of a complete commercial processor. A test chip was fabricated in 45nm CMOS to validate the technique and showed a 100% throughput improvement or 60% energy savings over running with worst-case timing margins.

| Processor Core        | ARM<br>Cortex-M3    |  |

|-----------------------|---------------------|--|

| Process<br>Technology | IBM 45nm<br>SOI12S0 |  |

| Nominal VDD           | 1.0 V               |  |

| SRAM Size             | 16 kB               |  |

| Latches               | 7159                |  |

| Positive<br>Clusters  | 70                  |  |

| Negative<br>Clusters  | 100                 |  |

| Speculation<br>Window | 55%                 |  |

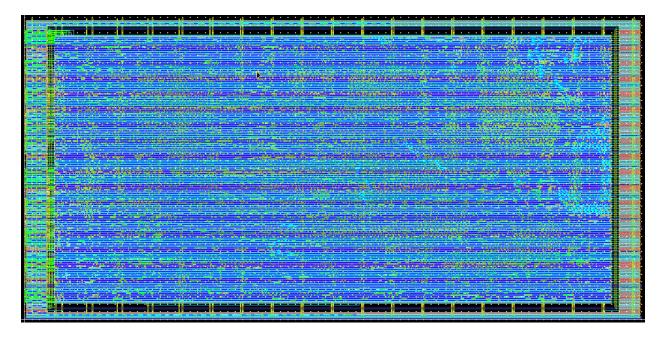

Figure 3.7: Die photo and system information.

## CHAPTER 4

# Voltage Razor: Using Supply Voltage Boosting as Error Correction

Similar to Bubble Razor, Voltage Razor uses a 2-phase edge-based latch clocking with transition detectors at latch inputs. The unique feature of Voltage Razor is that, upon detection of an error, the effective time available for each pipeline stage computation is increased by making logic faster, rather than stretching the cycle time. When a latch is transparent and detects a transition, an error is detected, and the supply voltage is quickly boosted to speed subsequent logic, allowing for the compensation of the late arriving input. Many prior Razor techniques have employed voltage regulation to keep average error rate within bounds, but this is always performed with a slow feedback loop that cannot correct incoming errors at run time. In Voltage Razor, we propose new circuit techniques to enable voltage boosting times that are comparable to the clock cycle time.

## 4.1 Principle and Motivation

As with Bubble Razor, in Voltage Razor the integrity of the state is preserved by the same latches within pipeline stages, as long as the error is corrected quickly enough to avoid state corruption. When a latch observes its input switching during its transparent phase, it flags an error. The failing latch still holds the correct data but is now effectively borrowing time from the next logic stage. Unless the error is corrected, this time borrowing can increase with each stage and will eventually cause a failure when the maximum amount of time borrowing is exceeded. In Voltage Razor, we avoid this failure by boosting the supply from the value  $VDD_L$  in normal operation to the boosted voltage  $VDD_H$ , which speeds up the logic of subsequent stages. If the voltage is boosted sufficiently fast, the time borrowing will be negated before its limit is reached and the circuit will return to normal operation where all max-delay constraints are met and no error is flagged. The supply voltage is then returned to  $VDD_L$ .

The key challenge in Voltage Razor is to boost the supply sufficiently fast (within a few clock cycles). This goal can be feasibly pursued if the amount of boosting is limited and the cycle time is not too short. Both conditions can be met when the core operates at near threshold (e.g.,  $VDD_L$  400-700 mV), since:

- At near threshold, gate delay is rather sensitive to VDD. For example, in 45nm SOI IBM technology, boosting the voltage from  $VDD_L = 500 \text{ mV}$  to  $VDD_H = 650 \text{ mV}$  leads to a significant gate delay (fanout-of-four, or FO4) reduction by 2.5.

- When  $VDD_L$  is close to the threshold, operating frequencies are typically much lower than the conventional low-GHz regime. Given these larger cycle times, it becomes much easier to boost the voltage in 1-2 clock cycles. For example, FO4 at  $VDD_L =$ 500 mV is 4.6 greater than at VDD = 1 V.

The large speculation time that is enabled by Voltage Razor permits detection of the large variations that are observed near threshold, which are greater by almost one order of magnitude than at nominal voltage (at 45nm, process variations require a 0.7 margin at VDD = 1 V, which becomes 5.8 at 500 mV). Hence, near threshold is the natural operating range for Voltage Razor.

Within the speculation window, Voltage Razor can correct errors without introducing any stalling. This gives Voltage Razor two very unique properties:

- It corrects errors with no performance penalty, as opposed to previous techniques that require several or tens of cycles to recover from errors.

- External behavior is not affected by error detection. Hence, no modification of the

interfaces with surrounding blocks is required, dramatically simplifying system integration.

Also, Voltage Razor is able to correct fully correlated errors, e.g., the occasional delay increase in adjacent pipeline stages due to a common voltage droop lasting multiple cycles. In this case, voltage boosting is activated by the first stage violating its timing constraint, and also compensates the delay increase of the second stage. The same consideration holds for multiple errors occurring in the same stage and adjacent cycles.

From a design point of view, the introduction of Voltage Razor into a microprocessor does not interfere with the cycle timing of the original circuit, as the latch error signals and the supply are orthogonal to the paths where data flows.

## 4.2 Error Correction Through Voltage Boosting

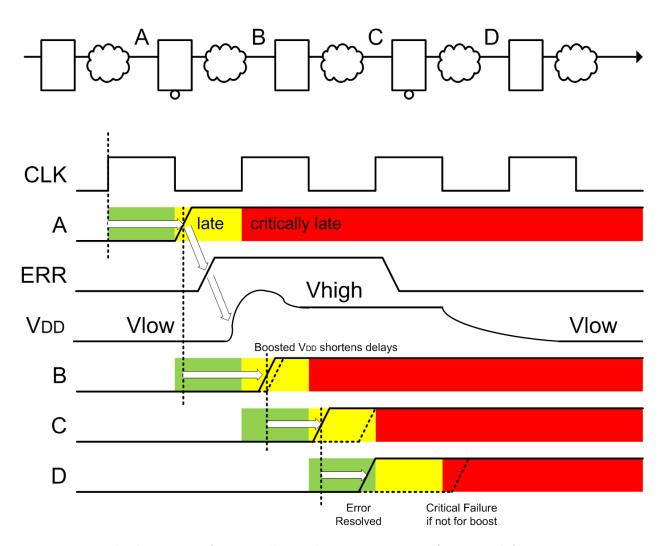

Figure 4.1 shows how timing errors are corrected in a Voltage Razor system. The green, yellow, and red regions signify where transitions are on time, late and borrowing time, and critically late past the point of correction respectively.

Data arrives at point A slightly after the negative edge of CLK and begins to borrow time from the next stage. This late transition is flagged as an error which starts the boosting process. VDD transitions from Vlow to Vhigh as a result of the flagged error. As this is happening, data continues to flow through the pipeline, initially borrowing more time when reaching point B. However as delays decrease due to the higher supply voltage, the time borrowed when reaching point C is less and the error has been completely corrected by the time data reaches point D. Alternatively, had the boost not occurred, data would transition as shown in the dashed lines, continually borrowing more time. By the time the data reached point D, so much time would have been borrowed that data would have arrived critically late and caused a system failure.

Figure 4.2 shows simulation results of a voltage boosting correction. The top half of the plot shows the system clock while the bottom half shows the arrival of data values at latch inputs. Once a violation is detected in cycle 2, the boosting process begins. Voltage rapidly rises and overshoots the desired value for some time before ringing and eventually settling

Figure 4.1: The boosting of VDD allows the circuit to run faster and for timing errors to recover

on Vhigh. Despite the fact that VDD has not yet settled on its final value, it remains higher than Vlow and thus decreases circuit delay allowing for the timing violation to be corrected.

Although in conventional systems, ringing and instability on VDD are considered extremely negative effects, in Voltage Razor, the initial overshoot of VDD while boosting is beneficial. This overshoot results in the lowest values for circuit delays and rapidly assists in recovery at a time when it is most needed.

Figure 4.2: Boosting of VDD allows for the correction of the timing error even before VDD has stabilized and stopped ringing

### 4.3 28nm Test Chip Overview

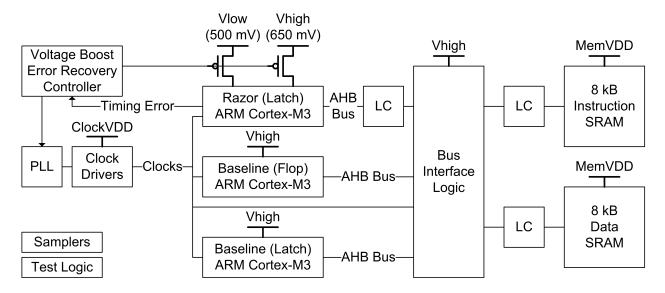

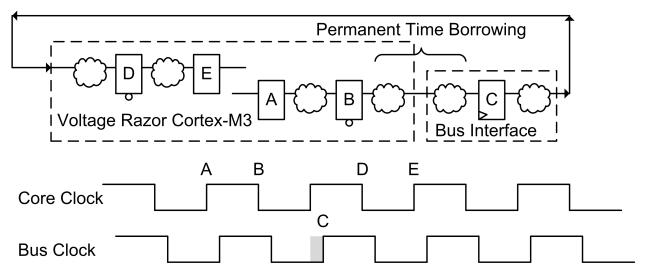

Voltage Razor was implemented on an ARM Cortex-M3 and a test chip was implemented in a 28nm process. Figure 4.3 shows a block diagram of the system. Three ARM Cortex-M3 processors are included, a baseline flip-flop based core, a baseline two-phase latch based core, and the Voltage Razor core. Since there is no error detection on the baseline cores or bus interface logic, they are always powered by Vhigh. Level converters exist to boost bus signals from the Razor core to bus logic, as well as from the bus logic to the SRAM blocks.

Two sets of headers can be independently controlled to connect the supply of the Razor core to either Vlow or Vhigh. The Razor core outputs a signal to the voltage boosting error

Figure 4.3: Block diagram of Voltage Razor test chip

recovery controller signifying that a timing error has occurred and requesting a boost in supply voltage. This error recovery controller contains several highly configurable timers which can control the exact sequence in which the supply is raised and lowered.

A PLL creates a master clock which is used to derive all the various clocks in the system which are computed and driven by logic running at ClockVDD. The boost controller also can control whether the PLL is in slow or fast mode and rapidly change the clock frequency in a glitch-free manner if needed. Samplers and test logic are present to control the system's various testing controls and sample voltage and clock waveforms.

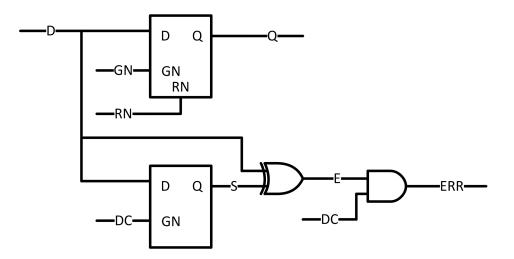

### 4.4 Error Detection Latch

As full view layouts of standard cells were not available, the error detection latch was comprised of several standard cell gates as shown in Figure 4.4. The timing of this latch is shown in Figure 4.5.

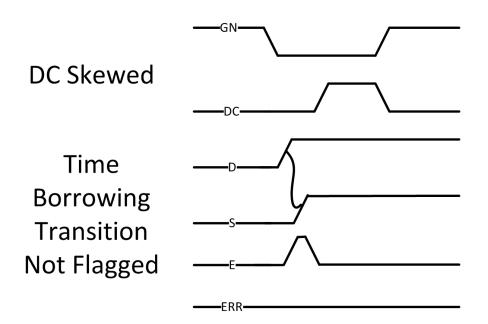

Unlike with Bubble Razor, the shadow latch uses a separate detection clock DC than the datapath latch. This allows for the error detection window to be adjusted such that some amount of time borrowing is allowed without flagging errors as shown in Figure 4.6. Alternatively, DC could be shifted earlier in time such that a boost is triggered earlier, even

Figure 4.4: Standard cells comprising error detection latch

before time borrowing actually occurs.

As this error detection latch is made of standard cells, it is non-optimal in terms of area usage. Were full view layouts available, the cell could have been more aggressively optimized.

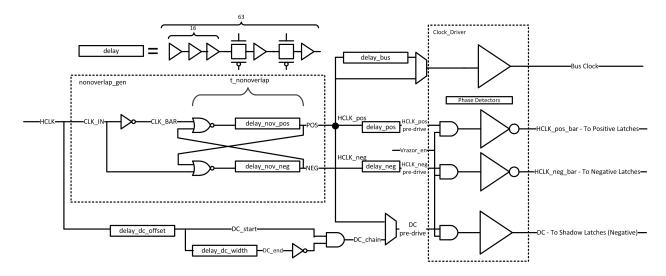

Error signals are combined using a tree of 16 input dynamic OR gates into a single signal representing whether any latch in the core has experienced a timing error. This signal is sent to the timers in the configurable boosting controller.