# **Energy-Efficient Decoders of Near-Capacity Channel Codes**

by

Youn Sung Park

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2014

Doctoral Committee:

Assistant Professor Zhengya Zhang, Chair Professor David Blaauw Assistant Professor Jianping Fu Professor Trevor Mudge © Youn Sung Park 2014

All Rights Reserved

To my loving family

### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor Professor Zhengya Zhang for his support and guidance. It has been an honor to be his first Ph.D. student. His tremendous effort, valuable ideas, and warm encouragement helped me make my Ph.D. experience productive and stimulating. I would like to thank Professor David Blaauw and Dennis Sylvester for the insightful discussions and ideas. I would also like to thank Professor Trevor Mudge and Jianping Fu for participating in my dissertation committee and evaluating my research proposal and reviewing this dissertation.

My research was supported by NSF under grant CCF-1054270, DARPA under cooperative agreement HR0011-13-2-0006, NASA, Intel, Broadcom Foundation, and the University of Michigan. The chip fabrication donation was provided by ST Microelectronics. Dr. Pascal Urard at ST Microelectronics, Dr. Engling Yeo at Marvell Semiconductor, and Dr. Andrew Blanksby at Broadcom offered valuable feedback in reviewing my chip designs.

I consider myself very fortunate to be able to work with very talented individuals here at the University of Michigan. I will never forget the enjoyable memories that are shared with Jungkuk Kim, Dongsuk Jeon, Yaoyu Tao, Yoonmyung Lee, Inhee Lee, Chia-Hsiang Chen, Phil Knag, Shuanghong Sun, Wei Tang, Thomas Chen, Shiming Song, Gyouho Kim, Dongmin Yoon, Yejoong Kim, Suho Lee, Suyoung Bang, Sechang Oh, Jaeyoung Kim, Seok-Hyeon Jeong, Taehoon Kang, Hyunsoo Kim, Inyong Kwon, Jaehun Jeong, Zhiyoong Foo, Donghwan Kim, and Myungjoon Choi.

Last but not least, I thank my parents in Korea as well as my wife Yeori Choi and daughter Ji Yu Park, for their endless support and trust. I dedicate this work to them for their love and support.

## TABLE OF CONTENTS

| DEDICATION  | <b>v</b>                                                                                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLE    | DGEMENTS iii                                                                                                                                              |

| LIST OF FIG | URES vi                                                                                                                                                   |

| LIST OF TAB | BLES x                                                                                                                                                    |

| ABSTRACT    | xi                                                                                                                                                        |

| CHAPTER     |                                                                                                                                                           |

| I. Introd   | luction                                                                                                                                                   |

| 1.1         | Near-Capacity Channel Codes                                                                                                                               |

|             | 1.1.1 Low-Density Parity-Check Codes                                                                                                                      |

|             | 1.1.2 Nonbinary Low-Density Parity-Check Codes                                                                                                            |

|             | 1.1.3 Polar Codes                                                                                                                                         |

| 1.2         | Scope of this Work $\ldots \ldots \ldots$ |

|             | 1.2.1 Low-Density Parity-Check Codes                                                                                                                      |

|             | 1.2.2 Nonbinary Low-Density Parity-Check Codes                                                                                                            |

|             | 1.2.3 Polar Codes $\ldots$ 13                                                                                                                             |

| II. LDPC    | <b>Decoder with Embedded DRAM</b>                                                                                                                         |

| 2.1         | Decoding Algorithm                                                                                                                                        |

| 2.2         | Decoder Architecture $\dots \dots \dots$                  |

|             | 2.2.1 Pipelining and Throughput 19                                                                                                                        |

| 2.3         | Throughput Enhancement                                                                                                                                    |

|             | 2.3.1 Row Merging                                                                                                                                         |

|             | 2.3.2 Dual-Frame Processing                                                                                                                               |

| 2.4         | Low-Power Memory Design                                                                                                                                   |

|             | 2.4.1 Memory Access Pattern                                                                                                                               |

|             | 2.4.2 Non-Refresh Embedded DRAM                                                                                                                           |

|             | 2.4.3 Coupling Noise Mitigation                                                                                                                           |

|             | 2.4.4 Retention Time Enhancement                                                                                                                          |

| 2.5         | Efficient Memory Integration                                                                                                                              |

|             | 2.5.1 Sequential Address Generation                                                                                                                       |

|            | 2.5.2 Simulation Results                                  |

|------------|-----------------------------------------------------------|

| 2.6        | Decoder Chip Implementation and Measurements              |

|            | 2.6.1 Chip Measurements                                   |

|            | 2.6.2 Comparison with State-of-the-Art                    |

| 2.7        | Summary                                                   |

| III. Nonb  | inary LDPC Decoder with Dynamic Clock Gating              |

| 3.1        | Decoding Algorithm                                        |

|            | 3.1.1 VN Initialization                                   |

|            | 3.1.2 CN Operation $\ldots$                               |

|            | 3.1.3 VN Operation $\ldots$                               |

| 3.2        | High-Throughput Fully Parallel Decoder Architecture       |

|            | 3.2.1 Look-Ahead Elementary Check Node                    |

|            | 3.2.2 Two-Pass Variable Node                              |

|            | 3.2.3 Interleaving Check Node and Variable Node           |

| 3.3        | Low-Power Design by Fine-Grained Dynamic Clock Gating     |

|            | 3.3.1 Node-Level Convergence Detection                    |

|            | 3.3.2 Fine-Grained Dynamic Clock Gating                   |

| 3.4        | Decoder Chip Implementation and Measurement Results       |

|            | 3.4.1 Chip Measurements                                   |

| ~ ~        | 3.4.2 Comparison with State-of-the-Art                    |

| 3.5        | Summary                                                   |

| IV. Belief | f-Propagation Polar Decoder                               |

| 4.1        | Decoding Algorithm                                        |

|            | 4.1.1 Successive Cancellation Decoding                    |

|            | 4.1.2 Belief Propagation Decoding                         |

| 4.2        | Decoder Architecture                                      |

| 4.3        | High-Throughput Double-Column Unidirectional Architecture |

|            | 4.3.1 Unidirectional Processing Architecture              |

|            | 4.3.2 Double-Column Architecture                          |

| 4.4        | High-Density Bit-Splitting Register File                  |

| 4.5        | Decoder Chip Implementation and Measurement Results       |

|            | 4.5.1 Chip Measurements                                   |

|            | 4.5.2 Comparison with State-of-the-Art                    |

| 4.6        | Summary                                                   |

| 4.7        | Future Research Directions                                |

|            | 4.7.1 Polar Code Design                                   |

|            | 4.7.2 Reconfigurable BP Polar Decoder                     |

| V. Concl   | lusion                                                    |

|            |                                                           |

|            |                                                           |

| LIOGRA     | PHY                                                       |

## LIST OF FIGURES

# Figure

| 1.1 | Bit error rate comparison between uncoded and encoded systems                                                                                                                                                                                                                                                | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | An example H matrix and factor graph representation of an LDPC code $% \mathcal{A}$ .                                                                                                                                                                                                                        | 3  |

| 1.3 | BER (solid-line) and FER (dashed-line) of rate- $1/2$ LDPC codes used in wireless communication standards $[1, 2, 3]$                                                                                                                                                                                        | 4  |

| 1.4 | Comparison of binary LDPC and nonbinary LDPC (NB-LDPC) code. $\ . \ .$                                                                                                                                                                                                                                       | 6  |

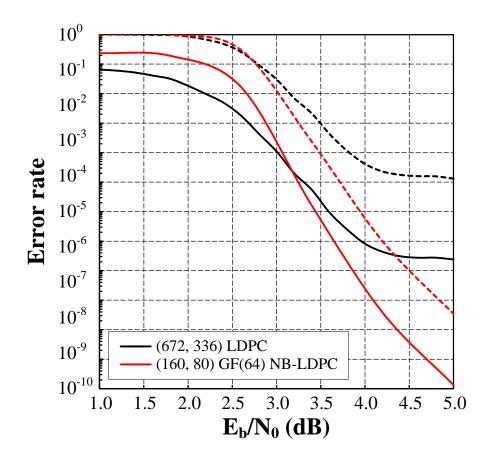

| 1.5 | BER (solid-line) and FER (dashed-line) comparison of LDPC and NB-LDPC.                                                                                                                                                                                                                                       | 7  |

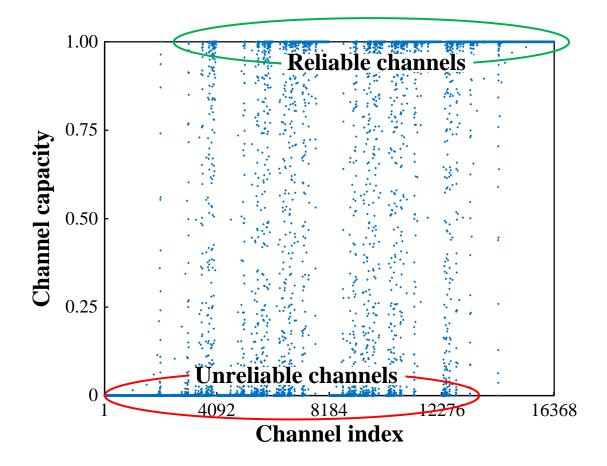

| 1.6 | Example of polarization effect on $N = 2^{14}$ for a BEC channel with $\epsilon = 0.5$ .                                                                                                                                                                                                                     | 9  |

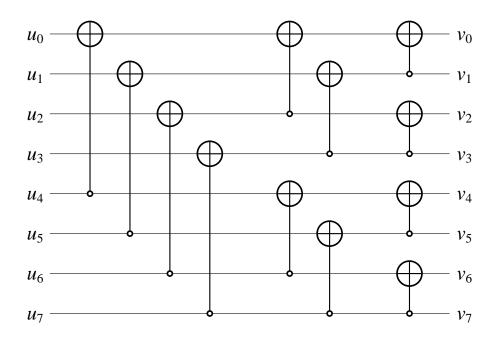

| 1.7 | Polar code encoder example for $N = 8. \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                            | 9  |

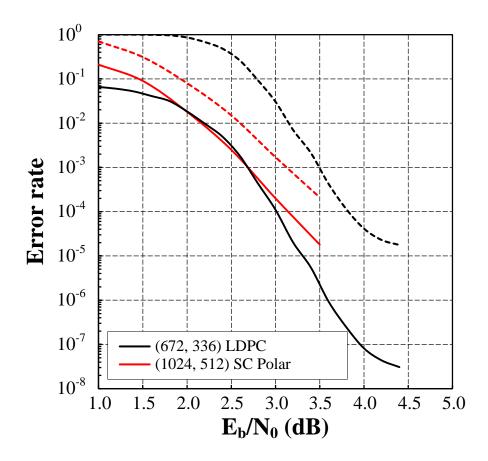

| 1.8 | BER (solid-line) and FER (dashed-line) comparison of LDPC and polar codes under successive cancellation decoding.                                                                                                                                                                                            | 11 |

| 2.1 | H matrices of the rate-1/2, rate-5/8, rate-3/4 and rate-13/16 LDPC code for the IEEE 802.11ad standard [1]                                                                                                                                                                                                   | 16 |

| 2.2 | Illustration of LDPC decoder architectures. The shaded part represents the section of the H matrix that is processed simultaneously                                                                                                                                                                          | 18 |

| 2.3 | (a) Variable node, and (b) check node design (an XOR gate is incorporated<br>in the sort and compare-select logic of the CN to perform the parity check.)                                                                                                                                                    | 20 |

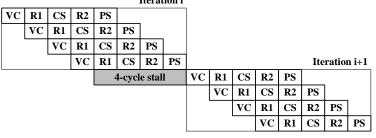

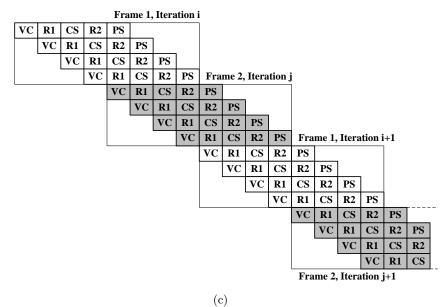

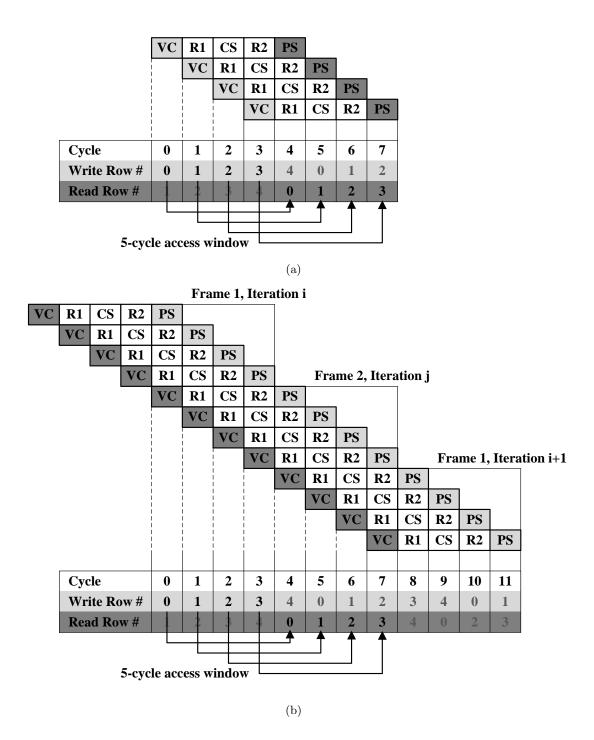

| 2.4 | Pipeline schedule of (a) a conventional single-frame decoder without row merging, (b) a conventional single-frame decoder with row merging, and (c) proposed dual-frame decoder with row merging. Note that (a) and (b) require stalls in-between frames due to data dependency between the PS and VC stages | 21 |

| 2.5  | (a) Illustration of row merging applied to the H matrix of the rate-1/2 LDPC code for IEEE 802.11ad. The merged matrix has only 4 rows, short-ening the decoding iteration latency; and (b) modified check node design to support row merging.                                       | 24 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

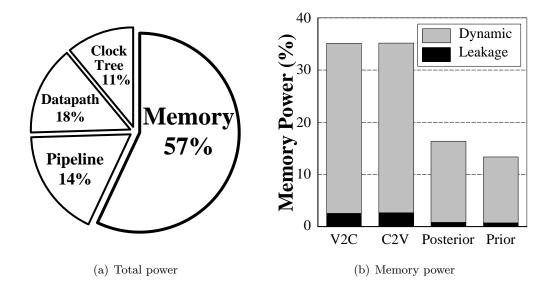

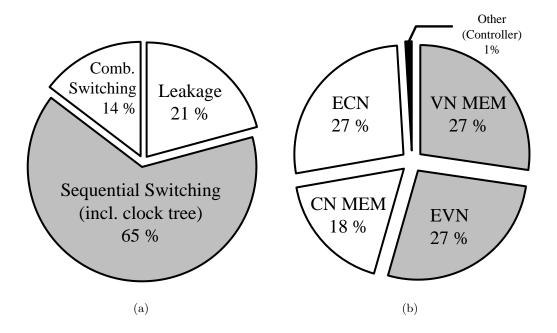

| 2.6  | (a) Power breakdown of a 65 nm synthesized 200 MHz row-parallel register-<br>based LDPC decoder for the IEEE 802.11ad standard, and (b) memory<br>power breakdown. Results are based on post-layout simulation                                                                       | 26 |

| 2.7  | (a) V2C memory access pattern, and (b) C2V memory access pattern                                                                                                                                                                                                                     | 28 |

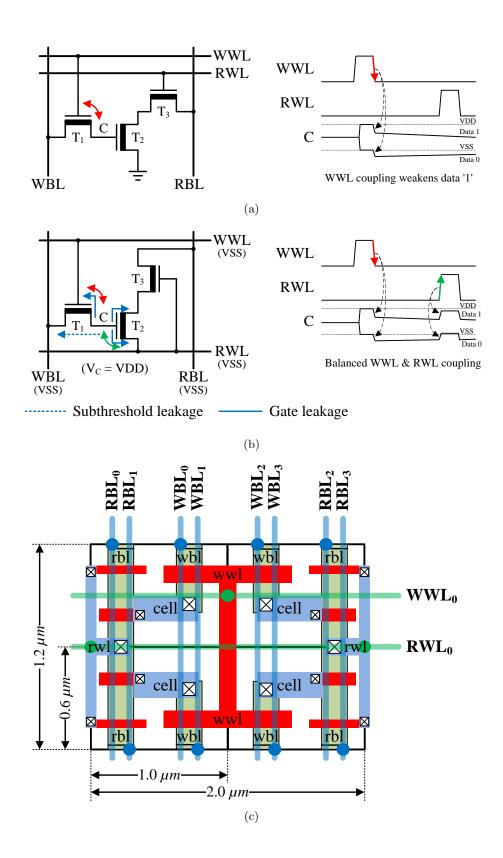

| 2.8  | Schematic and capacitive coupling illustration of the (a) classic 3T cell [4], and (b) proposed 3T cell and (c) its 4-cell macro layout.                                                                                                                                             | 30 |

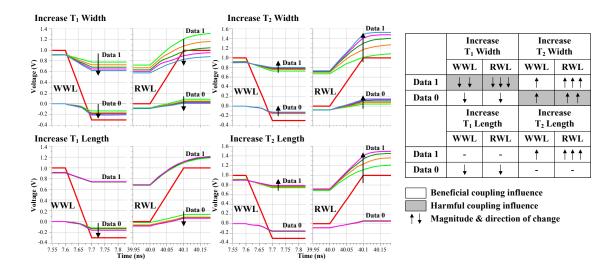

| 2.9  | Effects of transistor sizing on WWL and RWL coupling noise. Only the falling transition of WWL and the rising transition of RWL are shown as they determine the cell voltage after write and before read.                                                                            | 31 |

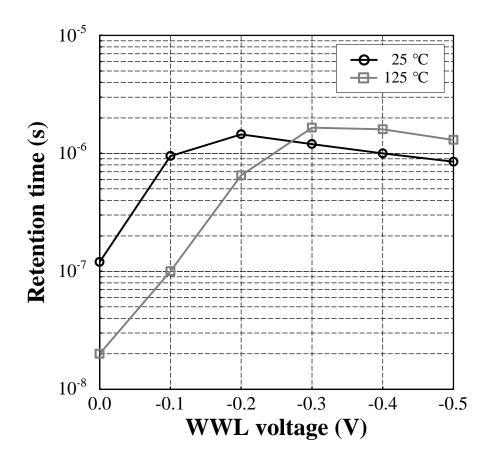

| 2.10 | Cell retention time with negative WWL voltage.                                                                                                                                                                                                                                       | 32 |

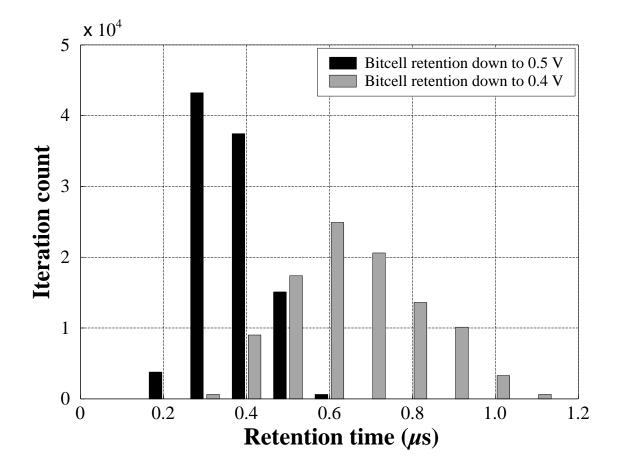

| 2.11 | 100k Monte-Carlo simulation results of cell retention time at 125°C. The simulation was done on post-layout extracted netlist at 1.0V supply voltage with -300mV WWL. The retention time is measured as the time for the cell voltage to drop to 0.5V (in black) and 0.4V (in grey). | 34 |

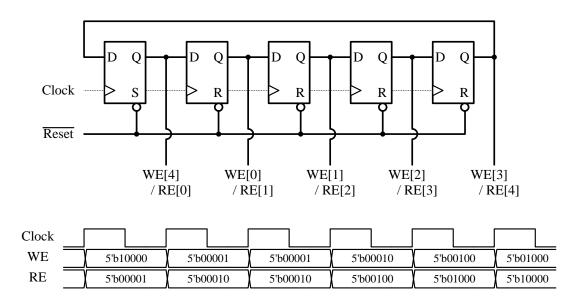

| 2.12 | Schematic and waveform of sequential address generation based on 5-stage circular shift register                                                                                                                                                                                     | 36 |

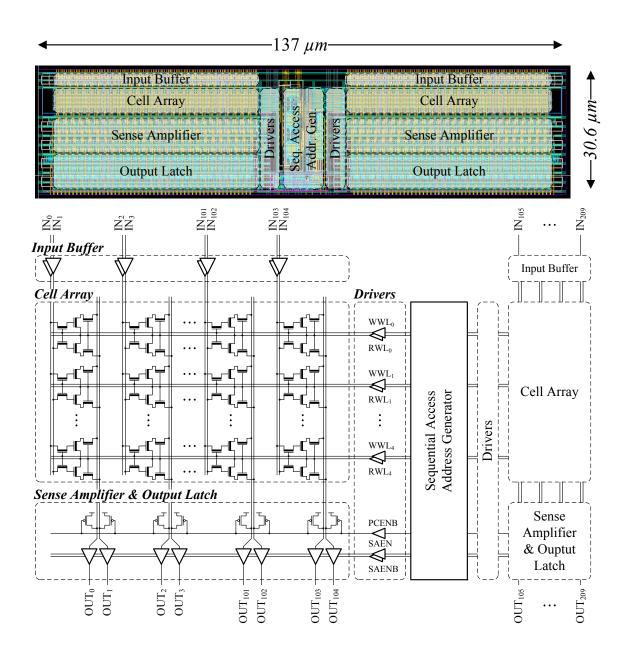

| 2.13 | Layout and schematic illustration of a $5 \times 210$ eDRAM array including cell array and peripherals.                                                                                                                                                                              | 37 |

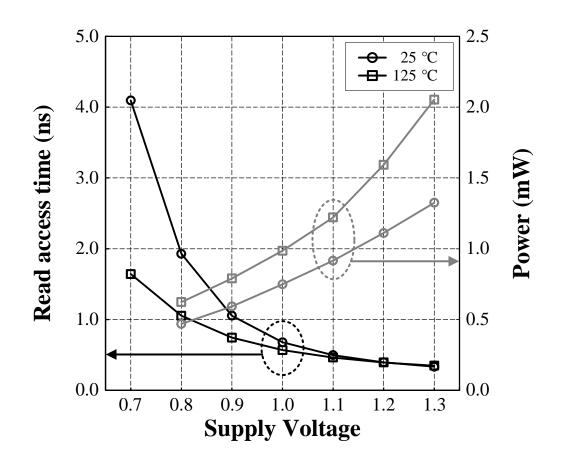

| 2.14 | Simulated read access time (in black) and power consumption (in grey) of<br>the eDRAM array at 25°C and 125°C. Results are based on post-layout<br>simulation using a -300mV WWL and power is measured at a 180 MHz<br>clock frequency.                                              | 38 |

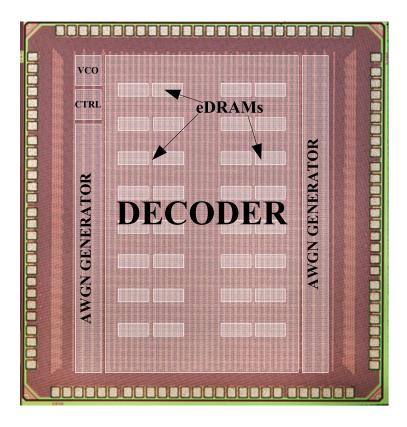

| 2.15 | Chip microphotograph of the decoder test chip. Locations of the 32 eDRAM arrays inside the LDPC decoder and the testing peripherals are labeled. $\ .$                                                                                                                               | 39 |

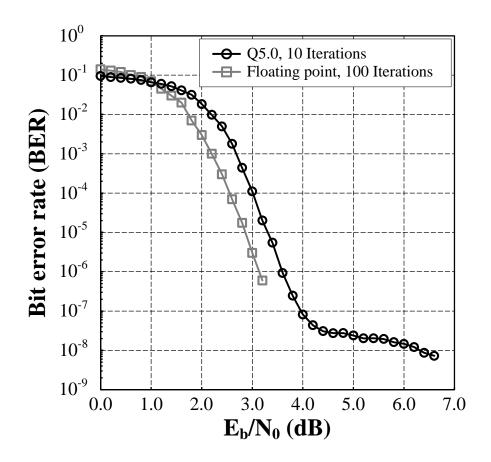

| 2.16 | BER performance of the (672, 336) LDPC code for the IEEE 802.11ad standard using a 5-bit quantization with 10 decoding iterations and floating point with 100 iterations.                                                                                                            | 40 |

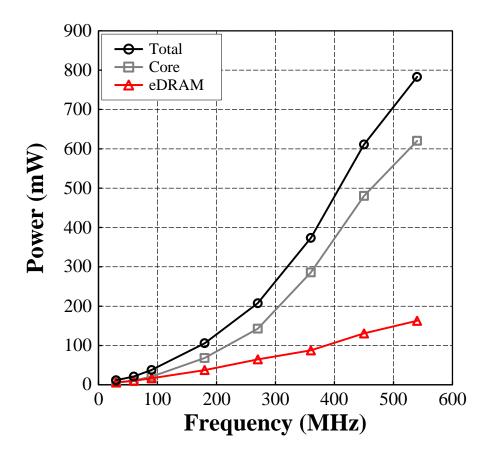

| 2.17 | Measured LDPC decoder power at 5.0 dB SNR and 10 decoding iterations.<br>The total power is divided into core and eDRAM power. Voltage scaling is<br>used for the optimal core and eDRAM power                                                                                       | 42 |

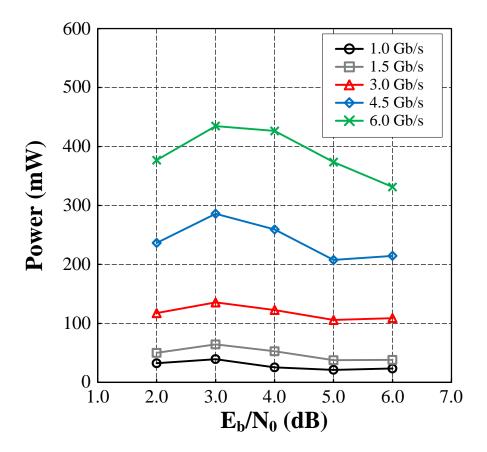

| 2.18 | Measured LDPC decoder power across SNR range of interest at 10 decoding iterations. Voltage scaling is used for optimal core and eDRAM power                                                                                                           | 43 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

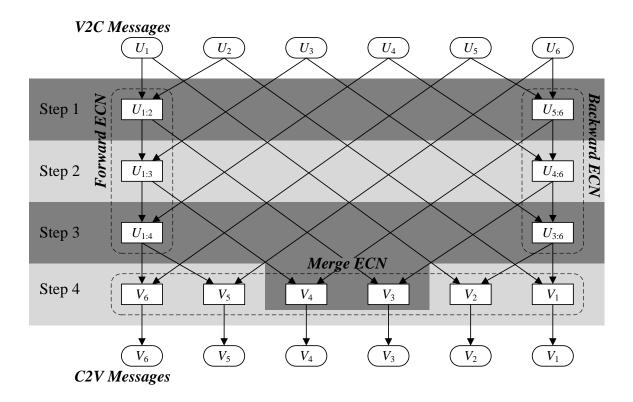

| 3.1  | Illustration of forward-backward algorithm with $d_c = 6. \ldots \ldots \ldots$                                                                                                                                                                        | 49 |

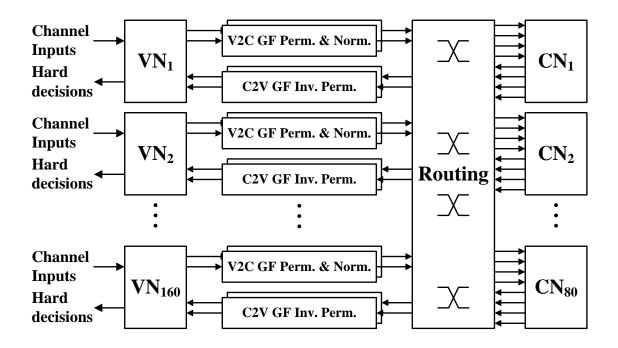

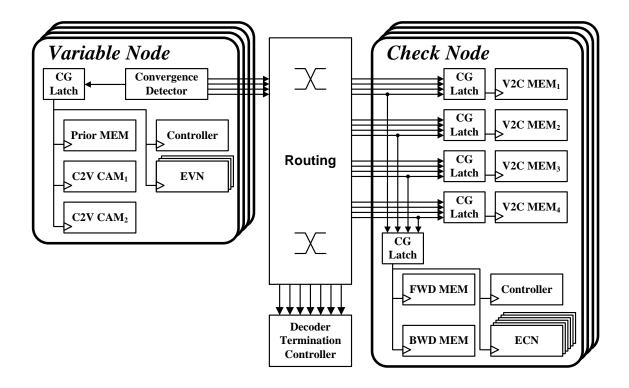

| 3.2  | Architecture of the fully parallel nonbinary LDPC decoder                                                                                                                                                                                              | 51 |

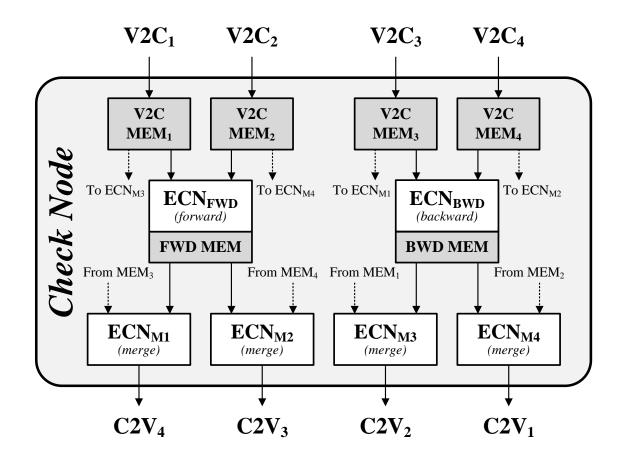

| 3.3  | Architecture of the check node.                                                                                                                                                                                                                        | 53 |

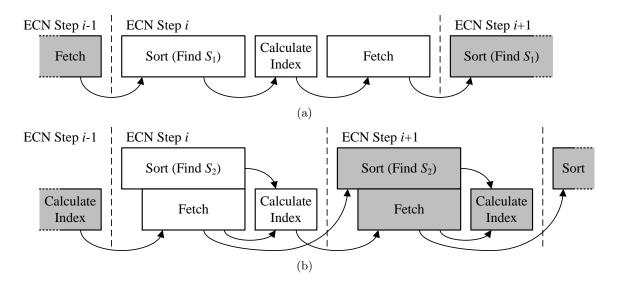

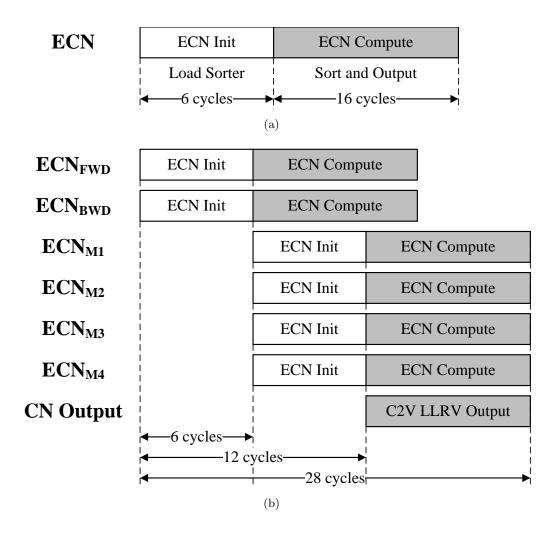

| 3.4  | Sub-operation schedule of (a) the bubble check elementary check node and (b) the look-ahead elementary check node                                                                                                                                      | 53 |

| 3.5  | Operation schedule of (a) the elementary check node and (b) the check node.                                                                                                                                                                            | 55 |

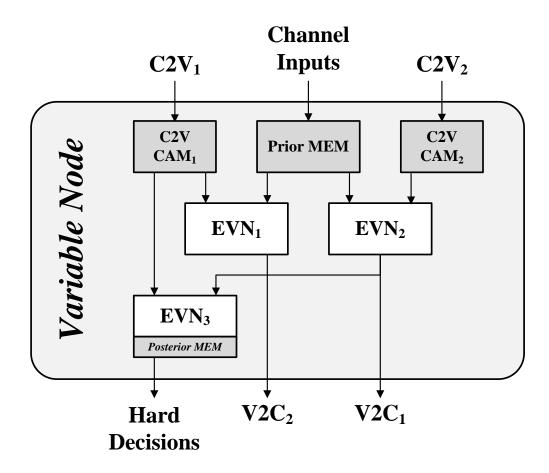

| 3.6  | Architecture of the variable node                                                                                                                                                                                                                      | 56 |

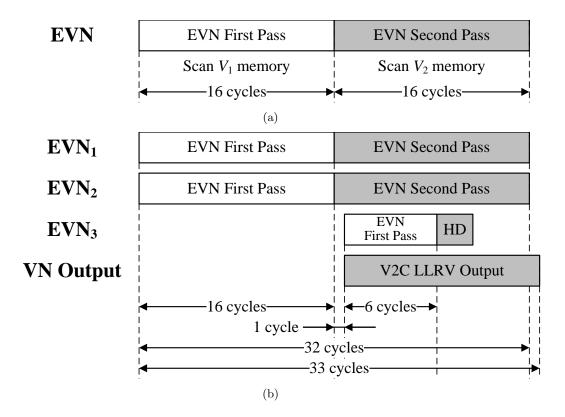

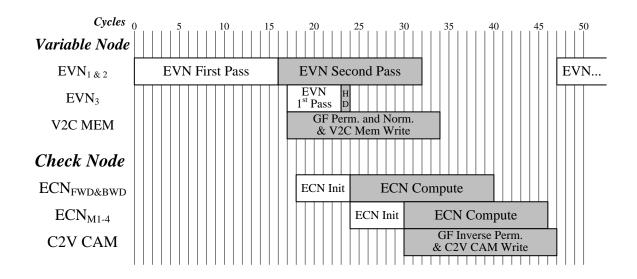

| 3.7  | Operation schedule of (a) the elementary variable node and (b) the variable node. Note that $EVN_3$ uses a shorter sorter length since only the minimum is required.                                                                                   | 57 |

| 3.8  | Operation schedule of the decoder which includes the variable node, check node, permutation & normalization, and inverse permutation stages                                                                                                            | 58 |

| 3.9  | (a) Power breakdown of the 65 nm synthesized fully parallel nonbinary LDPC decoder, and (b) the distribution of sequential logic used in the decoder.                                                                                                  | 60 |

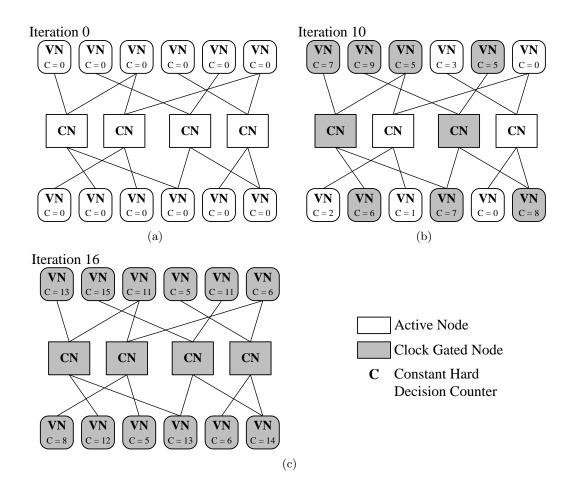

| 3.10 | Example of clock gating showing active and clock gated nodes at different iterations during the decoding process of one frame.                                                                                                                         | 61 |

| 3.11 | Implementation of fine-grained dynamic clock gating for the variable and check node.                                                                                                                                                                   | 62 |

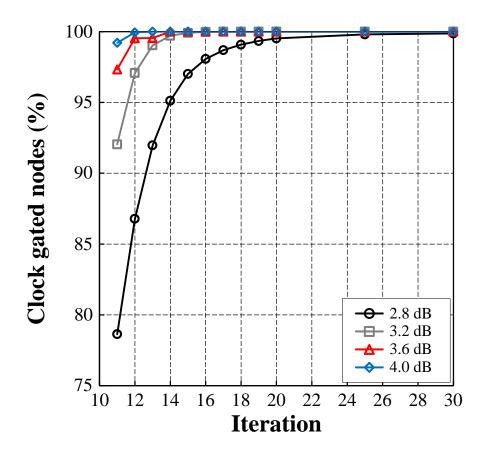

| 3.12 | Cumulative distribution of clock gated nodes at each iteration for various SNR levels with a decoding iteration limit of 30. The parameters used for clock gating are $M = 10$ and $T = 10$ .                                                          | 64 |

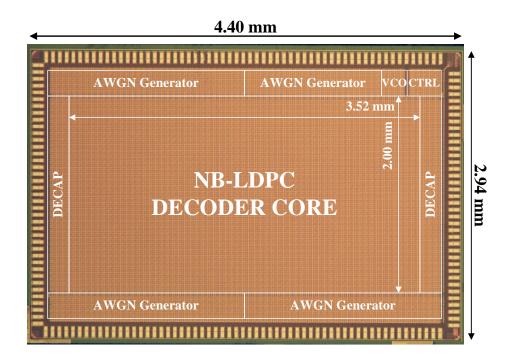

| 3.13 | Chip microphotograph of the decoder test chip. Locations of the test peripherals and the decoder are labeled.                                                                                                                                          | 65 |

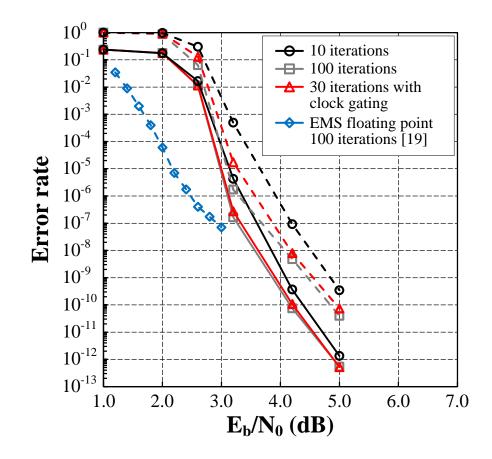

| 3.14 | BER and FER performance of the GF(64) (160, 80) regular-(2, 4) NB-<br>LDPC code using 5-bit quantization.                                                                                                                                              | 66 |

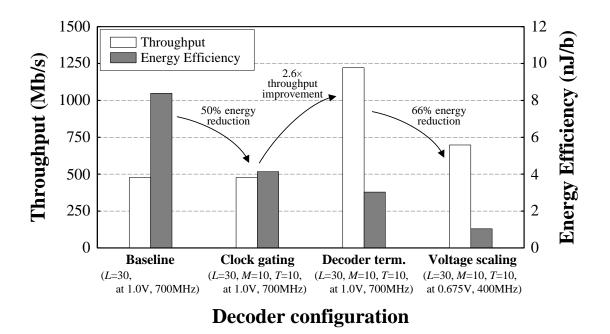

| 3.15 | Illustration of throughput and energy efficiency of various decoder config-<br>urations at 5.0 dB SNR. $L$ , $M$ , and $T$ represents decoding iteration limit,<br>minimum decoding iteration, and consecutive iteration threshold, respec-<br>tively. | 67 |

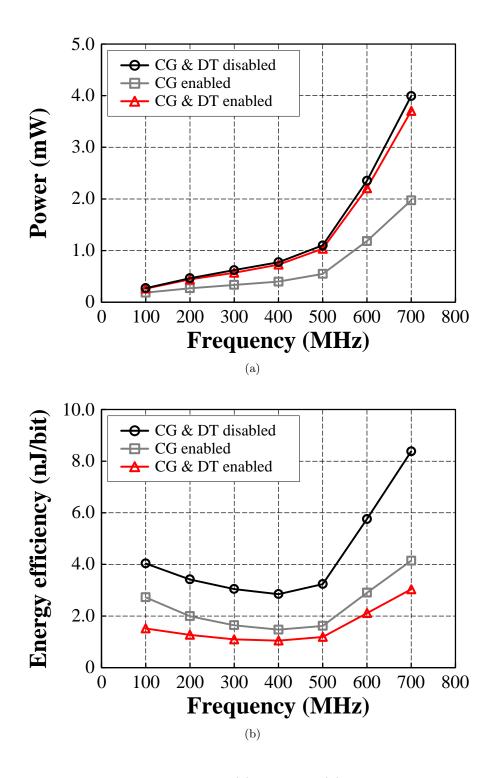

| 3.16 | Measured NB-LDPC decoder (a) power and (b) energy efficiency at 5.0 dB SNR and 30 decoding iterations. CG denotes clock gating and DT denotes decoder termination. The parameters used for clock gating and decoder termination are $M = 10$ and $T = 10. \dots \dots \dots \dots \dots \dots \dots$ | 68 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

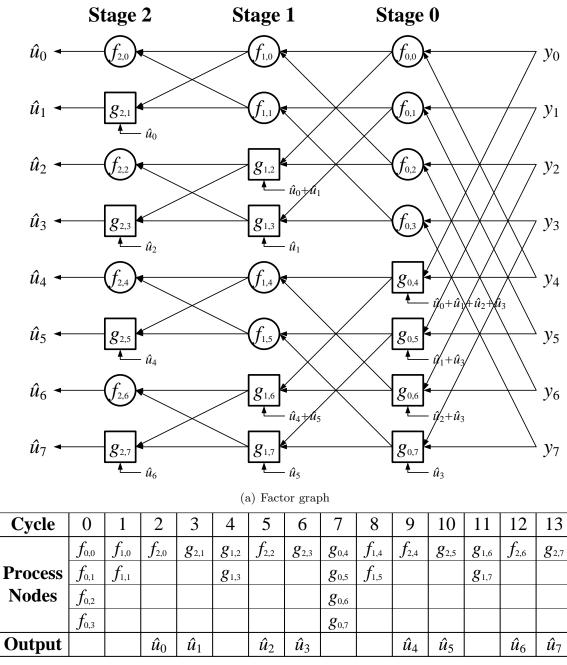

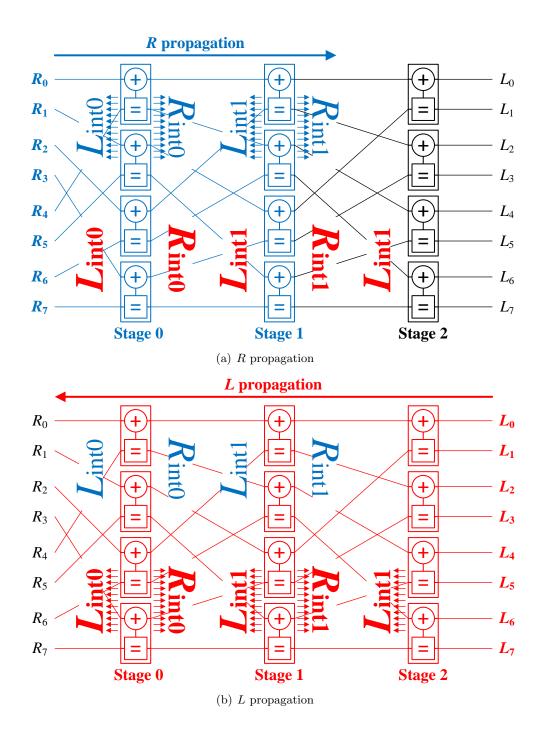

| 4.1  | Example of successive cancellation: (a) factor graph for a $N = 8$ polar code<br>and (b) successive cancellation decoding schedule                                                                                                                                                                   | 73 |

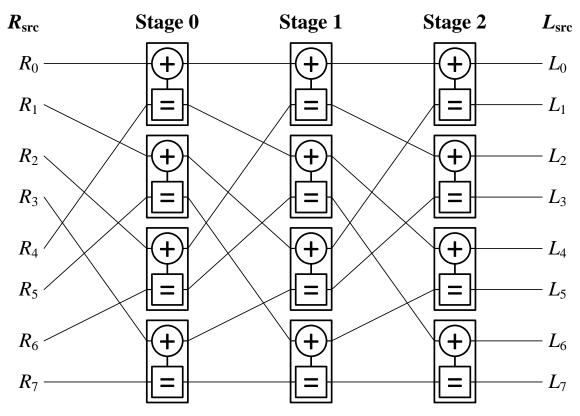

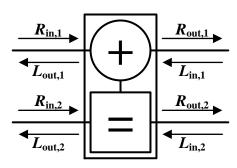

| 4.2  | Example of BP factor graph for $N = 8$ polar code                                                                                                                                                                                                                                                    | 75 |

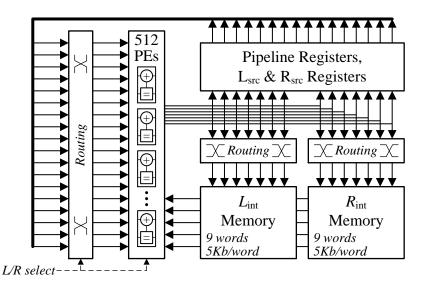

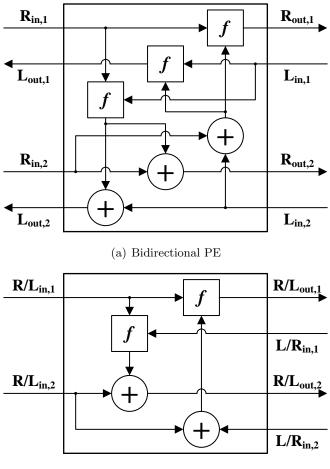

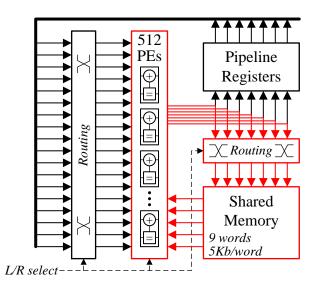

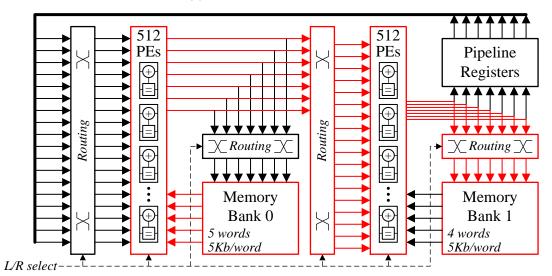

| 4.3  | Conventional single-column bidirectional architecture of a 1024-bit BP po-<br>lar decoder.                                                                                                                                                                                                           | 77 |

| 4.4  | Illustration of the PE outputs in a bidirectional architecture. The outputs produced by the PEs in the $R$ and $L$ propagations are shown in blue and red, respectively.                                                                                                                             | 78 |

| 4.5  | Illustration of the (a) bidirectional PE which outputs both $L_{out}$ and $R_{out}$ and (b) unidirectional PE which outputs either $L_{out}$ or $R_{out}$ based on direction.                                                                                                                        | 79 |

| 4.6  | <ul><li>(a) single-column and (b) double-column unidirectional architecture and</li><li>(c) their comparison. The critical paths are highlighted in red</li></ul>                                                                                                                                    | 81 |

| 4.7  | Conventional memories: (a) standard register file and (b) distributed reg-<br>isters.                                                                                                                                                                                                                | 82 |

| 4.8  | Illustration of the proposed bit-splitting register file                                                                                                                                                                                                                                             | 83 |

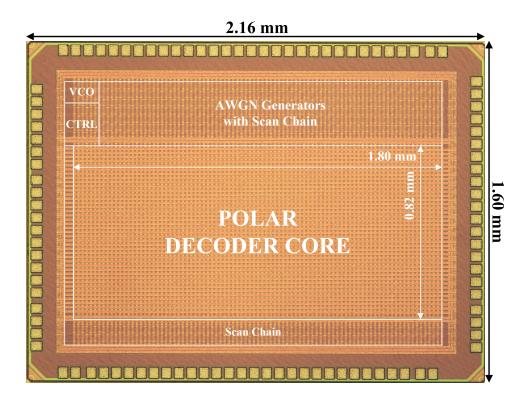

| 4.9  | Chip microphotograph of the decoder test chip. Locations of the test peripherals and the decoder are labeled.                                                                                                                                                                                        | 84 |

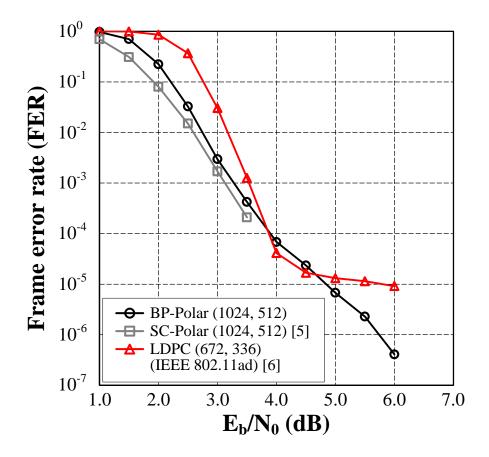

| 4.10 | FER performance of the (1024, 512) polar code using SC and BP decoding algorithm, and the (672, 336) LDPC code for the IEEE 802.11ad standard for comparison.                                                                                                                                        | 85 |

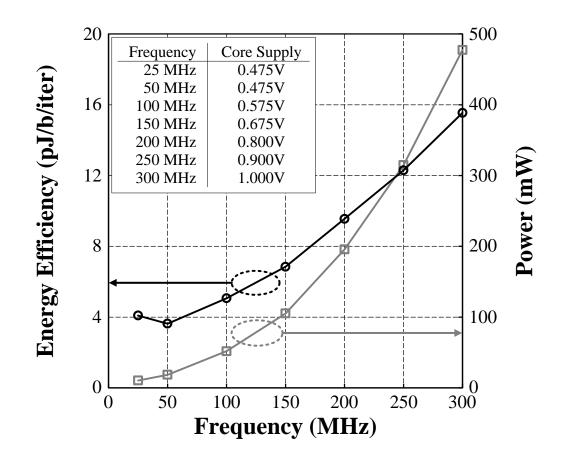

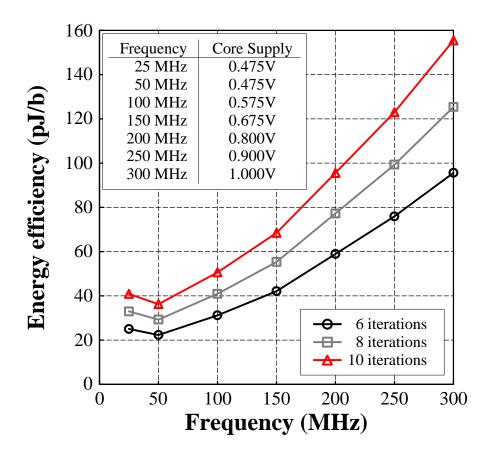

| 4.11 | Measured power consumption and energy efficiency of the BP polar de-<br>coder at the minimum supply voltage for each clock frequency. (BP polar<br>decoding using maximum 15 iterations with early termination enabled.)                                                                             | 87 |

| 4.12 | Measured energy efficiency of the BP polar decoder at the minimum supply voltage for each clock frequency at various decoding iteration limit                                                                                                                                                        | 88 |

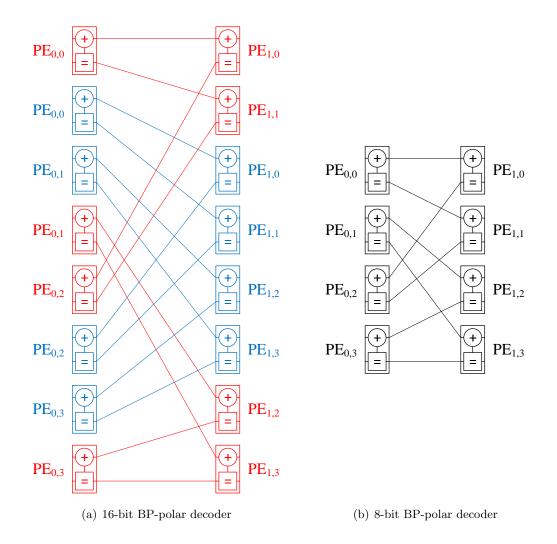

| 4.13 | Illustration of 16-bit BP polar decoder factor graph containing 2 8-bit BP polar decoder factor graphs.                                                                                                                                                                                              | 91 |

# LIST OF TABLES

# <u>Table</u>

| 1.1 | Summary of state-of-the-art LDPC decoder ASIC implementations                         | 4  |

|-----|---------------------------------------------------------------------------------------|----|

| 1.2 | Summary of state-of-the-art NB-LDPC decoder ASIC layout implementa-<br>tions          | 8  |

| 1.3 | Summary of state-of-the-art polar decoder ASIC synthesis implementations.             | 11 |

| 2.1 | Measurement summary of the LDPC decoder at 5.0 dB SNR and 10 de-<br>coding iterations | 42 |

| 2.2 | Comparison of state-of-the-art LDPC decoders                                          | 44 |

| 3.1 | Measurement summary of the NB-LDPC decoder at 5.0 dB SNR $\ .$                        | 67 |

| 3.2 | Comparison of state-of-the-art NB-LDPC decoders (ASIC layout)                         | 70 |

| 3.3 | Comparison of state-of-the-art NB-LDPC decoders (ASIC synthesis) $\ . \ .$            | 70 |

| 4.1 | Comparison of state-of-the-art polar decoders                                         | 89 |

### ABSTRACT

Energy-Efficient Decoders of Near-Capacity Channel Codes

by

Youn Sung Park

Chair: Zhengya Zhang

In state-of-the-art communication and storage systems, channel coding, or error control coding (ECC), is essential for ensuring the reliable transmission and storage. State-of-the-art communication and storage systems have adopted channel codes such as LDPC and turbo codes to close the gap towards the ultimate channel capacity known as the Shannon limit. Their goal is to achieve high transmission reliability while keeping the transmit energy consumption low by taking advantage of the coding gain provided by these channel codes. The lower transmit energy is at the cost of extra energy to decode the channel codes. Therefore a decoder that provides a good coding gain at high energy efficiency is essential for achieving the lowest total energy. This work focuses on reducing the decode energy of near-capacity channel codes, including LDPC codes, nonbinary LDPC codes, and polar codes.

LDPC code is one of the most widely used ECC in communication and storage systems due to its capacity-approaching error correcting performance. State-of-the-art LDPC decoder implementations have demonstrated high-throughput in the Gb/s range through the use of highly parallel architectures. However, these designs consumed high memory power due to the use of registers for the high access bandwidth. A non-refresh embedded DRAM is proposed as a new memory solution to replace the most power-hungry parts of the decoder. The proposed eDRAM takes advantage of the deterministic memory access pattern and short access window to eliminate its refresh circuitry and trades off excess retention time for faster read access time. Architectural techniques can be employed to improve throughput and to accommodate the eDRAM memory. A prototype 1.6 mm<sup>2</sup> 65 nm decoder for a (672, 336) LDPC code compatible with the IEEE 802.11ad standard achieves a peak throughput of 9 Gb/s at 89.5 pJ/b. With voltage and frequency scaling, the power consumption is further reduced to 37.7 mW for a 1.5 Gb/s throughput at 35.6 pJ/b.

Nonbinary LDPC (NB-LDPC) code achieves even better error-correcting performance than a binary LDPC code of comparable block length at the cost of significantly higher decoding complexity and low decoding throughput. However, the factor graph of a NB-LDPC code consists of much fewer edges compared to binary LDPC code. In this work, a Gb/s fully parallel NB-LDPC decoder architecture is proposed to take advantage of the low wiring overhead of NB-LDPC codes. With new architectural techniques including a one-step look-ahead check node design and interleaving of variable node and check node operations, both the clock frequency and iteration latency are significantly improved over the state-of-the-art. By a node level convergence detection strategy, a fine-grained dynamic clock gating can be applied to save dynamic power. A 1.22 Gb/s NB-LDPC decoder test chip for a (160, 80) GF(64) NB-LDPC code is designed as a proof-of-concept. The test chip consumes 3.03 nJ/b, or 259 pJ/b/iteration, at 1.0 V and 700 MHz. Voltage scaling to 675 mV improves the energy efficiency to 1.04 nJ/b, or 89 pJ/b/iteration for a throughput of 698 Mb/s at 400 MHz.

The recently invented polar code is provably capacity-achieving compared to capacityapproaching codes. Although the achievable error-correcting performance of a polar code of a practical block length is similar to LDPC code of comparable block length, the recursive construction of polar codes allows for a very regular structure that reduces the wiring complexity of the encoder and decoder design. This work proposes a belief propagation polar decoder, which delivers a much higher throughput over a conventional successive cancellation decoder. Architectural improvements using unidirectional processing element and doublecolumn parallelism further reduce the decoding latency and improve throughput. A latchbased register file is designed to maximize the memory bandwidth while keeping a small footprint. A 1.48 mm<sup>2</sup> 65 nm polar decoder test chip is designed for a 1024-bit polar code. The decoder achieves a peak throughput of 4.68 Gb/s at 15.5 pJ/b/iteration. With voltage and frequency scaling, the energy efficiency is further improved to 3.63 pJ/b/iteration for a throughput of 779 Mb/s at 50 MHz.

This work has demonstrated energy-efficient decoders for LDPC, NB-LDPC, and polar codes to advance the state-of-the- art. The decoders will enable the continued reduction of decode energy for the latest communication and storage applications. The new techniques developed in this work, including non-refresh embedded memory, bit-splitting register file, and fine-grained dynamic clock gating are widely applicable to designing low-power DSP processors.

## CHAPTER I

## Introduction

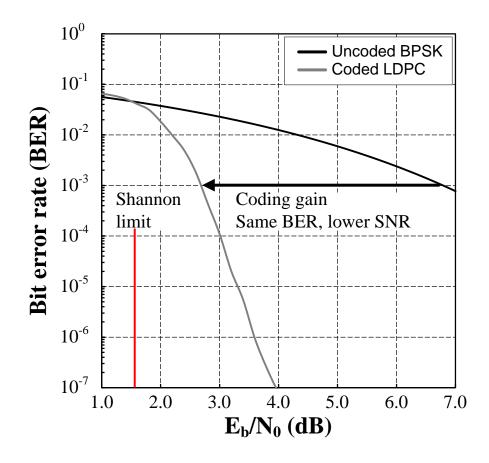

Communication and storage of information have become a ubiquitous part of modern technology. The goal of efficient communication and storage is to transmit or store the most information using the least energy. The ultimate theoretical limit of efficient communication and storage is defined by the Shannon capacity, which captures the least transmit energy, or signal-to-noise ratio (SNR), needed for reliable transmission. For a given information reliability measured in terms of bit error rate (BER), a system with weak or no errorcorrecting code (ECC) will require a high SNR, whereas a system with a strong ECC will be able to reduce the necessary SNR and the transmit energy. Fig. 1.1 illustrates the difference between a coded system versus an uncoded system. A near-capacity code is the most efficient in terms of SNR, but the decoding can be complex, adding significant decode energy. Therefore it is essential to design good decoders for near-capacity channel codes to achieve both good SNR and high decode energy efficiency to reduce the total energy cost. This research is focused on ECC algorithms and their very-large scale integration (VLSI) implementation through algorithm, architecture, and circuits co-optimizations. State-ofthe-art near-capacity codes will be considered, including low-density parity-check (LDPC) [5], nonbinary LDPC (NB-LDPC) [6], and polar codes [7].

### 1.1 Near-Capacity Channel Codes

Turbo code was invented in 1996 [8]. Soon after, LDPC code was rediscovered [5, 6]. Turbo and LDPC codes have been widely adopted in commercial applications, such as

Figure 1.1: Bit error rate comparison between uncoded and encoded systems.

3GPP-HSDPA [9], 3GPP-LTE [10], WiFi (IEEE 802.11n) [3], WiMAX (IEEE 802.16e) [11], digital satellite broadcast (DVB-S2) [12], 10-gigabit Ethernet (IEEE 802.3an) [13], magnetic [14] and solid-state storage [15]. This section reviews LDPC, nonbinary LDPC and polar codes, their current state-of-the-art decoder designs, and major challenges.

#### 1.1.1 Low-Density Parity-Check Codes

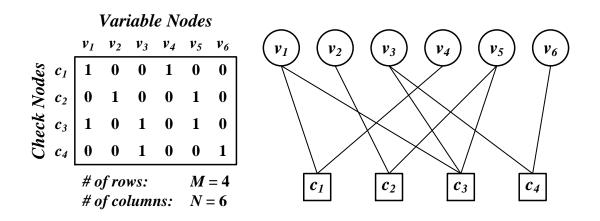

An LDPC code is a block code defined by a  $M \times N$  parity-check matrix H [5, 16], where M is the block length (number of bits in the codeword) and N is the number of parity checks. The elements of the matrix H(i, j) are either 0 or 1 to represent whether bit j of the codeword is part of parity check i. An H matrix can be represented using a factor graph composed of two sets of nodes: a variable node (VN) for each column of the H matrix and a check node for each row. An edge is drawn between VN(j) and CN(i) if H(i, j) = 1.

Figure 1.2: An example H matrix and factor graph representation of an LDPC code

An example H matrix with its corresponding factor graph is shown in Fig. 1.2.

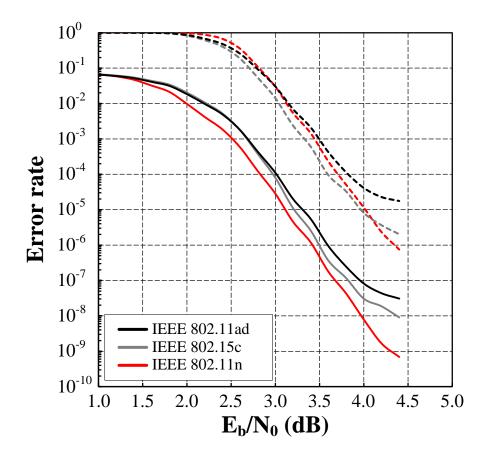

Due to their excellent error-correcting performance, LDPC codes have been used in a wide range of applications. The bit error rate and frame error rate (FER) of three wireless standards are illustrated in Fig. 1.3. In addition, the iterative belief propagation (BP) decoding algorithm can be efficiently implemented in the min-sum algorithm [17]. The algorithm enables simple processing nodes that are easily implemented in hardware. Therefore the decoder complexity can be kept low while achieving good error-correcting performance.

Table 1.1 summarizes some key metrics of state-of-the-art LDPC decoders. A 3.03 mm<sup>2</sup> 0.13  $\mu$ m LDPC decoder for WiMAX consumes more than 340 mW for a throughput up to 955 Mb/s [18]. With technology scaling, the area and power consumption of LDPC decoders continue to improve. A 1.56 mm<sup>2</sup> 65 nm LDPC decoder for the high-speed wireless standard IEEE 802.15.3c consumes 360 mW for a throughput of 5.79 Gb/s [19]. For a higher throughput, the decoder architecture can be further parallelized, but the power and area increase accordingly. A 5.35 mm<sup>2</sup> 65 nm 10-gigabit Ethernet LDPC decoder consumes 2.8 W for up to 47 Gb/s [20].

Parallelizing LDPC decoder for high throughput increases the interconnect complexity [21, 22, 23, 24, 25] and memory bandwidth [26]. Though the interconnect challenge has largely been addressed through the use of structured codes and row-parallel [20, 24, 19]

Figure 1.3: BER (solid-line) and FER (dashed-line) of rate-1/2 LDPC codes used in wireless communication standards [1, 2, 3].

|                                                      | JSSC'12<br>[19] | JSSC'11<br>[18] | JSSC'10<br>[20]   | ASSCC'10<br>[32] |

|------------------------------------------------------|-----------------|-----------------|-------------------|------------------|

| Standard                                             | 802.15.3c       | 802.16e         | 802.3an           | 802.11n          |

| Core Area (mm <sup>2</sup> )                         | 1.56            | 3.03            | 5.35              | 1.77             |

| Throughput (Gb/s)                                    | 5.79            | 0.955           | 6.67 <sup>a</sup> | 0.679            |

| Norm. Energy Eff. (pJ/bit) <sup>b</sup>              | 62.4            | 207.9           | 61.7              | 79               |

| Norm. Area Eff. (Gb/s/mm <sup>2</sup> ) <sup>b</sup> | 3.70            | 0.63            | 0.44              | 0.77             |

Table 1.1: Summary of state-of-the-art LDPC decoder ASIC implementations.

<sup>a</sup> Early termination enabled.

<sup>b</sup> Normalized to 65nm, 1.0V. Throughput is normalized to 10 decoding iteration for flooding decoders and 5 decoding iteration for layered decoders.

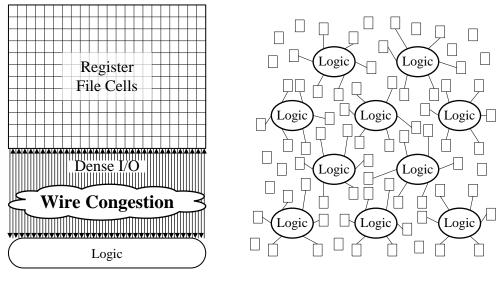

or block-parallel architectures [27, 26, 28, 29, 30, 31, 32, 18, 33], memory bandwidth still remains a major challenge. To support highly parallel architectures, SRAM array needs to be partitioned into smaller banks, resulting in very low area efficiency. High-throughput LDPC decoders use registers for high-speed and wide access, at the expense of high power and area. As a result, memory dominates the power consumption and area of LDPC decoders [34].

#### 1.1.2 Nonbinary Low-Density Parity-Check Codes

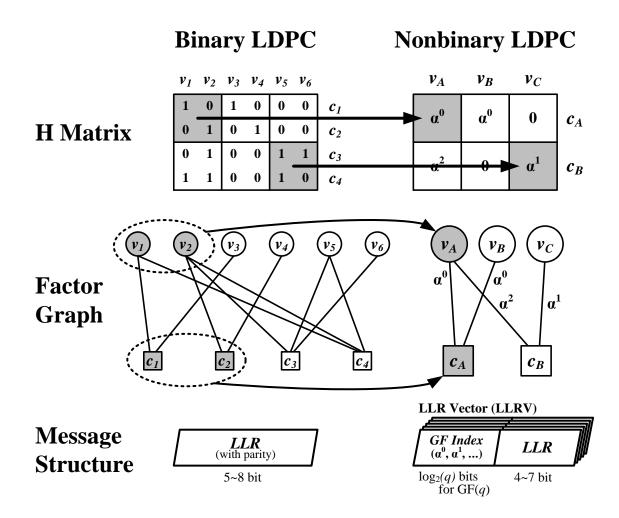

Nonbinary LDPC codes, defined over Galois field GF(q), where q > 2, offers better coding gain than binary LDPC codes [6]. NB-LDPC codes' excellent coding gain can be achieved even at a short block length, and a low error floor has also been demonstrated.

The main difference between an LDPC and an NB-LDPC code is that an NB-LDPC code is formed by grouping multiple bits to symbols using GF elements, as illustrated in an example in Fig. 1.4. In this example, two bits are grouped to a 2-bit symbol using  $GF(2^2)$ or GF(4). From the 4 × 6 binary LDPC H matrix on the left-hand side, 2 × 2 submatrices are replaced with single GF(4) elements, resulting in the 2 × 3 GF(4) nonbinary H matrix on the right-hand side. An NB-LDPC code can also be illustrated using a factor graph composed of variable nodes (VN), check nodes (CN). An edge connects VN  $v_j$  and CN  $c_i$  if the corresponding entry in the H matrix  $H(i, j) \neq 0$ . Similarly, 2 VNs of the binary LDPC factor graph are merged to a single VN in the NB-LDPC factor graph. The same applies to the CNs.

The decoding of NB-LDPC codes follows the same BP algorithm [6] that is used in the decoding of binary LDPC codes. However, the complexity of an NB-LDPC decoder is notably higher: each message exchanged between processing nodes in an NB-LDPC decoder carries an array of log-likelihood ratios (LLR) as illustrated in Fig. 1.4; parity check processing follows a forward-backward algorithm; and high-order GF operations require expensive matching and sorting, in contrast to the much simpler addition and compareselect used in binary LDPC decoding.

As shown in Fig. 1.5, the error-correcting performance of NB-LDPC surpasses that of binary LDPC introduced in the previous section. In addition, no error floor is observed for

Figure 1.4: Comparison of a binary LDPC code and a nonbinary LDPC (NB-LDPC) code.

Figure 1.5: BER (solid-line) and FER (dashed-line) comparison of an LDPC code and a NB-LDPC code.

NB-LDPC even at very low error rates. This is an important characteristic as many LDPC codes of finite block length suffer from error floors preventing them from achieving very low error rates.

The high complexity in the processing elements and large memory requirements have prevented any large-scale high-throughput chip implementations in silicon. Only FPGA, synthesis and layout based designs have been demonstrated prior to this work [35, 36, 37, 38, 39, 40, 41, 42, 43]. Table 1.2 summarizes some key metrics of state-of-the-art NB-LDPC decoder layout implementations. A 10.33 mm<sup>2</sup> 90 nm NB-LDPC decoder achieves a throughput of 47.7 Mb/s [37]. Another 46.18 mm<sup>2</sup> 90 nm NB-LDPC decoder achieves a throughput of 234 Mb/s [40]. With technology scaling, architecture improvements, and algorithm simplifications, the throughput of NB-LDPC decoders continue to improve. A 1.289 mm<sup>2</sup> 28 nm NB-LDPC decoder and a 6.6 mm<sup>2</sup> 90 nm NB-LDPC decoder achieves

|                                                      | TVLSI'13<br>[43] | TVLSI'14<br>[42] | TSP'13<br>[40] | TCAS-I'12<br>[37] |

|------------------------------------------------------|------------------|------------------|----------------|-------------------|

| Design                                               | layout           | layout           | layout         | layout            |

| Block Length                                         | 837<br>GF(32)    | 110<br>GF(256)   | 837<br>GF(32)  | 248<br>GF(32)     |

| Core Area (mm <sup>2</sup> )                         | 6.6              | 1.289            | 46.18          | 10.33             |

| Throughput (Mb/s)                                    | 716              | 546              | 234            | 47.7              |

| Energy Efficiency (nJ/b) <sup>a</sup>                | -                | 4.15             | 2.76           | 7.27              |

| Area Efficiency (Mb/s/mm <sup>2</sup> ) <sup>a</sup> | 288              | 33.9             | 13.4           | 12.3              |

Table 1.2: Summary of state-of-the-art NB-LDPC decoder ASIC layout implementations.

<sup>a</sup> Normalized to 65nm, 1.0V.

throughputs of 546 Mb/s and 716 Mb/s, respectively [42, 43]. However, these throughputs are still low compared to Gb/s throughputs of recent LDPC decoders.

#### 1.1.3 Polar Codes

Polar code is a block code recently invented by Arikan which provably achieves the symmetric capacity I(W) of any given binary-input discrete memoryless channel (B-DMC)[7]. Compared to traditional capacity-approaching codes such as turbo and LDPC, polar code is currently the first code that is provably capacity-achieving. Through the channel polarization effect described by Arikan in [7], N independent channels are combined systematically using a recursive function, and only the k most reliable channels are used for sending information while the remaining N - k channels are frozen to known values for both encoder and decoder. An example of channel polarization is illustrated in Fig. 1.6. The plot shows the capacity of each channel index for a block length  $N = 2^{14}$  for a BEC channel with erasure probability  $\epsilon = 0.5$ . From the polarization effect, a group of channels, shown in the green circle, approach a capacity of 1 which means they are reliable channels to transmit information. On the other hand, a group of channels, shown in the red circle, approach a capacity of 0, which mean they are unreliable channels that need to be frozen to known values. The remaining channels would either be frozen or used for information transmission depending on the code rate.

Figure 1.6: Example of polarization effect on a  $N = 2^{14}$  polar code in a BEC channel with  $\epsilon = 0.5$ .

Figure 1.7: Polar code encoder example for N = 8.

Polar codes can be constructed with block length  $N = 2^n$  and generator matrix

$$F_N = F^{\otimes n}, \text{ where } F = \begin{bmatrix} 1 & 0\\ 1 & 1 \end{bmatrix}.$$

$$(1.1)$$

where  $\otimes$  is the Kronecker product operation. Using n = 3 as an example,

$$F_8 = F^{\otimes 3} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

A graphical representation of the encoder using the generator matrix  $F_8$  is shown in Fig. 1.7 where u represents the original message, v represents the encoded message to be sent through the channel, and  $\oplus$  represents the modulo-2 (or xor) operation.

Although Arikan proved that polar code achieves capacity as the block length N approaches infinity, the error-correcting performance of polar codes of finite block lengths are still away from the Shannon limit. Fig. 1.8 shows the error rate of a 1024-bit polar code

Figure 1.8: BER (solid-line) and FER (dashed-line) comparison of an LDPC code and polar code under successive cancellation decoding.

using successive cancellation (SC) decoding. Current polar codes have similar performance as binary LDPC codes of similar block length.

Due to the recent introduction of polar codes, only a few hardware implementation of polar decoders are found in literature. Most of the work has been done in SC decoding because it is believed that SC decoding provides better error-correcting performance. Several architectures for SC polar decoder have been proposed including the FFT-like SC decoder, pipeline tree architecture, line SC architecture, vector-overlapping architecture [44], and simple successive cancellation (SSC) architecture [45]. On the other hand, little work has been done in BP decoding despite its advantage of higher degree of parallelism.

Table 1.3 summarizes the state-of-the-art polar decoder designs. A 1.71 mm<sup>2</sup> 0.18  $\mu$ m SC polar decoder implementing the 1024-bit polar code consumes 67 mW for a throughput

|                                                      | ASSCC'12<br>[46]        | JSAC'14<br>[48]            | TSP'13<br>[47]          | ISWCS'11<br>[49]       |

|------------------------------------------------------|-------------------------|----------------------------|-------------------------|------------------------|

| Design                                               | silicon                 | fpga                       | synthesis               | fpga                   |

| Code                                                 | SC-Polar<br>(1024, 512) | SC-Polar<br>(32768, 29492) | SC-Polar<br>(1024, 512) | BP-Polar<br>(512, 426) |

| Core Area (mm <sup>2</sup> )                         | 1.71                    | -                          | 0.309                   | -                      |

| Throughput (Mb/s)                                    | 49                      | 1044                       | 246.1                   | 52.03                  |

| Energy Efficiency (pJ/b/iter) <sup>a</sup>           | 292.2                   | -                          | -                       | -                      |

| Area Efficiency (Mb/s/mm <sup>2</sup> ) <sup>a</sup> | 608.5                   | -                          | 796.44                  | -                      |

Table 1.3: Summary of state-of-the-art polar decoder ASIC synthesis implementations.

<sup>a</sup> Normalized to 65nm, 1.0V.

of 49 Mb/s [46]. It is the first reported hardware implementation of a SC polar decoder. Another 0.309 mm<sup>2</sup> 65 nm synthesis-based design achieves 246.1 Mb/s at 500 MHz [47]. FPGA designs have also been proposed, one of which is a 32768-bit SC polar decoder which achieves 1044 Mb/s by using the SSC architecture with a high-rate code as a method to increase throughput [48]. An FPGA-based 512-bit BP decoder achieves 52 Mb/s [49] while a GPU-based 1024-bit design achieves 5 Mb/s [50].

#### 1.2 Scope of this Work

In this work, new design techniques are proposed to improve upon the state-of-theart designs reviewed in the previous section through the use of architecture and circuit techniques that are co-optimized to work with the decoding algorithms.

#### 1.2.1 Low-Density Parity-Check Codes

Logic-compatible embedded DRAM (eDRAM) [4, 51, 52, 53] is proposed as a promising alternative to register-based memory that has been used in building high-throughput LDPC decoders. Logic-compatible eDRAM does not require a special DRAM process and it is both area efficient and low power – an eDRAM cell can be implemented in 3 transistors [4] and it supports one read and one write port, at half the size of a dual-port SRAM cell and its energy consumption is substantially lower than a register. A conventional eDRAM is however slow. A periodic refresh is also necessary to maintain continuous data retention. Interestingly, we find that when eDRAM is used in high-speed LDPC decoding, refresh can be completely eliminated to save power and access speed can be improved by trading off the excess retention time.

In this work, we co-design a non-refresh eDRAM with the LDPC decoder architecture to optimize its read and write timing and simplify its addressing. An analysis of the LDPC decoder's data access shows that the access window of the majority of the data ranges from only a few to tens of clock cycles. The non-refresh eDRAM is designed to meet the access window with a sufficient margin and the excess retention time is cut short to increase the speed. The resulting 3T eDRAM cell balances wordline coupling to mitigate the effects on its storage. We integrate  $32.5 \times 210$  non-refresh eDRAM arrays in the design of a 65 nm LDPC decoder to support the (672, 336) LDPC code for the high-speed wireless standard IEEE 802.11ad[1]. All columns of the eDRAM arrays can be accessed in parallel to provide the highest bandwidth. The decoder throughput is further improved using row merging and dual-frame processing to increase hardware utilization and remove pipeline stalls. The resulting decoder achieves a throughput up to 9 Gb/s and consumes only 37.7 mW at 1.5 Gb/s.

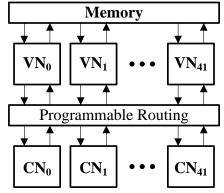

#### 1.2.2 Nonbinary Low-Density Parity-Check Codes

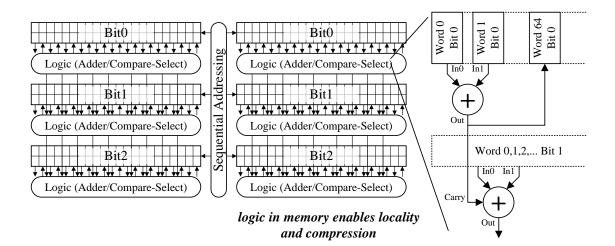

The complex decoding and large memory requirement of NB-LDPC decoders have prevented any practical chip implementations. Compared to binary LDPC code, the reduced number of edges in NBLDPC codes factor graph permits a low wiring overhead in the fully parallel architecture. The throughput is further improved by a one-step look-ahead check node design that increases the clock frequency to 700 MHz, and the interleaving of variable node and check node operations that shortens one decoding iteration to 47 clock cycles. We allow each processing node to detect its own convergence and apply fine-grained dynamic clock gating to save dynamic power. When all processing nodes have been clock gated, the decoder terminates and continues with the next input to increase the throughput.

In this work, we present a 7.04  $\text{mm}^2$  65 nm CMOS NB-LDPC decoder chip for a GF(64) (160, 80) regular-(2, 4) code using the truncated EMS algorithm. With the proposed fully

parallel architecture and scheduling techniques, the decoder achieves a 1.22 Gb/s throughput using fine-grained dynamic clock gating and decoder termination for an efficiency of 3.03 nJ/b, or 259 pJ/b/iteration, at 1.0V and 700 MHz. Dynamic voltage and frequency scaling further improves the efficiency to 89 pJ/b/iteration for a throughput of 698 Mb/s, at 675 mV and 400 MHz.

#### 1.2.3 Polar Codes

Due to the inherent serial nature of SC decoding, we turn our attention to BP decoding. A BP decoder is inherently more parallel than SC decoder due to the lack of inter-bit dependency on the decoded output bits. Therefore the decoder can be designed to implement a whole column of processing nodes in the factor graph to increase throughput. The simple computation performed in the processing elements allows for small node footprint which helps achieve high parallelism. By exploiting the order of computation in the BP algorithm, a unified shared memory can be used which reduces the memory size by half and the processing node logic by 33%. To achieve higher throughput and lower latency, a double-column architecture is used which implements twice as many nodes while the memory size remains constant. The double-column architecture increases the throughput at the cost of a slight increase in clock period. To reduce the memory footprint of the decoder, a bit-splitting latch-based register file is employed which enables an 85% placement density.

In this work, we present a 1.476 mm<sup>2</sup> 65 nm CMOS polar decoder for the 1024-bit polar code using the BP algorithm. With the proposed architectural transformations and memory optimization, the overall decoder achieves a 4.68 Gb/s throughput while consuming 478 mW for an efficiency of 15.5 pJ/b/iteration, at 1.0 V and 300 MHz. Dynamic voltage and frequency scaling further improves the efficiency to 3.6 pJ/b/iteration for a throughput of 780 Mb/s, at 475 mV and 50 MHz.

### CHAPTER II

## LDPC Decoder with Embedded DRAM

#### 2.1 Decoding Algorithm

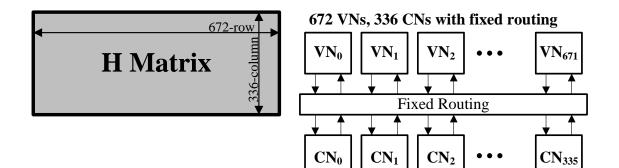

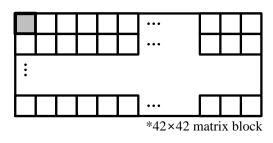

Almost all the latest applications have adopted LDPC codes whose H matrix is constructed using submatrices that are cyclic shifts of an identity matrix or a zero matrix. For example, the newest high-speed wireless standard IEEE 802.11ad [1] specifies a family of four LDPC codes whose H matrices are constructed using cyclic shifts of the  $Z \times Z$  identity matrix or zero matrix where Z = 42. The structured H matrix can be partitioned along submatrix boundaries, e.g., the H matrix of the rate-1/2 (672, 336) code can be partitioned to 8 rows and 16 columns of  $42 \times 42$  submatrices as shown in Fig. 2.1.

LDPC encoding and decoding are both based on the H matrix. Encoding produces LDPC codewords that are transmitted over the channel. The receiver decodes the codewords based on the channel output. LDPC decoding uses an iterative soft message passing algorithm called belief propagation [16, 54] that operates on the factor graph in the following steps:

- (a) Initialize each VN with the prior log-likelihood ratio (LLR) based on the channel output y and its noise variance  $\sigma^2$

- (b) VNs send messages (the prior LLRs in the first iteration) to the connected CNs

- (c) Each CN computes an extrinsic LLR for each connected VN (i.e., the likelihood of each bit's value given the likelihoods from all other VNs connected to the CN), which is then sent back to the VN.

| Rate 1/2                                                       | M = 336 N = 672 Z = 42                                                                                 | <i>Rate 13/16 M</i> = 126 <i>N</i> = 672 <i>Z</i> = 42                                                                                                                                                                               |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{40}$ $I_{38}$ $I_{13}$ $I_5$                               | I <sub>18</sub>                                                                                        | $I_{29} I_{30} I_0 I_8 I_{33} I_{22} I_{17} I_4 I_{27} I_{28} I_{20} I_{27} I_{24} I_{23}$                                                                                                                                           |

| I <sub>34</sub> I <sub>35</sub> I <sub>27</sub> I <sub>2</sub> | 30 I <sub>2</sub> I <sub>1</sub>                                                                       | $I_{37} I_{31} I_{18} I_{23} I_{11} I_{21} I_6 I_{20} I_{32} I_9 I_{12} I_{29} I_{10} I_0 I_{13}$                                                                                                                                    |

| I <sub>36</sub> I <sub>31</sub> I <sub>7</sub> I <sub>5</sub>  | $I_{10} I_{41}$                                                                                        | $I_{25} I_{22} I_4 I_{34} I_{31} I_3 I_{14} I_{15} I_4 I_2 I_{14} I_{18} I_{13} I_{13} I_{22} I_{24}$                                                                                                                                |

| $I_{27}$ $I_{18}$ $I_{12}$ $I_{20}$                            | I <sub>15</sub> I <sub>6</sub>                                                                         |                                                                                                                                                                                                                                      |

| $I_{35}$ $I_{41}$ $I_{40}$ $I_{39}$                            | I <sub>28</sub> I <sub>3</sub> I <sub>28</sub>                                                         |                                                                                                                                                                                                                                      |

| I <sub>29</sub> I <sub>0</sub> I <sub>22</sub> I               | 4 I <sub>28</sub> I <sub>27</sub> I <sub>23</sub>                                                      |                                                                                                                                                                                                                                      |

| $I_{31}$ $I_{23}$ $I_{21}$ $I_{21}$                            |                                                                                                        |                                                                                                                                                                                                                                      |

| $I_{22}$ $I_{34}$ $I_{31}$ $I_{14}$                            | I <sub>4</sub> I <sub>13</sub> I <sub>22</sub> I <sub>24</sub>                                         |                                                                                                                                                                                                                                      |

| Rate 5/8                                                       | M = 252 $N = 672$ $Z = 42$                                                                             | Cyclic Shift of Identity Matrix                                                                                                                                                                                                      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$          |                                                                                                        | For <i>Z</i> = 4                                                                                                                                                                                                                     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$          |                                                                                                        |                                                                                                                                                                                                                                      |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                  | $\mathbf{I_0} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \qquad \mathbf{I_1} = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \end{bmatrix}$ |

|                                                                |                                                                                                        | $\mathbf{I_0} = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \qquad \mathbf{I_1} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$                                                                     |

|                                                                |                                                                                                        |                                                                                                                                                                                                                                      |

|                                                                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                  |                                                                                                                                                                                                                                      |

| $I_{22}$ $I_{34}$ $I_{31}$ $I_{14}$                            | I <sub>4</sub> I <sub>22</sub> I <sub>24</sub>                                                         |                                                                                                                                                                                                                                      |

| D = 4 = 2/4                                                    | M 169 M 672 7 42                                                                                       | $\mathbf{I_2} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \qquad \mathbf{I_3} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix}$ |

| <i>Rate 3/4</i>                                                | M = 168 N = 672 Z = 42                                                                                 | $\mathbf{I}_2 = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \end{bmatrix} \qquad \mathbf{I}_3 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix}$                                                                     |

| $I_{35} I_{19} I_{41} I_{22} I_{40} I_{41} I_{39} I$           |                                                                                                        |                                                                                                                                                                                                                                      |

|                                                                | $_{4} \mathbf{I}_{27} \mathbf{I}_{28} \mathbf{I}_{20} \mathbf{I}_{27} \mathbf{I}_{24} \mathbf{I}_{23}$ |                                                                                                                                                                                                                                      |

| $I_{37} I_{31} I_{18} I_{23} I_{11} I_{21} I_6 I_2$            |                                                                                                        |                                                                                                                                                                                                                                      |

| $I_{25} I_{22} I_4 I_{34} I_{31} I_3 I_{14} I_4$               | $I_{15} I_4 I_{14} I_{18} I_{13} I_{13} I_{13} I_{22} I_{24}$                                          |                                                                                                                                                                                                                                      |

Figure 2.1: H matrices of the rate-1/2, rate-5/8, rate-3/4 and rate-13/16 LDPC code for the IEEE 802.11ad standard [1].

(d) Each VN computes the posterior LLR based on the extrinsic LLRs received and the prior LLR, and makes a hard decision (0 or 1). If the hard decisions satisfy all the parity checks, decoding is complete, otherwise the steps (b) to (d) are repeated.

A detailed description of the decoding algorithm can be found in [16]. In BP decoding, soft messages are passed back and forth between VNs and CNs until all the parity checks are met, which indicates the convergence to a valid codeword. In practice, a maximum iteration limit is imposed to terminate decoding if convergence cannot be reached within the given iteration limit.

A practical decoder design follows either the sum-product [16] or the min-sum algorithm [17], which are two popular implementations of the BP algorithm. Using the sum-product algorithm in the log-domain, the VNs perform sum operations and the CNs perform logtanh, sum and inverse log-tanh operations. Min-sum simplifies the CN operation to the minimum function. The min-sum algorithm usually performs worse than the sum-product algorithm, and techniques including offset correction and scaling [55] are frequently applied to improve the performance.

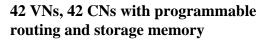

#### 2.2 Decoder Architecture

Common LDPC decoder architectures belong to one of three classes: full-parallel, rowparallel and block-parallel [56] as shown in Fig. 2.2. The full-parallel architecture shown in Fig. 2.2(a) realizes a direct mapping of the factor graph with VNs and CNs mapped to processing elements and edges mapped to interconnects [21, 22, 25]. This architecture provides the highest throughput, allowing each decoding iteration to be done in one or two clock cycles, but it incurs a large area due to complex interconnects.

For a lower throughput of up to hundreds of Mb/s, the block-parallel architecture shown in Fig. 2.2(b) processes only one section of the factor graph that corresponds to one or a few submatrices of the H matrix per clock cycle [27, 26, 28, 29, 30, 31, 32, 18, 33]. The VNs and CNs are time-multiplexed, so it takes tens to hundreds of clock cycles to complete one decoding iteration. The more serialized processing requires memories to store messages and configurable routers to shuffle messages between VNs and CNs. The extra overhead in memory and routing results in worse energy and area efficiency. A row-parallel architecture improves upon the block-parallel architecture by processing a larger section of the factor graph that corresponds to an entire row of submatrices of the H matrix per clock cycle [20, 24, 19].

The row-parallel architecture [20, 24, 19] shown in Fig. 2.2(c) provides a high throughput of up to tens of Gb/s, while its routing complexity can still be kept low, permitting a high energy and area efficiency. To meet the 6 Gb/s that is required by the IEEE 802.11ad standard, we choose the row-parallel decoder architecture. The IEEE 802.11ad standard [1] specifies four codes of rate-1/2, rate-5/8, rate-3/4 and rate-13/16, whose H matrices are made up of 16 columns  $\times$  8 rows, 6 rows, 4 rows and 3 rows of cyclic shifts of the 42  $\times$  42 identity matrix or zero matrix, as illustrated in Fig. 2.1. The four matrices are compatible, sharing the same block length and component submatrix size.

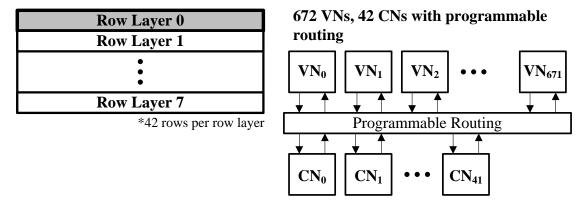

A row-parallel decoder using flooding schedule is designed using 672 VNs and 42 CNs.

(a) Full-parallel architecture

(b) Block-parallel architecture

(c) Row-parallel architecture

Figure 2.2: Illustration of LDPC decoder architectures. The shaded part represents the section of the H matrix that is processed simultaneously.

The 672 VNs process the soft inputs of 672 bits in parallel by computing VN-to-CN (V2C) messages and send them to the 42 CNs following the H matrix shown in Fig. 2.1. The 42 CNs compute the parity checks and send CN-to-VN (C2V) messages back to the VNs. The C2V messages are post-processed by the VNs and stored in their local memories. The row-parallel architecture operates on one block row of submatrices in the H matrix at a time, as highlighted in Fig. 2.2.

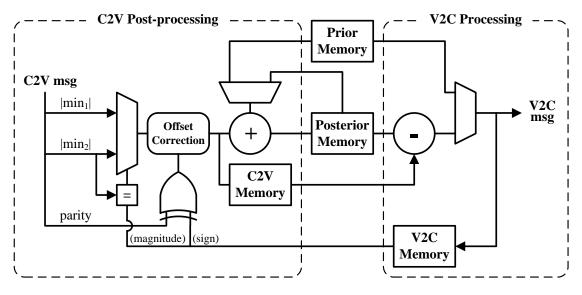

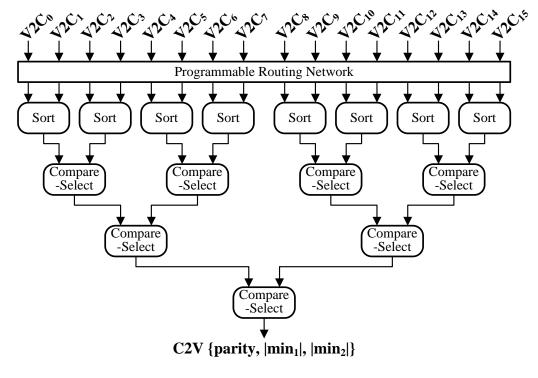

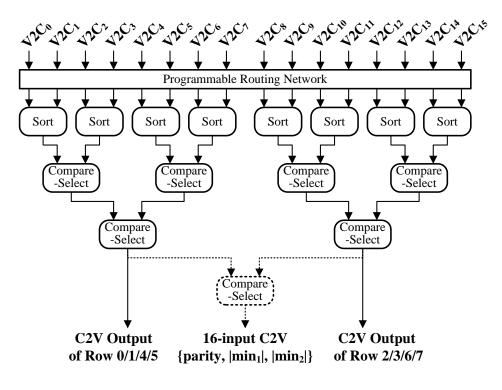

The VN and CN designs in detail are shown in Fig. 2.3. A VN computes a V2C message by subtracting the C2V message stored in the C2V memory from the posterior log-likelihood ratio (LLR). The V2C message is then sent to the CN while a copy is stored in the V2C memory for post-processing the C2V message later in the iteration. A CN receives up to 16 V2C inputs from the VNs and computes the XOR of the signs of the inputs to check if the even parity is satisfied. The CN also computes the minimum and the second minimum magnitude among the inputs by compare-select for an estimate of the reliability of the parity check. Both the XOR and the compare-select are done using a tree structure. The CN prepares the C2V message as a packet composed of the parity, the minimum and the second minimum magnitude.

After the C2V message is received by the VN, it compares the V2C message stored in memory with the minimum and the second minimum magnitude to decide whether the minimum or the second minimum is a better estimate of the reliability of the bit decision. The sign and the magnitude are then merged and an offset is applied as an algorithmic correction. The post-processed C2V message is stored in the C2V memory. The C2V message is accumulated and summed with the prior LLR to compute the updated posterior LLR. A hard decoding decision is made based on the sign of the posterior LLR at the completion of each iteration. The messages and computations are quantized for an efficient implementation. We determine based on extensive simulations that a 5-bit fixed-point quantization offers a satisfactory performance.

#### 2.2.1 Pipelining and Throughput

In the LDPC decoding described above, the messages flow in the following order: (1) each of the 672 VNs computes a V2C message, which is routed to one of the 42 CNs through

(a) variable node

(b) check node

Figure 2.3: (a) Variable node, and (b) check node design (an XOR gate is incorporated in the sort and compare-select logic of the CN to perform the parity check.)

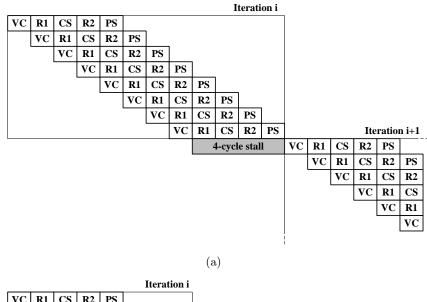

Figure 2.4: Pipeline schedule of (a) a conventional single-frame decoder without row merging, (b) a conventional single-frame decoder with row merging, and (c) proposed dual-frame decoder with row merging. Note that (a) and (b) require stalls inbetween frames due to data dependency between the PS and VC stages. point-to-point links; (2) each CN receives up to 16 V2C messages, and computes a C2V message to be routed back to the VNs through a broadcast link; and (3) each VN postprocesses the C2V message and accumulates it to compute the posterior LLR. These steps complete the processing of one block row of submatrices. The decoder then moves to the next block row and the V2C routing is reconfigured using shifters or multiplexers. Based on these steps, we can design a 5-stage pipeline: (1) VN computing V2C message, (2) routing from VN to CN, (3) CN computing C2V message, (4) routing from CN to VN, and (5) VN post-processing C2V messages and computing posterior. For simplicity, the five stages are named VC, R1, CS, R2, and PS, as illustrated in Fig. 2.4(a). The throughput of a row-parallel architecture is determined by the number of block rows  $m_b$  and the number of pipeline stages,  $n_p$ . The H matrix of the rate-1/2, 5/8, 3/4, and 13/16 code has  $m_b = 8$ , 6, 4 and 3, respectively. Based on the pipeline chart in Fig. 2.4(a), the number of clock cycles per decoding iteration is  $m_b + n_p - 1$ . Suppose the number of decoding iteration is  $n_{it}$ , then the decoding throughput is given by

$$TP = \frac{f_{clk}N}{(m_b + n_p - 1)n_{it}}$$

(2.1)

where  $f_{clk}$  is the clock frequency and N is the block length of the LDPC code. N = 672for the target LDPC code. The 1/2-rate LDPC code has the most number of block rows,  $m_b = 8$ .  $n_p = 5$  for the 5-stage pipeline. To meet the 6 Gb/s throughput with 10 decoding iterations ( $n_{it} = 10$ ), the minimum clock frequency is 1.07 GHz, which is challenging and entails high power consumption.

Each VN in this design includes two message memories, V2C memory and C2V memory. CN does not retain local memory. Each memory contains  $m_b = 8$  words to support the row-parallel architecture for the 1/2-rate LDPC code. Each word is 5-bit wide, determined based on simulation. In each clock cycle, one message is written to the V2C memory and one is read from the V2C memory. The same is true for the C2V memory.

For a scalable design and a higher efficiency, the 672 VNs in the row-parallel LDPC decoder are grouped to 16 VN groups (VNG), each of which consists of 42 VNs. The V2C memories of the 42 VNs in a VNG are combined in one V2C memory that contains  $m_b =$

8 words and each word is  $5b \times 42 = 210b$  wide. Similarly, the C2V memories of the 42 VNs in a VNG are combined in one C2V memory of 8  $\times$  210b. In each clock cycle, one 210b word is written to the V2C memory and one 210b word is read from the memory. The same is true for the C2V memory. Each memory's read and write access latency have to be shorter than 0.933 ns to meet the 1.07 GHz clock frequency.

# 2.3 Throughput Enhancement

The throughput of the LDPC decoder depends on the number of block rows. To enhance the throughput, we reduce the number of effective block rows to process using row merging and apply dual frame processing to improve efficiency [34].

# 2.3.1 Row Merging

The H matrix of the rate-1/2 code has the most number of block rows among the four codes, but note that the H matrix of the rate-1/2 code is sparse with many zero submatrices. We take advantage of the sparseness by merging two sparse rows to a full row so that they can be processed at the same time (e.g., merge row 0 and row 2, row 1 and row 3, etc.), as illustrated in Fig. 2.5(a). To support row merging, each 16-input CN is split to two 8-input CNs, as in Fig. 2.5(b), when decoding the rate-1/2 code with minimal hardware additions.

The same technique can be applied to decoding the rate-5/8 code by merging row 2 and row 4, and row 3 and row 5. Row merging reduces the effective number of rows to process to 4, 4, 4, and 3 for the rate-1/2, 5/8, 3/4, and 13/16 codes, respectively. Row merging improves the worst-case throughput to

$$TP = \frac{f_{clk}N}{(n_p + 3)n_{it}}$$

(2.2)

To meet the 6Gb/s throughput with 10 decoding iterations, the minimum clock frequency is reduced to 720 MHz. Row merging reduces the V2C memory and C2V memory in each VNG to  $4 \times 210$ b. Each memory's read and write access latency is relaxed, but it has to be below 1.4 ns to meet the required clock frequency.

Rate 1/2

M = 336 N = 672 Z = 42

| Row 0 | I <sub>40</sub> |                 | I <sub>38</sub> |                 | I <sub>13</sub> |                 | I <sub>5</sub>  |                 | I <sub>18</sub> |          |                 |                 |                 |                 |                 |                 |

|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Row 1 | I <sub>34</sub> |                 | I <sub>35</sub> |                 | I <sub>27</sub> |                 |                 | I <sub>30</sub> | I <sub>2</sub>  | $I_1$    |                 |                 |                 |                 |                 |                 |

| Row 2 |                 | $I_{36}$        |                 | I <sub>31</sub> |                 | $I_7$           |                 | I <sub>34</sub> |                 | $I_{10}$ | $I_{41}$        |                 |                 |                 |                 |                 |

| Row 3 |                 | I <sub>27</sub> |                 | I <sub>18</sub> |                 | I <sub>12</sub> | I <sub>20</sub> |                 |                 |          | I <sub>15</sub> | $I_6$           |                 |                 |                 |                 |