# Towards Very Large Scale Analog (VLSA): Synthesizable Frequency Generation Circuits

by

# **Muhammad Faisal**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2014

## **Doctoral Committee:**

Associate Professor David D. Wentzloff, Chair Professor Michael P. Flynn Yorgos Palaskas, Intel Corporation Associate Professor Sara A. Pozzi

# © Muhammad Faisal

\_\_\_\_\_

All rights reserved

2014

To my family and friends

# **ACKNOWLEDGEMENTS**

I'd like to start off by thanking my advisor, David Wentzloff, who has been a great coach and mentor throughout my PhD. Throughout the past five years, the extent of his guidance extended beyond just setting the direction of my Ph.D research. Not too many advisors can race their first year students down the sleeping bear dunes – sorry about your hamstring by the way. I would also like to thank Prof. Michael Flynn, Prof. Sara Pozzi & Prof. (③) Yorgos Palaskas for serving on my Ph.D committee and providing valuable suggestions to refine further improve my thesis.

I must give credit to all the educators who inspired me to pursue my ambitions, academic or otherwise. In particular, Professor Adel Sedra, who's is the reason I am a circuit designer today, and to this day he remains a strong advocate of me and my work – instilling confidence in me. He used to tell us that circuits are good for our soul, something I hope to understand someday. I must also thank Mark Spera, my high school chemistry teacher, who once said, "Muhammad, choose your path carefully. You've got what it takes to achieve anything in life. It better be the right thing". His words echo in my head to this day.

I also want to thank the entire Radio Integration Lab at Intel. Their encouragement and genuine interest in my research motivated me to push forward in this direction.

I want to thank my parents, Razzaq and Sajida, for their unconditional love and support, my siblings, Umair, Waqas, Saima, Shaista and my brothers in law, Asif and Azam, for their constant encouragement and curiosity about my school.

I'd like to thank the past and present members of the WICS mafia who enriched my life in more ways than I can imagine. In particular, Nathan Roberts, who has been a friend, colleague and a football buddy since the first of grad school. Osama Khan, who didn't have to think twice before helping me with technical matters and off the field personal situations. Sangwook Han, without whom, I would not have finished my first tapeout. Jonathan Brown, who convinced me to come to the University of Michigan. Kuo-Ken Huang, who was my goto car guy and helped me pick out two cars. Dae Young Lee, who constantly encouraged me to keep my head up when my first chip wasn't behaving. Seunghyun Oh, who's efficiency and intelligence amazed me every day. Youngmin Park, who blazed the VLSA trails for me. Ryan Rogel, who added a new dimension to the group dynamics. David Moore, who is the greatest protégé on the planet and will go on to do some amazing things. Elnaz Ansari, who taught me Persian dance moves. Hyeongseok Kim, who was quiet but had a lot of interesting stories to share. Yao Shi, whose knowledge of random things surprised me a few times. Michael Kines, who found the level of my corruption quite amusing. Avish Kosari, who has promised to turn me into a violinist someday. Armin Alaghi, the honorary member of WICS group who could probably be a very successful comedian.

I would also like to thank a number of past and present students from the rest of Michigan Integrated Circuits Lab. I'd like to start off with Jorge Pernillo, who enhanced my social life in Ann Arbor. Jeffrey Fredenburg, who makes generating innovative ideas seem effortless. Mo Barangi, who embarrassed me in front of friends and strangers more times than I want to remember. I'd also like to thank Chunyang, Jaehun, Mohammad, Batu, Nick, Hyungil, David, Ben, Bharan, Dave, Zhiyoong, Yoonmyung, Gyuho, Hassan and Greg.

A number of non-UM friends played a crucial role in keeping me sane throughout my PhD. Emily Grekin was my social key and yoga buddy (John's pretty cool too). My Canadian friends, Sunny, Mintu, Yashar, Kundan, Anand, George, Sep and Jorge, made sure that I didn't miss non-Ph.D life too much. Only these guys would travel 4200 kilometers on a whim to hang out with Mo and then spend three days sardined up in an SUV, listening to "the big bad wolf" while fighting and arguing over who gets to take the shot gun seat.

Big thumbs up to the Ann Arbor coffee shops and libation venues for providing the essential fuel!

# TABLE OF CONTENTS

| DEDICATI  | ION                                                         | ii     |

|-----------|-------------------------------------------------------------|--------|

| ACKNOW    | LEDGEMENTS                                                  | iii    |

| LIST OF F | IGURES                                                      | ix     |

| LIST OF T | ABLES                                                       | xii    |

| ABSTRAC   | Т                                                           | . xiii |

| Chapter   | 1 Introduction                                              | 1      |

| 1.1.      | More than Moore                                             | 2      |

| 1.2.      | Moore to Bell                                               | 4      |

| 1.3.      | Internet of Things                                          | 5      |

| 1.4.      | Applications of Phase-Locked Loops                          | 9      |

| 1.5.      | All-Digital PLLs to Synthesized PLLs                        | 13     |

| 1.6.      | PLL Design for Internet of Things                           | 14     |

| 1.7.      | Thesis Contributions                                        | 16     |

| Chapter   | 2 A Design Methodology for Accelerated ADPLL Design         | 19     |

| 2.1.      | Analog vs. Digital Design Flow                              | 20     |

| 2.2.      | Why isn't Analog Synthesis a Reality Yet?                   | 24     |

| 2.3.      | A Brief Survey of Analog Synthesis                          | 26     |

| 2.4.      | Current State of Commercially Available Analog Layout Tools | 30     |

| 2.5.    | A New Analog Synthesis Philosophy                      | 31 |

|---------|--------------------------------------------------------|----|

| 2.6.    | The Design Methodology                                 | 33 |

| 2.7.    | Conclusion                                             | 37 |

| Chapter | 3 Enhancing DCO Resolution                             | 40 |

| 3.1.    | Assumptions & Specifications                           | 40 |

| 3.2.    | Tuning Delay with a Switched Capacitor                 | 42 |

| 3.3.    | Tuning Delay with Parallel Buffers                     | 46 |

| 3.4.    | Pulse Width Modulated Delay/Frequency Tuning           | 49 |

| 3.5.    | Resolution using PWM Technique                         | 54 |

| 3.6.    | Drawbacks of PWM-based Frequency Tuning                | 56 |

| 3.7.    | Measured Results                                       | 57 |

| 3.8.    | Conclusion                                             | 58 |

| Chapter | 4 An Automatically Placed and Routed 400-460 MHz ADPLL | 60 |

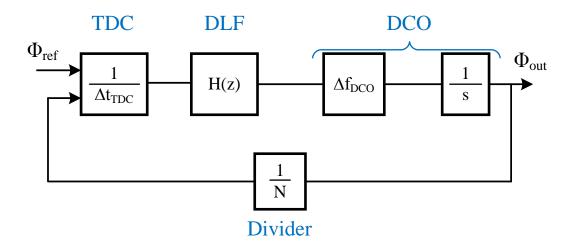

| 4.1.    | Sub-sampling ADPLL Model                               | 62 |

| 4.2.    | Overall Architecture of the ADPLL                      | 67 |

| 4.3.    | Sub-block Design Details                               | 68 |

| 4.4.    | DCO Resolution Enhancement Technique                   | 73 |

| 4.5.    | Design Methodology                                     | 73 |

| 4.6.    | Measurement Results                                    | 74 |

| 4.7.    | Conclusion                                             | 77 |

| Chapte  | r 5 An Ultra-Low Power Near-Threshold Clock Generator | . 79 |

|---------|-------------------------------------------------------|------|

| 5.1.    | Clock Generator Architecture                          | . 80 |

| 5.2.    | Near Threshold Design for Ultra Low Power             | . 83 |

| 5.3.    | Sub-block Design Details                              | . 85 |

| 5.4.    | Measurement Results                                   | . 86 |

| 5.5.    | Conclusion                                            | . 92 |

| Chapte  | r 6 Conclusions                                       | . 93 |

| 6.1.    | Thesis Summary & Conclusions                          | . 93 |

| 6.2.    | Future Work                                           | . 94 |

| REFEREN | ICES                                                  | . 96 |

# LIST OF FIGURES

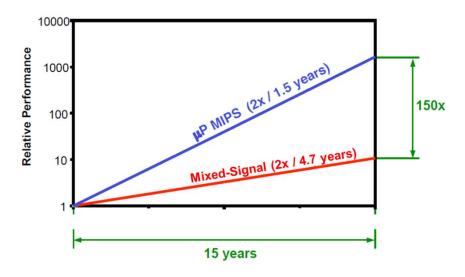

| Figure 1.1: Analog vs. Digital scaling [4]                                | 3  |

|---------------------------------------------------------------------------|----|

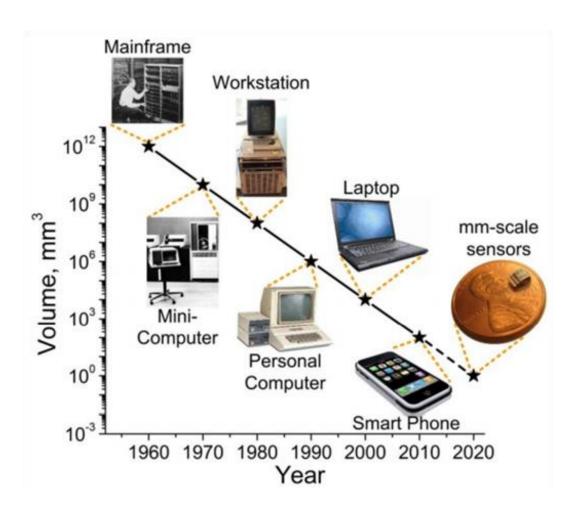

| Figure 1.2: Bell's Law [7]                                                | 5  |

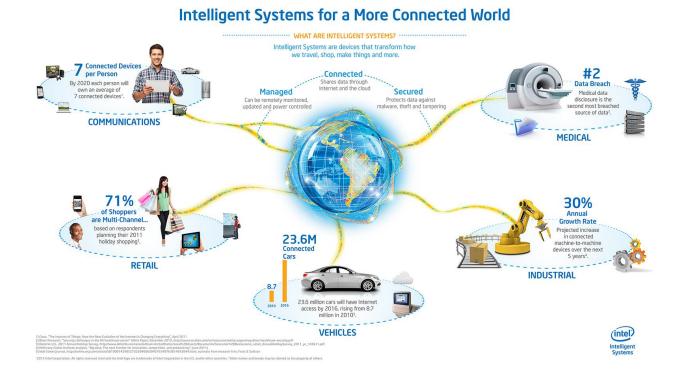

| Figure 1.3: Internet of Things, Intel's view [9]                          | 6  |

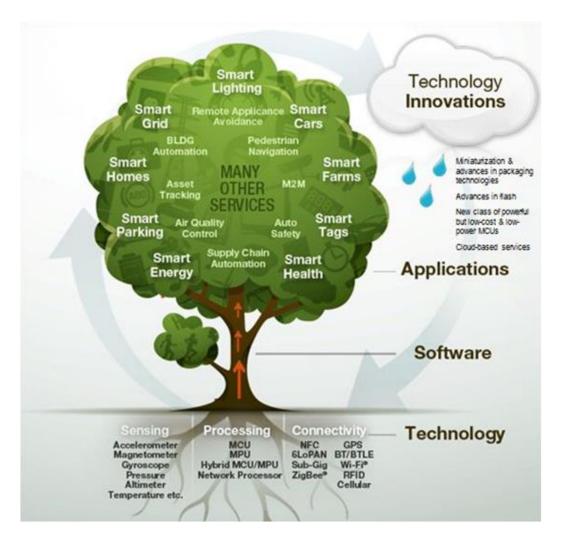

| Figure 1.4: Internet of Things ecosystem [12]                             | 8  |

| Figure 1.5: Typical PLL-based clock generator                             | 9  |

| Figure 1.6: A typical clock and data recovery system                      | 10 |

| Figure 1.7: A PLL based demodulator                                       | 11 |

| Figure 1.8: A PLL-based demodulator                                       | 11 |

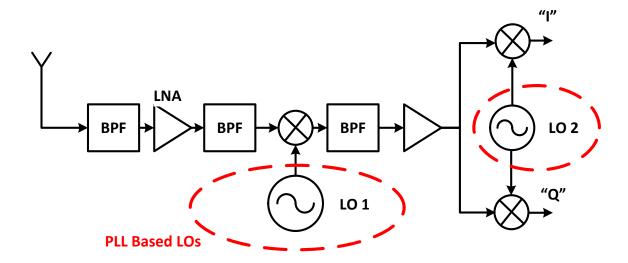

| Figure 1.9: A heterodyne receiver requires a PLL to generate LO           | 12 |

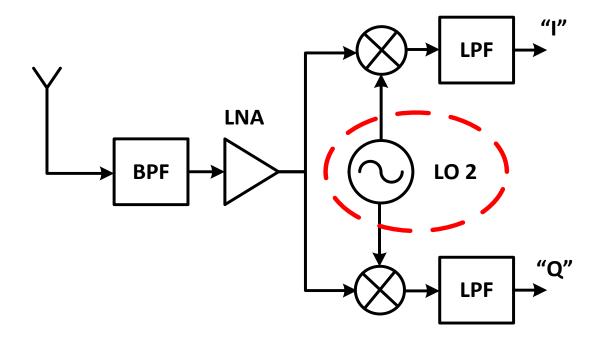

| Figure 1.10: A direct conversion receiver with a PLL based LO             | 13 |

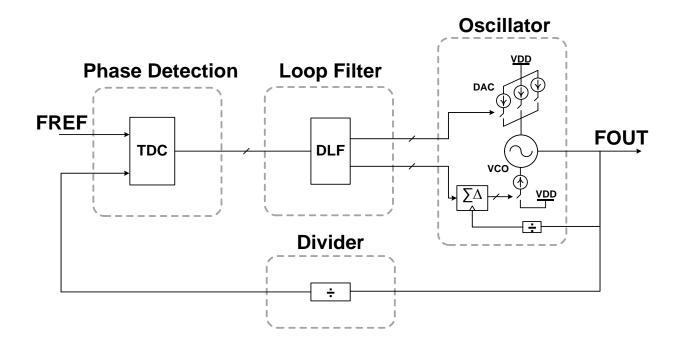

| Figure 1.11: Typical ADPLL architecture                                   | 14 |

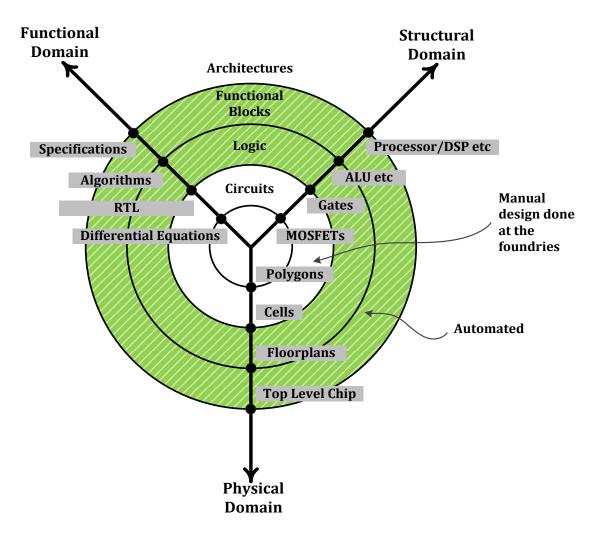

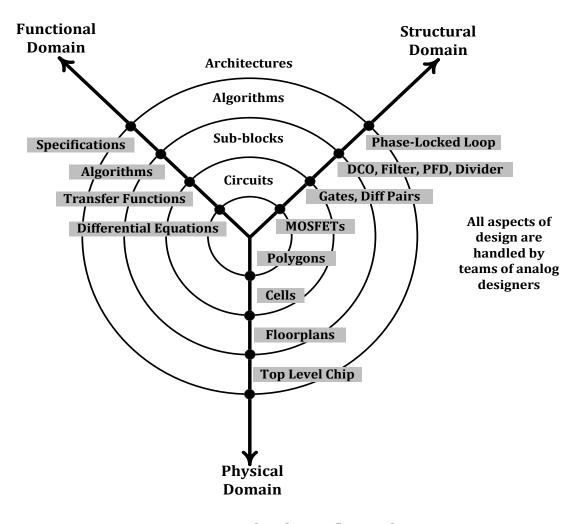

| Figure 2.1: Gajski's chart of general purpose VSLI design [25]            | 21 |

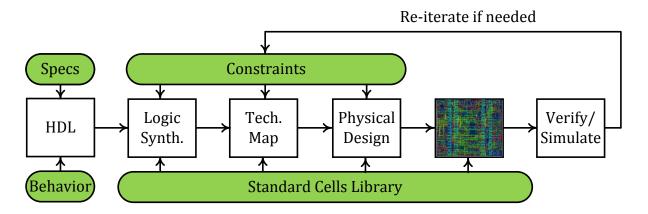

| Figure 2.2: Linear representation of digital design flow [26][27]         | 22 |

| Figure 2.3: Analog design flow Y-chart                                    | 23 |

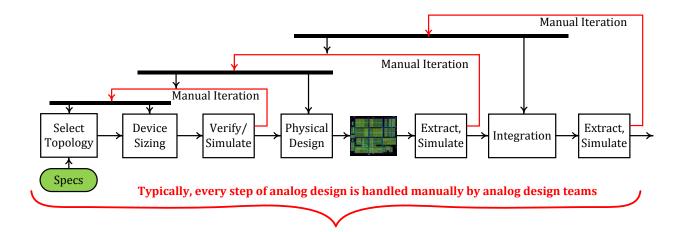

| Figure 2.4: Typical progression of analog system design [30]              | 24 |

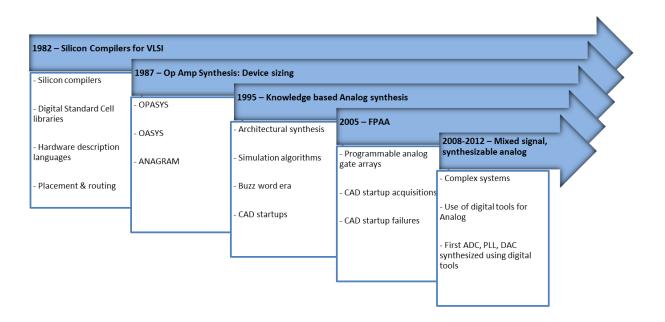

| Figure 2.5: History of analog synthesis summarized                        | 26 |

| Figure 2.6: Current state of commercial digital vs. analog tools [53][57] | 29 |

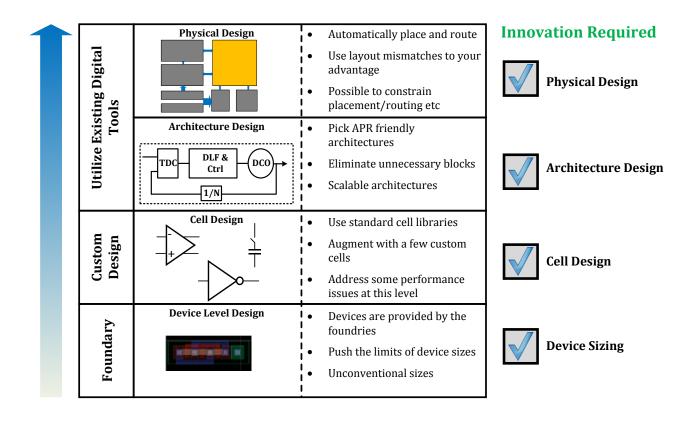

| Figure 2.7: Analog Circuit Design Innovation Chain                        | 33 |

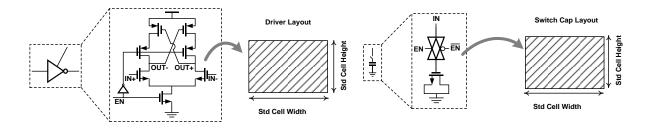

| Figure 2.8: Cell design step [33]                                         | 34 |

| Figure 2.9: Illustration of Macro Design                                  | 34 |

| Figure 2.10: Verification and iteration step                              | 35 |

| Figure 2.11: Top level design and integration                                      | 36 |

|------------------------------------------------------------------------------------|----|

| Figure 2.12: Top level physical design                                             | 37 |

| Figure 2.13: Analog design Y-chart using the proposed design methodology           | 38 |

| Figure 2.14: Analog design representation using the proposed design methodology    | 39 |

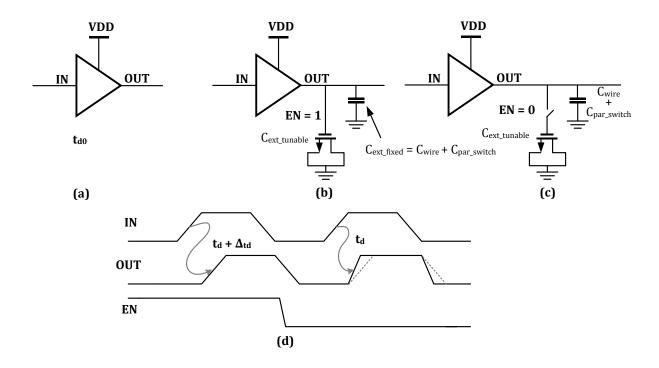

| Figure 3.1: (a) Unloaded buffer (b) Switch capacitor on (c) off (d) delay waveform | 43 |

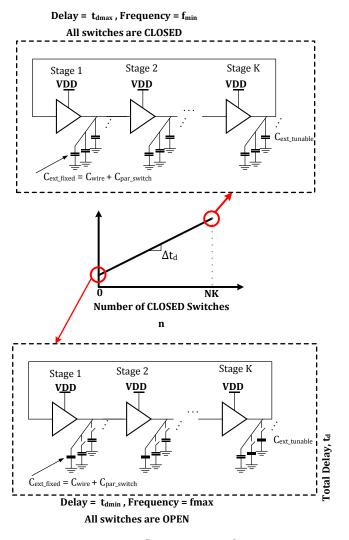

| Figure 3.2: Maximum and minimum frequency scenarios                                | 44 |

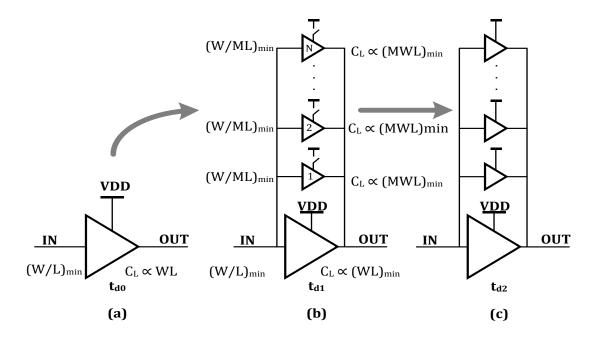

| Figure 3.3: Tuning delay with parallel buffers                                     | 47 |

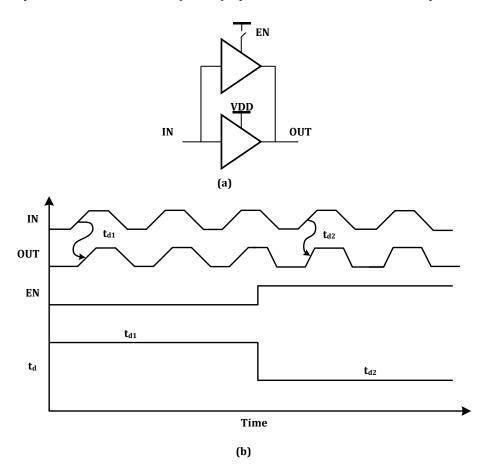

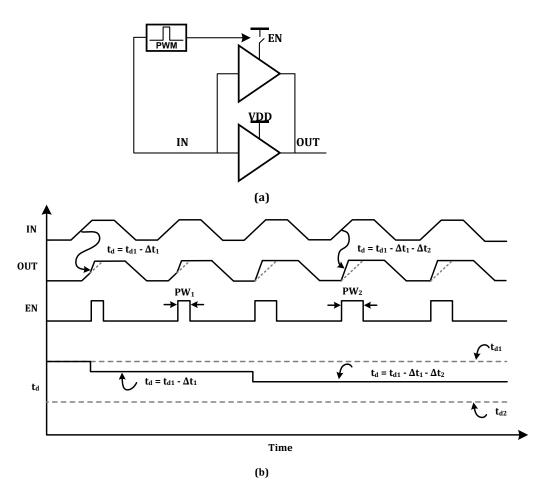

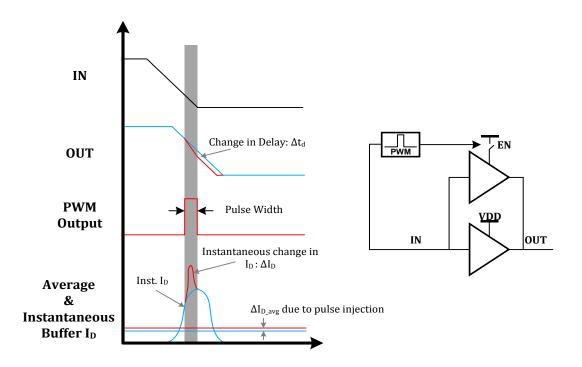

| Figure 3.4: Tuning delay by turning on/off a buffer for the entirety of the period | 50 |

| Figure 3.5: Delay as a function of pulse width                                     | 51 |

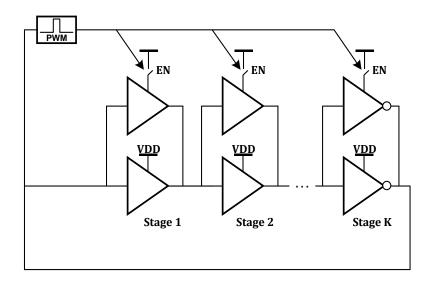

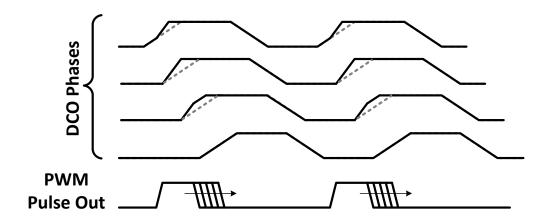

| Figure 3.6: Pulse Width Modulator Based Frequency Tuning in an RDCO                | 52 |

| Figure 3.7: Pulse width modulator in a ring oscillator                             | 52 |

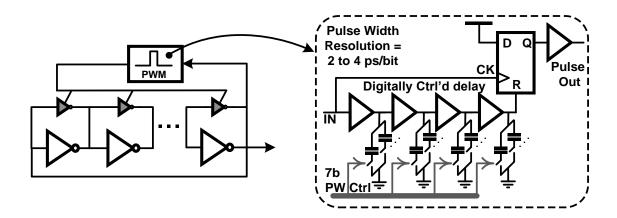

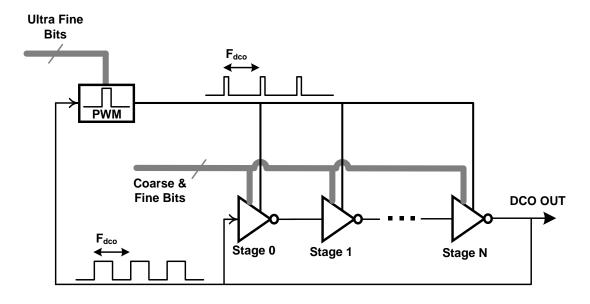

| Figure 3.8: The pulse width modulator architecture in a ring DCO                   | 53 |

| Figure 3.9: Delay resolution as a function of the pulse width                      | 55 |

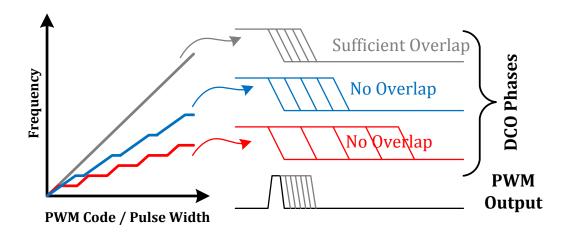

| Figure 3.10: Different scenarios of PWM-based frequency tuning                     | 57 |

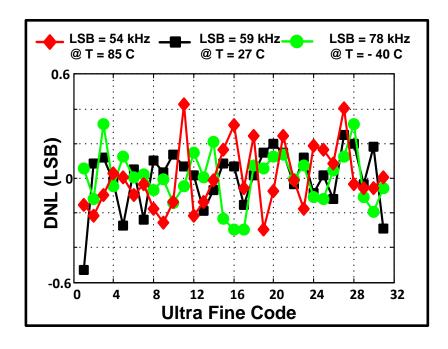

| Figure 3.11: Differential non-linearity of the PWM frequency control               | 57 |

| Figure 4.1: Typical ADPLL model                                                    | 62 |

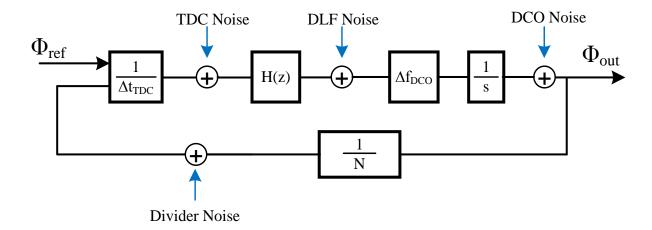

| Figure 4.2: ADPLL model with phase noise contributors                              | 63 |

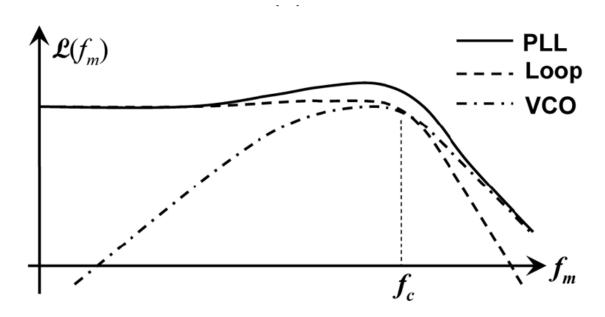

| Figure 4.3: Breakdown of two dominant phase noise sources[77]                      | 64 |

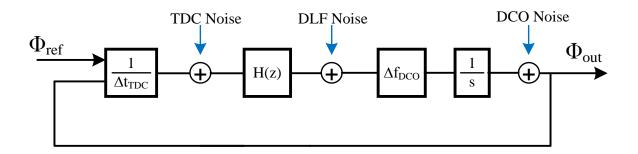

| Figure 4.4: Noise model of a dividerless ADPLL                                     | 65 |

| Figure 4.5: The overall ADPLL architecture                                         | 68 |

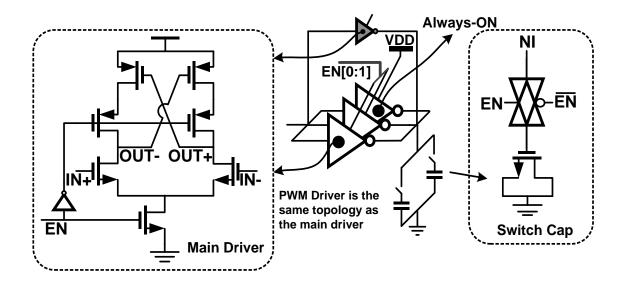

| Figure 4.6: Ring DCO circuit diagram                                               | 70 |

| Figure 4.7: Details of one DCO stage                                               | 70 |

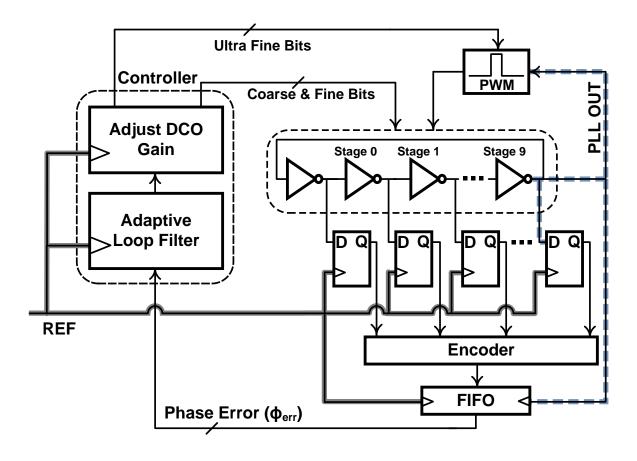

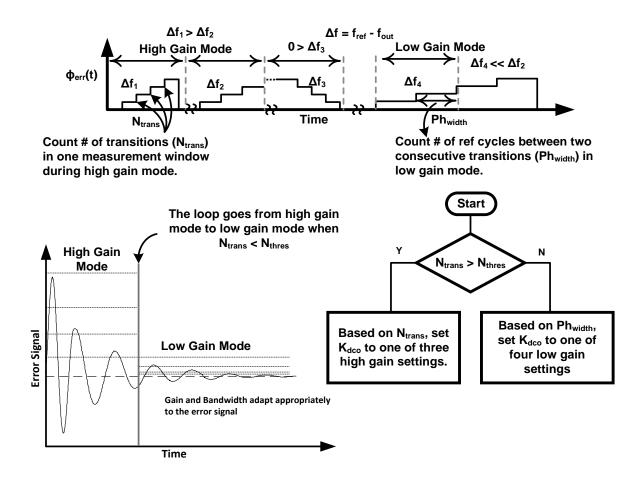

| Figure 4.8: Adaptive Loop Filtering Technique                                      | 72 |

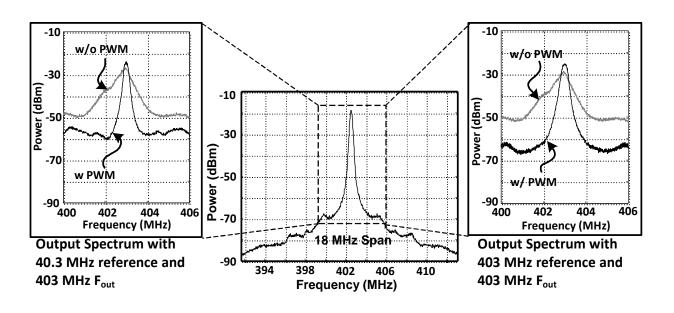

| Figure 4.9: The output spectrum of the PLL with and without the PWM      | 75 |

|--------------------------------------------------------------------------|----|

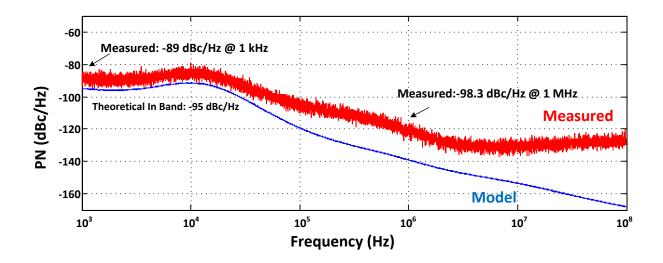

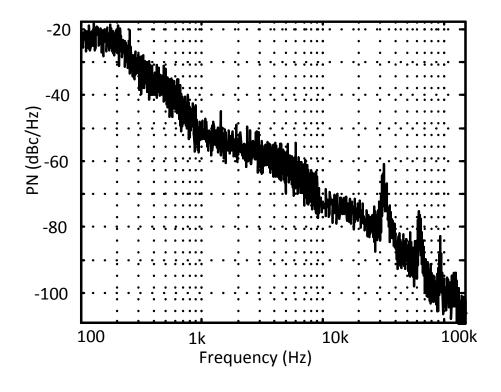

| Figure 4.10: Phase noise of the ADPLL with 403MHz Fref                   | 75 |

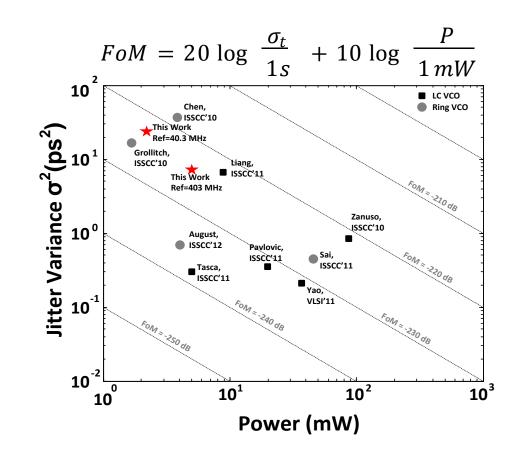

| Figure 4.11: Figure of Merit Comparison                                  | 76 |

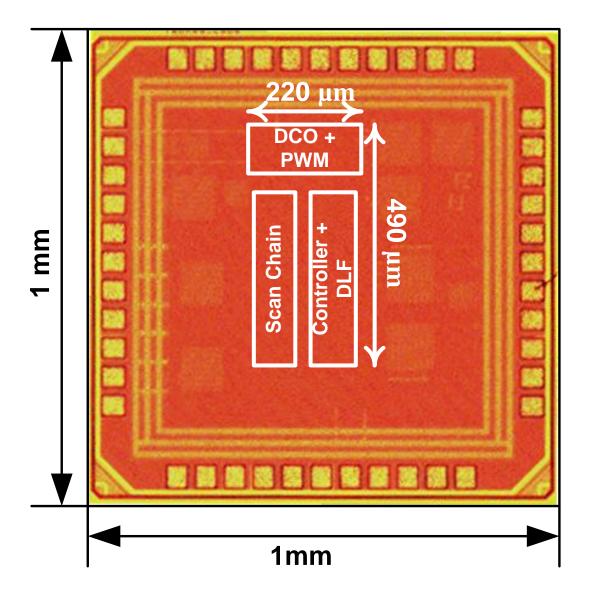

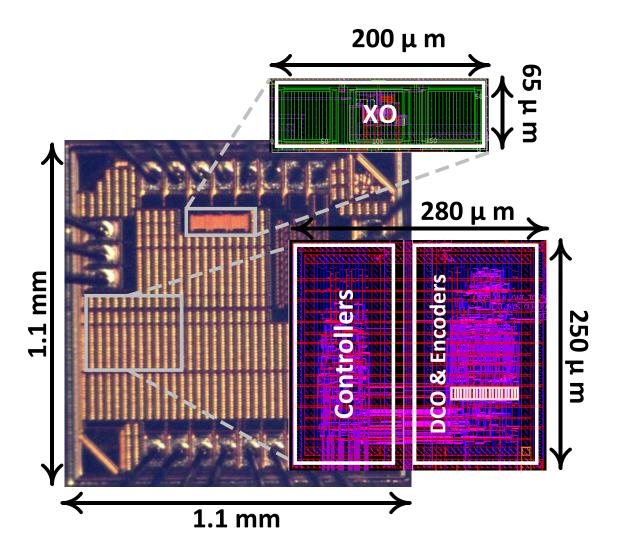

| Figure 4.12: The die photo of the ADPLL                                  | 77 |

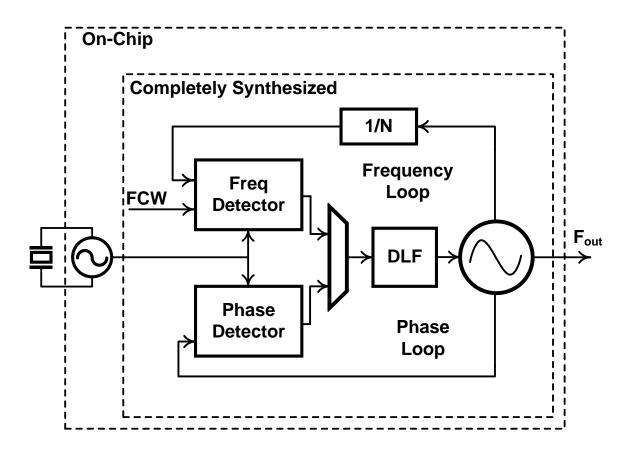

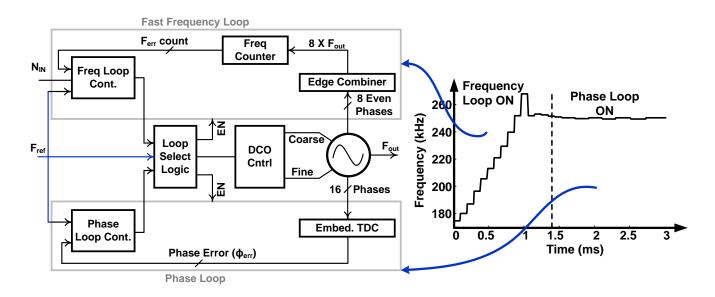

| Figure 5.1: The overall architecture of the clock generator              | 81 |

| Figure 5.2: Details of frequency and phase loops and the step response   | 82 |

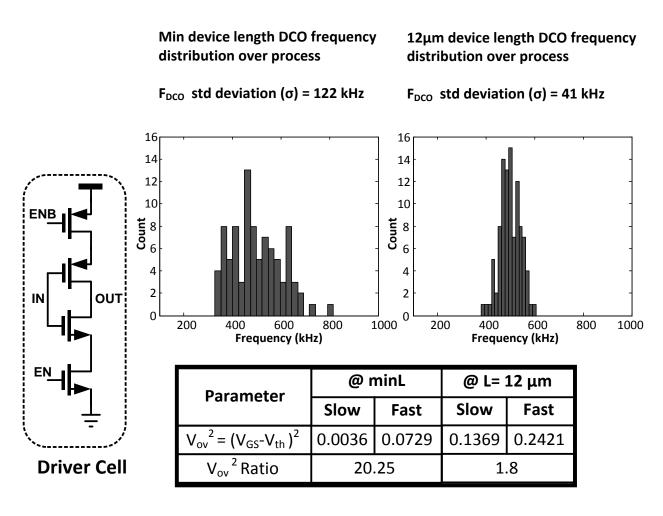

| Figure 5.3: Effect of increasing transistor length on the PVT variations | 84 |

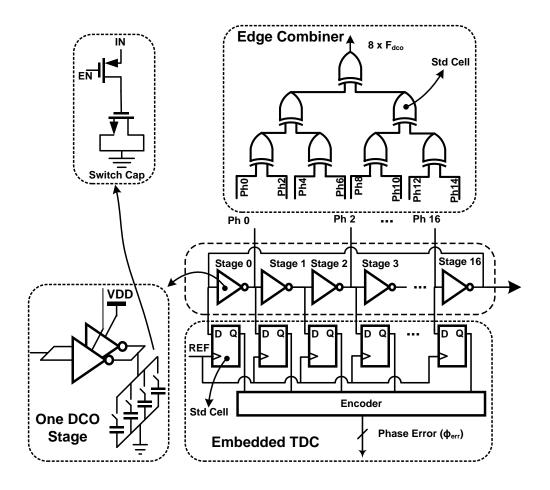

| Figure 5.4: Details of DCO, TDC and the edge combiner                    | 85 |

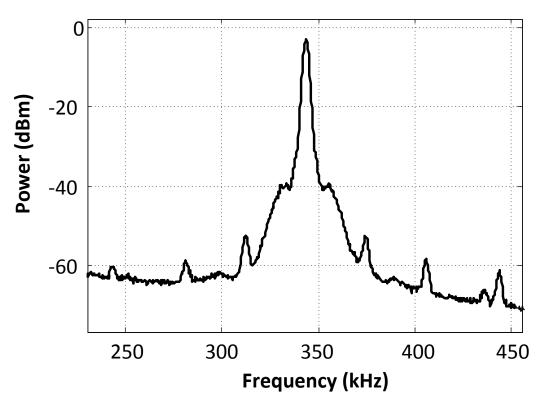

| Figure 5.5: Output spectrum of the clock generator for N = 11            | 86 |

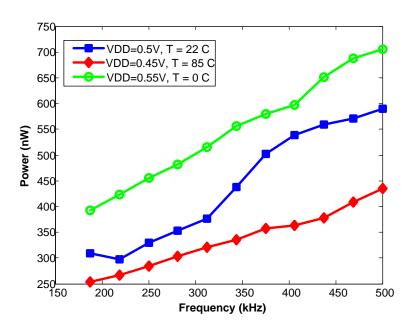

| Figure 5.6: Power vs. frequency for the entire frequency range           | 87 |

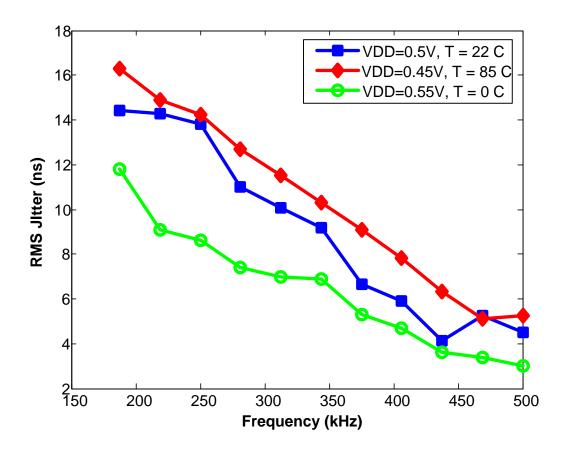

| Figure 5.7: RMS Jitter vs. Frequency of the Clock Generator              | 88 |

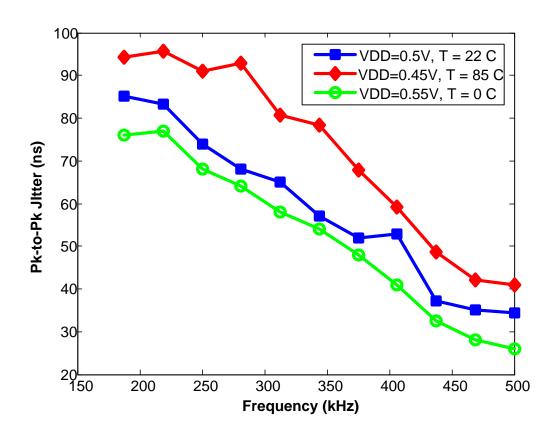

| Figure 5.8: Peak-to-Peak Jitter vs. Frequency of the Clock Generator     | 89 |

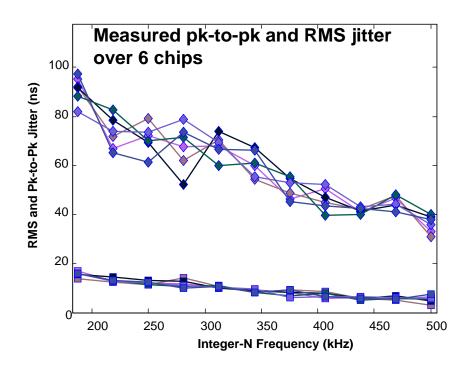

| Figure 5.9: Pk-Pk and RMS jitter measured for six chips                  | 90 |

| Figure 5.10: Clock Generator phase noise with N = 11                     | 90 |

| Figure 5.11: The die photo of the CKGEN                                  | 92 |

# LIST OF TABLES

| Table 2.1: Commercial Layout Tools vs. Proposed Design Methodology   | 31 |

|----------------------------------------------------------------------|----|

| Table 3.1: Assumptions and design specifications                     | 41 |

| Table 3.2: Power comparison of the frequency/delay tuning techniques | 59 |

| Table 3.3: Frequency resolution comparison                           | 59 |

| Table 4.1: Performance comparison with state-of-the-art work         | 76 |

| Table 5.1: Comparison of the CKGEN to the state-of-the-art work      | 91 |

# **ABSTRACT**

Driven by advancement in integrated circuit design and fabrication technologies, electronic systems have become ubiquitous. This has been enabled powerful digital design tools that continue to shrink the design cost, time-to-market, and the size of digital circuits. Similarly, the manufacturing cost has been constantly declining for the last four decades due to CMOS scaling. However, analog systems have struggled to keep up with the unprecedented scaling of digital circuits. Even today, the majority of the analog circuit blocks are custom designed, do not scale well, and require long design cycles.

This thesis analyzes the factors responsible for the slow scaling of analog blocks, and presents a new design methodology that bridges the gap between traditional custom analog design and the modern digital design. The proposed methodology is utilized in implementation of the frequency generation circuits – traditionally considered analog systems. Prototypes covering two different applications were implemented. The first synthesized all-digital phase-locked loop was designed for 400-460 MHz MedRadio applications and was fabricated in a 65 nm CMOS process. The second prototype is an ultralow power, near-threshold 187-500 kHz clock generator for energy harvesting/autonomous applications. Finally, a digitally-controlled oscillator frequency resolution enhancement technique is presented which allows reduction of quantization noise in ADPLLs without introducing spurs.

# Chapter 1

# Introduction

In the summer of 1948, a tiny electronic device called a transistor was announced at the headquarters of Bell Labs in New York at a press conference. The invention failed to create a buzz and barely received any attention from the local newspaper, the New York Times [1]. Fast forward to October 2013, and the entire world tuned in to watch the launch of the latest generation of the iPhone. The event was streamed live on the internet, and millions of people were able to watch the unveiling of the latest Apple gadgets in the comfort of their homes across the globe. The entire infrastructure that allows such incredible connectedness and the sophistication of electronic gadgets is built on what's called integrated circuits. Even today the smallest unit of electronic circuits is a transistor - precisely the invention that gained little attention from the general public 65 years earlier. Integrated circuits have enabled a stunning transformation of every aspect of human life. They have turned room sized computers and bulky furniture sized radios to hand held devices. The electronic revolution is driven by the unprecedented ability to scale and miniaturize transistors at an incredible pace as encapsulated by Moore's law [2].

## 1.1. More than Moore

In 1965, Gordon Moore suggested, based on empirical data that the *number of transistors in integrated circuits doubles every two years*. This was later modified by David House to state the chip performance, facilitated by an increased number of transistors and the ability to design that quicker, doubles every 18 months [2]. The semiconductor industry has remarkably followed Moore's law. The deflationary effect of Moore's law has played a crucial role in wide spread proliferation of electronics in every aspect of our lives. The tremendous scale of this deflationary effect can be understood by comparing the cost per transistor. For example, the average price of an integrated transistor was \$5.52 in 1954, and it has dropped to about one billionth of a dollar in 2013 [3]. However, the process scaling is running into some fundamental physical limits, and the speed of Moore's law is predicted to slow down by 2020.

The extreme scaling suggested by Moore's law works well for microprocessors, and memories, but not for analog components which interface with the external world. Even "all-digital" systems require some sort of analog components on-chip [3]. For example, an all-digital microprocessor requires a clock generator as well as a power management system, and both of these systems are inherently analog in nature; therefore, do not scale according to Moore's law. However, these analog components add significant value for the consumers. A microprocessor cannot function without power management or the clock generator. As we know, analog circuits scale significantly slower than their digital counterparts. Some empirical evidence shows that the analog circuits double in performance approximately every five years, while digital circuits double in performance every 18 months [4]. Therefore, significant innovation at the block and architectural levels along with a paradigm

shift in the design procedure for analog circuits must take place in order to keep up with the growing need for higher performance at a lower cost in consumer electronics.

Figure 1.1: Analog vs. Digital scaling [4]

Figure 1.1 shows how the digital domain has followed Moore's law. However, the analog domain has scaled at a much slower pace. A number of reasons can be attributed to the slow scaling of analog circuits [5]:

- Scaling leads to smaller transistors, which have worse control over their current due

to second order short channel effects that appear in deep sub-micron technologies.

This can be compensated with more sophisticated circuits and calibration techniques

which lead to larger area.

- Scaling leads to reduced supply voltage, limiting headroom as well as the dynamic range of various analog blocks. This leads to exacerbated non-linearities in circuits as well as lower voltage operations require a proportionally lower noise levels.

- Passive components such as capacitors and inductors are often required in analog blocks, which have not scaled with process.

Therefore, a strong emphasis has been placed on developing digitally-assisted or all-digital architectures for traditionally analog components. Regardless of relatively slower scaling of analog components, new classes of computing are appearing at a rapid pace as described by Bell's law [4][6].

## 1.2. Moore to Bell

Bell's Law states that roughly every decade a new, lower priced computer class forms based on a new programming platform, network, and interface resulting in new usage and the establishment of a new industry. This has been proven true since the 1960s when the mainframe computer used to be the size of a room then came the era of work station computers in the 1970s. However, computers were still considered a luxury and were reserved for educational and research purposes, which changed with the appearance of Apple Computers and the PC, followed by laptops and now smartphones. This trend has continued to this day, and there are no signs of stopping. As illustrated by Figure 1.2, Bell's Law for the next class of computing seems to be becoming true. Several millimeters scaled computing systems have already been reported [7]. This new class of ubiquitous computing will give birth to what's dubbed as Internet of Things. The University of Michigan is leading the way with its millimeter cubed project as well as its strong research in ultra-low power near threshold digital and analog/RF circuits[7].

Figure 1.2: Bell's Law [7]

# 1.3. Internet of Things

The Internet of Things is loosely defined as virtually every object can have the ability to sense, process and communicate information [8]. It has been predicted by many major technological players that the Internet of Things will penetrate every aspect of human life within the current decade. As shown in Figure 1.3, the ability to sense, process and communicate is already affecting our experience of shopping, transportation, communication and health care. It has been repeatedly predicted, as listed below, that the

trend of an increased number of connected devices will only continue as the technology progresses to facilitate wide spread proliferation.

- Intel predictions 50 billion connected devices by 2020 [9].

- Cisco predicts 1 trillion connected devices by 2025 [10].

- Bosch predicts that the average person will carry up to 1000 sensors by 2025 [11].

Figure 1.3: Internet of Things, Intel's view [9]

Upon closer observation, one can argue that the technical capabilities required to make the IoT a reality already exist. For example, technologies such as wireless communication, embedded processing and sensing already exist. Then why hasn't the IoT become a reality yet? Though the required technologies exist, significant innovation is still required in order to make the IoT feasible. Figure 1.4 shows the ecosystem and how various different aspects of technology will interact to make up the overall IoT environment. More efficient and cost effective applications, data management and software are required. However, the real bottle neck is still the hardware that cannot yet support the wide spread use of various things due a number of reasons [12]:

- Power consumption is too prohibitive in various different components of a

computing system. Long battery life or energy autonomy will be required for IoT

since changing batteries on 1 trillion devices every day will be an impossible task to

achieve.

- Electronics **cost** in its current state is too high. The only way to make 1000 devices per person a reality would be if the ICs in these devices are prices at cents per unit.

- The current state of electronics is too bulky, and significant efforts must be focused

on miniaturization of existing systems as well as development of new small form

factor systems.

- Quicker design and manufacturing cycles will be required in order to meet the predicted high demand for the connected devices.

Figure 1.4: Internet of Things ecosystem [12]

One of the key contributions of the presented research is the development of a design methodology as well as innovative architectures to address the issues that are stalling the realization of the Internet of Things. One of the major analog components that can be found virtually in every electronic system is a frequency generation circuit. Frequency generation circuits serve as the heartbeat of every electronic system, and are often based on phase-locked loops. An overview of the phase-locked loop (PLL) applications is given in the following section.

# 1.4. Applications of Phase-Locked Loops

There are widespread applications of frequency generation circuits. As mentioned earlier, they serve as the heartbeat of electronic systems. They could be used as clock generators for embedded processing applications or local oscillator (LO) generation for radios, for modulation and demodulation. Some examples of applications are given below.

## Clock generator:

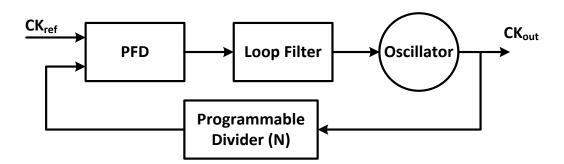

One of most wide spread applications of frequency generation circuits is for clock generation in digital systems. Typically, the clock generators consist of a reference signal, and an on-chip programmable frequency multiplier block [13]. The frequency multiplier block could either be a phase-locked loop, frequency-locked loop or delay-locked loop based system. The block diagram of a typical PLL-based clock generator is shown in Figure 1.5 below.

Figure 1.5: Typical PLL-based clock generator

This particular clock generator multiplies the frequency by the divider ratio *N*. Therefore, the output clock frequency is *N* times that of the reference clock.

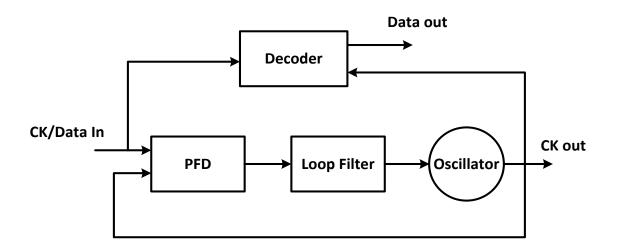

#### Clock and Data Recovery:

In many interconnect applications such as USB and VGA, the data is transmitted without an accompanying timing reference signal. For example, in optical communication, information only travels on a single fiber optics channel. However, the receiver must process this data synchronous to some timing reference. Therefore, the receiver must not only recover information but also the clock signal from the received data. Most clock and data recovery systems are based on some sort of frequency generation/phase-locked loop [13]. Figure 1.6 shows a simple block diagram of a typical clock and data recovery circuit.

Figure 1.6: A typical clock and data recovery system

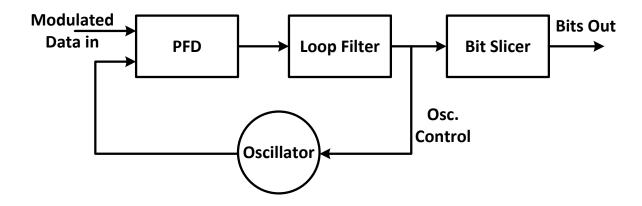

## **Modulation and Demodulation:**

When a phase-locked loop is in the lock state, the control of the oscillator (either a voltage or binary number) is proportional to the output frequency. Therefore, by observing the oscillator control, one can demodulate either phase or frequency modulated data. Figure 1.7 shows a typical block diagram of a PLL-based demodulator.

Figure 1.7: A PLL based demodulator

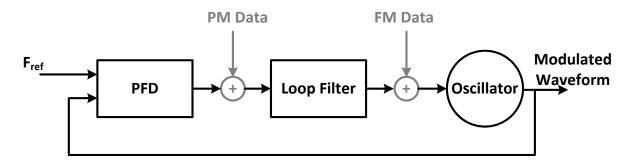

Similarly, the PLL can also be used as a modulator, as illustrated in the Figure 1.8 below.

Figure 1.8: A PLL-based demodulator

Phase modulated bits can be fed into the output of the phase frequency detector (PFD), and the output of the oscillator appears to be phase modulated. Similarly, if frequency modulation is required, the data can be directly fed into the control word or control voltage of the oscillator [14].

# Local Oscillator Generation for Receivers:

Almost all receiver architectures require a local oscillator (LO) that is used to down convert the signal to either low-IF or baseband frequency which then is digitized and processed in the digital domain. A typical LO generator based on a PLL is often one of the most challenging blocks to design in a receiver. Figure 1.9 and Figure 1.10 show typical architectures of both low IF heterodyne and direct conversion homodyne receivers. LOs are always the crucial part of the receivers, and they are often PLL based [14].

Figure 1.9: A heterodyne receiver requires a PLL to generate LO

Figure 1.10: A direct conversion receiver with a PLL based LO

Based on the applications discussed above, it is clear that addressing the previously mentioned issues of analog scaling for frequency generation circuits would be a significant contribution towards making IoT a reality [14].

# 1.5. All-Digital PLLs to Synthesized PLLs

All-digital phase locked loops (ADPLLs) have been the focus of major research efforts since the 90s since they eliminate the need for bulky loop filters and offer increased flexibility and configurability [13]-[19]. However, the overall design of ADPLLs has barely changed since their inception. Figure 1.11 shows a block diagram of a typical ADPLL which consists of a time-to-digital converter (TDC), a digital loop filter (DLF), a frequency divider and a voltage controlled oscillator (VCO) which is typically controlled by a digital to analog converter (DAC) [20].

Figure 1.11: Typical ADPLL architecture

Regardless of its classification as an all-digital PLL, a significant amount of analog design goes into the VCO, DAC, and often the divider and TDC. These blocks are all-analog blocks and suffer from the issues highlighted in section 1.1 as process scales, and therefore these ADPLLs do not scale as well as the digital circuits. The next logical step is to implement the ADPLLs using traditional digital design methodologies, with ideally full-swing signals (like digital CMOS signals). This will allow faster design cycles as well as the potential to take advantage of process scaling.

# 1.6. PLL Design for Internet of Things

From discussions in prior sections, it can be inferred that PLLs designed for IoT applications will be required to address the following issues:

#### Energy constraint

IoT applications will require either long battery life or energy autonomy. This problem can be addressed from two directions: (i) improving the energy source or (ii) reducing energy consumption. Improving the energy source or batteries is outside of the scope of this research work, and significant research efforts are being focused on power harvesting [16]-[17]. However, power harvesting systems produce very low voltage levels and cannot source large currents that are often required in analog components. Achieving robust operation in voltage- and energy-constrained environments is a major requirement for IoT electronics.

#### Size

The size of PLLs for IoT applications must be as small as possible because the weight and size of the 10s of connected devices (as predicted) could become prohibitive.

## Cost

Cost will play an important role in IoT development. Therefore, PLLs for IoT applications must be as cost effective as possible. All-digital PLL architectures that occupy small silicon area, and do not require external components or expensive bias generation circuitry will be the key.

## Accelerated Design

With 1 trillion devices deployed, an unprecedented demand will be placed on new connected devices. Therefore, the ADPLLs designed for IoT must have short design cycles in order to meet the market demand. A design methodology was developed as part of this project to allow synthesis of ADPLLs.

## 1.7. Thesis Contributions

This thesis builds upon research conducted by Dr. Youngmin Park [18]. Dr. Park's work was mainly focused on utilizing digital standard cells only to implement traditionally analog components. He successfully implemented an ultra-wide band transmitter, time-to-digital converters, and all-digital phase-locked loop [18]. However, this research differs from Dr. Park's contributions in the following ways:

## 1. ADPLL Performance

This thesis is only concerned with ADPLLs, and explored implementations for ADPLLs for various applications. Dr. Park proved the merits of cell-based design for analog/RF blocks using only digital standard cells. Although the design time can be significantly shortened with utilizing digital standard cells only, it's extremely challenging to match the performance of custom designed ADPPLs. Therefore, extensive calibration techniques are required.

This thesis is focused on bridging the gap between performance and automated cell-based design. Thereby implementing ADPLLs efficiently for high performance applications.

#### 2. ADPLL Architectures

This research also proposes new ADPLL architectures as a means to reduce power consumption, and overcome some of the non-idealities of automated layout. These architectures remove the divider, and use an embedded TDC architecture – resulting in significant power reductions.

## 3. Low Voltage Applications

This research also extends the cell-based design approach to low-voltage and ultra-low power applications. This was not previously explored in Dr. Park's research.

This thesis explores innovative architectures for ADPLLs, and design methodologies to accelerate design by utilizing existing digital tools, to implement low power PLLs without compromising the performance. The contributions are briefly described as follows.

## 1. Design Methodology for Synthesizable ADPLLs

A new design methodology for accelerated design of PLLs was developed in this project. This design methodology utilizes existing digital and analog design flows to implement ADPLLs. The ADPLL designs are portable across process nodes since they are represented by a hardware description language (HDL). Further details of the methodology are provided in Chapter 2.

#### 2. Synthesizable 400-460 MHz ADPLL

Secondly, a novel ADPLL architecture that was implemented entirely using digital design flows is presented. This ADPLL was developed for a 400-460MHz frequency range, and

for wireless body area network applications. Details of this ADPLL, including a number of architectural contributions, are discussed in Chapter 4 .

## 3. Synthesizable Ultra-low Power Clock Generator

In order to prove feasibility of the new design approach in a variety of applications, a near-threshold, ultra-low power clock generator for energy autonomous/harvesting application was designed and implemented. This system is the smallest known clock generator in sub-MHz frequency ranges. Further details are provided in Chapter 5.

## 4. DCO Resolution Enhancement Technique

Lastly, a novel digitally controlled oscillator resolution enhancement technique was developed. This technique allows frequency tuning in DCOs with small steps without a sigma-delta modulator, and do not introduce any undesirable spurious tones at the output of the ADPLL. The circuits that make up this technique can be entirely implemented using digital standard cells, and the digital design flows. This technique linearizes the resolution-power tradeoff which is a hyperbolic relationship in traditional frequency tuning approaches. Further details of this frequency tuning and resolution enhancement technique are discussed in Chapter 3 .

# Chapter 2

# A Design Methodology for Accelerated ADPLL Design

In the 1970s and early 1980s, any CAD research focused on analog circuit design optimization and automation was considered antiquated and too slow to adjust to the sweeping wave of all things digital. Traditional analog functions were rapidly being implemented with digital circuits, and analog CAD research was considered intellectually insignificant [21]. However, the digital design methodologies progressed at an unprecedented pace, and it became possible to perform logic-to-gate mapping and automatically generate layout from standard cell libraries for complex digital systems such as microprocessors by mid 1980s. This provided a reliable and safe path for designers to quickly go from an idea to silicon implementation for a large array of digital systems [22].

The emergence of application specific integrated circuits (ASICs) in the late 80s exposed the lack of analog synthesis and layout tools which kick-started a new wave of research efforts into analog circuit design tools. In particular, many of the leading integrated circuits research groups around the world began to explore the possibilities of synthesizing analog circuits the same way digital circuits are done. These analog CAD research efforts have resulted in various fragmented analog design assistance tools, many of which have been absorbed by popular CAD tools of today, such as Cadence and Synopsys. However, even after thirty years of research, analog design is still considered "black magic", and the dream of

analog synthesis has yet to be realized [23]. In this chapter, current analog and digital design methodologies are briefly contrasted, various factors that have hindered the realization of an analog synthesis tool are discussed, and finally a design methodology that significantly accelerates design of some traditionally analog systems is proposed.

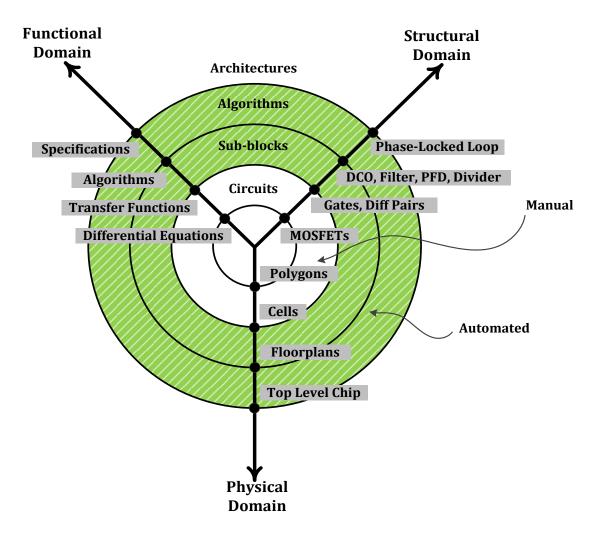

# 2.1. Analog vs. Digital Design Flow

In order to do a fair comparison of the current state of analog design with digital design flows, Gajski's chart (or the Y-chart) will be used. Gajski's chart was proposed in 1983 to illustrate various steps and levels of abstraction required for VLSI design [24]. Though it was proposed for digital systems only, it will be adapted for analog circuit design for illustration purposes. The main goal of this chart is to map out the various hierarchical steps that are required in order to effectively solve complex design problems. Figure 2.1 shows the Y-chart for a typical digital system design of present day. The Y-chart consists of three different domains: functional domain, structural domain and physical design. Digital system design begins with functional/behavioral specifications, and after some initial mathematical modeling, the design moves to the structural domain through some mapping method or tool, and finally the design concludes in the physical domain. In addition to the design domains, Gajski also highlighted that there are various layers of abstraction in digital system design – depicted by concentric circles in the Y-chart. Design of complex and large digital systems can be simplified significantly as highly specialized designers are only responsible for one layer of abstraction [25]. For example, a digital systems designer can use well optimized cells for their designs without diving into the details of device sizing etc. Therefore, a top down design process that starts with system level modelling coupled with specialized transistor and cell

level design can significantly reduce the design complexity. This also opened the possibilities of automating a large portion of digital design. The shaded area in Figure 2.1 shows the portion of design that's done with CAD tools today. However, transistor and cell level design still requires significant human capital. Typically, foundries provide cells that have been optimized for performance, and from a digital designer's point of view, the design flow is completely automated.

Figure 2.1: Gajski's chart of general purpose VSLI design [25]

Figure 2.2: Linear representation of digital design flow [26][27]

A more linear representation of today's digital design flow is given in Figure 2.2. The entire process of digital design past the cell design is automated. A digital designer's job is to describe the desired circuit behavior using a hardware description language (HDL) and define the constraints which are typically determined by the performance requirements of the design. The next step after HDL entry is to use the standard cells library, and logic synthesis tools such as Synopsys Design Compiler to convert behavior description to a structural logic description. The final step prior to final verification is the physical design. Current physical design tools have the ability to optimize placement and routing of digital designs to meet specifications [26]-[32].

Similarly, the Y-chart can be used to represent analog design. Figure 2.3 shows the Y-chart for a PLL design. The design of a typical analog system begins with mathematical modeling which helps determine the specifications of the overall system as well as the specifications of the sub-blocks [31][33]. After mathematical modeling, analog designers select circuit topologies as well as types of devices to be used in the structural domain. Extensive simulations are then conducted in order to finalize the device sizes at which point physical design can begin. Analog designs are significantly more susceptible to parasitics and

mismatch caused by routing and inefficient placement, and therefore verification at each level of hierarchy is typically required.

One of the main reasons why analog synthesis hasn't yet become a reality is because analog design is often quite recursive and requires simultaneous changes at multiple levels of hierarchy in order to arrive at a robust design. Figure 2.4 shows a typical progression of analog design. Simulations are required at every hierarchical level, and typically the design is tweaked manually by analog designers.

Figure 2.3: Analog design flow Y-chart

Figure 2.4: Typical progression of analog system design [30]

# 2.2. Why isn't Analog Synthesis a Reality Yet?

Automated analog integrated circuit design is slowly becoming a viable solution for improving design productivity for critical analog components. Over the past decade or so, analog design automation has significantly progressed. There are commercially viable tools that allow device sizing, automatic layout, and can design components with 10 to 100 devices. However, these tools face serious issues in terms of productivity since they aren't able to scale from the component level to the system level. Regardless of the success of these tools, analog design still lacks abstraction, and cannot be automatically synthesized. Some of the reasons are discussed below [27]-[29][32].

**1.** *Non-Linear Design:* Analog design is a very non-linear process which makes hierarchical abstraction challenging. Many parameters must be optimized simultaneously in order to meet specifications with robust designs and it is a

- recursive process that often requires a number of iterations and often changes must be made at multiple hierarchical levels simultaneously.

- 2. Bifurcation of Analog Design: Analog circuits do not scale as well as digital circuits. Some of the challenges that analog designs face with CMOS scaling: reduced voltage headroom, exacerbated mismatches, increased leakage and second order effects in transistor behavior. Two philosophies have emerged in analog design. According to the first school of thought, due to poor scaling of analog circuits, it is better to implement analog blocks in older processes, and use multi-die integration techniques to advance the overall performance of mixed signal systems. Secondly, there is a group of researchers who are pushing the limits of analog design in the advanced CMOS processes, and are inventing digitally intensive or all-digital architectures for rationally analog blocks. Due to this division, standardization and therefore development of standardized tools has been slow [31].

- **3.** *Variations:* In digital circuits, process, voltage and temperature (PVT) variations are often addressed by overdesigning the entire digital block. They are often designed for the worst case scenario. However, PVT variations cannot be mitigated in analog design by simply overdesigning because designs that are not tuned precisely may result in a complete breakdown. For example, an overdesigned amplifier may become unstable.

- 4. Highly Individualized Skills: Today, the analog design skills are highly individualized where skills are highly specialized and stored in the memory of analog designers. These skills do not necessarily translate to algorithms or simple scripts or pieces of code.

**5.** *Lack of Architectural Innovation:* In the last four decades, not much architectural innovation has occurred in analog designs. Simpler architectures typically lend themselves nicely to design automation, and often amenable to levels of abstraction.

This research presents a different approach to analog synthesis. The design methodology is discussed in the following section in detail.

## 2.3. A Brief Survey of Analog Synthesis

Figure 2.5: History of analog synthesis summarized

The advances in integrated circuits have been driven by unprecedented advances in computer aided design. The CAD tools have come so far that a majority of the digital design is completely automated today. However, almost all of the analog/RF circuits are custom designed and manually laid out. Typically, in a mixed-signal SoC, analog components make up about 20% of the circuits while requiring orders of magnitude greater design effort compared to their digital counter parts [27]. Therefore, significant research efforts have

been focused on developing analog synthesis tools. This section briefly highlights the history of analog synthesis – as illustrated in Figure 2.5.

## Silicon Compilers for VLSI (1982 - Present)

The appearance of silicon compilers became regular in 1982 as a result of research on digital design automation that began in the late 1970s. Some of the first reported design automation tools, known as silicon compilers, for VLSI were reported by Gajski in 1981 [24]-[25]. These tools had the ability to translate behavioral description into a structural netlist, and select an appropriate architecture for digital blocks based on delay specifications. In addition, Gajski reported algorithms for automatic layout of digital circuits. This was the beginning of a CAD tool revolution that propelled the digital integrated circuits to become so prevalent in society.

## Automatic Device Sizing (1987 - Present)

Automatic synthesis and layout tools were quickly adopted for digital design, and by the 1980s, researchers began to develop analog synthesis tools. The University of California at Berkeley, and Carnegie Melon University led the way in analog synthesis and layout tools. By 1987, researchers began to develop analog standard cell libraries [34]. However, due to a much wider range of applications, specifications and possibly standard cells, a truly general purpose analog standard cell library was never developed. This caused a shift in focus by the late 80s towards the development of efficient simulation tools that would allow automatic transistor sizing and development of standard cells such as opamps. Two of the earliest reported tools for automatic opamp design were Opasys, and Oasys [34]-[38].

### Automatic Hierarchical Knowledge Based Design (1995 - Present)

After relatively mediocre success with analog standard cell libraries, researchers shifted focus towards abstraction, and hierarchical design automation for analog circuits. Applications of complex algorithms such as genetic algorithms began as an attempt to replace the intuition of analog designers. This approach was dubbed knowledge based analog synthesis, which gave birth to wide spread IP reuse. However, one of the major drawback of this approach is that often multi-level hierarchical optimization is required for analog systems which was not possible with such tools. However, a large portion of these tools were integrated into the simulation tools that are utilized even today for example circuit optimizer in Spectre is a combination of algorithms developed since the late 80s [39]-[43].

## Field Programmable Analog Array (1998 - Present)

By early 1990s, field programmable gate arrays for digital applications had become quite common, which triggered a wave of new research towards development of the analog equivalent of a general purpose programmable sea of blocks. This was dubbed the field programmable analog array (FPAA). However, FPAA researchers faced the same challenges as the tool developers for analog synthesis. The sheer number of parameters to be optimized simultaneously, and the trade-off of performance and reconfigurability is too costly. Research on FPAAs is still going strong, and is showing promise with the increase of digitally assisted analog circuits. [44]-[49]

## Analog design with Digital Tools (2008 - Present)

In 2008, the first ever analog/RF blocks completely implemented using digital standard cells and design flows was reported at the University of Michigan. This started a trend towards migrating traditionally analog blocks to all-digital, synthesizable architectures which then

could be implemented using standard digital synthesis and place-and-route tools. A number of different blocks such as ultra-wide band transmitters, time-to-digital converters, all-digital PLLs, and ADCs, have been reported to date [50]-[52][65][66][33]. This approach shows promise, and is the focus of this thesis.

### Digital vs. Analog Synthesis in Industry

To further understand the disparity between analog synthesis tools versus the digital tools, a brief study was conducted on the current state of commercial analog tools, and the digital synthesis tools. As can be seen in Figure 2.6, there are barely any tools that allow analog synthesis. The only tools that the authors were able to locate that claim analog synthesis, and are commercially available are filter design tools.

Figure 2.6: Current state of commercial digital vs. analog tools [53][57]

However, these tools have severe limitations, and often accompany chip manufacturers development kits. On the other hand, there is a plethora of digital tools available. Very complex digital systems can be completely implemented using automated tools [53][57].

## 2.4. Current State of Commercially Available Analog Layout Tools

A number of companies offer "automatic" analog layout tools that come with a wide range of capabilities. The common goal, however, is to increase productivity and shorten the physical design cycle. Three of the most popular analog layout tools are discussed in this section.

## Synopsys Helix - Device Level Placement for Custom Design [54]

Synopsys offers an analog layout tool known as Helix which automates layout of analog blocks such as PLLs, ADCs, SerDes [54]. This design tool depends on prior generation of parametric cells that require an additional suite of design tools (PyCells or Sagantec). Moreover, Helix is meant to be used to generate an initially estimated floor plan, and estimate the parasitics, and the designs are DRC-aware which result in design time savings.

## Cadence Virtuoso -Electrically Aware Design (EAD) [55]

The layout design tool offered by Cadence Systems offers a unique real-time DRC and parasitics feedback to the designer as the designer lays out an analog block. This results in significant design time savings by reducing the number of iterations that are often required to fix DRC and layout parasitics. However, the analog blocks are still custom laid out by a designer.

## Tanner EDA - HiPer Design Suit [56]

Tanner EDA offers a powerful analog layout tool that comes with automated device generation, place and route. However, this tool is severely limited in it's capabilities with advanced technologies nodes. To date, this tool has only been reported to work with technologies nodes up to 90nm.

### Proposed Design Methology vs. Commercial Analog Layout Tools

A detailed comparison of the above mentioned design tools to the proposed design methodology is given in **Error! Reference source not found.**.

Table 2.1: Commercial Layout Tools vs. Proposed Design Methodology

| Comparison Metric               | Synopsys | Cadence | HiPer | Proposed Design |

|---------------------------------|----------|---------|-------|-----------------|

|                                 | Helix    | EAD     |       | Methodology     |

| <b>Device Level Layout</b>      | Yes      | No      | Yes   | No              |

| Automation                      |          |         |       |                 |

| Cell to Top level layout        | No       | No      | Yes   | Yes             |

| automation                      |          |         |       |                 |

| <b>Utilizes Existing Design</b> | No       | No      | No    | Yes             |

| Tools                           |          |         |       |                 |

| Readily integrated with         | No       | No      | No    | Yes             |

| Digital                         |          |         |       |                 |

| DRC/Parasitic Aware             | Yes      | Yes     | No    | Yes             |

It can be seen from the table above, the layout automation tools that are available in the market today only solve a portion of the problem. One significant step forward is the real-time parasitics feedback to layout design. This can reduce the number of design iterations. However, the proposed design methodology is differentiated from the existing analog layout automation tools in two ways: 1) No additional tools or training is required 2) designs are readily integrated with digital.

# 2.5. A New Analog Synthesis Philosophy

The proposed analog synthesis philosophy is highlighted in Figure 2.7. The main goal of the idea behind this philosophy is to pay special attention to innovation at every level of the hierarchy throughout the design process while keeping in mind what the limitations of existing digital tools are. This allows for an accelerated design, and significantly reduces the

design time without compromising the performance of analog circuits. Various hierarchical steps of the design methodology are described below:

**Device Sizing:** Analog design starts at the very bottom where the size of the transistors that make up various circuits is determined. Today, an average analog designer believes that digital synthesis only allows minimum length devices, and limited sets of widths. However, this is not the case. It is possible to design circuits with unconventional aspect ratios, abstract these as custom cells, and integrate them with the standard cell libraries. The first step towards synthesizing analog blocks is the ability to design with unconventional aspect ratios.

*Cell Level Design:* In order to bridge the gap between completely synthesized circuits and the analog performance, new cells must be designed and added to the existing digital standard cell libraries. If the cells are designed with analog performance in mind, and laid out at the standard cell grid, one can make the trade-off between performance, and the length of the design cycle [33].

Architectural Design: As mentioned earlier, one of the major challenges a synthesized analog circuit faces is that the performance does not compare to those of fully custom hand crafted designs. Though it might not be possible to achieve equal performance, many decisions made at the architectural level can mitigate the performance loss greatly. An approach similar to logic simplification should be applied to analog architectures. Often, the functionality can be maintained by removing a few of the non-essential blocks by migrating the complexity to the digital domain. For example, the divider can be eliminated from a PLL without losing programmability or performance of a PLL [33]. Further details of this simplification will be discussed in the later chapters.

Figure 2.7: Analog Circuit Design Innovation Chain

# 2.6. The Design Methodology

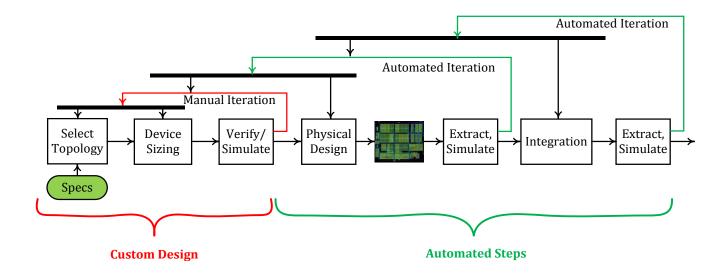

The steps of the analog synthesis methodology are discussed below.

### Step 1: Unit Cell Design

The first step is to augment the digital standard cells library with some analog unit cells that are optimized for analog performance. For example, in a PLL design, the most crucial component is the oscillator. The unit cells that make up the oscillators (e.g. tunable delay cell) are custom designed. These cells must be laid out in accordance with the standard cell

grid and integrated with the existing digital design flows [33]. This is illustrated in Figure 2.8 below.

Figure 2.8: Cell design step [33]

Step 2: Macro/Sub-block Design

Figure 2.9: Illustration of Macro Design

Once the unit cells have been designed, the next step is to design a unit macro that will allow a moderate level of layout matching. This step simply instantiates the cells designed in

the previous step. HDL code is written for one stage of critical blocks such as the oscillator or a delay line in a PLL. Moreover, the placement is forced in order to achieve matching. This is all done with a script and can be reiterated very easily [33]. An illustration of this step is given in Figure 2.9.

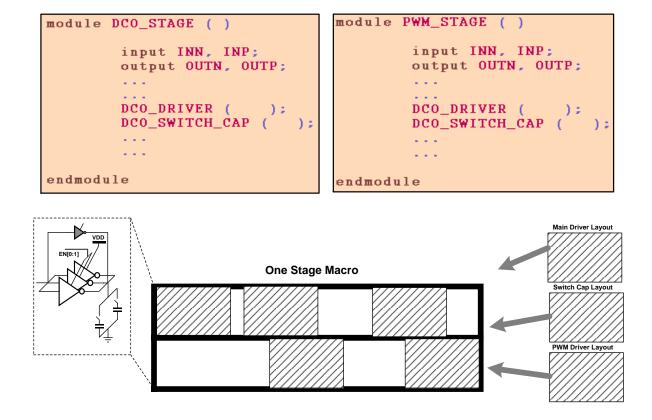

## Step 3: Verification & Iterations

Once the macro has been designed, it must be simulated and verified to make sure it will meet specifications. Figure 2.10 shows the logical flow of the various steps. Depending on how far the performance of the macros is from the requirements, designer may need to go back to either the cell design or macro design steps to iterate. Because all the design steps are scripted beyond the cell design step, the iterations tend to be significantly quicker than those in traditional analog design [33].

Figure 2.10: Verification and iteration step

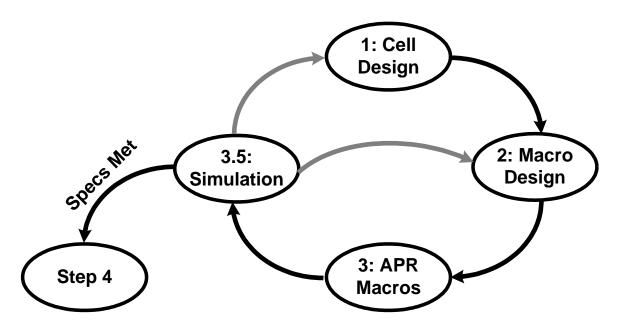

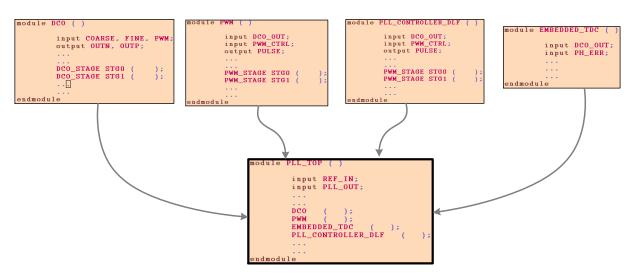

## Step 4: Top Level Design and Integration

Once the macros have been verified, the top level design and integration can begin. In this step, the entire design is brought together with HDL code, and integrated (see Figure 2.11). The digital components can be verified using digital simulations tools, and the results can then be augmented with analog models [33].

Figure 2.11: Top level design and integration

## Step 5: Top Level Physical Design

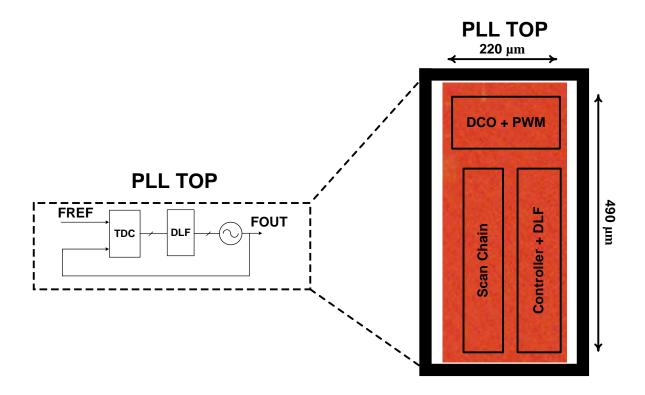

The last step in the design methodology is to perform automatic place and routing of the top level design. In this step, the top level design is run through an APR tool such as Encounter. The result is a top level PLL, as illustrated by in Figure 2.12 [33].

Figure 2.12: Top level physical design

## 2.7. Conclusion

In conclusion, the main goal of this methodology is to make the analog design process conform to the digital design process in order to use automatic design tools only available in the digital CAD flow as much as possible to accelerate the design time. This results in a significant reduction in non-recurring engineering cost as well as allows better integration. Figure 2.13 shows what the analog design looks like when done using this methodology. Compared to Figure 2.1, the steps that are automated in the digital design flow are also automated here.

Figure 2.13: Analog design Y-chart using the proposed design methodology

Figure 2.14: Analog design representation using the proposed design methodology

Figure 2.14 above shows what the design process for a typical analog block looks like when the proposed design methodology is utilized. The entire design process beyond the initial cell design is migrated to digital design tools. This allows quick design iterations and a significant reduction in design time. The ability to quickly design mixed-signal circuits will be of utmost importance with increased electronics demand.

This methodology has been proven in silicon, and a number of research prototypes were fabricated. Two of the prototypes are discussed in the following Chapter 4 & Chapter 5.

Lastly, automated layout design methodologies for analog have been proposed before. Significant research resources have been spent on developing analog synthesis and layout tools with no avail. However, there are some automatic analog layout tools available in the market today. Each of these tools require additional training for the designers, are expensive and the resultant layout cannot be readily integrated with digital designs.

# Chapter 3

# **Enhancing DCO Resolution**

We know from [58] that the dominant source of phase noise in ADPLLs is the quantization noise in the TDC and the DCO. This chapter explores possibilities for resolution enhancement while optimizing power, that are amenable to design and synthesis in a digital CAD flow. It is worth mentioning here that only truly digitally controlled ring oscillators are considered in this chapter, and this analysis doesn't apply to LC oscillators. In other words, all control voltages are assumed to have a value of 0 or VDD, and no voltage tuning via a digital-to-analog converter or otherwise is used. Therefore, the frequency can only be tuned with discrete steps, and the oscillator responds instantaneously to a change in the frequency control word.

# 3.1. Assumptions & Specifications

The design of digitally controlled ring oscillators is a challenging and recursive process which is often facilitated by powerful simulation tools. Therefore, a number of simplifying assumptions will be made here in order to gain design insight without getting buried in complicated mathematics. The assumptions, design requirements, and specifications are summarized in Table 3.1. In addition, a number of constraints are set by the process technology, the design methodology, and the DCO architecture selection. Those limitations are as following:

- 1. Tunable delays must be amenable to implementation in a digital standard cell form factor in order to facilitate automatic placing and routing of the ring oscillator. This primarily constrains the size and/or speed of these elements to be on the same order as that of a standard cell (e.g. a minimum sized inverter).

- 2. Only digitally tunable switch capacitors & buffers are considered for frequency tuning of the DCO. There are several options and implementation variants of tunable oscillators. Upon evaluating several options, we concluded these two were the most practical for implementation in a VLSA flow, and therefore restrict the analysis to these elements.

Table 3.1: Assumptions and design specifications

| Specification/Assumption                  | Value                    | Comment                                                                                                                                                                |  |

|-------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of stages                          | K                        | K-stage digitally controlled ring oscillator                                                                                                                           |  |

| Tuning steps per stage                    | N                        | Total tuning steps: $N \cdot K$ for large N                                                                                                                            |  |

| Linearity                                 | -                        | Assuming we are designing for fine control                                                                                                                             |  |

|                                           |                          | and frequency tuning will be linear.                                                                                                                                   |  |

| Delay model                               | -                        | We will be using a simplified capacitor                                                                                                                                |  |

|                                           |                          | charge/discharge model for delay/frequency                                                                                                                             |  |

|                                           |                          | calculations.                                                                                                                                                          |  |

| DCO Frequency tuning range ( $\Delta f$ ) | $f_{min}$ to $f_{max}$   | $\frac{1}{2Kt_{dmax}}$ to $\frac{1}{2Kt_{dmin}}$                                                                                                                       |  |

|                                           |                          | $2Kt_{dmax}$ to $2Kt_{dmin}$                                                                                                                                           |  |

| Delay tuning range                        | $t_{dmin}$ to $t_{dmax}$ | As capacitors are added, the delay will shift                                                                                                                          |  |

|                                           |                          | away from the original specifications.                                                                                                                                 |  |

|                                           |                          | Therefore, more current must be injected in                                                                                                                            |  |

|                                           |                          | order to bring it back to the original                                                                                                                                 |  |

|                                           |                          | specifications.                                                                                                                                                        |  |

| Nominal minimum delay per stage           | $t_{d0}$                 | $t = \frac{C_{L_{\min}\_buffer}V_{DD}/2}{C_{L_{\min}\_buffer}V_{DD}/2}$                                                                                                |  |

|                                           |                          | $t_{d0} = rac{C_{L\_{min\_buffer}}V_{DD}/2}{I_{DSAT\_{min\_buffer}}}$                                                                                                 |  |

| Minimum sized buffer's intrinsic          | $C_{int\_min\_buffer}$   | $C_{int\_min\_buffer} \propto (WL)_{min\_buffer}$                                                                                                                      |  |

| capacitance                               |                          | Cint_min_buffer: Cdiff & Cgate lumped together                                                                                                                         |  |

| External fixed capacitance                | Cext_fixed               | Consists of wiring capacitance, and any                                                                                                                                |  |

| -                                         |                          | parasitics that are added when turning                                                                                                                                 |  |

|                                           |                          | buffers/switches are added                                                                                                                                             |  |

| Minimum current                           | $I_{DSAT\_min\_buffer}$  | $V_{DSAT}^2$                                                                                                                                                           |  |

|                                           | ,,                       | $k' \left(\frac{W}{L}\right)_{\min\_buffer} \left[ (V_{DD} - V_T) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right]$ $\left(\frac{W}{L}\right)_n = 2 \left(\frac{W}{L}\right)_n$ |  |

| Relative aspect ratios                    | $(\underline{W})$        | $\left(\frac{W}{W}\right) = 2\left(\frac{W}{W}\right)$                                                                                                                 |  |

|                                           | $(L)_{n,p}$              | $(L I_p - L (L I_n))$                                                                                                                                                  |  |

| Voltage supply                            | V <sub>DD</sub> = 1      |                                                                                                                                                                        |  |

## 3.2. Tuning Delay with a Switched Capacitor

One way to tune delay (and frequency) digitally is to add digitally controlled switched-capacitor elements at the output node of the ring oscillator buffers – shown in Figure 3.1. This allows linear tuning of delay since the delay is linearly proportional to the load capacitance. We will assume that we are adding N switched capacitors per stage.

The delay,  $t_d$ , in Figure 3.1 can be expressed as [59]:

$$t_d = t_{d0} \left( 1 + \frac{C_{ext\_fixed} + n \cdot C_{ext\_tunable}}{C_{int\_min\_buffer}} \right)$$

(3.1)

Where  $t_{d0}$  is the intrinsic delay of the buffer without any external loading (i.e. without the switch capacitor),  $C_{ext\_fixed}$  is the fixed external capacitance loading the buffer (e.g. wiring capacitance & the parasitic capacitance added by the switch) that will vary non-linearly with N,  $C_{ext\_tunable}$  is the incremental capacitance added by one switched capacitor stage being activated, n is the digital control word and ranges from 0 to N, and  $C_{int\_min\_buffer}$  is the internal fixed capacitance of the minimum sized buffer.

Figure 3.1: (a) Unloaded buffer (b) Switch capacitor on (c) off (d) delay waveform

Here we will make some further simplifying assumptions. First, we assume we are targeting high frequencies, therefore the buffers in the ring oscillator will use transistors that are near minimum-sized for the given process to achieve the smallest nominal gate delay. Second, a switched capacitor load element (designed as shown in Figure 3.1) would also use minimum-sized transistors in order to achieve the finest possible resolution control. These assumptions result in the loading capacitance of a single switched capacitor element being on the order of the intrinsic capacitance of the buffer ( $C_{int\_min\_buffer}$ ). More specifically, we assume the minimum size NMOS device adds a tunable capacitance value  $C_{ext\_tunable}$ . We must also note that  $C_{ext\_fixed}$  is a non-linear function of N, the total number of tunable switched-capacitors.

Now we can compute  $t_d(n)$  (from Figure 3.1) as follows:

$$t_d(n) = t_{d0} \left( 1 + \frac{C_{ext\_fixed}(N) + n C_{ext\_tunable}}{C_{int\_min\_buffer}} \right)$$

(3.2)

$$t_d(n) = t_{d0} \left( 1 + \frac{c_{ext\_fixed}(N)}{c_{int\_min\_buffer}} \right) + t_{d0} \left( \frac{n c_{ext\_tunable}}{c_{int\_min\_buffer}} \right)$$

(3.3)

$$\Delta t_d = t_{d0} \left( \frac{n \, C_{ext\_tunable}}{C_{int \, min \, buffer}} \right) \tag{3.4}$$

Therefore, the resolution is determined by the external tunable capacitance relative to the fixed capacitance (made up of wiring, switch parasitics and intrinsic capacitance of the buffer). For  $f_{min}$ , we can set n=N in equation 3.3, and for  $f_{max}$ , n=0.

Figure 3.2: Maximum and minimum frequency scenarios

### Frequency Resolution

As a specific example, let's assume that we tune  $C_{\text{ext\_tunable}}$  with a minimum sized NMOS devices and that  $C_{\text{ext\_tunable}} = (1/3) C_{\text{int\_min\_buffer}}$ . This means that the delay can be tuned with a step size of  $t_{d0}/3$ . The intrinsic delay in a 65 nm CMOS technology (used to fabricate the first prototype) is approximately 10ps. Therefore, a switch capacitor allows tuning delay with ~3ps steps – which translates to approximately 500 kHz step @ 400 MHz  $f_{rosc}$ . This **frequency step is too large**, and alternative methods of delay/frequency tuning are discussed in the following sections.

From 3.3, we can calculate the frequency of the DCO:

$$f(n) = \frac{c_{int\_min\_buffer}}{2Kt_{d0}} \left( \frac{1}{c_{int\_min\_buffer} + c_{ext_{fixed}}(N) + nc_{ext_{tunable}}} \right)$$

(3.5)

$$\frac{d}{dn}f(n) = \frac{C_{int\_min\_buffer}}{2Kt_{d0}} \left( \frac{-C_{ext\_tunable}}{(C_{int\_min\_buffer} + C_{ext\_fixed}(N) + nC_{ext\_tunable})^2} \right)$$

(3.6)

Therefore, if large frequency tuning range is required, this is a very non-linear method of frequency tuning.

### **Power Consumption**

The power of a ring oscillator using static CMOS buffers is:

$$P = CV_{DD}^2 f (3.7)$$

As illustrated in Figure 3.2, Maximum frequency is achieved by opening all N switches. Therefore, the external capacitance is at its minimum in all K stages of the ring oscillator.

$$P_{switches\_off} = K(C_{int\_min\_buffer} + C_{ext\_fixed}(N))V_{DD}^2 f_{max}$$

(3.8)

When all switches are turned on:

$$P_{switches\_on} = K \left[ C_{ext\_fixed}(N) + C_{L\_min\_buffer} + N C_{ext\_tunable} \right] V_{DD}^2 f_{min}$$

(3.9)

From equation 3.3,

$$\frac{1}{f_{max}} = t_{dmin} = 2Kt_d(0) = 2Kt_{d0} \left( 1 + \frac{C_{ext\_fixed}(N)}{C_{int\_min\_buffer}} \right)$$

(3.10)

$$\frac{1}{f_{min}} = t_{dmax} = 2Kt_d(N) = 2Kt_{d0} \left( 1 + \frac{c_{ext\_fixed}(N)}{c_{int\_min\_buffer}} \right) + 2KN \ t_{d0} \left( \frac{c_{ext\_tunable}}{c_{int\_min\_buffer}} \right)$$

(3.11)

Therefore, maximum and minimum power levels are:

$$P_{switches_{off}} = \left[C_{int\_min\_buffer} + C_{ext_{fixed}}(N)\right] (V_{DD})^2 \frac{1}{2t_{d0} \left(1 + \frac{C_{ext_{fixed}}(N)}{C_{int\_min\_buffer}}\right)}$$

$$= C_{int\_min\_buffer} (V_{DD})^2 \frac{1}{2t_{d0}} = V_{DD}I_{DSAT\_min\_buffer}$$

(3.12)

$$\begin{split} P_{switches\_on} &= \left[C_{ext\_fixed}(N) + C_{int\_min\_buffer} + NC_{ext\_tunable}\right] (V_{DD})^2 \frac{1}{2t_{d0} \left(1 + \frac{C_{ext\_fixed}(N) + NC_{ext\_tunable}}{C_{int\_min\_buffer}}\right)} \\ &= C_{int\_min\_buffer} \frac{1}{2t_{d0}} = V_{DD}I_{DSAT\_min\_buffer} \end{split} \tag{3.13}$$

From 3.12 & 3.13 we can conclude that power stays constant.

# 3.3. Tuning Delay with Parallel Buffers

Next, we will discuss delay tuning by switching parallel buffers on/off - as shown in Figure 3.3. We begin with a minimum sized buffer (Figure 3.3a), and maximum delay is achieved by turning all the switchable buffers off (Figure 3.3b), and the minimum delay is achieved when all the buffers are turned on (Figure 3.3c). The delay is to be tuned between  $t_{d2}$  and  $t_{d1}$  with N steps.

Figure 3.3: Tuning delay with parallel buffers

Simplified expression for the delay of a minimum sized buffer is as following:

$$t_{d0} = \frac{C_{int\_min\_buffer}V_{DD}/2}{I_{DSAT\_min\_buffer}}$$

(3.14)

**Note:** The assumptions discussed in section 3.1 are valid in this analysis as well.

We are to design a digitally tunable delay element by adding N parallel buffers to the minimum sized buffer. The desired delay tuning range is  $t_{dmin}$  to  $t_{dmax}$  which is achieved by turning off buffers. Each of the additional buffers has  $C_L \propto (MWL)$  since the aspect ratio of additional buffers is  $\propto \frac{W}{ML}$ . This results in total overall  $C_{ext\_fixed}$ :

$$C_{ext\_fixed} \propto (WL)_{min} + (MWL)_{min[1]} + (MWL)_{min[2]} \dots + (MWL)_{min[N]}$$

(3.15)

$$C_{ext\_fixed} \propto (MN+1)(WL)_{min} \propto (MN+1)C_{int\_min\_buffer}$$

(3.16)

$$t_d(n) = \frac{(MN+1)C_{int\_min\_buffer}V_{DD}/2}{I_{DSAT\_min\_buffer} + nI_{DSAT\_tunable}}$$

(3.17)

$$f(n) = \frac{I_{DSAT\_min\_buffer} + nI_{DSAT\_tunable}}{2K(MN+1)C_{int\ min\ buffer}V_{DD}/2}$$

(3.18)

We know that  $I_{DSAT\_tunable}$  by design is:

$$I_{DSAT\_tunable} = \frac{I_{DSAT\_min\_buffer}}{M}$$

(3.19)

Therefore, the frequency resolution is:

$$\frac{d}{dn}f(n) = \frac{I_{DSAT_{tunable}}}{K(MN+1)C_{int\_min\_buffer}V_{DD}} = \frac{I_{DSAT\_min\_buffer}}{KM(MN+1)C_{int\_min\_buffer}V_{DD}}$$

(3.20)

We can see from 3.19 that the frequency resolution is a strongly non-linear function of the number of tunable buffers as well as the relative size of the tunable buffer – captured by M. To calculate the minimum frequency, n = 0:

$$\frac{1}{f_{min}} = 2Kt_d(0) = \frac{K(MN+1)C_{int\_min\_buffer}V_{DD}}{I_{DSAT\_min\_buffer}}$$

(3.21)

The maximum frequency can be calculated by setting n=N:

$$\frac{1}{f_{max}} = 2Kt_d(N) = \frac{K(MN+1)C_{int\_min\_buffer}V_{DD}}{I_{DSAT\_min\_buffer} + NI_{DSAT\_tunable}}$$

(3.22)

The power levels when all buffers are on/off can be expressed as following:

$$P_{buffers\_off} = K(MN+1)C_{int\_min\_buffer}V_{DD}^2f_{min}$$

(3.23)

$$P_{buffers\_on} = K(MN + 1)C_{int\_min\_buffer})V_{DD}^2 f_{max}$$

(3.24)

By substituting the values of  $f_{min}$ , and  $f_{max}$  into 3.23 & 3.24:

$$P_{buffers\_off} = I_{DSAT\_min\_buffer} V_{DD}$$

(3.25)

$$P_{buffers_{on}} = (I_{DSAT\_min\_buffer} + NI_{DSAT_{tuning}})V_{DD}$$

(3.26)

If we substitute 3.22 into 3.26, then

$$P_{buffers_{on}} = \left(1 + \frac{N}{M}\right) I_{DSAT\_min\_buffer} V_{DD}$$

(3.27)

## Frequency Resolution

High delay/frequency resolution can be achieved using this approach. However, the power consumption is inversely proportional to the resolution. The frequency resolution of this approach is given by 3.19.

### **Power Consumption**