# **Resistive-RAM for Data Storage Applications**

## by

# Siddharth Gaba

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2014

# **Doctoral Committee**

Associate Professor Wei Lu, Chair Assistant Professor Emmanouil Kioupakis Professor Jerome P. Lynch Assistant Professor Zhengya Zhang Associate Professor Zhaohui Zhong

# **TABLE OF CONTENTS**

| List of Figu | res                                                            | vi   |

|--------------|----------------------------------------------------------------|------|

| List of Tabl | es                                                             | xiii |

| Abstract     |                                                                | xiv  |

| Chapter 1    | Introduction                                                   | 1    |

|              | 1.1 Data Explosion                                             | 1    |

|              | 1.2 The NVM Workhorse: FLASH                                   | 1    |

|              | 1.3 Semiconductor Flash Memory Scaling                         | 3    |

|              | 1.4 Emerging Non-Volatile Memories                             | 5    |

|              | 1.5 RRAM                                                       | 8    |

|              | 1.6 Organization of the Thesis                                 | 11   |

|              | References                                                     | 12   |

| Chapter 2    | Amorphous Silicon Based Electrochemical Metallization Memories | 18   |

|              | 2.1 Introduction                                               | 18   |

|              | 2.2 Physical characterization of metallic filaments            | 19   |

|           | 2.2.1 Device Fabrication                           |

|-----------|----------------------------------------------------|

|           | 2.2.2 Electron Microscopy Studies                  |

|           | 2.3 MIM vs. MIS                                    |

|           | 2.3.1 Device Fabrication                           |

|           | 2.3.2 Electrical Characterization                  |

|           | 2.3.3 SPICE Simulation                             |

|           | 2.4 CMOS / RRAM Vertical Integration               |

|           | 2.4.1 Bottom Electrode Engineering                 |

|           | 2.4.2 CMOS Circuit Operation                       |

|           | 2.4.3 Fabrication Process Flow                     |

|           | 2.4.4 Electrical Data                              |

|           | 2.4.4a DC Characteristics                          |

|           | 2.4.4b Array Operation                             |

|           | 2.5 Conclusion                                     |

|           | References                                         |

| Chapter 3 | Stochastic RRAM Devices for Computing Applications |

|           | 3.1 Introduction                                   |

|           | 3.2 Device Fabrication                             |

|           | 3.3 Stochastic Nature of Devices                   |

|           | 3.4 Random But Predictable                         |

|           | 3.5 Application: Stochastic Computing                             | 56       |

|-----------|-------------------------------------------------------------------|----------|

|           | 3.6 Conclusion                                                    | 61       |

|           | References                                                        | 62       |

|           | Appendix 3: Experimental Setup                                    | 64       |

| Chapter 4 | Ultralow Sub-1nA Operating Current Resistive Memory               | 65       |

|           | 4.1 Introduction                                                  | 65       |

|           | 4.2 Device Structure / Fabrication                                | 68       |

|           | 4.3 Electrical Results                                            | 72       |

|           | 4.3.1 Low Current Operation                                       | 72       |

|           | 4.3.2 Retention and Endurance                                     | 79       |

|           | 4.3.3 Multilevel Operation                                        | 80       |

|           | 4.3.4 Array Operation                                             | 81       |

|           | 4.4 Passive Crossbar Arrays                                       | 82       |

|           | 4.5 Conclusion                                                    | 84       |

|           | References                                                        | 84       |

| Chapter 5 | 3D Vertical Dual-Layer Oxide RRAM for Vertical Memory             | 88       |

|           | 5.1 Introduction                                                  | 88       |

|           | 5.2 3D Integration                                                | 89       |

|           | 5.3 3D Monolithic Integration Traditional Crosspoint vs. Vertical | Sidewall |

|           | Structure                                                         | 90       |

|           | 5.4 Device Fabrication                                                    | 92 |

|-----------|---------------------------------------------------------------------------|----|

|           | 5.5 Measurement Setup                                                     | 95 |

|           | 5.6 Results and Discussions                                               | 96 |

|           | 5.6.1 Bipolar Operation                                                   | 96 |

|           | 5.6.2 Current Non-linearity                                               | 98 |

|           | 5.6.3 Device Matching                                                     | 99 |

|           | 5.6.4 Pulse Operation                                                     | 01 |

|           | 5.6.5 Endurance                                                           | 03 |

|           | 5.6.6 Crosstalk                                                           | )4 |

|           | 5.7 Conclusion                                                            | )5 |

|           | References                                                                | 06 |

| Chapter 6 | Future Work                                                               | )9 |

|           | 6.1 Integration with CMOS Circuits and RRAM Arrays – A Hybrid Approach 10 | )9 |

|           | 6.1.1 Device Fabrication                                                  | 14 |

|           | 6.1.2 Electrical Testing                                                  | 19 |

|           | 6.2 Achieving self-compliance in devices                                  | 23 |

|           | 6.3 CMOS compatible ultra-low current devices                             | 24 |

|           | References                                                                | 25 |

# LIST OF FIGURES

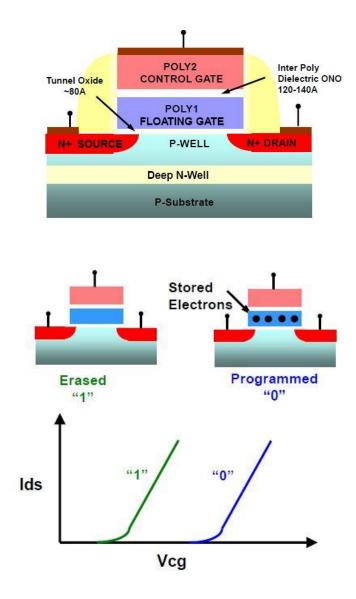

| Figure 1-1 | Flash memory works by adding (charging) or removing (uncharging) electrons to and from a floating gate. A bit's 1 or 0 state depends upon whether the floating gate is charged or not                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

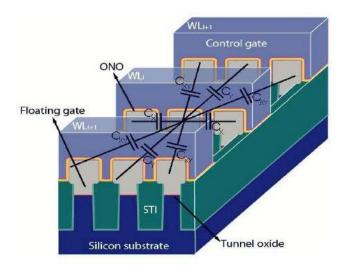

| Figure 1-2 | Diagram showing capacitive coupling in flash memory4                                                                                                                                                                                                                                                                                                                                                                              |

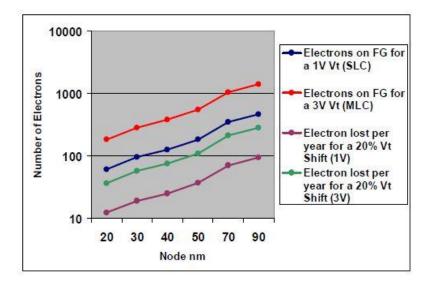

| Figure 1-3 | The number of electrons stored vs. lithographic dimension and electron loss requirement for retention                                                                                                                                                                                                                                                                                                                             |

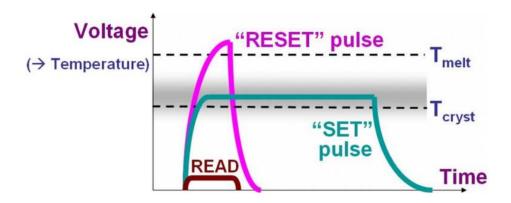

| Figure 1-4 | Programming of a PCM device involves application of electrical power through applied voltage, leading to internal temperature changes that either melt and then rapidly quench a volume of amorphous material reset, or which hold this volume at a slightly lower temperature for sufficient time for recrystallization set. A low voltage is used to sense the device resistance read so that the device state is not perturbed |

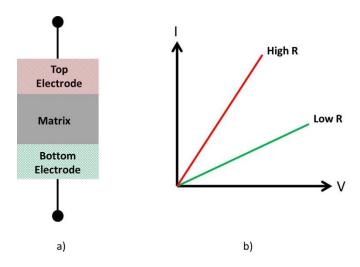

| Figure 1-5 | a) A RRAM cell has a very simple structure - matrix material sandwiched between two electrodes. b) The matrix resistance (high or low) is read out using a low voltage                                                                                                                                                                                                                                                            |

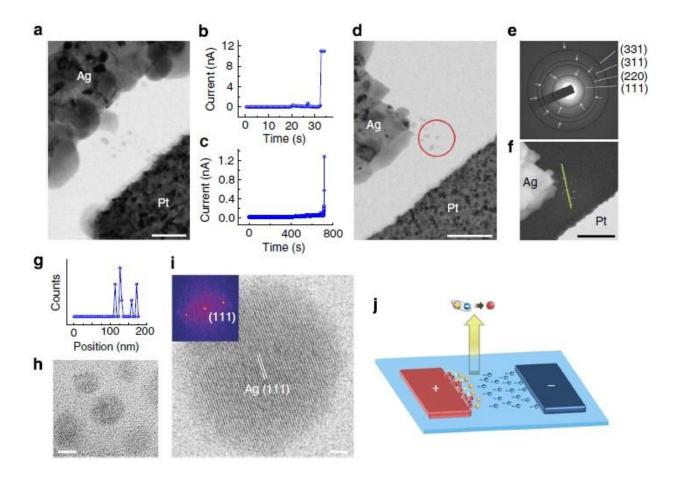

| Figure 2-1 | Observation of conducting filament dynamics in a-Si-based resistive memories21                                                                                                                                                                                                                                                                                                                                                    |

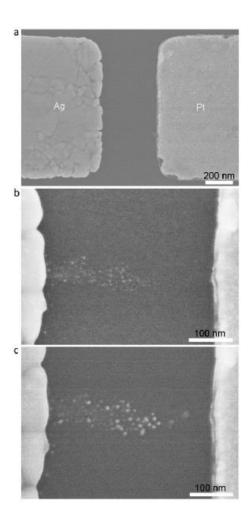

| Figure 2-2 | Controlling the filament size by limiting the programming current22                                                                                                                                                                                                                                                                                                                                                               |

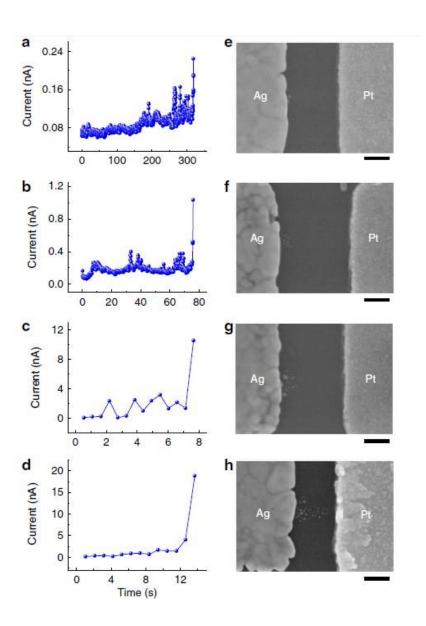

| Figure 2-3 | Step-by-step filament growth                                                                                                                                                                                                                                                                                                                                                                                                      |

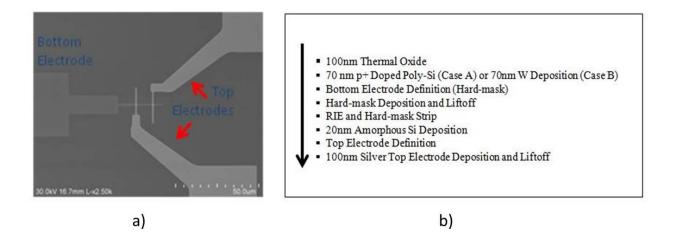

| Figure 2-4 | a) Scanning electron micrograph of a fabricated cell where two top electrodes share a common bottom electrode. b) An overview of the process flow for the two different devices. Except the bottom electrode material (p+ poly-Si vs. tungsten), all processing conditions were kept identical to allow a fair comparison                                                                                                         |

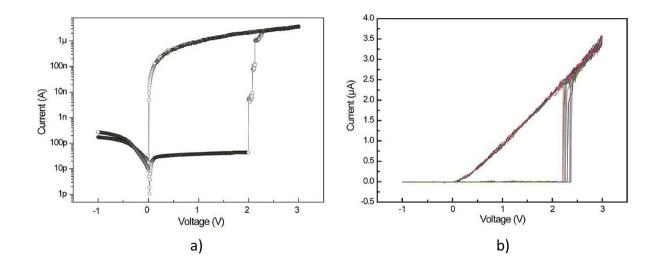

| Figure 2-5  | a) I-V sweep of a virgin device showing sharp switching at ~3.5V. b) Subsequent SET voltage is slightly lower than the initial forming voltage. Ron ~ 110 kohm. c) A typical log scale I-V curve demonstrating highly non-linear and sharp switching characteristics.                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

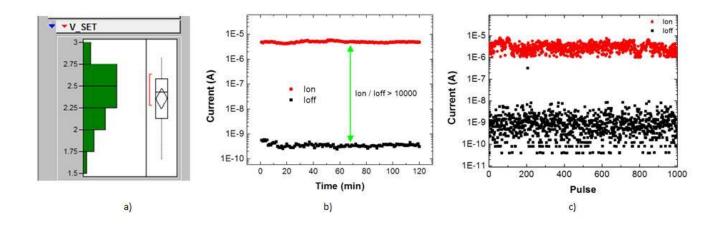

| Figure 2-6  | a) Distribution of VSET for 30 consecutive write cycles. b) Two hour retention data (red circles) and two hour read disturb data (black squares). Readout utilized a 1V-10ms pulse repeated every 60 seconds. Device was written with a 5V/400us pulse for the retention test and erased with a -4V/400us pulse for the read disturb test. c) Endurance Data. Devices can be cycled continuously and do not exhibit stuck-atone (SA1) or stuck-at-zero (SA0) faults. |

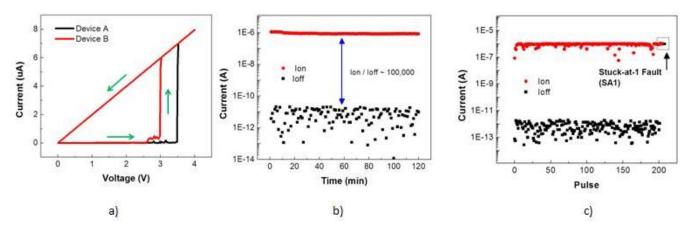

| Figure 2-7  | a) Switching curves from two devices. A 500k external series resistor was used Ron $\sim 5~\mathrm{k}\Omega$ . b) ON state retention (red) and OFF state read-disturb (black) data. A 1 M $\Omega$ series resistor was used in the setup and the device was read with a 1V-10ms pulse repeated every 60 seconds. c) Metal bottom electrode based devices have a significantly smaller endurance and tend to get stuck in the programmed state27                      |

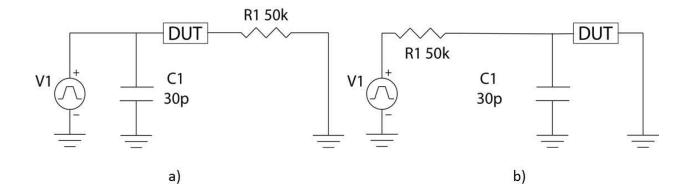

| Figure 2-8  | a) Case A: Equivalent circuit for a device based on poly-BE. b) Case B: Equivalent circuit for a device based on metal-BE and utilizing an external 50k series resistor                                                                                                                                                                                                                                                                                              |

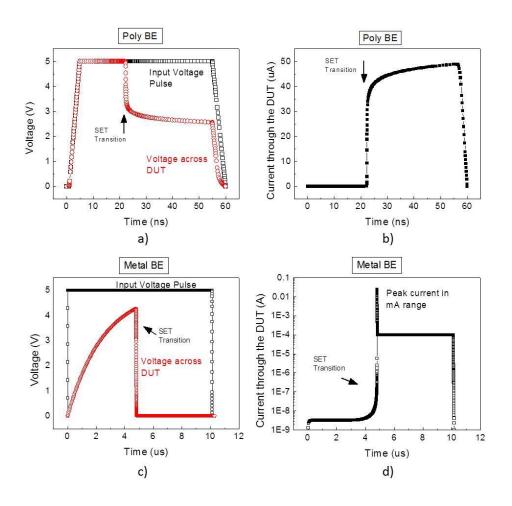

| Figure 2-9  | a) and b) Case A: The device switches in less than 20 ns as can be observed by monitoring the voltage across the DUT. The voltage across DUT settles at around half the voltage of the input pulse due to the series resistor effect. No sharp current transients are observed as the device switches. c) Case B: The device takes much longer to switch due to the RC delay. d) A sharp current discharge accompanies device switching                              |

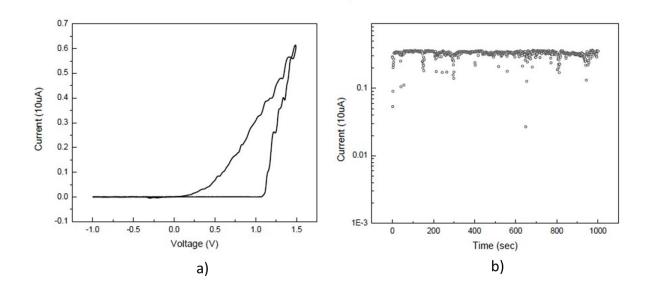

| Figure 2-10 | a) I-V switching curve from SiGe based RRAM showing intrinsically rectifying I-V characteristics. b) Retention characteristics of the SiGe-based RRAM34                                                                                                                                                                                                                                                                                                              |

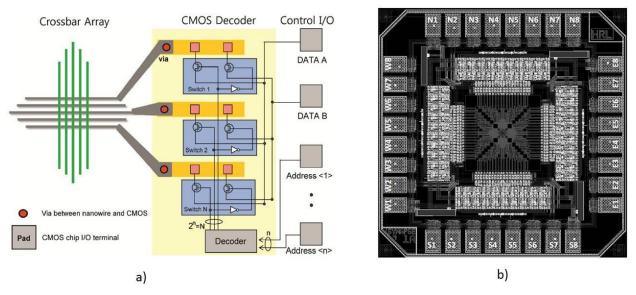

| Figure 2-11 | a) Schematic of the program/read schemes. Each column or row in the crossbar array is connected to one of the two external signal pads (DATA A for signal applied to the selected column/row, DATA B for signal connected to the unselected column/row) through CMOS decoder circuits controlled by address I/O pads. by Die image of the CMOS decoder circuit.                                                                                                      |

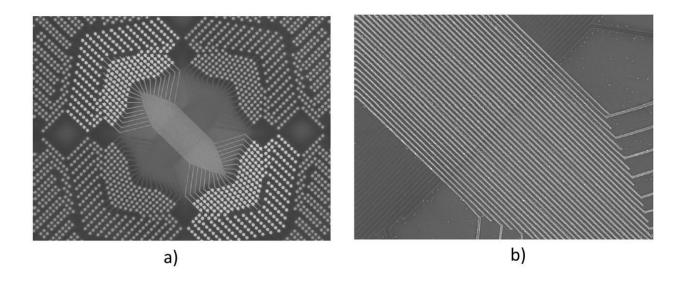

| Figure 2-12 | The complete device structure of the integrated crossbar array. (a) SEM image of the crossbar array along with the CMOS vias. (b)High magnification image of the crossbar array. The density of the crossbar memory is 10 Gbits/cm2 with 100 nm pitch.                                                                                                                                                                                                               |

| Figure 2-13 | a) I-V switching curve from SiGe based RRAM showing intrinsically rectifying I-V characteristics. b) I-V switching characteristics from 10 different cells in the crossbar array                                                                                                                                                                                                                                                                                     |

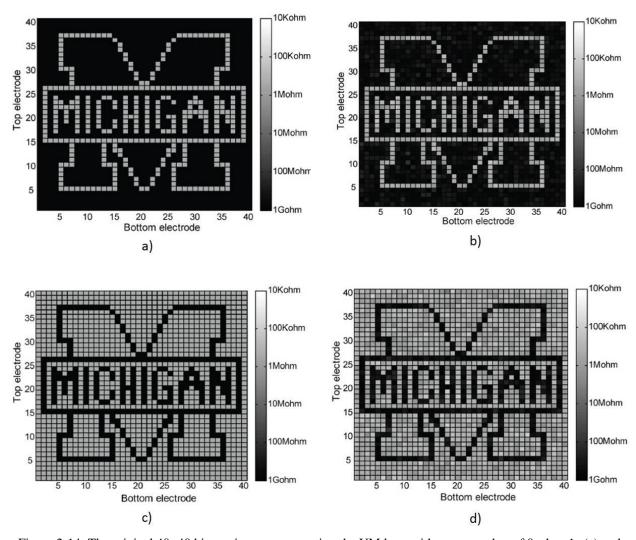

| Figure 2-14 | The original 40×40 bitmap image representing the UM logo with more number of 0s than 1s (a) and more 1s than 0s (c). The reconstructed bitmap images (b and d)                                                                                                                                                                                                                                                                                                       |

|             | after storing and retrieving data in the 40×40 crossbar array for each case above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

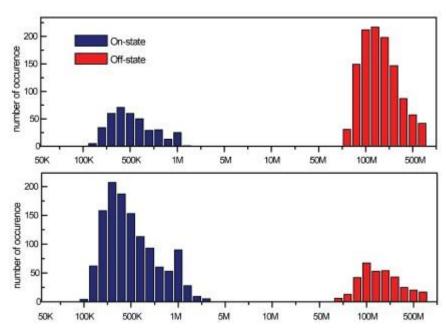

| Figure 2-15 | Histograms of the on- and off-state resistances for the data in Fig. 2-14b and Fig. 2-14d, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                               |

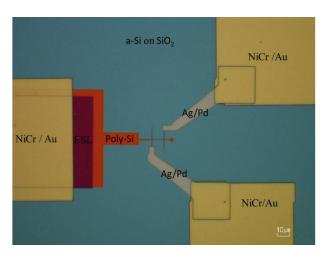

| Figure 3-1  | (a) An optical micrograph of the fabricated device. A resistive switch is formed at each location where the Ag top electrode crosses over the poly-Si bottom electrode. (b) Scanning electron micrograph of the crosspoint device structure                                                                                                                                                                                                                                                                                                           |

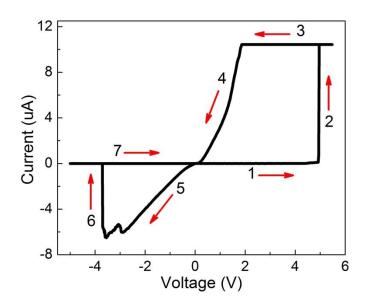

| Figure 3-2  | DC switching curve of the fabricated device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

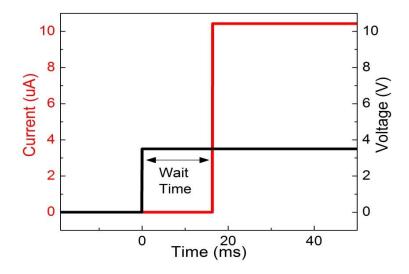

| Figure 3-3  | Example of a wait time measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

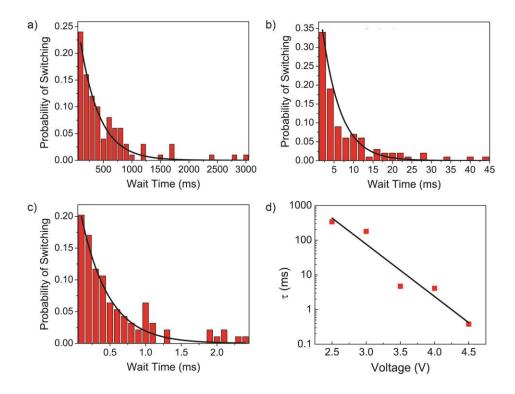

| Figure 3-4  | Stochastic wait time distribution. (a–c) Distributions of wait times applied voltages of 2.5 V (a), 3.5 V (b) and 4.5 V (c). Solid lines: fitting to the Poisson distribution of eqn. (1) using s as the only fitting parameter. $\tau$ = 340 ms, 4.7 ms and 0.38 ms for (a)–(c), respectively. (d) Dependence of s on the programming voltage. Solid squares were obtained from fitting of the wait time distributions while the solid line is an exponential fit                                                                                    |

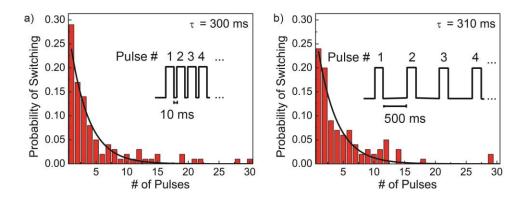

| Figure 3-5  | Switching probability when subjected to a series of short pulses The average switching time can be calculated by measuring the number of pulses, regardless of the gap between the pulses. The pulse width was kept constant at 100 ms while the gap was changed from 10 ms (a) to 500 ms (b). The voltage amplitude was fixed at 2.5 V for all pulses.                                                                                                                                                                                               |

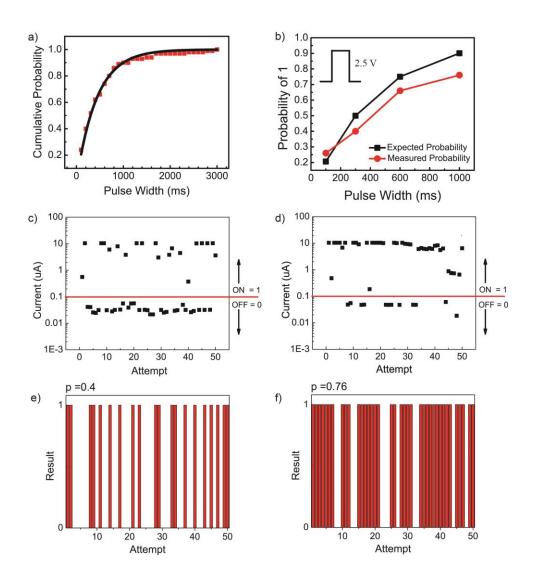

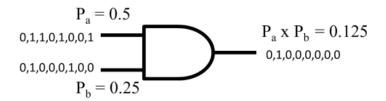

| Figure 3-6  | Probability of switching within a single pulse. (a) Pulse width dependence. The solid line shows values predicted from equation 3-2, squares were obtained from measuring the cumulative probability obtained from Fig. 3-5a. (b) Expected and measured probability using a single 2.5 V pulse. (c–d) Device current measured after repeated application of a single 2.5 V, 300 ms (c) and 1000 ms (d) pulse. The device was reset after each measurement. (e–f) Corresponding bitstreams of (e) p= 0.4 and (f) p= 0.76 corresponding to (c) and (d). |

| Figure 3-7  | Stochastic multiplication using a logic AND gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 3-8  | Stochastic implementation of logic function $y=x1x2x3+x3(1-x4)58$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

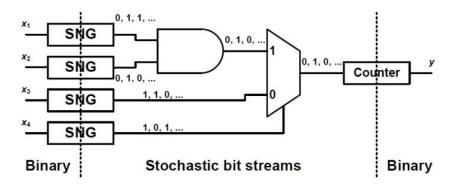

| Figure 3-9  | Stochastic switching in different devices (a–d) obtained from a second fabrication run. The devices were measured with twenty 2.75 V, 1000 ms pulses59                                                                                                                                                                                                                                                                                                                                                                                                |

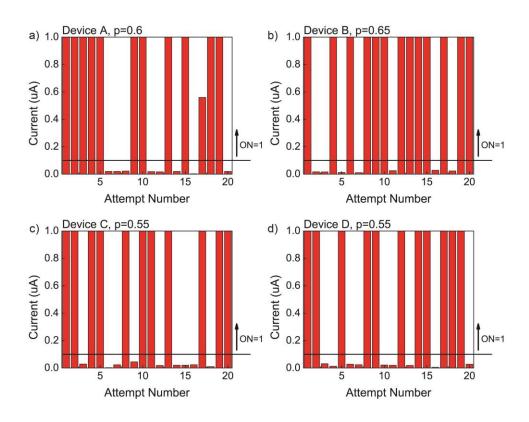

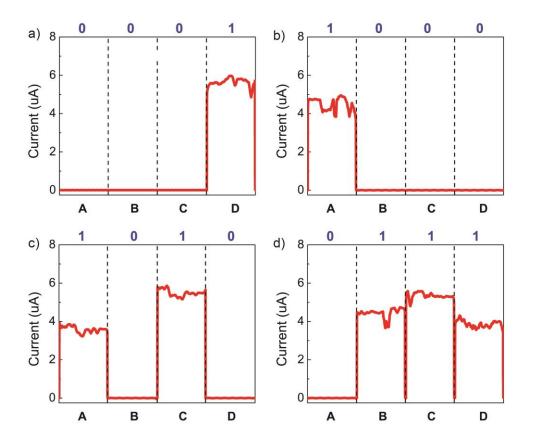

| Figure 3-10 | Stochastic programming of a device array. 4 representative combinations $\{0001\}$ (a), $\{1000\}$ (b), $\{1010\}$ (c), and $\{0111\}$ (d) are shown here out of a total of $2^4 = 16$ combinations. The different combinations were obtained in the same array under identical pulses. The devices were programmed in parallel using a single 2.75 V, $1000$ ms pulse and their states were measured using 2 V, $100$ ms pulses individually after the programming pulse. The array was reset after each measurement.                                |

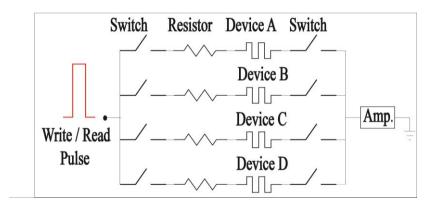

| Figure 3-11 | Experimental setup used to generate bitstreams that are stochastic in space64                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

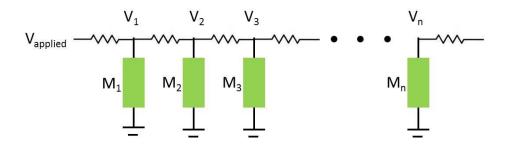

| Figure 4-1  | Voltage is dropped due to the line resistance. All cells are assumed in high resistance state                                                                                                                                                                                                                                                                                                                                                                                                     |

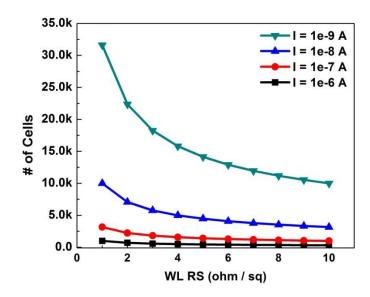

| Figure 4-2  | Number of resistive switching cells along a word line as a function of the operating current and line resistance                                                                                                                                                                                                                                                                                                                                                                                  |

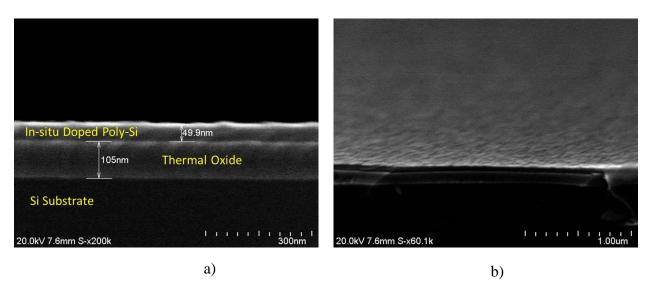

| Figure 4-3  | a) X-SEM of the deposited poly-silicon film. 9 minutes deposition time gives a film thickness ~50nm. b) Tilt view (45 degrees) of the poly-silicon film confirms relatively flat surface                                                                                                                                                                                                                                                                                                          |

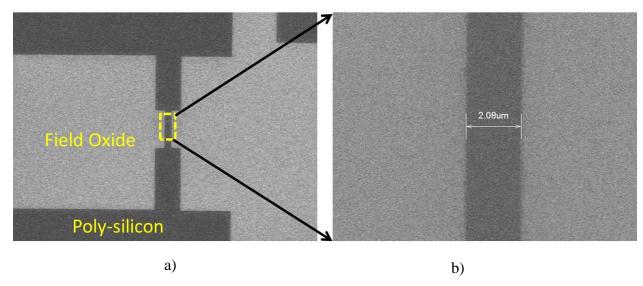

| Figure 4-4  | a) Scanning electron micrograph of the etched poly-silicon bottom electrodes. b) A 2um as-designed line becomes slightly larger in dimension due to lithography/etch process bias                                                                                                                                                                                                                                                                                                                 |

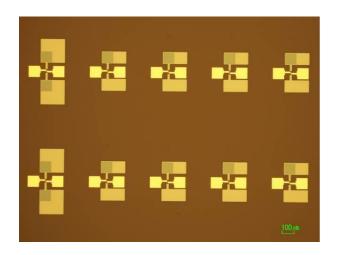

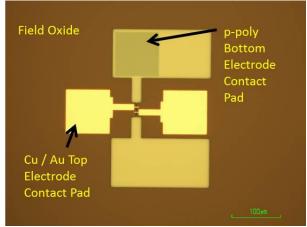

| Figure 4-5  | a) Optical micrograph of the devices after opening the pads for the bottom electrodes. The first device in each row has two contacts for the bottom electrode and serves as a test structure to allow measurement of line resistance. b) Higher magnification view of each device. Each poly-silicon bottom electrode is shared between two copper top electrodes.                                                                                                                                |

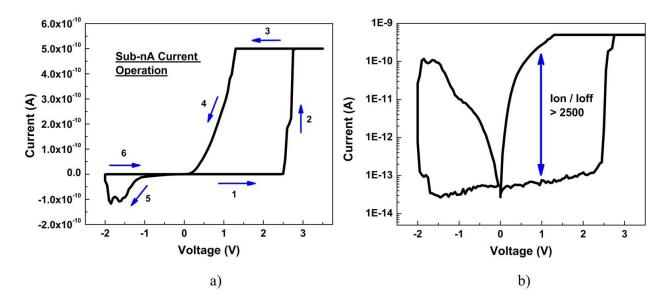

| Figure 4-6  | Linear (a) and log (b) scale I-V curve showing sub-1nA current operation. Despite the low current, large (> 2500) Ion-Ioff ratio is obtained                                                                                                                                                                                                                                                                                                                                                      |

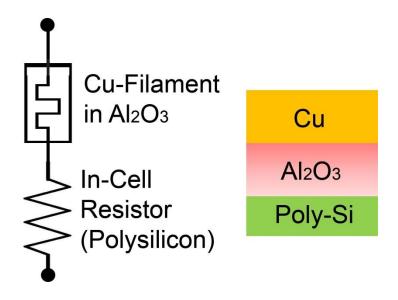

| Figure 4-7  | Device structure schematic. The polysilicon BE effectively acts as an in-cell resistor and prevents overshoot during writing                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 4-8  | Forming curves of 10 different control devices (W / 10nm Al <sub>2</sub> O <sub>3</sub> / Cu). The devices cannot be cycled even with very low current compliance                                                                                                                                                                                                                                                                                                                                 |

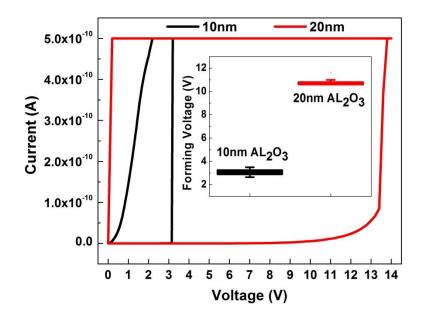

| Figure 4-9  | Comparison of forming curves of devices with different thickness. Forming voltages show tight distribution (inset). The 20nm Al <sub>2</sub> O <sub>3</sub> devices require significantly higher forming voltage and typically cannot be cycled                                                                                                                                                                                                                                                   |

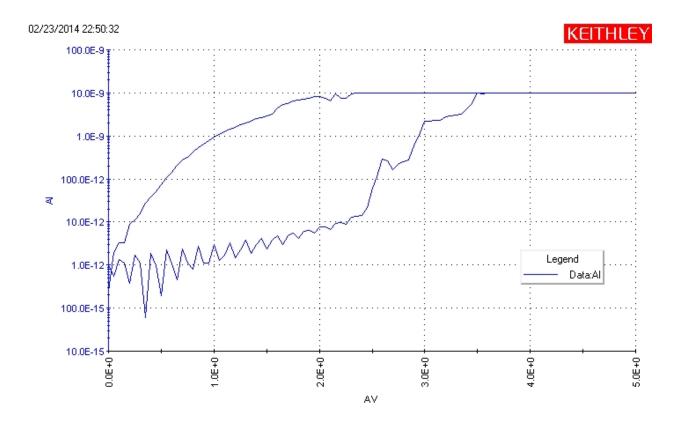

| Figure 4-10 | Current-voltage curve of a Cu / 8.5nm Al <sub>2</sub> O <sub>3</sub> / Poly-Si virgin device                                                                                                                                                                                                                                                                                                                                                                                                      |

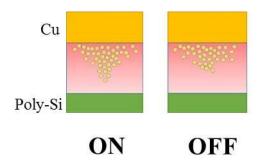

| Figure 4-11 | Since the copper filament does not completely bridge the two electrodes in the ON state, very low operating current can be obtained                                                                                                                                                                                                                                                                                                                                                               |

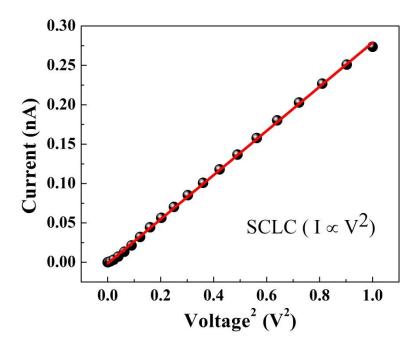

| Figure 4-12 | Linear fit for on-state current vs. voltage <sup>2</sup> indicating SCLC conduction mechanism                                                                                                                                                                                                                                                                                                                                                                                                     |

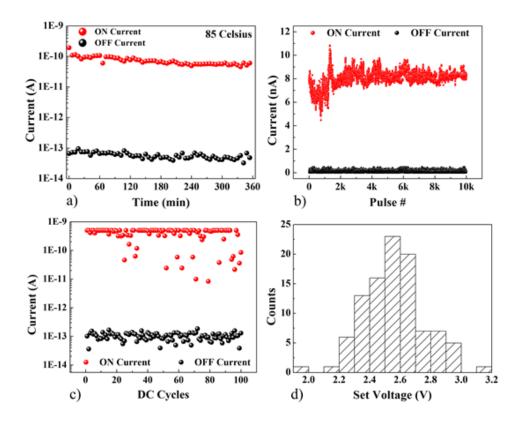

| Figure 4-13 | a) Elevated temperature retention test. Read pulse (1V/10ms) was repeated every 6 minutes. Large read window is maintained after 6 hours at 85°C. b) 10 000 cycle pulse data indicating robust endurance. Write pulse: 5V/5ms, erase pulse: -2.5V/4ms., read pulse: 1V, 10ms c) Endurance data from 100 DC cycles. ON current and OFF current were read at 1V. d) Distribution of the SET voltage taken from 100 consecutive DC sweeps. Mean SET voltage is 2.53V with standard deviation of 0.2V |

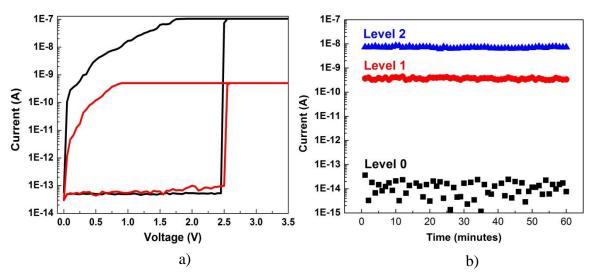

| Figure 4-14 | Multilevel cell (MLC) capability achieved by controlling compliance current during programming (a). Different states exhibit stable read window (b). Device state was read with 1V pulse repeated every 1 minute                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

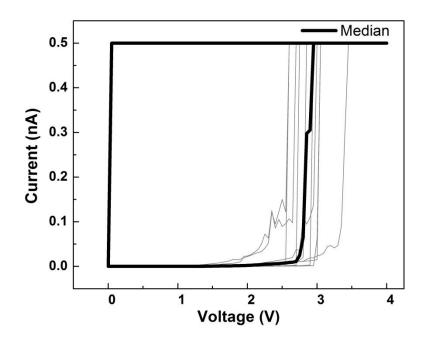

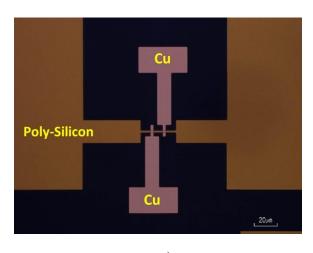

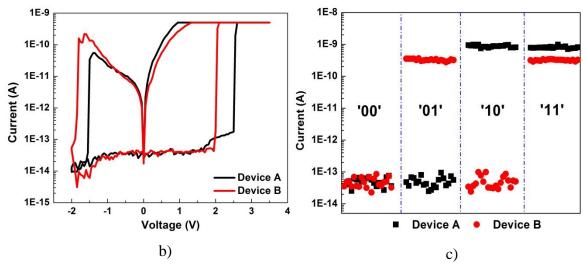

| Figure 4-15 | (a) 2x1 arrays fabricated with two Cu top electrodes sharing a poly-silicon bottom electrode (Scale bar 20um). (b) Matched I-V curves for one such 2x1 array. (c) Devices exhibit stable read currents for different combinations of device states reset / reset, reset/set, set/reset and set/set. The devices were written with DC sweeps                                                                                                                                                                                                     |

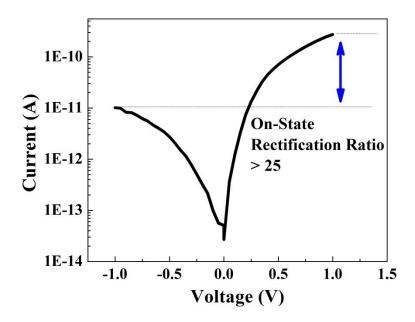

| Figure 4-16 | Intrinsic rectifying behavior in the device on-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

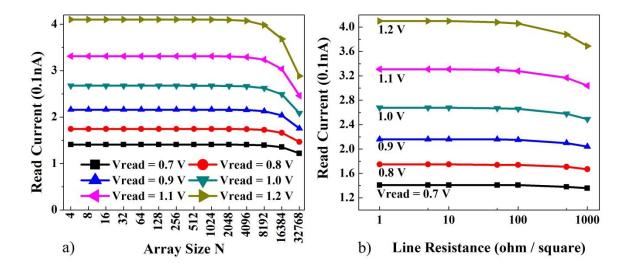

| Figure 4-17 | Read margin for square arrays with N rows and N columns. Line resistance of $100^\circ$ ohm/sq. is assumed. Grounding scheme is utilized for array simulation - unselected word-lines and bit- lines are held at ground potential. The selected word-line is biased biased at VREAD while the selected bit-line is grounded. Worst case scenario with the target cell located at the farthest corner and all unselected cells are in low resistance state. b) Read current degradation as a function of word / bit line resistance for N = 512. |

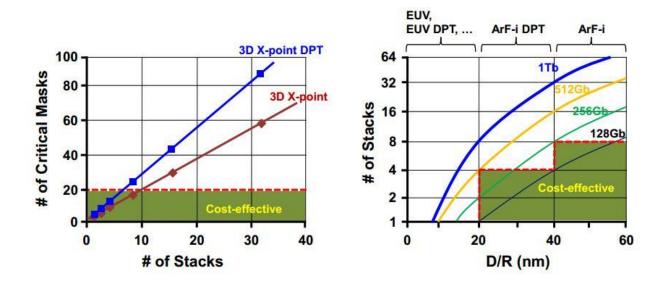

| Figure 5-1  | Minimum number of critical masks necessary for 3D X-point FLASH arrays as a function of stacked layer number, (b) Memory density as a function of design rule and the number of stacked memory layers composed of 4F2 sized 2bit MLC cells at the condition of chip area x cell efficiency=100mm <sup>2</sup> ————————90                                                                                                                                                                                                                        |

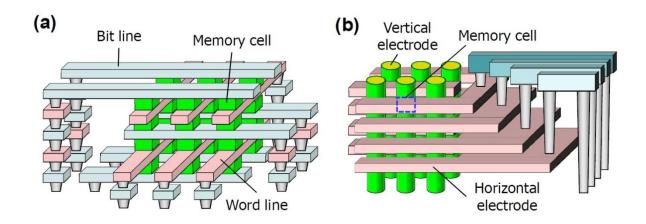

| Figure 5-2  | Schematics of the traditional crosspoint structure (a) and vertical 3D structure (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

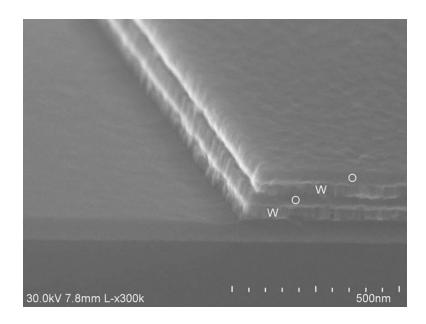

| Figure 5-3  | Scanning electron micrograph after the bottom electrode stack etch93                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

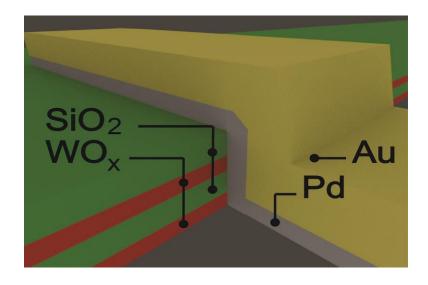

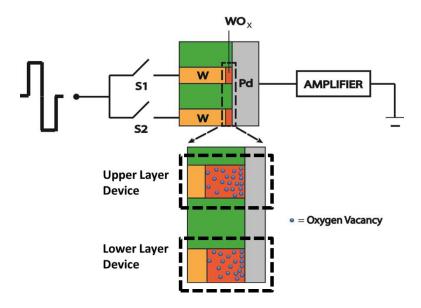

| Figure 5-4  | Schematic showing the dual layer device structure94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

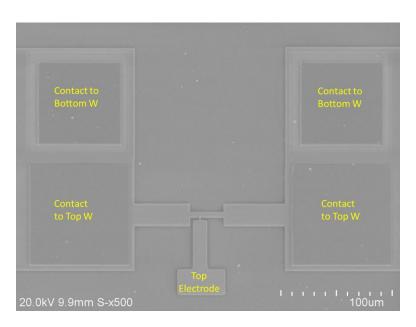

| Figure 5-5  | Contacts to the bottom W and top W layers were opened using lithography and RIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

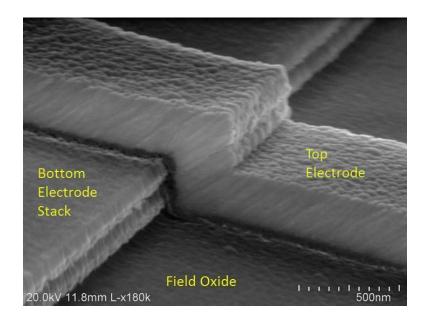

| Figure 5-6  | Scanning electron micrograph of the completed device95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 5-7  | Experimental setup for electrical characterization of the dual layer device96                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

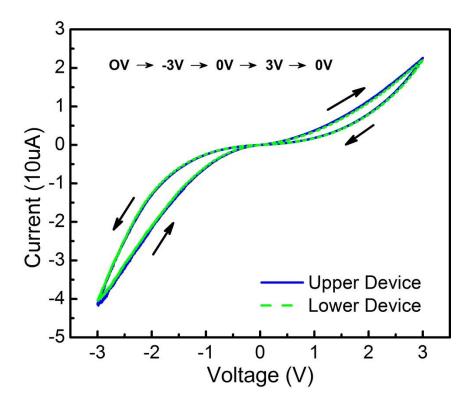

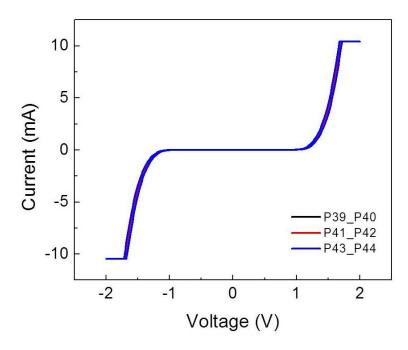

| Figure 5-8  | I-V plot for each device in the dual layer structure97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

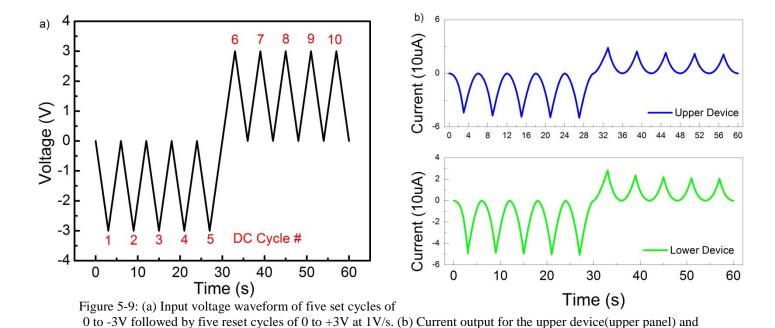

| Figure 5-9  | (a) Input voltage waveform of five set cycles of 0 to -3V followed by five reservoycles of 0 to +3V at 1V/s. (b) Current output for the upper device(upper panel) and the lower device (lower panel)                                                                                                                                                                                                                                                                                                                                            |

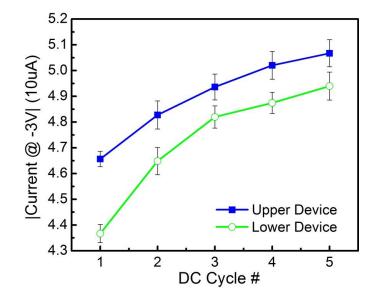

| Figure 5-10 | Incremental change of the maximum current during DC programming for both devices. The error bars were obtained from five different DC sweep measurements                                                                                                                                                                                                                                                                                                                                                                                        |

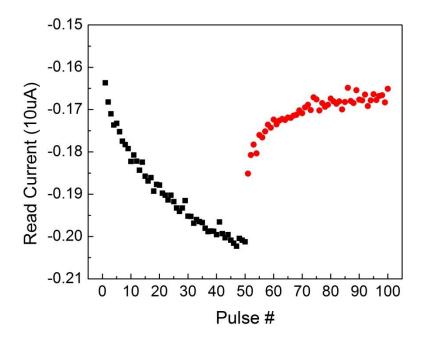

| Figure 5-11 | Write/erase voltages were applied to the device in the form of 50 write pulses followed by 50 erase pulses. Read current after each voltage pulse is measured and plotted. Each write pulse was -3V/400us and each erase pulse was +3V/400us. The read voltage pulse was -0.8V/10ms. Upper device in the dual layer stack was used for this test |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-12 | A representation showing the similarity between a biological synapse and a RRAM device                                                                                                                                                                                                                                                           |

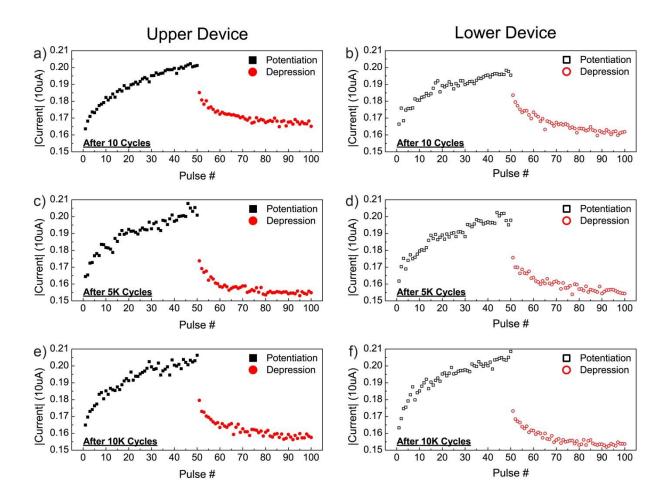

| Figure 5-13 | Current measured after consecutive potentiation (-3V/400us) and depression pulses (3V/400us) for the upper device (a) and lower device (b). Each cycle comprises of 50 potentiation pulses and 50 depression pulses. The read voltage was -0.8V. The device performance remains unchanged after 5000 cycles (c, d) and 10000 cycles (e, f)       |

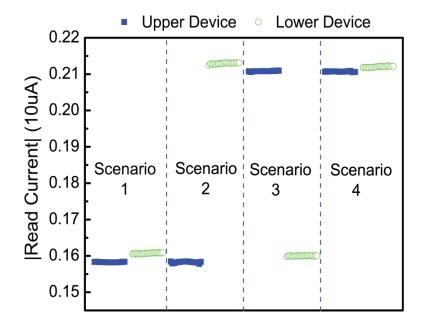

| Figure 5-14 | Independent programing/read of devices in the dual-layer structure. The read currents obtained during 20 consecutive read pulses were plotted for the four scenarios after the upper/lower device has been reset/reset, reset/set, set/reset, and set/set                                                                                        |

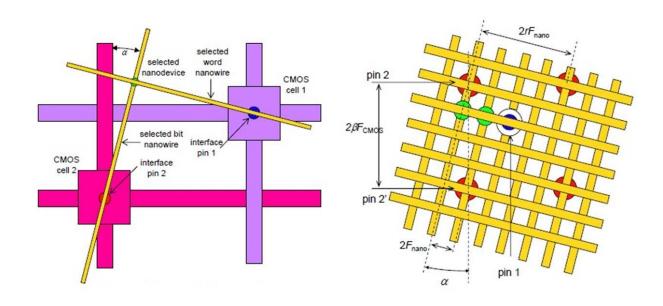

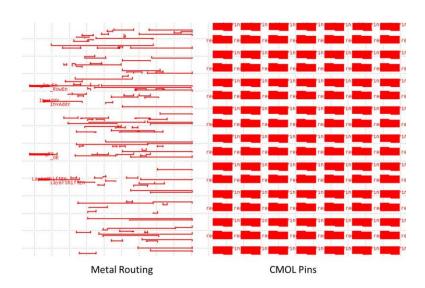

| Figure 6-1  | Representation of connection of CMOS cells and resistive switches using a CMOL approach                                                                                                                                                                                                                                                          |

| Figure 6-2  | Each nano-device or resistive switch can be addressed by a red pin and a blue pin (a). By tilting the crossbars by angle $\alpha$ , each resistive switch can be uniquely addressed by a red pin and a blue pin, without the need for perfect alignment111                                                                                       |

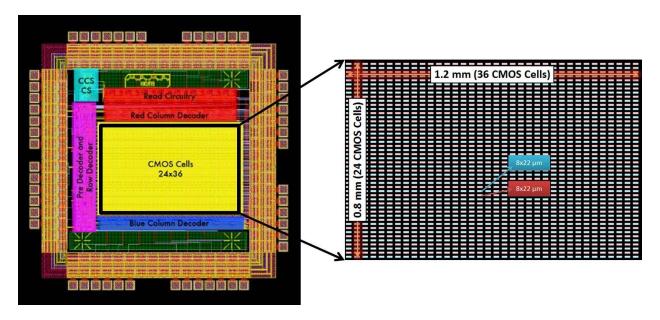

| Figure 6-3  | Block diagram of the test chip (a). The red and blue pins are designed using the top metal (M3) and form an array in the center of the test chip (b)                                                                                                                                                                                             |

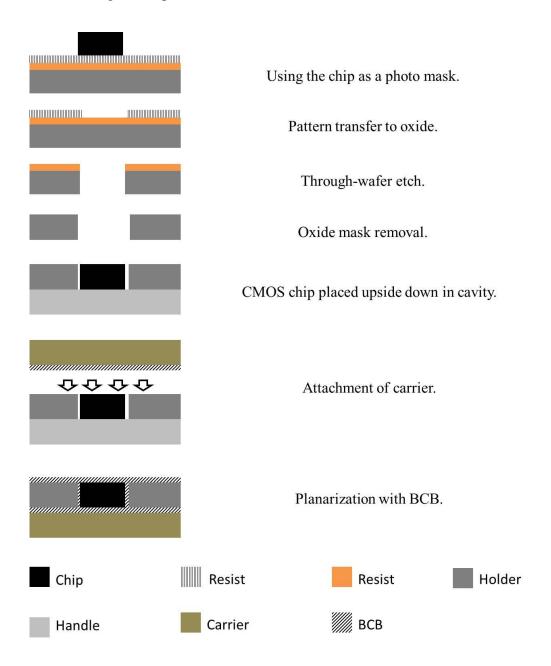

| Figure 6-4  | Wafer level integration scheme used to integrate the 2mm x 2mm chip onto a large piece of silicon                                                                                                                                                                                                                                                |

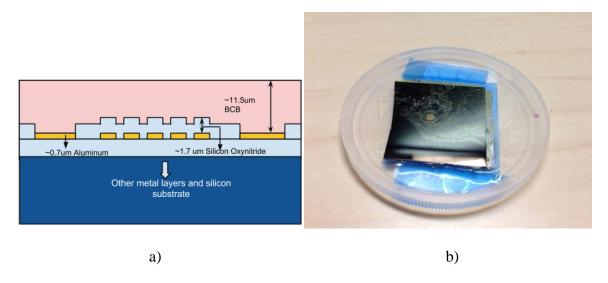

| Figure 6-5  | Photograph of the CMOS IC mounted onto a larger piece of silicon (a). (The round plastic wafer carrier has a diameter of 2 inches, for size reference). A schematic showing the CMOS pins buried under a thick film of BCB after the wafer level integration process has been completed.                                                         |

| Figure 6-6  | Low (a) and high magnification (b) optical images of the CMOS pins after etching away the BCB film. Scanning electron micrographs taken at 35 degree tilt show that the CMOS pins(c) and the I/O pads (d) are completely exposed                                                                                                                 |

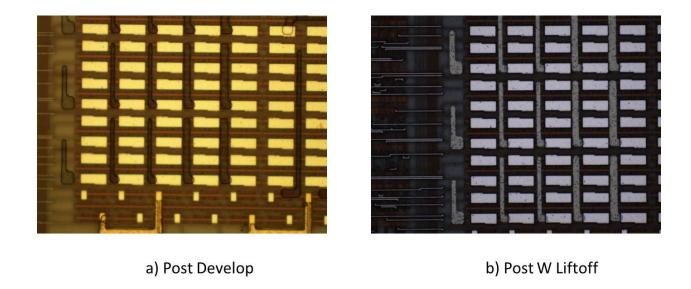

| Figure 6-7  | Optical micrographs of the CMOS chip after develop step and after the W liftoff step                                                                                                                                                                                                                                                             |

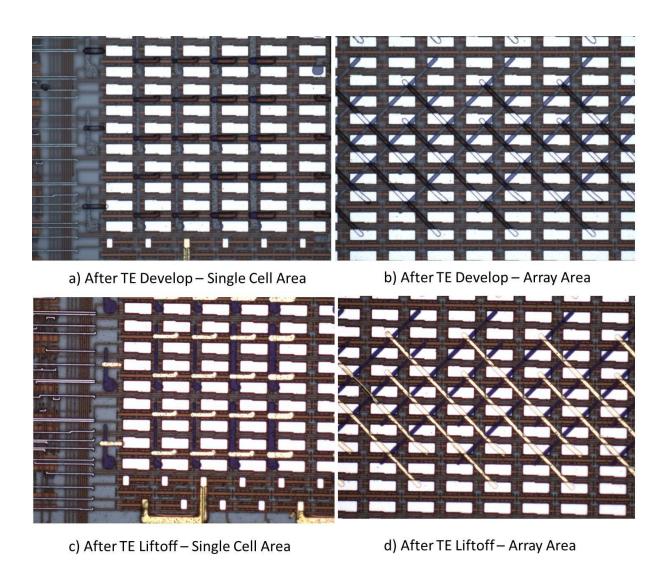

| Figure 6-8  | Optical micrographs of the CMOS chip after develop step (a,b) and after the Pd liftoff step (c,d)                                                                                                                                                                                                                                                |

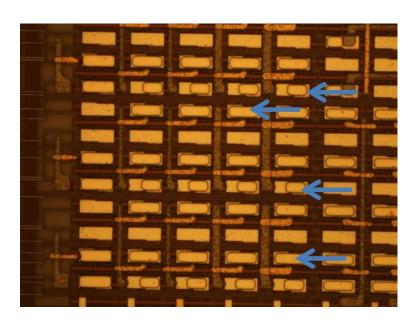

| Figure 6-9  | Optical micrograph of the vias etched in the PECVD ILD to access the CMOL pins                                                                                                                                                                                                                                                                   |

| Figure 6-10 | Optical scope images of the final metal liftoff step to connect the RRAM devices to the CMOL pins                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

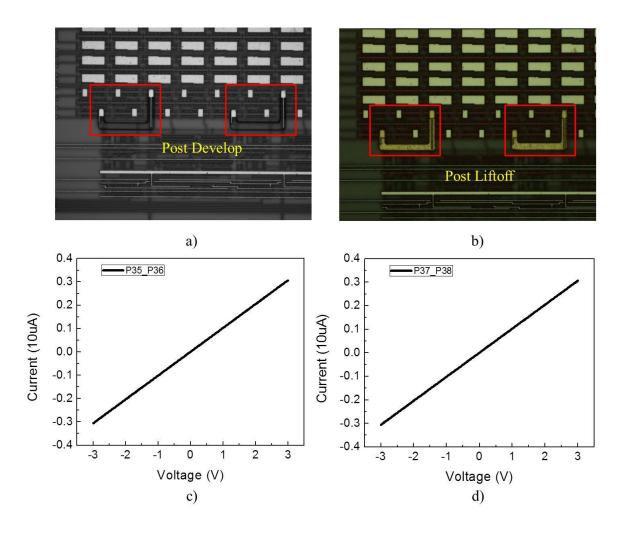

| Figure 6-11 | Optical image of the etch end point test structure – post develop (a) and post liftoff (b). Good contact to the CMOL pins is indicated by the linear I-V(c and d). Two test structures (I/O pad 35/36 and I/O pad 37/38) show similar results. ). A 1M series resistor was used to prevent any damage to the metal lines due to Joule heating. |

| Figure 6-12 | Current thorough ESD diode (instead of the current through the test devices) is measured by probing the I/O pads with test devices due to the shunt connection of the ESD diodes                                                                                                                                                               |

| Figure 6-13 | Top metal layer is used for defining both the CMOL pins and also for signal routing                                                                                                                                                                                                                                                            |

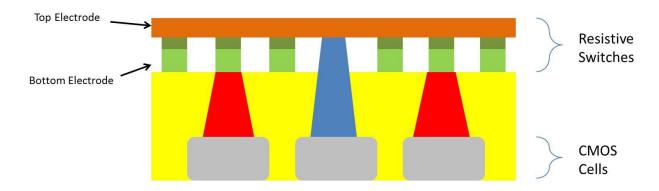

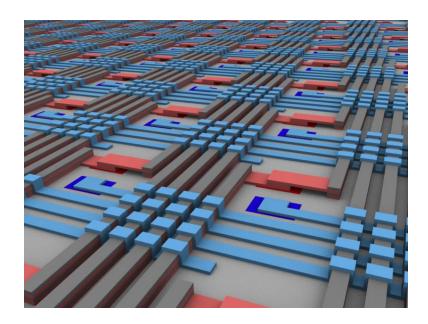

| Figure 6-14 | Representation of a dual layer crossbar vertically integrated on top of the CMOS pins                                                                                                                                                                                                                                                          |

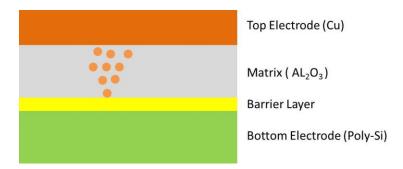

| Figure 6-15 | Insertion of a barrier layer to prevent over-programming of the device and to achieve self-compliance                                                                                                                                                                                                                                          |

# LIST OF TABLES

| Table 2-1 | Traditional metals used in commercial CMOS applications                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-2 | Fabrication process flow for the vertically integrated devices                                                                                                                                                |

| Table 3-1 | Fabrication flow used to fabricate cross-point devices based on the Ag / a-Si / poly-Si sandwich structure                                                                                                    |

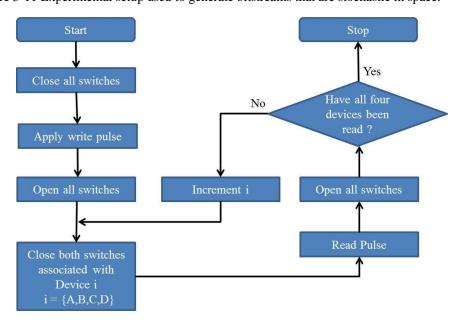

| Table 3-2 | Flowchart representing the parallel write and serial read of four devices. The analog switches are controlled by a microcontroller which is programmed using MATLAB before initiating the measurement routine |

| Table 4-1 | Comparison of the Cu/Al <sub>2</sub> O <sub>3</sub> /Poly-Si devices with other recent low current systems                                                                                                    |

| Table 6-1 | Brief description of the process flow for the hybrid CMOS-RRAM test chip119                                                                                                                                   |

#### **ABSTRACT**

Non-volatile memories play an indispensable role in today's electronic systems and information driven society. Mainstream non-volatile memory technology, dominated by the floating gate transistor, has historically improved in density, performance and cost primarily by means of process scaling. This simple geometrical scaling now faces significant challenges due to fundamental constraints of electrostatics and reliability. Therefore novel non-transistor based memory paradigms are being widely explored by both industry and academia. Among the various contenders for next generation storage technology, resistive switching memory devices have got immense attention due to their high speed, multilevel capability, scalability, simple structure, low voltage operation and high endurance.

In this thesis, we present studies on resistance switching memory devices. Electrical and material characterization was carried out on a metal-insulator-metal device system and formation / annihilation of nanoscale filaments was shown to be the reason behind the resistance switching behavior. The metal/insulator/metal system was optimized to include an in-cell resistor which was shown to improve device endurance and reduce stuck-at-one faults. For highest density, the devices were arranged in a crossbar geometry and vertically integrated on CMOS decoders to demonstrate the feasibility of practical data storage applications.

Next, we show that these binary resistive switching devices can exhibit native stochastic nature of resistive switching. Even for a fixed voltage on the same device, the wait time associated with programming is not fixed but rather random and broadly distributed. However, the probability of switching can be predicted and controlled by the applied voltage and the pulse width used to program the device. These binary devices have been used to generate random bit streams with predicable bias ratios in time and space domains. The ability to produce random bit streams using binary resistive switching devices based on the native stochastic switching principle may potentially lead to novel non-von-Neumann, alternative computing paradigms.

Further, sub-1nA operating current devices showing pronounced rectifying behavior have been developed. This ultra-low current provides energy savings by minimizing programming erase and read currents. Despite having such low currents, excellent retention, on/off ratio and endurance have been demonstrated. Devices programmed with less than 1nA peak current pass 6 hour retention test at 85 °C and show no significant degradation after 10000 write/erase cycles and with good switching uniformity. Due to the partially written filament, the devices exhibit pronounced non-linear I-V and current rectification in the on-state at the low bias regime – both factors are very beneficial for array operation. Also, the filament shape can be modulated by controlling the compliance current to obtain multilevel storage.

Finally a scalable approach to simple 3D stacking is discussed. By implementation of a vertical sidewall-based architecture, the number of critical lithography steps can be reduced. A vertical device structure based on a W / WO<sub>x</sub> / Pd material system is developed. The devices show well-defined incremental resistance switching behavior and good endurance. The devices can be programmed with less than 10% mismatch and no apparent crosstalk. This scalable architecture is well suited for development of analog memory and neuromorphic systems.

## Chapter 1

### Introduction

### 1.1 Data Explosion

Our society's ever growing demand for information and entertainment has led to an explosive growth in the amount of storage capacity in almost every electronic device we use – from laptops, phones and tablets used for personal communication, entertainment and business to large commercial data centers and server farms where a big chunk of the world's big data resides. Non-volatile memory is also extensively used in controller chips that have touched every aspect of modern society from programmable coffee makers, microwaves, toys to smart sensors in cars and buildings to automated tools used in manufacturing. Data retrieval times and instant access needs have seen intense increase of popularity and adoption of FLASH memory compared to the older and slower hard disk technology.

#### 1.2 The NVM Workhorse: FLASH

Flash memory was developed by Toshiba in 1980s from electrically erasable programmable read-only memory (EEPROM). Flash memory can be written and read at the byte level (NOR Flash) or in in small blocks (NAND flash). Both types of flash – NAND and NOR-rely on the floating gate transistor to store information (Fig. 1-1). The floating gate transistor adds an extra gate and a tunneling oxide in addition to a normal MOS transistor. Programming is usually

done through FN tunneling or hot carrier injection and erasing of the cell is achieved by FN tunneling. The cell is nonvolatile in nature – charge trapped in the floating gate stays there for many years. It is this relatively simple structure and excellent data retention property that have made flash storage so popular in today's world.

Figure 1-1: Flash memory works by adding (charging) or removing (uncharging) electrons to and from a floating gate. A bit's 1 or 0 state depends upon whether the floating gate is charged or not.

While both NOR and NAND are based on floating gate transistors they use different logical connection of these transistors to map data. NOR flash provides high-speed random access,

reading and writing data in specific memory locations. Thus, NOR is typically used to store code such as cell phones' operating systems and in BIOS chips. NAND flash reads and writes sequentially at high speed, handling data in small blocks called pages. This type of flash is typically used to store data in solid-state and USB flash drives, digital cameras, audio and video players, and TV set-top boxes. NAND flash reads faster than it writes, quickly transferring whole pages of data. Less expensive than NOR flash, NAND flash technology offers higher capacity for the same-size silicon and dominates today's flash market.

## 1.3 Semiconductor Flash Memory Scaling

Flash memory application has seen explosive growth in recent years and this trend is likely to continue because new and more demanding applications are constantly added partly due to the need for low power solid-state storage and partly due to rapidly declining prices. Conventional floating gate flash memories, no matter in NOR or NAND architecture, however, face steep challenges[1–4]. In addition to conventional CMOS scaling issues like short channel effects, loss of gate control and patterning issues, flash memory faces additional unique challenges.

For tight spacing rules, floating gate interference and the need for sufficient gate control (gate coupling ratio) have questioned the continued scaling of the floating gate device below 10nm. With scaling, crosstalk between the neighboring floating gates, word lines and even the adjacent channels becomes non-negligible and starts to cause data corruption.

Figure 1-2: Diagram showing capacitive coupling in flash memory. Reproduced from [2]

Even though the channel dimensions scale, the dielectric thickness does not scale and is limited by the cell retention to about 50nm. The high voltage programming circuitry (~20V) needed for older generation also does not move towards lower voltages as the devices scale. Thus, running high voltages on metal lines with very small spacing raises endurance and reliability issues.

Further, as cell capacitance scales, less number for electrons are stored per unit shift in the threshold voltage. This causes higher impact and degradation from single electron events and increased 1/f noise. Channel electron trapping and de-trapping during read cause current to fluctuate resulting in increased random telegraph noise. Due to scaled channel lengths, channel dopant fluctuations increase the threshold voltage distributions. Continued degradation in threshold distribution width from cell scaling will eventually become unacceptable.

Fundamentally, the scalability of flash is based on charge which is quantized. With shrinking geometries, the number of electrons stored in the floating gate is fast reducing. At 20nm, there are less than 100 electrons present in the floating gate for a threshold of 1V. If 10% charge

loss during device lifetime is assumed to be within spec and retention specification is 10 years, this translates to 1 electron being lost per year.

Figure 1-3: The number of electrons stored vs. lithographic dimension and electron loss requirement for retention.

Reproduced from [2]

While recent development of 3D flash memory[5–9] will likely keep flash's dominance for the near future, such fundamental issues with flash scaling have forced both industry and academia to consider other non-charge based storage. Some of the more prominent emerging non-volatile memory devices are discussed on the next section.

#### 1.4 Emerging Non-Volatile Memories

Due to this uncertain future of flash memory and the associated challenges, other non-volatile memory architectures are being explored. These include PCRAM, FeRAM and MRAM.

PCRAM or phase change random access memory (also known as phase change memory, ovonic unified memory or chalcogenide memory) relies on phase change of a material from an amorphous state to a crystalline state[10–12]. Each state has a distinct electrical conductivity which is sensed with a read process and interpreted as a 1 or a 0 for information storage purposes.

Phase change memory bit cells use localized joule heating to convert the switching material (generally a chalcogenide) from an amorphous phase (low conductivity or a binary 0) to a crystalline phase (high conductivity or a binary 1) or vice versa. In almost all prototype PCRAM devices, a chalcogenide alloy of germanium, antimony and tellurium (GeSbTe or GST) is used[13]. When heated to a high temperature (>600 °C), it loses its crystallinity and can be frozen in an amorphous glass-like state. By heating it again to a temperature above its crystallization point, but below its melting point, the material transforms into a low resistance conductive state.

Figure 1-4: Programming of a PCM device involves application of electrical power through applied voltage, leading to internal temperature changes that either melt and then rapidly quench a volume of amorphous material during reset, or heat this volume at a lower temperature for sufficient time for recrystallization during set. A low voltage is used to sense the device resistance read so that the device state is not perturbed. Reproduced from [11].

Relatively high currents are needed for the crystalline to amorphous transition while a relatively long time (of the order of a 100ns) is used to fully convert the amorphous state to crystalline state. This continuous heating and quenching process results in a material expansion and contraction and causes significant thermal stress, which results in low device endurance[14]. Further, due to the thermal process involved, crosstalk between neighboring cells becomes an issue in large arrays.

FeRAM or ferroelectric RAM is similar in construction to a DRAM but uses a ferroelectric layer (typically lead zirconate titanate or PZT) instead of a dielectric layer in the capacitor to achieve non-volatility[15,16]. When an external electric field is applied across the ferroelectric layer, the dipoles tend to align themselves with the field direction, produced by small shifts in the positions of atoms and shifts in the distributions of electronic charge in the PZT crystal structure. After the charge is removed, the dipoles retain their polarization state. Binary "0"s and "1"s are stored as one of two possible electric polarizations in each data storage cell. It offers very low power consumption, very fast write performance and excellent endurance (often exceeding 1e16 cycles). However, a destructive read process makes its use as a replacement for flash less attractive. Further, CMOS compatibility, cost and density are the inhibiting factors which have prevented large scale adoption of FeRAM. While FeRAM devices from some manufacturers like Ramtron can now be found in niche areas like some electricity meters, air bag controllers, RAID disk controllers, RFID systems, FeRAM technology has failed to challenge flash as the medium of choice for large-scale data storage.

MRAM or magnetic RAM, in its simplest form, uses a magnetic tunneling junction to store information[17–19]. Two ferromagnetic plates, each of which can hold a magnetic field, are separated by an insulator. While one of the plates holds a permanent magnetic field, the field direction of the other can be switched. Due to the tunneling magnetic resistance effect, the electrical resistance of the cell changes due to the orientation of the fields in the two plates. By measuring the resulting current, the resistance inside any particular cell can be determined, and from this the polarity of the writable plate. Typically if the two plates have the same polarity this is considered to mean "1", while if the two plates are of opposite polarity the resistance will be higher and this translates to "0". Currently only one company (Everspin) produces a commercially

available 4Mbit part using an older 180nm process. MRAM still remains largely in the development phase. The large programming current and scalability issues (crosstalk issues when cell size scales) prevent it from being cost effective and challenging the well-established flash memory market.

Currently PCRAM, FeRAM and MRAM are in small volume production, but remain limited to niche applications. All the above have transitioned to the a commercial arena but have still failed to replace Flash

Resistive memory has recently emerged as another contender in the non-volatile memory race.

The next section introduces this memory concept and discusses why it stands to challenge the flash dominance.

#### **1.5 RRAM**

A RRAM device (or a resistive random access memory device) is a two terminal device in which a switching medium (or matrix) is sandwiched between top and bottom electrodes (Fig.1.1). The resistance of the device is modulated by applying voltage or current signals to the electrode(s). Unlike PCRAM, there is no phase change involved in RRAM.

Figure 1-5: a) A RRAM cell has a very simple structure - matrix material sandwiched between two electrodes. b)

The matrix resistance (high or low) is read out using a low voltage.

The basic idea is very simple and elegant: that a dielectric, which is normally insulating, can be made to conduct through a filament or conduction path formed after application of a sufficiently high voltage (or current). The conduction path formation can arise from different mechanisms, including defects, metal migration, etc. Once the filament is formed, it may be reset (broken, resulting in high resistance) or set (re-formed, resulting in lower resistance) by an appropriately applied voltage. This simple two terminal structure, among other things, is a reason for the popularity of RRAM devices among non-volatile memory researchers.

The first resistive switching effects were reported in the early 1960s[20]. Memories based on this concept never caught on due to concerns about scalability and stability and because of the emergence and rapid successful development of Si-based memories. Renewed interest in early 2000s[21–23] brought back the RRAM concept into limelight and it has been the focus of intense research in the last decade. The resistance switching effect has been observed in a broad range of materials including perovskites[24–27], binary metal oxides[28–31] and solid electrolytes[32–37].

While the exact classification based on mechanism is still debatable, these devices are often broadly sub-divided into two major categories based on the switching behavior: bipolar devices and unipolar devices. Bipolar devices need opposite voltage polarities for the two resistance transitions. For example, a device goes from high resistance (RESET) state to a low resistance (SET) state by application of a positive voltage higher than the threshold voltage. To RESET the device, a negative voltage must be applied. Since the devices show preference for switching polarities, the associated switching mechanism is electric field driven. Commonly used models and hypothesis include metal ion migration and redox processes [38-40] within a switching medium) and drift of oxygen vacancies[41,42]. Devices based on ion migration are often called conductive-bridge RAM (or CBRAM) while devices based on drift of oxygen vacancies are often simply called RRAM. This is different from unipolar devices where a single voltage polarity is enough to cause both transitions: SET to RESET and, also, RESET to SET. Because of lack of voltage polarity preference, Joule heating /thermal breakdown models are often used to describe such resistance switching behavior. RRAM has great potential as the memory of choice for next generation storage requirements. Non-volatility[39], sub-ns switching[43], high ON/OFF ratios[44], low switching voltages[39], (moderately) low current operation[45–48], capability to integrate multi-level characteristics [47,49,50] and high endurance have been demonstrated. A simple two terminal structure and absence of any select transistor has led to highly scaled bit cells often limited only by lithography. Further, RRAM does not suffer from any traditional scaling issues like short channel effects and loss of gate control. Since information is not stored as charge, there is no leakage or capacitive coupling issue like that in flash and DRAM. High performance devices have been shown with CMOS compatible materials and with minimum process

overheads[29, 41]. As a result, RRAM is considered as one of the most promising approaches for next generation memory needs, according to researchers in this field.

However, industry analysts and commercial companies have been a bit reserved in promoting RRAM primarily because the underlying mechanisms are not completely understood and the lack of systematic analysis of device performance including failure modes. Physics/device models still remain at a nascent stage. Most of the work done in the RRAM area has been experimental in nature and has thrown up a large number of materials as possible candidates for a commercially viable RRAM structure. In many studies, performance data comes from single isolated devices and not integrated large scale systems. Yield, cycle to cycle and device to device uniformity and array operation issues are also relatively unexplored areas.

This thesis attempts to explore some of these unknowns and endeavors to build a more holistic picture of RRAM devices and RRAM based systems.

## 1.6 Organization of the Thesis

In chapter 1, several essential topics pertaining to nonvolatile memory in general and resistive memory specifically have been discussed. In chapter 2, physical characterization studies (particularly in-situ transmission electron microscopy) are detailed. These studies explain the filamentary nature of resistive switching. Over-programming of the devices is shown to be linked to formation of robust filaments which can be prevented by incorporation of an in-cell resistor. This optimized structure is vertically integrated on a CMOS chip to show the feasibility of high density resistive memory and hybrid CMOS / RRAM systems.

In chapter 3, natural variations in switching parameters in resistive switching devices are shown to be due to the inherent stochastic nature of the switching process itself. Instead of forcing

the devices to behave in a deterministic way, the native non-determinism can be used to generate bit-streams. The use of these bit streams in stochastic computing are discussed.

The need for reduction of the operation current for resistive memories is described in Chapter 4. The retention-operating current tradeoff is discussed along with development of a novel device structure which can be programed and erased with less than 1nA. Despite such low currents, the device demonstrates excellent retention characteristics.

While all devices discussed in chapters 1-4 are 2D in nature, 3D scaling is discussed in chapter 5. A scalable device structure based on vertical sidewalls is developed. Mismatch between devices and properties like endurance and crosstalk are studied and characterized.

An implementation of a hybrid RRAM/CMOS architecture and future optimizations and studies are briefly mentioned in chapter 6.

#### References

- [1] C.-Y. Lu, K.-Y. Hsieh, and R. Liu, "Future challenges of flash memory technologies," Microelectron. Eng., vol. 86, no. 3, pp. 283–286, Mar. 2009.

- [2] K. Prall, "Scaling Non-Volatile Memory Below 30nm," 2007 22nd IEEE Non-Volatile Semicond. Mem. Work., pp. 5–10, 2007.

- [3] A. Fazio, "Flash memory scaling," MRS Bull., vol. 29, no. 11, pp. 814–817, 2004.

- [4] B. Govoreanu, D. P. Brunco, and J. Van Houdt, "Scaling down the interpoly dielectric for next generation Flash memory: Challenges and opportunities," Solid. State. Electron., vol. 49, no. 11, pp. 1841–1848, Nov. 2005.

- [5] H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and a. Nitayama, "Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory," 2007 IEEE Symp. VLSI Technol., pp. 14–15, Jun. 2007.

- [6] A. Hubert, E. Nowak, K. Tachi, C. Vizioz, C. Arvet, and J. Colonna, "A stacked SONOS technology, up to 4 levels and 6nm crystalline nanowires, with gate-all-around or independent gates (Φ-Flash), suitable for full 3D integration," Electron Devices Meet. (IEDM), 2009 IEEE Int. IEEE, pp. 637–640, 2009.

- [7] S. Whang, K. Lee, D. Shin, B. Kim, M. Kim, J. Bin, J. Han, S. Kim, B. Lee, Y. Jung, S. Cho, C. Shin, H. Yoo, S. Choi, K. Hong, S. Aritome, S. Park, and S. Hong, "Novel 3-dimensional Dual Control-gate with Surrounding Floating-gate (DC-SF) NAND flash cell for 1Tb file storage application," 2010 Int. Electron Devices Meet., pp. 29.7.1–29.7.4, Dec. 2010.

- [8] E.-S. Choi, H.-S. Yoo, H.-S. Joo, G.-S. Cho, S.-K. Park, and S.-K. Lee, "A Novel 3D Cell Array Architecture for Terra-Bit NAND Flash Memory," 2011 3rd IEEE Int. Mem. Work., pp. 1–4, May 2011.

- [9] A. Katsumata, R., Kito, M., Fukuzumi, Y., Kido, M., Tanaka, H., Komori, Y., Ishiduki, M., Matsunami, J., Fujiwara, T., Nagata, Y., Li Zhang, Iwata, Y., Kirisawa, R., Aochi, H., Nitayama, "Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices," 2009 Symp. VLSI Technol., pp. 136–7, 2009.

- [10] H.-S. P. Wong, S. Raoux, S. Kim, J. Liang, J. P. Reifenberg, B. Rajendran, M. Asheghi, and K. E. Goodson, "Phase Change Memory," Proc. IEEE, vol. 98, no. 12, pp. 2201–2227, Dec. 2010.

- [11] G. W. Burr, M. J. Breitwisch, M. Franceschini, D. Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, L. a. Lastras, A. Padilla, B. Rajendran, S. Raoux, and R. S. Shenoy, "Phase change memory technology," J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., vol. 28, no. 2, p. 223, 2010.

- [12] M. Wuttig and N. Yamada, "Phase-change materials for rewriteable data storage.," Nat. Mater., vol. 6, no. 11, pp. 824–32, Nov. 2007.

- [13] D. Lencer, M. Salinga, B. Grabowski, T. Hickel, J. Neugebauer, and M. Wuttig, "A map for phase-change materials.," Nat. Mater., vol. 7, no. 12, pp. 972–7, Dec. 2008.

- [14] L. Goux, D. Tio Castro, G. a. M. Hurkx, J. G. Lisoni, R. Delhougne, D. J. Gravesteijn, K. Attenborough, and D. J. Wouters, "Degradation of the Reset Switching During Endurance Testing of a Phase-Change Line Cell," IEEE Trans. Electron Devices, vol. 56, no. 2, pp. 354–358, Feb. 2009.

- [15] G. R. Fox, F. Chu, and T. Davenport, "Current and future ferroelectric nonvolatile memory technology," J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., vol. 19, no. 5, p. 1967, 2001.

- [16] S. L. Miller and P. J. McWhorter, "Physics of the ferroelectric nonvolatile memory field effect transistor," J. Appl. Phys., vol. 72, no. 12, p. 5999, 1992.

- [17] J. Slaughter and R. Dave, "Fundamentals of MRAM technology," J. Supercond., vol. 15, no. 1, pp. 19–25, 2002.

- [18] S. Tehrani, B. Engel, J. M. Slaughter, E. Chen, M. DeHerrera, M. Durlam, P. Naji, R. Whig, J. Janesky, and J. Calder, "Recent developments in magnetic tunnel junction MRAM," IEEE Trans. Magn., vol. 36, no. 5, pp. 2752–2757, 2000.

- [19] Y. Huai, "Spin-transfer torque MRAM (STT-MRAM): Challenges and prospects," AAPPS Bull., vol. 18, no. 6, pp. 33–40, 2008.

- [20] J. F. Gibbons, "Switching properties of thin NiO films," Solid. State. Electron., vol. 7, no. 2, pp. 785–797, 1964.

- [21] A. Beck, J. G. Bednorz, C. Gerber, C. Rossel, and D. Widmer, "Reproducible switching effect in thin oxide films for memory applications," Appl. Phys. Lett., vol. 77, no. 1, p. 139, 2000.

- [22] A. Shimaoka, K. Inoue, T. Naka, N. A. K. Sakiyama, Y. Wang, S. Q. Liu, N. J. Wu, and A. Ignatiev, "Novell Colossal Magnetoresistive Thin Film Nonvolatile Resistance Random Access Memory (RRAM)," IEDM, pp. 193–196, 2002.

- [23] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found.," Nature, vol. 453, no. 7191, pp. 80–3, May 2008.

- [24] X. Chen, N. Wu, J. Strozier, and A. Ignatiev, "Spatially extended nature of resistive switching in perovskite oxide thin films," Appl. Phys. Lett., vol. 89, no. 6, p. 063507, 2006.

- [25] K. Szot, W. Speier, G. Bihlmayer, and R. Waser, "Switching the electrical resistance of individual dislocations in single-crystalline SrTiO3.," Nat. Mater., vol. 5, no. 4, pp. 312– 20, Apr. 2006.

- [26] M. Hasan, R. Dong, H. J. Choi, D. S. Lee, D.-J. Seong, M. B. Pyun, and H. Hwang, "Uniform resistive switching with a thin reactive metal interface layer in metal-La0.7Ca0.3MnO3-metal heterostructures," Appl. Phys. Lett., vol. 92, no. 20, p. 202102, 2008.

- [27] A. Wang, "Bistable resistive switching of a sputter-deposited Cr-doped SrZrO3 memory film," IEEE Electron Device Lett., vol. 26, no. 6, pp. 351–353, Jun. 2005.

- [28] Z. Wei, Y. Kanzawa, and K. Arita, "Highly reliable TaOx ReRAM and direct evidence of redox reaction mechanism," Meet. 2008. IEDM, 2008.

- [29] J. J. Yang, M.-X. Zhang, J. P. Strachan, F. Miao, M. D. Pickett, R. D. Kelley, G. Medeiros-Ribeiro, and R. S. Williams, "High switching endurance in TaO x memristive devices," Appl. Phys. Lett., vol. 97, no. 23, p. 232102, 2010.

- [30] B. Govoreanu, G. S. Kar, Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I. P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, K. Seo, P. Hendrickx, G. Pourtois, H. Bender, L. Altimime, D. J. Wouters, J. A. Kittl, M. Jurczak, B.- Leuven, and K. U. Leuven, "10x10nm2 Hf / HfOx Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation," Electron Devices Meet. (IEDM), 2011 IEEE Int. IEEE, pp. 729–732, 2011.

- [31] S. Yu, X. Guan, and H.-S. P. Wong, "Conduction mechanism of TiN/HfOx/Pt resistive switching memory: A trap-assisted-tunneling model," Appl. Phys. Lett., vol. 99, no. 6, p. 063507, 2011.

- [32] D. Deleruyelle, M. Putero, T. Ouled-khachroum, M. Bocquet, M. Coulet, C. Calmes, C. Muller, E. Nationale, M. De Saint, C. D. M. De, P. G. Charpak, and D. Mimet, "Ge2Sb2Te5 layer used as solid electrolyte in Conductive-Bridge memory devices fabricated on flexible substrate," Solid State Electron., vol. 79, pp. 159–165, 2013.

- [33] Q. Liu, J. Sun, H. Lv, S. Long, K. Yin, N. Wan, Y. Li, L. Sun, and M. Liu, "Real-time observation on dynamic growth/dissolution of conductive filaments in oxide-electrolyte-based ReRAM.," Adv. Mater., vol. 24, no. 14, pp. 1844–9, Apr. 2012.

- [34] T. Fujii, M. Arita, Y. Takahashi, and I. Fujiwara, "In situ transmission electron microscopy analysis of conductive filament during solid electrolyte resistance switching," Appl. Phys. Lett., vol. 98, no. 21, p. 212104, 2011.

- [35] S. Z. Rahaman, S. Maikap, H.-C. Chiu, C.-H. Lin, T.-Y. Wu, Y.-S. Chen, P.-J. Tzeng, F. Chen, M.-J. Kao, and M.-J. Tsai, "Bipolar Resistive Switching Memory Using Cu Metallic Filament in Ge[sub 0.4]Se[sub 0.6] Solid Electrolyte," Electrochem. Solid-State Lett., vol. 13, no. 5, p. H159, 2010.

- [36] J. Jang, F. Pan, K. Braam, and V. Subramanian, "Resistance switching characteristics of solid electrolyte chalcogenide Ag(2)Se nanoparticles for flexible nonvolatile memory applications.," Adv. Mater., vol. 24, no. 26, pp. 3573–6, Jul. 2012.

- [37] S.-J. Choi, G.-S. Park, K.-H. Kim, S. Cho, W.-Y. Yang, X.-S. Li, J.-H. Moon, K.-J. Lee, and K. Kim, "In situ observation of voltage-induced multilevel resistive switching in solid electrolyte memory.," Adv. Mater., vol. 23, no. 29, pp. 3272–7, Aug. 2011.

- [38] P. Sheridan, K.-H. Kim, S. Gaba, T. Chang, L. Chen, and W. Lu, "Device and SPICE modeling of RRAM devices.," Nanoscale, vol. 3, no. 9, pp. 3833–40, Sep. 2011.

- [39] S. H. Jo and W. Lu, "CMOS compatible nanoscale nonvolatile resistance switching memory.," Nano Lett., vol. 8, no. 2, pp. 392–7, Feb. 2008.

- [40] S. H. Jo, K.-H. Kim, and W. Lu, "Programmable resistance switching in nanoscale two-terminal devices.," Nano Lett., vol. 9, no. 1, pp. 496–500, Jan. 2009.

- [41] T. Chang, S.-H. Jo, K.-H. Kim, P. Sheridan, S. Gaba, and W. Lu, "Synaptic behaviors and modeling of a metal oxide memristive device," Appl. Phys. A, vol. 102, no. 4, pp. 857–863, Feb. 2011.

- [42] N. Raghavan, K. Pey, and X. Li, "Very low reset current for an RRAM device achieved in the oxygen-vacancy-controlled regime," Electron Device Lett., vol. 32, no. 6, pp. 716–718, 2011.