## **Energy-Efficient Digital Signal Processing Hardware Design**

by

**Dongsuk Jeon**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctorate of Philosophy (Electrical Engineering) in the University of Michigan 2014

**Doctoral Committee:**

Professor Dennis M. Sylvester, Chair Professor David Blaauw Professor Katsuo Kurabayashi Assistant Professor Zhengya Zhang © Dongsuk Jeon

All Rights Reserved 2014

To God and my family with love and gratitude

### ACKNOWLEDGEMENTS

I have been very fortunate to meet great people along the way. Many people have helped me throughout my Ph.D., but no one was more crucial than my advisor, Prof. Dennis Sylvester. Since I started this journey not knowing the way forward, he has guided me with insightful advice in many aspects. Without his continuous support and encouragement, I would have never completed any project in this dissertation. What I have learned from him is not limited to circuit designs, but spans over how to look at the big picture and manage research. I am also very indebted to Prof. David Blaauw for his insightful feedbacks. He has always been enthusiastic whenever I wanted to discuss about technical details and new ideas, and gladly given invaluable advice about the things that can be easily disregarded. I also would like to thank other committee members, Prof. Zhengya Zhang and Katsuo Kurabayashi for their key questions and helpful feedbacks. I would especially like to thank Zhengya for being a great mentor and sharing his experience as a senior in DSP hardware design area. Prof. Chaitali Chakrabarti also provided lots of help in the FFT processor design in Chapter 2.

Most works in this dissertation were completed through much support from the industry. STMicroelectronics and TSMC have generously provided chip fabrication, and Samsung Scholarship Foundation has provided financial support for the entire period. During summer internships at Texas Instruments and imec, I met many great mentors including Manish Goel, Seok-Jun Lee from TI, Refet Firat Yazicioglu and Hyejung Kim from imec who all inspired me with their expertise in various areas.

I am indebted to many of my colleagues for their help and advice during my time at Michigan. I worked closely with Mingoo Seok in the FFT project in Chapter 2, and he taught me nearly everything about digital circuit design. I am grateful to Yejoong Kim for many discussions and his help in other 3 projects in Chapter 4, 5 and 6. I enjoyed working with Yen-Po Chen and Qing Dong whose help was crucial in the ECG and face recognition projects. I also thank other co-authors, Yoonmyung Lee, Inhee Lee, Michael Henry and Zhiyoong Foo for their crucial help. I need to say that Prof. Hao Yu, Prof. Tony Tae-Hyoung Kim, Xiaolong Wang and Shuai Chen made my time at NTU in Singapore an invaluable research experience.

Since joining our research group, I have had a great time with fellow students here. I have learned a lot about circuit design and related knowledge from Jae-sun Seo, Daeyeon Kim, David Fick, Michael Wieckowski, Sudhir Satpathy, Matt Fojtik, Bharan Giridhar, Gyouho Kim, Dongmin Yoon, Nathaniel Pinckney, Suyoung Bang, Laura Freyman, Seok-Hyeon Jeong, Sechang Oh, Myungjoon Choi, Taekwang Jang, and Wootaek Lim.

Finally, but not least, I am very grateful to my family for their continuous support throughout my graduate study.

## **TABLE OF CONTENTS**

| DEDIC  | ATION   | ii                                                                  |

|--------|---------|---------------------------------------------------------------------|

| ACKNO  | WLED    | GEMENTS                                                             |

| LIST O | F FIGU  | <b>RES</b>                                                          |

| LIST O | F TABL  | <b>ES</b>                                                           |

| СНАРТ  | ER      |                                                                     |

| 1      | Introdu | uction                                                              |

|        | 1.1     | Voltage Scaling                                                     |

|        | 1.2     | Timing Error Management                                             |

|        | 1.3     | Architecture and Algorithm Optimization                             |

|        | 1.4     | Dissertation Overview                                               |

| 2      | Energy  | P-Optimized FFT Processor                                           |

|        | 2.1     | Introduction                                                        |

|        | 2.2     | Energy-optimal FFT Architecture                                     |

|        |         | 2.2.1 Modified R4MDC architecture                                   |

|        |         | 2.2.2 Parallel-pipelined architecture                               |

|        | 2.3     | Robust Subthreshold FIFO Design                                     |

|        | 2.4     | Clock Distribution Network                                          |

|        | 2.5     | Measurement Results                                                 |

|        | 2.6     | Conclusions                                                         |

| 3      | Design  | Methodology for Voltage Overscaled Ultra-Low Power Systems 25       |

|        | 3.1     | Introduction                                                        |

|        | 3.2     | Related Work                                                        |

|        |         | 3.2.1 Error-tolerant DSP applications                               |

|        |         | 3.2.2 Design approach for voltage overscaled systems                |

|        | 3.3     | Error Analysis in Voltage Overscaled Systems                        |

|        |         | 3.3.1 Ripple carry adder starting point                             |

|        |         | 3.3.2 Generalized critical path delay model                         |

|        |         | 3.3.3 Model verification with pipelined Baugh-Wooley multipliers 31 |

|        |         |                                                                     |

|        | 3.4            | Case Study: Error-Resilient K-Best Decoder                    | 36  |

|--------|----------------|---------------------------------------------------------------|-----|

|        | 3.5            | Conclusions                                                   | 41  |

| 4      | Energy         | -Optimized Feature Extraction Accelerator                     | 43  |

|        | 4.1            | Introduction                                                  | 43  |

|        | 4.2            | Proposed Visual Feature Extraction Algorithm                  | 44  |

|        |                | 4.2.1 Visual feature extraction                               | 44  |

|        |                | 4.2.2 Proposed hardware-oriented feature extraction algorithm | 46  |

|        | 4.3            | Energy-Efficient Hardware Architecture                        | 51  |

|        |                | 4.3.1 Accelerator architecture                                | 51  |

|        |                | 4.3.2 Parallelized filters and arithmetic blocks              | 54  |

|        |                | 4.3.3 Single stream descriptor                                | 56  |

|        | 4.4            | Latch-based Low-Power and Robust FIFO Design                  | 58  |

|        | 4.5            | Measurement Results                                           | 65  |

|        | 4.6            | Conclusions                                                   | 67  |

| 5      | Implan         | table ECG Monitoring System                                   | 68  |

|        | 5.1            | Introduction                                                  | 68  |

|        | 5.2            | Proposed ECG Monitoring System                                | 69  |

|        | 5.3            | Hardware design and optimization techniques                   | 71  |

|        |                | 5.3.1 Analog front end optimization                           | 71  |

|        |                | 5.3.2 Digital back end design                                 | 73  |

|        | 5.4            | Measurement Results                                           | 79  |

|        | 5.5            | Conclusions                                                   | 84  |

| 6      | Low-p          | ower Face Detection and Recognition Accelerator               | 85  |

|        | 6.1            | Introduction                                                  | 85  |

|        | 6.2            | Face Detection and Recognition Algorithm                      | 87  |

|        | 6.3            | Proposed Hardware Architecture                                | 88  |

|        | 6.4            | Write-Once Read-Only 5T SRAM                                  | 91  |

|        | 6.5            | Implementation                                                | 97  |

|        | 6.6            | Conclusions                                                   | 97  |

| 7      | Conclu         | isions                                                        | 98  |

| BIBLIO | GRAPI          | HY                                                            | 100 |

|        | <b>J 1 1 1</b> | **                                                            | 100 |

# LIST OF FIGURES

#### Figure

| 1.1  | ARM Cortex-M4 processor architecture optimized for digital signal processing applications [3] | 2  |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.2  | Simulated energy as a function of power supply voltage [10].                                  | 2  |

| 1.3  | Process variation in SRAM hold noise margin in super and sub-threshold operation              |    |

|      | regions [11]                                                                                  | 3  |

| 1.4  | Basic Razor flip-flop [13].                                                                   | 4  |

| 1.5  | Algorithmic noise tolerance technique [15].                                                   | 5  |

| 1.6  | An example of application-specific efficient hardware architecture [7]                        | 6  |

| 2.1  | (a) Memory-based architecture and (b) R4MDC pipelined architecture                            | 11 |

| 2.2  | Modified R4MDC architecture for 1024-pt FFT                                                   | 13 |

| 2.3  | FFT core architecture with 2 processing lanes                                                 | 14 |

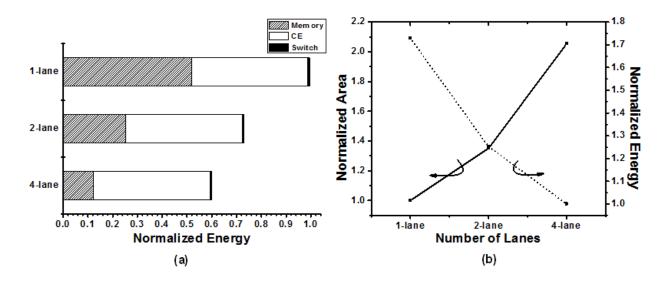

| 2.4  | (a) Energy breakdown and (b) energy-area tradeoff of parallel-pipelined architec-             |    |

|      | tures                                                                                         | 15 |

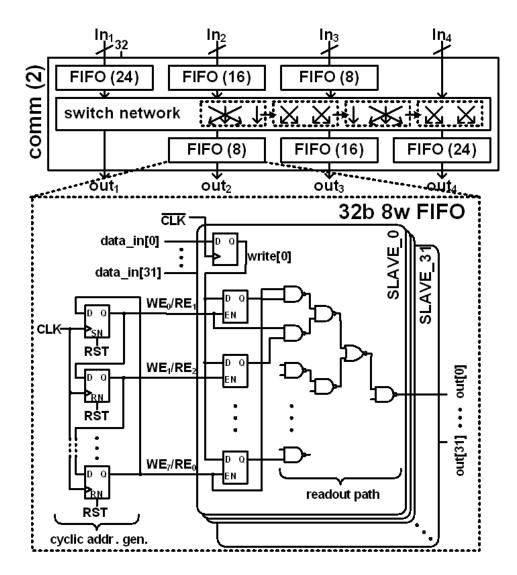

| 2.5  | Proposed 8-word FIFO design with commutator architecture                                      | 17 |

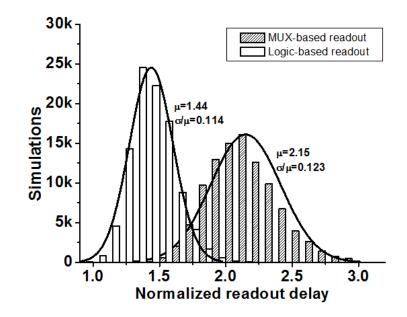

| 2.6  | Readout delay distributions from 100k Monte-Carlo SPICE simulations                           | 18 |

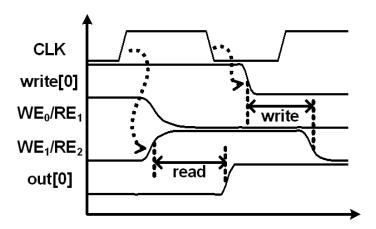

| 2.7  | Positive-edge read and negative-edge write scheme                                             | 19 |

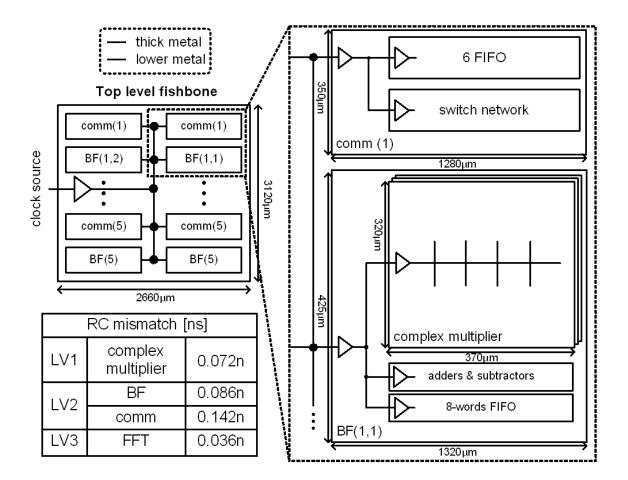

| 2.8  | RC-matched 3-level clock distribution network along with maximum RC mis-                      |    |

|      | match values.                                                                                 | 20 |

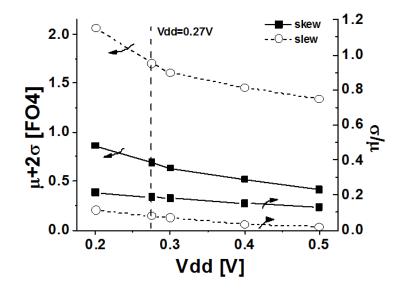

| 2.9  | Simulated clock skew and slew rates in proposed clock network design                          | 20 |

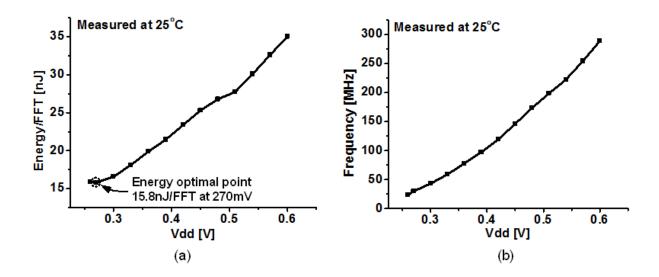

| 2.10 |                                                                                               | 21 |

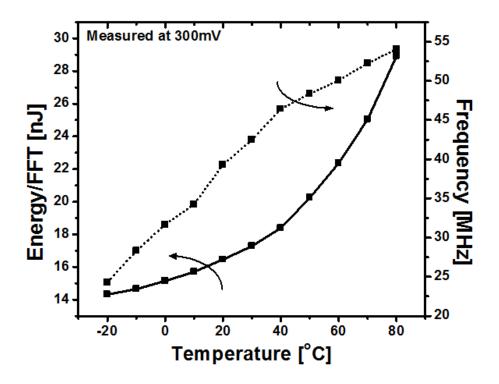

| 2.11 | Measured performance and energy consumption as a function of temperature                      | 22 |

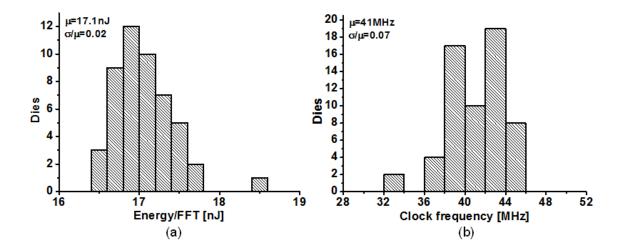

| 2.12 | Measured energy (a) and performance (b) distributions at Vdd = $300$ mV                       | 23 |

| 2.13 |                                                                                               | 23 |

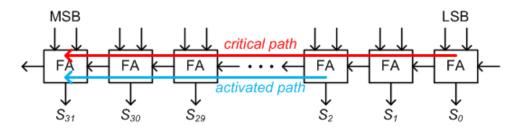

| 3.1  | Critical path and an example activated path in a 32-bit ripple carry adder                    | 28 |

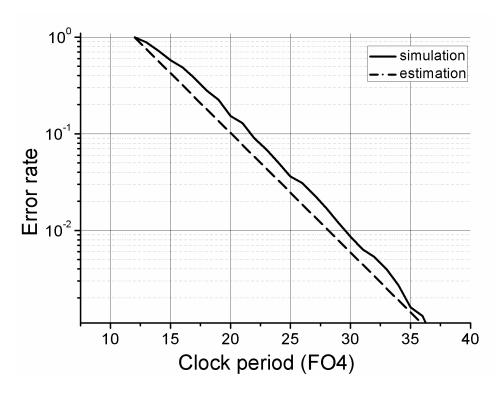

| 3.2  | Error rate of RCA from simulation and proposed equation.                                      | 29 |

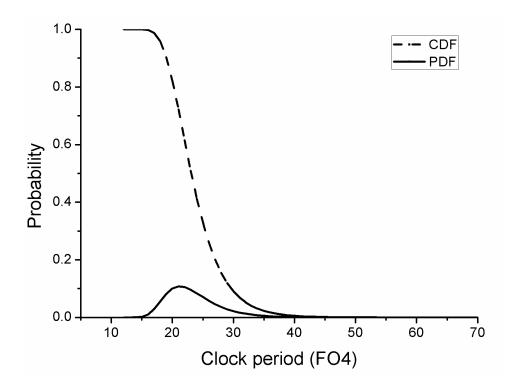

| 3.3  | Error rate considering multiple critical paths.                                               | 30 |

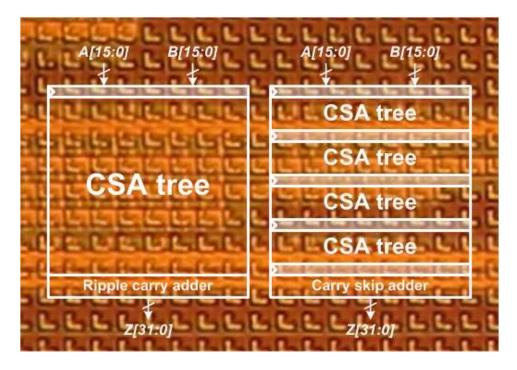

| 3.4  | Fabricated un-pipelined and 5-stage pipelined multipliers in 65nm                             | 32 |

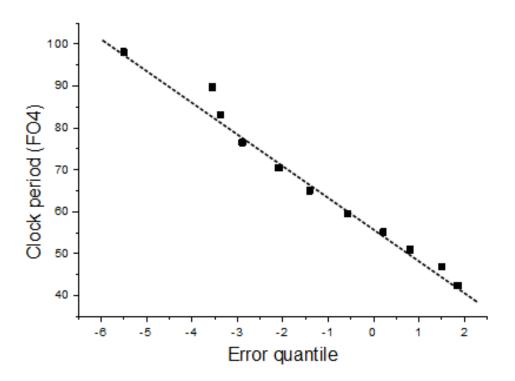

| 3.5  | Error rate quantile-clock period plot from measurements of the un-pipelined mul-              |    |

|      | tiplier                                                                                       | 32 |

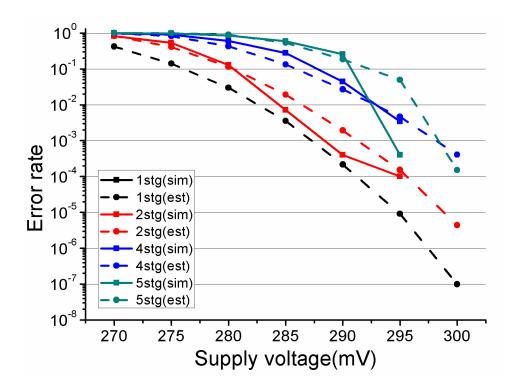

| 3.6  | Simulated and estimated error rates of various multiplier designs                             | 34 |

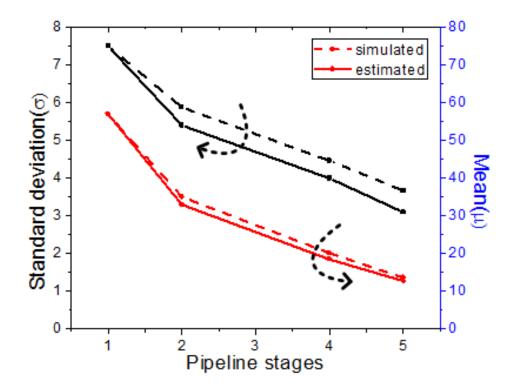

| 3.7   | $\mu$ and $\sigma$ from simulation and the proposed model                           | 34 |

|-------|-------------------------------------------------------------------------------------|----|

| 3.8   | Measurements of un-pipelined and 5-stage pipelined multipliers                      | 35 |

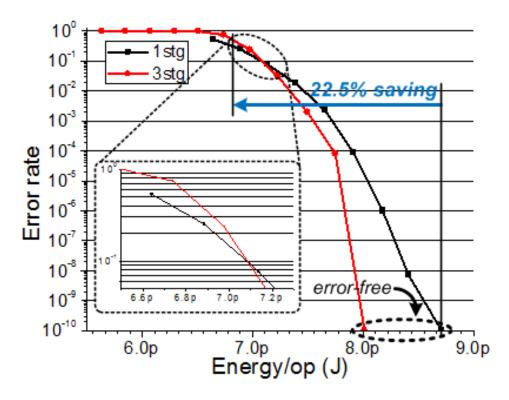

| 3.9   | Energy consumption-error rate plot from simulation.                                 | 35 |

| 3.10  | K-best decoder architecture.                                                        | 36 |

| 3.11  | Voltage overscaled CE assignment scheme.                                            | 37 |

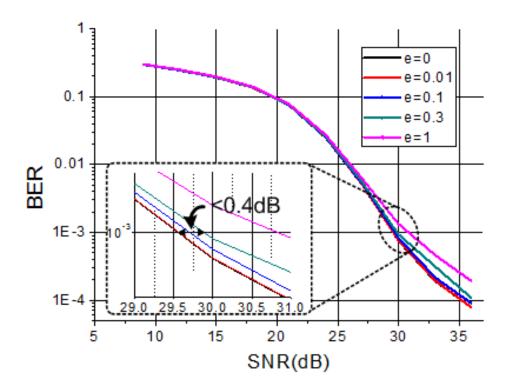

| 3.12  | SNR-BER plot for different error rates.                                             | 38 |

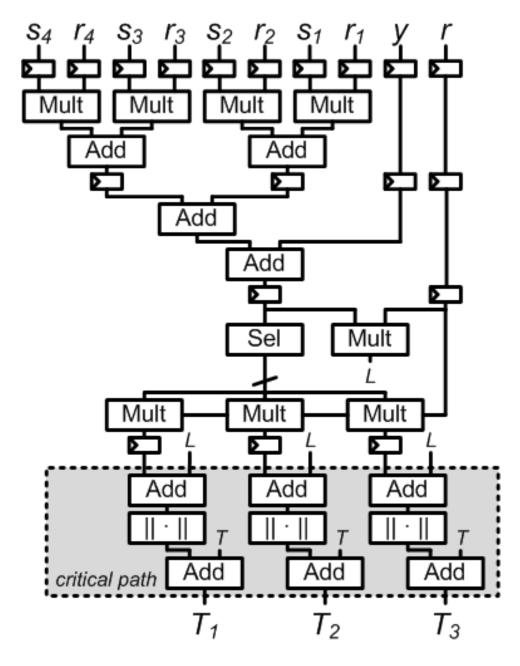

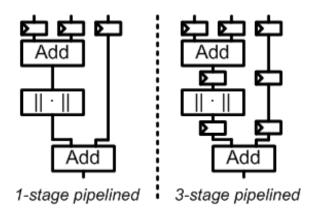

| 3.13  | Detailed CE architecture.                                                           | 39 |

| 3.14  | Two different pipeline stage assignments for critical path                          | 40 |

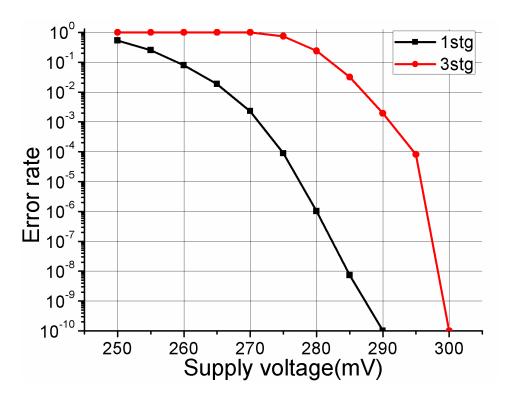

| 3.15  | Error rate of voltage-overscaled CEs                                                | 40 |

| 3.16  | Energy-error rate tradeoffs of CE for different pipeline depths                     | 41 |

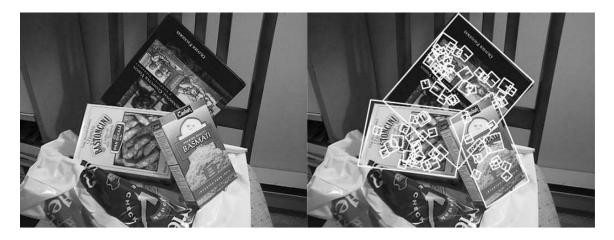

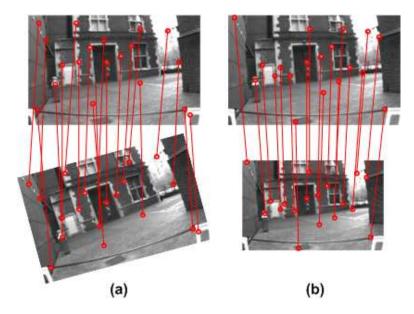

| 4.1   | An example of object recognition using extracted features [58]                      | 44 |

| 4.2   | Two key constraints of feature extraction algorithms: (a) rotation and (b) scale    |    |

|       | invariance                                                                          | 45 |

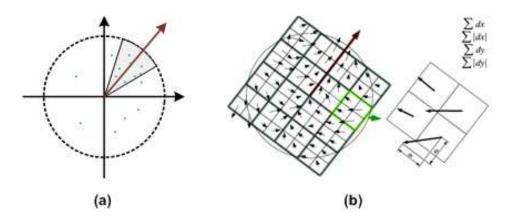

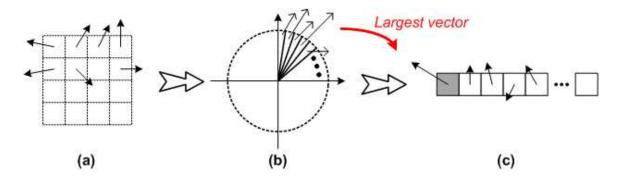

| 4.3   | Original feature vector generation process consisting of (a) orientation assignment |    |

|       | and (b) feature vector generation [59]                                              | 45 |

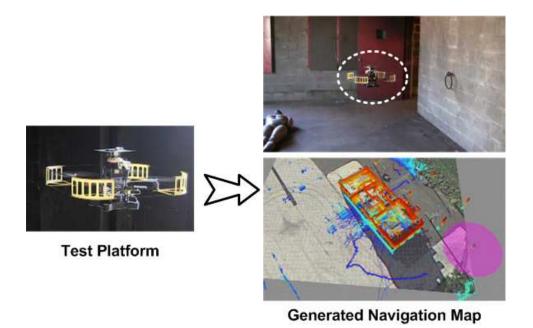

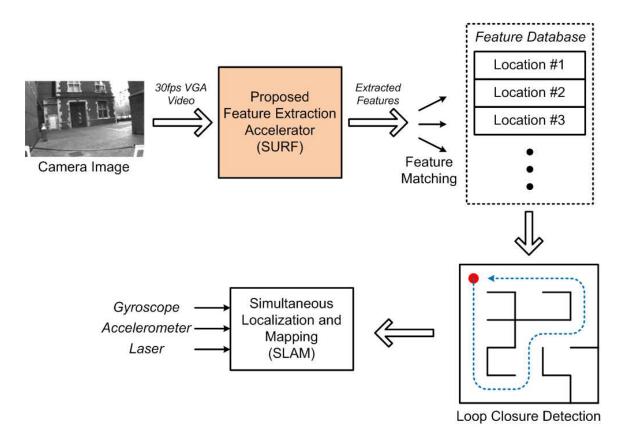

| 4.4   | A target application of MAV with visual navigation.                                 | 47 |

| 4.5   | An overview of the visual navigation algorithm flow.                                | 47 |

| 4.6   | Proposed (a) single-octave scale space; and (b) fast localization techniques for    |    |

|       | detector optimization.                                                              | 49 |

| 4.7   | Proposed circular-shaped sampling region approach.                                  | 49 |

| 4.8   | Unified description process consists of (a) filter response calculation; (b) summa- |    |

|       | tion in circular-shaped sampling region; and (c) reordering and normalization of    | -  |

|       | feature vector.                                                                     | 50 |

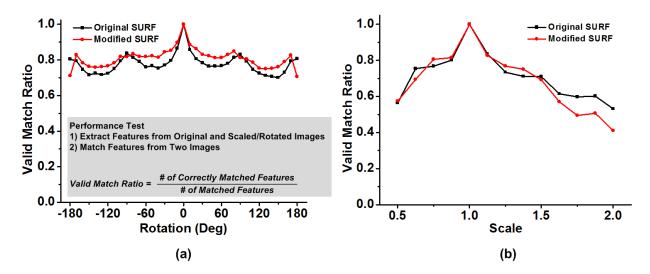

| 4.9   | (a) Rotation; and (b) scale invariance performance comparisons.                     | 51 |

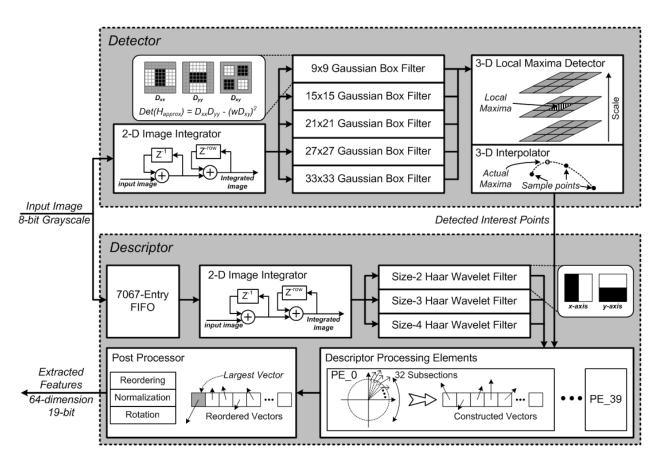

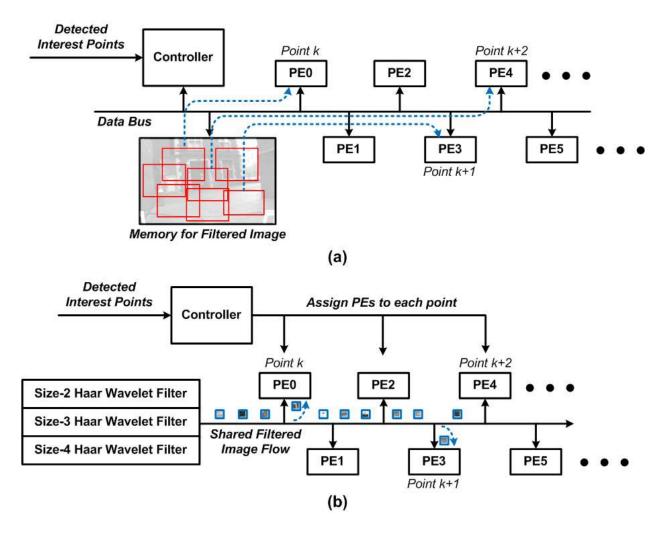

| 4.10  | Proposed feature extraction processor architecture.                                 | 52 |

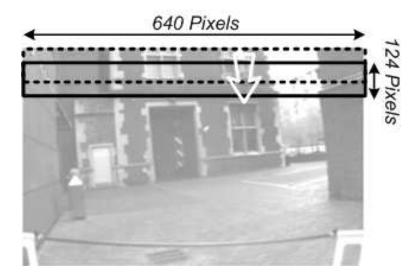

| 4.11  | Overlapped image subsections are processed successively to allow for proper fea-    | 50 |

| 4 10  | ture extraction at boundaries.                                                      | 52 |

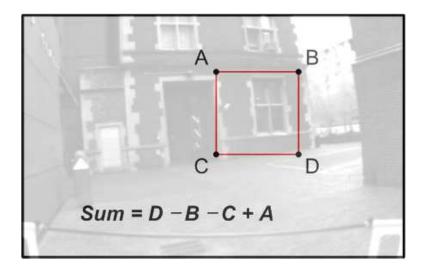

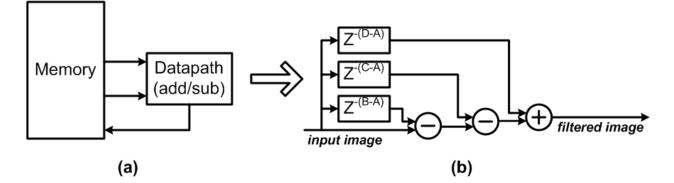

| 4.12  | Image summation in a rectangular region implemented with 3 arithmetic opera-        | 51 |

| 4 1 2 | tions on a 2-D integrated image.                                                    | 54 |

| 4.13  | Image summation calculators based on (a) a single datapath with memory and (b)      | 54 |

| 1 11  | multiple arithmetic units with different delay elements                             | 55 |

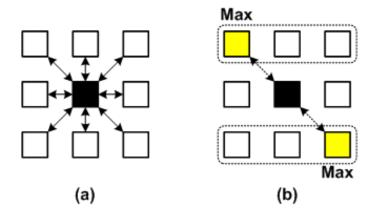

|       | (a) Original and (b) proposed local maxima detection schemes. In (b), maximum       | 55 |

| 4.13  | point of each row is already stored and only one comparison per row is required     | 56 |

| 4 16  | (a) Conventional multi-core architecture where each core communicates through a     | 50 |

| 4.10  | shared data bus independently. (b) Proposed architecture where a single response    |    |

|       | flows continuously through shared data bus and each core reads in only its required |    |

|       | blocks.                                                                             | 57 |

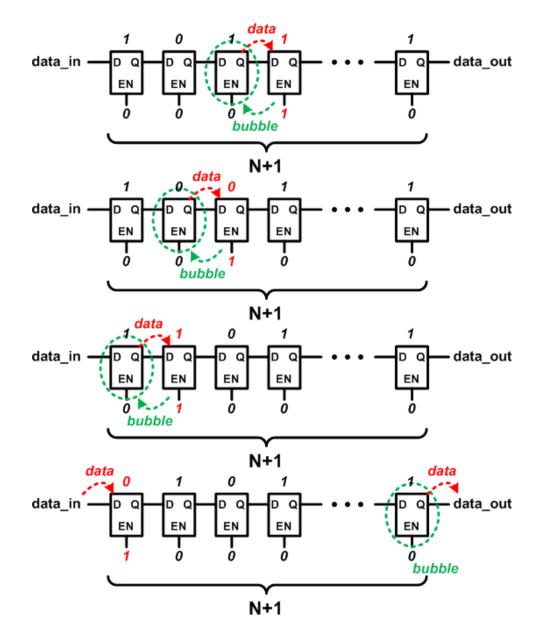

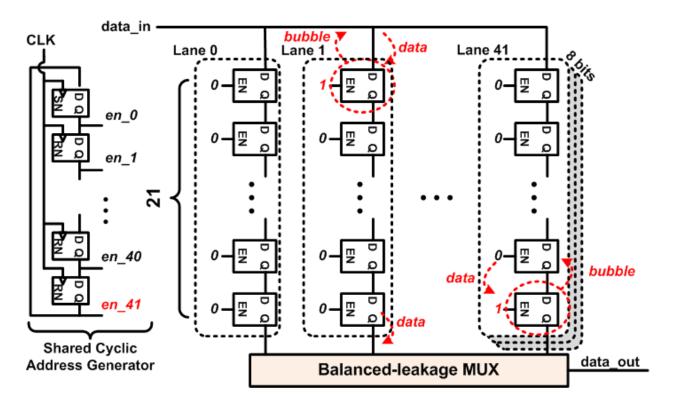

| 4.17  | Proposed single-lane shift latch propagating data and a bubble in opposite direc-   | -  |

|       | tions at each cycle.                                                                | 60 |

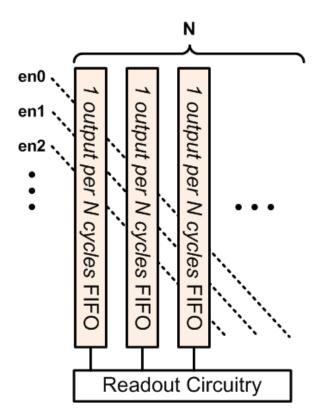

| 4.18  | A one-output-per-cycle FIFO consisting of N lanes and shared readout circuitry      | 61 |

|       | An 8-bit 840-entry FIFO based on the proposed shift-latch architecture.             | 61 |

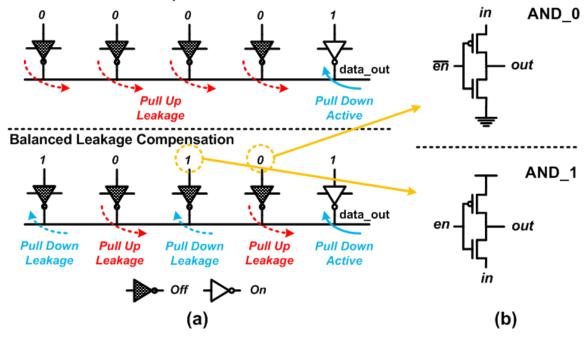

| 4.20 | (a) Worst-case scenario for leakage current affecting bitline pull-down with and without leakage compensation technique. (b) Proposed 2-transistor AND gates | 62 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

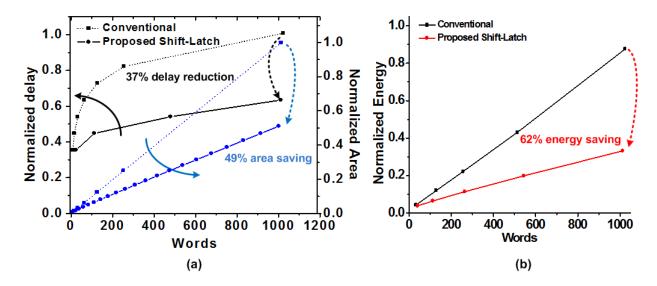

| 4.21 | Simulated (a) delay, area, and (b) energy consumption of baseline and proposed FIFO designs as a function of FIFO size.                                      | 63 |

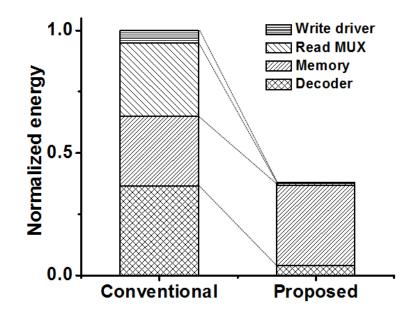

| 4.22 | Simulated energy savings in each component of a 1k-entry FIFO                                                                                                | 63 |

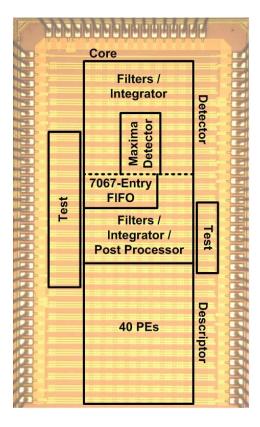

|      | A microphotograph of the fabricated feature extraction accelerator and summary                                                                               |    |

|      | table.                                                                                                                                                       | 64 |

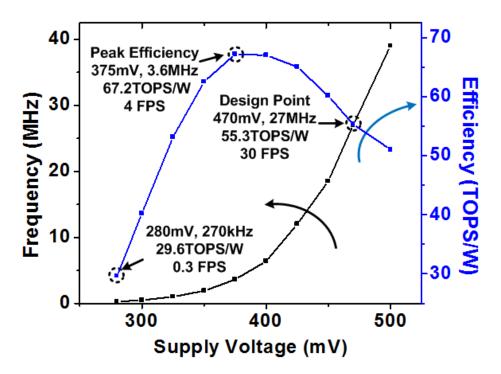

| 4.24 | Measurement results across different operating voltages                                                                                                      | 65 |

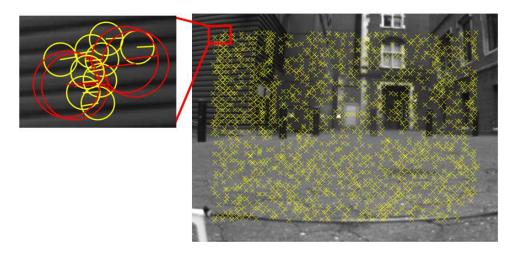

| 4.25 | A sample image marked with 1421 extracted features from measurements                                                                                         | 66 |

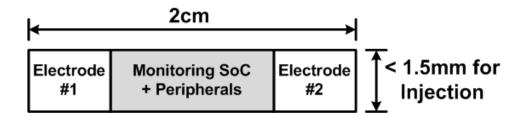

| 5.1  | Overview of syringe implantable ECG monitoring system.                                                                                                       | 70 |

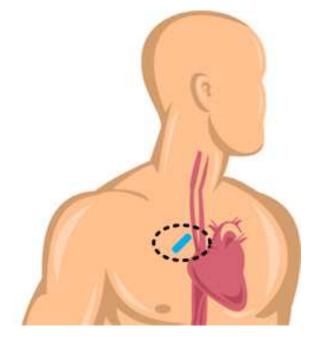

| 5.2  | Monitoring device implanted near the heart.                                                                                                                  | 70 |

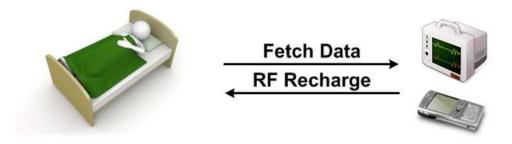

| 5.3  | Usage scenario of the proposed system.                                                                                                                       | 71 |

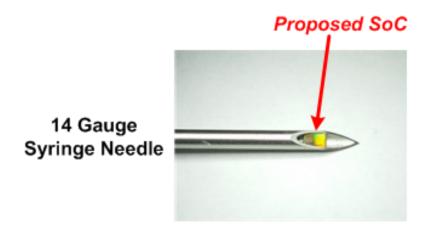

| 5.4  | Proposed SoC in a 14 gauge syringe needle.                                                                                                                   | 71 |

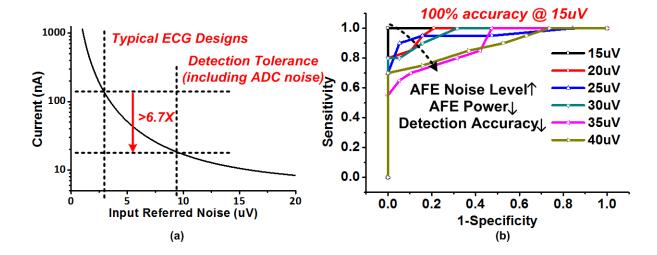

| 5.5  | Tradeoffs between (a) input referred noise and current consumption, and (b) detec-                                                                           |    |

|      | tion accuracy and input referred noise                                                                                                                       | 72 |

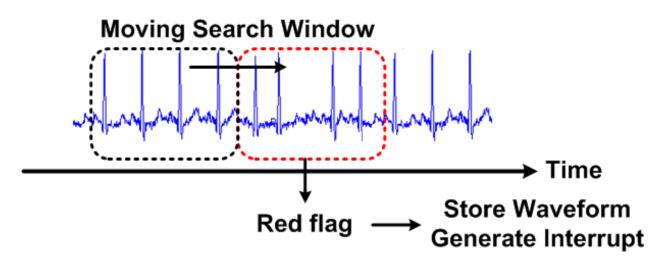

| 5.6  | Arrhythmia detection in a moving 10-second window                                                                                                            | 73 |

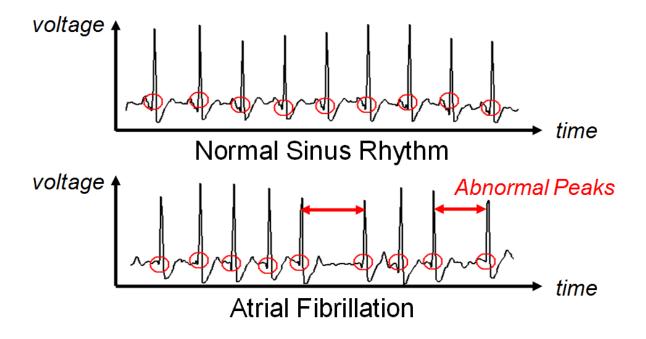

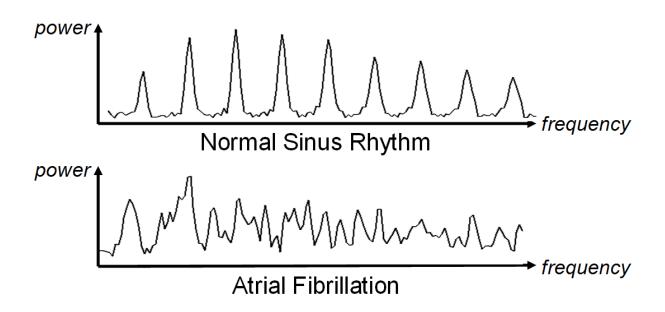

| 5.7  | Time domain detection algorithm.                                                                                                                             | 74 |

| 5.8  | Frequency domain detection algorithm.                                                                                                                        | 74 |

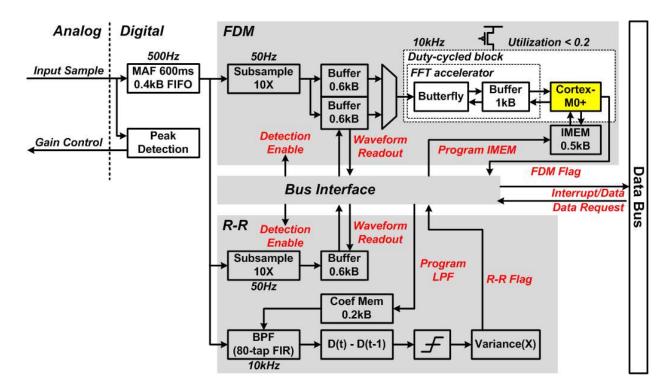

| 5.9  | Overview of the proposed digital back end design                                                                                                             | 75 |

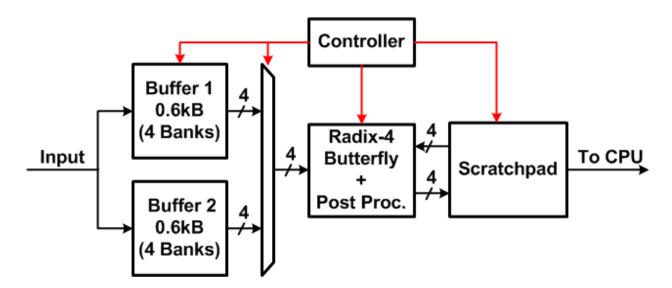

| 5.10 | Proposed 512-point real-valued FFT accelerator                                                                                                               | 76 |

| 5.11 | Proposed minimum energy computation technique applied to the FDM block                                                                                       | 77 |

| 5.12 | Die photo of the proposed SoC and summary table.                                                                                                             | 78 |

| 5.13 | Measurement results from ECG simulator test                                                                                                                  | 79 |

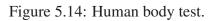

| 5.14 | Human body test.                                                                                                                                             | 80 |

| 5.15 | Implantation environment test with live sheep heart                                                                                                          | 80 |

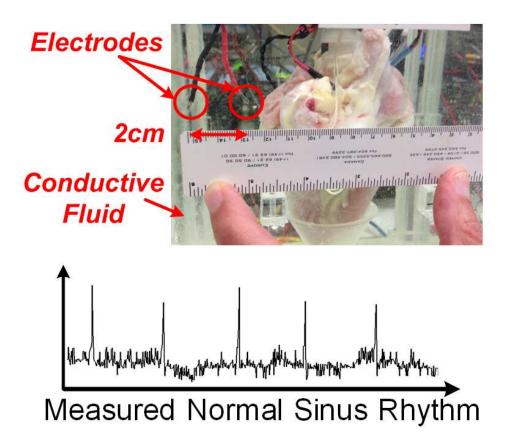

|      | Overview of the complete system configuration                                                                                                                | 82 |

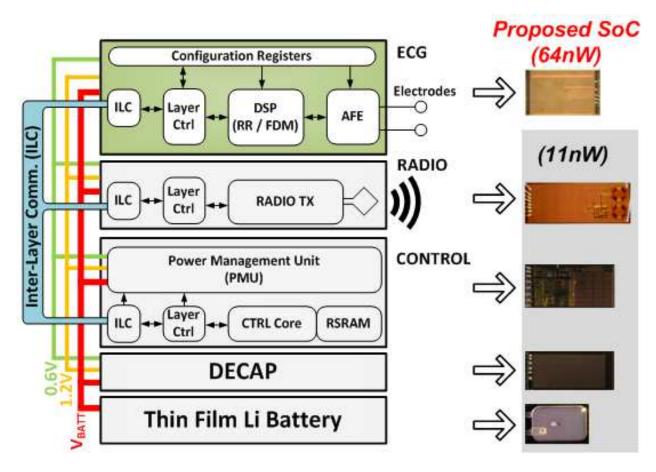

| 5.17 | Macro-scale test setup with control, decap and radio layers                                                                                                  | 83 |

| 6.1  | Applications for real-time face detection and recognition system                                                                                             | 86 |

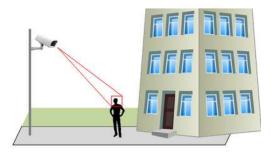

| 6.2  | Proposed face detection and recognition system flow.                                                                                                         | 87 |

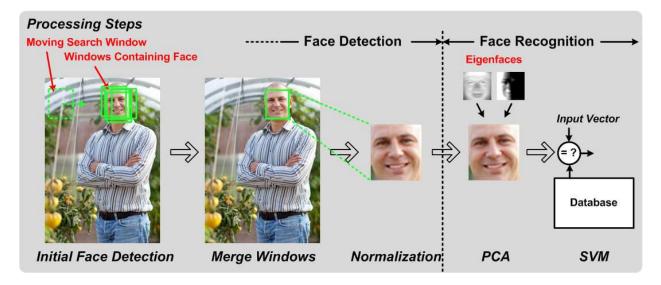

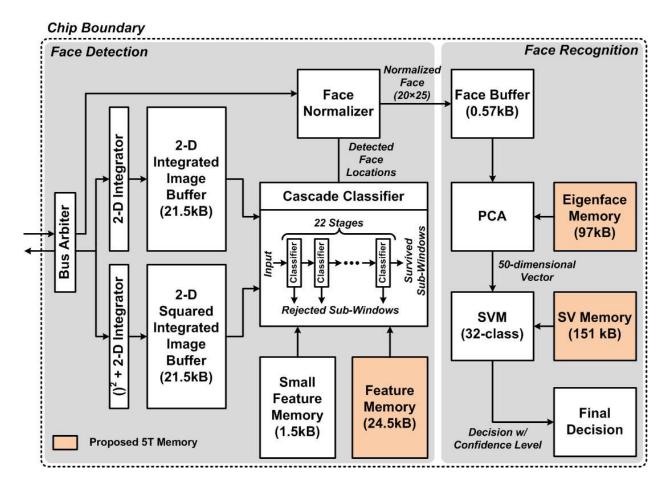

| 6.3  | Proposed face detection and recognition system architecture                                                                                                  | 88 |

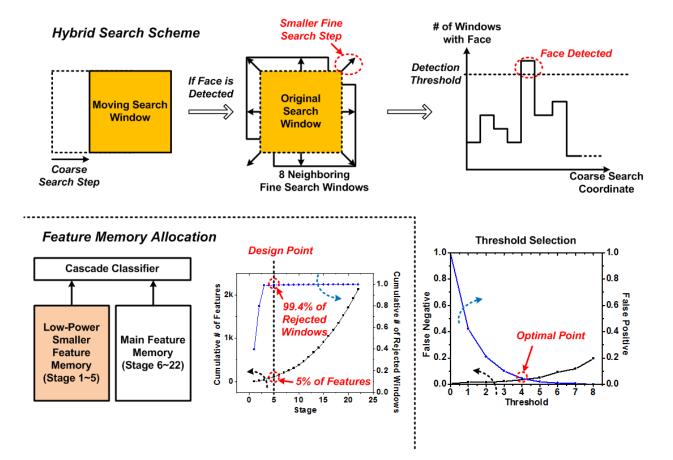

| 6.4  | Proposed architecture optimization techniques.                                                                                                               | 90 |

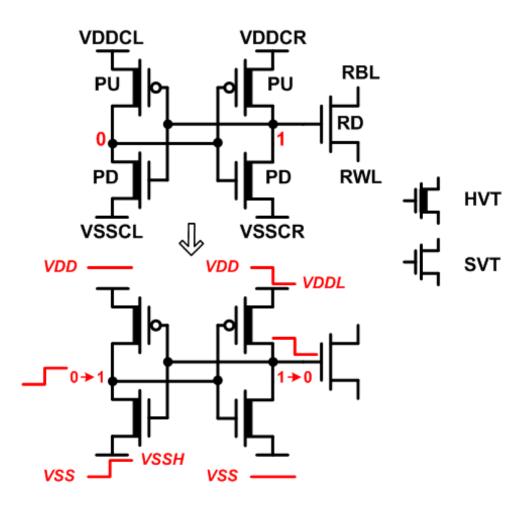

| 6.5  | Proposed 5T bit cell and basic write operation.                                                                                                              | 91 |

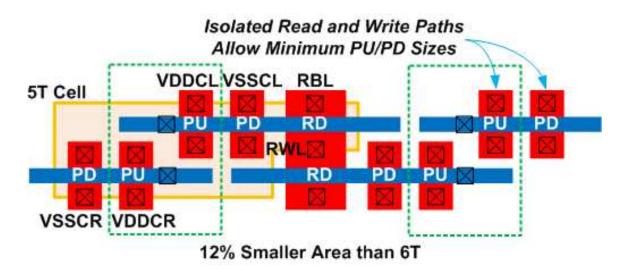

| 6.6  | Layout of the proposed 5T bit cell.                                                                                                                          | 92 |

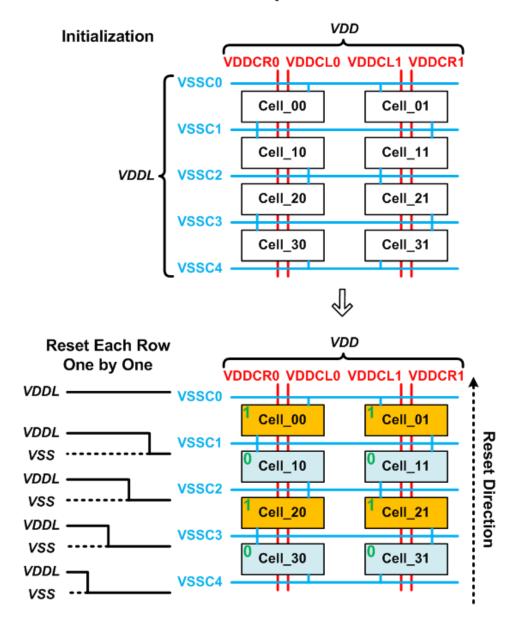

| 6.7  | Reset sequence of the proposed design.                                                                                                                       | 93 |

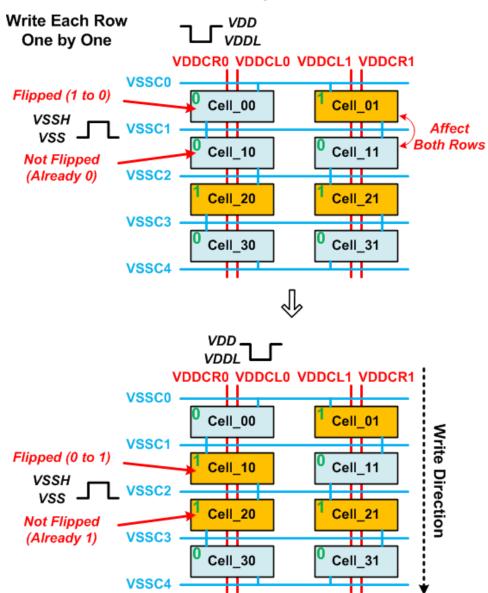

| 6.8  | Write sequence of the proposed design.                                                                                                                       | 94 |

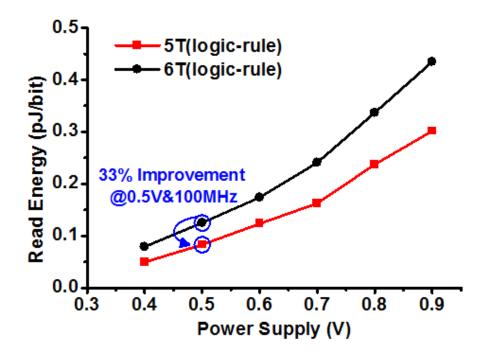

| 6.9  | Read energy consumption of the proposed 5T and conventional 6T designs                                                                                       | 95 |

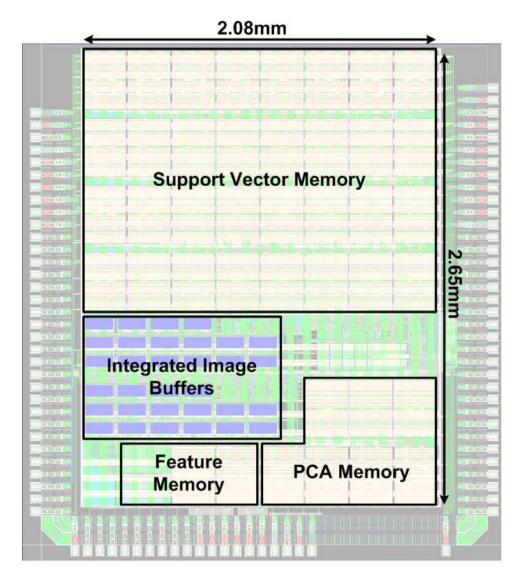

| 6.10 | Implemented face detection and recognition accelerator                                                                                                       | 96 |

# LIST OF TABLES

#### Table

| 2.1 | Characteristics of published FFT cores and the proposed design | 24 |

|-----|----------------------------------------------------------------|----|

| 4.1 | Comparisons of prior works and proposed design.                | 66 |

| 5.1 | Comparisons of prior works and the proposed design             | 81 |

#### **CHAPTER 1**

#### Introduction

As CMOS technology developed rapidly in the last few decades, various systems on chips (SoCs) have been implemented across different applications due to reduced area and power requirements. Digital signal processing (DSP) algorithms are frequently employed in these systems to achieve more accurate estimation or faster computation. However, CMOS technology scaling started to slow down recently and relatively large systems consume too much power to solely rely on the scaling effect while system power budget such as battery capacity improves slowly. In addition, there exist increasing needs for miniaturized computing systems including sensor nodes that can accomplish similar operations with significantly smaller power budget [1][2].

Due to continuous technology scaling and advances in circuit design techniques, various general purpose cores now provide significantly improved energy efficiency while still providing flexibility necessary for versatile systems (Fig. 1.1). In addition. application-driven optimizations such as instruction set selection and architecture modification have been successfully applied to complex SoCs [4]. However, the need for supporting even more complicated algorithm is growing in multimedia and wireless communication applications [5]. For instance, references [6] and [7] propose energy-efficient reconfigurable accelerator designs aimed for multimedia applications. Authors in [8] describe a LDPC decoder design with fine-grained dynamic clock gating that reduces switching energy. Significant amount of energy savings shown in these works mainly result from architecture optimization and circuit techniques. This dissertation will expand the scope into multiple design levels ranging from circuit technique to algorithmic modification and study various energy efficiency improvement techniques.

| ARM <sup>®</sup> Cortex <sup>®</sup> -M4 |               |                                           |                       |  |

|------------------------------------------|---------------|-------------------------------------------|-----------------------|--|

| Nested Ver<br>Interrupt Co               |               | Wake Up Interrupt<br>Controller Interface |                       |  |

| CPU<br>(with DSP Ext                     | ensions)      | FPU                                       |                       |  |

| Code<br>Interface                        | Bus<br>Matrix | Data<br>Watchpoint                        | Debug<br>Access       |  |

| Memory<br>Protection                     |               | Flash Patch<br>& Breakpoint               | Port                  |  |

| Unit                                     |               | ITM Trace                                 | Serial<br>Wire        |  |

| SRAM &<br>Peripheral<br>Interface        |               | ETM Trace                                 | Viewer,<br>Trace Port |  |

Figure 1.1: ARM Cortex-M4 processor architecture optimized for digital signal processing applications [3].

## 1.1 Voltage Scaling

There have been many research activities on different circuit techniques to enhance power efficiency, but voltage scaling is one of the most widely used low power techniques since it reduces switching power consumption dramatically. However, leakage energy consumption increases simultaneously due to longer clock period and there exists theoretical limit on obtainable energy efficiency due to increasing leakage power consumption [9].

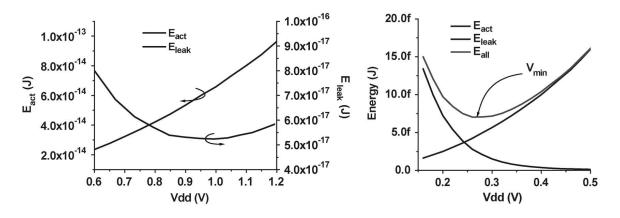

Figure 1.2: Simulated energy as a function of power supply voltage [10].

Figure 1.3: Process variation in SRAM hold noise margin in super and sub-threshold operation regions [11].

Fig. 1.2 shows simulated energy consumption of an inverter chain as a function of power supply voltage. The left plot confirms that as the supply voltage drops leakage energy starts to increase fast at some point while switching energy reduces continuously at the same rate. The total energy dissipation per operation is simply the summation of leakage and switching energy integrated over each cycle and its trend is described in the right plot. The total energy reaches the minimum point below 0.3V and increases again after that. This minimum point (or optimal point) represents the minimum possible energy consumption one can achieve for the given system.

In addition, low supply voltage incurs significant amount of PVT variation, which requires additional compensation circuitry and design overheads. In Fig. 1.3, it is observed that the distribution of SRAM hold noise margin becomes significantly wider as the supply voltage changes from 1.2V (super-threshold) to 0.3V (sub-threshold). This issue makes it difficult to design a robust SRAM operating at lower operating voltages and various variants of SRAM bitcell such as 8T, 10T and 12T have been proposed to achieve better reliability. It also affects the operation of digital logic circuits and the variation translates to the fluctuation in the critical path delay, which

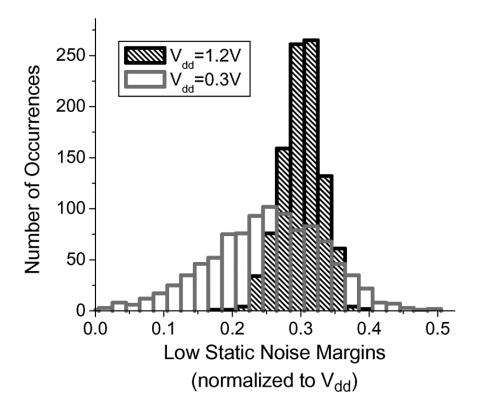

Figure 1.4: Basic Razor flip-flop [13].

necessitates larger amount of timing margins to guarantee correct circuit operation [12].

#### **1.2 Timing Error Management**

To mitigate increased variability in low operating voltage and remove consequent timing errors of the system, various error correction circuit techniques have been proposed in the last decade. Fig. 1.4 shows a basic Razor flip-flop that can detect a timing error caused by tight timing margin. The shadow latch observes the incoming data based on the delayed clock signal and checks if there is any data change in the observation window. This simple circuit can detect a timing error effectively without causing large hardware overhead.

Error correction circuitry such as variants of Razor [13][14] can detect certain amount of timing errors and force entire system to halt and re-perform that operation, which leads to operation at lower operating voltage than conventional optimal point. Although it guarantees correct operation by correcting all errors, generally only small amount of voltage margin may be achieved since the overhead from error correction starts to exceed the benefit of reduced energy. In other words, the amount of savings that can be achieved from timing error correction circuit is still limited since the correction overhead exceeds the benefit of deeper voltage scaling when the error rate is high.

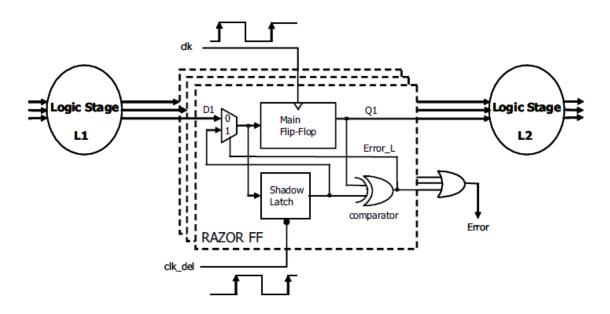

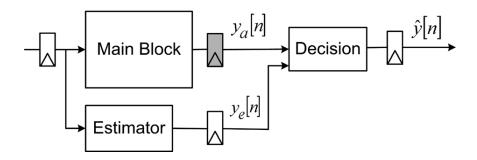

Figure 1.5: Algorithmic noise tolerance technique [15].

Alternatively, it is also possible to take advantage of error correction scheme by decreasing operating voltage even further below nominal operation range for better energy efficiency, which is called "voltage overscaling". Voltage overscaled systems usually employ architecture or algorithm level techniques to deal with significantly increased timing error rate. Since reduced clock period causes timing errors mainly in critical paths, it is important to ensure correct operation and outcome in those paths. The block diagram in Fig. 1.5 shows an example of architecture and algorithm level technique called ANT (Algorithmic Noise Tolerance). Instead of detecting all timing errors in the critical paths and correcting them at the expense of additional operations, it has an additional estimator block that produces similar, but lower accuracy results than the main computation block. The decision block observes the outputs from the main block and the estimator, and if the difference exceeds a pre-defined threshold value, it takes the estimator output instead, which guarantees operations with certain accuracy. This allows large amount of energy savings by compensating for relatively high error rate. However, this technique can be applied only to certain type of digital signal processing hardwares with simple architecture and few dominating blocks in terms of energy consumption.

#### **1.3** Architecture and Algorithm Optimization

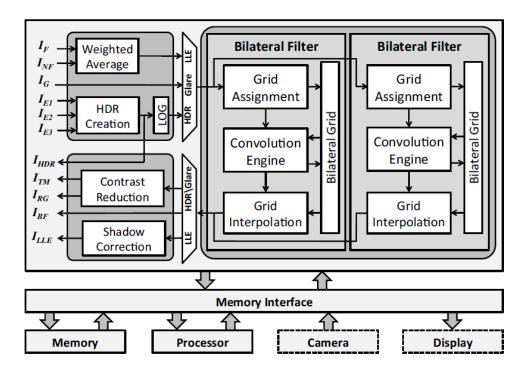

A large amount of efficiency improvement may be also obtained by optimization techniques in architecture and algorithm levels. Reference [7] proposes an efficient hardware architecture that targets computational photography such as High-Dynamic Range (HDR) imaging and Low-Light Enhanced (LLE) imaging. This provides a good example of architecture optimization with the given algorithm (Fig. 1.6). On the other hand, algorithm optimization may enable substantial

Figure 1.6: An example of application-specific efficient hardware architecture [7].

improvement in overall energy efficiency. Many systems allow small amount of accuracy or quality degradation where it introduces large amount of energy savings. Reference [16] proposes a motion estimation processor with algorithm and architecture co-optimization. It successfully demonstrates significant amount of power savings along with performance improvement. Due to low sensitivity of human eye to small color or brightness changes, especially computer vision and video codec algorithms have the potential of large energy savings.

#### **1.4 Dissertation Overview**

This dissertation seeks to mitigate excessive power consumption of conventional DSP algorithm implementations by proposing various DSP hardware design approaches targeted for powerconstrained systems. First, a fast fourier transform (FFT) accelerator is studied as one of the key parts in various DSP algorithms in Chapter 2. Along with energy-efficient FIFO for subthreshold operation, various FFT hardware architectures are analyzed in terms of energy efficiency. A parallel-pipelined architecture is proposed, which suppresses leakage energy by ensuring full utilization of functional units and reduces memory size. These techniques are applied to a 16-b 1024-pt complex-valued Fast Fourier Transform (FFT) core along with low-power first-in first-out (FIFO) design and robust clock distribution network.

Chapter 3 takes a closer look at the properties of pipelining in ULV regime and search for theoretical limit of energy efficiency for the given operations. Energy savings from deep pipelining is promising in ultra-low voltage (ULV) regime, but as scaling down continues its benefit starts to saturate and implementation overheads may increase rapidly depending on hardware topology. Energy efficiency gains in the subthreshold regime are limited by exponentially increasing cycle times, and hence leakage energy. Voltage overscaling lowers circuit operating voltage aggressively, leading to an overall improvement in energy efficiency in applications that can tolerate errors. Based on simple and intuitive mathematical model, a design methodology for voltageoverscaling of ultra-low power systems in ULV regime is proposed. First, a probabilistic model of error rate increase is proposed for basic arithmetic units, and it is validated using both simulations and measurements. This model allows the estimation of energy savings for the given amount of error tolerance. The model is then applied to a modified K-best decoder that employs error tolerance to reveal the potential benefit of the framework. With simple modifications, the conventional Kbest decoder is improved to obtain noticeable error tolerance of child node expansion modules with minimal SNR degradation while the resulting design does not require additional error-correction circuits and employs only simple timing error-detection circuitry.

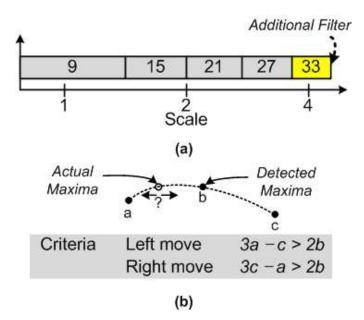

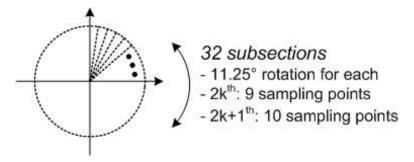

Chapter 4 proceeds to higher level approach for energy efficient hardware design. For recent highly complicated DSP algorithms, there still exists a large room for further energy reductions. In other words, hardware-oriented algorithm optimization may provide significant savings while maintaining identical or similar algorithm quality. This chapter presents an energy-efficient feature extraction accelerator design aimed for visual navigation. The hardware-oriented algorithmic modifications such as circular-shaped sampling region and unified description are proposed to minimize area and energy consumption while maintaining feature extraction quality. A matched-throughput accelerator architecture employs fully unrolled filter architectures and single stream descriptor architecture enabled by algorithm-architecture co-optimization. This provides significantly larger headroom for aggressive voltage scaling with the given throughput requirement and reduces the hardware cost of description processing elements. Due to a large number of FIFO blocks required, a robust low-power FIFO architecture for ULV regime is also proposed. Based on shift-latch delay elements and balanced-leakage readout technique, it achieves noticeable energy savings and delay reduction. These techniques are applied to feature extraction accelerator which can process 30fps VGA video in real time and it is fabricated in 28nm LP CMOS technology. The resulting design provides significantly better energy efficiency than current state-of-the-art while extracting features from entire image.

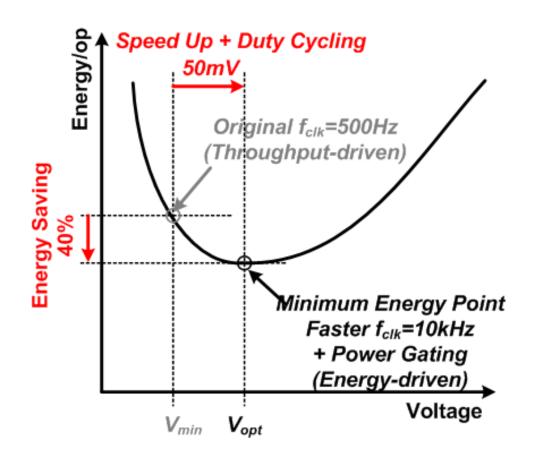

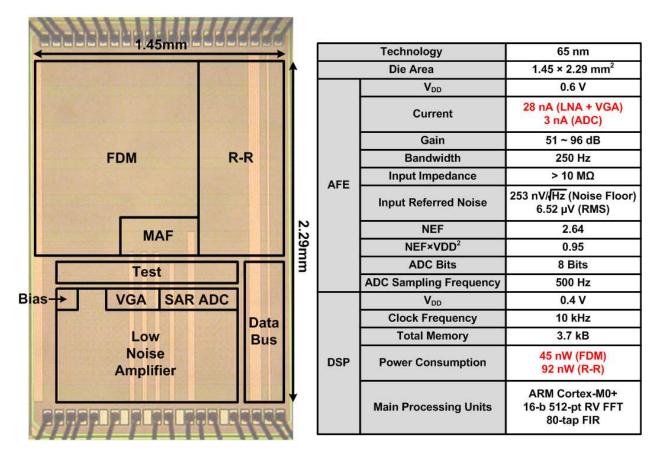

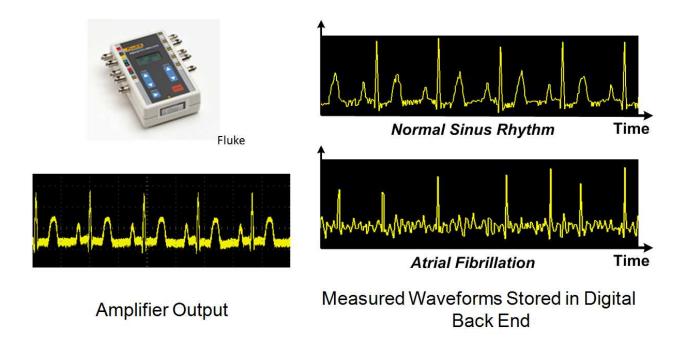

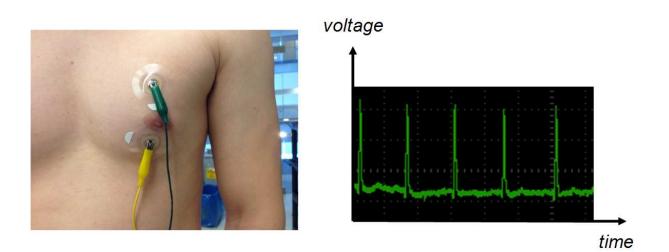

Chapter 5 moves the focus to a system level energy optimization and describes a highly powerconstrained ECG monitoring system. Recent complicated SoCs often include both analog and digital domain components and the energy consumption of each block should be considered altogether to maximize energy efficiency. This chapter shows that the system level noise optimization and circuit techniques in the analog front end enable 31nA current consumption and minimum energy computation approach in the digital back end further reduces the energy by 40%. Duty cycling is studied as an alternate approach to reduce power consumption in the digital processing block when original performance-driven minimum frequency and voltage operating point are below minimum energy point (MEP). To mitigate various types of noise and irregularity in the ECG signal, two different algorithms are implemented while each can be power-gated independently depending on the environment. The proposed system achieves more than 100× power saving over prior works.

Finally, Chapter 6 advances both architecture and circuit techniques. This chapter proposes a single-chip solution for face detection and recognition problem. Machine learning algorithms including SVM (Support Vector Machine) are transformed into feasible forms for hardware implementation. Since the memory blocks occupy most of the area and dominates the systems in terms of power consumption, a write-once read-only memory based on a new 5T bit cell is proposed. The resulting hardware can process 5fps HD video with a low clock frequency of 81MHz while consuming only 21.7mW power.

#### **CHAPTER 2**

#### **Energy-Optimized FFT Processor**

#### 2.1 Introduction

Recently, voltage scaling has been widely applied to highly energy-constrained systems such as battery-powered sensor nodes to minimize energy consumption. Voltage scaling enables energy efficient computation by quadratic (or greater) reductions of switching and leakage power dissipation. Although voltage scaling increases gate delay and thus degrades performance, it is still advantageous for many applications with relaxed performance requirements [1][17] and the supply voltage may be scaled down to, or below, the device threshold voltage  $V_{th}$ . However, leakage energy consumption per cycle increases due to enlarged stage delay as voltage scales and this overhead starts to exceed the switching energy savings below the optimal operating point  $V_{opt}$ , producing optimal energy consumption  $E_{opt}$ . Therefore there exists a fundamental limit for energy savings from voltage scaling in the subthreshold regime regardless of  $V_{th}$  [9]. To enhance energy efficiency beyond this point, leakage energy must be suppressed by elimination of idle gates or other techniques to boost the utilization of each gate or module in the system. Since ultra-low voltage operation incurs high process/voltage/temperature (PVT) variation [18], variation tolerance should also be considered in designing these low voltage systems. Such an energy-optimal design methodology is demonstrated on a FFT (Fast Fourier Transform) accelerator in this chapter.

The Fast Fourier Transform (FFT) is a key digital signal processing (DSP) algorithm and is widely used in digital communication and sensor signal processing. Aided by technology scaling, FFT accelerators have become feasible, offering higher energy efficiency than general purpose processors even for volume-constrained systems such as sensor nodes [17][19]. Such an FFT core is used as a demonstration vehicle for circuit and architectural techniques aimed at reducing  $V_{opt}$  and  $E_{opt}$ , while achieving unusually high throughput for a subthreshold circuit. Past work in power efficient FFTs include [20], where the authors propose a cached-memory FFT architecture that processes intermediate results within cached data sets to minimize the number of main memory accesses. In [19], the authors employ voltage scaling to improve energy efficiency. They use standard cells and memories optimized for subthreshold operation and target their design at the optimal energy operating point. However, the body of prior work in this area has not investigated the key role of leakage energy in the subthreshold regime, and it will be shown that energy efficiency can be improved beyond the conventional optimal energy operating point by suppressing leakage effectively.

This chapter describes the use of circuit techniques with an architectural study focused on extending voltage scalability and enhancing performance in the design of 1024-point complex-valued FFT core. A parallel-pipelined FFT architecture is proposed to maximize computational element and memory utilization, while reducing memory size and overall leakage energy. Such an approach is ideally suited to subthreshold design where leakage energy is significant, in contrast to traditional superthreshold design paradigm where dynamic energy and performance are the primary metrics. An energy-efficient FIFO block targeted for robust operation in subthreshold regime is also proposed. Combining these techniques, the parallel-pipelined FFT core with pipelined CEs (computational elements) is fabricated in a standard 65nm CMOS process. The resulting design achieves 15.8 nJ/FFT operating at 30 MHz with  $V_{dd} = 270$  mV, enabling throughput of 240 Msamples/s.

As a joint project with Mingoo Seok, he proposed a power saving technique called "super pipelining" that employs significantly more pipelining stages than conventional low voltage designs to suppress leakage energy by shortening clock period. Computational blocks including adders and multipliers are implemented using this technique, which also contributes to power saving.

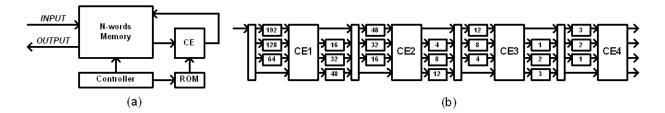

Figure 2.1: (a) Memory-based architecture and (b) R4MDC pipelined architecture.

### 2.2 Energy-optimal FFT Architecture

Contrary to nominal voltage operation, leakage energy limits energy efficiency in the ultralow voltage regime. Conventional FFT architectures mainly focus on reducing dynamic power and hardware cost while meeting a performance target, and energy efficiency can be simply calculated from the number of required computations such as complex multiplications and additions [31]. Idle cells or modules, while contributing to hardware or area overhead, are not seriously explored for improving energy efficiency for these reasons. As voltage scales, however, idle cells consume significant leakage energy per cycle while the switching energy of arithmetic units is reduced. Therefore it is critical to eliminate idle cells or modules as much as possible, enabling high utilization and improving energy efficiency.

The best-known FFT architectures are the memory-based and pipelined architectures. The memory-based architecture is one of the simplest ways of implementing the FFT algorithm. It consists of a large memory divided into several banks storing initial input data and intermediate results for the next butterfly operation, as depicted in Fig. 2.1(a). The computational element (CE) pulls one set of data from memory and stores results into the same memory space after processing. While the CE is processing data, the unaccessed memory cells simply store their previous values and consume leakage energy. Although the CE is fully utilized, memory utilization is very low and only 0.8% of total memory is accessed every cycle for 1024-pt radix-4 FFT. SPICE simulations indicate that 85% of overall energy is dissipated in memory at 300 mV for a radix-4 memory-based architecture, implying this architecture is not appropriate for highly energy efficient operation in subthreshold regime. In addition, it requires the use of a ping-pong type input buffer, increasing memory size, to perform successive FFT of incoming data for applications such as audio processing or OFDM [32][33].

The pipelined architecture comprises several stages connected in series with CEs and multiple FIFOs to store and re-order intermediate values. It leads to higher dynamic power since multiple CEs switch simultaneously. However, CEs only access FIFOs of the previous stage, and these FIFOs are relatively small compared to the large memory in a memory-based architecture. This significantly reduces the average number of memory cells per CE, enabling high memory utilization and in turn reducing memory leakage energy.

The most straightforward pipelined architecture is MDC (Multi-path Delay Commutator), shown in Fig. 2.1(b) [34]. Each stage corresponds to one segment of the signal flow graph and the CE performs butterfly computation in the same way as in the memory-based architecture. The commutator consists of switching network and FIFOs, and re-orders the data flow for CE of next stage. However, this architecture suffers from CE utilization as low as 25% for R4MDC (radix-4 MDC) architecture since it accepts only one input per cycle, then waits for several cycles to build a full set of data required for a butterfly operation. This drawback becomes worse in higher-radix FFT algorithms since more data is required for a butterfly operation. In addition, for an N-point FFT this architecture requires 3(log<sub>4</sub>N-1) complex multipliers and 5N/2-4 memory cells, making the hardware costs higher than other pipelined architectures.

A widely used pipelined architecture is  $R2^2SDF$  (Single-path Delay Feedback) [31]. This approach introduces a feedback path composed of local memory beside each CE to temporarily store intermediate values rather than a large memory in the commutator module of the R4MDC architecture.  $R2^2SDF$  requires  $log_4N-1$  complex multipliers and only N-1 memory cells, achieving 75% utilization of complex multipliers.

#### 2.2.1 Modified R4MDC architecture

The conventional R4MDC architecture accepts only one input per cycle while processing 4 input data concurrently per cycle, and thus the CEs performing radix-4 butterfly operations are activated partially to match throughput with input data rate. This incurs significant leakage energy overhead due to low CE and memory utilization. However, if four inputs from a single channel are obtained in one cycle, full CE utilization can be achieved, which also minimizes memory leakage energy since the number of cycles required to perform one FFT is reduced.

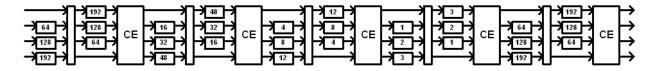

Figure 2.2: Modified R4MDC architecture for 1024-pt FFT.

This modified R4MDC architecture with 4 inputs per cycle is depicted in Fig. 2.2. In altering the original R4MDC architecture to achieve full utilization, several changes are made:

- Altered data scheduling within a commutator

- Different configurations for each FIFO

- Process four input data per cycle

While the original R4MDC architecture employs large input buffers to convert serial input to a parallel data stream for the first CE, the modified architecture allows the input re-ordering buffer to be half as large since four input data are fed into the FFT core per cycle. Therefore data scheduling within a commutator had to be changed from the original R4MDC architecture, which results in smaller FIFO configurations as shown in Fig. 2.2. The switching network remains the same as the original R4MDC and a look-up table for twiddle factors is embedded in each CE along with a controller.

In addition to full CE utilization, this architecture requires fewer memory cells for commutators. Specifically, modified R4MDC contains 7N/4-4 memory cells compared to 5N/2-4 in R4MDC, reducing memory size by 30% for a 1024-pt FFT. Although a CE accesses memory every cycle, implying full memory utilization, this does not reflect the actual number of activated versus idle cells. Instead the average number of memory cells per complex multiplier can be used as an alternate metric in energy-constrained applications. For a 1024-pt FFT, the modified R4MDC requires 149 cells per complex multiplier while R2<sup>2</sup>SDF needs 255.75 cells (72% more). Taken together, modified R4MDC achieves 4 higher throughput and more energy efficient operation than R2<sup>2</sup>SDF with smaller hardware cost. Simulation results indicate that modified R4MDC and R2<sup>2</sup>SDF consume 52% and 68% of their total energy in memory at 250mV, respectively, with modified R4MDC consuming 43.2% less energy with 2.6× better performance than R2<sup>2</sup>SDF at their respective energy-optimal points.

Figure 2.3: FFT core architecture with 2 processing lanes.

#### 2.2.2 Parallel-pipelined architecture

The improvements above significantly increase memory utilization and suppress leakage energy. However, even the modified R4MDC architecture consumes 52% of its total energy in memory, indicating that further room for improvement exists in memory utilization. This section shows that FFT architecture parallelization reduces energy consumption per operation and improves performance simultaneously.

Fig. 2.3 shows the modified R4MDC architecture with 2 processing lanes in parallel. Eight in-order input data are fed into the FFT core every cycle and each processing lane processes data within its own data set until the 2nd stage from the last, after which intermediate results are exchanged followed by independent processing in each lane. The proposed design in Fig. 2.3 requires 4N/7-8 memory cells, similar to the 1-lane version. Thus, the average number of memory cells per

Figure 2.4: (a) Energy breakdown and (b) energy-area tradeoff of parallel-pipelined architectures.

multiplier is reduced by more than 50%, translating directly to memory leakage reduction. The proposed design improves performance by  $2\times$  through parallelism while consuming only 35% of its total energy in memory, indicating a greater degree of voltage scalability and potential  $E_{opt}$  improvements.

Area-time-energy optimization has been applied in a FIR filter [35] previously to improve energy efficiency with fixed throughput. The proposed FFT architecture differs from this work in that it focuses solely on achieving minimum energy consumption with emphasis on the role of leakage current in the subthreshold regime. Since ultra-low voltage (subthreshold) FFT architectures consume most of their energy in memory as leakage, the enhanced memory utilization from the proposed architecture provides significant energy savings.

The FFT core can be further parallelized to achieve continued benefits. However, hardware costs increase while the benefit from parallelization saturates as the CE active energy starts to dominate. Fig. 2.4(a) shows energy breakdowns of modified R4MDC architectures with different degrees of parallelism. With the CE already fully utilized, its energy consumption remains unchanged while memory energy decreases with additional parallelization. The energy-area tradeoff shown in Fig. 2.4(b) clearly indicates that energy reductions from aggressive parallelism saturate while incurring large area overhead. Although the minimum energy will be achieved when entire signal flow of FFT algorithm is implemented without any memory modules, increased numbers of multipliers and other modules results in higher PVT-induced variability and lower maximum

operating frequency, translating to more leakage energy per cycle. In addition, higher parallelism incurs wire overheads including the switching network and input/output interfaces. Based on this and available silicon area constraints, the 2-lane version was implemented.

Simulation results show that the proposed design with 2 lanes consumes 27.5% less energy with 2 higher performance than a 1-lane version, translating to  $2.4 \times$  better energy efficiency and  $5.2 \times$  higher throughput than the conventional R2<sup>2</sup>SDF architecture.

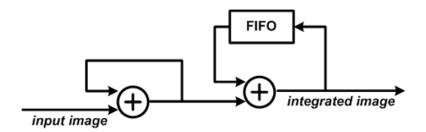

#### 2.3 Robust Subthreshold FIFO Design

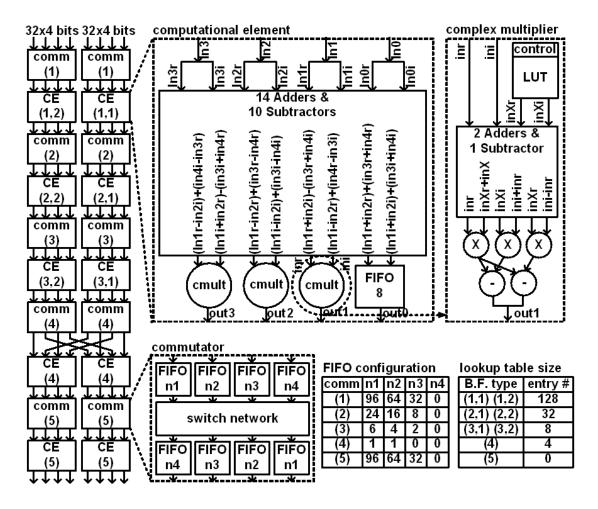

The First-in First-out (FIFO) is a key module in commutators, and the proposed architecture employs a large number of these modules. Simulations of the 2-lane modified R4MDC architecture show that FIFOs consume up to 29% of total energy, making it necessary to explore energy efficient FIFO design.

The most straightforward FIFO implementation is a shift register-based FIFO [36]. For an N delay FIFO, N registers are connected in series and all of them switch every cycle, sending data to next stage. Although this is very robust due to its negative hold time property, registers toggling every cycle have significant switching power overhead, making them less attractive for low power designs. Another possible candidate for a low-power FIFO is an SRAM-based design [37], which uses conventional SRAM for storing data and reads data from each word successively, writing subsequent data into the same address. For nominal voltage operation, a simple 6T SRAM can be used for high density with lower switching power than shift registers while retaining sufficient speed to match the data rate. However, a 6T SRAM is not suitable for the subthreshold regime due to its susceptibility to process variability and resulting small read/write margins, and variants such as 10T [38] are preferred for robust operation. The maximum operating frequency of robust subthreshold SRAM designs is typically below 1 MHz [39][40], making it impossible to meet performance requirements of the target FFT design.

To mitigate these performance and variation issues, a latch-based memory is used. Although latch-based memory as described in [19] increases read/write margins and offers potential performance improvements, additional address generator or decoder is necessary for read/write address signal generation. In addition, MUX-based readout paths are slow and suffer from leakage energy

Figure 2.5: Proposed 8-word FIFO design with commutator architecture.

Figure 2.6: Readout delay distributions from 100k Monte-Carlo SPICE simulations.

overhead due to the correspondingly long cycle time. For improved energy efficiency, a latchbased memory with dedicated address generator and logic-based readout path is proposed. The entire FIFO architecture is described in Fig. 2.5.

The proposed design contains a cyclic address generator consisting of a single chain of registers, producing both write and read enable signals. While one of the latches is enabled for write operation based on the enable signal from address generator, the data stored in the next latch is read through the NAND gate using the same signal. This cyclical access pattern reduces energy by sharing one address generator for read and write operation rather than using a separate decoder for write operation as in conventional SRAM designs. The logic-based readout path operates faster than the MUX-based option, allowing the FIFO to match the performance of the deeply pipelined CEs. Fig. 2.6 shows Monte-Carlo simulation results of readout delays of MUX-based and logicbased readout scheme. The logic-based design is 33% faster on average than the MUX-based one, indicating that the proposed design effectively reduces leakage energy by shortening stage delay while improving throughput. Simulation results further confirm that the 32-word FIFO with proposed logic-based design consumes 12% lower energy with 20% higher performance than the MUX-based design.

For robust read operation, hold time issues must be avoided between the write enable and write data signals. If write data changes while write enable of previous cycle is still asserted, the stored

Figure 2.7: Positive-edge read and negative-edge write scheme.

data of previous latch will be corrupted. To avoid this hold time issue, it utilizes a negative-edge write scheme. As described in Fig. 2.7, the write data signal remains unchanged for a half cycle after the previous write enable signal is disabled to provide large write operation timing margin and guaranteeing timing violation-free write operation. Since the readout path is critical for this FIFO module, this increased timing margin for write operation does not impact overall performance. 8-word and 32-word FIFOs are first implemented, and larger FIFOs are obtained by connecting them in series.

#### 2.4 Clock Distribution Network

Clock tree distribution networks of large integrated circuits are generally composed of several levels with local clock buffers to suppress RC delay of long wires. In the nominal voltage regime, clock buffer gate delay is small compared to the RC delay of global clock networks and inserting a large number of clock buffers is used to reduce clock skew. In the subthreshold regime, however, exponentially increased gate delay dominates while RC delay no longer contributes appreciably to clock path delay mismatches. In contrast, buffer mismatch significantly impacts clock distribution delays and adding more buffers leads to higher clock skew. Mismatch can be effectively suppressed by employing only a small number of large buffers, since they are robust to random process variations [18][41].

In this design, the clock network was designed with only 3 levels and a small number of rela-

Figure 2.8: RC-matched 3-level clock distribution network along with maximum RC mismatch values.

Figure 2.9: Simulated clock skew and slew rates in proposed clock network design.

Figure 2.10: Measured (a) energy consumption and (b) performance of the FFT core.

tively large buffers to suppress clock skew incurred by clock buffer mismatch. RC delay mismatch is also minimized by matching wire lengths of each level. Fig. 2.8 shows the complete clock distribution network. The lowest and middle level networks, which have relatively small RC delays, are implemented with minimum width lower level metallization for low power consumption while the top level is designed in a fish-bone network using top thick metal layers to minimize RC delay. Worst-case RC mismatch from simulation is less than 150ps or 0.14 fanout-of-four (FO4) delays at  $V_{dd} = 270$  mV. Fig. 2.9 also indicates that simulated 2 clock skew due to buffer mismatch is 0.68FO4, which is 2% of the clock cycle at 270 mV.

#### 2.5 Measurement Results

The FFT core is designed using the described circuit and architectural techniques. Fig. 2.10 provides measured energy and performance results for the proposed FFT core. The core consumes 15.8 nJ/FFT at a measured maximum clock frequency of 30 MHz at 270 mV, yielding 240 Msamples/s. This throughput is 10 100 higher than typical ULV designs [17][19]. At 600 mV the proposed design consumes 35.0 nJ/FFT at a clock frequency of 290 MHz; this energy efficiency is a  $2 \times$  improvement over the high performance design in [42] at the same throughput. Fig. 2.11 reports the measured performance and energy efficiency as a function of temperature, demonstrating

Figure 2.11: Measured performance and energy consumption as a function of temperature.

functionality across a wide temperature range, which is often a challenge in subthreshold designs. Also, note that higher operating frequencies due to fast operating frequency may cause temperature increases, pushing leakage energy up exponentially. However, since the proposed FFT core consumes only 3.7 mW at 270mV and 30MHz, power density is very low ( $0.043W/cm^2$ ) and there are no self-heating effects that could compromise energy efficiency at low V<sub>dd</sub>.

The average energy consumption and clock frequency at Vdd = 300 mV are 17.1 nJ/FFT and 41 MHz, respectively, as measured across 60 dies (Fig. 2.12). This figure also shows modest frequency and energy spreads of only 7% and 2%, respectively, in terms of  $\sigma/\mu$ . Table 2.1 shows performance characteristics from recent publications along with the proposed FFT design normalized to technology, FFT size, and bit width using the expression in [42]. The proposed design shows 2.4× better energy efficiency than the previous state-of-the-art. Fig. 2.13 shows the die photograph of the fabricated FFT core with core area of 8.3 mm<sup>2</sup> (2.66×3.12mm) in 65nm CMOS technology.

Figure 2.12: Measured energy (a) and performance (b) distributions at Vdd = 300mV.

Figure 2.13: Die photograph of the FFT core in 65nm CMOS.

|                       | Proposed                                 | [5]                                  | [28]                                     | [29]                                    |

|-----------------------|------------------------------------------|--------------------------------------|------------------------------------------|-----------------------------------------|

| Technology            | 65nm                                     | 180nm                                | 90nm                                     | 65nm                                    |

| FFT mode              | 1024-point<br>complex-valued             | 128~1024-point<br>real-valued        | 256-point<br>complex-valued              | 128-2048pt<br>complex-valued            |

| word width            | 16 bit                                   | 16 bit                               | 10 bit                                   | 16 bit                                  |

| Vdd                   | 0.27~1.0 V                               | 0.18~0.9 V                           | 0.625~1.0 V                              | 0.5~1.0 V                               |

| area                  | 2.71×3.15 mm <sup>2</sup>                | 2.6×2.1 mm <sup>2</sup>              | 2.26×2.26 mm <sup>2</sup>                | 1.375mm <sup>2</sup>                    |

| design point          | 1024-point CV<br>0.27V, 30MHz<br>240MS/s | 1024-point RV<br>0.35V, 10KHz<br>N/A | 256-point CV<br>0.85V, 300MHz<br>2.4GS/s | 1024-point CV<br>0.43V, 10MHz<br>80MS/s |

| Energy/FFT            | 15.8 nJ                                  | 155 nJ                               | 12.8 nJ                                  | 37.3nJ                                  |

| Normalized Energy/FFT | 15.8 nJ                                  | 111.9 nJ                             | 71 nJ                                    | 37.3nJ                                  |

Table 2.1: Characteristics of published FFT cores and the proposed design.

## 2.6 Conclusions

This chapter describes circuit and architecture techniques that enhance energy efficiency in the subthreshold regime, with application to an FFT module. A parallel-pipelined architecture maximizes CE and memory utilization, enabling greater voltage scaling range and further enhancing throughput. In addition, an energy efficient and robust FIFO design and variation-tolerant clock distribution network are employed. The proposed FFT design is fabricated in 65nm CMOS and measurements indicate that it successfully operates at an optimal operating point of 270 mV at a clock frequency of 30 MHz. Its energy efficiency is  $2.4 \times$  higher than previous state-of-art FFT designs, while performance is more than  $10 \times$  higher than past ULV designs, demonstrating the feasibility of very low voltage design for moderate to high performance systems.

#### **CHAPTER 3**

# Design Methodology for Voltage Overscaled Ultra-Low Power Systems

#### 3.1 Introduction

Continuous technology scaling enables complicated DSP algorithms to be implemented in highly energy-constrained systems such as wireless sensor nodes. Along with technology improvements, voltage scaling has also been applied in a wide range of applications to further reduce power consumption. Although this effectively boosts energy efficiency by reducing dynamic energy, it also increases stage delay, translating to significant leakage energy per cycle in the near and subthreshold regimes. Therefore a lower bound on energy per operation is reached in these operating regimes [11][44].

However, the worst-case critical path in a design is not always activated and supply voltage can be further scaled while maintaining fixed performance if the system can tolerate timing errors. This enables improved energy efficiency beyond the lower bound described above via removal of the timing correctness assumption. To reduce margins in conventional error-free systems, some circuit techniques [45] can detect and correct timing errors. While this allows for aggressive voltage scaling, the energy overhead of error correction eventually exceeds energy savings from voltage scaling beyond some error rate. On the other hand, some DSP systems have innate algorithmic error-tolerance or can be modified to achieve error tolerance without significant quality degradation as shown in [15][46]. These types of systems show much larger benefit from VOS (voltage overscaling) compared to error-free computing systems with additional error correction circuitry.

In voltage overscaled error-tolerant systems, it is critical to understand the tradeoff between energy savings and quality degradation in order to estimate headroom during the design phase and select an appropriate design point. Therefore an accurate timing error model for digital systems is a key enabler to design using voltage-overscaling. One approach to building such a model is through exhaustive search with simulation tools. However, the required time increases impractically as the system grows. A preferred alternative would be a simple probabilistic timing error model that provides reasonable accuracy, and makes the design of large DSP systems targeted at extreme energy efficiency feasible.

In this chapter, a practical design framework using an analytical timing error distribution model is proposed. Starting from the analysis of a simple ripple carry adder, a normally distributed error model for more complex circuits is derived. The model fits reasonably well to typical circuit building blocks using simulation and measurement results of pipelined Baugh-Wooley multipliers. Then the proposed model is applied to an error-resilient K-best decoder to obtain an optimal design point for peak energy efficiency.

## **3.2 Related Work**

#### **3.2.1** Error-tolerant DSP applications

The computation quality of many DSP systems can be measured as SNR performance. Generally such systems are allowed to incur a reasonably low SNR degradation (often less than 1dB) to achieve a given power budget or performance target. In [47], the authors perform intensive simulations of different adder types and investigate the benefit of VOS in a FIR filter. The work mainly focuses on the average error magnitude without architectural modification to suppress timing errors. However, error correction is not considered and performance degrades sharply as voltage scales.

More advanced approaches that incorporate error correction schemes were proposed in [15] and [46]. An estimator that is a simpler version of the main computation block produces approximate calculation results, which are then compared with the result from the main block to detect timing

errors. If the difference exceeds a pre-decided limit, the estimator result is chosen and sent to the next stage. The authors claim up to 71% power savings with coding gain loss of 0.8dB relative to error-free systems including PVT variations.

#### **3.2.2** Design approach for voltage overscaled systems

Design approaches to enhance or estimate the effect of VOS have been previously proposed. Reference [48] suggests a design flow to redistribute slack for maximizing the amount of VOS. The method is effective in improving VOS, but requires intensive simulations to determine the degree of improvement. In [49] a similar flow is proposed with additional weight assignments including a detailed analysis on adders and CORDIC processor.

In [50], the authors assume that the delay of a single gate follows the Gaussian distribution and estimate error rate of a given circuit using simulation. They use clock skew scheduling based on the importance of each signal to improve voltage scalability. Although this provides a simple design approach for voltage overscaled systems, it may not be feasible to carefully control clock skew in ultra-low power designs given that the corresponding low operating voltages lead to heightened PVT variation. In addition, the approaches above use empirical models that do not directly extend to other systems without significant recharacterization.

## **3.3** Error Analysis in Voltage Overscaled Systems

The conventional error analysis methods described above are based on extensive simulations. They can reveal an error model underlying the circuit topology and enable prediction of the benefits of voltage scaling. However, upon design modification (e.g., changing the pipeline stage assignment and redistributing timing slacks), the analysis must be performed again with mostly different variables, making it challenging to determine the optimal design point. To mitigate this exhaustive search problem, this chapter proposes a simple timing error model that can be applied to general complex circuits with acceptable accuracy to provide design guidance.

Figure 3.1: Critical path and an example activated path in a 32-bit ripple carry adder.

### 3.3.1 Ripple carry adder starting point

The adder is a basic element in typical DSP systems and even larger modules such as multipliers are frequently implemented with multiple adders. By first finding an accurate error model for adders, the model can be extended to the analysis of larger complicated modules. Here a ripple carry adder is chosen as a testbench since it has a simple critical path and makes it possible to understand the nature of timing errors and hence build an intuitive model.

The worst-case critical path of a ripple carry adder is well known to be the carry propagation path from the LSB to the MSB, as shown in Fig. 3.1. For error-free computation, the pipeline stage should be designed to accommodate this worst-case delay. However, the full critical path is activated infrequently given the probability of appropriate input vectors. Using this, one can calculate the probability of timing errors across the input vector space. Since the path from LSB to MSB is the longest, it is assumed that the packet error rate can be approximated by the MSB error rate. Then the probability that the length of the activated path culminating at the MSB is exactly N in terms of the number of full adders is given by

$$p_N = p^N (1-p)$$

(3.1)

where p is the probability that the carry input of the full adder propagates to the next stage. Then the error rate is given by the probability that the length of the activated critical path is larger than the clock period N, which is the sum of pk for all k>N. If p is 0.5 and the clock period is T, then the probability  $E_T$  that a timing error occurs is given by

$$E_T = \sum_{N=T/d_{fa}}^{32} p_N \approx 0.5^{T/d_{fa}}$$

(3.2)

Figure 3.2: Error rate of RCA from simulation and proposed equation.

where  $d_{fa}$  is the delay of a single full adder. Fig. 3.2 shows the error rate of a ripple carry adder from simulation in 65nm CMOS technology as well as estimated using Eq. 3.2. The results confirm the model accuracy in predicting error rates.

While an accurate error model for the simple RCA can be easily found, an extendable probabilistic model that can apply to larger systems is needed. As system size grows, there are more critical and sub-critical paths in the module and the error pattern starts to behave more probabilistically in contrast to the relatively deterministic model in Eq. 3.2. Given a system with N critical paths following independent delay distributions, the error rate at the clock period T is given by

$$E_{system;T} = 1 - \prod_{k=1}^{N} (1 - E_{k,T})$$

(3.3)

where  $E_{k,T}$  is the error rate of the k<sup>th</sup> critical path.

To simplify, it is assumed that all critical paths have distributions identical to Eq. 3.2 in order to represent a complex system with multiple critical paths of the same delay. Then the CDF (Cumulative Distribution Function) and the PDF (Probability Density Function) are obtained as shown in Fig. 3.3. Rather than increasing continuously as the timing slack shrinks, the behavior of the

Figure 3.3: Error rate considering multiple critical paths.

error rate is similar to a Gaussian distribution. Although the PDF in Fig. 3.3 is slightly skewed rightward, it is fitted to a Gaussian distribution. This is pessimistic in modeling voltage overscaled systems since the long tail of Fig. 3.3 will push the zero-error point farther right, and lead to more achievable gains through VOS (i.e., larger margins to be exploited via VOS) than would be found with a traditional Gaussian decay in the delay PDF.

### **3.3.2** Generalized critical path delay model

As the supply voltage reduces at a fixed clock speed, or clock period reduces at a fixed voltage, timing slack of the module also shrinks and at a specific point critical path delay will exceed the clock period depending on the input vectors. For a system with tight timing distributions, other sub-critical paths will impact the error rate. However, this chapter focus on the primary critical paths and assume that they dominate timing errors at relatively low error rates for simplicity and practicality.

If the delay of a critical path is modeled as a Gaussian random variable over the input vector space with worst-case delay of N FO4, it can be viewed as an inverter chain of length N. Each

inverter delay also follows the Gaussian distribution with mean  $\mu$  and standard deviation  $\sigma$ . Therefore the delay of entire critical path becomes the sum of random variables as in

$$D_{path} = \sum_{k=1}^{N} D_{inv,k} \sim N(N\mu, N\sigma^2)$$

(3.4)

where  $D_{path}$  and  $D_{inv,k}$  are the delays of the entire critical path and single inverter, respectively. Then the timing error rate is the probability that  $D_{path}$  exceeds a given timing constraint, which can be calculated with the CDF of a normal distribution.

Although this simplified model trades off some accuracy compared to exhaustive search, it greatly simplifies error rate prediction, making it easier to tailor the design a voltage overscaled system. If the values of  $\mu$  and  $\sigma$  are known, then distributions of the various pipeline stages and modules in a large system are estimated with this simple equation. Furthermore, timing slack redistribution or tuning of pipeline depth may be performed without costly iterative simulations.

### 3.3.3 Model verification with pipelined Baugh-Wooley multipliers

This section investigates the accuracy of the simple model described above in predicting error rate behavior of larger digital modules. Since the multiplier is one of the key components in DSP systems and is usually significantly larger than an adder, it is selected as a testbench. In the subthreshold regime, exponentially increased stage delay contributes to large leakage energy per operation and limits achievable energy efficiency. This leakage energy consumption can be suppressed by pipelining (increasing overall circuit activity and making dynamic energy dominant over leakage energy for a wider range of supply voltages) and pipelined multipliers may achieve better energy efficiency than un-pipelined multipliers [21]. However, added pipeline registers incur switching power overhead and there exists an optimal number of pipeline stages that gives the lowest energy per operation. In this section, the proposed model is used to find the optimal pipeline depth for a voltage-overscaled multiplier.

Pipelined Baugh-Wooley multipliers with various pipeline depths are implemented and Fig. 3.4 shows fabricated un-pipelined and 5-stage pipelined versions. These designs were fabricated in 65nm CMOS technology as a testbench to compare the prediction model with simulation and measurement results. To validate the proposed delay model, it should be determined whether the

Figure 3.4: Fabricated un-pipelined and 5-stage pipelined multipliers in 65nm.

Figure 3.5: Error rate quantile-clock period plot from measurements of the un-pipelined multiplier.

actual error rate distribution follows the Gaussian assumption. Measured error rate of un-pipelined multiplier is shown in Fig. 3.5 and the plot indicates the linear relationship between clock period and error rate quantile, therefore the proposed model reasonably reflects the behavior of error probability.

Given an un-pipelined multiplier with critical path delay of N FO4 that follows the normal distribution  $N(\mu, \sigma^2)$ , a K-stage pipelined multiplier will have a critical path delay of  $N(\mu', \sigma'^2)$  with the relationships:

$$\mu' = \mu/K, \sigma' = \sigma/\sqrt{K} \tag{3.5}$$

based on the model in Eq. 3.5. In addition, pipelining may increase the number of first-order critical paths, which this should be included in error rate calculations. Then the error rate of a K-stage pipelined multiplier at a given clock period T is given by

$$E_{mult;k,T} = 1 - \{F(T;\mu',\sigma'^2)\}^C$$

(3.6)

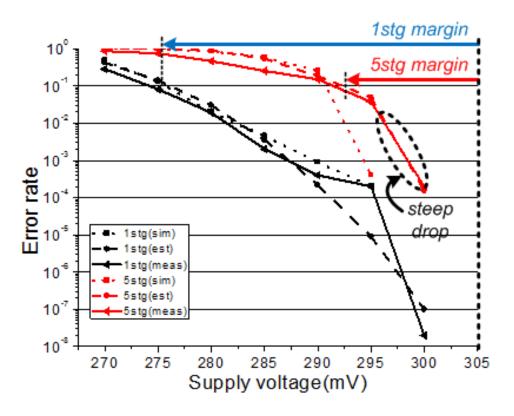

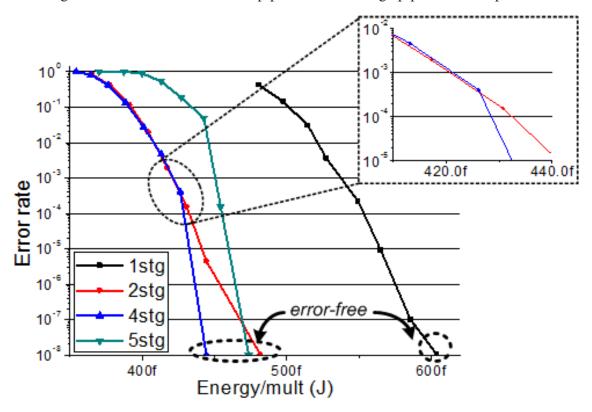

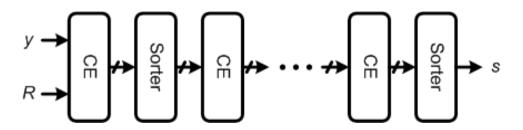

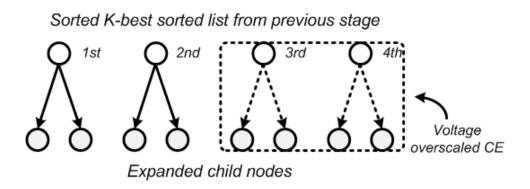

where F is the CDF of a Gaussian distribution and C is the number of critical paths. For voltage overscaled systems, the effect of voltage scaling translates to increased gate delay and T effectively becomes shorter when normalized to FO4 delay at the new voltage. Therefore it is directly reflected by T in this equation.