## **Power Management Circuits for Miniature Sensor Systems**

by

#### In Hee Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2014

#### **Doctoral Committee:**

Professor David Blaauw, Chair Professor Michael Flynn Assistant Professor Jeffrey T. Scruggs Professor Dennis Michael Sylvester To my wife Haehyun

and my children Sichan and Siwoo

and my parents

## TABLE OF CONTENTS

| DEDICA | ATION                                            |                                                    | ii                  |

|--------|--------------------------------------------------|----------------------------------------------------|---------------------|

| LIST O | F <b>FIGU</b>                                    | RES                                                | v                   |

| LIST O | F TABL                                           | <b>ES</b>                                          | /iii                |

| СНАРТ  | ER                                               |                                                    |                     |

| 1      | Introdu<br>1.1<br>1.2                            | Motivation                                         | 1<br>1<br>7         |

| 2      | A Cons<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Motivation                                         | 26<br>80            |

| 3      | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                  | Energy Harvester Using Ripple Voltage Sensing MPPT | 9<br>.0<br>.4<br>.6 |

| 4      | 4.1<br>4.2<br>4.3                                | J 1 J                                              |                     |

|         | 4.3.1 Diode-Stack Voltage Divider                                          | 56 |

|---------|----------------------------------------------------------------------------|----|

|         | 4.3.2 Voltage Reference                                                    | 59 |

|         | 4.3.3 Comparator and Clock Generator                                       | 63 |

|         | 4.3.4 Other Blocks                                                         | 66 |

| 4.4     | Reset Propagation Strategy                                                 | 68 |

|         | 4.4.1 Reset Propagation Strategy in mm-scale Multi-layer System            | 68 |

|         | 4.4.2 Secondary Reset Detector                                             | 72 |

| 4.5     | Experimental Results                                                       | 74 |

| 4.6     | Summary                                                                    | 80 |

| 5 A Lo  | w Power Battery Supervisory Circuit with Adaptive Battery Health Monitor . | 83 |

| 5.1     | Introduction                                                               | 83 |

| 5.2     | Proposed BSC                                                               | 86 |

| 5.3     | Measurement Results                                                        | 89 |

| 5.4     | Summary                                                                    | 94 |

| 6 Conc  | lusion                                                                     | 95 |

| LIOCDAI | PHY                                                                        | 98 |

## LIST OF FIGURES

| Figure |                                                                                                        |    |

|--------|--------------------------------------------------------------------------------------------------------|----|

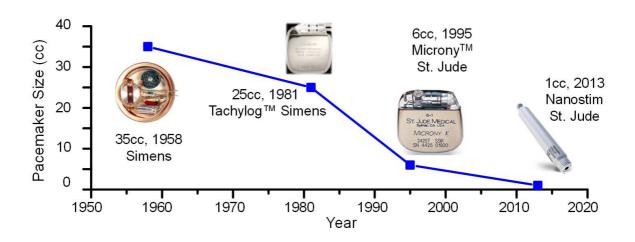

| 1.1    | Miniaturization of implantable pacemakers                                                              | 2  |

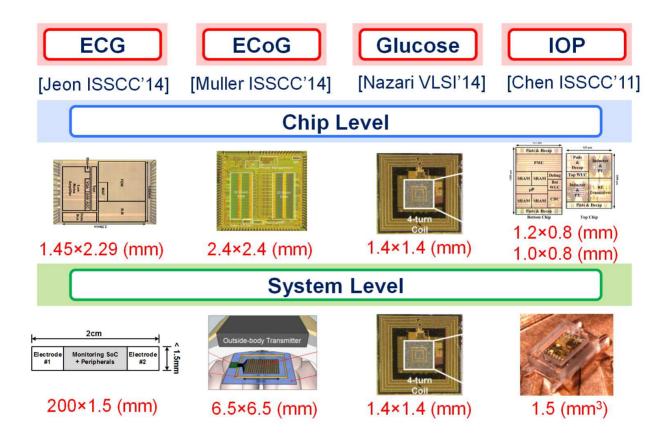

| 1.2    | Examples of recent miniature sensing systems                                                           | 2  |

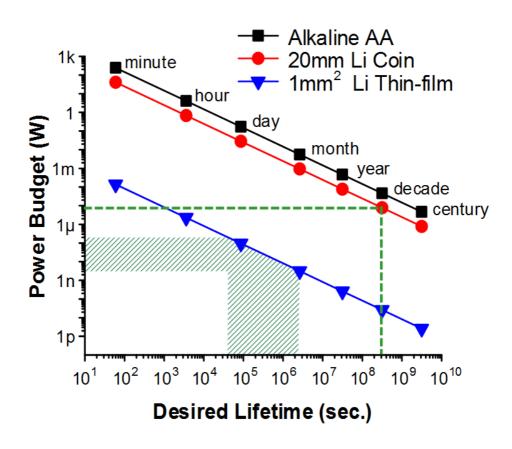

| 1.3    | Batteries                                                                                              | 3  |

| 1.4    | Average power budget for desired lifetime with different batteries                                     | 4  |

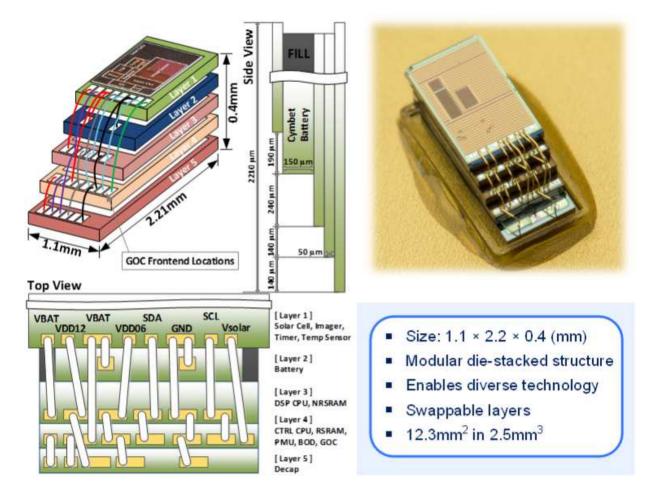

| 1.5    | Michigan Micro-Mote: a mm-scale sensing platform [2]                                                   | 5  |

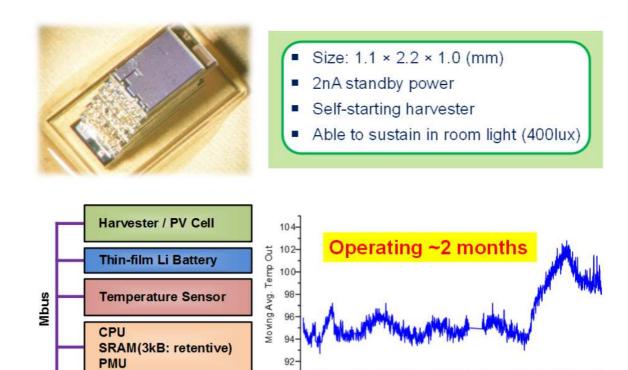

| 1.6    | mm-scale temperature sensing system [12]                                                               | 6  |

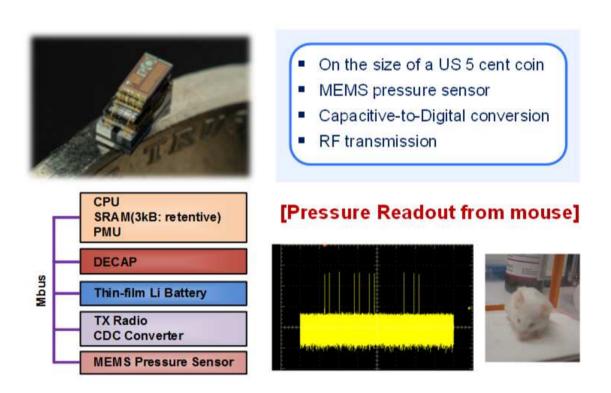

| 1.7    | Implantable pressure monitor [13]                                                                      | 6  |

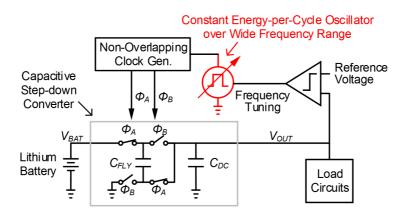

| 2.1    | Capacitive step-down converter in a wireless sensor node with a lithium battery                        | 11 |

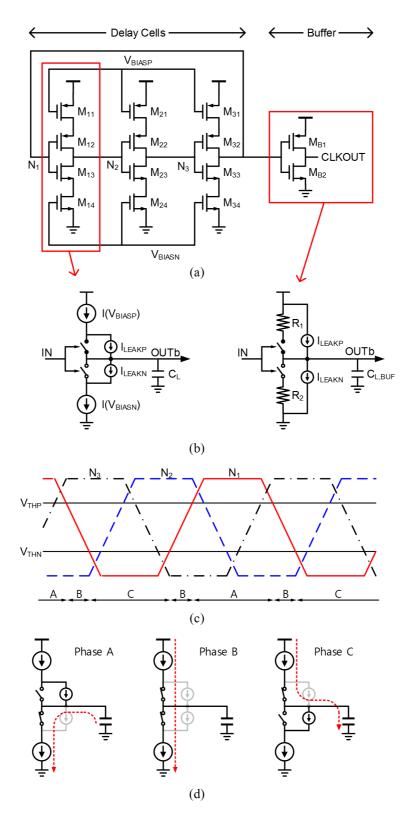

| 2.2    | Current-starved ring oscillator (a) oscillator circuit diagram (b) simplified model                    |    |

|        | (c) internal node waveforms (d) circuit status of the first stage delay cell                           | 14 |

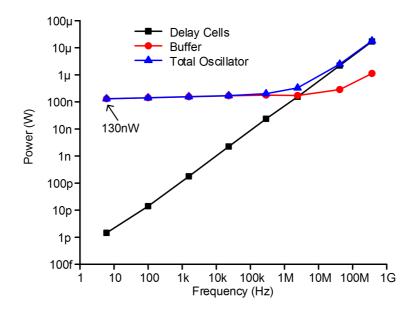

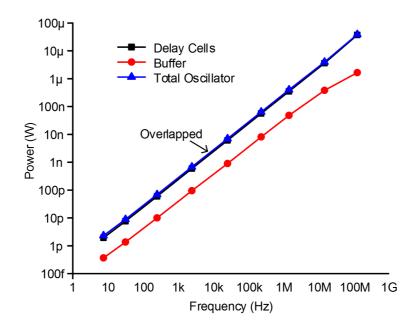

| 2.3    | Simulated power consumption of a 7-stage conventional current-starved ring os-                         |    |

|        | cillator with an inverter output buffer over frequency                                                 | 16 |

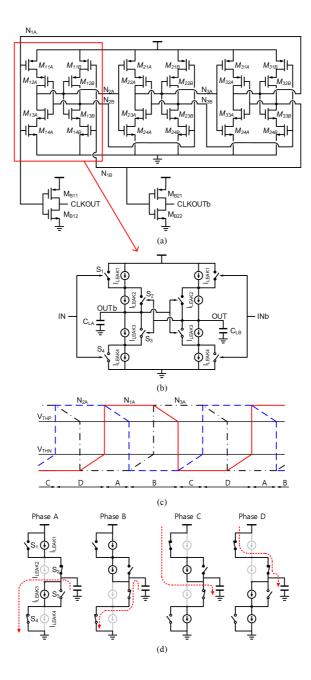

| 2.4    | Fixed-frequency leakage-based oscillator (a) oscillator circuit diagram (b) simpli-                    |    |

|        | fied model (c) internal node waveforms (d) circuit status of the first stage delay                     |    |

|        | cell                                                                                                   | 17 |

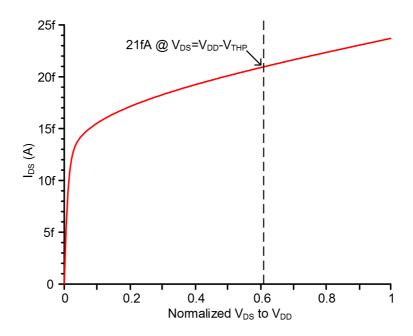

| 2.5    | Simulated $I_{DS}$ versus $V_{DS}$ (minimum-size transistor)                                           | 18 |

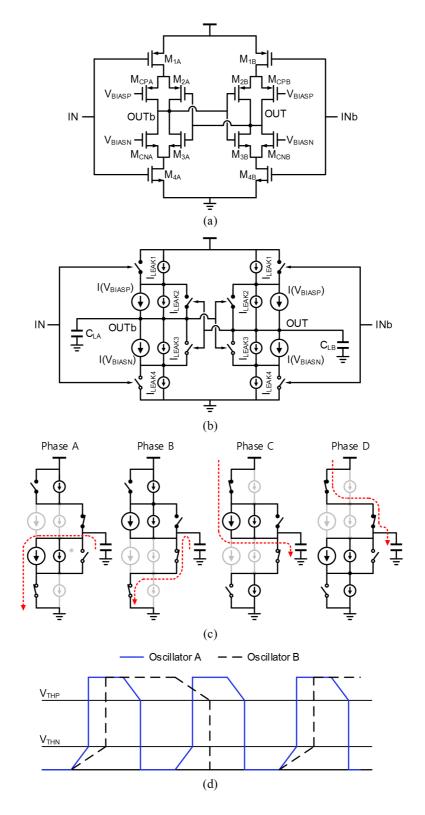

| 2.6    | Proposed constant energy-per-cycle ring oscillator (a) oscillator delay cell (b) sim-                  |    |

|        | plified model (c) circuit status of a delay cell (d) internal node waveforms from                      | 20 |

| 2.7    | oscillators with different speed                                                                       | 20 |

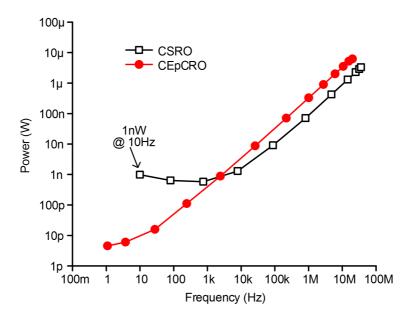

| 2.7    | Simulated power consumption of a 7-stage proposed CEpCRO with an inverter output buffer over frequency | 21 |

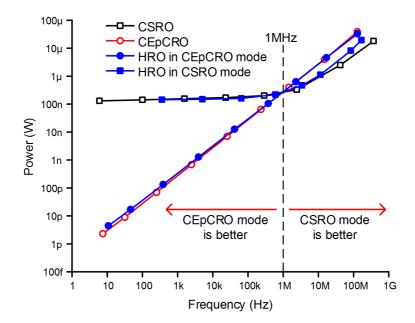

| 2.8    | Simulated power consumption of CSRO, CEpCRO, and HRO over frequency                                    | 23 |

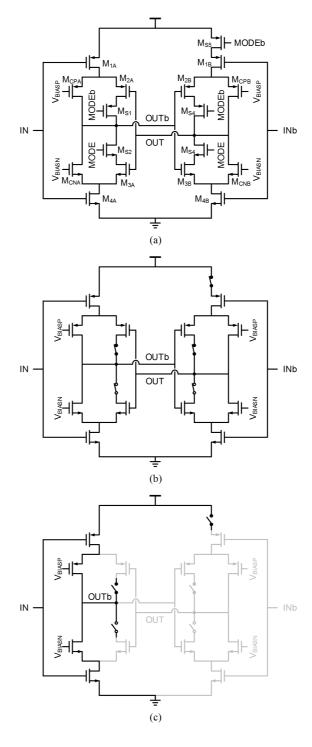

| 2.9    | Proposed hybrid ring oscillator (HRO) (a) circuit diagram of a delay cell (b) CEpCRO                   | 23 |

| 2.9    | mode (c) CSRO mode                                                                                     | 24 |

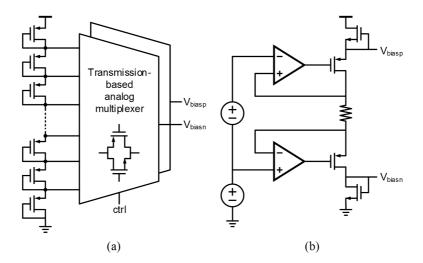

| 2.10   | Bias voltage generator (a) voltage-divider-based circuit followed by analog mux                        |    |

| 2.10   | (b) current-mirror-based circuit                                                                       | 26 |

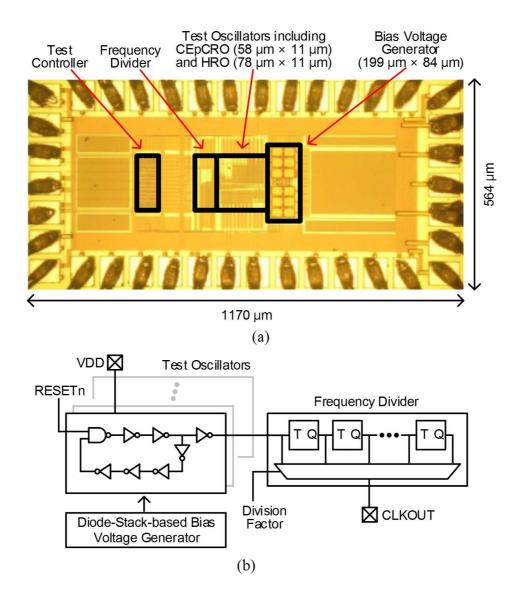

| 2.11   | Test chip for oscillators (a) die photograph (b) test structure                                        | 27 |

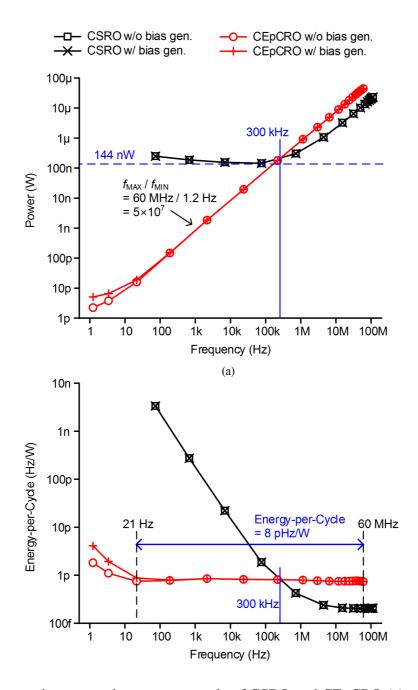

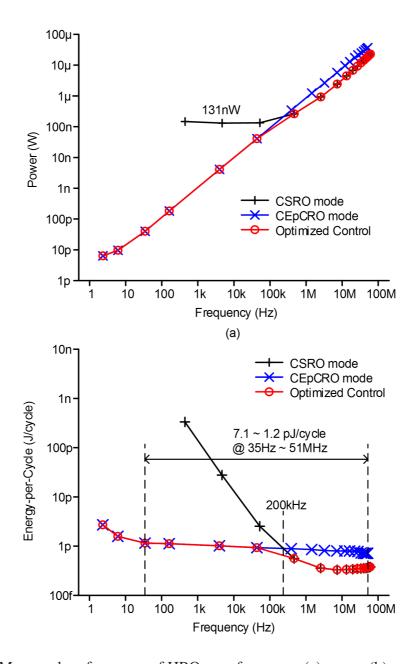

|        | Measured power and energy-per-cycle of CSRO and CEpCRO (a) power (b) energy-                           |    |

|        | per-cycle                                                                                              | 29 |

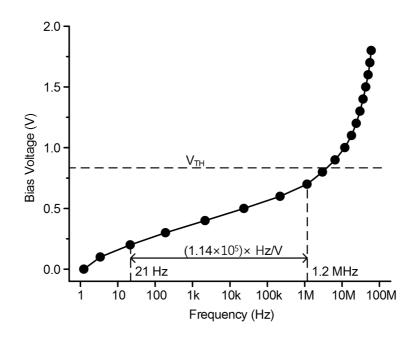

| 2.13   | Measured bias voltage profile of CEpCRO over frequency                                                 | 30 |

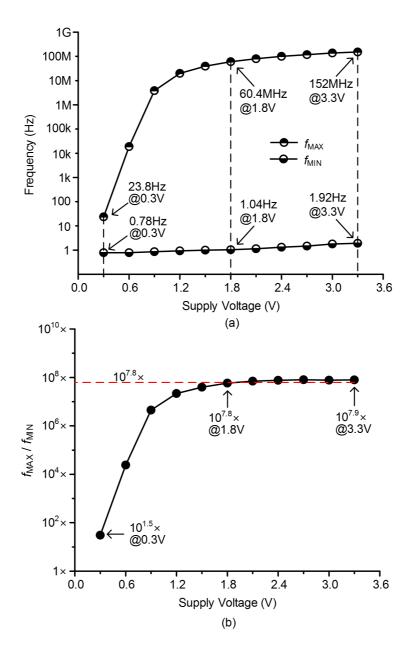

| Measured frequency range of CEpCRO over supply voltage (a) $f_{MAX}$ and $f_{MIN}$ (b)                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_{MAX}/f_{MIN}$                                                                                                                                                 |

| Measured performance of HRO over frequency (a) power (b) energy-per-cycle                                                                                         |

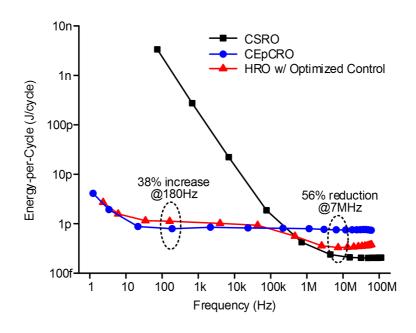

| Measured energy-per-cycle of CSRO, CEpCRO, and HRO                                                                                                                |

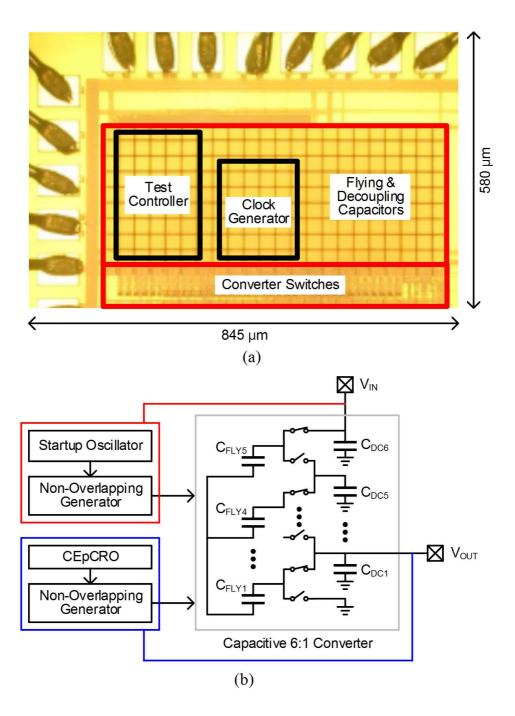

| Test chip for a capacitive step-down converter (a) die photograph (b) converter                                                                                   |

| diagram                                                                                                                                                           |

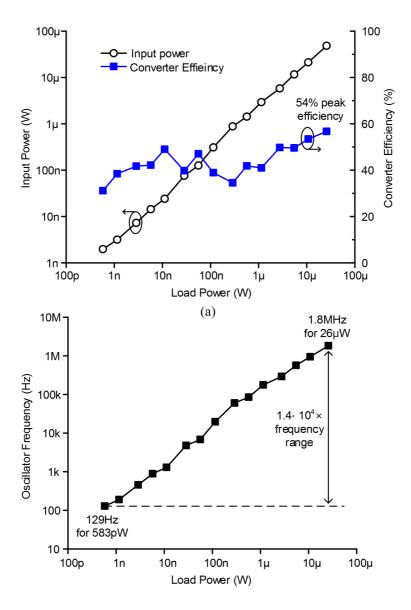

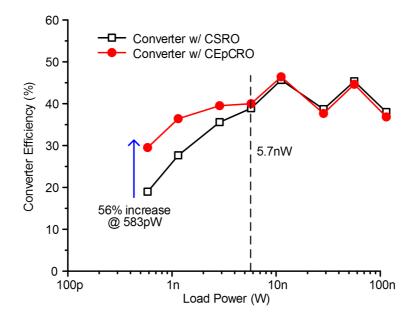

| Measured converter over load power (a) input power and converter efficiency (b) operating frequency                                                               |

| Measured power consumption of oscillators at oscillator supply voltage in the converter.                                                                          |

| Efficiency of converters using CSRO and CEpCRO                                                                                                                    |

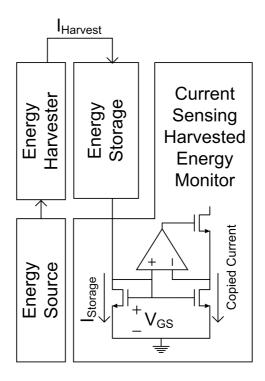

| Conventional harvested energy monitor for maximum power point tracking (MPPT).                                                                                    |

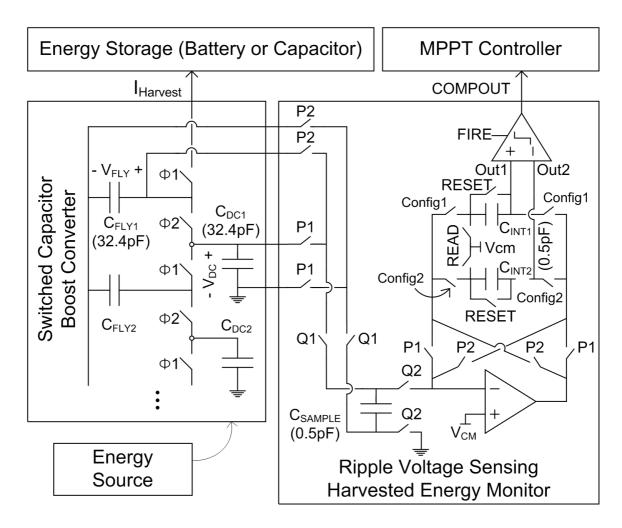

| Proposed ripple voltage sensing harvested energy monitor                                                                                                          |

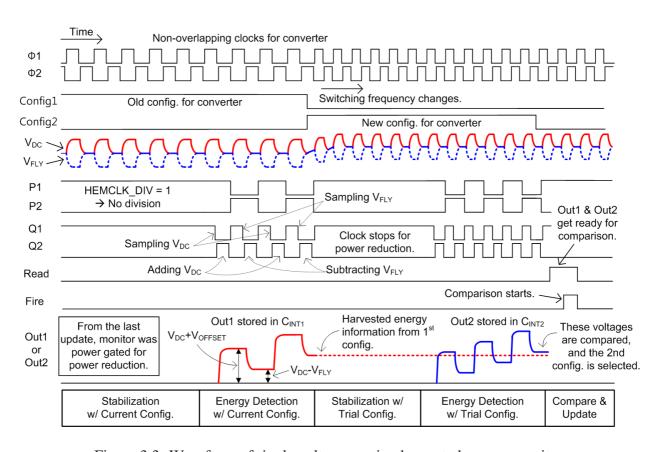

| Waveform of ripple voltage sensing harvested energy monitor                                                                                                       |

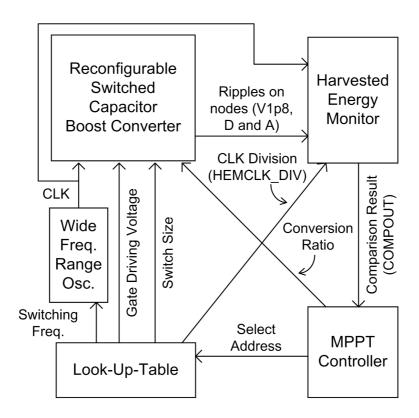

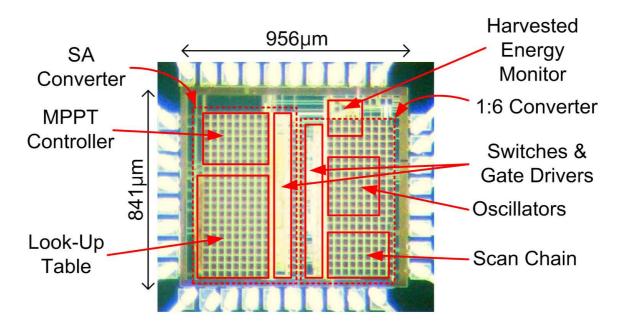

| Block diagram of the designed energy harvesting unit                                                                                                              |

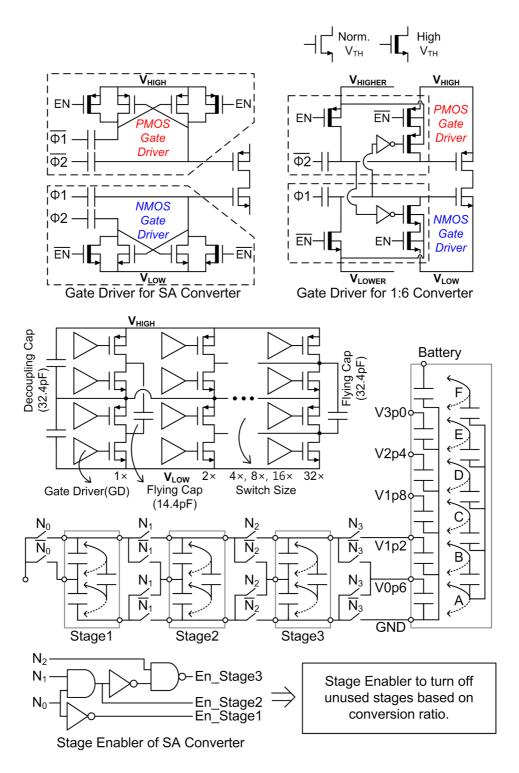

| Reconfigurable switched capacitor boot converter                                                                                                                  |

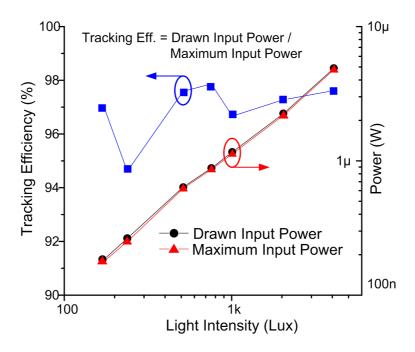

| Tracking efficiency over light intensity.                                                                                                                         |

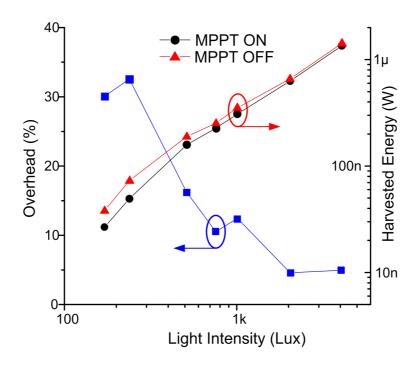

| MPPT overhead over light intensity                                                                                                                                |

|                                                                                                                                                                   |

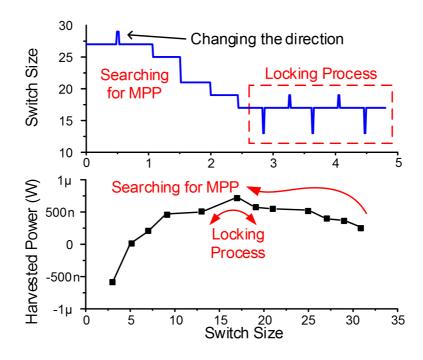

| Examples of MPPT operation with conversion ratio                                                                                                                  |

| Examples of MPPT operation with switch size update                                                                                                                |

|                                                                                                                                                                   |

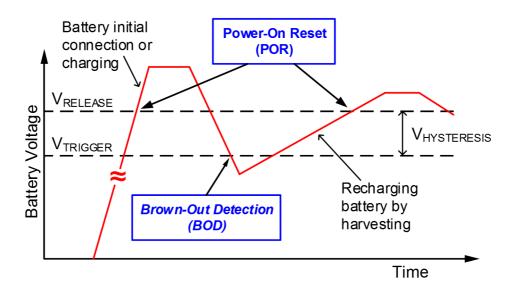

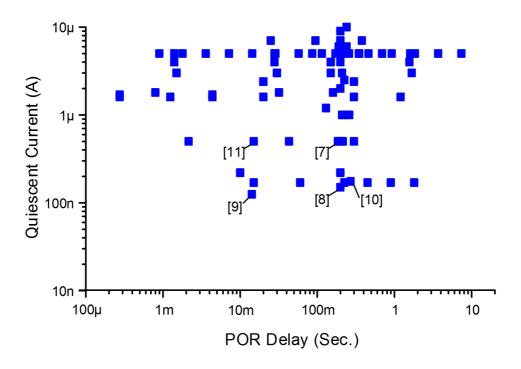

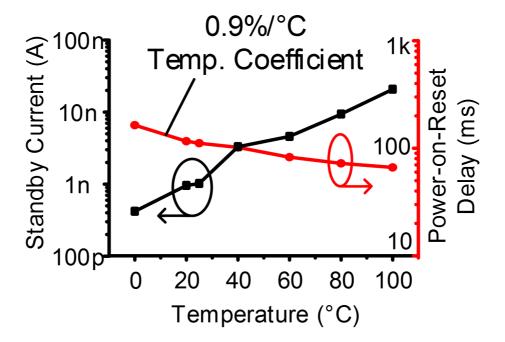

| Varying battery voltage and required functions of battery supervisory circuit (BSC). Quiescent current over power-on-reset (POR) delay of commercial POR/BOD cir- |

| cuits                                                                                                                                                             |

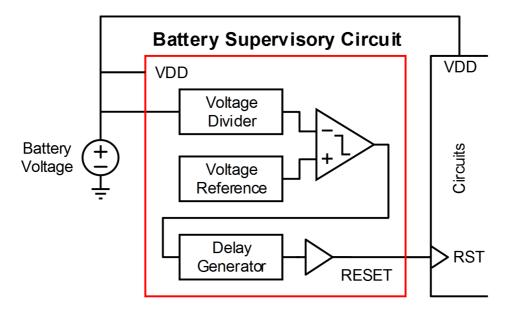

| Conventional BSC structure                                                                                                                                        |

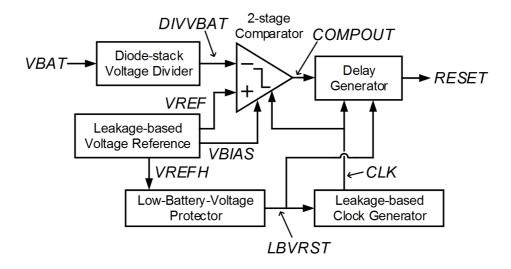

| Proposed BSC structure                                                                                                                                            |

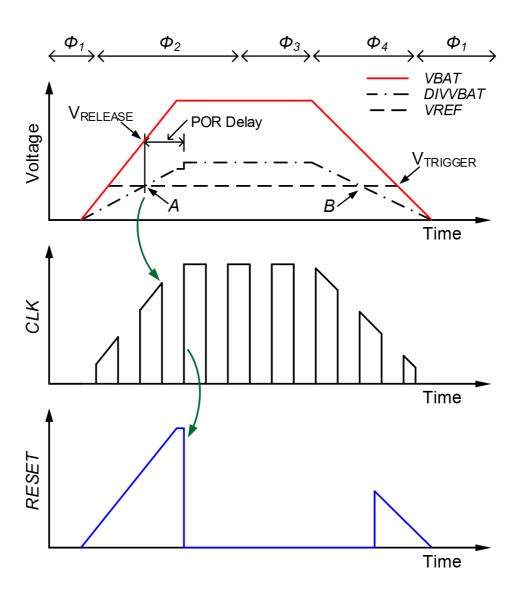

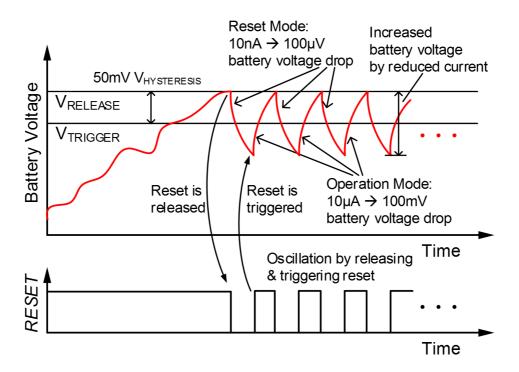

| Conceptual BSC operation according to battery voltage $(V_{BAT})$                                                                                                 |

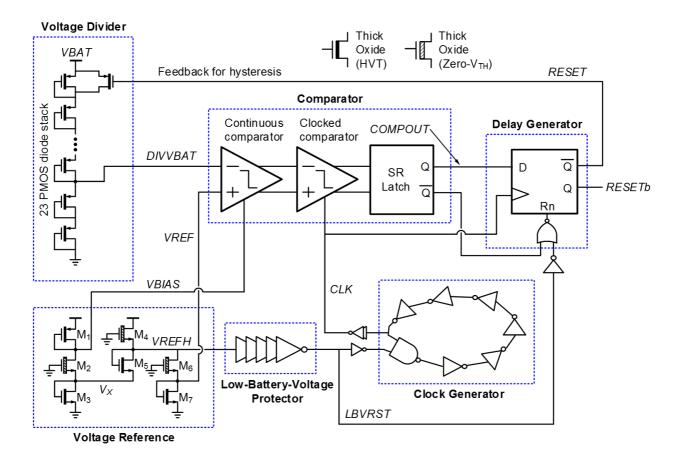

| Circuit implementation of proposed BSC                                                                                                                            |

| Problem from small $V_{HYSTERESIS}$ in a system with high battery internal resistance.                                                                            |

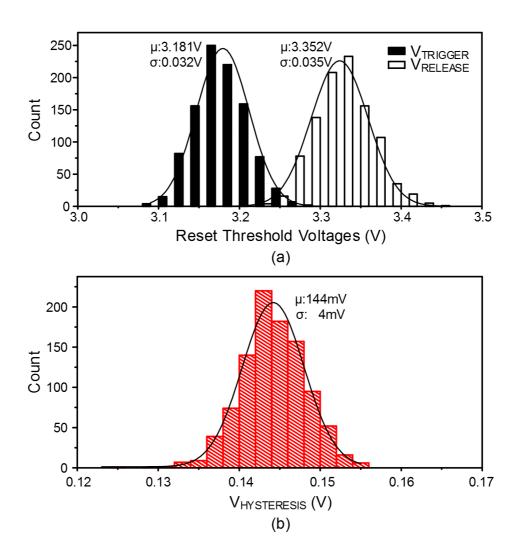

| Impact of process variation and mismatch on reset threshold voltages (a) $V_{TRIGGER}$                                                                            |

| and $V_{RELEASE}$ (b) $V_{HYSTERESIS}$ (= $V_{RELEASE}$ - $V_{TRIGGER}$ )                                                                                         |

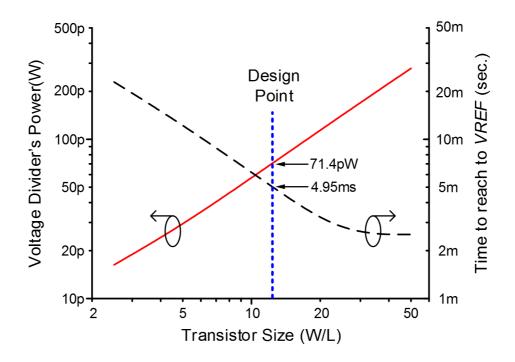

| Simulated power consumption and speed of voltage divider                                                                                                          |

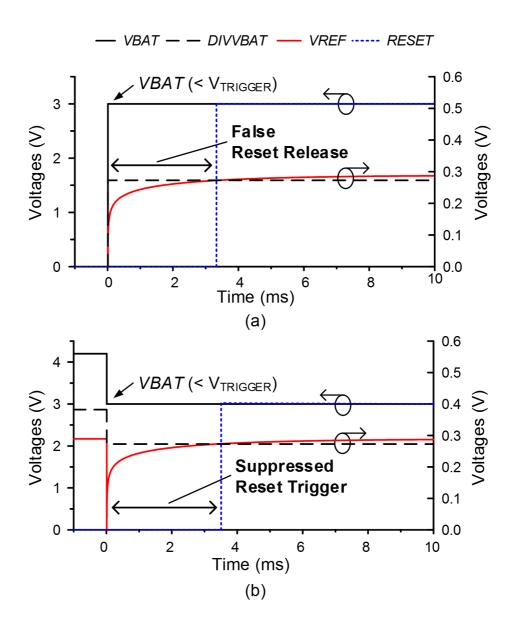

| Problems from using conventional low-power voltage reference (a) false reset re-                                                                                  |

| lease using decoupling capacitor to ground (b) suppressed reset trigger by using                                                                                  |

| decoupling capacitor to supply                                                                                                                                    |

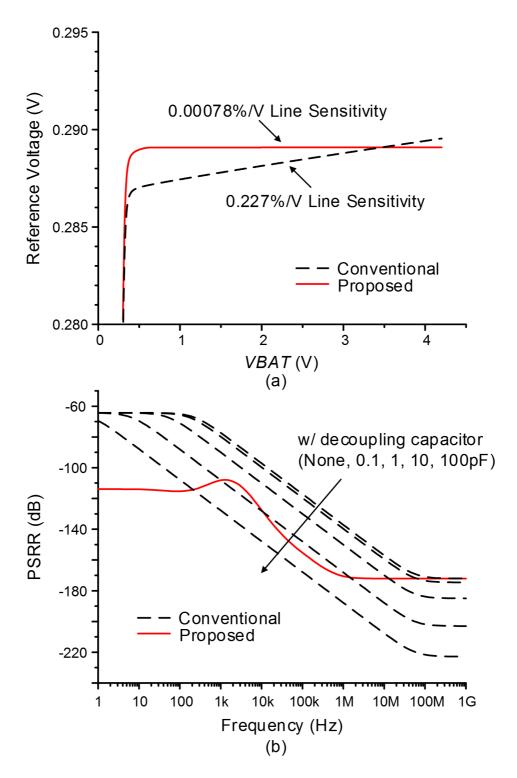

| Simulated conventional and proposed voltage reference (a) line sensitivity (b) power                                                                              |

| supply rejection ratio (PSRR)                                                                                                                                     |

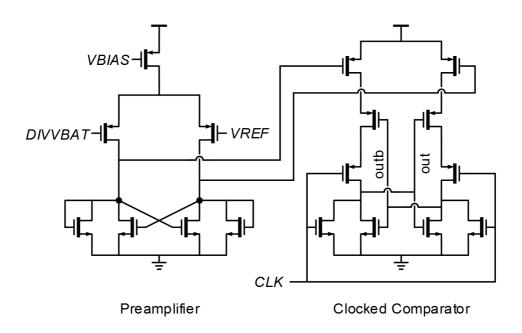

| Comparator transistor diagram                                                                                                                                     |

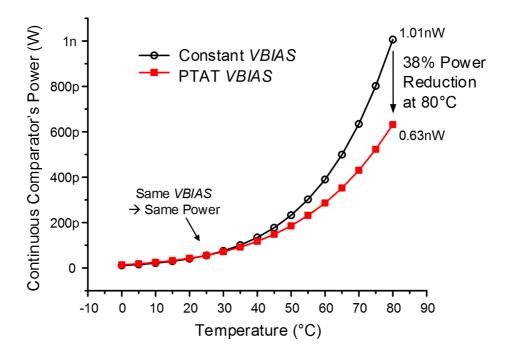

| Simulated power consumption of preamplifier over temperature                                                                                                      |

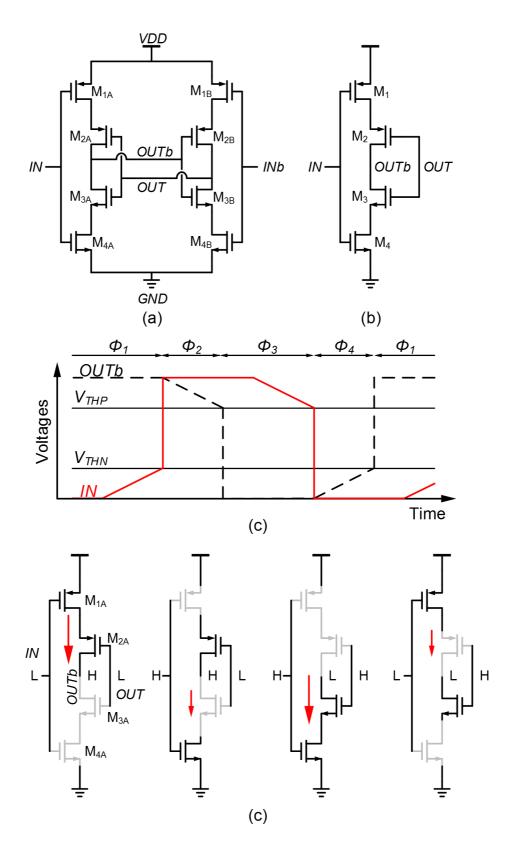

| Leakage-based oscillator (a) delay cell (b) its half circuit (c) waveform (d) half                                                                                |

| circuits for each phase of operation.                                                                                                                             |

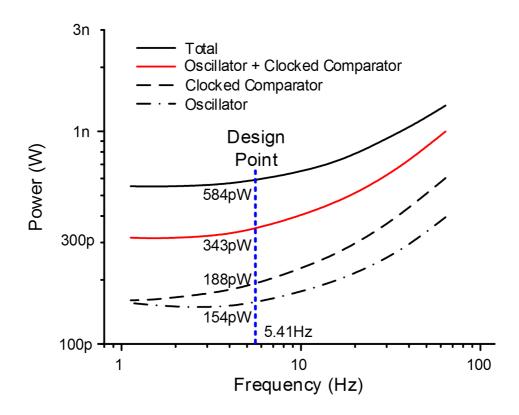

| Power consumption versus operating frequency                                                                                                                      |

|                                                                                                                                                                   |

| 4.16   | RESET control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

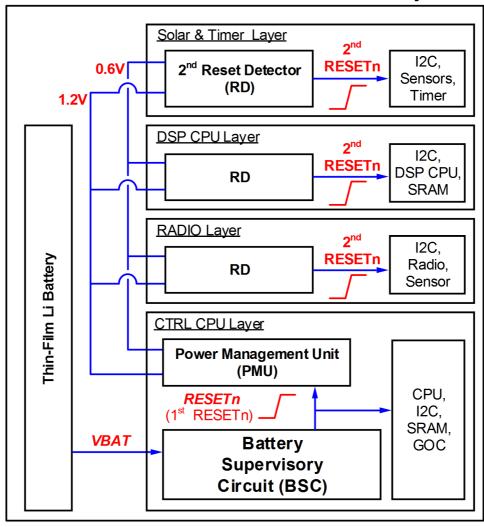

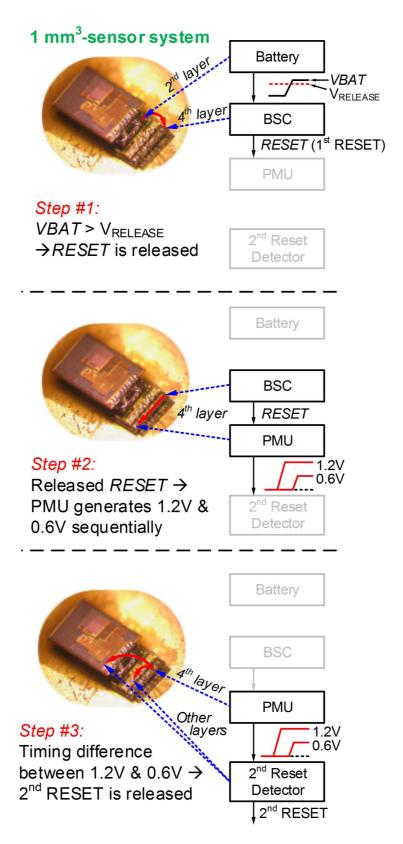

| 4.17   | 1 mm <sup>3</sup> -sensor system where proposed BSC is integrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69 |

| 4.18   | Reset propagation in 1 mm <sup>3</sup> -sensor system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

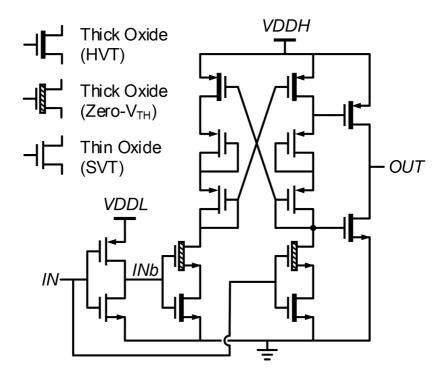

| 4.19   | Conventional level converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

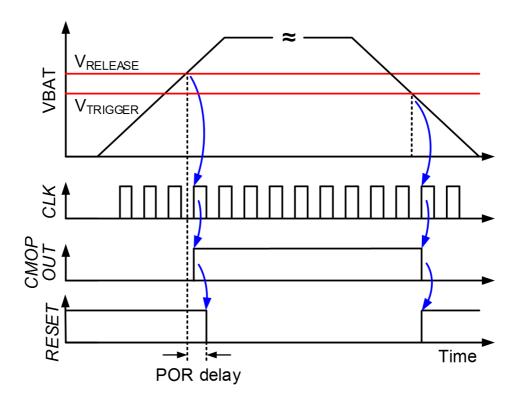

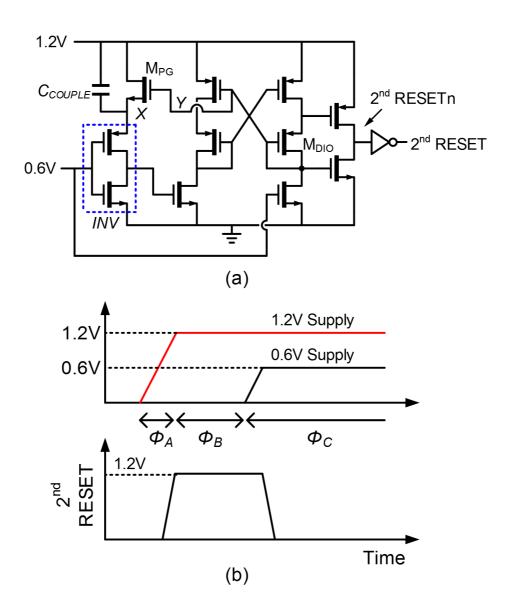

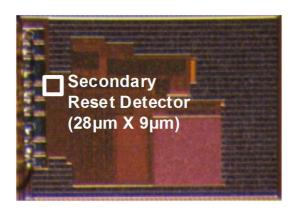

| 4.20   | Secondary reset detector (a) proposed reset detector (b) waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73 |

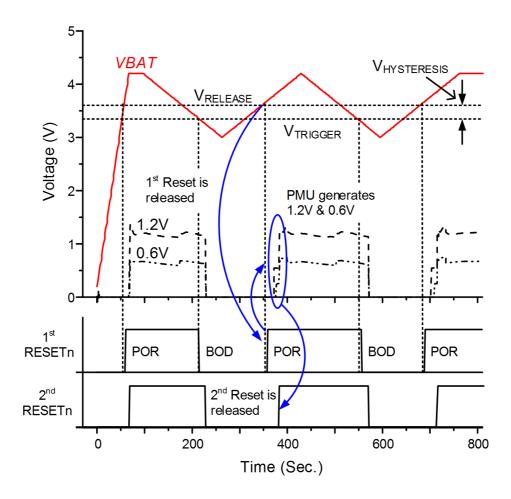

| 4.21   | Measured operation of BSC and secondary reset detector in the complete sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|        | system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

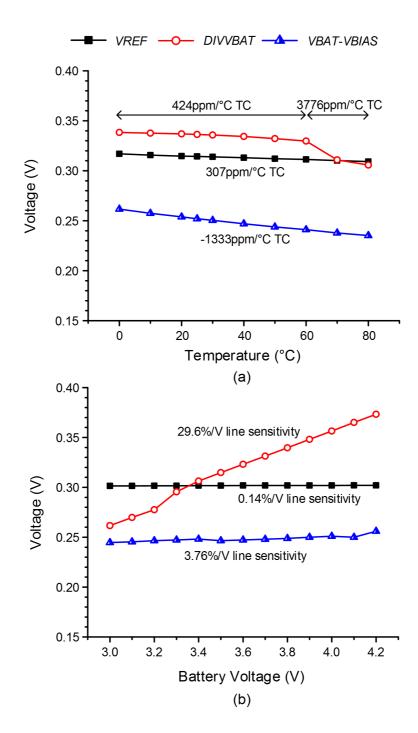

| 4.22   | Measured $V_{REF}$ , $DIVVBAT$ , and ' $V_{RET}$ - $V_{BIAS}$ ' (a) temperature dependency (b) battery voltage dependency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

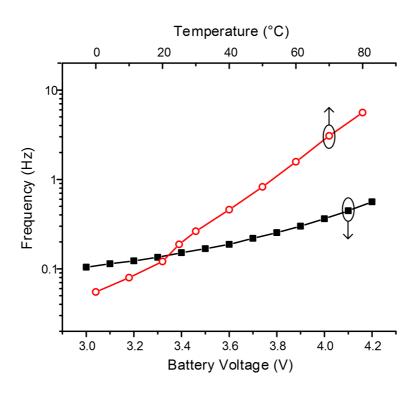

| 4.23   | Measured operating frequency of oscillator over temperature and battery voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

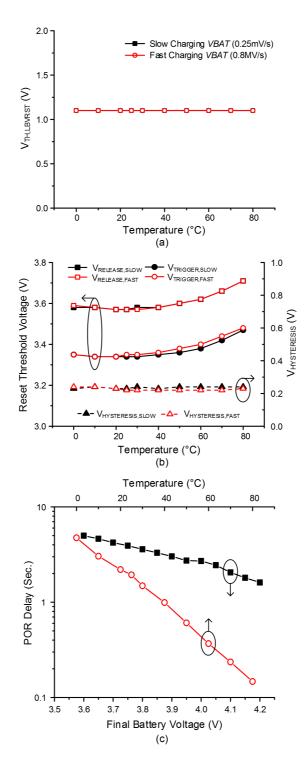

| 4.24   | Measured parameters of BSC (a) $V_{TH,LBVRST}$ over temperature from different battery voltage transition speed (0.25 mV/s and 0.8 MV/s) (b) $V_{TRIGGER}$ , $V_{RELEASE}$ , and $V_{TRIGGER}$ are the state of the specific parameters of the state of the specific parameters of the state of the specific parameters of the |    |

|        | and $V_{HYSTERESIS}$ over temperature from different battery voltage transition speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

| 1 25   | (0.25 mV/s and 0.8 MV/s) (c) POR delay over temperature and battery voltage Power consumption of BSC (a) Average power consumption from 15 chips over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78 |

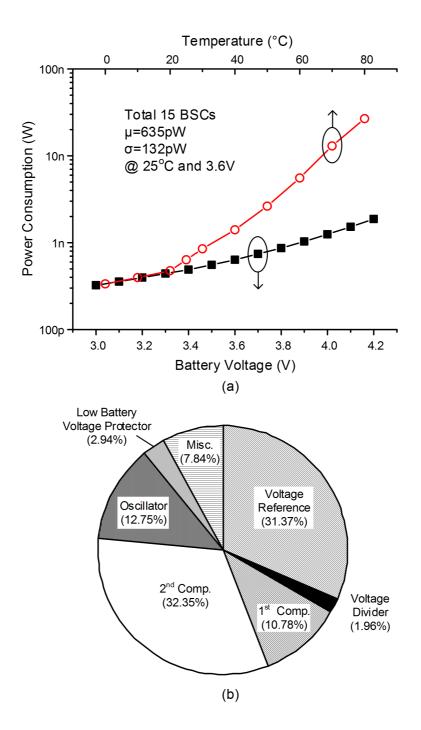

| 4.23   | temperature and battery voltage (b) Power breakdown at 25 °C and 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79 |

| 4.26   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81 |

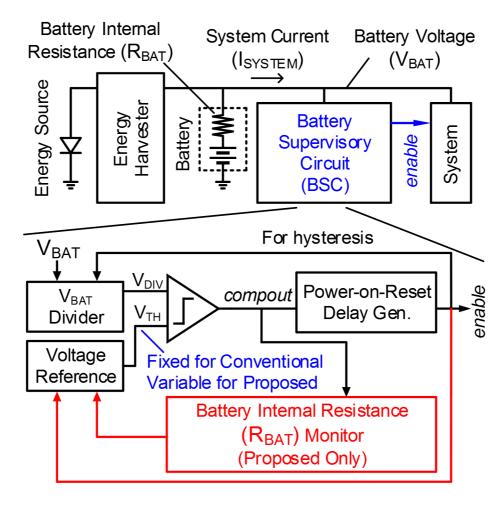

| 5.1    | Battery supervisory circuit (BSC) for a wireless sensor node (Red: Proposed only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84 |

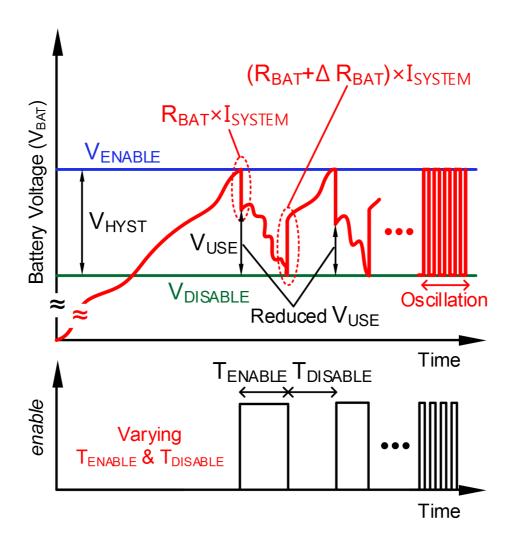

| 5.2    | Operation of conventional BSC with fixed-threshold voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85 |

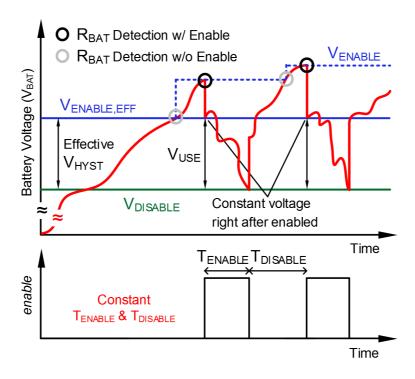

| 5.3    | Operation of proposed BSC with adaptive-threshold voltage ( $V_{ENABLE}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 86 |

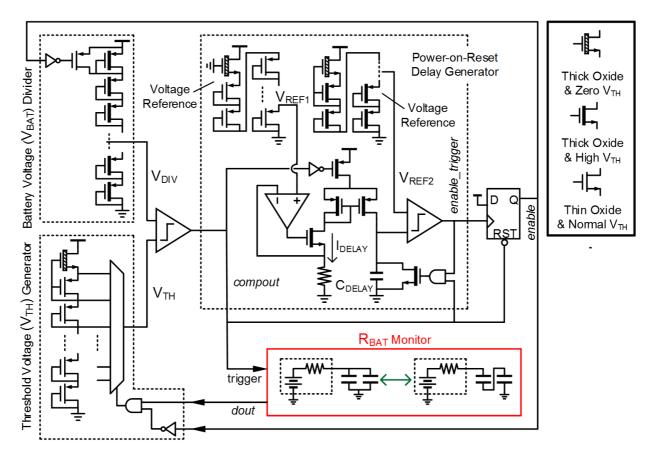

| 5.4    | Circuit diagram of proposed BSC with $R_{BAT}$ monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87 |

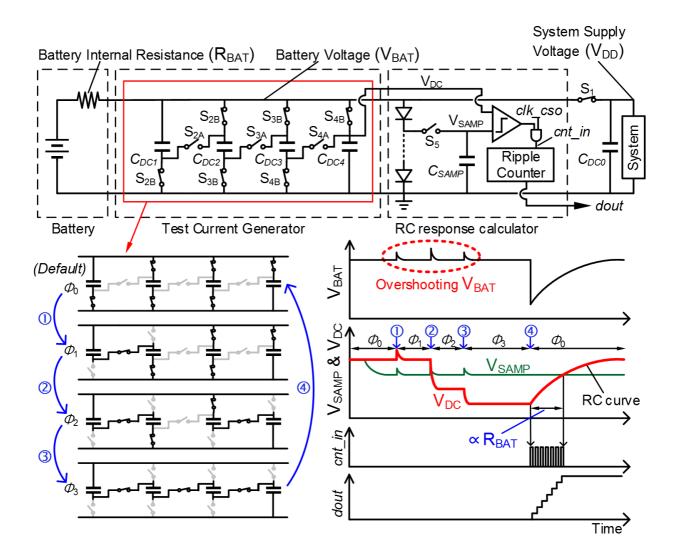

| 5.5    | Circuit diagram and operation of proposed $R_{BAT}$ monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88 |

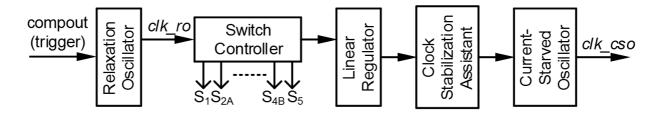

| 5.6    | Clock and control signal generation for $R_{BAT}$ monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 89 |

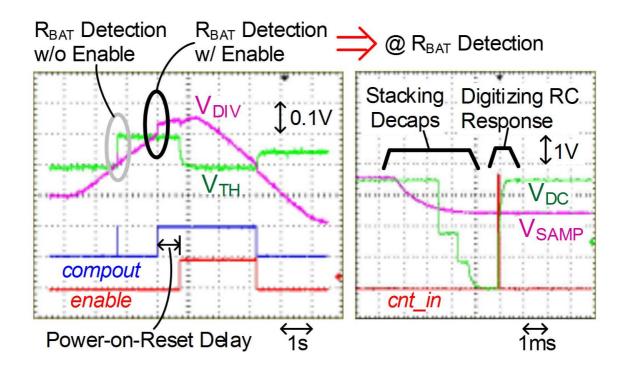

| 5.7    | Measured oscilloscope waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90 |

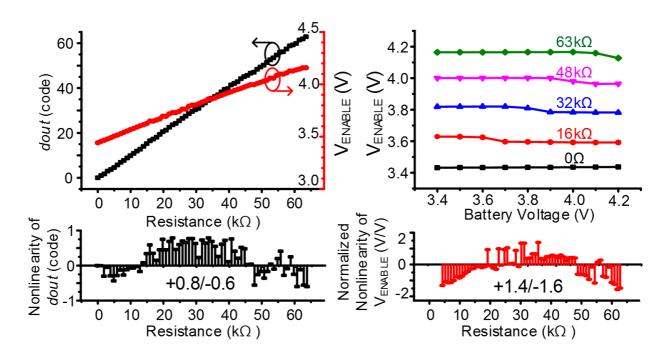

| 5.8    | Measured dout & $V_{ENABLE}$ over $R_{BAT}$ & $V_{BAT}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

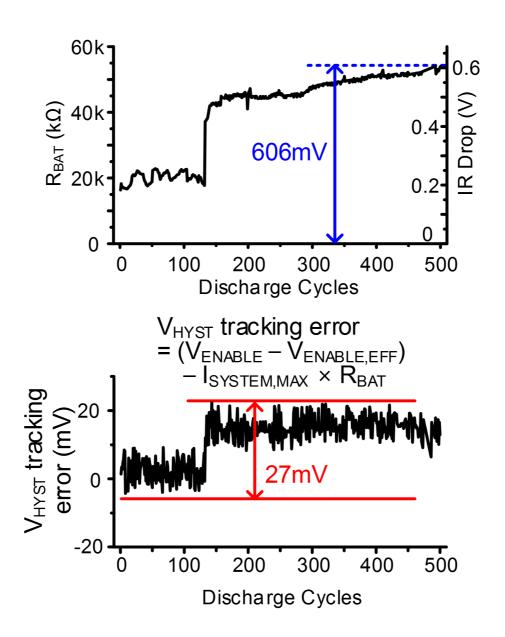

| 5.9    | Measured $R_{BAT}$ over discharge cycles & $V_{HYST}$ tracking error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91 |

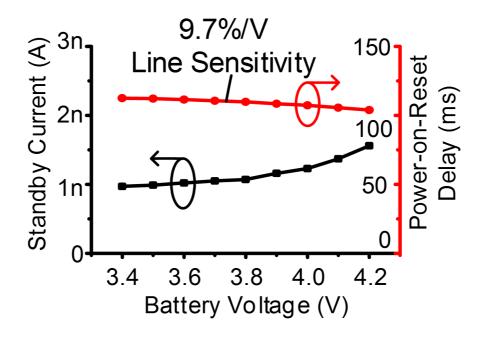

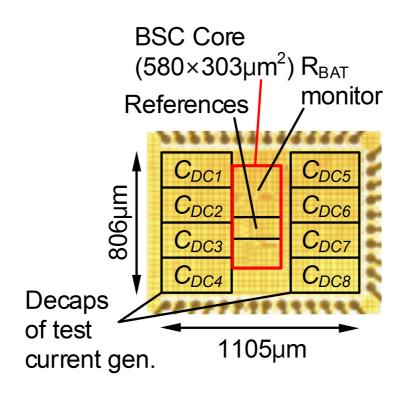

| 5.10   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92 |

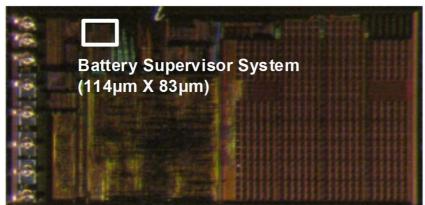

|        | Die photo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93 |

| J. I J | DIC DIIUU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | フィ |

## LIST OF TABLES

| Table |                                                                                 |    |

|-------|---------------------------------------------------------------------------------|----|

| 2.1   | Performance summary of the proposed oscillator and comparison to other prior    |    |

|       | works                                                                           | 33 |

| 3.1   | Performance summary of the proposed MPPT circuit and comparison to other prior  |    |

|       | works                                                                           | 49 |

| 4.1   | Measured reset threshold voltages from 15 chips at 25 °C with different battery |    |

|       | voltage transition speed.                                                       | 77 |

| 4.2   | Performance summary of the proposed BSC and comparison to other prior works     | 80 |

| 5.1   | Performance summary of the proposed adaptive BSC and comparison to other prior  |    |

|       | works                                                                           | 93 |

#### **CHAPTER 1**

#### Introduction

#### 1.1 Motivation

Miniature sensor nodes have recently enabled new application spaces in VLSI. In the continuation of Bell's Law [1], the size of computing systems have been shrunk down to cubic-millimeter scale (e.g. Michigan micro-mote) [2]. Especially, since the term "Smart Dust" was coined [3], rapid advances in low-power wireless sensor nodes have been driving the realization of Internet of Things [4]. With a unique feature set such as wireless communication, energy harvesting, the small form-factor, thus enabling non-invasive and secure placement, the sensor nodes have been developed for a number of applications such as medical, infrastructure, and surveillance [5–8].

For example, biomedical sensors have significantly increased the quality of medical care through miniaturization. Fig. 1.1 shows how the implantable cardiac pacemakers have changed in size. Their size has been reduced by 35 times over the last 54 years. There are the reasons for creating smaller biomedical devices: 1) with a smaller device, implantation can be done through a minimally invasive surgery or even a syringe; 2) small devices have better bio-compatibility and reduce foreign body rejection; 3) the small size allows devices to be placed in new locations where the space is very limited, like eyes, which enables more efficient treatments for a disease, such as glaucoma [9].

There has been active research on miniaturization of the sensing systems [5,6,9,10]. As shown in Fig. 1.2, the size of the bare die is often  $1 \sim 2$  mm. However, the associated systems, which are shown in the bottom of Fig. 1.2, are typically much larger than the bare die, resulting in

Figure 1.1: Miniaturization of implantable pacemakers.

Figure 1.2: Examples of recent miniature sensing systems.

Figure 1.3: Batteries.

the size up to centimeters, due to included peripherals such as electrodes, batteries, and casings. This leads to the first design challenge for electronics of the miniaturized systems; the maximum physical battery size is severely limited, so is the battery storage capacity. This issue becomes more important in implantable biomedical sensing systems, where the battery cannot be easily replaced, since it requires a surgery which would be difficult and expensive. As a result, low-power circuit design and energy harvesting techniques need to be investigated to allow the system operation within a very small power budget. Another important issue is that discrete components cannot be used due to the size constraint. This limits use of off-chip components such as a high-density capacitor, a high q-factor inductor, and a precise crystal oscillator. Thus, it requires design of high quality on-chip references, DC-DC converters, and RF frequency synthesizers. Of course, there are other challenges as well (e.g. packaging). However, in this dissertation, we will focus on the low power circuit and energy harvesting techniques.

Fig. 1.3 shows alkaline and lithium coin batteries, which are used widely in everyday life. From these two large batteries, Fig. 1.4 shows available average power budget for desired lifetime [11]. With 10  $\mu$ W average power, a system can be sustained for over a decade. However, these large-size batteries cannot be used for a miniature sensor node. Fig. 1.3 also shows a mm-scale lithium thin-film battery, which is designed for the miniature systems. As the battery size is reduced, its battery storage capacity is also limited as shown in the blue line in Fig. 1.4. With 2 nW to 200 nW average power consumption, a system can survive several days (up to a month). This lifetime

Figure 1.4: Average power budget for desired lifetime with different batteries.

Figure 1.5: Michigan Micro-Mote: a mm-scale sensing platform [2].

can then be extended with the help of an energy harvester. If the harvested power is larger than the average power of the system, the lifetime becomes no longer limited by the battery capacity but by the battery endurance, i.e., the number of charging cycles till the battery becomes worn out.

With this energy limitation, a mm-scale sensing platform, called Michigan micro-mote, has been developed [2]. In order to optimize circuit performance, the system is constructed from die fabricated in different technologies which are then stacked and wire-bonded together. Fig. 1.5 shows the wire bonding scheme for electrical connectivity. The stacked structure increases silicon area per unit volume and also makes it easy to swap layers in and out for flexibility in system configuration. To create a sensor system for new applications, end users can design an application-specific layer in a preferred technology, which complies with the given system power and communication interface. Fig. 1.6 shows a mm-scale temperature sensing system based on the platform [12]. Its size is 1.1mm × 2.2mm × 1mm and consists of an energy harvester, a recharge-

Figure 1.6: mm-scale temperature sensing system [12].

Radio

9/15

9/8

9/22

Figure 1.7: Implantable pressure monitor [13].

able thin-film lithium battery, a temperature sensor, an ARM processor, a 3kB retentive SRAM, power management circuits, and a near-field radio transmitter. For inter-layer communications, a low-power serial protocol, called Mbus, is used. This temperature sensing system has 8 nW standby power. With self-starting harvesting, it can sustain indefinitely in the room light condition, which is about 400 lux. In this condition, the system has survived a long-term test (over 1month of operation), which is also shown in Fig. 1.6. Fig. 1.7 shows another miniature system, which is an implantable pressure monitor [13]. The system is small enough to be placed on the side of a nickel. This pressure monitor includes a MEMS pressure sensor and a capacitive-to-digital converter. The system was implanted in a mouse and radio signals were received from the in-vivo sensor.

In these miniature sensing systems, there are four different energy flows: 1) energy harvester from a source (e.g., solar cells) to the battery; 2) power delivery circuits (e.g., Power Management Unit); 3) always-on circuits; 4) duty-cycled circuits. Available energy from the source of the harvester changes depending on the environmental condition, and the load current also changes considerably due to the duty-cycled operation. In such a dynamic system, an optimization of the energy harvester and the power converter is a key issue. In order to minimize the average power consumption to achieve a longer lifetime, always-on circuits should be designed to meet the extremely low standby power requirement of the system. Also, duty-cycled circuits need to be power-gated to keep the low standby power.

In this dissertation, new circuit techniques developed to satisfy these requirements will be discussed, which include a constant energy-per-cycle ring-oscillator designed for wide frequency range and a low power maximum-power-point-tracking circuit. A low power battery supervisory circuit and a battery health monitoring circuit will be also covered.

#### 1.2 Contribution of This Work and Organization

In Chapter 2, two energy-efficient oscillators that can be used for power converters are discussed. They are based on a leakage-based oscillator where the intermediate voltage region that causes a short-circuit current is quickly restored to the full-rail voltage, and the amount of the cell delay is determined by charging/discharging the internal nodes through the leakage. Also, the oscillators provide wide frequency range without a loss in energy efficiency thanks to a current

feeding scheme with gate voltage control. A test chip is fabricated in 0.18  $\mu$ m CMOS process, and the measurements show that the first proposed oscillator, Constant Energy-per-Cycle Ring-Oscillator (CEpCRO), achieves the constant energy-per-cycle of 0.8 J/cycle in 21 Hz  $\sim$  60 MHz, which is more energy-efficient than a conventional Current-Starved Ring-Oscillator (CSRO) if operating below 300 kHz at 1.8 V supply voltage. CEpCRO is implemented in a capacitive step-down converter, and compared to a converter using CSRO, it shows 56 % higher converter efficiency for 583 pW load power. The second proposed oscillator, Hybrid Ring-Oscillator (HRO), improves energy efficiency by 56 % for >80 kHz operations, compared to CEpCRO, by utilizing different modes to reduce switching capacitance.