# High Aspect-ratio Biomimetic Hair-like Microstructure Arrays for MEMS Multi-Transducer Platform

by

### Yemin Tang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2018

### **Doctoral Committee:**

Professor Khalil Najafi, Chair Doctor Jae Yoong Cho Professor Karl Grosh Assistant Professor Rebecca L Peterson Professor Kamal Sarabandi

## Yemin Tang

yemin@umich.edu

ORCID iD: 0000-0002-3986-1049

© Yemin Tang 2018

## **DEDICATION**

To my parents, Hong Liping 洪莉萍 and Tang Jianfa 唐建法.

#### **ACKNOWLEDGEMENTS**

First of all, I would like to acknowledge my PhD thesis advisor, Professor Khalil Najafi, for his patient guidance and support over the past six years. It has been great honor and privilege to have the opportunity to work with him, and I am always inspired by his enthusiasm, energy and dedication to both research and our EECS Department at the University of Michigan. I learn a lot from Professor Najafi not only through my own research project, but more broadly on the research and development processes of microelectromechanical systems (MEMS), micromachined transducers, and integrated microsystems. He will always be one of my favorite teachers and whom I have always been trying to emulate in my own life: be professional, be approachable, enjoy what we do, be kindly demanding to both ourselves and others, and be creative.

I would like to acknowledge my dissertation committee, Prof. Kamal Sarabandi, Prof. Karl Grosh, Prof. Rebecca L Peterson, and Dr. Jae Yoong Cho for their evaluation of this thesis work. My special thanks go to Mr. Robert Gordenker for his help in sustaining the Najafi testing labs and many insightful and inspiring discussion on the MAST project. I would also like to take this opportunity to thank Dr. Brett Piekarski and Dr. William Nothwang of Army Research Laboratory, and the Micro Autonomous Systems & Technology (MAST) Program for support of the research in this dissertation.

This thesis work is also not possible without many LNF staff and engineers. Their hard work and professionalism ensure that the various equipment in the cleanroom meet the designed specs, and the processes yield in a timely manner, so that I can meet many important deadlines. Special thanks to the SPTS Pegasus 4 Deep Reactive Ion Etch (DRIE) etcher.

This moment also brings me to express my gratitude to all my past and present fellow Najafi group mates, as well as friends from SSEL and LNF community, for their academic and personal support. Their strive for excellence and perseverance in their own research work over the years have encouraged and motivated me to achieve my own research goals. They have made my years in Ann Arbor and graduate school enjoyable and fulfilling, and I believe our everlasting friendship will be the most valuable gifts from Ann Arbor.

Last but not least, I owe my deepest gratitude to my parents, Hong Liping and Tang Jianfa. They have always supported me and encouraged me to try my best to pursue my dreams throughout all these years since I came to Ann Arbor junior year undergrad in 2009 from an ocean apart in Shanghai China, and continued graduate school. I also want to thank Yi for his company and love. I am so happy to have met him in Ann Arbor.

### **Table of Contents**

|                  |       | ON                                                                 |      |

|------------------|-------|--------------------------------------------------------------------|------|

| ACKN(            | OWL   | EDGEMENTS                                                          | iii  |

| List of l        | Figuı | 'es                                                                | viii |

| List of 7        | Гabl  | es                                                                 | XX   |

| ABSTR            | ACI   |                                                                    | xxi  |

| Chapte           | r 1   | INTRODUCTION                                                       | 1    |

| 1.1              | Mo    | otivation for Biomimetic Hair Multi-Transducer Microsystem         | 2    |

| 1                | 1.1.1 | High Accuracy Over Wide Full-Scale Range                           | 7    |

| 1                | 1.1.2 | Micromechanical Frequency Processer over Wide Frequency Spectrum   | 14   |

| 1                | 1.1.3 | High Frequency Stability and Accuracy by Resonator Array           | 17   |

| 1                | 1.1.4 | Technology Development: 3D Vertical Integration                    | 18   |

| 1.2              | Lit   | erature Reviews on MEMS Biomimetic Hair Sensors and Sensor Arrays  | 22   |

| 1.3              | Th    | esis Contributions and Organization                                | 25   |

| 1.4              | Re    | ferences                                                           | 29   |

| Chapte           | r 2   | HIGH ASPECT-RATIO BIOMIMETIC HAIR STRUCTURE                        | 33   |

| 2.1              | M     | EMS Accelerometer and Hair Structure Description                   | 33   |

| 2.2              | Op    | timization of Hair Structure Design                                | 37   |

| 2.3              | De    | sign Constraints Imposed by Critical Fabrication Steps             | 42   |

| 2                | 2.3.1 | Nominal Sensing Gap and Device Height Constraints Imposed by DRIE  | 42   |

| 2                | 2.3.2 | Shock Survival Constraints Imposed by Hair Spring Bonding Strength | 46   |

| 2.4              | Re    | ferences                                                           | 49   |

| Chapter<br>THICK |       | ULTRA-HIGH-ASPECT RATIO DEEP REACTIVE ION ETCHING IT               |      |

| 3.1              | En    | abling Technology: Deep Reactive Ion Etching (DRIE)                |      |

|       | 3.1.1 | Shortcomings of Standard Time-Multiplexed Bosch DRIE                                                 | 55    |

|-------|-------|------------------------------------------------------------------------------------------------------|-------|

|       | 3.1.2 | Standard Fixed-Parameter Bosch DRIE Process                                                          | 62    |

| 3.2   | DRI   | E with Ramped Process Parameters for High Aspect-Ratio Deep DRIE                                     | 65    |

|       | 3.2.1 | DRIE Process Parameters                                                                              | 67    |

|       | 3.2.2 | Microfabrication process                                                                             | 69    |

| 3.3   | Ultra | a-High-Aspect-Ratio Deep DRIE Results                                                                | 70    |

|       | 3.3.1 | DRIE of Trenches: Etch Rate and Etch Profile                                                         | 70    |

|       | 3.3.2 | DRIE of Circular Holes: Etch Rate and Etch Profile                                                   | 75    |

|       | 3.3.3 | Ultra-Deep and Through-Wafer DRIE                                                                    | 76    |

|       | 3.3.4 | Pattern Dependency                                                                                   | 81    |

| 3.4   | Sum   | mary                                                                                                 | 83    |

| 3.5   | Refe  | rences                                                                                               | 84    |

| Chapt |       | UNIFORM-GAP HAIR ACCELEROMETER BY SILICON-ON-GLASS                                                   |       |

| ` ′   |       | ESS                                                                                                  |       |

| 4.1   |       | nology Development and Microfabrication                                                              |       |

|       | 4.1.1 | Applying Ultra High Aspect-Ratio DRIE                                                                |       |

|       | 4.1.2 | Silicon-Glass Anodic Bonding with Metal                                                              |       |

| 4.2   |       | Accelerometer Testing Results                                                                        |       |

| 4.3   | Refe  | rences                                                                                               | . 100 |

| Chapt |       | WO-GAP HAIR STRUCTURE                                                                                |       |

| 5.1   |       | gn Objectives                                                                                        |       |

| 5.2   |       | -Gap Process                                                                                         |       |

|       |       | OW-NOISE HIGH-SENSITIVITY MULTI-AXIS CAPACITIVE HAIR                                                 |       |

| 6.1   |       | ectives: High Sensitivity (>1pF/g/mm <sup>2</sup> ) and Low Noise Floor (sub- $\mu$ g/ $\sqrt{Hz}$ ) |       |

| 6.2   |       | ication Results                                                                                      |       |

| 0.2   | 6.2.1 | Ultra-Deep DRIE                                                                                      |       |

|       | 6.2.2 |                                                                                                      |       |

|       |       | Silicon-Gold Eutectic Bonding                                                                        |       |

| (2    | 6.2.3 | Thinning Hair Spring by Isotropic RIE                                                                |       |

| 6.3   |       | digitated-Electrode Device by Two-Gap Process                                                        |       |

| 6.4   | -     | acitive Hair Accelerometer Testing Results                                                           |       |

|       | 6.4.1 | Electromechanical Testing                                                                            | . 135 |

| $\epsilon$       | 5.4.2 Resonance Testing and Quality Factor                               | 141 |

|------------------|--------------------------------------------------------------------------|-----|

| 6.5              | References                                                               | 145 |

| Chapter          | 7 CAPACITANCE READOUT FRONT-END                                          | 147 |

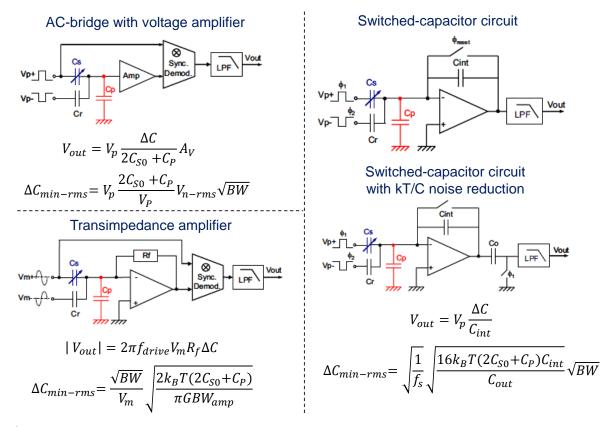

| 7.1              | Precision Readout Circuits for Capacitive MEMS Accelerometer             | 147 |

| 7.2              | Pixel-Level Differential Switched-Capacitor Charge Amplifier Front-End   | 149 |

| 7.3              | CMOS MEMS Integration                                                    | 157 |

| 7.4              | References                                                               | 166 |

| Chapter<br>ACCEL | 8 LOW-POWER WIDE-RANGE DIGITAL HAIR ACCELEROMETER<br>EROMETER ARRAYS     |     |

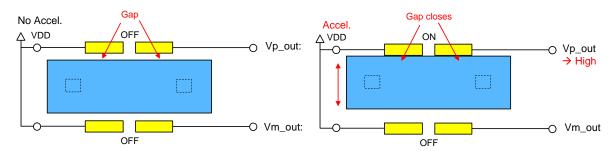

| 8.1              | Motivation                                                               | 168 |

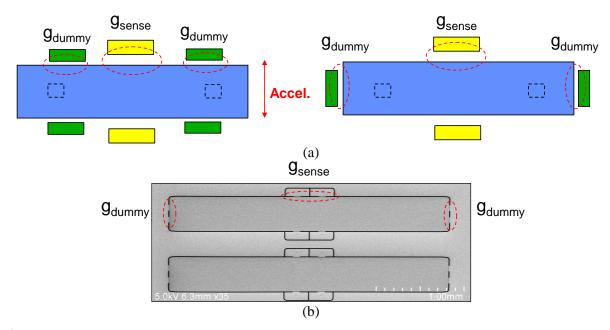

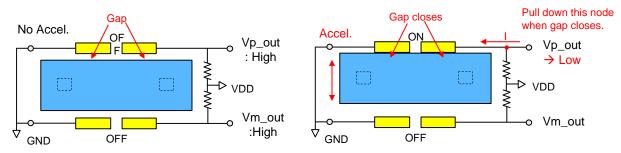

| 8.2              | Digital Threshold Array Design Objectives                                | 174 |

| 8.3              | Fabrication Process and Results                                          | 181 |

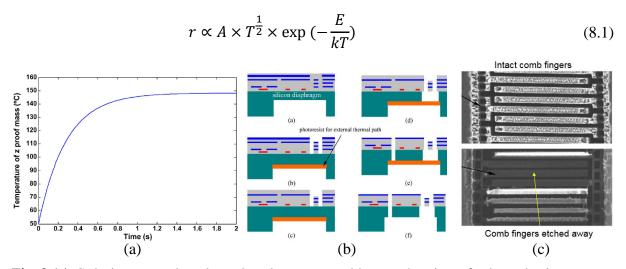

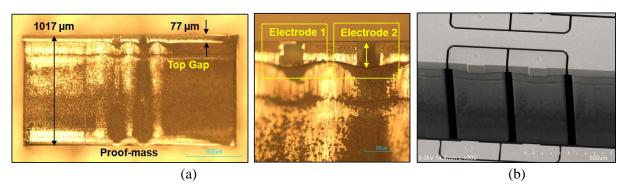

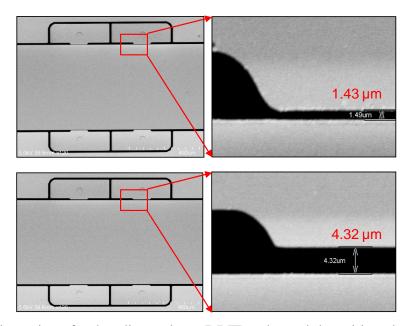

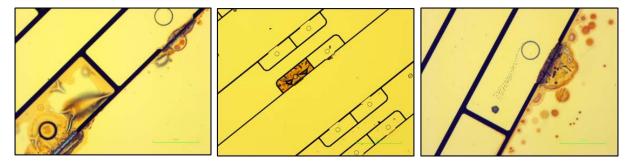

| 8                | 3.3.1 Release DRIE                                                       | 185 |

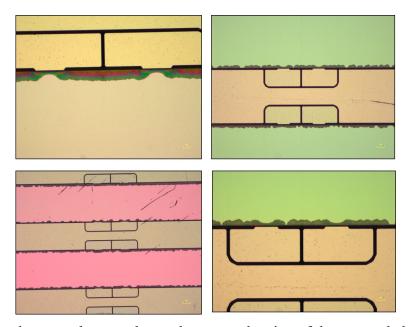

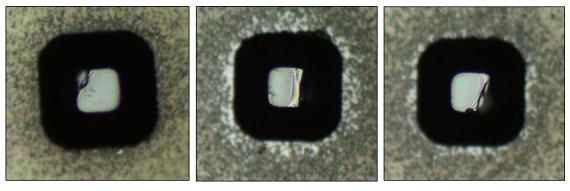

| 8                | 3.3.2 Silicon-Glass Anodic Bonding Quality and Strength                  | 191 |

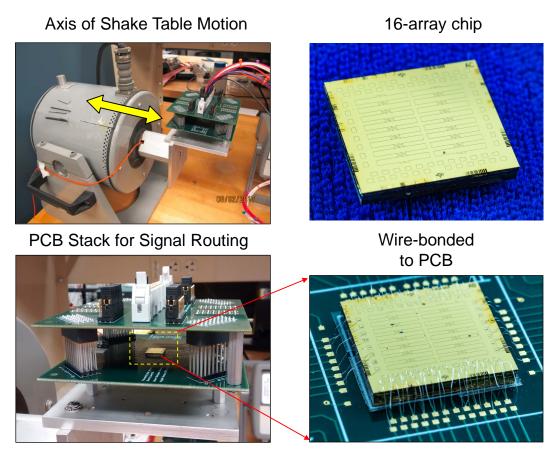

| 8.4              | Electromechanical Testing Results                                        | 195 |

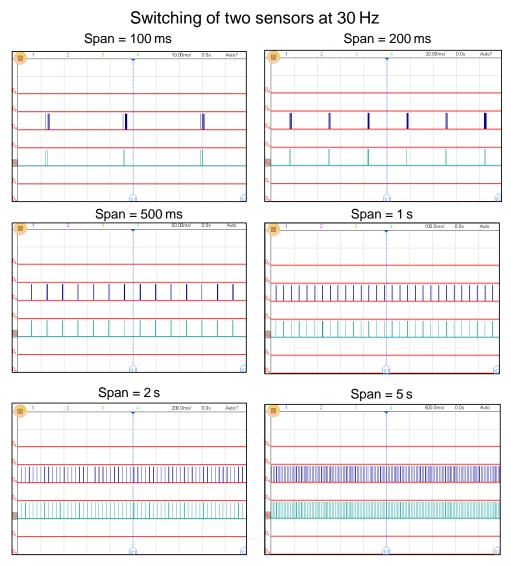

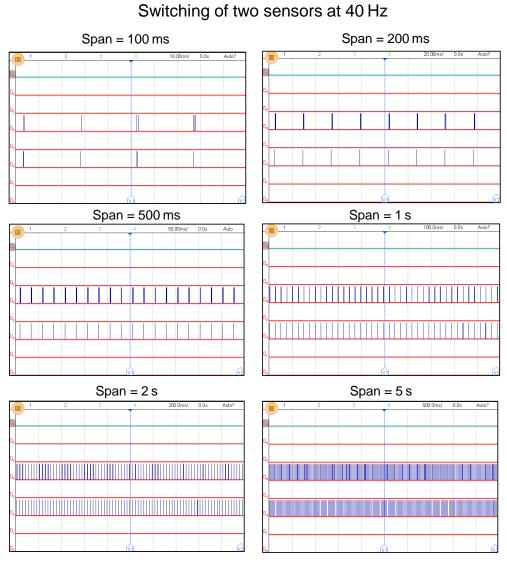

| 8.5              | Low-Power Digital Resonant Array for Micromechanical Frequency Processer | 200 |

| 8.6              | References                                                               | 207 |

| Chapter          | 9 CONCLUSION                                                             | 209 |

| 9.1              | Accomplishments                                                          | 209 |

| 9.2              | Suggestions for Future Work                                              | 212 |

| 93               | References                                                               | 214 |

# **List of Figures**

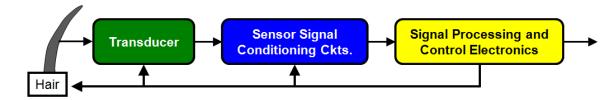

| Fig. 1.1. Biomimetic hair sensor system [1].                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

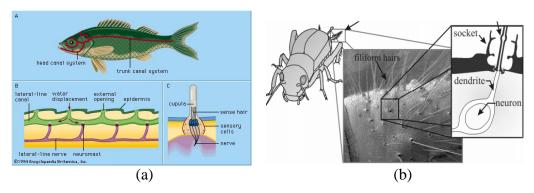

| Fig. 1.2. Hair in nature: (a) Neuromast called cupula going down the side of the fish [2]; (b) Air flow sensing in crickets by appendages call "cerci" [3]                                                                                                                                                         |

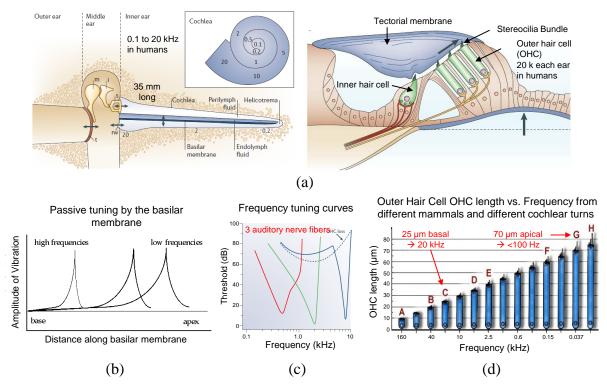

| Fig. 1.3. Hair cells in the vestibular system and cochlear: (a) Inner and outer hair cells interact with basilar membrane excited by sound wave;(b) (c) (d) Auditory frequency selectivity [4] 4                                                                                                                   |

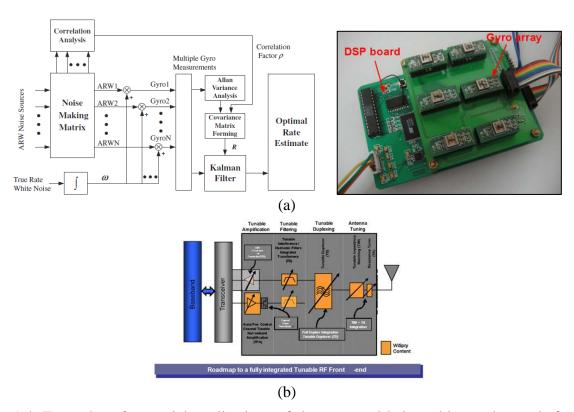

| Fig. 1.4. Examples of potential applications of the proposed hair multi-transducer platform: (a) Synthetic Gyroscope [7], (b) Fully integrated tunable RF front-end [8]                                                                                                                                            |

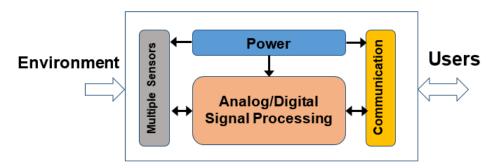

| Fig. 1.5. Components of smart sensors.                                                                                                                                                                                                                                                                             |

| Fig. 1.6. Measurement results of some of the 16 application nodes of a Smartec UTI [1.14] 8                                                                                                                                                                                                                        |

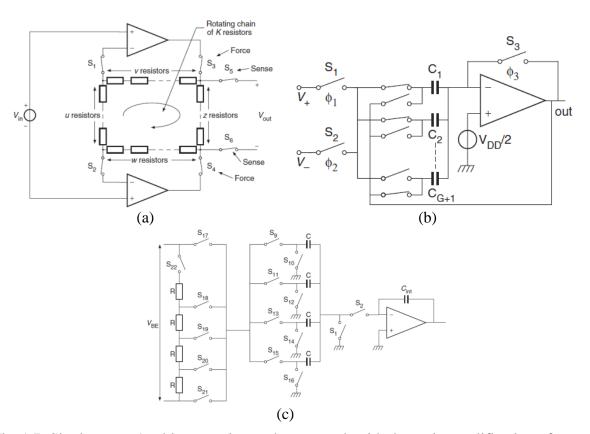

| Fig. 1.7. Single-sensor/multi-processing-paths approach with dynamic amplification of sensor output by circuit: (a) Rotating chain of K resistors as a dynamic-feedback instrumentation amplifier [15]; (b) A dynamic element matching (DEM) switched capacitor amplifier [16]; (d) A dynamic voltage divide [17]. |

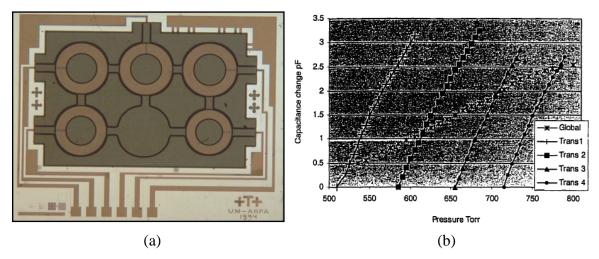

| Fig. 1.8. An integrated high resolution barometric pressure sensing system [18-19]: Measured output voltage of global range selection transducer and four segment transducers                                                                                                                                      |

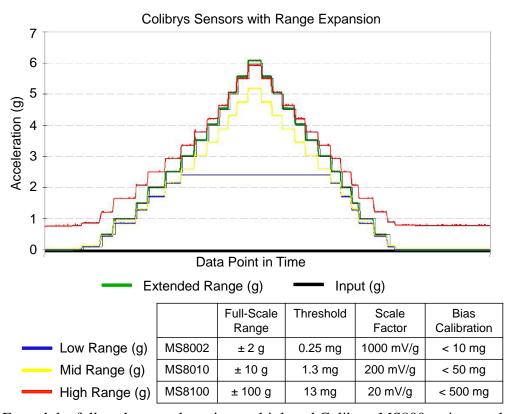

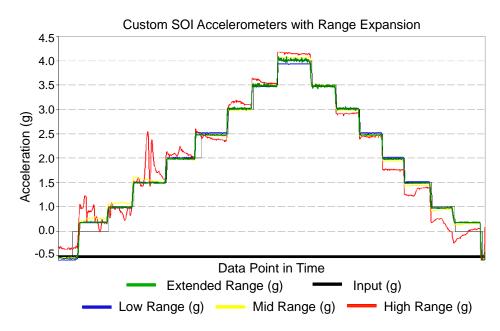

| Fig. 1.9. Extend the full-scale range by using multiplexed Colibrys MS800 series accelerometer arrays [5]                                                                                                                                                                                                          |

| Fig. 1.10. Extend the full-scale range by using of multiplexed accelerometer arrays co-fabricated on custom SOI substrates [5]                                                                                                                                                                                     |

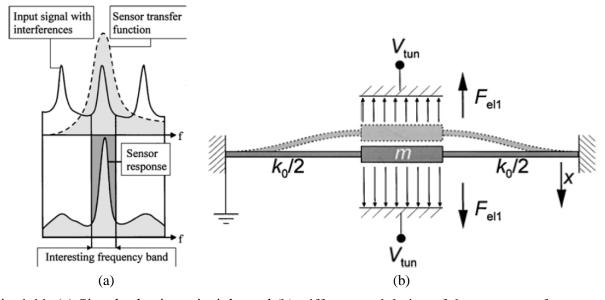

| Fig. 1.11. (a) Signal selective principle, and (b) stiffness modulation of the resonance frequency of the spring-mass pair by electrostatic forces. [20]                                                                                                                                                           |

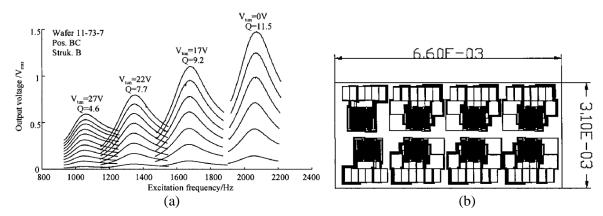

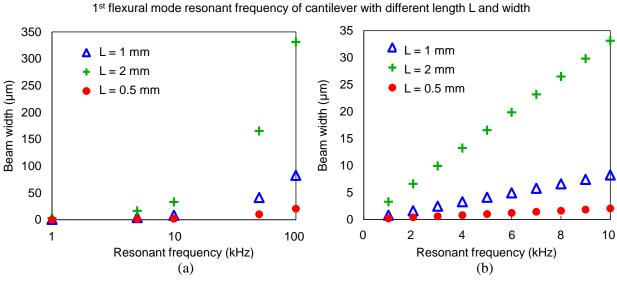

| Fig. 1.12. (a) Measurement of one sensor structures that covers 1 to 2 kHz with various tuning voltage, and (b) Layout of eight-sensor array that covers 1 to 10 kHz. [20]                                                                                                                                         |

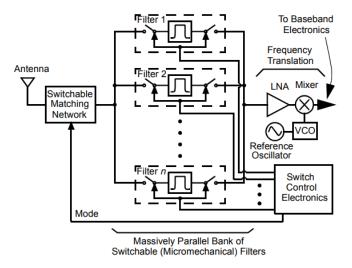

| Fig. 1.13. Simplified block diagram of highly selective filters proposed for communications subsystems, where each filter switch combination corresponds to a single micromechanical filter [21]                                                                                                                   |

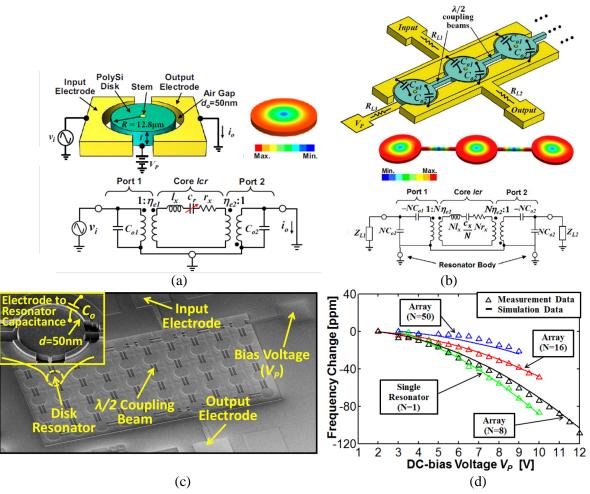

| Fig. 1.14. (a) Schematic of a 215-MHz radial-contour mode polysilicon disk resonator in a two-port excitation and sensing configuration with the classic equivalent electrical circuit that has the electrical stiffness lumped into the variable capacitance $C_r$ ; (b) Schematic of a disk array-composite resonator with disks linked by $\lambda/2$ coupling beams to enforce in phase vibration of each individual resonator. Negative capacitance equivalent circuit of a disk array-composite with N resonators based on element values of the single resonator equivalent circuit; (c) SEM of a 215-MHz 50 nm capacitive-gap transduced contour mode disk array employing 50 mechanically coupled resonators; and (d) Measured curves of resonance frequency versus dc-bias voltage $V_p$ plotted against simulation using negative capacitance equivalent circuit models for disk arrays with N=1, N=8, N=16, and N=50. [22] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.15. Options for process integration of MEMS and electronic fabrication sequences: i) interleaved steps, ii) MEMS-first, and iii) MEMS-last, including formation of microstructures from the metallization stack layers [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

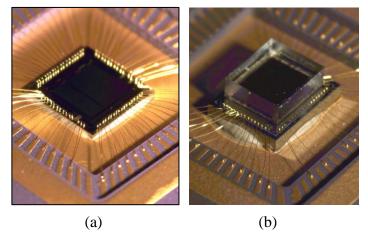

| Fig. 1.16. CMOS image sensors (a) a CMOS die and (b) VI-CMOS prototype with a photodetector die stack on top of a CMOS die [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

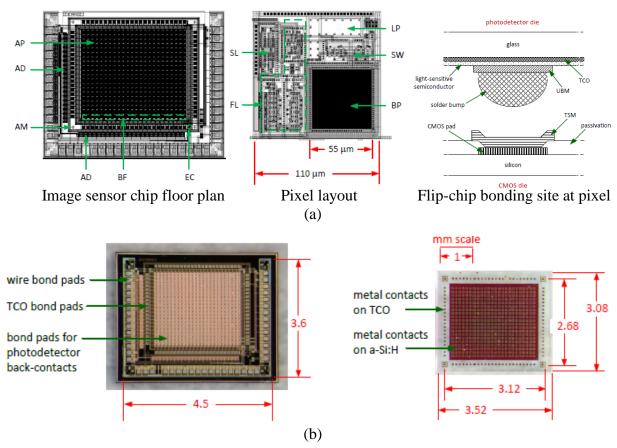

| Fig. 1.17. VI-CMOS prototypes: (a) pixel dimension of $100 \times 100 \mu\text{m}^2$ ; (b) pixel dimension of $10 \times 10 \mu\text{m}$ pixel dimension of $100 \times 100 \mu\text{m}^2$ [30].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

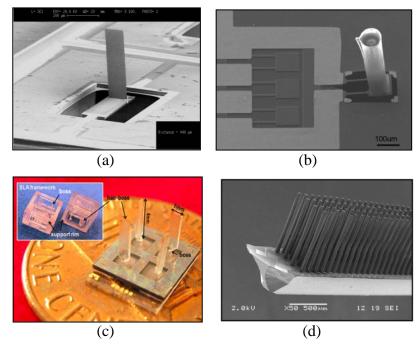

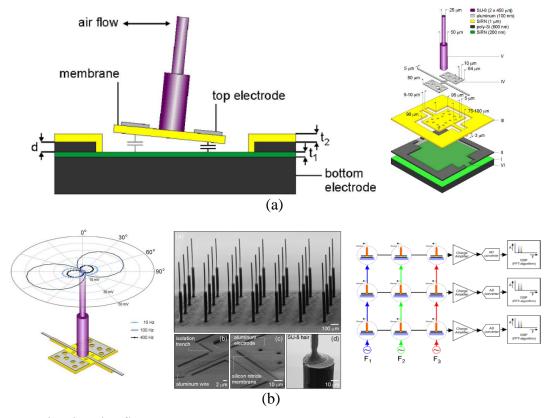

| Fig. 1.18. Micromachined hair sensors in literature: (a) 820-μm tall cilium is curled up by plastic deformation magnetic-assembly with strain gauge attached [34] to mimic lateral line sensors in fish; (b) 700-μm tall SU - 8 hair and strain gauges at their base [35]; (c) Directional air flow sensor array by stereo-lithography and MEMS micro-hydraulic structures [36-37]; (d) Arrays of SU8 hair by lithography. Capacitive sensing is at the base [38-39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

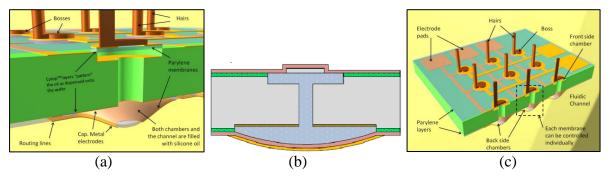

| Fig. 1.19. Micro-hydraulic structure with hair attached to bossed membrane. The base structure consists of top and bottom chambers and a pair electrodes for electrostatic actuation and capacitive sensing [36-37]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 1.20. Biomimetic flow sensor array with sensitivities on the order of 1 mm/s. (a) Operation: Capacitive transduction relies on the tilting of a membrane by drag forces acting on the SU-8 receptive hair of the sensor; (b) Superposition of the acoustic measurements at three different frequencies (10 Hz, 100 Hz and 400 Hz) on the flow-sensor. An array of sensors uses frequency-division modulation (FDM) circuits for flow pattern recognition [38-39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

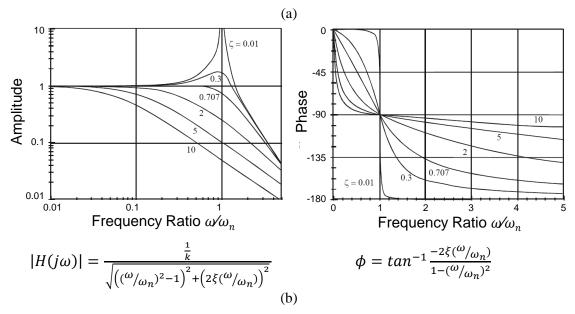

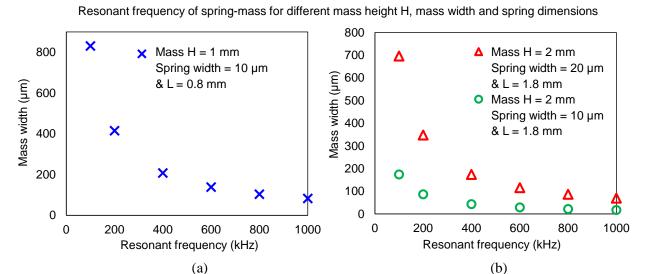

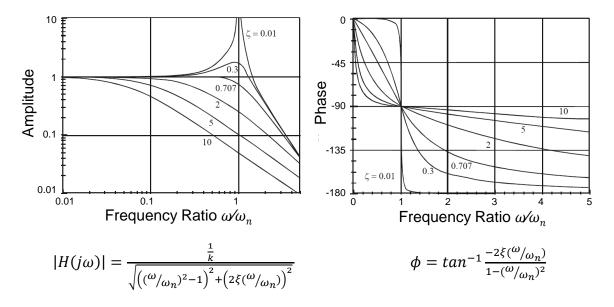

| Fig. 2.1. (a) MEMS accelerometer: second order mass-spring-damper system. (b) Amplitude and phase response of the second order mass-spring-damper system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

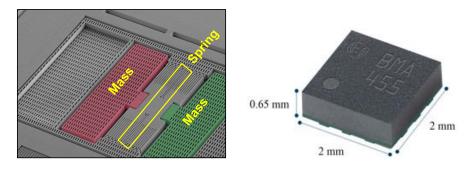

| Fig. 2.2. Bosch BMA455 Accelerometer [2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

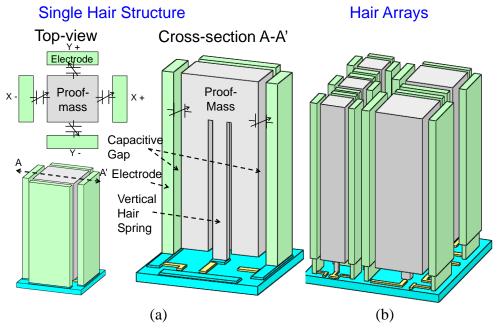

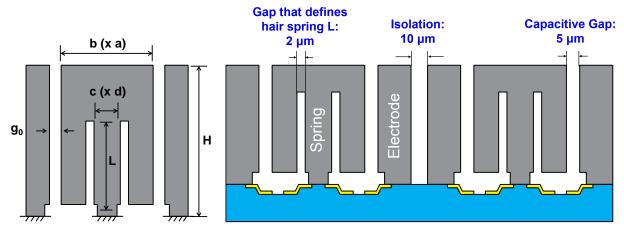

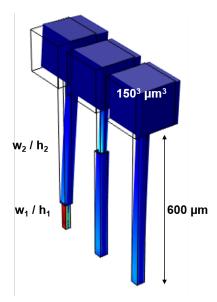

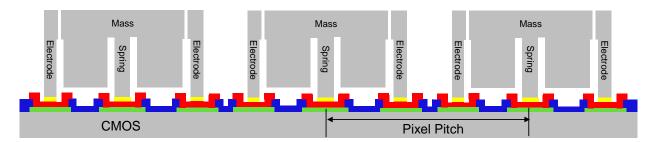

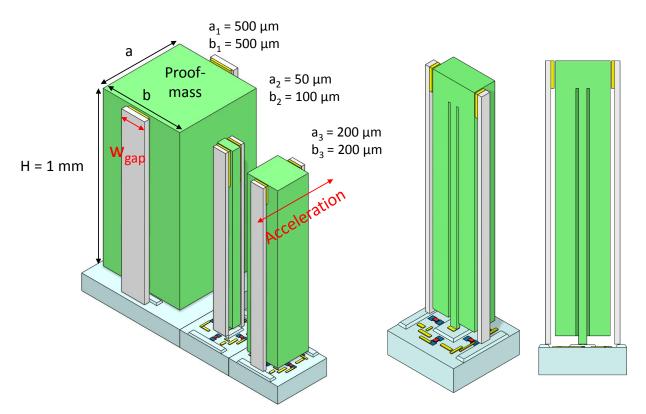

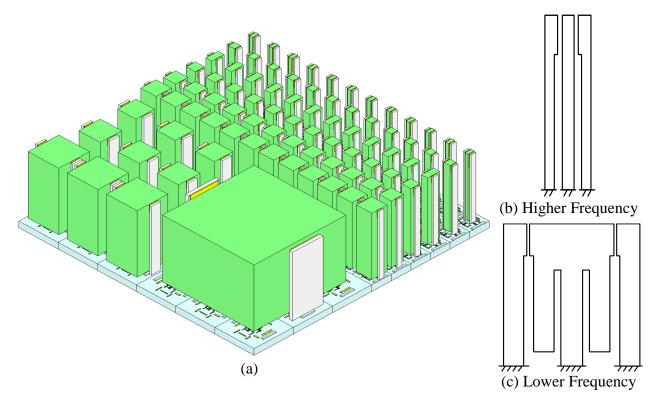

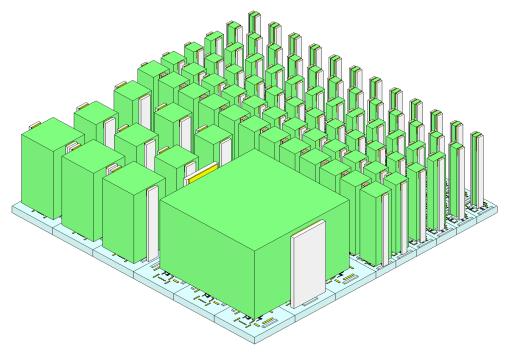

| Fig. 2.3. Proposed biomimetic hair sensor structure: (a) Single biomimetic hair structure with vertical hair-like spring, tall proof-mass, and electrodes for capacitive sensing and actuation; (b) An array of hair structures with various dimensions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

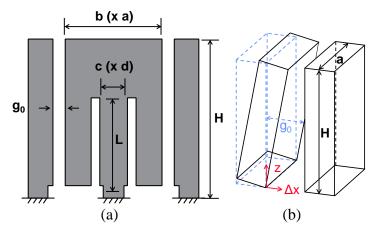

| Fig. 2.4: (a) Critical design parameters of the hair structure; (b) Gap profile when lateral acceleration is applied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

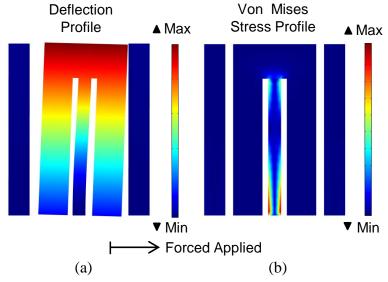

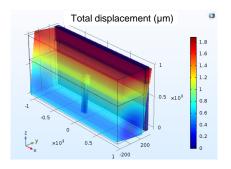

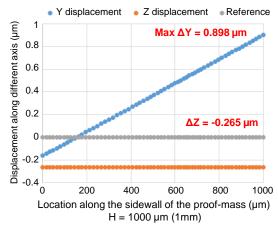

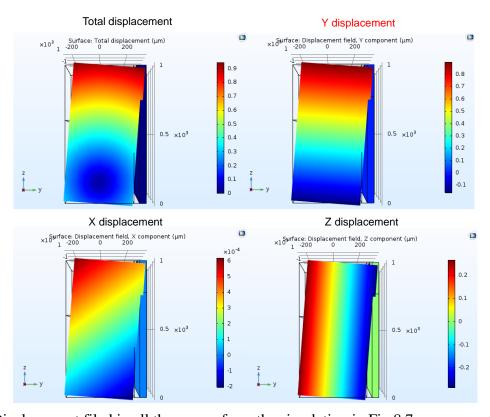

| Fig. 2.5. COMSOL simulation results showing: (a) Deflection profile and (b) von Mises stress profile of the hair structure along the axis of acceleration applied under in-plane lateral force. Maximum stress is at the anchor of the vertical hair spring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

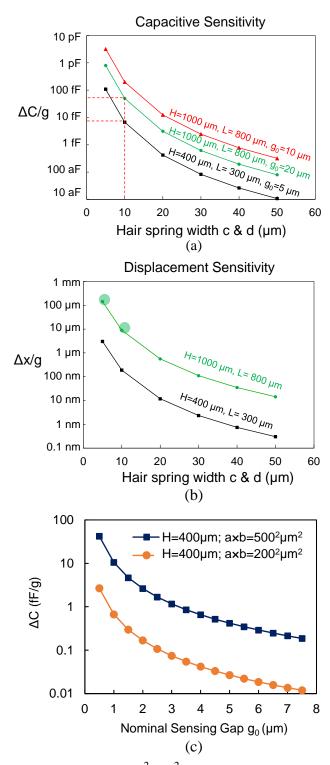

| Fig. 2.6. Sensitivity: (a) $\Delta C/g$ for $500^2  \mu m^2$ footprint with various device height H, spring dimensions, and nominal sensing gap; (b) Displacement sensitivity; and (c) Comparison of $200^2  \mu m^2$ and $500^2  \mu m^2$ proof-mass footprint devices for various nominal sensing gaps as small as $0.5  \mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

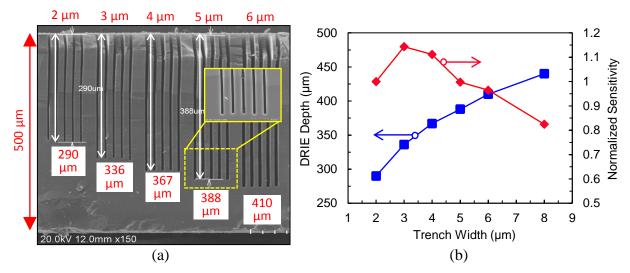

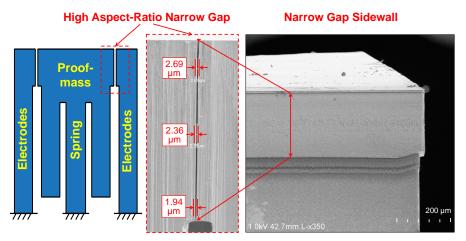

| Fig. 2.7. Ultra-HAR DRIE characterization: (a) SEM cross-section of UHAR DRIE for 2 μm – 6 μm gaps; (b) DRIE depth vs. gap width (red) and the normalized capacitive sensitivity when this width/depth combination is used as the capacitive sensing gap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

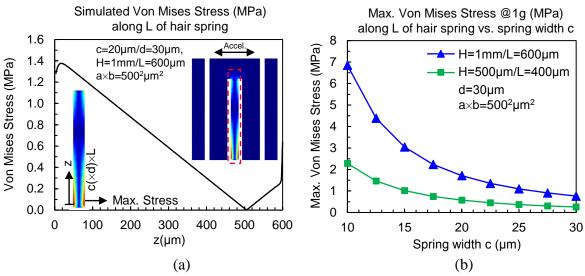

| Fig. 2.8. Maximum von Mises stress analysis for in-plane motion for proof-mass footprint $a \times b = 500^2 \mu\text{m}^2$ . (a) von Mises stress profile along the deflected hair spring; (b) Max. stress for different spring design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 2.9. Maximum stress and the corresponding acceleration at full gap $g_0 = 2 \mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

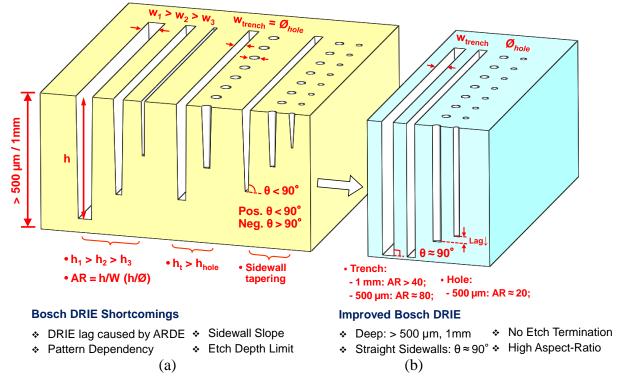

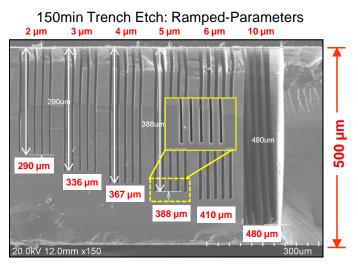

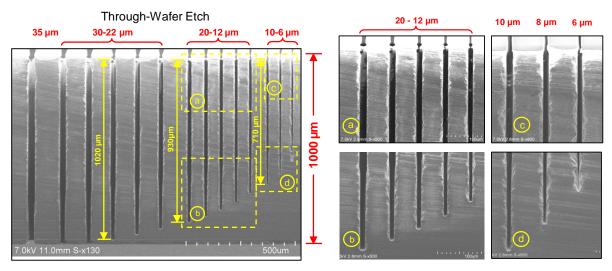

| Fig. 3.1. Ultra-deep ultra-high aspect-ratio etching of thick silicon wafers ( $\geq 500 \mu m$ ) with straight sidewalls across a wide range of feature sizes and patterns using an improved Bosch DRIE process. Shortcomings of the standard Bosch DRIE process with fixed etch and passivation sub-cycle parameters include:1) sidewall slope ( $\theta < 90^{\circ}$ defined as positive and $\theta > 90^{\circ}$ defined as negative), etch termination (instantaneous etch rate equals zero), and DRIE-lag ( $W_1 > W_2 > W_3 \rightarrow h_1 > h_2 > h_3$ ), all caused by ARDE; and 2) DRIE pattern dependency ( $W_{trench} = \Phi_{hole} \rightarrow h_{trench} > h_{hole}$ ). These shortcomings are addressed by continuously ramping the Bosch DRIE etch and passivation sub cycle parameters (plasma power, step duration, and chamber pressure) throughout the process. The achieved aspect-ratios ( $W/h$ for trenches, $\Phi/h$ for holes) are greatly increased and sidewall slopes approach 90°. No etch termination is observed. |

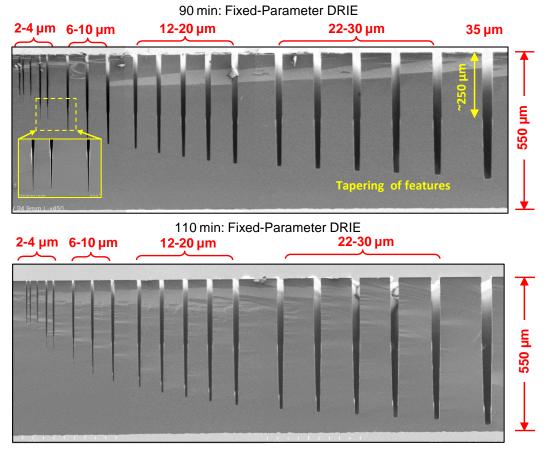

| Fig. 3.2. Standard fixed-parameter DRIE results: 90 min and 110 min DRIE on $2-35 \mu m$ wide trenches. Sidewalls of trenches $< 6 \mu m$ wide converge to a point and the etching is terminated within the 90 min DRIE. Although the apparent etch rate of trenches $> 6 \mu m$ wide does not reach zero, sidewall tapering of all feature sizes is observed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

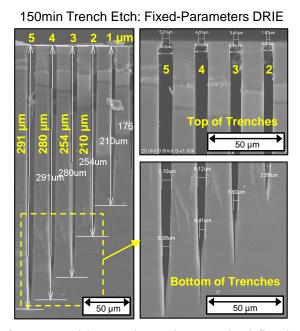

| Fig. 3.3. 150 min DRIE of 1-5 μm wide trenches using standard fixed process parameters. SEM images show major sidewall tapering and convergence to a point at the bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

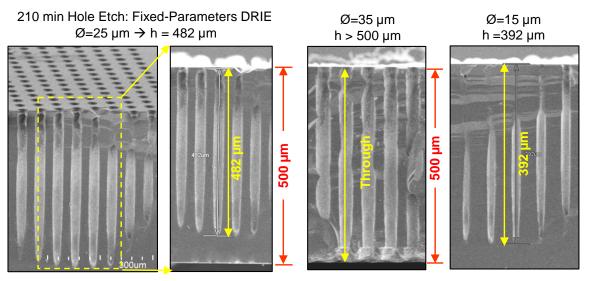

| Fig. 3.4. SEM images of holes with various diameter etched for 210 min with the standard fixed-parameter DRIE process. The bottom of the holes converge to a sharp point and etching is terminated. Due to the ion flux and ion energy dependency on in-plane aspect-ratio (length to width), obtaining HAR DRIE in hole/via etching is more difficult compared to etching trench with the same width as the hole diameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig. 3.5. DRIE masking materials used for ultra-deep ultra-high aspect-ratio (UHAR) long DRIE processes: $5$ - $6 \mu m$ LPCVD SiO <sub>2</sub> and thick photoresist layers are used as hard and soft masking material respectively. Thinner resist ( $\sim 3 \mu m$ ) is used for $1$ - $10 \mu m$ feature sizes due to lithography limitations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

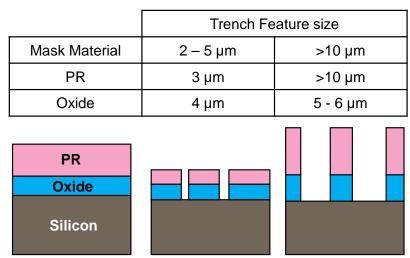

| Fig. 3.6. DRIE of 2-10 µm wide trenches by the ramped-parameter process for 150 min. Deeper trenches with straight sidewalls and flat bottom is obtained compared to the results of fixed-parameter DRIE shown in Fig. 3.3                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

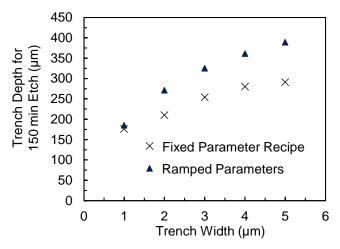

| Fig. 3.7. Comparison of DRIE results of 1-5 µm wide trenches using the fixed-parameter and the ramped-parameter process for 150 min: for all feature sizes, deeper depth is obtained by using the ramped-parameter DRIE process.                                                                                                                                                                                                                                                        |

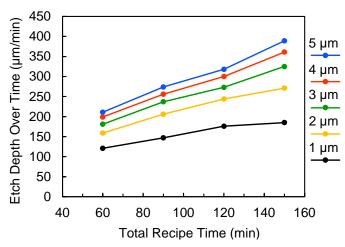

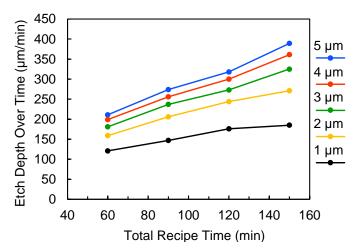

| Fig. 3.8. Trench depth obtained at different time intervals for 1-5 µm wide trenches using the ramped-parameter DRIE process. Time-lapse depth measurements are made at 60 min, 90 min, 120 min and 150 min of DRIE to monitor the progress of the etch rate and aspect-ratio dependency.                                                                                                                                                                                               |

| Fig. 3.9. Trench depth obtained at different time intervals for 1-5 $\mu$ m wide trenches using the ramped-parameter DRIE process. Time-lapse depth measurements are made at 60 min, 90 min, 120 min and 150 min to monitor the progress of the etch rate and aspect-ratio dependency 73                                                                                                                                                                                                |

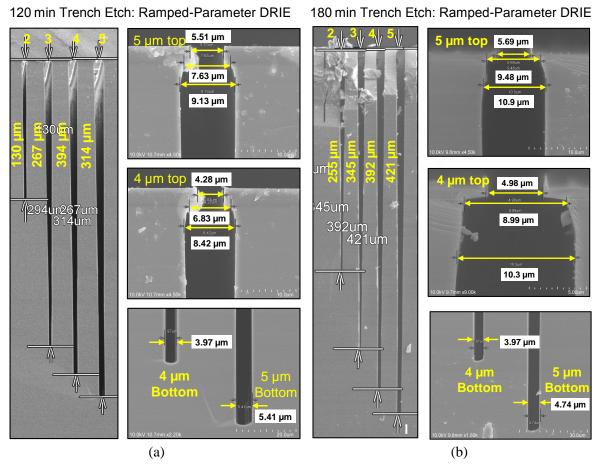

| Fig. 3.10. 2-5 $\mu$ m wide trenches etched for (a)120 min and (b) 180 min with ramped-parameter DRIE process. Final etch profiles are shown by highlighting the trench openings at both the bottom of the trenches and underneath the oxide mask near the top. The trench bottoms are relatively flat, and the widths are almost the same as the original feature sizes defined on the mask. The upper half of the trench is tapered slightly due to DRIE undercut and lateral etch 74 |

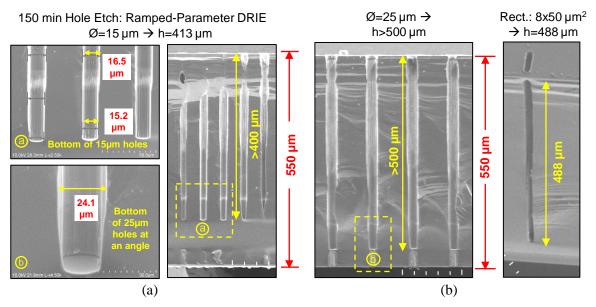

| Fig. 3.11. (a) Holes and (b) small in-plane aspect-ratio rectangles at $8 \mu m \times 50 \mu m$ are etched for 150 min with the ramped-parameter DRIE recipe                                                                                                                                                                                                                                                                                                                           |

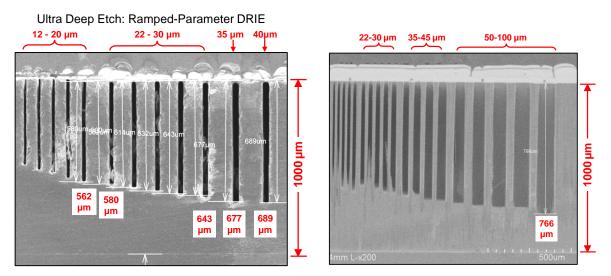

| Fig. 3.12. Ultra-deep DRIE of $12-100\mu m$ wide trenches in 1 mm thick silicon wafer by the ramped-parameter recipe for >130 min. The sidewall slopes are slightly positive (89.50 °<0<90 ° for relatively narrow trenches (1 - 10 $\mu m$ wide as shown in Fig. 6, and 10-25 $\mu m$ wide), and slightly negative (0 > 90 °) for wider trenches (> 25 - 100 $\mu m$ ).                                                                                                                |

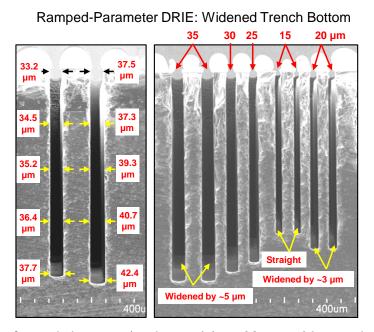

| Fig. 3.13. Widening of trench bottoms is observed in $> 20\mu m$ wide trenches caused by the ramped DRIE process parameters (increase biased power, longer etch duration, and lower etch step chamber pressure), while 15 $\mu m$ features has very straight sidewalls                                                                                                                                                                                                                  |

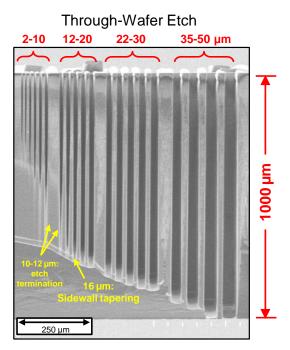

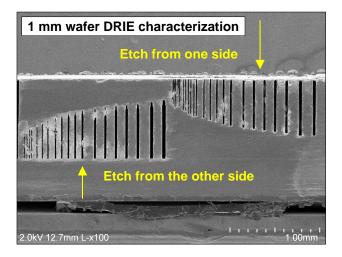

| Fig. 3.14. Ultra-deep DRIE in 1 mm thick <100> silicon substrate using 240 min of continuously-ramped DRIE process. This recipe produces very straight sidewalls for trenches wider than 18 $\mu$ m. However, although final boost power is increased from 140 W in Table 2 to 180 W, and final etch step chamber pressure is reduced to 10mTorr from of 15 mTorr, trenches smaller than ~16 $\mu$ m wide are tapered and converged before the end of the 4 hour DRIE 79                |

| Fig. 3.15. Ultra-deep ultra-high aspect-ratio DRIE in 1 mm thick <111> silicon substrate. Trench depth of >900 $\mu$ m with width <20 $\mu$ m (AR > 40:1), and trench depth of >700 $\mu$ m with width ~10 $\mu$ m (AR>70:1) are obtained. After the 5 hour DRIE process, 1.5 $\mu$ m oxide remains. Vertical sidewall profile and flat trench bottoms are achieved and no etch termination is observed 80                                                                              |

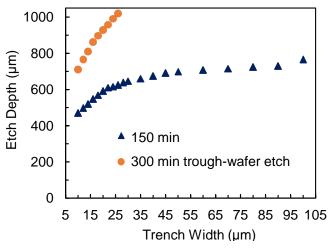

| Fig. 3.16 Etch depth of ultra-deep ultra-high aspect-ratio DRIE for >130 min with the ramped-parameter recipe, compared to 300 min (5 hour) through wafer etch results from Fig. 3.15 81                                                                                                                                                                                                                                                                                                |

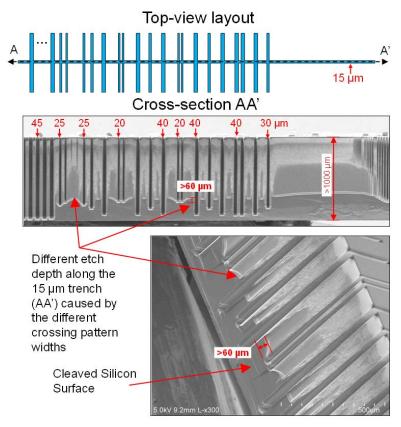

| Fig. 3.17. Effect of crossing patterns on the etch depth: one 15 $\mu$ m wide trench with crossing trenches of different widths from 20 - 45 $\mu$ m is etched to a depth > 700 $\mu$ m. The 15 $\mu$ m trench is etched more than 60 $\mu$ m deeper near the 20 $\mu$ m crossing trenches compared to the one close to the 40 $\mu$ m crossing trenches and both are etched deeper than where no crossing is present 82                                                                          |

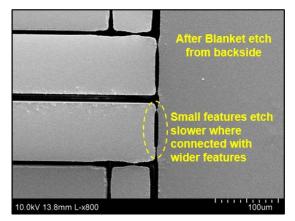

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.18. Etch profile at junctions of narrow and wide features: Bottom of deep trenches are revealed by thinning down the wafer from backside: etch depth on the narrow side near the junctions are greatly reduced.                                                                                                                                                                                                                                                                            |

| Fig. 4.1. Uniform-gap hair accelerometer: ultra-high aspect-ratio DRIE of trenches defines the device height, vertical hair spring length and isolation between neighboring electrodes 90                                                                                                                                                                                                                                                                                                         |

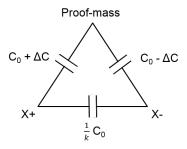

| Fig. 4.2. Capacitive feedthrough due to the maximum separation gaps that can be realized by the SOG process in Fig. 4.4.                                                                                                                                                                                                                                                                                                                                                                          |

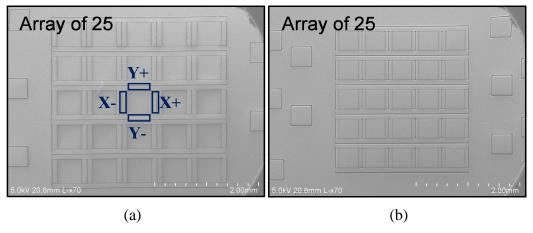

| Fig. 4.3. SEM of 25 (5×5) arrays of hair accelerometers: (a) Proof-mass footprint (a×b) equals $500\times500~\mu\text{m}^2$ ; (b) Proof-mass footprint (a×b) equals $400\times400~\mu\text{m}^2$                                                                                                                                                                                                                                                                                                  |

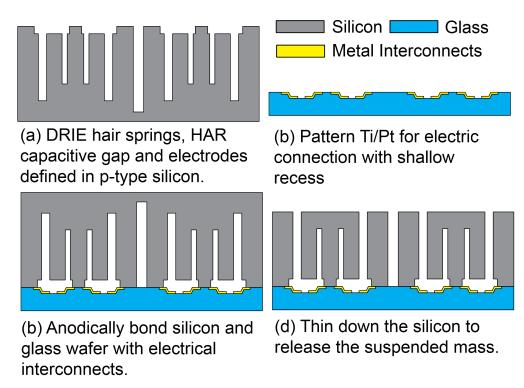

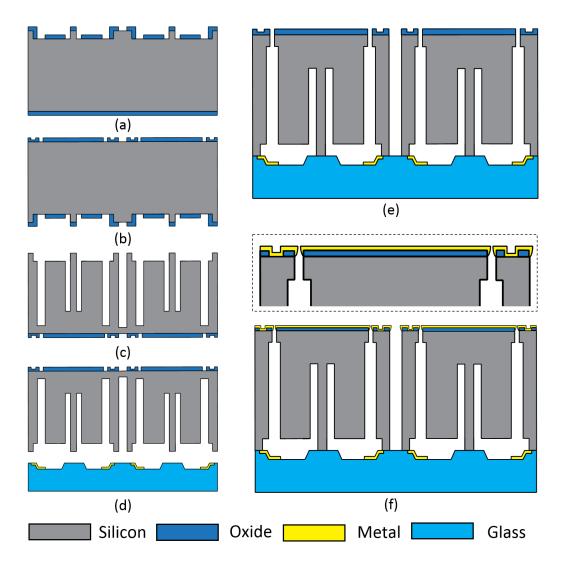

| Fig. 4.4. Silicon-on-Glass (SOG) fabrication process for fabricating uniform gap hair accelerometer. The sensing gap g <sub>0</sub> , mass height H and spring length L are defined by a single DRIE step                                                                                                                                                                                                                                                                                         |

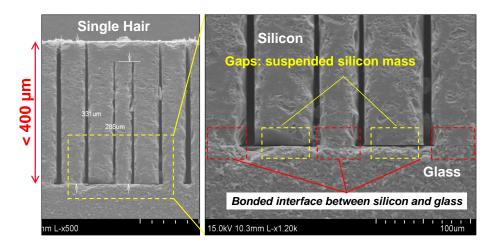

| Fig. 4.5. Bonded silicon-glass interface: SEM of single hair structure cross-section and close-up of the silicon-glass interface.                                                                                                                                                                                                                                                                                                                                                                 |

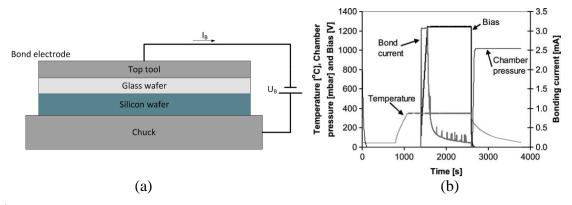

| Fig. 4.6. Anodic bonding principle and plot of bonding parameters vs. time for a typical anodic bonding process                                                                                                                                                                                                                                                                                                                                                                                   |

| Fig. 4.7. Bonded silicon-glass interface: SEM of single hair structure cross-section and close-up of the silicon-glass interface.                                                                                                                                                                                                                                                                                                                                                                 |

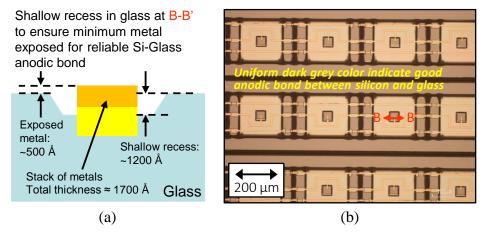

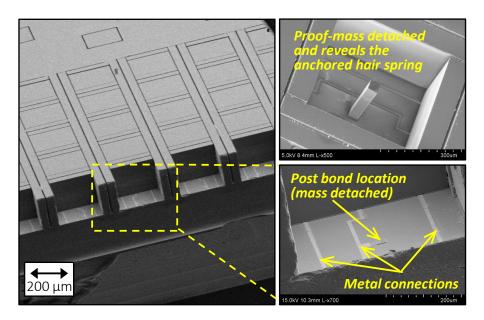

| Fig. 4.8. Close-up of an array of hair accelerometer structures and their cross-section: vertical silicon hair spring is anodically bonded to the glass substrate and makes electrical contact with the metal fingers patterned on the glass substrate                                                                                                                                                                                                                                            |

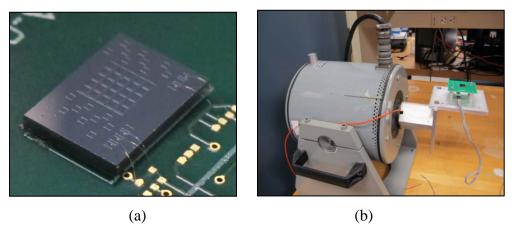

| Fig. 4.9. Fabricated sensor chip mounted on PCB and then mounted on shaker table for electromechanical testing                                                                                                                                                                                                                                                                                                                                                                                    |

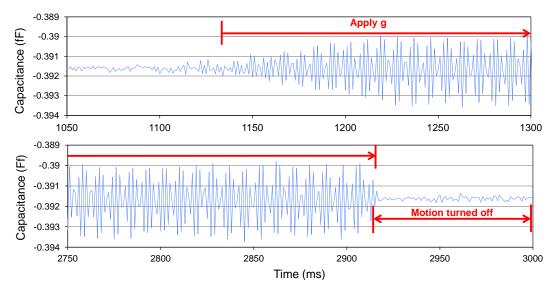

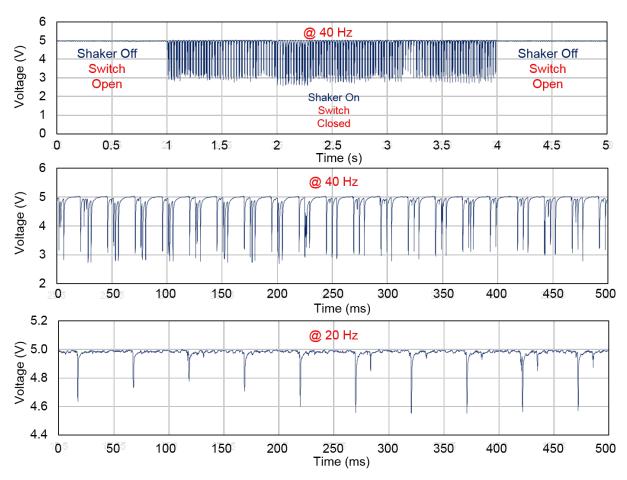

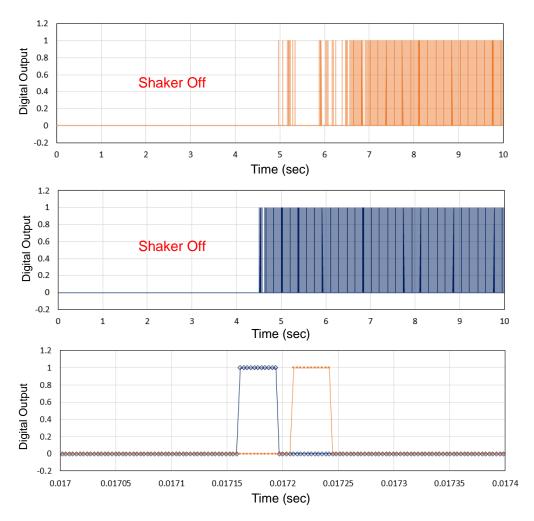

| Fig. 4.10. Time domain capacitance change when shaker motion is turn on and off                                                                                                                                                                                                                                                                                                                                                                                                                   |

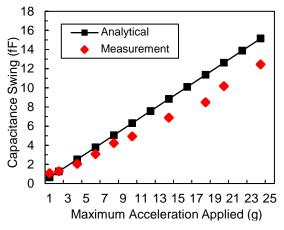

| Fig. 4.11. Differential capacitance changes in X-axis of an array of 25 hair accelerometers connected in parallel when subjected to peak acceleration from 1 g to 24 g on Unholtz-Dickie shaker table. Each hair accelerometer in the array is composed of: 1) a 380 $\mu$ m tall proof-mass that has footprint at $500 \times 500 \ \mu\text{m}^2$ ; 2) a ~300 $\mu$ m long spring that has a cross-sectional area of $50 \times 50 \ \mu\text{m}^2$ , and 3) nominal sensing gaps at 5 $\mu$ m. |

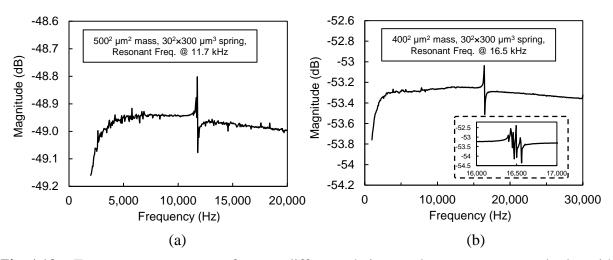

| Fig. 4.12. Frequency response of two different hair accelerometer arrays both with $30^2 \times 300 \mu\text{m}^3$ hair springs: (a) Proof-mass footprint (a × b) equals $500 \times 500 \mu\text{m}^2$ ; (b) Proof-mass footprint (a × b) equals $400 \times 400 \mu\text{m}^2$                                                                                                                                                                                                                  |

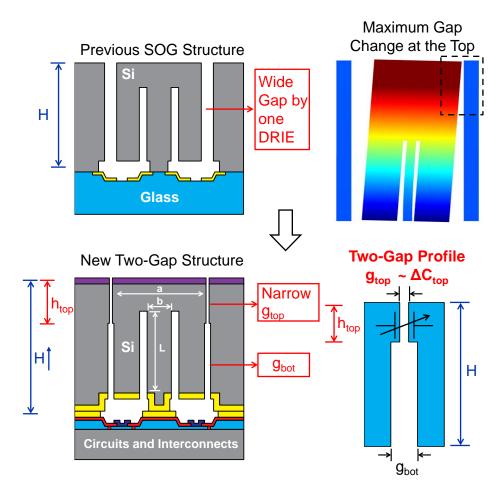

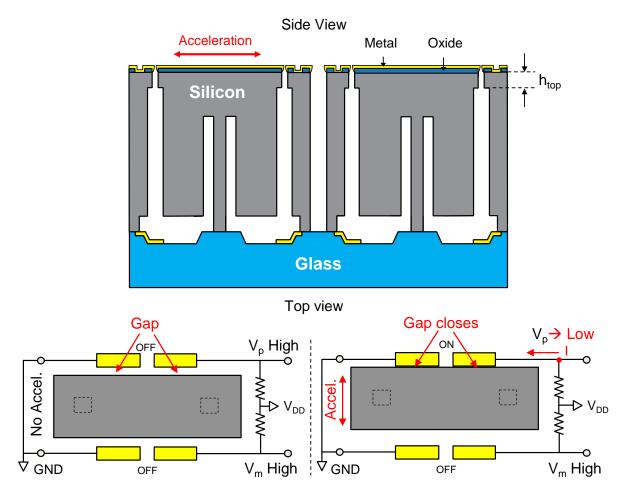

| Fig. 5.1. 2-gap structure compared with SOG structure with uniform capacitive gap: Deflection of the proof mass under applied force is maximum at the top where the top gap $g_0$ ( $g_{top}$ / $h_{top}$ ) contributes to $\Delta C_{top}$ .                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

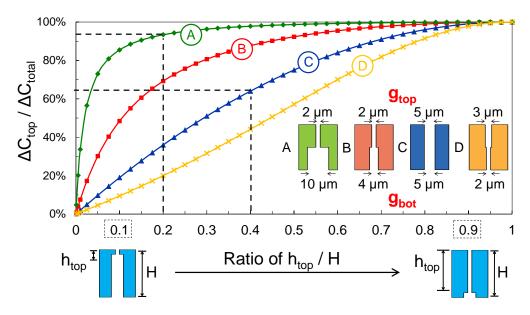

| Fig. 5.2. $\Delta C_{top}$ contributes to most of total $\Delta C_{total}$ .                                                                                                                                                                                                                                                                   |

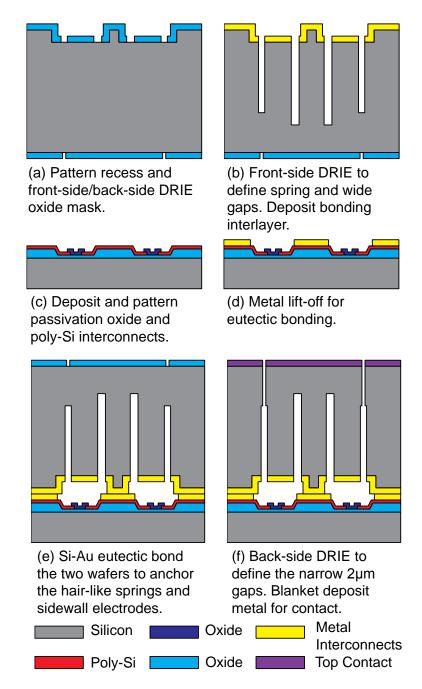

| Fig. 5.3. Two-gap CMOS compatible dry-release all-silicon fabrication process                                                                                                                                                                                                                                                                  |

| Fig. 5.4. DRIE characterization to determine the gap dimensions and etch depth to ensure the release of the capacitive hair accelerometer                                                                                                                                                                                                      |

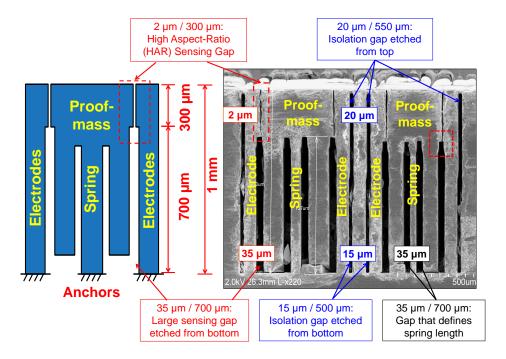

| Fig. 5.5. SEM cross sections of fabricated 2-gap devices: two neighboring 1 mm tall devices with $g_{top}$ = 2 $\mu$ m extending 300 $\mu$ m and spring L = 700 $\mu$ m                                                                                                                                                                        |

| Fig. 5.6. Junction of g <sub>top</sub> and g <sub>bot</sub> .                                                                                                                                                                                                                                                                                  |

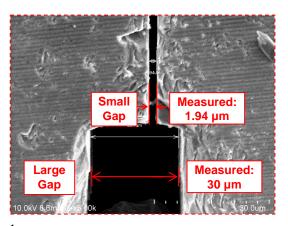

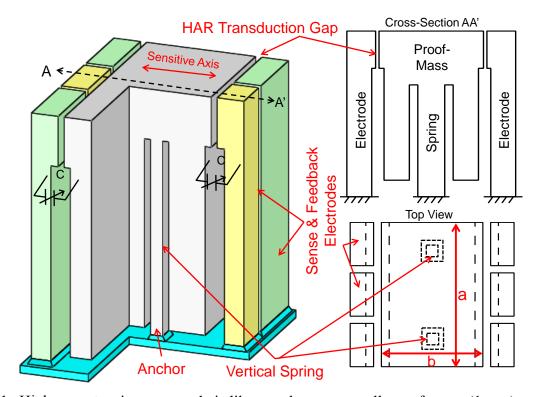

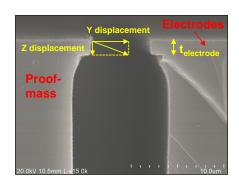

| Fig. 6.1. High aspect-ratio two-gap hair-like accelerometer: tall proof-mass (1 mm), vertical spring, sense/feedback electrodes, and high aspect-ratio capacitive transduction gaps                                                                                                                                                            |

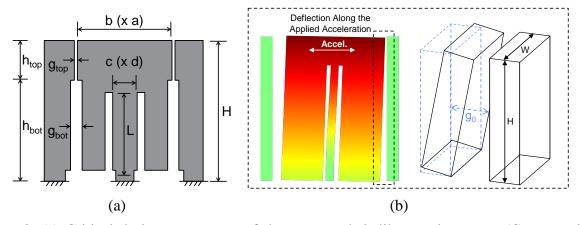

| Fig. 6.2. (a) Critical design parameters of the two-gap hair-like accelerometer (Cross-section AA in Figure 6.1); (b) Deflection profile of the hair structure and sense gap profile of the inverted pendulum design with applied acceleration.                                                                                                |

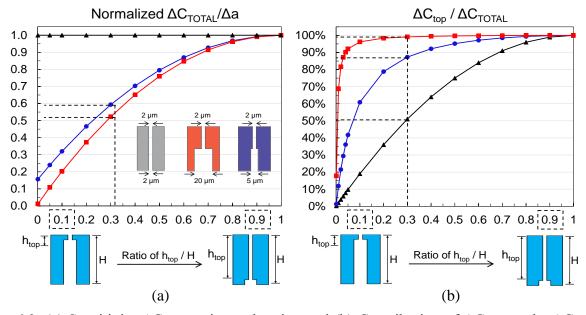

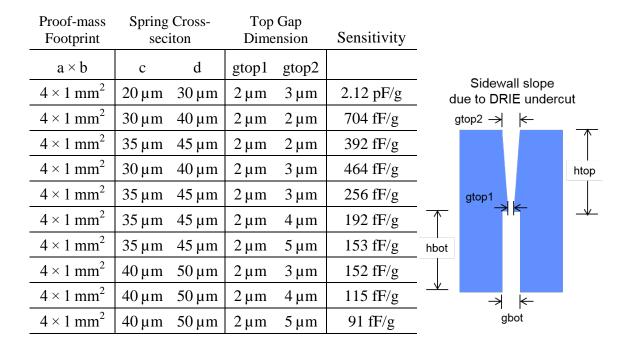

| Fig. 6.3. (a) Sensitivity $\Delta C$ per unit acceleration and (b) Contribution of $\Delta C$ top to the $\Delta C$ total for different gap profiles ( $g_{top}/h_{top}$ and $g_{bot}/h_{bot}$ ).                                                                                                                                              |

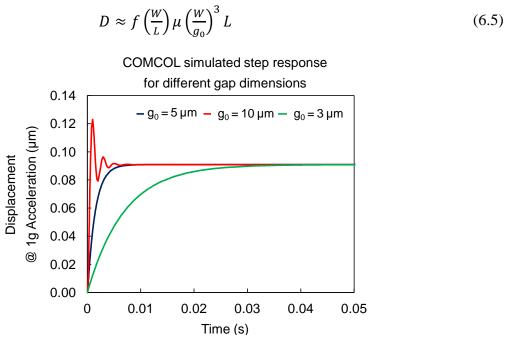

| Fig. 6.4. COMSOL solid mechanics model including squeeze film damping effect for different sensing gap dimensions of 3 $\mu$ m, 5 $\mu$ m and 10 $\mu$ m at 100 mTorr                                                                                                                                                                          |

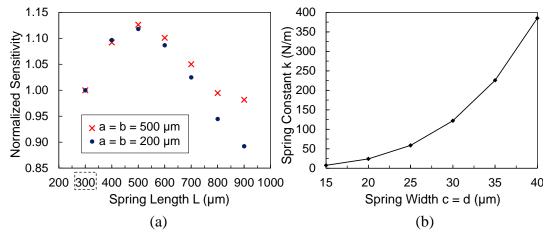

| Fig. 6.5. (a) Optimize spring length: $L\approx 500\text{-}600\mu\text{m}$ gives the maximum sensitivity for two different proof-mass sizes; The sensitivity is normalized to $L=300\mu\text{m}$ ; (b) Setting $L=600\mu\text{m}$ and reducing the spring width (c and d) to $<25\mu\text{m}$ lower the spring constant to $<50\text{N/m}$ 116 |

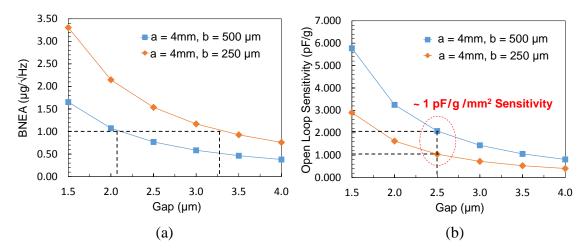

| Fig. 6.6. COMSOL simulation to optimize the capacitive gap size for minimizing BNEA and maximizing capacitive sensitivity (S) for a sensor footprint of 1 mm <sup>2</sup> and 2 mm <sup>2</sup>                                                                                                                                                |

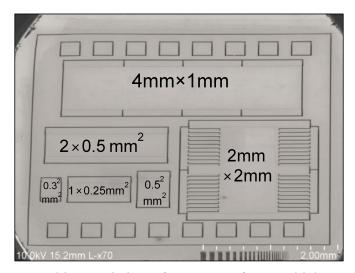

| Fig. 6.7. SEM of a sensor chip consisting of an array of 1mm thick high sensitivity and low noise capacitive hair accelerometers with various design parameters                                                                                                                                                                                |

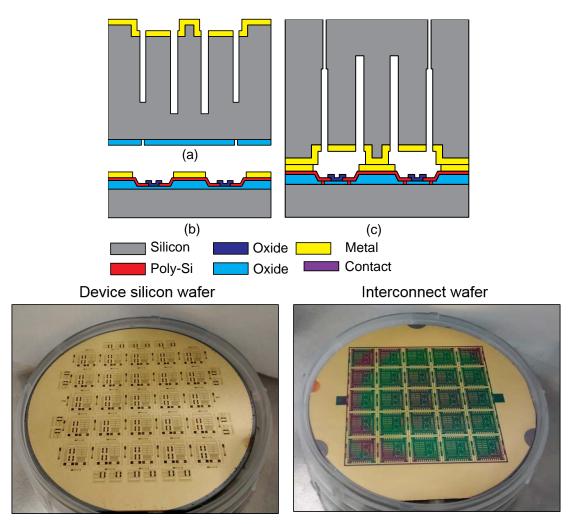

| Fig. 6.8. CMOS-Compatible two-gap fabrication process: (a) MEMS devices wafer patterned with the spring, mass, narrow and wide gaps; (b) Interconnect wafer patterned with electrical connections and eutectic bonding metals; (c) Released bonded wafer                                                                                       |

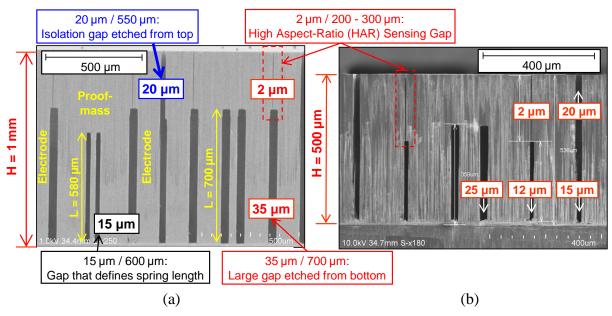

| Fig. 6.9. SEM cross-section of fabricated 3D vertical hair-like accelerometers by the two-gap process: (a) Two 1-mm tall devices side-by-side. The left device has $L=580\mu m$ and the right one has $L=700\mu m$ ; (b) Cross-section of a 500- $\mu m$ tall device.                                                                          |

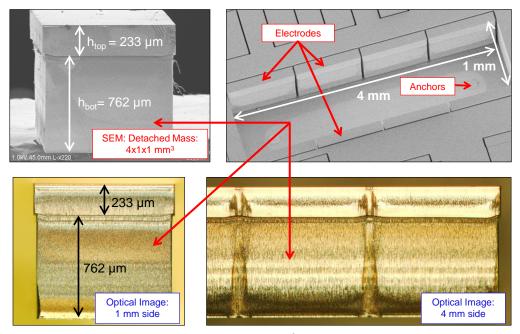

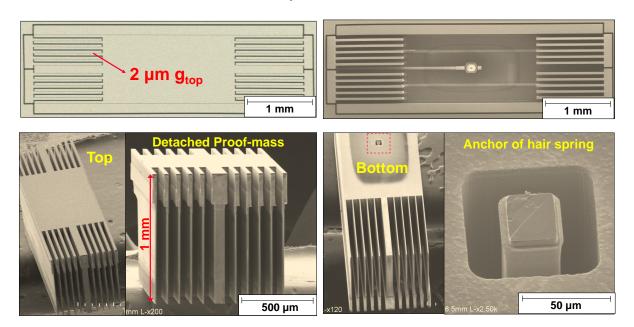

| Fig. 6.10. Fully released accelerometer (4×1×1 mm <sup>3</sup> proof-mass): optical and SEM images of detached proof-mass sidewalls formed by DRIE. The device is fully released when gtop is etched                                                                                                                                           |

| through and joined with gbot. The two-part gaps along the height are htop = $233 \mu m$ DRIE-ed from the top and hbot = $762 \mu m$ DRIE-ed from the other side                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 6.11. HAR transduction gap profile with gap dimension measured along htop for 2 $\mu$ m initial capacitive transduction gap defined on the mask                                                                                                                                                                                                        |

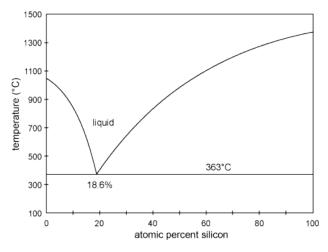

| Fig. 6.12. Silicon-gold phase diagram.                                                                                                                                                                                                                                                                                                                      |

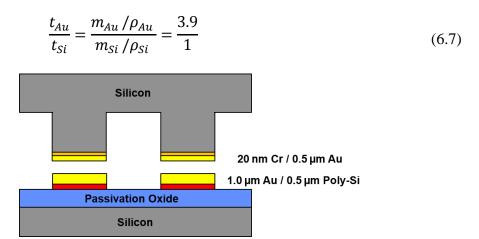

| Fig. 6.13. Patterned eutectic bonding stack in the fabrication of capacitive hair accelerometer. 124                                                                                                                                                                                                                                                        |

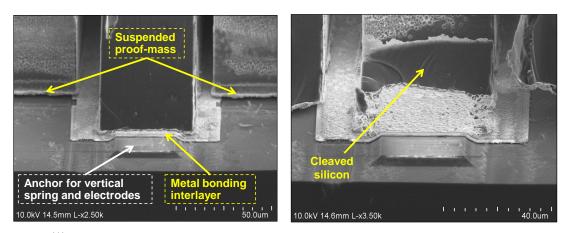

| Fig. 6.14. Silicon gold eutectic bonding sites showing recess in the bottom silicon substrate and the suspended structure from device wafer                                                                                                                                                                                                                 |

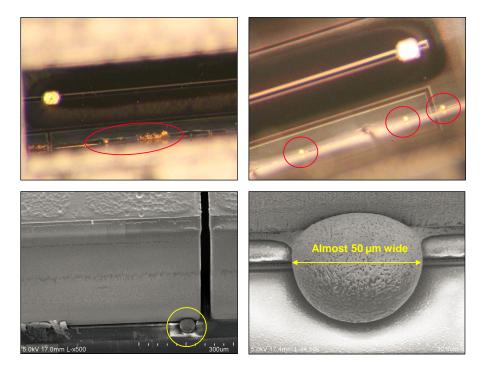

| Fig. 6.15. Au-Si alloy squeezed out during bonding due to high contact force to ensure atomic contact of the two wafers: they can be seen on almost all the devices since the electrodes have larger bonding area (more Au-Si alloy formed).                                                                                                                |

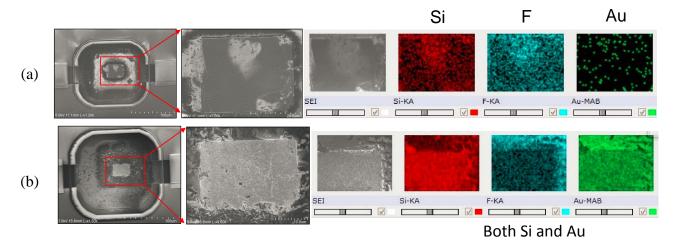

| Fig. 6.16. EDX analysis of silicon-gold eutectic bonding interface                                                                                                                                                                                                                                                                                          |

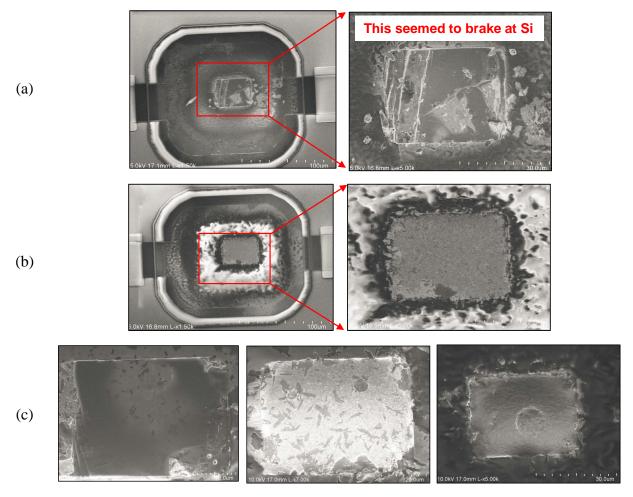

| Fig. 6.17. (a) Silicon peeled off from the hair spring indicates that the bonding strength is higher than the silicon fracture strength; (b) The hair spring broke off at the alloyed interlayer. (c) Other bonding locations.                                                                                                                              |

| Fig. 6.18. Hair spring composed of different width sections are simulated to study the effectiveness of narrowing the spring: narrowing the spring width from $30\mu m$ to $20\mu m$ for a length of $200\mu m$ out of the entire $600\mu m$ spring length from the anchor point increases the displacement sensitivity by more than three times (> $3x$ ). |

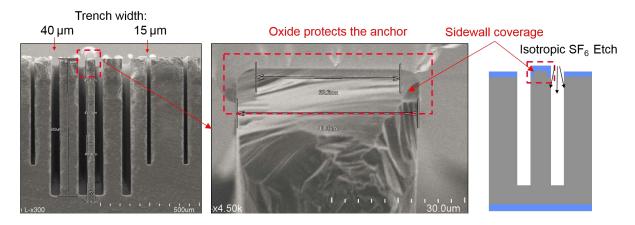

| Fig. 6.19. Spring width after 130 min DRIE on 1 mm thick silicon wafer: oxide patterned around the spring anchor protect it from being etched during isotropic SF <sub>6</sub> etch                                                                                                                                                                         |

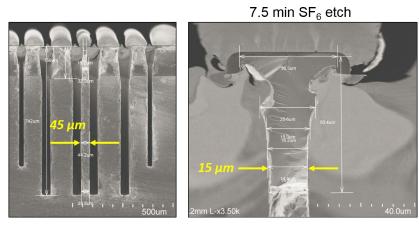

| Fig. 6.20. Spring profile after 7.5 min isotropic SF <sub>6</sub> etch experimented on 1 mm thick silicon wafer (trenches are DRIE-ed for 130 min).                                                                                                                                                                                                         |

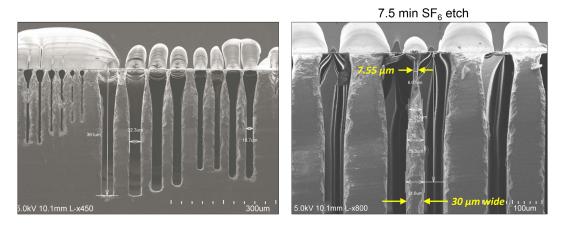

| Fig. 6.21. Spring profile after 7.5 min isotropic $SF_6$ etch: experimented on 500 $\mu$ m thick wafer (trenches are DRIE-ed for 70 min). Different openings result in different etch depth                                                                                                                                                                 |

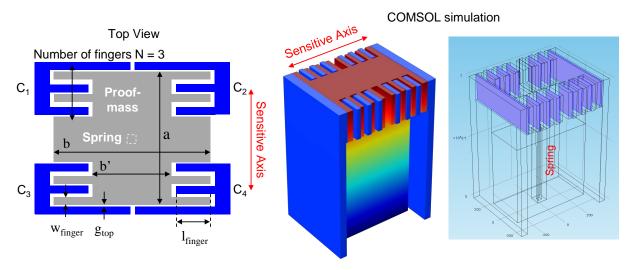

| Fig. 6.22. Increasing the capacitive sensitivity per unit footprint by optimization of the gap dimension $g_{top}$ , and interdigitated electrode width $w_{finger}$ and length $l_{finger}$                                                                                                                                                                |

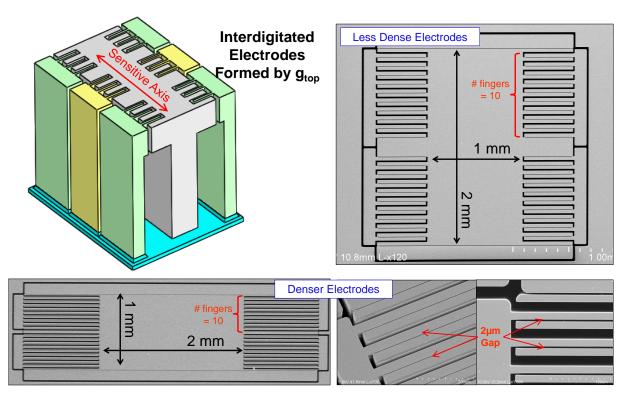

| Fig. 6.23. Hair accelerometer with interdigitated electrodes form by the top gap: schematic and two devices with different electrodes density.                                                                                                                                                                                                              |

| Fig. 6.24. Interdigitated devices successfully released                                                                                                                                                                                                                                                                                                     |

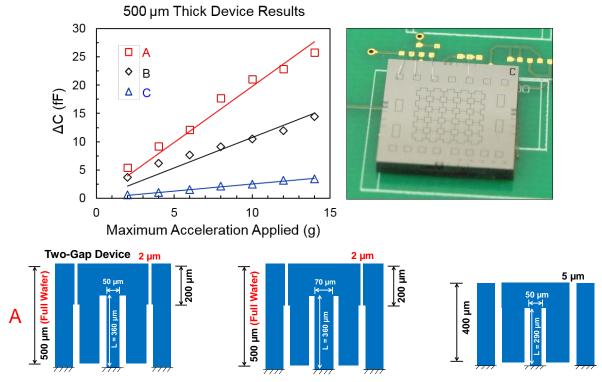

| Fig. 6.25. Vibration table electromechanical testing of the second-generation two-gap device compared to the SOG devices, showing an improvement of 8x in capacitive sensitivity 136                                                                                                                                                                        |

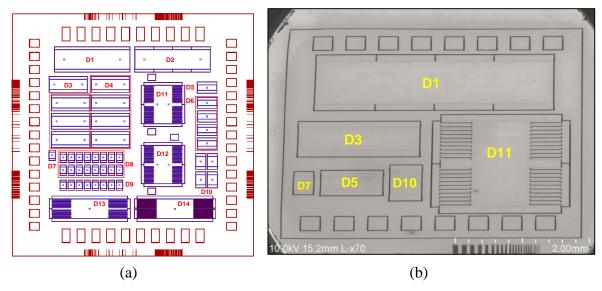

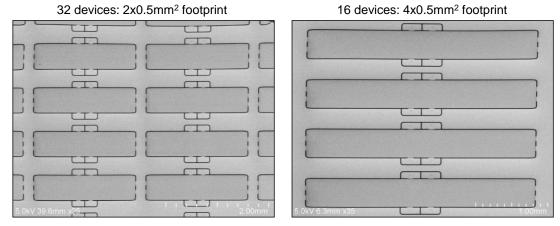

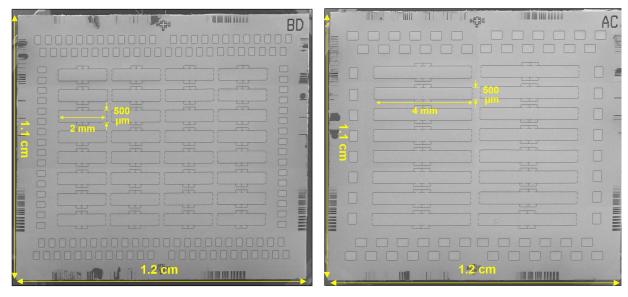

| Fig. 6.26. Layout of 1mm thick devices: (a) Single chip layout including multiple devices with different designs; (b) SEM of another fabricated chip highlighting the single devices                                                                                                                                                                        |

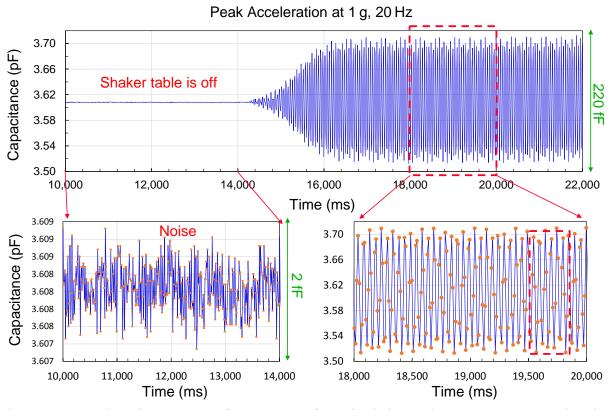

| Fig. 6.27. Time-domain response of a $4\times1$ mm2 footprint hair accelerometer to 1 g acceleration at 20 Hz. The capacitance change ramped up after shaker table is turned on. At 90.0 Hz sampling frequency, the noise envelope is less than 1.5 fF                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

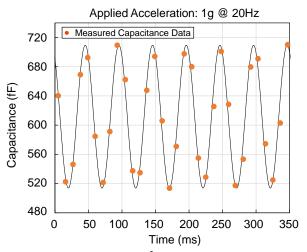

| Fig. 6.28. Time-domain response of a 4x1 mm <sup>2</sup> footprint hair accelerometer to 1 g acceleration at 20 Hz and zoom-in on the response in Fig. 6.25. It is fit with a 20 Hz sine wave                                                                                                                                                                           |

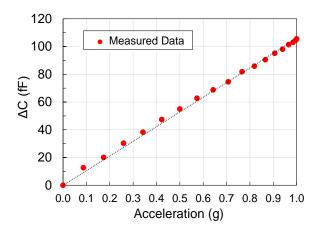

| Fig. 6.29. Measured $\Delta C$ vs. acceleration for a $4 \times 1 \text{ mm}^2$ footprint hair accelerometer. The acceleration ranges from 0 g to 1 g                                                                                                                                                                                                                   |

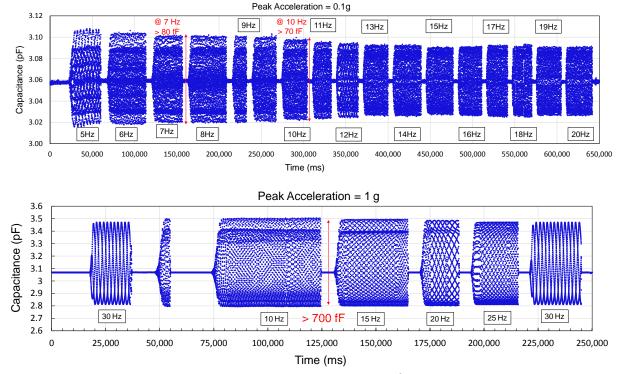

| Fig. 6.30. Measured $\Delta C$ in time domain for another $4 \times 1 \text{ mm}^2$ footprint hair accelerometer over a frequency range                                                                                                                                                                                                                                 |

| Fig. 6.31. DIRE undercut and etch depth non-uniformity across a 4-inch wafer and between different runs cause the critical sensing gap dimensions and spring cross-sections to vary from the designed values, thus resulting in variation in the capacitive sensitivity                                                                                                 |

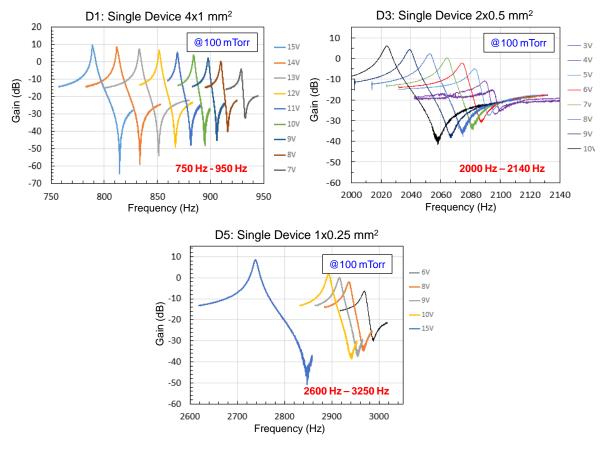

| Fig. 6.32. Single devices with different resonant frequencies fres around:1 kHz (Device D1), 2 kHz (Device D3), and 3 kHz (Device D5) at 100 mTorr                                                                                                                                                                                                                      |

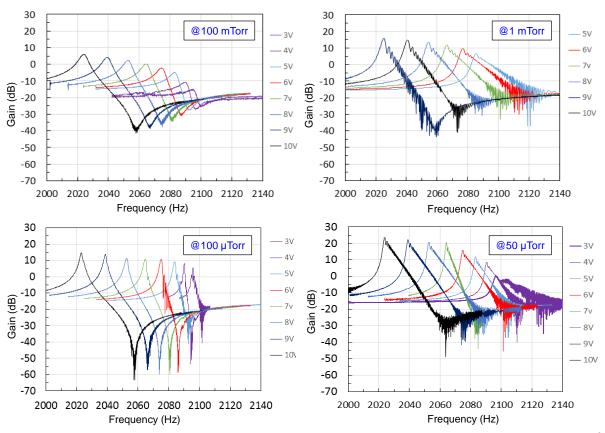

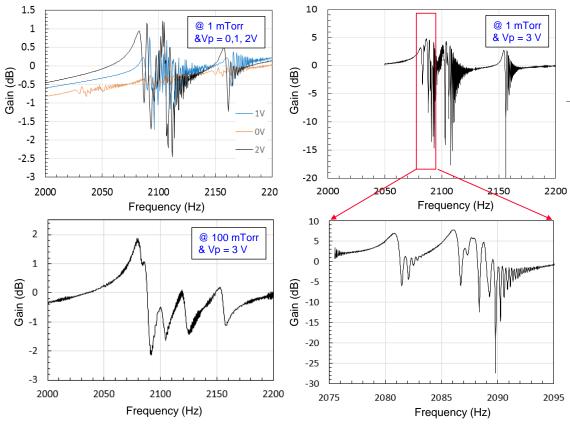

| Fig. 6.33. Resonance testing of device D3: single device with footprint $a \times b = 2000 \times 500 \mu\text{m}^2$ . The resonant frequency $f_{res}$ is measured around 2.1 kHz. The resonant responses are measured at different vacuum levels with different bias voltage applied.                                                                                 |

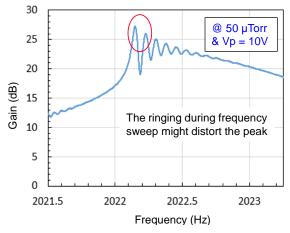

| Fig. 6.34. Zoom-in on resonant peak of device D3 single device with footprint $a \times b = 2 \times 0.500 \text{ mm}^2$ . The ringing during the frequency sweep may distort the peak. At 50 $\mu$ Torr, it is zoomed-in near the resonant peak with span = 2 Hz, $f_{center} = 2.022146 \text{ kHz}$ and $\Delta f - 3dB = < 40 \text{ mHz}$ , which gives a Q > 50k. |

| Fig. 6.35. Zoom-in the resonant response of an array of seven D3 in parallel (D4 in Figure 6.24). Multiple peaks are observed. At 100 mTorr, we can track the resonant peak shifts between the multiple devices in the array.                                                                                                                                           |

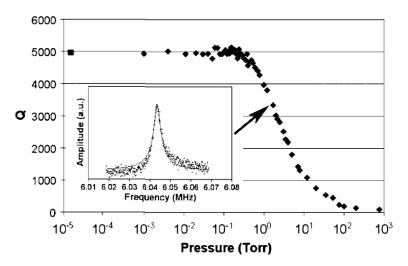

| Fig. 6.36. Quality factor vs. pressure curve [10]                                                                                                                                                                                                                                                                                                                       |

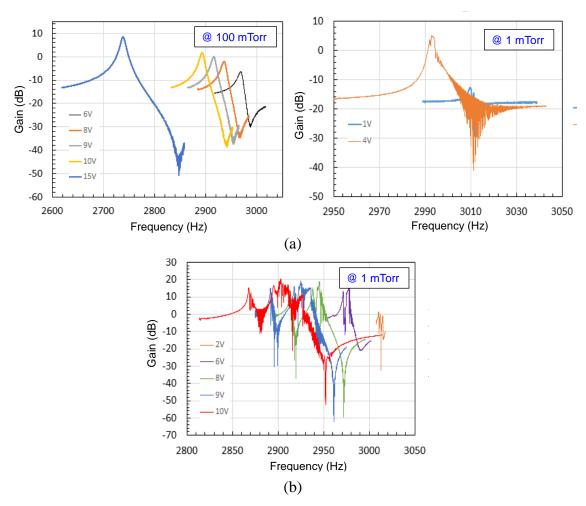

| Fig. 6.37. Comparison between the resonant responses around 3 kHz of (a) D5: single $1000 \times 250 \mu\text{m}^2$ and (b) an array of four D5 in parallel (D6 in Figure 6.24)                                                                                                                                                                                         |

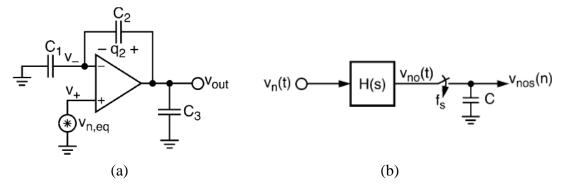

| Fig. 7.1. Simplified block diagram of various capacitive readout circuits: AC-bridge with voltage amplifier, transimpedance amplifier (TIA), and switch capacitor circuit (SC) [11]                                                                                                                                                                                     |

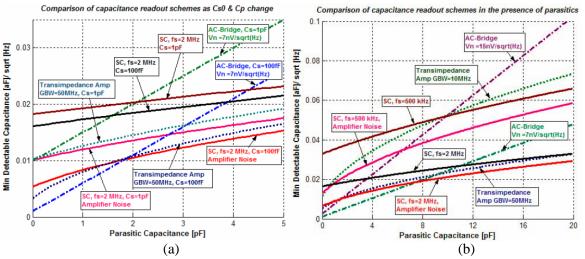

| Fig. 7.2. Minimum detectable $\Delta C_{minrms}$ for different capacitance readout schemes [11]: (a) Comparing $C_{S0}$ =100 fF and $C_{S0}$ =1 pF shows that a larger $C_{S0}$ will result in larger $\Delta C_{min.}$ ; and (b) Capacitance resolution for various readout schemes with $C_{S0}$ =250 fF                                                              |

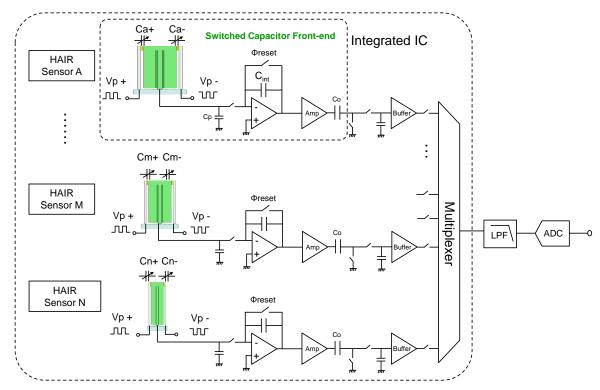

| Fig. 7.3. Hair sensor array with integrated IC block diagram: switched-capacitor front-end and multiplexing of sensor array                                                                                                                                                                                                                                             |

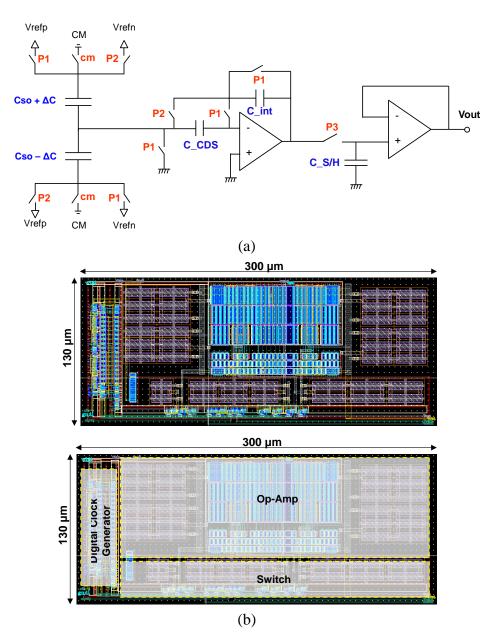

| Fig. 7.4. Switched-capacitor front-end core: (a) schematic, (b) layout including both digital and analog block.                                                                                                                                                                                                                                                         |

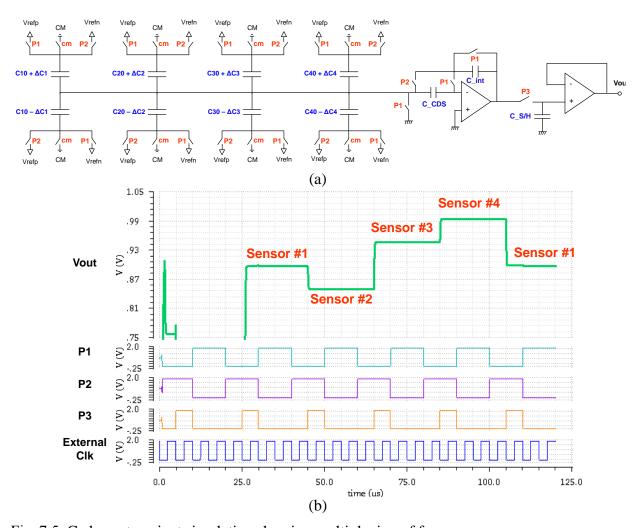

| Fig. 7.5. Cadence transient simulation showing multiplexing of four sensors                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 7.6. Calculation of equivalent noise of continuous and sampled data [12]                                                                                                                                                                                                                                                                                                                                                                  |

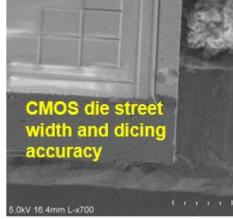

| Fig. 7.7. CMOS chip from 180nm process: bond pads for post-CMOS processing and integration and die edge                                                                                                                                                                                                                                                                                                                                        |

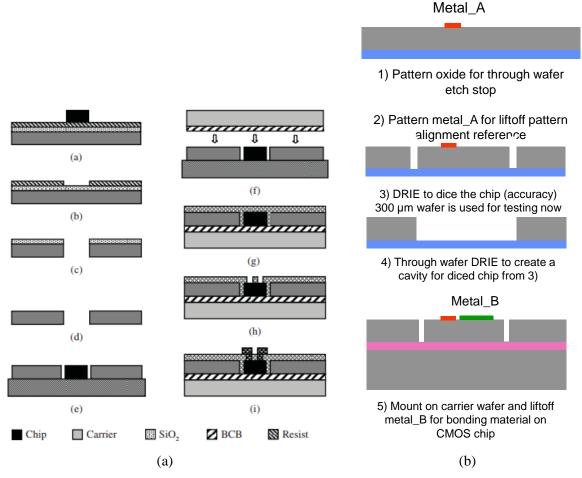

| Fig. 7.8. (a) CMOS chip and microfluidic chip self-aligned (accuracy can be within $5\mu m$ ) integration process includes placing the CMOS die in a silicon socket and patterning metal lift-off on CMOS chip for electrical connections; (b) Testing procedure to verify the alignment accuracy of process in (a): metal A represents the original patterns on CMOS chip and metal B will be lift-off when the chip is placed in the socket. |

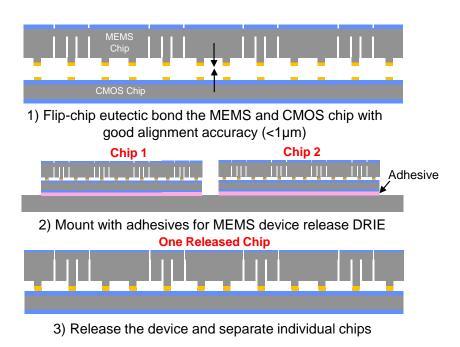

| Fig 7.9. CMOS-MEMS chip-scale integration and hair sensor array release process                                                                                                                                                                                                                                                                                                                                                                |

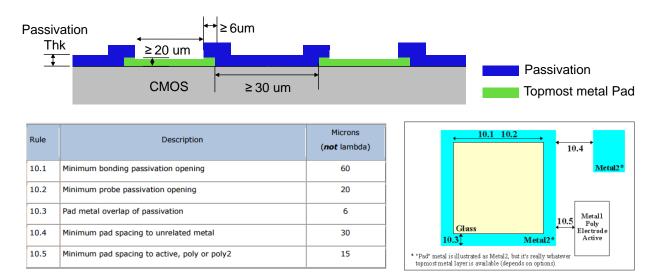

| Fig 7.10. Technology parameters of top metal and passivation layers of an IC technology 160                                                                                                                                                                                                                                                                                                                                                    |

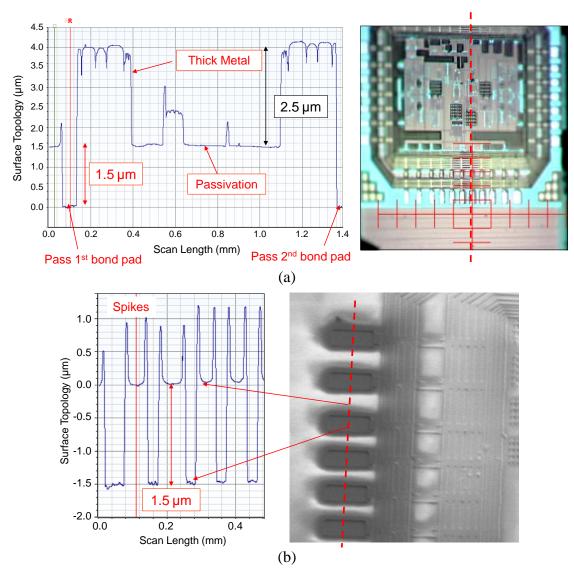

| Fig 7.11. TSMC 0.35- $\mu$ m technology (2015) surface topology scan: passivation openings are the lowest points on the chip, 1.5 $\mu$ m below the flat passivation level. Additional topology is present where UTM (ultra-thick-metal) is patterned.                                                                                                                                                                                         |

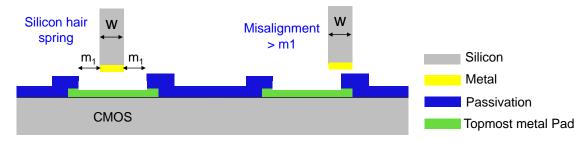

| Fig 7.12. CMOS-MEMS chip-scale integration and hair sensor array release process                                                                                                                                                                                                                                                                                                                                                               |

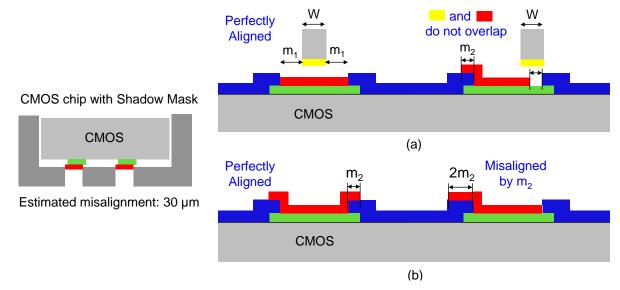

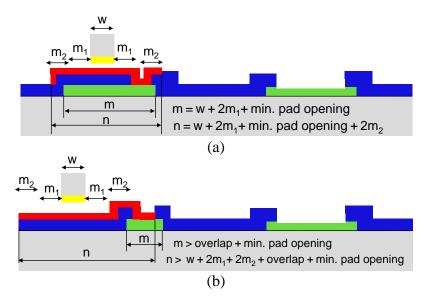

| Fig 7.13. Pattern additional metal by shadow mask. (a) Width designed the same as the bond pad opening cannot cover the bond pad with misalignment m <sub>2</sub> ; (b) The metal pattern extended by m <sub>2</sub> ; to cover the exposed bond pad                                                                                                                                                                                           |

| Fig 7.14. Minimum electrode pitch determined by technology parameters and alignment capability                                                                                                                                                                                                                                                                                                                                                 |

| Fig 7.15. Minimum hair sensor pixel pitch is determined by the electrode layout and minimum achievable electrode pitch                                                                                                                                                                                                                                                                                                                         |

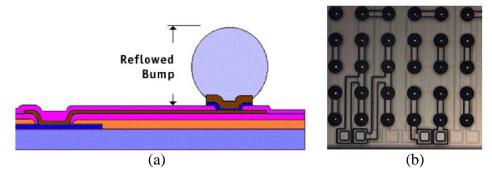

| Fig 7.16. Bond Pad Redistribution Layers (RDL): (a) Polyimide dielectric layer is deposited and patterned to open bond pads while sealing fuse openings. Conductive metal layer connects old bond pads to new pad locations. The second layer of polyimide protects the metal trace. New bond pad location is opened for solder bumps reflow. (b) Optical image of old bond pads patterned with RDL and solder bumps. [6]                      |

| Fig 7.17. Patterned metal runs over the passivation and bond to the hair springs, similar to bond pad redistribution Layers (RDL) method                                                                                                                                                                                                                                                                                                       |

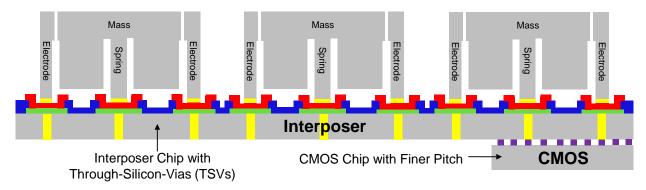

| Fig 7.18. Heterogeneous integration with intermediate interposer substrates assists mapping of MEMS devices leads to the finer-pitch IC chips                                                                                                                                                                                                                                                                                                  |

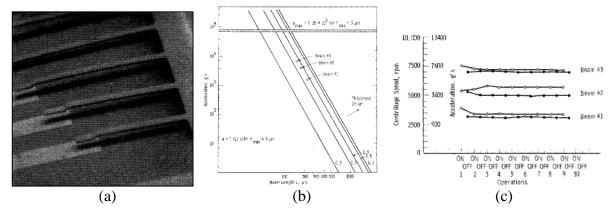

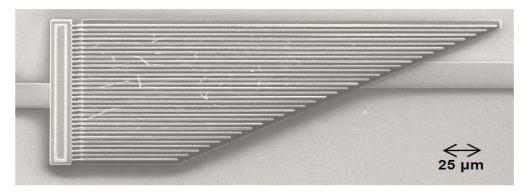

| Fig. 8.1. Microminiature threshold accelerometers [2]: (a) SEM of a seven-cantilever module; (b) Design curves; and (c) Acceleration test results of a three-beam module accelerated in a 24-cm diameter biochemical centrifuge                                                                                                                                                                                                                |

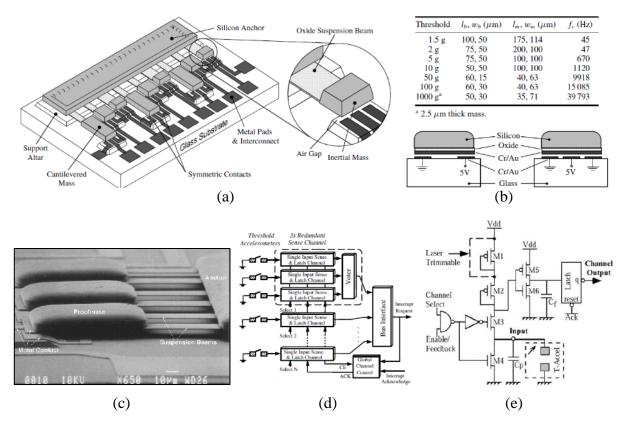

| Fig. 8.2. Microminiature threshold accelerometers [4]: (a) Illustration of threshold acceleration sensors employing redundancy (three identical sets, each set containing three different                                                                                                                                                                                                                                                      |

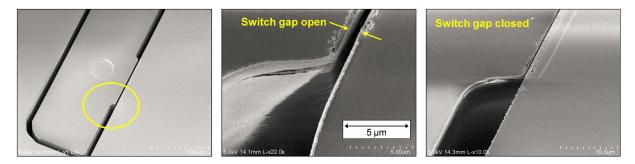

| switch: asymmetric pull down with double contact configuration vs. balanced pull down with triple contact layout with well-defined contact gap at 0.25 μm; (c) SEM micrograph of a triple array with threshold of 1.5 g with 100 μm long 25 μm wide and 0.75 μm thick oxide beams and 175 μm long, 114 μm wide and 15 μm thick inertial mass; (d) Functional circuit block diagram showing the input redundant channels and the logic voting of the majority function; (e) Schematic diagram of a sense channel        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

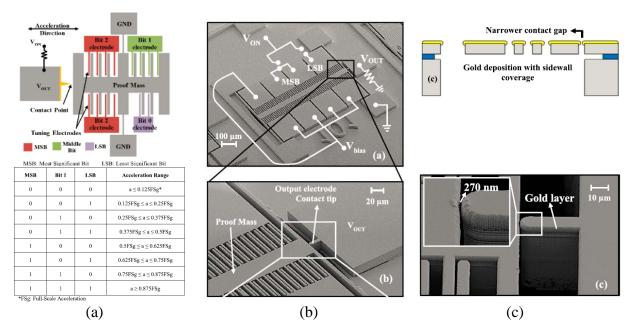

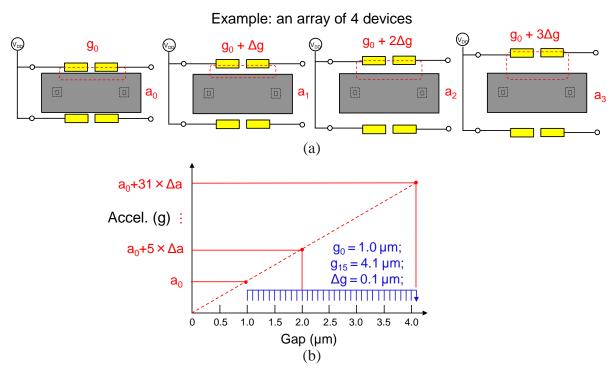

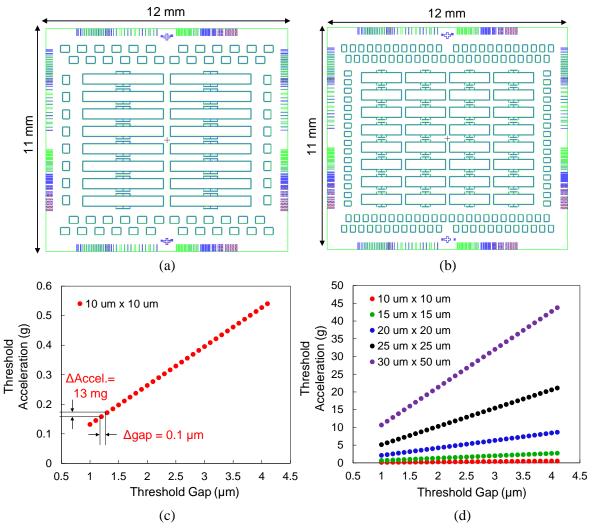

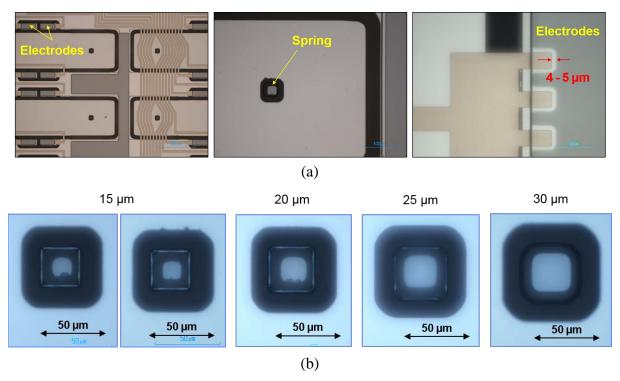

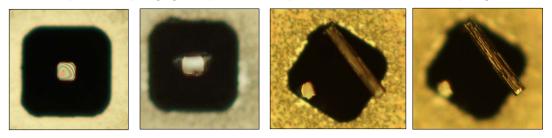

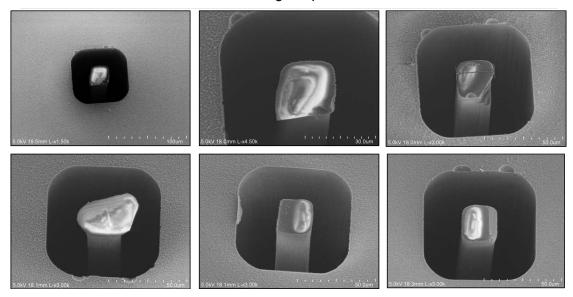

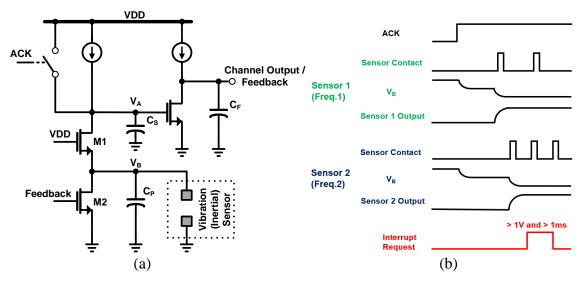

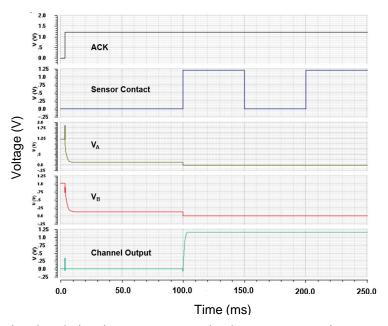

| Fig. 8.3. 3-bit digitally operated accelerometer [5]: (a) Mapping of the acceleration binary output; (b) SEM view a fabricated digital accelerometer also showing device electrical connections; (c) Zoomed-in side view of the gap between the proof mass and the output electrode showing the gap narrowed down by gold deposition.                                                                                                                                                                                  |