# Leveraging Processor Features for System Security

by

Zelalem Birhanu Aweke

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2019

Doctoral Committee:

Professor Todd M. Austin, Chair Assistant Professor Reetuparna Das Assistant Professor Jean-Baptiste Jeannin Assistant Professor Baris Can Cengiz Kasikci Zelalem Birhanu Aweke

zaweke@umich.edu

ORCID iD: 0000-0002-6899-6938

© Zelalem Birhanu Aweke 2019

To my family

# Acknowledgments

First and foremost I would like to thank my adviser, Professor Todd Austin, for his constant support and for being a great mentor. Todd has taught me a great deal about how to be a good researcher and how to effectively communicate my work.

I would also like to thank my thesis committee members, Professor Reetuparna Das, Professor Baris Can Cengiz Kasikc and Professor Jean-Baptiste Jeannin for their support and valuable feedback.

I am especially fortunate to have worked with Professor Reetuparna Das at the beginning of my graduate school career. She had been patient with me and taught me a lot about research while I transition from being a mere student to a researcher. I Would also like to thank my collaborators, Salessawi Ferede Yitbarek and Matthew Hicks, who played major roles in my first research project.

I would like to thank my friends and colleagues at the University of Michigan. Salessawi Ferede Yitbarek, Biruk Mammo, William Arthur and Patipan Prasertsom were immensely helpful while I settle in Ann Arbor. I would also like to thank Misiker Aga, Abraham Addisie, Doowon Lee, Pete Ehrett, Brendan West, Lauren Biernacki, Mark Gallagher, Colton Holoday, Taru Verma, Vidushi Goyal, Timothy Linscott, Andrew McCrabb, Hiwot Kassa, Leul Belayneh, Nishil Talati, Kidus Admassu, Abeselom Fanta and a lot more others that I havent mention here - who helped me navigate through grad school life, be it in discussing ideas, reviewing my papers or just being friends.

My stay at the University of Michigan has gone smoothly, thanks to the wonderful CSE staff. I would especially like to thank Ashley Andreae, Dawn Freysinger, Christine Boltz, Alice Melloni, Tracie Straub, Laura Pasek, Denise DuPrie, Erika Hauff, Karen Liska and Stephen Reger for their great assistance.

Finally, I would like to thank my family who has been extremely supportive and continue to support me in my endeavors, especially my parents who, despite receiving little education themselves, understood its value and did everything they could to make sure I focus on what is important to me. I am also blessed with great brothers and sisters who have always been there for me. Thank you all.

# **Table of Contents**

| Dedicat   | ion .         | ii                                                               |

|-----------|---------------|------------------------------------------------------------------|

| Acknow    | vledgmo       | ents                                                             |

| List of l | Figures       | vii                                                              |

| List of 7 | <b>Fables</b> |                                                                  |

| List of A | Algoritl      | nms                                                              |

| Abstrac   | et            |                                                                  |

| Chapte    | r1 In         | troduction                                                       |

| 1.1       | Memo          | ry Corruption Vulnerabilities                                    |

| 1.2       | Memo          | ry Corruption Exploit Mitigations                                |

| 1.3       | Contri        | butions of the Thesis                                            |

|           | 1.3.1         | Efficient Temporal Memory Safety with Pointer Authentication 5   |

|           | 1.3.2         | Efficient Software-based Fault Isolation for Embedded Devices 7  |

|           | 1.3.3         | Detecting Rowhammer Attacks with Hardware Performance Counters 8 |

| Chapte    | r2Po          | inter Authentication for Efficient Temporal Memory Safety 13     |

| 2.1       | Introd        | uction                                                           |

| 2.2       | Backg         | round                                                            |

|           | 2.2.1         | The Lock-and-key Technique                                       |

|           | 2.2.2         | ARM Pointer Authentication                                       |

|           | 2.2.3         | The Low-fat Memory Layout                                        |

| 2.3       | Pointe        | r Authentication for Temporal Safety                             |

|           | 2.3.1         | PETS with Shadow Storage (Baseline PETS)                         |

|           | 2.3.2         | Low-fat PETS                                                     |

| 2.4       | PETS          | Implementation                                                   |

|           | 2.4.1         | PETS Compiler Instrumentation                                    |

|           | 2.4.2         | Memory Allocators                                                |

|           | 2.4.3         | Support for Multithreaded Applications                           |

| 2.5       | Experi        | imental Evaluation                                               |

|                 | 2.5.1 Experimental Setup                                       | 26       |

|-----------------|----------------------------------------------------------------|----------|

|                 | 2.5.2 Runtime Overhead:                                        | 29       |

|                 | 2.5.3 Memory Overhead                                          | 29       |

|                 | 2.5.4 Comparison with other Temporal Safety Techniques         | 30       |

| 2.6             | Related Work                                                   | 32       |

|                 | 2.6.1 Temporal Safety Techniques                               | 34       |

| 2.7             | Chapter Summary                                                | 36       |

|                 |                                                                |          |

| Chapter         |                                                                | 37       |

| 3.1             | Introduction                                                   | 37       |

| 3.2             | Threat Model                                                   | 39       |

| 3.3             | <b>u</b> SFI System Architecture                               | 39       |

|                 | 3.3.1 Module Privilege Levels                                  | 40       |

|                 | 3.3.2 Memory Isolation                                         | 42       |

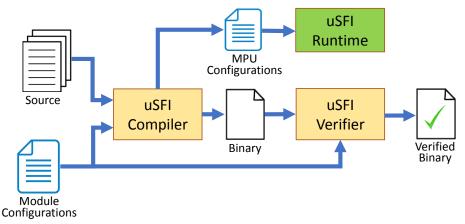

|                 | 3.3.3 uSFI Compiler and Verifier                               | 43       |

|                 | 3.3.4 uSFI Runtime                                             | 48       |

| 3.4             | <b>u</b> SFI Implementation                                    | 51       |

|                 | 3.4.1 MPU Configuration                                        | 51       |

|                 | 3.4.2 uSFI Compiler and Verifier                               | 52       |

|                 | 3.4.3 uSFI Runtime                                             | 53       |

| 3.5             | Experimental Evaluation                                        | 54       |

|                 | 3.5.1 Code Size Overhead                                       | 55       |

|                 | 3.5.2 Performance Overhead                                     | 56       |

|                 | 3.5.3 Case Study 1: Step Analysis                              | 57       |

|                 | 3.5.4 Case Study 2: HTTPS File Download                        | 58       |

|                 | 3.5.5 Trusted Code Size                                        | 59       |

| 3.6             | Related Work                                                   | 60       |

|                 | 3.6.1 Software-based Fault Isolation                           | 60       |

|                 | 3.6.2 Sandboxing in Embedded Devices                           | 60       |

| 3.7             | Chapter Summary                                                | 63       |

|                 |                                                                |          |

| -               | 24 Detecting Rowhammer Attacks with Hardware Performance Coun- | 64       |

| <b>ters</b> 4.1 |                                                                | 64<br>64 |

|                 | Introduction                                                   | 64<br>65 |

| 4.2             | Breaking Current Mitigation Techniques                         |          |

|                 | 4.2.1 Rowhammering under a Double Refresh Rate                 | 66       |

| 1.2             | 4.2.2 Rowhammering without the CLFLUSH instruction             | 67       |

| 4.3             | Software-Based Rowhammer Detection and                         |          |

|                 | Protection                                                     | 72       |

|                 | 4.3.1 Detecting Rowhammer Attacks                              | 72       |

|                 | 4.3.2 Protecting Potential Rowhammer Victims                   | 73       |

|                 | 4.3.3 ANVIL: A Linux-Based Rowhammer Protection Mechanism      | 74       |

| 4.4             | Experimental Evaluation                                        | 78       |

|                 | 4.4.1 Benchmark Applications                                   | 78       |

|                 | 4.4.2 Rowhammer Detection Characteristics                      | 78       |

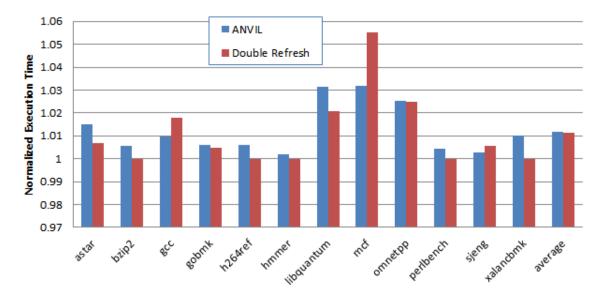

|          | 4.4.3   | Performance Evaluation                           | 30             |

|----------|---------|--------------------------------------------------|----------------|

|          | 4.4.4   | Comparison with Increased Refresh Rate           | 81             |

|          | 4.4.5   | Robustness to Potential Future Rowhammer Attacks | 32             |

| 4.5      | Related | 1 Work                                           | 33             |

|          | 4.5.1   | Rowhammer Vulnerability and Its Exploitation     | 34             |

|          | 4.5.2   | Rowhammer Mitigations                            | 36             |

| 4.6      | Chapte  | r Summary                                        | 38             |

| Chapter  | 5 Co    | nclusion                                         | 90             |

| 5.1      | Future  | Directions                                       | <del>)</del> 0 |

| Bibliogr | aphy .  |                                                  | <del>)</del> 3 |

# **List of Figures**

| 1.1 | Root Causes of Critical Vulnerabilities for the Past Five Years             | 2  |

|-----|-----------------------------------------------------------------------------|----|

| 1.2 | Control-flow Hijacking Attack and Mitigations                               | 3  |

| 2.1 | The Lock-and-Key Technique                                                  | 15 |

| 2.2 | ARM Pointer Authentication – Computing the PAC                              | 16 |

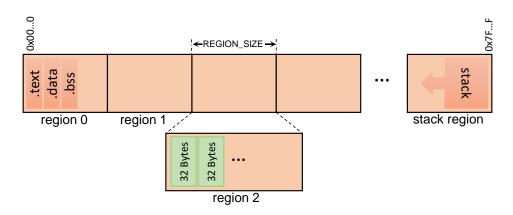

| 2.3 | Low-fat Memory Layout                                                       | 17 |

| 2.4 | Metadata Storage and Access                                                 | 18 |

| 2.5 | Percentage of Redundant Memory Access Checks Removed by PETS Com-           |    |

|     | piler Optimization                                                          | 28 |

| 2.6 | PETS Runtime Overhead                                                       | 28 |

| 2.7 | PETS Memory Overhead                                                        | 30 |

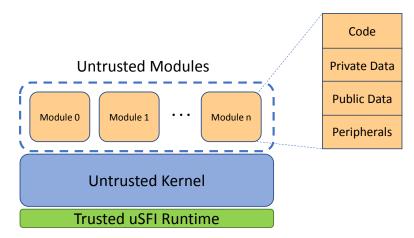

| 3.1 | uSFI System Components                                                      | 40 |

| 3.2 | uSFI Compiler and Verifier                                                  | 44 |

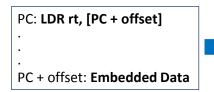

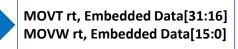

| 3.3 | Potential Illegal Instructions and How to Fix Them                          | 45 |

| 3.4 | PC-relative Load Instruction and its Conversion to Safe Move Instructions . | 46 |

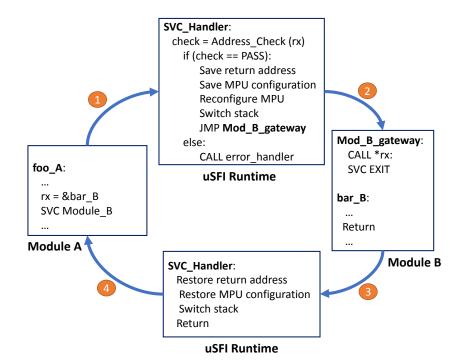

| 3.5 | Inter-module Function Call                                                  | 49 |

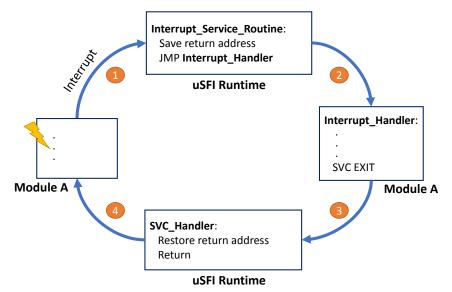

| 3.6 | uSFI Interrupt Handling                                                     | 50 |

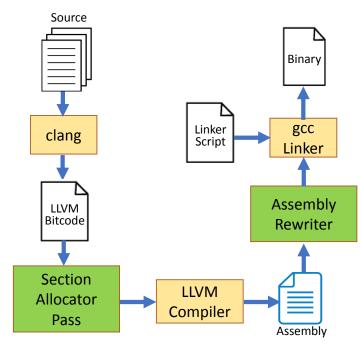

| 3.7 | uSFI Compiler Implementation                                                | 52 |

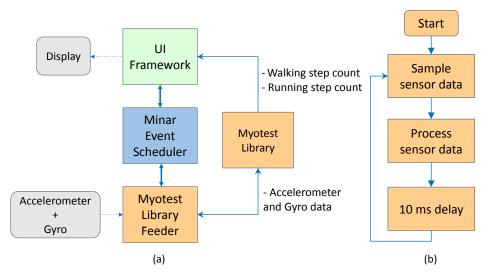

| 3.8 | ARM Wearable Reference Design Step Analysis Application                     | 57 |

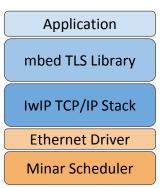

| 3.9 | Software Modules for HTTPS File Download Application                        | 58 |

| 4.1 | Memory Access Patterns for CLFLUSH-based & CLFLUSH-free Double-             |    |

|     | sided Rowhammer Attacks                                                     |    |

| 4.2 | Software-Based Rowhammer Attack Detector                                    |    |

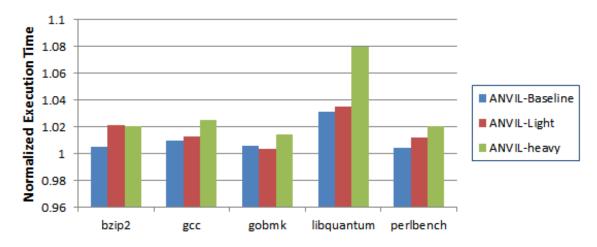

| 4.3 | ANVIL's Impact on Non-Malicious Programs                                    | 81 |

| 4.4 | Sensitivity of Execution Overheads to Potential Future Attacks              | 84 |

# **List of Tables**

| 2.1<br>2.2 | Memory Overhead Comparison                                       | 32 |

|------------|------------------------------------------------------------------|----|

|            | Safety Techniques                                                | 33 |

| 3.1        | uSFI Privilege Levels and Allowed Access                         | 42 |

| 3.2        | Access Permission Configuration for Module Memory Regions        | 43 |

| 3.3        | Code Size Overhead                                               | 56 |

| 3.4        | Execution Cycles for the Step Analysis Application               | 59 |

| 4.1        | Rowhammer Attack Characteristics                                 | 66 |

| 4.2        | Rowhammer Detector Parameters to Evaluate Accuracy of Rowhammer  |    |

|            | Detection                                                        | 79 |

| 4.3        | Rowhammer Detection Result for Rowhammering Programs             | 80 |

| 4.4        | Rate of False Positive Refreshes                                 | 82 |

| 4.5        | Rate of False Positive Refreshes for ANVIL-Heavy and ANVIL-Light | 84 |

# **List of Algorithms**

| 2.1 | Algorithm for UAF Detector Pass | • | 23 |

|-----|---------------------------------|---|----|

| 3.2 | Algorithm for uSFI Verifier     | • | 47 |

# Abstract

Errors in hardware and software lead to vulnerabilities that can be exploited by attackers. Proposed exploit mitigation techniques can be broadly categorized into two: software-only techniques and techniques that propose specialized hardware extensions. Software-only techniques can be implemented on existing hardware, but typically suffer from impractically high overheads. On the other hand, specialized hardware extensions, while improving performance, in practice require a long time to be incorporated into production hardware. In this dissertation, we propose adapting existing processor features to provide novel and low-overhead security solutions.

In the first part of the dissertation, we show how modern hardware features can be used to provide efficient memory safety. One component of memory safety that has become important in recent years is temporal memory safety. Temporal memory safety techniques are used to detect memory errors such as use-after-free errors. This dissertation proposes a temporal memory safety technique that takes advantage of pointer authentication hardware to significantly reduce the memory and runtime overhead of traditional temporal safety techniques. Providing complete memory safety on resource constrained devices is expensive, therefore we propose software-based fault isolation (sandboxing) as an efficient alternative to constrain attackers' access to code and data in embedded systems. We show how we can use the memory protection unit (MPU) hardware available in many embedded devices along with a small trusted runtime to build a low-overhead sandboxing mechanism.

In the second part of the dissertation, we show how hardware performance counters in modern processors can be used to detect rowhammer attacks. Our technique detects rowhammer attacks by monitoring for high locality memory accesses out of the last-level cache using hardware performance counters. The technique accurately detects rowhammer attacks with a low performance overhead and without requiring hardware modifications.

# Chapter 1 Introduction

In recent years it has become common to hear news stories such as ransomware attacks forcing hospitals to shutdown [1], power plants being at risk due to software flaws [2] and companies rolling out patches to stop major security bugs [3, 4]. Such stories typically begin with software bugs such as memory corruption bugs. These bugs create vulnerabilities that can be exploited by attackers to, for example, leak memory, escalate privilege or execute arbitrary code. One of the most exploited software vulnerabilities are memory corruption vulnerabilities.

## **1.1 Memory Corruption Vulnerabilities**

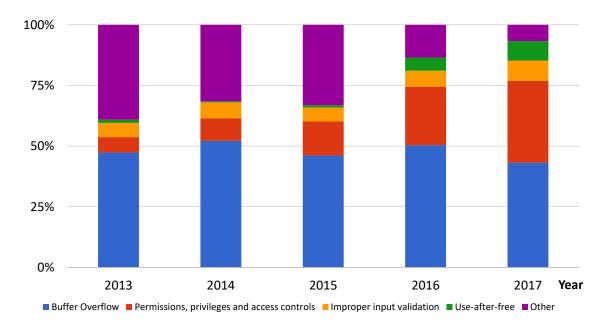

Many programs including OS kernels and runtime environments are written in unmanaged languages such as C and C++. While programs written with these languages can achieve high performance, the fact that memory is managed by the programmer makes them prone to memory corruption errors such as buffer overflow and use-after-free errors. These errors have historically been one of the most exploited errors and still persist today. Figure 1.1 shows a study of the root causes of critical vulnerabilities for a five year period. The data is compiled from [5]. From the graph we can see that memory corruption errors (buffer overflow and use-after-free errors) are still the number one causes of critical vulnerabilities. In 2017 alone, they made up more than 50% of the vulnerabilities.

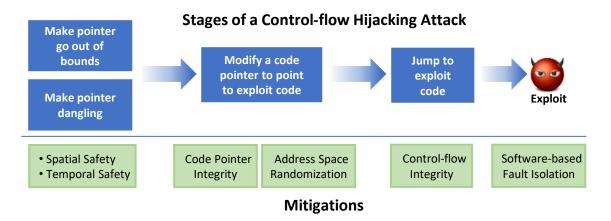

Memory corruption errors are typically used as a basis for exploits such as control-flow hijacking or data-oriented programming [6, 7]. Figure 1.2 shows how memory corruption

Figure 1.1 Root Causes of Critical Vulnerabilities for the Past Five Years.

errors are used to mount an attack, taking control-flow hijacking attack as an example [8]. The first step of a control-flow hijacking attack is making a pointer go out-of bounds using a buffer overflow vulnerability or accessing a dangling pointer by using a use-after-free error. Assuming now the pointer points to a code pointer, we can use it to modify the value of the code pointer so that the code pointer points to exploit code. Then using an indirect call, an indirect branch or a return instruction, control is transferred to the exploit code. The exploit code can be new code injected by the attacker or chained together using already existing code (*code gadgets*). The exploit code typically starts a command shell to allow the attacker to gain control of the system (i.e. to execute arbitrary code and access arbitrary data).

## **1.2 Memory Corruption Exploit Mitigations**

Various defenses against memory corruption exploits have been proposed. These techniques target the various stages of the exploit as shown on Figure 1.2. A group of techniques, called *memory safety* techniques, target the root causes of the exploits - the memory corruption

**Figure 1.2** Control-flow Hijacking Attack and Mitigations. The figure shows the stages of mounting a control-flow hijacking attack and the different mitigation techniques that have been proposed. The mitigations target the different stages of the attack.

errors themselves. These techniques are categorized as *spatial safety* or *temporal safety* techniques. Spatial safety techniques detect spatial errors such as buffer overflows [8]. This typically involves transforming code to include bounds checking instructions. Temporal safety techniques detect temporal errors such as use-after-free errors using various approaches [9, 10, 11, 12, 13, 14].

Enforcing complete memory safety would stop all memory-corruption-based attacks; however, its performance overhead would be very high. For this reason, other techniques that target the later stages of the control-flow hijacking attack have been proposed. Assuming there is a potential memory corruption error, one thing that can be done is prevent the corruption of code pointers at the second stage on Figure 1.2. That is what *Code Pointer Integrity (CPI)* does [15]. Other techniques attempt to hide the addresses of payload code or gadgets by randomizing the locations of code and data. *Address Space Layout Randomization (ASLR)* [16] is an example of such a technique.

Assuming the attacker knows the location of the payload code or gadgets, and they can corrupt a code pointer, the next step is to jump to that code. This entails diverting the execution from the control-flow defined by the source code. *Control-flow Integrity (CFI)* solutions that enforce some policy regarding indirect control transfers can detect control-

flow hijacking attacks at this stage. If the attack makes it past this stage, the control-flow hijacking attack is considered a success and the attacker is assumed to have some control of the system. At this stage, higher-level defences such as *Software-based fault Isolation (sandboxing)* can be used to confine the attacker's access to code and data (*i.e.*, the attacker is only allowed to access code and data defined by an access control policy).

Typically, mitigations are implemented using software-only techniques. While softwareonly techniques can be implemented on existing hardware, they suffer from high performance overheads. For example, complete memory safety (*i.e.*, a technique that provides both spatial and temporal memory safety) has an average slow down of more than 2x [17]. To reduce the overhead of software-only techniques, specialized hardware extensions have been proposed (*e.g.* [18, 19, 20]). Hardware extensions can significantly reduce the overhead, however the techniques can not be used on existing hardware. In addition to this, in practice it takes a long time for a hardware extension to be incorporated into production hardware. For example, control-flow integrity (CFI) [21] is one of the most popular control flow security techniques. Even though hardware support for CFI has been proposed as early as 2005, it is only recently that Intel announced its plan to include hardware support for CFI in future processors [22].

A middle ground in addressing the issue of high overhead in software-only techniques and usability in specialized hardware extensions is adapting existing processor features. Modern processors are rich with hardware features. For example, the x86 architecture has introduced more than 20 ISA extensions since 2011 [23]. We can use these features along with software techniques to design more practical security solutions without requiring specialized hardware extensions.

## **1.3** Contributions of the Thesis

In this dissertation, we take the approach of adapting existing processor features to provide novel and practical security solutions. We present three works that demonstrate this approach. In Chapter 2, we present an efficient temporal memory safety technique that uses the pointer authentication feature in ARM processors. In Chapter 3, we present a technique that uses memory protection unit hardware to provide an efficient sandboxing capability in an embedded device. Finally, in Chapter 4, we show how we can detect rowhammer attacks using hardware performance counters.

### **1.3.1** Efficient Temporal Memory Safety with Pointer Authentication

As mentioned in the previous section, temporal safety is the first line of defense against use-after-free errors. Use-after-free errors occur when an object is accessed outside of the time during which it was allocated (after the object has been freed). As shown on Figure 1.1, they are among the top four critical vulnerabilities and have been consistently on the rise. For example, from the year 2015 to 2017, the number of critical use-after-free errors has increased by 8x. In the 2017 Pwn2Own hacking contest, more than half of the exploits used a use-after-free vulnerability [24].

**The Lock-and-key Temporal Safety Technique:** A number of temporal safety techniques have been proposed over the years [9, 10, 11, 12, 13, 14]. These techniques vary from those that provide probabilistic protections to those that guarantee temporal safety with varying degree of compatibility, complexity and performance overhead. One such technique is the *lock-and-key* technique [9, 14, 25]. This technique assigns a key for each pointer to a memory object, and a matching lock value to the object. On every access to the memory object, a check is made to see if the lock and key values match. Access to the memory object is allowed only if a pointer key matches that of the object lock. When a memory object is deallocated, the lock value is changed, so that further accesses using dangling pointers will be detected.

An important parameter that affects the performance of a lock-and-key technique is *metadata management (i.e,* how lock and key metadata is stored and accessed). Two aspects of metadata management are important:

(1) Granularity of metadata (*i.e.*, pointer metadata vs. memory object metadata): Previous lock-and-key defenses keep a *key* and *lock* pointer metadata *for each* pointer. Typically, there are more pointers than memory objects in a program, therefore keeping per-pointer metadata incurs higher memory overhead than keeping per-memory-object metadata.

(2) How metadata is stored: Some techniques replace pointers with *fat pointers* [14, 25] to store metadata. Fat pointers are structures that contain pointer metadata in addition to the original pointer value. Fat pointers do not add much additional cache pressure compared to regular pointers, however, they require extensive instrumentation of a program [26]. Other techniques have proposed using disjoint metadata storage [9, 18]. One such approach is using a direct-mapped shadow, where metadata is stored at a fixed offset from a pointer. However, shadowing every pointer with this approach incurs a high memory overhead. To reduce the memory footprint, CETS [9] uses a two-level trie data structure to store per-pointer metadata. While this approach has better compatibility than the fat-pointer-based approaches, the multiple loads required to access metadata incur a high runtime overhead. Furthermore, the need to explicitly propagate metadata when a new pointer is derived from an existing pointer makes code instrumentation complex. For example, function prototypes need to be replaced with new prototypes that include metadata.

The lock-and-key technique is effective in detecting use-after-free errors, however previous proposals suffer from complex program instrumentation and high memory and runtime overheads that arise from the way metadata is stored and accessed. In Chapter 2 of this thesis, we propose PETS, a lock-and-key temporal safety technique that takes advantage of the recently introduced pointer authentication feature in the ARM architecture [27] to provide efficient temporal safety.

Pointer authentication stores a cryptographic hash of the pointer value, called a *pointer authentication code (PAC)*, in the unused bits of pointers. With PETS, PACs are used as a replacement for keys. This way lock metadata is kept *per memory object* instead of per pointer, reducing the metadata storage overhead. Furthermore, the relatively small metadata means we can use a direct-mapped shadow to store lock pointer metadata resulting in faster metadata access. Finally, because the key metadata is embedded in the pointer itself, passing pointers as function arguments doesn't require changes to the standard calling convention.

#### **1.3.2** Efficient Software-based Fault Isolation for Embedded Devices

Embedded devices are exposed to the same memory corruption vulnerabilities that are common in traditional computing systems [28, 29, 30]. To make matters worse, many embedded systems lack fundamental code and data memory protection mechanisms that are available in more powerful computing systems. For example, low-end embedded processors typically do not include a memory management unit (MMU) to reduce cost and in some cases to provide real-time execution time guarantees [31]. Therefore, low-end embedded systems typically operate in a single address space with tightly-coupled software modules (e.g., RTOS kernels, peripheral drivers, libraries, etc.) without any form of isolation between modules. A bug in one software module can compromise the security of the whole system.

Previous works have proposed mechanisms to protect code and data in embedded systems, with varying degrees of security assurances and resource requirements. TrustLite [32] proposed a hardware extension to provide isolation of trusted modules (Trustlets) from untrusted code including an untrusted OS. While TrustLite provides strong data isolation guarantees, it requires a hardware extension. Most importantly, it is hardly scalable as the required area of the hardware extension grows linearly with the number of protected modules (the area of the hardware extension matches that of the core for nine modules). Other works have proposed variants of software-based fault isolation (SFI) as a mechanism to isolate tightly-coupled software modules that share the same address space. ARMor [33] uses SFI to sandbox non-critical code by performing binary rewriting to put checks before store operations identified as being potentially unsafe. At runtime, it uses a separate control stack to protect return addresses. Similarly, [34] and [35] use a separate stack to protect return addresses. Other indirect control flow instructions are validated by runtime checks. These software-based protection mechanisms are attractive as they don't require hardware changes. However, this reduced hardware requirement comes at the cost of reduced performance and/or security. In order to reduce the overhead of the runtime checks, the techniques only provide write protection. A malicious software can read and leak sensitive data. In addition to this, the additional memory guard instructions result in larger code sizes and higher performance overheads. As such, there is a need for a *low-cost* mechanism that provides *strong* (read, write, and execution) protection.

In Chapter 3, we present uSFI, a low-cost code and data isolation mechanism for resource constrained embedded devices. uSFI uses readily available hardware, memory protection unit (MPU), along with static software analysis to provide stronger security guarantees at a lower cost than previous efforts. MPU allows partitioning memory into regions and assigning attributes and access permissions to each region. The MPU hardware enforces the access permissions, therefore there is no need to instrument every memory access instruction, eliminating the performance overhead associated with memory access checks. Further, uSFI provides both read and write protection, guaranteeing stronger security than previous works.

# **1.3.3 Detecting Rowhammer Attacks with Hardware Performance Counters**

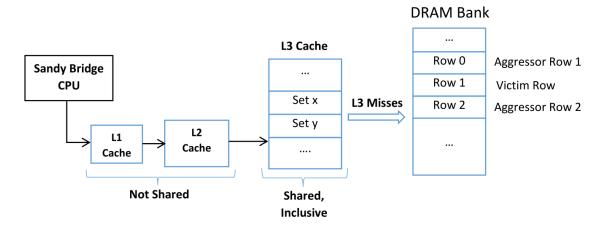

Rowhammer attacks exploit an electrical cross-talk property within the dense interconnect of modern DRAMs (also known as DRAM disturbance errors). Kim, et al. [36] showed that by repeatedly accessing a DRAM row referred to as an *aggressor row*, bits in adjacent DRAM

rows (called *victim rows*) can be flipped. To flip bits, the aggressor row has to be accessed 100's of thousands of times within a DRAM refresh period (typically 64ms). In order to bypass the cache and quickly access the aggressor row, the authors used x86's *CLFLUSH* instruction. Subsequently, Seaborn and Dullien [37] demonstrated two attacks that use rowhammering. The first attack used rowhammering to escape from the Native Client sandbox by rowhammering a code segment and rewriting an already verified instruction. In their second attack, they were able to gain read/write access to page table entries, essentially gaining access to all physical memory. These attacks showed that DRAM disturbance errors not only cause unexpected program behaviors or failures, but also present major security risks.

A number of mitigation techniques for the rowhammer problem have been suggested for both legacy and future systems. One technique that is currently in use is doubling DRAM refresh rate (*i.e.* reducing the refresh period from 64ms to 32ms) [38, 39, 40]. By doing this it is believed that there will not be sufficient time to generate enough DRAM row activations. But as has been suggested previously [36] and as we will show in Chapter 4, 32ms is more than sufficient to generate enough DRAM row activations to produce bit flips. A second protection mechanism used against rowhammering-based attacks is limiting access to cache flushing instruction CLFLUSH [37]. CLFLUSH allows quick access to DRAM by flushing a specific cache line, and restricting this instruction makes rowhammering non-trivial. But as we show in Chapter 4 and as shown by subsequent works [41, 42], rowhammering attack can be implemented with ordinary load and store instructions without requiring a cache flushing instruction.

There is a mention of the existence of protections against rowhammer errors on more recent devices [43, 44]. The LPDDR4 specification and new DDR4 modules include a targeted row refresh (TRR) capability designed to thwart rowhammer attacks. The mechanism tracks the number of row activations within a fixed time window, and selectively refreshes rows adjacent to a too-frequently accessed DRAM row. However, recent works have shown that DDR4 is also susceptible to rowhammer attacks [41, 45].

Finally, the architecture literature has seen a few rowhammer protection proposals [36, 46]. For example, one proposal utilizes probabilistic adjacent row activation (PARA) to refresh the neighboring rows of any DRAM row access, with low probability [36]. The idea behind this approach is that the many repeated DRAM row accesses required to hammer a victim DRAM row will result in an early refresh of the victim row with extremely high (cumulative) probability [36]. However, such solutions require the introduction of new hardware, therefore wouldn't protect existing systems.

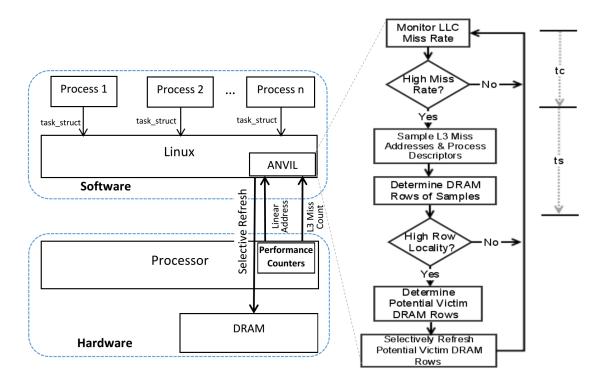

In Chapter 4 of this dissertation, we show how we can detect rowhammer attacks on existing systems. We make the observation that rowhammer attacks require *high-locality* misses out of the last-level cache. Therefore, it is possible to detect rowhammer attacks by monitoring for locality of DRAM memory accesses. To determine the locality of DRAM memory accesses, we use address sampling features provided by modern hardware performance counters.

In summary, the dissertation makes the following contributions:

**Using pointer authentication for efficient temporal safety:** In Chapter 2, we make the following contributions towards providing efficient temporal safety:

- We propose using pointer authentication for temporal safety. The proposed technique we call PETS adapts the lock-and-key mechanism, but instead of keeping per-pointer key metadata, it uses pointer authentication codes (PACs) embedded in the unused bits of pointers. We show that this allows using direct-mapped shadow to store metadata which improves performance compared to other lock-and-key techniques.

- We show how we can further improve the performance of PETS by using a low-fat memory allocator. In this scheme, the lock pointer is encoded in the pointer value itself, avoiding the need to store lock pointer metadata altogether.

- We evaluate PETS using SPECCPU2006 benchmarks and show that it has low runtime overhead compared to previous work (average overhead of 57% for low-fat PETS). In terms of memory overhead, we show that PETS has the least memory overhead

compared to other temporal safety techniques.

**Using memory protection unit for efficient and strong sandboxing:** In Chapter 3, we make the following contributions towards providing efficient sandboxing for embedded systems:

- We present uSFI, a code and data protection mechanism for low-resource devices. uSFI uses software analysis and widely available hardware support in embedded processors (memory protection units) to provide low-cost code and data isolation as well as I/O access control. Through the use of a specialized runtime and verifier, uSFI maintains these protections without instrumenting memory access instructions or indirect jumps, thus providing low-cost software module isolation even in the presence of buggy or malicious privileged code (e.g., a compromised kernel).

- We implement uSFI for the widely used ARMv7-M architecture. Using the MiBench embedded benchmarks suite and other real-world applications, we show that uSFI has low code size and performance overheads. Moreover, we show that the fraction of code that must be trusted in the system (i.e., the uSFI runtime) is a trivially small fraction of the overall system code size. At 150 lines of code, the attack surface of our trust management system can be easily analyzed and inspected to gain trust.

**Using hardware performance counters to detect rowhammer attacks:** In the last part of this thesis, we show that current rowhammer mitigation techniques for existing systems (i.e., disallowing cache flush instructions and doubling refresh rates) do *not* work. To that end, we proposed a software-based rowhammer detector that uses existing performance counter features. Specifically, we make the following contributions:

- We demonstrate the first *CLFLUSH-free* rowhammer attack, thereby thwarting efforts to deter rowhammering by restricting access to the *CLFLUSH* instruction.

- We present ANVIL, a software-based rowhammer detector which protects existing and future commodity DRAMs. We implement ANVIL using existing hardware performance monitoring infrastructure. ANVIL works by monitoring the locality of DRAM row accesses out of the last-level cache.

• We implement ANVIL as a Linux kernel module that utilizes Intel architecture performance monitoring capabilities to detect memory access locality. The detector uses a multi-staged approach to reduce detector overheads, leading to an average slowdown (for non-malicious programs) of about 1%, and worst-case slowdown of 3.2% for SPEC2006 integer benchmarks. The detector is accurate, with no false negatives and less than 1% false positives.

**Dissertation Organization:** The remainder of the dissertations is organized as follows. In Chapter 2, an efficient temporal safety technique is discussed. Chapter 3 proposes an efficient sandboxing mechanism for IoT-class devices. Chapter 4 details how hardware performance counters can be used to detect rowhammer attacks. Finally, we conclude in Chapter 5.

# Chapter 2

# Pointer Authentication for Efficient Temporal Memory Safety

## 2.1 Introduction

Temporal memory safety is one of the first line of defenses against memory corruption exploits. It is used to detect temporal errors such as use-after-free errors. Use-after-free errors occur when an object is accessed outside of the time during which it was allocated. The code example below shows a use-after-free vulnerability that can be used to mount a control-flow hijacking attack. The example is adapted from [10].

```

void(**ptr)() = malloc(sizeof(void*)); // Allocate space

*ptr = &func1;

....

void(**new_ptr)();

new_ptr = ptr; // Copy pointer

....

free(ptr); // Free space

user_input = malloc(...); // Reallocate space

*user_input = ... // Overwrite with input

(*new_ptr)(); // Use-after-free

```

Listing 2.1 Use-after-free Vulnerability Example

In the example *ptr* is a function pointer and points to the function *func1*. A copy of this pointer is made and is assigned to *new\_ptr* on line 5. When the memory object is freed on

line 5, *new\_ptr* becomes dangling. On line 8, the same memory object is reallocated and populated with a user-defined input value. The function call on line 10 creates a control-flow vulnerability because the address can be overwritten to an arbitrary value such as an ROP gadget.

Temporal memory safety techniques are used to detect such vulnerabilities. In this chapter, we show how modern processor features can be used to design an efficient temporal memory safety technique.

## 2.2 Background

In this section we introduce the concepts that are relevant throughout the chapter. We start by describing the *lock-and-key* technique - a popular temporal memory safety technique we build up on, and then we discuss two features that we use to improve the performance of the traditional lock-and-key technique.

## 2.2.1 The Lock-and-key Technique

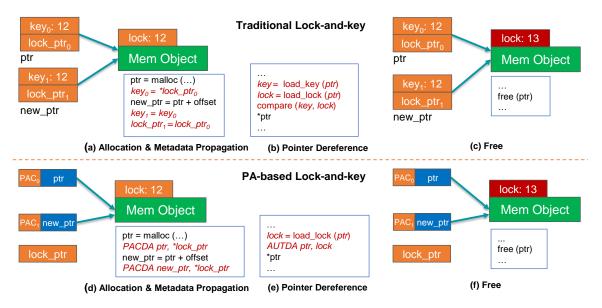

A number of techniques known as temporal safety techniques have been proposed to protect against use-after-free vulnerabilities. The related work section discusses in detail the different kinds of temporal safety techniques. Here we will only describe one commonly used technique, the *lock-and-key* technique [9], which this work builds up on.Figure 2.1(a,b,c) demonstrates the lock-and-key technique. With this technique, each memory allocation (memory object) is assigned a lock, and each valid pointer to that allocation is assigned a matching key. On each access to the object, a check is made to make sure that the lock and key values match. When the memory is deallocated, the lock value is incremented by one so that checks will fail on subsequent references using dangling pointers.

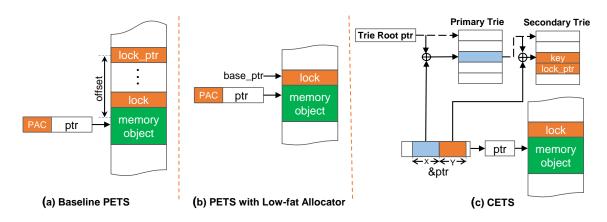

**Figure 2.1 The Lock-and-Key Technique**. The figure compares the *traditional* lock-and-key technique with our proposed pointer-authentication-based technique (PETS). When a memory object is allocated, it is assigned a lock. In the traditional technique, a matching key as well as a pointer to the lock is kept as metadata *for each* pointer. In our technique, pointer authentication code (PAC) values in the extra bits of pointers are used as a substitute to keys. In addition to this, only one lock address metadata is kept per the minimum allocatable object size. When a new pointer is derived from an old pointer, a PAC value is computed for the new pointer using the PACDA instruction. On each memory dereference, the PAC value of a pointer is verified using the AUTDA instruction. Finally, when the memory object is freed, the value of the lock is incremented by one.

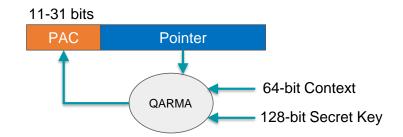

### 2.2.2 ARM Pointer Authentication

In this work, we use pointer authentication to provide efficient temporal safety. Pointer authentication is a security primitive introduced in ARMv8.3-A and is used to verify the integrity of pointers [27]. It uses the unused bits in a pointer to store a cryptographic hash of the pointer value called *Pointer Authentication Code (PAC)*. The size of the PAC can vary from 11 to 31 bits depending on the system configuration. For example on AArch64, the Linux kernel uses a 39-bit virtual address space by default which allows for a 24-bit PAC [27].

The PAC is computed as a truncated output of the QARMA block cipher [47] or an implementation defined algorithm [48]. In this work we assume QARMA is used. As shown in Figure 2.2, three inputs are used to compute the PAC: the pointer value, a 128-bit secret

**Figure 2.2** ARM Pointer Authentication – Computing the PAC. The PAC is computed as a truncated output of the QARMA block cipher.

key and a 64-bit *context* value. The key is stored in internal registers and is not accessible by user mode. The context value can be any user supplied value. In this work we use a memory object lock value as the context value. The Pointer Authentication specification defines five keys. Two keys (key A and key B) are used to compute PACs for data pointers and other two key are used for instruction pointers. A fifth key is provided for a generic authentication instruction.

The pointer authentication feature also provides instructions to compute and verify PAC values. For our work, we use two pointer authentication instructions: *PACDA* and *AUTDA*. The PACDA instruction computes and inserts a PAC for a data pointer using a context value and data pointer key A, while the AUTDA instruction authenticates a data pointer using a context value and data pointer key A [48]. If the authentication passes, the upper bits of the pointer are restored to enable subsequent use of the pointer. If the authentication fails, however, the upper bits are corrupted and any subsequent use of the pointer results in a translation fault.

#### 2.2.3 The Low-fat Memory Layout

In Section 2.3 we show how metadata can be kept to the minimum by using a *low-fat memory layout*. The low-fat memory layout [49] subdivides a program's virtual address space into several regions. Each region is responsible for allocation of objects of a given fixed size range. Figure 2.3 shows an example low-fat memory layout. On the figure *region*

**Figure 2.3** Low-fat Memory Layout. The low-fat memory layout subdivides a program's virtual address space into several regions. *Region 0* is used for text and data segments, and a *stack region* is used as program stack. Objects of a given size are allocated from a specific region. For example, objects of size 32 bytes are allocated from *region 2*.

*0* is reserved for program *text* and *data* segments, and a special region (*stack region*) is assigned for the program stack. The rest of the regions contain sub-heaps for the *low-fat memory allocator*. The low-fat memory allocator allocates objects of a given size from a specific region. For example, suppose object sizes are restricted to be powers-of-two sizes, and the minimum allocatable size is 16 bytes. In this case objects of size 1-16 bytes are allocated from *region 1*, objects of size 17-32 bytes are allocated from *region 2* and so on.

The low-fat memory layout allows for implicit encoding of *object size* information in pointer values. The upper bits of a pointer indicate the region number which directly corresponds to the size of the object the pointer references. In addition, the base pointer of an object can be directly computed from any pointer to that object. This characteristics can be used for efficient bounds checking [49].

In the next section we will show how a low-fat memory allocator can be used to further reduce the overhead of our temporal safety technique.

**Figure 2.4** Metadata Storage and Access. The figure shows metadata storage for the two variants of PETS and CETS. The first technique is for baseline PETS where *one-level mapping* is used to map a memory object pointer to a lock pointer location. With this approach, two load operations are required to get the lock value. The second technique is for PETS with low-fat allocator. This technique doesn't require storing a lock pointer, as the lock pointer is the same as the base pointer, which is directly calculated from the pointer value. This approach requires only one load operation to read the lock value. The last technique is used by CETS [9], which we catagorize as traditional lock-and-key technique. CETS uses two-level lookup trie data structure to store metadata. With this approach each metadata access requires four loads.

## **2.3** Pointer Authentication for Temporal Safety

Though effective, the traditional lock-and-key technique described in Section 2.2 incurs large performance and memory overheads. In this work, we propose using pointer authentication to reduce the performance and memory overhead of the traditional lock-and-key technique. The proposed technique, which we call PETS, adapts the lock-and-key mechanism for temporal safety, but instead of using explicit storage for keys, we propose using PACs (Pointer Authentication Codes).

**Allocation and Metadata Propagation:** Figure 2.1 compares the traditional lock-and-key technique with PETS. Similar to the traditional lock-and-key technique, each memory allocation (memory object) is assigned a lock. When a pointer to that allocation is created (using a memory allocation function such as *malloc*) a PAC value is computed and stored in the unused bits of the pointer using the *PACDA* instruction (Figure 2.1(d)). This instruction takes the pointer value and a 64-bit context value as inputs. We use the lock value as a

context. When a new pointer is derived from an old pointer, for example through pointer arithmetic, a PAC value is computed for the new pointer.

**Pointer Dereference:** On each pointer dereference, the PAC value of a pointer is verified using the *AUTDA* instruction (Figure 2.1(e)). The AUTDA instruction computes a PAC using the pointer value and the lock value and compares it with the PAC value stored in the unused bits of the pointer. If the two PAC values do not match, the pointer is stale and corrupted so that a translation fault is generated if the pointer is dereferenced

**Deallocation:** Finally, when the memory is deallocated, for example using *free()*, the lock value is incremented, similar to the traditional lock-and-key technique (Figure 2.1(f)). On subsequent accesses using a dangling pointer, PAC verification should fail since the lock value has changed.

We explored two variants of PETS: PETS with shadow storage (we will refer to this as *baseline PETS* for the rest of the paper) and low-fat PETS. Both variants use pointer authentication; the only difference is the memory allocators they use. We discuss the two variants in detail below.

## **2.3.1 PETS with Shadow Storage (Baseline PETS)**

Baseline PETS uses the standard C library memory allocator (dlmalloc-based allocator). Each heap memory object, regardless of the size of the object, keeps a 64-bit lock value. In addition to this, a 64-bit pointer to the lock (lock pointer) is kept per the minimum allocatable heap object. In our implementation the minimum size of a heap object is 32 bytes. Figure 2.4(a) shows how metadata is stored and accessed in the baseline PETS implementation. We use *one-level mapping* to map a pointer value to its metadata (lock pointer) location. With this mapping, the lock address is located at a fixed offset from the pointer value. This way the lock pointer location can be calculated by a single shift and

addition operations. On memory allocation, the memory allocator allocates metadata space for the memory object if it is not already allocated and updates the value of the lock pointer that corresponds to the new pointer.

The PETS compiler adds code to propagate metadata (including computing PAC) whenever a new pointer is derived from an old pointer. The code below shows the operations performed on pointer propagation. The lock pointer is copied from the old pointer lock pointer location to the new pointer lock pointer location. Then a PAC is computed for the new pointer after loading the lock value.

```

// Copy lock pointer

lock_ptr_addr = compute_lock_ptr_address(old_ptr)

old_lock_ptr = *lock_ptr_addr

lock_ptr_addr = compute_lock_ptr_address(new_ptr)

*lock_ptr_addr = old_lock_ptr

// Compute PAC

lock = *old_lock_ptr

PACDA new_ptr, lock

```

Listing 2.2 Baseline PETS - Metadata Propagation Code

The PETS compiler also adds code to verify PAC values on every relevant load and store as shown on the code below. The verification code first loads the lock that corresponds to the pointer from the metadata location. If the lock matches the lock used during PAC computation, then the verification should pass. When the memory object is freed, the memory allocator increments the lock value.

```

1 // Load lock and verify PAC

2 lock_ptr_addr = compute_lock_ptr_address(ptr)

3 lock_ptr = *lock_ptr_addr

4 lock = *lock_ptr

5 AUTDA ptr, lock

```

Listing 2.3 Baseline PETS - PAC Verification Code

### 2.3.2 Low-fat PETS

The baseline technique can be further optimized if a low-fat memory allocator is used instead of a dlmalloc-based allocator. In this technique, similar to the baseline PETS, each heap memory object keeps a 64-bit lock value at the *base* of the memory object (*i.e.* at the base pointer). With low-fat memory layout the base pointer of a memory object can be calculated from a pointer value, therefore there is no need to keep a lock pointer metadata. Figure 2.4(b) shows how metadata is stored and accessed for the low-fat based PETS implementation. For our implementation we used powers-of-two sizes for the heap objects with a minimum heap object size of 16 bytes. With this implementation, the base pointer can be calculated by fast logical shift and AND operations. The code below shows the operations for metadata propagation. Unlike baseline PETS, there is no need to copy metadata during propagation: only PAC computation for the new pointer is performed.

```

base_ptr = compute_base_pointer(new_ptr)

lock = *base_ptr

PACDA new_ptr, lock

```

Listing 2.4 Low-fat PETS - Metadata Propagation Code

In addition to this, on pointer dereference, the lock value is directly loaded from the base pointer, requiring only one load operation to read the lock value.

```

base_ptr = compute_base_pointer(ptr)

lock = *base_ptr

AUTDA ptr, lock

```

#### Listing 2.5 Low-fat PETS - PAC Verification Code

As a comparison with the closest related work, Figure 2.4(c) shows the metadata storage technique used by CETS [9], which we catagorize as traditional lock-and-key technique. CETS uses two-level lookup trie data structure to store metadata. It stores key and lock pointer metadata *for each* pointer. The upper x bits of a pointer address are used to index

the primary trie structure and the lower y bits are used to index the secondary trie structure. With this approach each metadata access requires four loads as opposed to only one load operation for low-fat PETS.

As we will show in Section 2.5, the metadata storage and access technique significantly affects the performance of the lock-and-key technique.

# 2.4 PETS Implementation

In this section, we discuss the implementation details of PETS. We describe the two components of PETS: the PETS compiler instrumentation and the memory allocators.

#### 2.4.1 PETS Compiler Instrumentation

PETS instruments code as described in Section 2.3. We implemented the compiler instrumentation with an LLVM [50] pass we call *UAF detector pass*. Algorithm 2.1 shows the algorithm for UAF detector pass. The pass checks each instruction to determine whether it is a pointer arithmetic instruction or a memory access instruction. For a pointer arithmetic instruction, it inserts the code on Listing 2.2 or Listing 2.4 *after* the instruction, depending on the variant of PETS used. Similarly, for a memory access instruction the code on Listing 2.3 or Listing 2.5 is inserted *before* the instruction.

Like mentioned earlier, stack use-after-free errors are rare, therefore PETS targets heap use-after-free errors. For this reason, no instrumentation code is inserted if a pointer is statically (at compile time) determined to point to the stack or global data. However, it is not always possible to determine where a pointer points to at compile time, therefore code that dynamically checks whether the pointer is within the bounds of the heap is inserted at the beginning of the instrumentation code. In a typical address space layout, the heap is located above the *.bss* section and below the stack, therefore the rest of the instrumentation code is bypassed if the pointer is greater than or equal to the stack pointer, or it is less than the end

|             | 6                                                  |                                 |  |  |

|-------------|----------------------------------------------------|---------------------------------|--|--|

| 1: <b>p</b> | 1: <b>procedure</b> INSTRUMENTFUNCTION(Function F) |                                 |  |  |

| 2:          | for Instruction I in F do                          |                                 |  |  |

| 3:          | if pointerArithmeticInst (I) then                  |                                 |  |  |

| 4:          | $ptr \leftarrow getSrcPtr(I)$                      |                                 |  |  |

| 5:          | if isGlobalVar (ptr) —— isStackVar (ptr) then      |                                 |  |  |

| 6:          | continue                                           |                                 |  |  |

| 7:          | instrumentPtrArithmetic (I)                        | $\triangleright$ Listing 1 or 3 |  |  |

| 8:          | else if memoryAccessInst (I) then                  |                                 |  |  |

| 9:          | $ptr \leftarrow getAddress(I)$                     |                                 |  |  |

| 10:         | if isGlobalVar (ptr) —— isStackVar (ptr) then      |                                 |  |  |

| 11:         | continue                                           |                                 |  |  |

| 12:         | instrumentMemoryAccess (I)                         | ⊳ Listing 2 or 4                |  |  |

|             |                                                    |                                 |  |  |

of the *.bss* section (bss\_end) as shown below. PETS doesn't need to know where the start or the end of the heap is, therefore it is compatible with ASLR.

```

// Bypass check if pointer points to data

// in the stack or data section

if (ptr >= stack_ptr)

goto end

if (ptr < bss_end)

goto end

// Rest of instrumentation code

end:</pre>

```

#### **Compiler Optimizations**

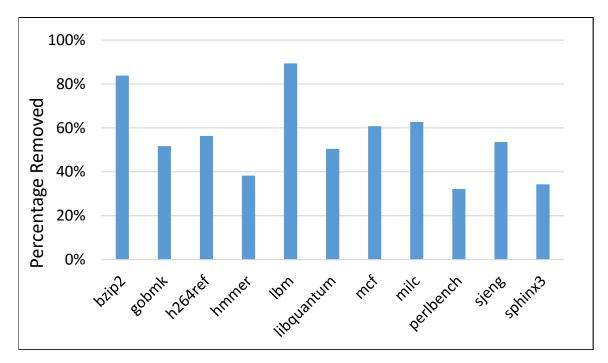

The PETS compiler eliminates redundant pointer dereference checks similar to [9]. Given a memory access instruction I that uses a pointer, if the instruction is dominated by an earlier check of the pointer and there is no call to a *free()* function between I and the check, then no check is inserted before I.

The PETS compiler doesn't perform inter-procedural analysis to determine calls to *free*, instead we conservatively assume any function call would potentially free any memory object. With this approach we were able to remove a significant number of redundant check

on some benchmarks as shown on Figure 2.5.

#### 2.4.2 Memory Allocators

As detailed in Section 2.3, we evaluated two variants of PETS. The two variants use different memory allocators.

**Baseline PETS:** The baseline PETS uses a dimalloc-based memory allocator. For our implementation, we modified the musl C library memory allocator. Specifically, we made the following modifications:

- The *chunk* struct which maintains metadata for memory chunks (memory objects) was modified to include a *lock* element.

- Memory allocation functions (*malloc, calloc, realloc*) were modified to include a routine that allocates metadata space and initializes the *lock pointer* value in the metadata space.

- On *free*, the *lock* value for the corresponding chunk is incremented by 1.

During the memory allocation or freeing process, memory objects can be split or merged together. The value of the lock in the memory object needs to account for these operations. When a memory object is split into two, the new memory object inherits the lock value of the parent memory object. When two memory objects are merged together, if the two objects have different lock values, the *larger* lock value is taken as the lock value of the new object. This insures that a lock value is never reset back to an older value.

**Low-fat PETS:** The low-fat PETS implementation uses a low-fat memory allocator. We used a modified version of a low-fat allocator implementation provided at [51]. We configured the allocator to use powers-of-two sizes. There are 30 possible heap object sizes with a minimum allocation size of 16B and a maximum size of 8GB. There are 32 regions in total including the *stack region* and *region 0* which is used for code and data sections as shown in Figure2.3. In our implementations, we assume a 39-bit virtual address space which is

the default for the Linux kernel on AArch64 [27]. The most significant 5 bits are used to indicate the memory object size. This leaves 34 bits to index a region.

With this setting the *compute\_base\_pointer* function on Listings 2.4 and 2.5 is implemented as:

```

compute_base_pointer (ptr) {

size = ptr >> 34

mask = 0x7FFFFFFF8 << size

base_ptr = ptr & mask

return base_ptr

}

</pre>

```

We made the following modifications to the memory allocator to enable use-after-free protection:

- A *lock* value is added at the base address of each allocation.

- On *free*, the *lock* value is incremented by 1.

#### 2.4.3 Support for Multithreaded Applications

Multithreaded applications present a challenge for memory safety techniques. One issue is a potential data race when accessing shared metadata structures. For example, CETS uses a shared *next\_key* counter that is incremented whenever a memory object is allocated [9]. To avoid races, either accesses to the counter need to be synchronized or each thread need to keep its own counter. PETS doesn't have such issues because metadata is kept for each memory object.

However there are situations where temporal safety might be violated if the multithreaded application is not properly synchronized. For example, between an address check and a memory object access, another thread might free the memory object, resulting in missed violation. PETS supports multithreaded programs without any change as long as the programs are properly synchronized (*i.e.* they are data-race free).

# 2.5 Experimental Evaluation

In this section we discuss the evaluation of PETS. We evaluated the runtime and memory overheads of the two variants of PETS and compared them with other temporal safety techniques. We start by detailing our setup for the evaluations.

## 2.5.1 Experimental Setup

#### **Pointer Authentication Implementation**

PETS makes use of the ARM pointer authentication extension. ARM pointer authentication extension is a feature of the new ARMv8.3-A ISA specification. At the time of the writing of this paper there were no hardware implementations that support ARMv8.3-A, therefore we had to model the pointer authentication feature. Specifically we modeled the two instructions used by our technique (*i.e.* PACDA and AUTDA instructions).

**Correctness Evaluation:** To evaluate the correctness of our technique (*i.e.* to verify that programs behave correctly with PETS instrumentation), we modeled the two instructions in the QEMU emulator [52]. We ran SPECCPU2006 benchmarks and verified the correctness of the outputs.

**Runtime Overhead Evaluation:** To evaluate runtime overhead, we modeled PACDA and AUTDA instructions in the gem5 cycle-accurate simulator [53]. In our gem5 model we assumed there is a single separate functional unit that performs pointer authentication related operations such as computing a PAC value as shown in Figure 2.2 and comparing the result of a PAC computation with a PAC value stored in a pointer. We modeled the PAC computation to take 8 cycles at a CPU frequency of 1.5 GHz based on the results of QARMA encryption latency given at [47].

Our tests using the model in gem5 revealed that the contribution in runtime overhead of

PAC computation and verification is negligible compared to the rest of PETS instrumentation code (For example, on baseline PETS, there are two loads per memory access check). For this reason and because running large benchmarks (such as SPECCPU2006 benchmarks) to completion in a cycle-accurate simulator takes a very long time, runtime evaluations are done on a real hardware by replacing PACDA and AUTDA instructions with NOPs.

**PAC Size:** In our implementations, we assume a 39-bit address space. That means there are 24 bits for PACs. Each memory object has a separate 64-bit lock value which is incremented whenever the memory object is freed. However due to the limited number of PAC bits we essentially have a 24-bit entropy. It is possible to get collusions during the lifetime of a memory object. The PETS memory allocator stops reallocating a memory object when the lock value overflows.

#### **Evaluation Platform**

As mentioned earlier, our model of the pointer authentication instructions in the gem5 simulator showed that the effect of pointer authentication instructions on the performance of the overall system is negligible. Therefore, all the evaluations in this section are performed on a real hardware. Note that only runtime is affected by pointer authentication instructions - memory overhead is not affected by the instructions.

Specifically we used the Xilinx ZCU102 evaluation board [54] for our evaluations. The board includes four ARM Cortex-A53 cores with 32kB L1 instruction and data caches and a 1MB shared L2 cache. The board also includes a 4GB DDR4 DRAM.

**Benchmarks:** We used the C benchmarks from SPECCPU2006 for our evaluations. We used the default -*O2* optimization when compiling the benchmarks.

Figure 2.5 Percentage of Redundant Memory Access Checks Removed by PETS Compiler Optimization.

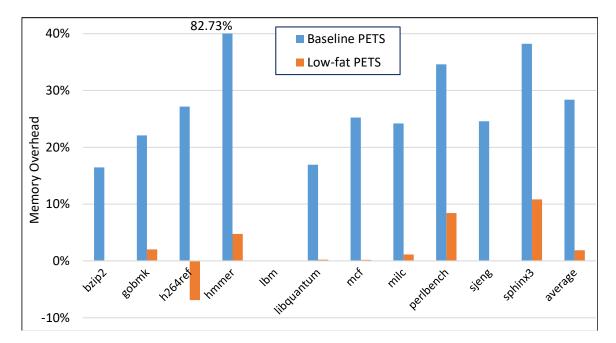

**Figure 2.6 PETS Runtime Overhead**. The graph shows the runtime overhead of the two variants of PETS for SPEC2006 benchmarks. In almost all benchmarks low-fat PETS performs better than baseline PETS. Most of the overhead for PETS comes from memory access checks. We can see a correlation between the overhead and the percentage of redundant checks removed shown on Figure 2.5. The benchmarks with the highest overhead are the ones with the least optimization.

#### 2.5.2 Runtime Overhead:

We measured the runtime overhead of the two variants of PETS. For the evaluation, the benchmarks were compiled with the redundant check optimization discussed in Section 2.4. Figure 2.5 shows the percentage of redundant memory access checks removed by the optimization. As shown in the figure, the optimization removed a significant number of redundant checks.

Figure 2.6 shows the runtime overheads of the two variants of PETS as compared to a baseline system without PETS instrumentation. As shown in the figure, lowfat-based PETS performs better on all the benchmarks except *libquantum* and *lbm*. This is attributed to the smaller number of loads per memory access checks for lowfat-based PETS. The two exceptions are due to the overhead of the low-fat memory allocator outweighing the overhead of the instrumentation. We can see a correlation between the percentage of redundant checks removed and the runtime overhead. Benchmarks that have the highest overheads (*perlbench*, *hmmer* and *sphinx3*) are also the ones with the least optimization. In summary, low-fat PETS has an average overhead of 57.12% while baseline PETS has an average overhead of 132.86%.

## 2.5.3 Memory Overhead

We also evaluated the physical memory overhead of PETs. Figure 2.7 shows the memory overhead of the two variants of PETS. The memory overhead was calculated using readings from the */proc/pid/status* file in Linux by adding the peak resident set size (vmHWM), page table entries size (VmPTE) and size of second-level page tables (VmPDE).

As shown on the figure, low-fat based PETS has a very low memory overhead averaging at 1.9%. Most of the overhead for low-fat PETS comes from the low-fat allocator itself. Baseline PETS has an average overhead of 28.4%. This is expected as 8-byte lock pointer metadata is kept for every 32-byte memory object. Ideally, this would result in a memory

**Figure 2.7 PETS Memory Overhead**. The graph shows the physical memory overhead for the two variants of PETS. From the graph we can see that low-fat PETS has a very low memory overhead as it almost entirely avoids using metadata. Note that h264ref has negative overhead for low-fat PETS. This is attributed to the low-fat memory allocator being more efficient than the baseline dlmalloc-based allocator.

overhead of 25%. The extra overhead comes from addition of a lock metadata per allocated memory object and the associated object alignment requirement.

# 2.5.4 Comparison with other Temporal Safety Techniques

The related work section discusses in detail the pros and cons of related temporal safety techniques, here we compare performance of PETS with some of these techniques. All the other techniques were implemented and evaluated on an X86 system and on different microarchitecture than ours, therefore we don't do a direct comparison of runtime overhead. However, we do a direct comparison of memory overhead as it is independent of architecture.

**Comparison with CETS:** CETS [9] is a lock-and-key technique that uses a disjoint metadata per pointer as shown on Figure 2.4. It is the closest work to PETS. CETS needs four load operations per metadata access, while lowfat-PETS needs only one, therefore CETS is expected to have a higher runtime overhead as compared to PETS.

Table 2.1 compares memory overhead of low-fat-based PETS with CETS. The original CETS paper doesn't provide memory overhead results. We estimated the overhead of CETS from the results given at the follow-up work SoftBoundCETS [17]. SoftBoundCETS provides both temporal and spatial memory safety. It keeps four 64-bit values (lock, key, base and bounds) as metadata per pointer while CETS keeps only two of the values (lock and key). Therefore we estimated that temporal protection alone (CETS) contributes to at least half of the memory overhead of SoftBoundCETS. The numbers for CETS in Table 2.1 are half of that is given for SoftBoundCETS at [17]. The numbers for some of the benchmarks are left blank since data is not available. From the table, we can see that low-fat PETS has far lower memory overhead than CETS on almost all the benchmarks. The average overhead for CETS for the benchmarks where data is available (92%) is much higher than even the baseline PETS (28.4%).

**Comparison with DangSan and DangNull:** Another temporal safety technique keeps track of all pointers to a memory object. When the memory object is deallocated, the values of all pointers to that object are corrupted by for example setting the values to NULL. DangSan [11] and DangNull [12] are such two techniques.

These techniques do not need to instrument pointer dereferences as the memory managment unit (MMU) performs null checks in hardware. The overhead for these techniques comes from traversing pointer tracking data structures during allocation and deallocation of memory objects. This means these techniques have better runtime performance than PETS on applications that do not allocate/deallocate memory frequently. However for benchmarks that create 100s of millions of objects, such as *perlbench*, we expect PETS to perform better.

In terms of memory overhead, as shown on Table 2.1, DangNull's and DangSan's overhead vary greatly depending on the benchmark, but overall lowfat-based PETS performs much better (1.9% average overhead for low-fat PETS vs. 212% average for DangNull and

| Benchmark |                 | Memory Overhead (%) |         |       |      |  |  |  |

|-----------|-----------------|---------------------|---------|-------|------|--|--|--|

|           | Low-fat<br>PETS | DangNull            | DangSan | Oscar | CETS |  |  |  |

| bzip2     | 0.07            | 0                   | 0       | 0     | -    |  |  |  |

| gobmk     | 2.04            | 21                  | 120     | 0     | 250  |  |  |  |

| h264ref   | -6.90           | 373                 | 16      | 10    | 190  |  |  |  |

| hmmer     | 4.75            | 1700                | 30      | 33    | -    |  |  |  |

| lbm       | 0               | 0                   | 1       | 0     | 40   |  |  |  |

| libquant  | 0.23            | 0                   | 2       | 5     | 0    |  |  |  |

| mcf       | 0.20            | 0                   | 62      | 0     | -    |  |  |  |

| milc      | 1.14            | 0                   | 25      | 16    | 55   |  |  |  |

| perlbench | 8.44            | -                   | 380     | 225   | -    |  |  |  |

| sjeng     | -0.02           | 0                   | 2       | 0     | 0    |  |  |  |

| sphinx3   | 10.82           | 34.7                | 180     | 400   | 110  |  |  |  |

Table 2.1

Memory Overhead Comparison. The table compares the physical memory overhead

of low-fat PETS with other temporal safety techniques. From the table we can see that low-fat PETS

has by far the least overhead.

74% average for DangSan).

**Comparison with Oscar:** Oscar [10] is a recently proposed page-permission-based temporal safety technique. Oscar doesn't instrument code - its overhead originates from creating shadow pages during allocations. For this reason, Oscar has low runtime overhead for applications that do not allocate memory frequently. However, PETS has much lower memory overhead than Oscar (1.9% average for lowfat-PETS vs. 62% average for Oscar for the benchmarks on Table 2.1).

In summary, low-fat PETS by far has the least memory overhead compared to the other temporal safety techniques on Table 2.1. The runtime overhead of PETS is expected to be lower than other lock-and-key techniques such as CETS.

# 2.6 Related Work

In this section we review previous work, focusing on temporal safety techniques.

|                         |                                     |                         |             |                   |               |                               |               | -                          |                                    |                                    |             |                 |               |                              |               |              |

|-------------------------|-------------------------------------|-------------------------|-------------|-------------------|---------------|-------------------------------|---------------|----------------------------|------------------------------------|------------------------------------|-------------|-----------------|---------------|------------------------------|---------------|--------------|

|                         | Disjoint Per-pointer<br>Metadata    | >                       | >           | >                 | >             |                               |               | >                          |                                    |                                    |             |                 |               |                              |               |              |

| igment                  | Tagged Pointers                     |                         |             |                   |               |                               |               |                            |                                    |                                    |             |                 |               |                              | >             | >            |

|                         | Fat Pointers                        |                         | >           |                   |               |                               |               |                            |                                    |                                    |             |                 |               |                              |               |              |

| Metadata Managment      | Custom Data<br>Structure            |                         |             |                   |               | >                             | >             |                            |                                    |                                    |             |                 |               |                              |               |              |

| Metad                   | Shadow<br>Shadow                    |                         |             |                   |               | >                             |               |                            |                                    |                                    |             | >               | >             |                              |               |              |

|                         | Direct-mapped<br>Shadow             |                         |             |                   |               |                               |               |                            |                                    |                                    | >           |                 |               |                              | >             |              |

| nanism                  | Probablistic/<br>Memory-reuse Delay |                         |             |                   |               |                               |               |                            |                                    |                                    | >           | >               | >             | >                            |               |              |

| UAF Detection Mechanism | Page-permission-<br>based           |                         |             |                   |               |                               |               |                            | >                                  | >                                  |             |                 |               |                              |               |              |

| F Detect                | Dangling Pointer<br>Tagging         |                         |             |                   | >             | >                             | >             | >                          |                                    |                                    |             |                 |               |                              |               |              |