## Reduction of dislocation density in mismatched SiGe/Si using a low-temperature Si buffer layer

K. K. Linder, F. C. Zhang, J.-S. Rieh, and P. Bhattacharya<sup>a)</sup> Department of Electrical Engineering and Computer Science, Solid State Electronics Laboratory, University of Michigan, Ann Arbor, Michigan 48109-2122

## D. Houghton

SiGe Microsystems, Inc., Nepean, Ontario, K2H 9C4, Canada

(Received 26 February 1997; accepted for publication 14 April 1997)

The reduction of the dislocation density in relaxed SiGe/Si heterostructures using a low-temperature Si(LT-Si) buffer has been investigated. We have shown that a 0.1  $\mu$ m LT-Si buffer reduces the threading dislocation density in mismatched Si<sub>0.85</sub>Ge<sub>0.15</sub>/Si epitaxial layers as low as  $\sim 10^4 \text{ cm}^{-2}$ . Samples were grown by both gas-source molecular beam epitaxy and ultrahigh vacuum chemical vapor deposition. © 1997 American Institute of Physics. [S0003-6951(97)03424-4]

SiGe/Si heterostructures have gained considerable attention for both electronic and optoelectronic applications due to their compatibility with existing Si technology. 1-5 In particular, there are device applications where a strained Si channel layer of a field-effect transistor needs to be grown on relaxed SiGe to produce a type II heterostructure band lineup. Producing relaxed, nearly defect-free SiGe alloys has been difficult due to the 4% mismatch between Si and Ge. Above the critical thickness, threading dislocations form in the SiGe epilayer, resulting in material degradation and poor device performance.<sup>6</sup> Both superlattices and step-graded layers have been used as techniques to reduce the strain energy while minimizing threading dislocations. 7-13 While some reduction was obtained, 7-9 the dislocation densities are still too high ( $\sim 10^9$  cm<sup>-2</sup>) for any practical device application.

Recent reports indicate that the use of amorphous, polycrystalline, and low-temperature buffer layers can significantly reduce dislocation densities in nitride, InAlAs/InP, and SiGe technologies. 14-16 We have investigated the use of a low-temperature Si (LT-Si) buffer layer for reducing the threading dislocation density in relaxed SiGe heterostructures. We report the characterization of these heterostructures grown by both gas-source molecular beam epitaxy (GSMBE) and ultrahigh vacuum chemical vapor deposition (UHV-CVD), and of heterojunction bipolar transistors (HBTs) using LT-Si buffers.

A number of relaxed SiGe samples with and without the LT-Si buffer layer were grown by GSMBE. Pure Si<sub>2</sub>H<sub>6</sub> and solid Ge were used as source materials. The samples were grown on (100)  $p^+$  Si substrates. Each sample consists of a 0.1  $\mu$ m Si layer grown at 700 °C followed by a 0.1  $\mu$ m LT-Si buffer layer grown at 450 °C. A 0.5  $\mu$ m Si<sub>0.85</sub>Ge<sub>0.15</sub> layer was then grown at 570 °C. Growth of the entire structure was monitored by in situ reflection high-energy electron diffraction measurements. The image displayed a streaked (2×1) pattern during growth of Si at 700 °C, which turned spotty during growth of the LT-Si buffer layer. The streaked pattern was restored after a few monolayers of growth of SiGe at 570 °C. The control sample consists of a 0.1  $\mu$ m Si layer also grown at  $700\,^{\circ}\text{C}$  followed by a 0.5  $\mu\text{m}$

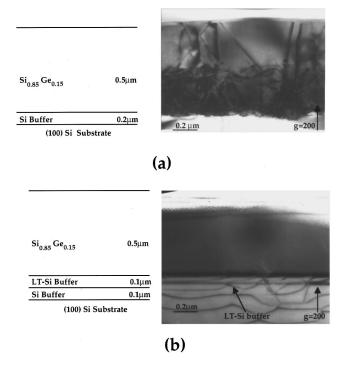

Bright-field cross-section (200) imaging of heterostructures without and with the LT-Si buffer layer are shown in Figs. 1(a) and 1(b), respectively. In the samples without the LT-Si buffer layer, the threading dislocations propagate throughout the alloy layer, as expected. An examination by bright field plan-view (022) imaging indicates a threading dislocation density of  $7.56 \times 10^9 \pm 2.08$  cm<sup>-2</sup> in the sample

FIG. 1. Bright field (200) cross-section TEM images of 0.5  $\mu$ m thick Si<sub>0.85</sub>Ge<sub>0.15</sub> grown at 570 °C on (100) Si substrates (a) without any lowtemperature Si(LT-Si) buffer and (b) with a 0.1  $\mu$ m LT-Si buffer layer grown at 450 °C. Both samples have a 0.1  $\mu m$  Si buffer layer grown first on the substrate at 700 °C.

Si<sub>0.85</sub>Ge<sub>0.15</sub> layer grown at 570 °C. Each SiGe sample thickness exceeds the thermodynamically stable critical thickness of 0.4  $\mu$ m. <sup>17</sup> The threading dislocation densities were examined by transmission electron microscopy (TEM) using a JEOL 2000-FX microscope with an accelerating voltage of 200 kV. Both cross-section TEM and plan-view imaging were performed.

a)Electronic mail: pkb@eecs.umich.edu

FIG. 2. TEM images of SiGe samples grown on (100) Si substrates by UHV-CVD. The samples contain a 0.2  $\mu$ m LT-Si buffer layer grown at 425 °C on the substrate followed by 0.7  $\mu$ m of SiGe grown at 525 °C. (a) and (b) show the bright field (200) cross-section and (022) plan-view TEM of a Si<sub>0.7</sub>Ge<sub>0.3</sub> layer, respectively. (c) shows the cross section of a Si<sub>0.6</sub>Ge<sub>0.4</sub> layer.

without the LT-Si buffer layer. It is evident in the sample with the LT-Si buffer layer, Fig. 1(b), most or all of the threading dislocations are prevented from propagating into the SiGe layer. These results, along with an examination by plan-view imaging of the same structure, indicate that the threading dislocation density is  $\leq 10^4~{\rm cm}^{-2}$  in the SiGe epilayer. Room-temperature Hall measurements were performed on 1  $\mu m$  thick boron doped  $(3.4\pm1.8\times10^{17}~{\rm cm}^{-3})$  Si\_0.7Ge\_0.3 samples. The hole mobility increased from 160  $\pm18~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  to  $200\pm2.5~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  by including the LT-Si buffer layer.

Motivated by these results, we then examined the effectiveness of the LT-Si buffer layer for several relaxed  $Si_{1-x}Ge_x$  samples with varying x grown on (100)  $p^+$  Si substrates by UHV-CVD. Ultralarge scale integration grade silane (100%) and germane (10% in helium) were used as material gas sources. The samples consist of an initial 0.2  $\mu$ m LT-Si buffer layer grown at 425 °C followed by 0.7  $\mu$ m  $Si_{0.7}Ge_{0.3}$  and  $Si_{0.6}Ge_{0.4}$ , respectively, grown at 525 °C. Bright field (200) cross-section and (022) plan-view imaging of the Si<sub>0.7</sub>Ge<sub>0.3</sub> sample, shown in Figs. 2(a) and 2(b), indicate a near defect-free SiGe region. The bright field (022) plan-view image of the same sample, shown in Fig. 2(b), indicates that the dislocations are contained within the LT-Si buffer layer. For higher (40%) Ge containing samples, as shown in Fig. 2(c), optimization of the LT-Si buffer layer thickness for minimizing the threading dislocation density is under investigation.

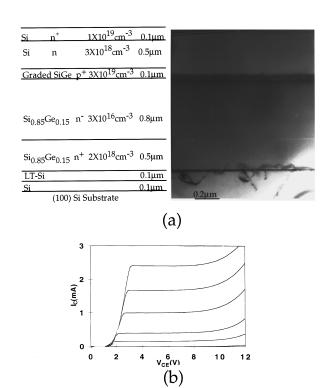

FIG. 3. (a) Cross-section TEM image and (b) dc common-emitter current-voltage characteristics of a n-p-n SiGe/Si bipolar transistor grown with the LT-Si buffer grown at MBE.

Double crystal x-ray measurements of the  $\mathrm{Si}_{0.85}\mathrm{Ge}_{0.15}$  layer without and with LT-Si buffer layers show that the width (full width at half-maximum) of the rocking curve corresponding to the alloy peak is reduced from 450 arc s to 371 arc s, respectively.

The mechanism for threading dislocation reduction is still under investigation. We suspect that because of the low growth temperature, a large number of point defects are generated in the LT-Si buffer layer. As the misfit dislocations propagate through the LT-Si layer, they become trapped by the defects and are annihilated.

From Fig. 1(b), one should note the existance of threading dislocations in the substrate region just below the LT-Si buffer layer. We believe that the threading dislocations found deep inside the substrate are generated from the activation of Frank–Read sources, which can relieve the strain in the SiGe epilayer. The bowing mechanism is also observed in samples using graded layers and superlattices to relieve strain. 10,19

We have grown and fabricated preliminary SiGe/Si n-p-n HBTs with LT-Si buffer layers. The complete heterostructure is shown in Fig. 3(a). It can be seen that the active region of the structure is defect-free although the area of  $10\times10~\mu\text{m}^2$  is shown in Fig. 3(b). The dc current gain is  $\sim6$  and the breakdown voltage is more than 10 V. The  $V_{ce}$  offset voltage is  $\sim1.5$  V and the Early voltage is approximately 1000 V.

Recent reports have shown that higher electron mobilities are measured in strained Si grown on relaxed SiGe than in bulk Si due to band splitting at the SiGe/Si heterojunction. Strained Si surface channel *n*-metaloxide-semiconductor field-effect transistors grown on re-

laxed SiGe, which exploit the LT-Si buffer layer are being investigated.

In conclusion, we have investigated a new defect density reduction method for SiGe heterostructures that uses a LT-Si buffer layer. Both gas-source MBE and UHV-CVD technologies have demonstrated threading dislocation densities as low as  $10^4$  cm<sup>-2</sup>. Preliminary SiGe/Si n-p-n HBTs exploiting the LT-Si buffer layer have been grown and fabricated.

The work is supported by the Air Force Office of Scientific Research under Grant No. F49620-95-1-0013 and by an AASERT Fellowship (AFOSR) under Grant No. F49620-94-0404.

- <sup>1</sup> A. Pruijmboom, J. W. Slotboom, D. J. Gravesteijn, C. W. Fredriksz, A. A. van Gorkum, R. A. van de Heuvel, J. M. L. van Rooij-Mulder, G. Streutker, and G. F. A. van de Walle, Electron. Device Lett. **12**, 357 (1991).

- <sup>2</sup> K. Ismail, S. F. Nelson, J. O. Chu, and B. S. Meyerson, Appl. Phys. Lett. **63**, 660 (1993).

- <sup>3</sup> K. Ismail, J. O. Chu, and B. S. Meyerson, Appl. Phys. Lett. **64**, 3124 (1994).

- <sup>4</sup>K. Ismail, B. S. Meyerson, and P. J. Wang, Appl. Phys. Lett. **58**, 2117 (1991).

- <sup>5</sup> K. D. Hobart, F. J. Kub, N. A. Papanicoloau, W. Kruppa, and P. E. Thompson, J. Cryst. Growth 157, 2115 (1995).

- <sup>6</sup> K. Ismail, F. K. LeGoues, K. L. Saenger, M. Arafa, J. O. Chu, P. M. Mooney, and B. S. Meyerson, Phys. Rev. Lett. **73**, 3447 (1994).

- <sup>7</sup>P. M. Mooney, J. L. Jordan-Sweet, J. O. Chu, and F. K. LeGoues, Appl. Phys. Lett. **66**, 3642 (1995).

- <sup>8</sup> M. A. Lutz, R. M. Feenstra, F. K. LeGoues, P. M. Mooney, and J. O. Chu, Appl. Phys. Lett. **66**, 724 (1995).

- <sup>9</sup>J. H. Li, V. Holy, G. Bauer, J. F. Nützel, and G. Abstreiter, Appl. Phys. Lett. 67, 789 (1995).

- <sup>10</sup> F. K. LeGoues, B. S. Meyerson, and J. F. Morar, Phys. Rev. Lett. **66**, 2903 (1991)

- <sup>11</sup>R. Hull, J. C. Bean, R. E. Leibenguth, and D. J. Werder, J. Appl. Phys. 65, 4723 (1989).

- <sup>12</sup>G. Kissinger, T. Morgenstern, G. Morgenstern, and H. Richter, Appl. Phys. Lett. 66, 2083 (1995).

- <sup>13</sup>F. K. LeGoues, Phys. Rev. Lett. **72**, 876 (1994).

- <sup>14</sup> H. Chen, L. W. Guo, Q. Cui, Q. Hu, Q. Huang, and J. M. Zhou, J. Appl. Phys. **79**, 1167 (1996).

- <sup>15</sup> J. M. Fernandez, J. Chen, and H. H. Weider, J. Vac. Sci. Technol. A 11, 889 (1993).

- <sup>16</sup>E. Scheid, L. K. Kouassi, R. Henda, J. Samitier, and J. R. Morante, Mater. Sci. Eng. B 17, 185 (1993).

- <sup>17</sup>E. Kasper, H.-J. Herzog, and H. Kibbel, Appl. Phys. **8**, 199 (1975).

- <sup>18</sup> J. P. Hirthe and J. Lothe, *Theory of Dislocations*, 2nd ed. (Wiley, New York, 1982).

- <sup>19</sup>B. S. Myerson, K. J. Uram, and F. K. LeGoues, Appl. Phys. Lett. **53**, 2555 (1988)

- <sup>20</sup>T. Vogelsang and K. R. Hofmann, Appl. Phys. Lett. **63**, 186 (1993).

- <sup>21</sup>D. Nayak and S. K. Chun, Appl. Phys. Lett. **64**, 2514 (1994).