# Performance-Driven Energy-Efficient VLSI

by

Wei-Hsiang Ma

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2011

### Doctoral Committee:

Professor Marios C. Papaefthymiou, Chair Professor Dennis M. Sylvester Associate Professor Jerome P. Lynch Assistant Professor Zhengya Zhang © Wei-Hsiang Ma 2011

All Rights Reserved

$To\ my\ family\ and\ friends\ for\ their\ love\ and\ support$

### ACKNOWLEDGMENTS

First and foremost I offer my sincerest gratitude to my advisor, Prof. Marios Papaefthymiou, who has supported me throughout my thesis with his patience and knowledge while allowing me the room to work in my own way. I would also like to thank all the other committee members, Prof. Dennis Sylvester, Prof. Zhengya Zhang, and Prof. Jerome Lynch, providing valuable feedback and support.

I want to thank Jerry Kao, who as a good friend and group mate of mine as always willing to help and give his best suggestions. It would have been a lonely office without him. Many thanks to Visvesh, Carlos, Yu-Shiang, Juang-Ying, and Tai-Chuan for sharing their time and expertise. Thanks to the program coordinator Beth Stalnaker and the ACAL/DCO staffs: Denise, Bert, Lauri, Steve, Ed, and Joel for their immense help.

Finally, I would like to thank my parents. They are always supporting me and encouraging me with their best wishes.

# TABLE OF CONTENTS

| DEDICATIO   | N                                                | ii   |

|-------------|--------------------------------------------------|------|

| ACKNOWLE    | EDGMENTS                                         | iii  |

| LIST OF FIG | URES                                             | vii  |

| LIST OF TAI | BLES                                             | xi   |

| LIST OF AP  | PENDICES                                         | xii  |

| LIST OF AB  | BREVIATIONS                                      | xiii |

| ABSTRACT    |                                                  | XV   |

| CHAPTER     |                                                  |      |

| 1 Intro     | duction                                          | 1    |

| 1.1         | Principles of Charge-Recovery Design Techniques  | 3    |

| 1.2         | LC Oscillation and Power-Clock                   | 7    |

| 1.3         | Power-Clock Generator                            | 9    |

| 1.4         | Charge-Recovery Systems                          | 12   |

|             | 1.4.1 Fine-grain Systems                         | 12   |

|             | 1.4.2 Coarse-grain Systems                       | 16   |

| 1.5         | Contributions                                    | 17   |

|             | 1.5.1 SBL and SBL-Based FIR Filter Design        | 18   |

|             | 1.5.2 Flash ADC with Resonant Clock Distribution | 19   |

| 1.6         | Thesis Outline                                   | 19   |

| 2 Backs     | ground                                           | 21   |

| 2.1         | Reversible Systems                               | 21   |

|             | 2.1.1 Reversible Computing                       | 21   |

|             | 2.1.2 Reversible Logic                           | 22   |

| 2.2         | Charge-Recovery Logic                            | 24   |

|   | 2.3         | Resonant-Clocked Designs                              | 31 |

|---|-------------|-------------------------------------------------------|----|

| 3 | Subth       | reshold Boost Logic                                   | 37 |

|   | 3.1         | Introduction                                          | 37 |

|   | 3.2         | SBL Overview and Blip Clock Generator                 | 39 |

|   | 3.3         | SBL Operation                                         | 41 |

|   | 3.4         | SBL Energetics                                        | 43 |

|   | 3.5         | Summary                                               | 48 |

| 4 | 187M        | Hz Charge-Recovery FIR Filter with Subthreshold Boost |    |

|   | Logic       |                                                       | 49 |

|   | 4.1         | FIR Filter Architecture                               | 50 |

|   | 4.2         | Power-Clock Generator and Clock Network Design        | 52 |

|   | 4.3         | SBL FIR Filter Design Methodology                     | 54 |

|   | 4.4         | SBL FIR Filter Spice-Level Analysis                   | 55 |

|   |             | 4.4.1 Spice Simulation Results                        | 55 |

|   |             | 4.4.2 Performance Comparison with CMOS FIR Filter     | 58 |

|   | 4.5         | SBL FIR Filter Test-Chip Measurement                  | 60 |

|   |             | 4.5.1 Single-Supply Configuration                     | 61 |

|   |             | 4.5.2 Two-Supply Configuration                        | 62 |

|   |             | 4.5.3 Energy Trade-off and Robustness Analysis        | 64 |

|   |             | 4.5.4 SBL FIR Filter Test-Chip Summary                | 66 |

|   | 4.6         | Summary                                               | 68 |

| 5 | Archi       | tecture and Design of Resonant-Clock Flash ADC        | 70 |

|   | 5.1         | Introduction                                          | 70 |

|   | 5.2         | Resonant-Clock Flash ADC Architecture                 | 71 |

|   | 5.3         | Resonant-Clock Flash ADC Building Blocks              | 72 |

|   |             | 5.3.1 Track-and-Hold Amplifier                        | 72 |

|   |             | 5.3.2 Comparators                                     | 73 |

|   |             | 5.3.3 Grey Code Encoder                               | 75 |

|   |             | 5.3.4 Sense-Amplifier Flip-Flop                       | 76 |

|   | 5.4         | Clock Network Design                                  | 77 |

|   | 5.5         | Inductor Design and Analysis                          | 79 |

| 6 | Evalu       | ation and Testing of 7GS/s Resonant-Clock Flash ADC   | 83 |

|   | 6.1         | Measurement Results                                   | 83 |

|   | 6.2         | Summary                                               | 91 |

|   | J. <u>-</u> | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~               | 91 |

| 7 | Concl       | usions and Future Directions                          | 03 |

| 7.2          | Subthreshold Boost Logic | 94  |

|--------------|--------------------------|-----|

| APPENDICE    | es                       | 98  |

| BIBLIOGRAPHY |                          | 111 |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                                                                                              |          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

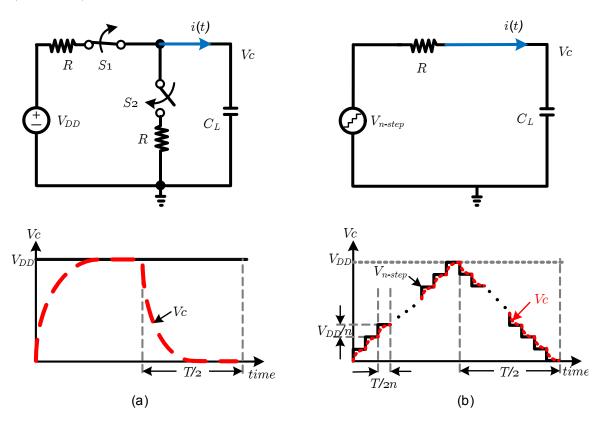

| 1.1           | Charging and discharging load capacitance using conventional and charge-recovery techniques: (a) First-order $RC$ network with DC supply. (b) First-order $RC$ network with $n$ -step supply | 4        |

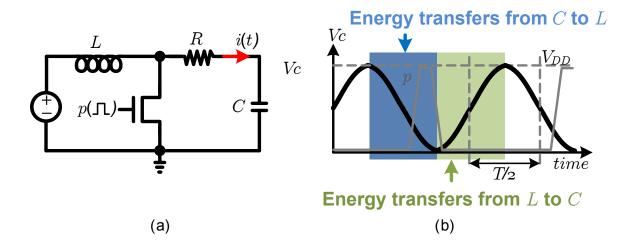

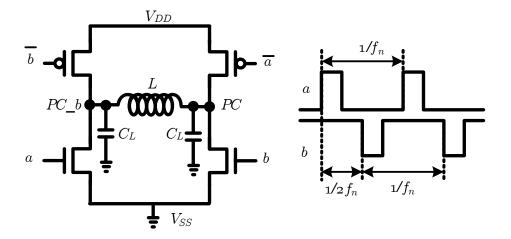

| 1.2           | Practical implementation of power-clock using an inductor: (a) Schematic (b) Waveform                                                                                                        | ic.<br>7 |

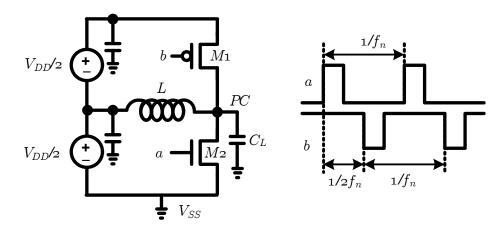

| 1.3           | A single-phase power-clock generator with two supplies                                                                                                                                       | S        |

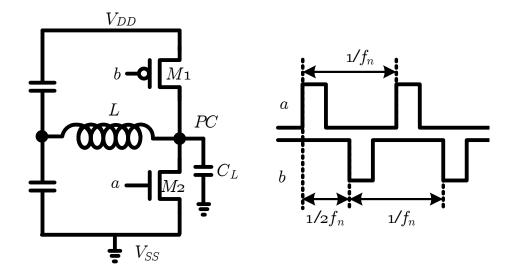

| 1.4           | A single-phase power-clock generator with single supply and a voltage divider                                                                                                                | 10       |

| 1.5           | H-bridge two-phase power-clock generator                                                                                                                                                     | 11       |

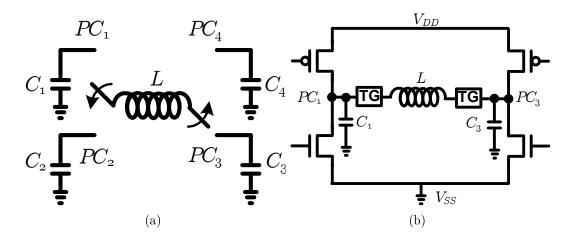

| 1.6           | (a) Basic scheme for a four-phase power-clock generator. (b) Circuit schematic related to $C1-C3$                                                                                            | 11       |

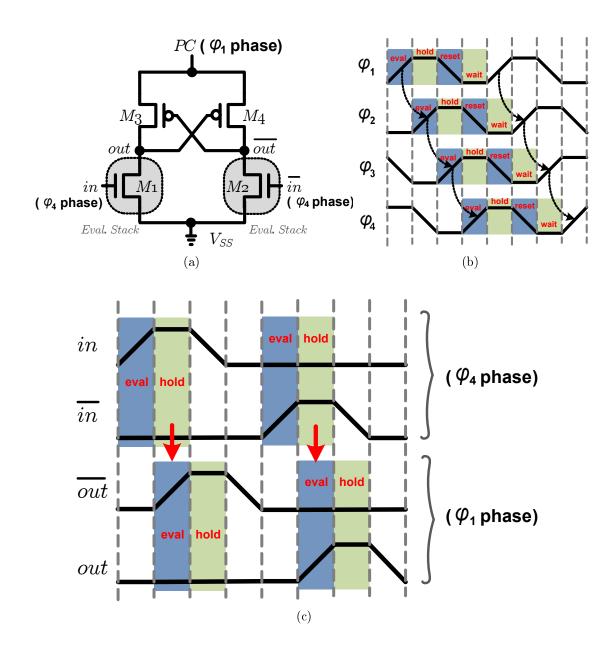

| 1.7           | (a) Schematic of 2N-2P inverter. (b) Four-phase power-clock waveforms. (c) Operating waveforms of 2N-2P inverter                                                                             | 14       |

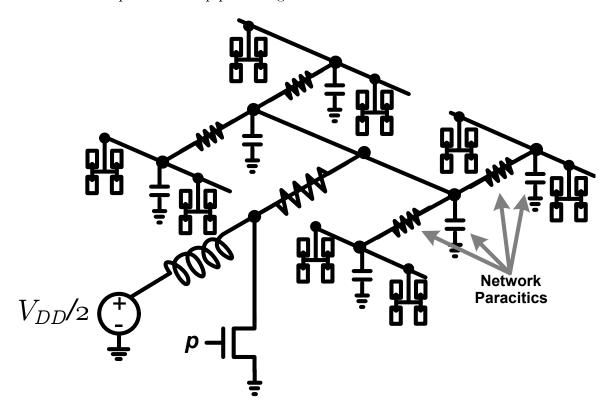

| 1.8           | Resonant-clocked pipeline example                                                                                                                                                            | 16       |

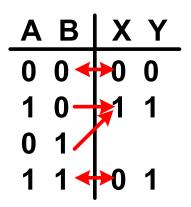

| 2.1           | Truth table of an irreversible gate                                                                                                                                                          | 23       |

| 2.2           | (a) Truth table and (b) symbol of the Feynman gate                                                                                                                                           | 24       |

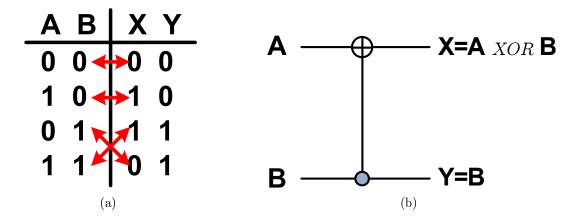

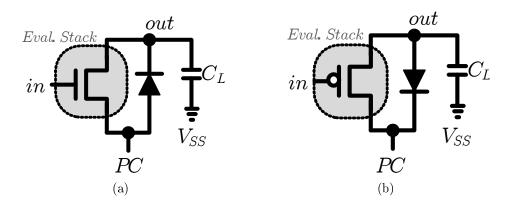

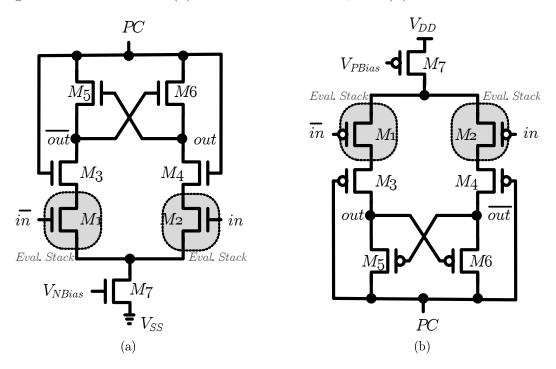

| 2.3           | Schematic of (a) NMOS ADL inverter, and (b) PMOS ADL inverter.                                                                                                                               | 25       |

| 2.4           | Schematic of QSERL inverter                                                                                                                                                                  | 26       |

| 2.5           | Schematic of 2N-2N2P inverter                                                                                                                                                                | 27       |

| 2.6  | Schematic of PAL inverter                                                                                          | 27 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | Schematic of PFAL inverter                                                                                         | 28 |

| 2.8  | Schematic of (a) NMOS TSEL inverter, and (b) PMOS TSEL inverter.                                                   | 29 |

| 2.9  | Schematic of (a) NMOS SCAL inverter, and (b) PMOS SCAL inverter.                                                   | 29 |

| 2.10 | Schematic of Boost Logic inverter                                                                                  | 30 |

| 2.11 | Schematic of Edge-Triggered (E-R) latch                                                                            | 32 |

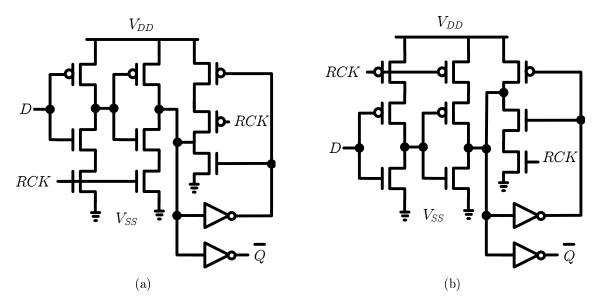

| 2.12 | Schematic of (a) pTERF flip-flop, and (b) nTERF flip-flop                                                          | 32 |

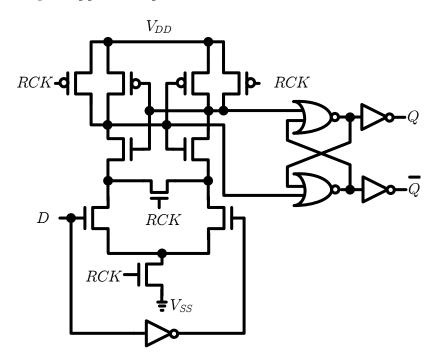

| 2.13 | Schematic of sense-amplifier flip-flop used in [1]                                                                 | 33 |

| 2.14 | Schematics of resonant-clocked latches used in RF1: (a) H-LAT, and (b) L-LAT                                       | 34 |

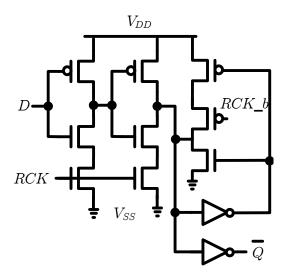

| 2.15 | Schematic of resonant-clocked latch used in RF1, B-LAT                                                             | 34 |

| 2.16 | Schematic of DESL inverter                                                                                         | 35 |

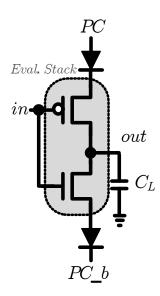

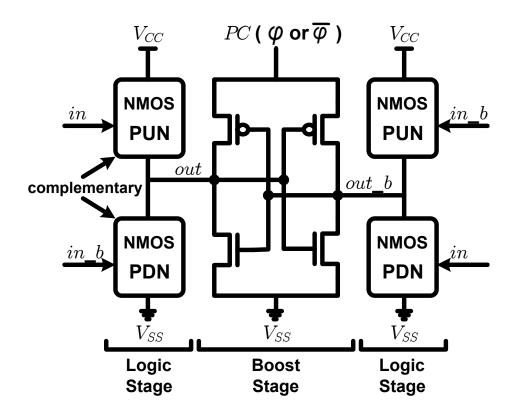

| 3.1  | Schematic of an SBL gate                                                                                           | 39 |

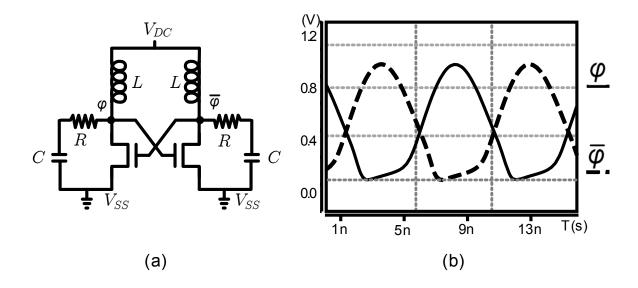

| 3.2  | Simple "blip" clock generator: (a) Schematic. (b) Waveform                                                         | 40 |

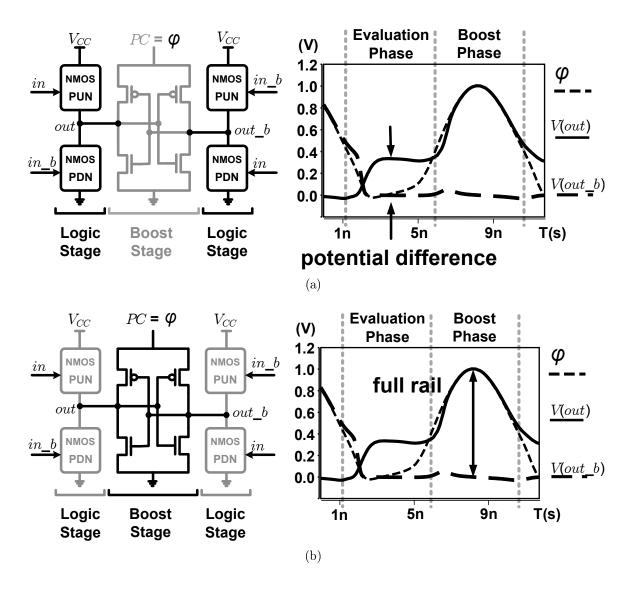

| 3.3  | SBL operation: (a) Evaluation Phase. (b) Boost Phase                                                               | 41 |

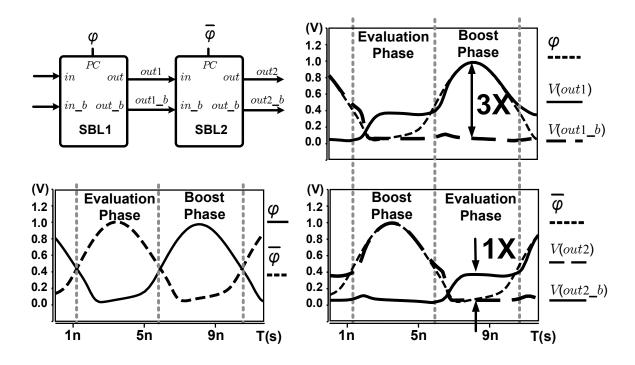

| 3.4  | Cascade of SBL gates                                                                                               | 42 |

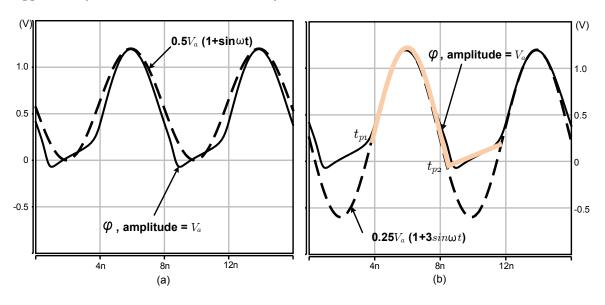

| 3.5  | Clock waveform modeling: (a) Sine clock with equal peak-to-peak swing. (b) Sine clock with 1.5X peak-to-peak swing | 44 |

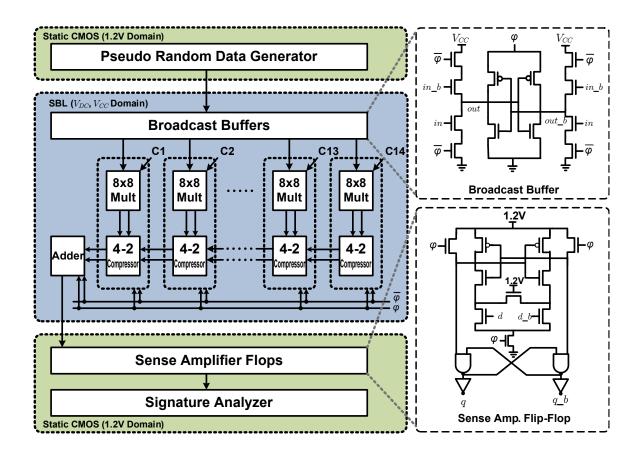

| 4.1  | Block diagram of SBL FIR filter and BIST circuits                                                                  | 50 |

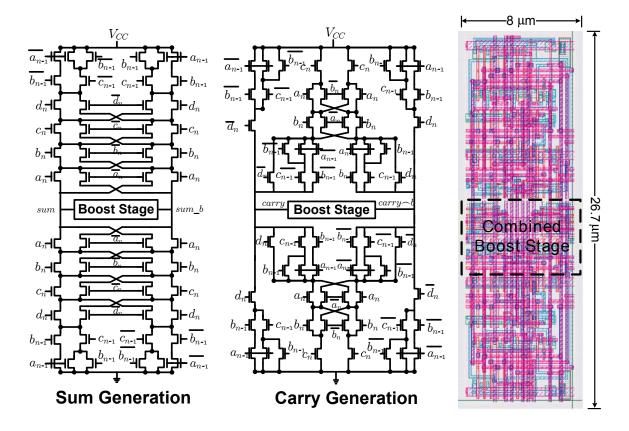

| 4.2  | Schematic and layout of a 4-2 compressor                                                                           | 51 |

| 4.3  | Distributed "blip" clock generator and measured clock waveform                                                     | 52 |

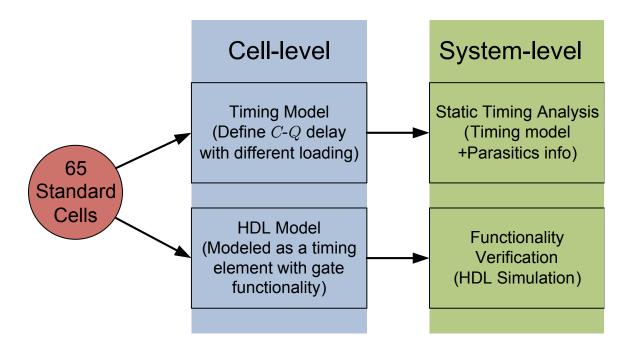

| 4.4  | SBL design flow                                                                                                    | 55 |

| 4.5  | Simulated energy consumption of SBL FIR filter                                                                     | 56 |

| 4.6  | frequency of 53.7MHz                                                                                                                                              | 57 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

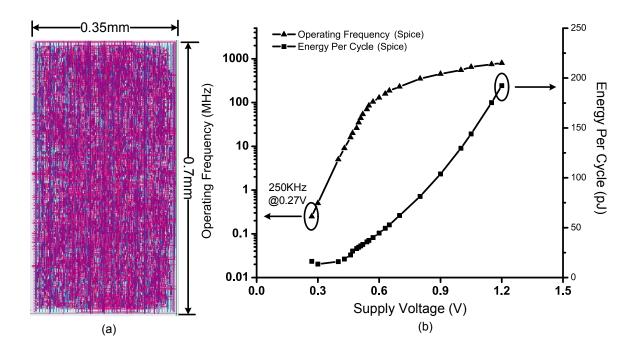

| 4.7  | (a) Layout of conventional CMOS FIR. (b) Simulated operating frequency and energy per cycle vs. supply voltage for conventional CMOS FIR filter                   | 58 |

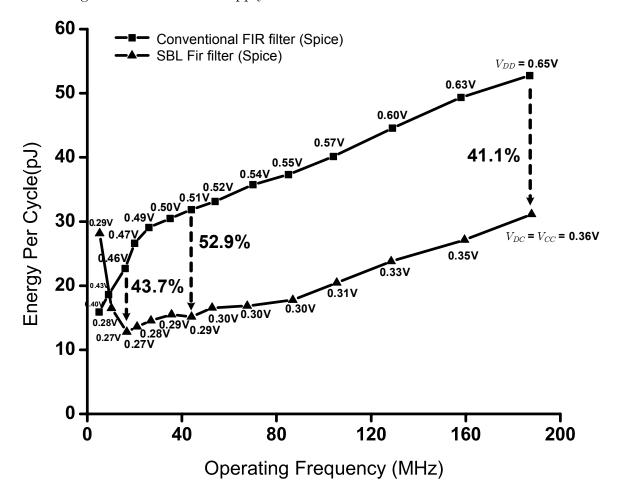

| 4.8  | Simulated energy consumption of conventional and SBL FIR filters.                                                                                                 | 59 |

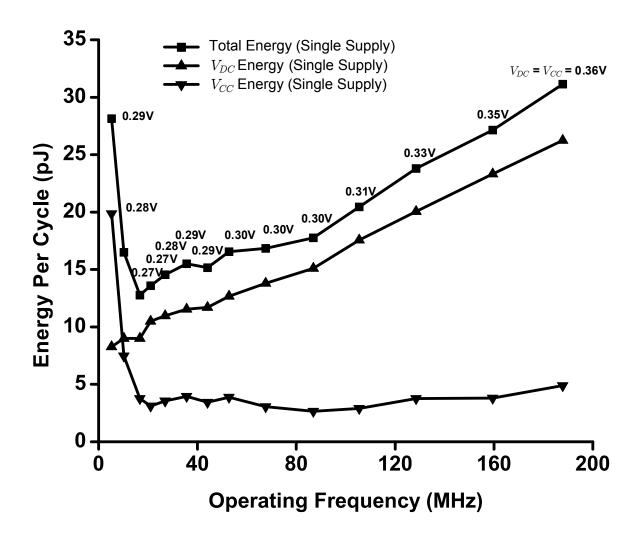

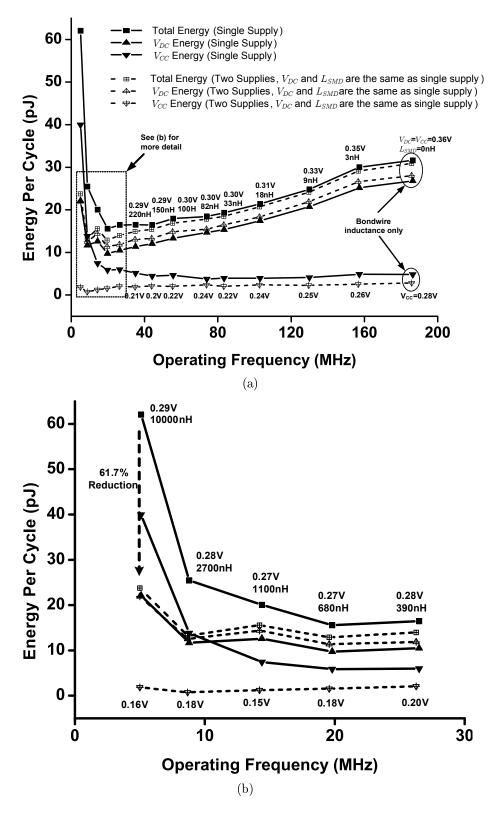

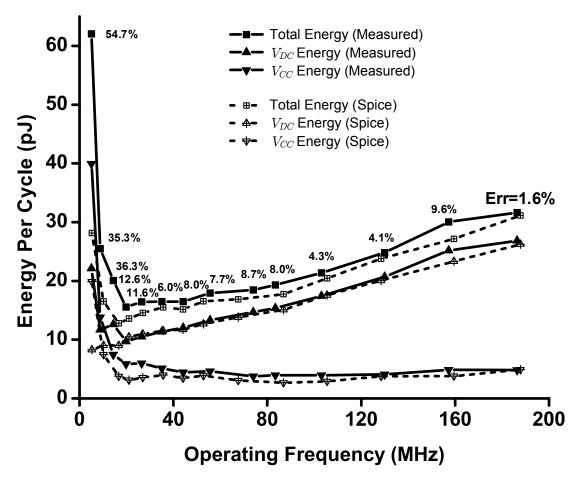

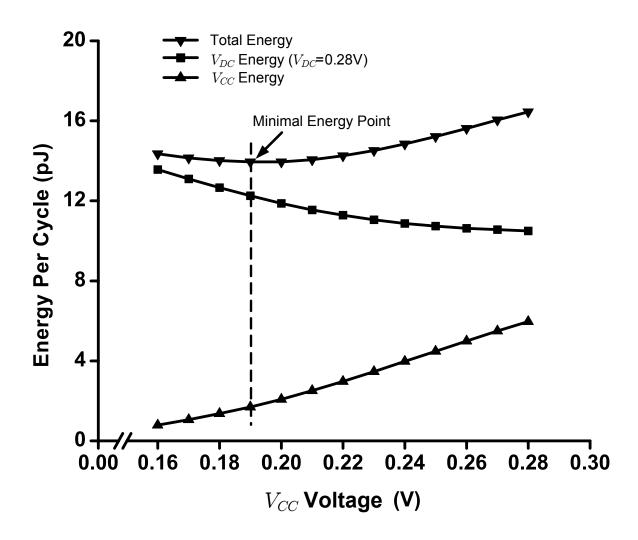

| 4.9  | Measured energy consumption vs. operating frequency for SBL FIR filter (single supply and two supplies)                                                           | 63 |

| 4.10 | Comparison of measured and simulated energy consumption for SBL FIR filter (single supply)                                                                        | 64 |

| 4.11 | Measured total energy consumption vs. $V_{CC}$ for the SBL FIR when operating at 26.4MHz with $V_{DC}=0.28$ V                                                     | 65 |

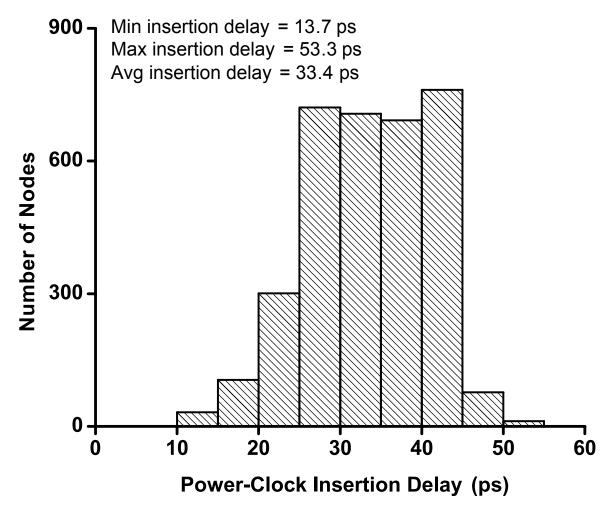

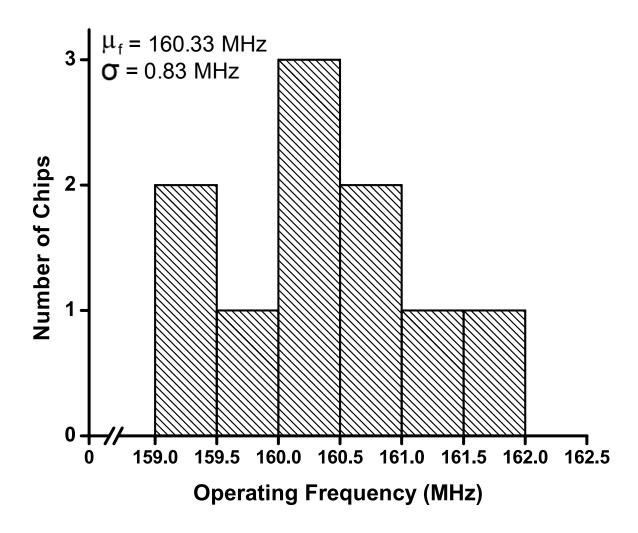

| 4.12 | Measured resonant frequency distribution at $V_{DC}=V_{CC}=0.36\mathrm{V}.$ .                                                                                     | 66 |

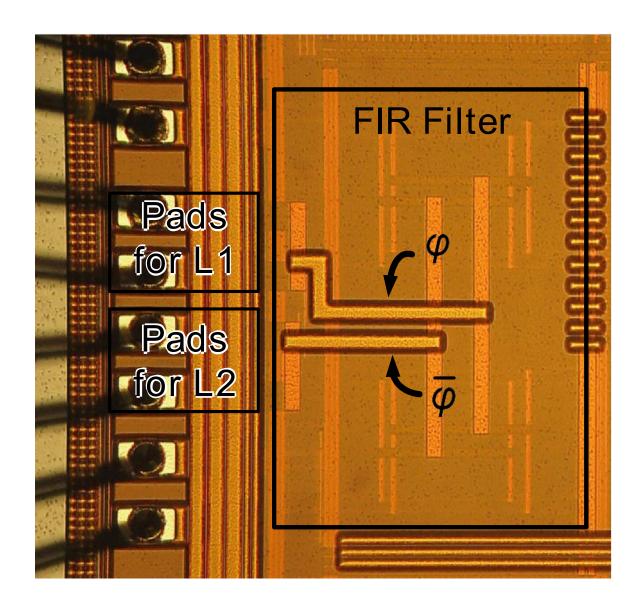

| 4.13 | SBL FIR die microphotograph.                                                                                                                                      | 68 |

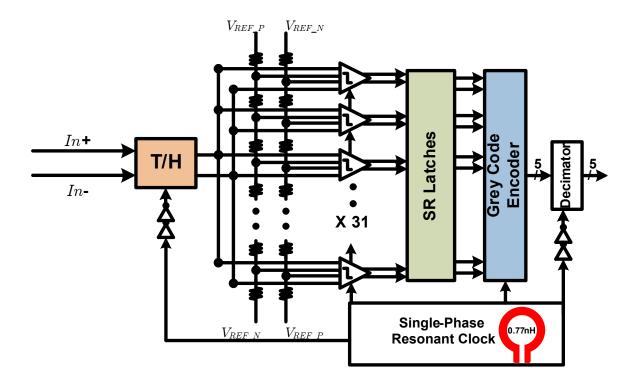

| 5.1  | Architecture of ADC with single-phase resonant clock                                                                                                              | 72 |

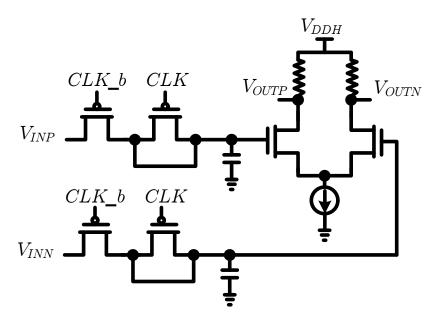

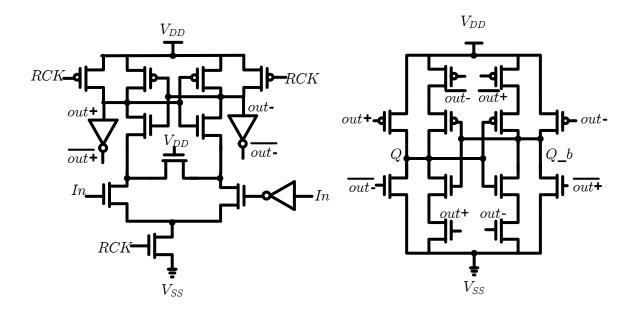

| 5.2  | Track-and-hold amplifier (THA) circuit                                                                                                                            | 73 |

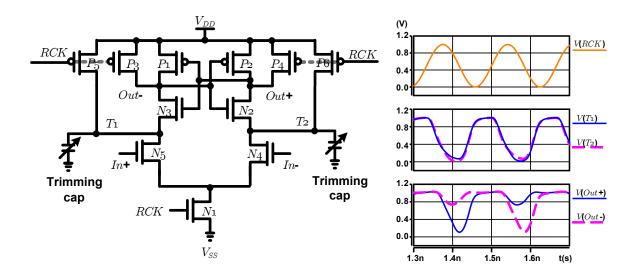

| 5.3  | Schematic of the comparator and waveform                                                                                                                          | 74 |

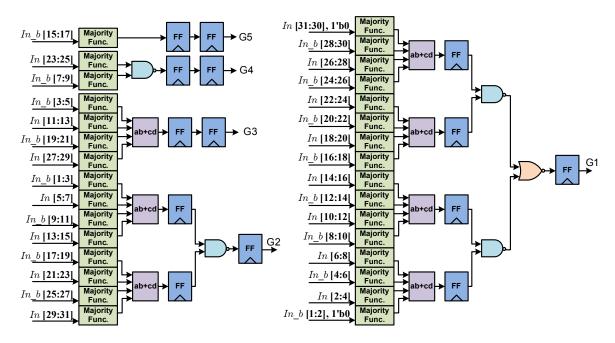

| 5.4  | Schematic of the 2-cycle resonant-clocked Gray code encoder                                                                                                       | 76 |

| 5.5  | Schematic of the sense-amplifier flip-flop                                                                                                                        | 77 |

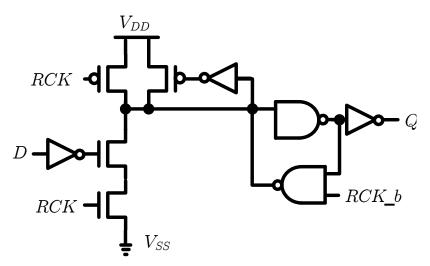

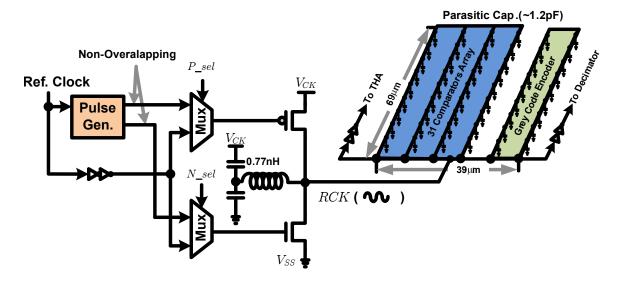

| 5.6  | Resonant clock generator with variable pulse controls                                                                                                             | 78 |

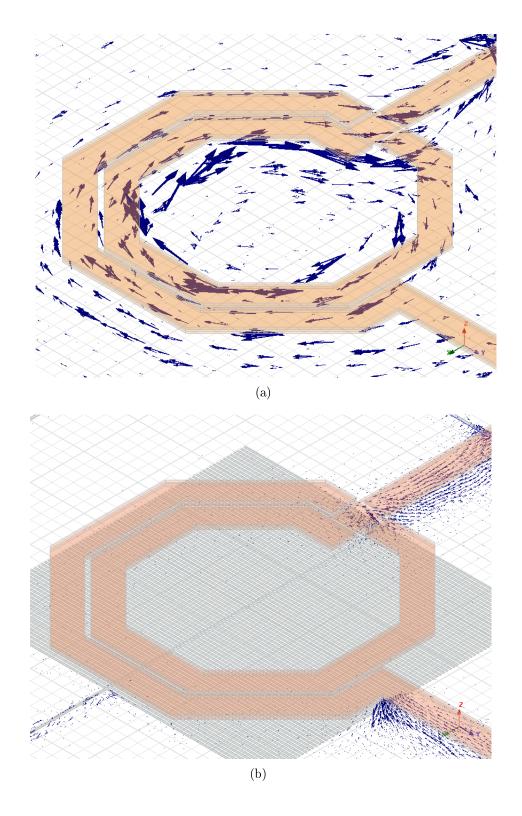

| 5.7  | Current density in the substrate underneath inductor: (a) without M1 shield, and (b) with M1 shield                                                               | 80 |

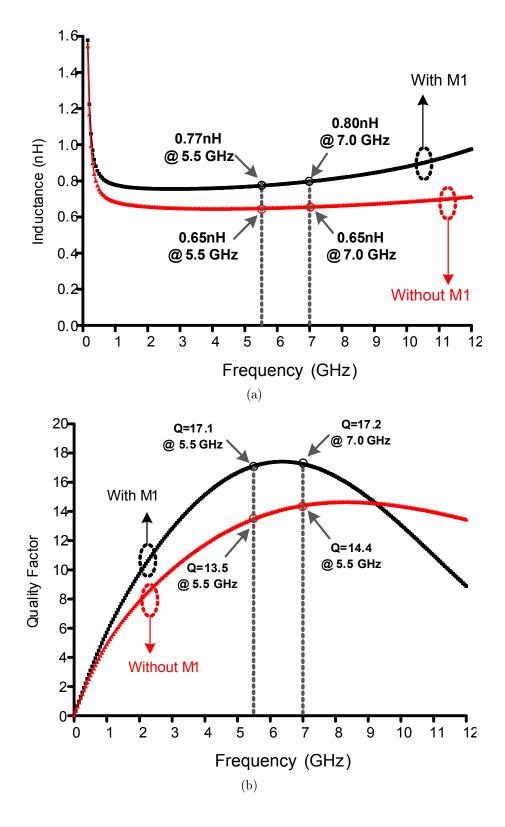

| 5.8  | <ul><li>(a) Inductance vs. resonant frequency with and without M1 shield.</li><li>(b) Quality factor vs. resonant frequency with and without M1 shield.</li></ul> | 81 |

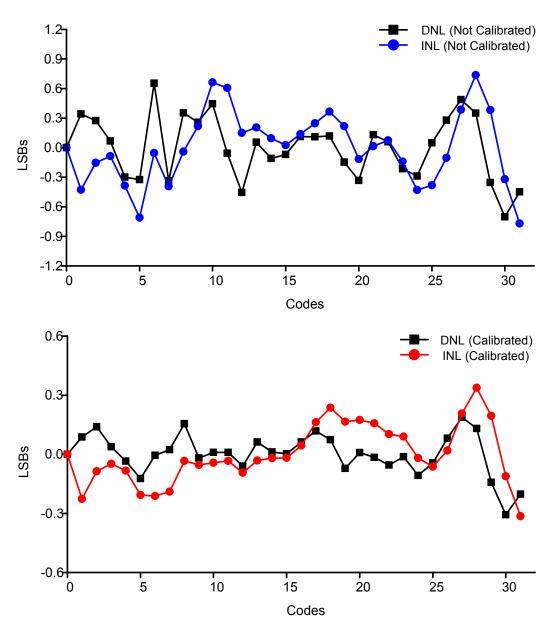

| 6.1  | Measured DNL/INL                                                                                                                                                  | 84 |

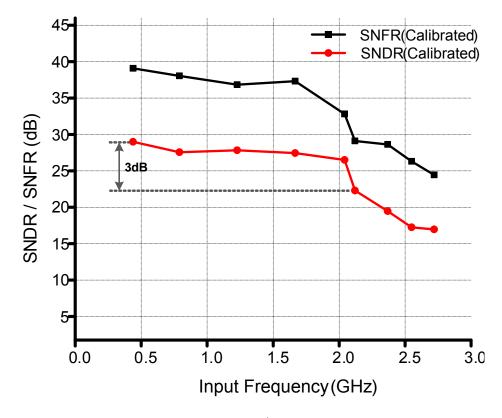

| 6.2  | Measured SNDR/SNFR vs. input frequency                                                                                                                            | 85 |

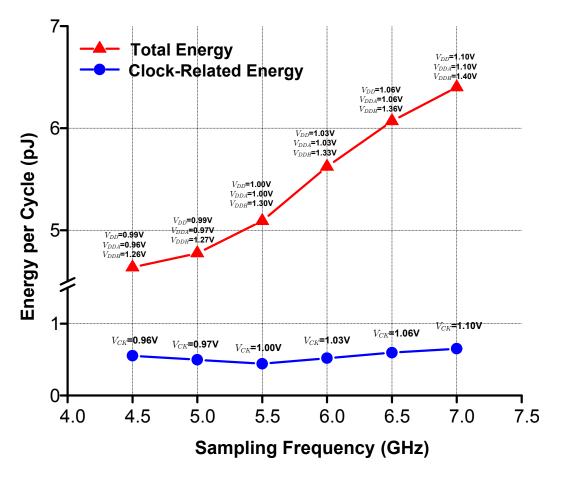

| 6.3  | Measured energy per cycle vs. sampling frequency                                                                                                                  | 86 |

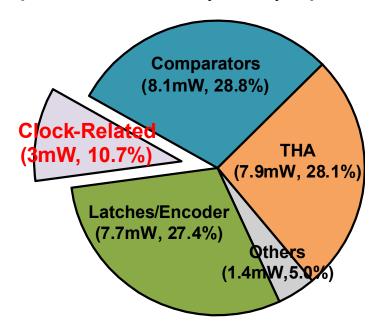

| 6.4 | Measured power breakdown at $5.5 \text{GS/s.} \dots \dots \dots \dots$                                           | 87   |

|-----|------------------------------------------------------------------------------------------------------------------|------|

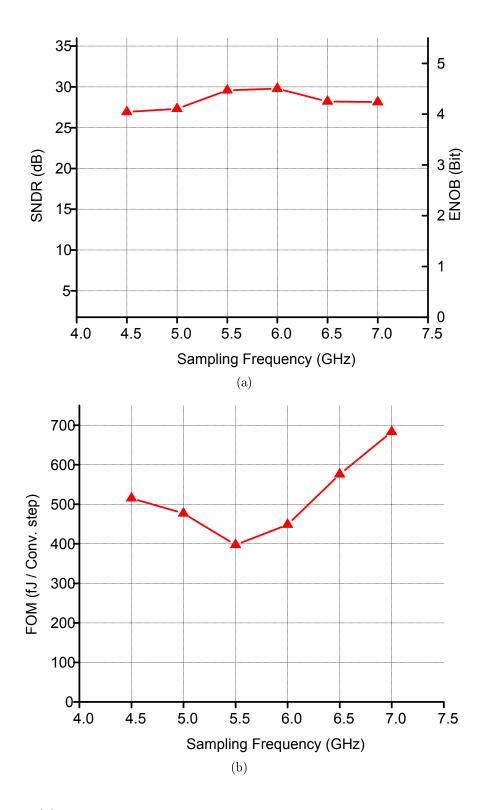

| 6.5 | (a) Measured SNDR vs. sampling frequency with input frequency of 400MHz. (b) Measured FoM vs. sampling frequency | 89   |

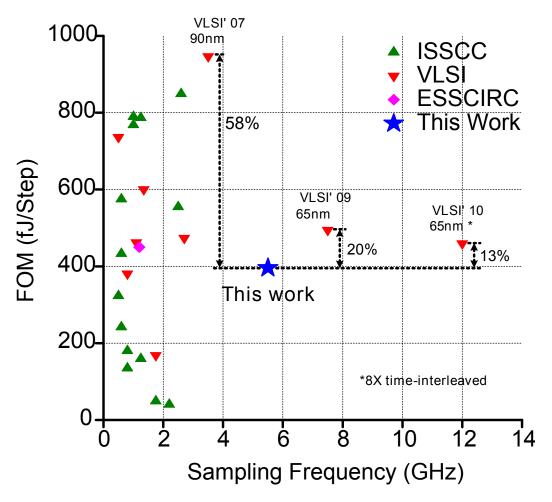

| 6.6 | FoM vs. sampling frequency: comparison to prior work summarized in [2]                                           | 91   |

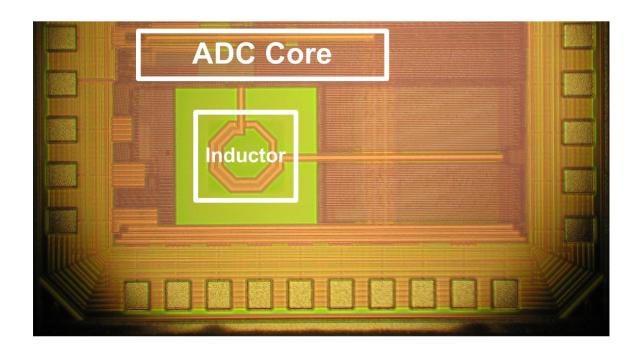

| 6.7 | ADC die microphotograph                                                                                          | 92   |

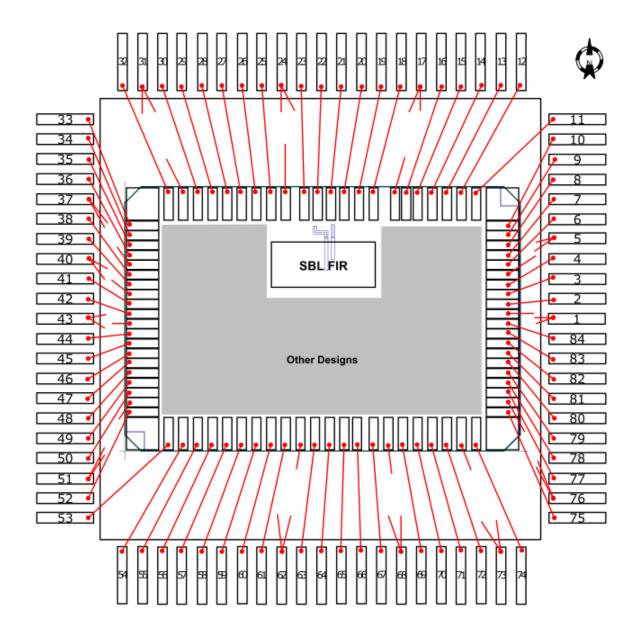

| A.1 | Bonding diagram for SBL FIR test-chip                                                                            | 100  |

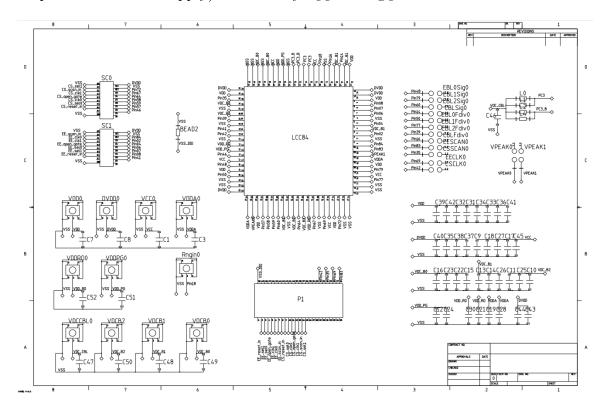

| A.2 | Schematic of the printed circuit board for SBL FIR test-chip                                                     | 102  |

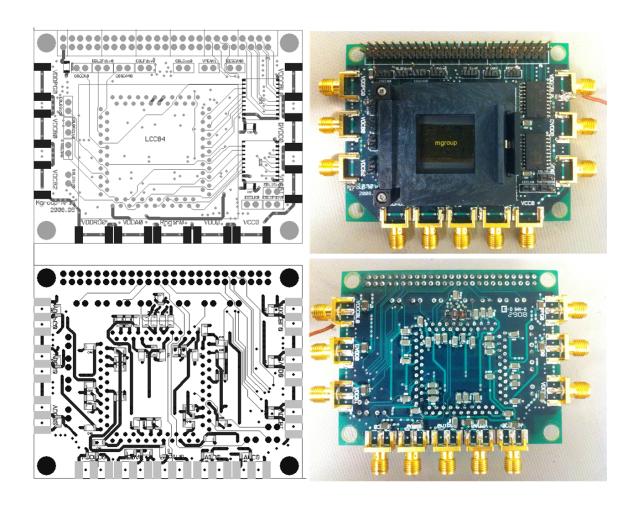

| A.3 | Printed circuit board for SBL FIR test-chip                                                                      | 104  |

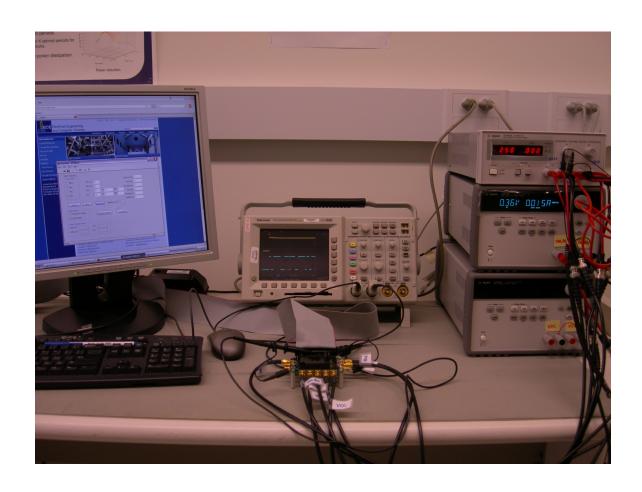

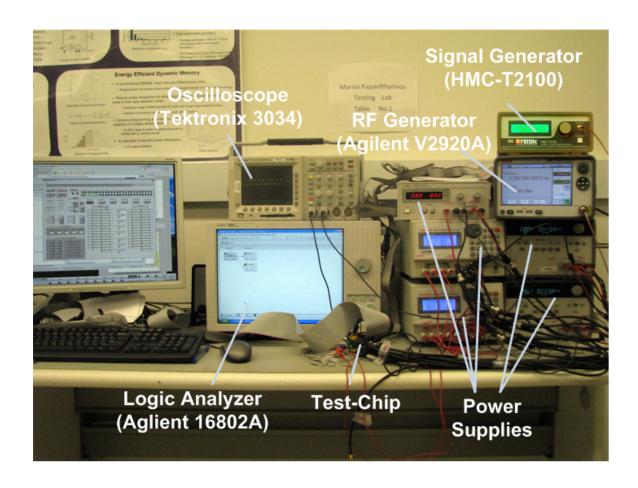

| A.4 | Test setup for SBL FIR test-chip                                                                                 | 105  |

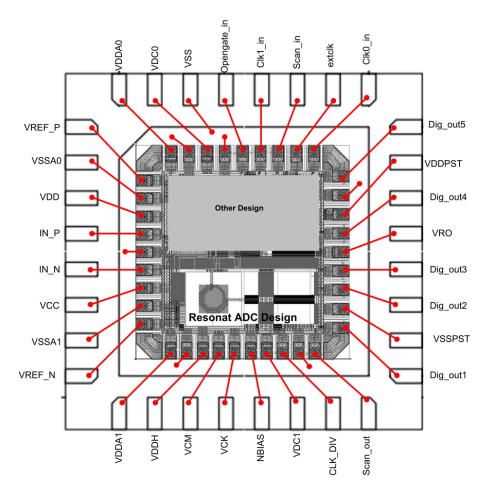

| B.1 | Bonding diagram for resonant-clock ADC test-chip                                                                 | 107  |

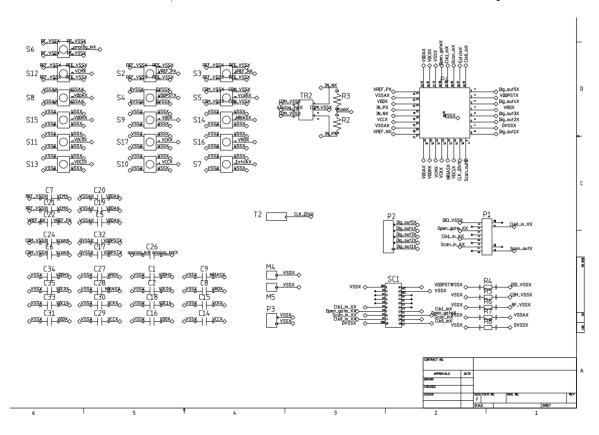

| B.2 | Schematic of the printed circuit board for resonant-clock ADC test-chip                                          | .108 |

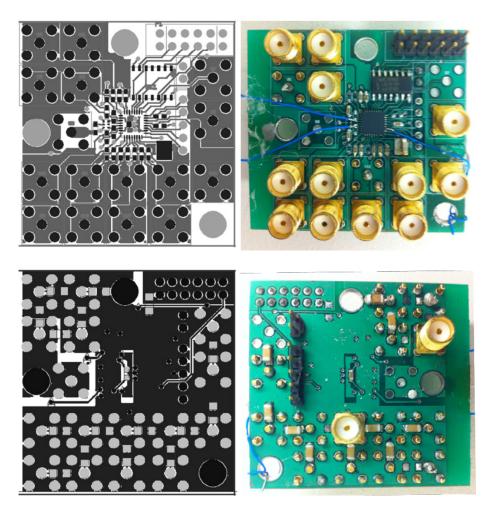

| В.3 | Printed circuit board for resonant-clock ADC test-chip                                                           | 109  |

| B.4 | Test setup for resonant-clock ADC test-chip                                                                      | 110  |

# LIST OF TABLES

| <u>Table</u> |                                                        |     |

|--------------|--------------------------------------------------------|-----|

| 4.1          | SBL FIR filter statistics and performance measurements | 60  |

| 4.2          | Performance table                                      | 67  |

| 6.1          | Performance summary                                    | 9(  |

| A.1          | I/O information for SBL FIR test-chip                  | 10  |

| A.2          | Parts list for SBL FIR test-chip                       | 103 |

| B.1          | I/O information for resonant-clock ADC test-chip       | 108 |

| B.2          | Parts list for resonant-clock ADC test-chip            | 109 |

## LIST OF APPENDICES

| Appe | $\frac{ndix}{dx}$                   |    |

|------|-------------------------------------|----|

| Α.   | Testing Setup for SBL FIR Test-Chip | 99 |

Testing Setup for Resonant-Clock Flash ADC Test-Chip . . . . . . .

106

В.

### LIST OF ABBREVIATIONS

ADC Analog-to-Digital Converter

ADL Adiabatic Dynamic Logic

**BIST** Built-in Self-Test

CMOS Complementary Metal-Oxide Semiconductor

dB Decibel

**DESL** Dynamic Evaluation Static Latch

**DNL** Differential Non-Linearity

**DSP** Digital Signal Processor

**ENOB** Effective Number of Bits

**ERBW** Effective Resolution Bandwidth

FIR Finite Impulse Response

**FOM** Figure of Merit

I/O Input/Output

**INL** Integral Non-Linearity

LCC Leadless Chip Carrier

LSB Least Significant Bit

MOS Metal-Oxide Semiconductor

nTERF NMOS Energy Recovery Flip-Flop

PAL Pass-transistor Adiabatic Logic

PC Power Clock

**PCB** Printed Circuit Board

PFAL Positive Feedback Adiabatic Logic

pterf PMOS Energy Recovery Flip-Flop

**QFN** Quad Flat No leads

**QSERL** Quasi-Static Energy Recovery Logic

**RCK** Resonant Clock

**RERL** Reversible Energy Recovery Logic

**SAFF** Sense-Amplifier Flip-Flop

SBL Subthreshold Boost Logic

SCAL Source-Coupled Adiabatic Logic

SCRL Split-level Charge Recovery Logic

**SMA** SubMiniature version A

**SMD** Surface Mount Devices

SNDR Signal to Noise and Distortion Ratio

SNFR Signal to Noise Floor Ratio

**THA** Track-and-Hold Amplifier

**TSEL** True Single-Phase Energy Recovery Logic

VLSI Vary Large Scale Integrated

ABSTRACT

Performance-Driven Energy-Efficient VLSI

by

Wei-Hsiang Ma

Chair: Marios C. Papaefthymiou

Today, there are two prevalent platforms in VLSI systems: high-performance and

ultra-low power. High-speed designs, usually operating at GHz level, provide the

required computation abilities to systems but also consume a large amount of power;

microprocessors and signal processing units are examples of this type of designs. For

ultra-low power designs, voltage scaling methods are usually used to reduce power

consumption and extend battery life. However, circuit delay in ultra-low power de-

signs increases exponentially, as voltage is scaled below Vth, and subthreshold leakage

energy also increases in a near-exponential fashion.

Many methods have been proposed to address key design challenges on these two

platforms, energy consumption in high-performance designs, and performance/reliability

in ultra-low power designs. In this thesis, charge recovery design is explored as a solu-

tion targeting both platforms to achieve increased energy efficiency over conventional

CMOS designs without compromising performance or reliability.

To improve performance while still achieving high energy efficiency for ultra-low

power designs, we propose Subthreshold Boost Logic (SBL), a new circuit family

that relies on charge recovery design techniques to achieve order-of-magnitude im-

XV

provements in operating frequencies, and achieve high energy efficiency compared to conventional subthreshold designs. To demonstrate the performance and energy efficiency of SBL, we present a 14-tap 8-bit finite-impulse response (FIR) filter test-chip fabricated in a  $0.13\mu m$  process. With a single 0.27V supply, the test-chip achieves its most energy efficient operating point at 20MHz, consuming 15.57pJ per cycle with a recovery rate of 89% and a figure of merit (FoM) equal to 17.37 nW/Tap/MHz/InBit/CoeffBit. In comparison with a static CMOS-based implementation derived by synthesis of the same FIR architecture and automatic place-and-route, the SBL-based FIR consumes 40% to 50% less energy per cycle in the 17MHz - 187MHz range.

To reduce energy consumption at multi-GHz level frequencies, we explore the application of resonant-clocking to the design of a 5-bit non-interleaved resonant-clock flash ADC with a sampling rate of 7GS/s. The ADC has been designed in a 65nm bulk CMOS process. An integrated 0.77nH inductor is used to resonate the entire clock distribution network to achieve energy-efficient operation. Operating at 5.5GHz, the ADC consumes 28mW, yielding 396fJ per conversion step. The clock network accounts for 10.7% of total power and consumes 54% less energy over  $CV^2$ . Operating at its maximum sampling frequency of 7.0GS/s with a 0.1V increase to each supply, the ADC dissipates 45mW. At this frequency, 11.1% of the total energy consumption is clock-related, and the ADC yields a FoM of 683fJ per conversion step. By comparison, in a typical flash ADC design, 30% of total power is clock-related.

### CHAPTER 1

### Introduction

Energy consumption has become a major design constraint in today's VLSI designs. For the last several decades, Moore's Law [3] has been the main driving force to reduce the size and energy consumption of silicon devices. However, this scaling does not reduce power consumption per unit area. As more devices can fit into a given area, and the heat generated increases. Heat removal at the package level limits further integration. Moreover, starting with 65nm, supply voltage no longer scales with device sizes, remaining essentially constant over past several years and foreseeable future. To make matters worse, leakage current increases due to the smaller device sizes. Therefore, one of the largest issues facing designers nowadays is energy and power dissipation. Their main challenge is to achieve energy efficient computing, extracting the maximum possible performance under a given power constraint.

Voltage scaling is one of the most effective methods for reducing energy consumption in digital circuits [4, 5, 6]. The energy consumption decreases quadratically when the supply voltage  $V_{DD}$  decreases, providing energy efficient operation. However, this energy-efficient operation comes at the expense of performance degradation. When voltage is scaled while remaining well above subthreshold  $(V_{DD} >> V_{th})$ , performance degradation is in approximately linear relationship with supply. When voltage is scaled deeper in the subthreshold regime  $(V_{DD} < V_{th})$ , circuit delay increases exposions.

nentially with  $V_{DD}$ , and becomes more sensitive to process variation. Leakage current also increases in a near-exponential fashion in the subthreshold regime. This rise in leakage energy eventually dominates total power consumption and creates a minimum energy operating point [4]. Further scaling beyond this minimum energy point results in total energy consumption increasing and yields diminished energy efficiency. Moreover, voltage scaling has its limitation on different applications. For example, in applications with constantly high workloads, voltage scaling can only help to a limited extent.

Charge-recovery is an alternative design approach that can reduce energy consumption by gradually charging/discharging capacitance and recycling the charge at the end of each cycle [7, 8, 9, 10]. The energy dissipation of a traditional CMOS circuit that goes through a charge or a discharge cycle is governed by the equation  $E_{conv} = switching \ activity \times CV^2$ , while the corresponding energy dissipation of a charge-recovery system is governed by  $E_{charge-recovery} = (K/T)CV^2$ , where T is the duration of the transition and K is a constant proportional to the RC constant of the system. Similar to voltage scaling, charge-recovery exhibits a trade-off relationship between energy consumption and computation delay, but this trade-off relation is linear. A large volume of previous work has been proposed based on this trade-off, improving the energy efficiency at the cost of system performance, focusing on achieving high energy efficiency in relatively low-performance designs. However, this trade-off dose not limit the design scope of charge-recovery techniques. In fact, charge-recovery design techniques can enable different design points compared to conventional static CMOS techniques. In principle, these design points could lead to better energy/performance trade-offs than conventional CMOS design.

This thesis argues that charge-recovery techniques can be used to design VLSI systems that achieve both high energy efficiency and high performance. To support this proposition, two charge-recovery systems operating at different frequency points are demonstrated. Both designs provide high performance at their corresponding supply-levels and achieve higher energy efficiency than their conventional CMOS designs counterparts. For ultra-low energy consumption with high performance, we present a novel fine-grain charge-recovery circuitry that uses a single subthreshold-level supply. By amplifying the internal subthreshold-level signals with a two-phase power-clock, this charge-recovery circuitry relies on gate overdrive to enable fast operation while improving robustness to the variations. In addition, it can share the same supply with the clock generator, allowing operation with a single DC supply level. An 8×8 bit 14-tap finite impulse response (FIR) filter is used to demonstrate the high energy efficiency of this logic, across the 5MHz-187MHz frequency range with a subthreshold supply ranging from 0.16V to 0.36V. This design achieves a higher Figure of Merit (FoM) than previous implementations of the same architecture in charge-recovery logic and in static CMOS.

For high performance and high energy efficiency, we present a coarse-grain resonant-clock flash ADC structure. In this design, resonant-clocking is used to decrease the energy consumption of the network that distributes the clock signal to the analog and digital circuitry of the flash ADC. A 5-bit non-interleaved flash ADC that achieves a sampling frequency range of 4.5GS/s-7GS/s is used to demonstrate the high energy efficiency of resonant-clocking techniques. An integrated inductor is used to resonate the capacitance of the entire clock distribution network at a target operating frequency range. This work achieves a lower FoM than all previously published ADCs operating above 2.2GHz.

## 1.1 Principles of Charge-Recovery Design Techniques

This section describes the principles of charge-recovery techniques as applied to digital circuit designs. In digital circuits, a MOS transistor is usually used as a switch with one node connected to supply  $(V_{DD})$  / ground  $(V_{SS})$  and the other node

connected to a capacitive load C. By observing the voltage level of the load, we can determine the logic state of a gate. By turning the transistor on, we can charge (discharge) the voltage level of the load and thus change the logic state of a gate.

Figure 1.1: Charging and discharging load capacitance using conventional and charge-recovery techniques: (a) First-order RC network with DC supply. (b) First-order RC network with n-step supply.

For simplicity, we can model digital circuits as first-order RC networks, as shown in Figure 1.1(a). In such a network, a capacitive load  $C_L$  is charged and discharged through transistors which are modeled as a resistor R. By turning on switch S1 and turning off switch S2, supply  $V_{DD}$  starts to charge the load  $C_L$  from  $V_{SS}$  to  $V_{DD}$ , and the voltage level at node  $V_{out}$  ramps up as an function of  $V_{DD}(1 - e^{-t/RC})$ , where t is the transition time. The total energy dissipation in the circuit can be obtained by integrating the instantaneous power dissipation on the resistive device,  $I^2R$ , over the charging time of  $C_L$ :

$$E = \int_{0}^{\infty} i_{C}(t)v_{out}(t) dt$$

$$= \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} v_{out} dt$$

$$= C_{L} \int_{0}^{V} v_{out} dv_{out}$$

$$= \frac{C_{L}V^{2}}{2}.$$

(1.1)

The total energy drawn from the supply during charge is equal to the sum of the energy stored in  $C_L$ ,  $\frac{1}{2}C_LV^2$ , and the energy loss on the resistor R,  $\frac{1}{2}C_LV^2$ .

Figure 1.1(b) illustrates how to charge and discharge  $C_L$  in a charge-recovery manner. In this figure, an n-step voltage source is used as an example. In practice, a supply could be a resonant source capable of reclaiming charge and re-using it for subsequent charging. This n-step source has a voltage of  $V_{DD}/n$  for each step and time interval of T/2n. While charging the capacitor, we assume that the time constant  $RC_L$  is much smaller than the time interval T/2n. This means that the output  $C_L$  can be charged to the same level of the supply during each time interval T/2n. To calculate the energy consumption in Figure 1.1(b) during charging, we apply Equation (1.1), and total energy dissipation is found to be

$$E = Energy \ Dissipation \ per \ Step \times n$$

$$= \frac{C_L(\frac{V}{n})^2}{2} \cdot n$$

$$= \frac{C_L V^2}{2} \cdot \frac{1}{n}.$$

(1.2)

The total energy drawn from the supply during charging phase is equal to the sum

of the energy stored in  $C_L$ ,  $\frac{1}{2}C_LV^2$ , and the energy loss on the resistor R,  $\frac{1}{2}C_LV^2$ .  $\frac{1}{n}$ . Unlike conventional CMOS circuits, energy loss for the circuit in Figure 1.1(b) decreases by a coefficient of  $\frac{1}{n}$ .

When discharging the capacitive load  $C_L$  with the same n-step source, the charge stored in the capacitive load  $C_L$  flows back to the source, and the amount of energy loss on resistor R is the same as when charging  $C_L$ . A typical voltage supply will shunt any returned energy to ground, dissipating it across some resistance, and rendering the charge-recovery discharging no more energy efficient than the conventional case. However, if the supply is, for example, a resonant source, it will be able to reclaim the returned charge and use it for subsequent charging. This discharging method is called charge recovery because the energy transferred to the capacitor is recovered and reused by the supply.

As the number of steps n approaches infinity, the dissipation approaches zero; however, large n also means small charge time T/2n. If T/2n is small enough compared to the time constant  $RC_L$  of the circuit, the switching event may not be completed and the result in Equation (1.2) is no longer valid. Since n is related to the energy savings of the circuit, we conclude that there is a trade-off between time (T) and energy dissipation (E). This energy-time trade-off forms the basis of charge-recovery techniques.

Equation (1.2) implies that gradual transitioning is the key to achieve energy-efficient charge-recovery operation. Gradual transition reduces the potential difference across the resistive element, results in a low-level current flow, and thus minimizes energy dissipation.

It should be noticed that in most charge-recovery systems, the power supply performs a dual role, providing charge to internal circuit nodes, and synchronizing the computation of the gate. For this reason, such a power supply is usually referred to as a Power-Clock (PC).

### 1.2 LC Oscillation and Power-Clock

Figure 1.2: Practical implementation of power-clock using an inductor: (a) Schematic. (b) Waveform.

One realization of a power-clock generator with energy recovery ability is shown in Figure 1.2. Here, an inductor L is employed to store the energy of the charge returned from capacitor C in the form of a magnetic field. Periodic energy transfer between the inductor L and the capacitor C results in a sinusoidal waveform. The only energy losses in the system are due to the parasitic resistance of the circuit. To compensate for these losses, a shunt switch driven by pulse p is used to inject current into the inductor, replenishing energy in each cycle. The natural oscillation frequency  $f_n$  of the ideal LC system is

$$f_n = \frac{1}{2\pi} \sqrt{\frac{1}{LC}},\tag{1.3}$$

where C is the total capacitance of LC oscillation system.

During practical design, the inductance value for L is chosen to meet a target frequency  $f_n$  with a given extracted load C. For example, with a load  $C_L$  and a target frequency  $f_n$ , the inductance is chosen as  $L = 1/(2\pi f_n)^2 C_L = T^2/4\pi^2 C_L$ . The

waveform of the forced LC oscillation is a sinusoid-like waveform, and the energy consumption can be derived as

$$E = \frac{1}{2} |I^2| RT$$

$$= \frac{1}{2} \left| \frac{V/2}{1/j\omega C} \right| RT$$

$$= \frac{1}{2} \left( \frac{\omega V}{2} C \right)^2 RT$$

$$= \frac{1}{2} (\pi f V C)^2 RT$$

$$= \frac{1}{2} (\frac{\pi^2 CR}{T}) C V^2. \tag{1.4}$$

Using Equation (1.3), Equation (1.4) can be further simplified to obtain an expression of energy dissipation in terms of circuit parameters:

$$E = \frac{1}{2} \cdot \frac{\pi^2 CR}{2\pi \sqrt{LC}} CV^2$$

$$= \frac{\pi}{4} R \sqrt{\frac{C}{L}} CV^2$$

$$= \frac{\pi}{4Q} CV^2. \tag{1.5}$$

With the quality factor defined as  $Q = \frac{\sqrt{LC}}{R}$ , a direct energy dissipation comparison can be drawn between a charge-recovery system and a conventional CMOS one with the same load. As a result, Q is an important metric and is often used to evaluate the efficiency of a charge-recovery system.

### 1.3 Power-Clock Generator

Figure 1.3 shows a single-phase power-clock generator, which uses an inductor L and parasitic capacitance  $C_L$  to form an LC oscillation. This clock generator provides a single-phase sinusoidal clock waveform, and an inductor L is chosen to achieve a target resonant frequency for a given load  $C_L$ .

Figure 1.3: A single-phase power-clock generator with two supplies.

The clock drivers (M1 and M2), similar to the one used in [9], periodically replenishes the energy losses in the resonant system through current injection in the inductor. As the clock approaches its minimum, pulse a causes the pull-down switch to conduct, discharging the output clock voltage to 0V, and causing an RL current build-up in the inductor. At the falling edge of pulse a, the system continues oscillating freely with an initial condition V(PC) = 0V and  $I(L) = I_n$ , where  $I_n$  is the current flowing in the inductor at that time. Similarly, when the clock reaches its peak, pulse b causes the pull-up switch to conduct, resulting in a similar RL current build-up in the inductor. At the rising edge of b, the system once again resumes a free oscillation, with an initial condition  $V(PC) = V_{DD}$  and  $I(L) = I_p$ , where  $I_p$  is the current flowing in the inductor at that time.

The current build-up in the inductor at the crest and trough of V(PC) enables the supply to provide energy to the system periodically, which is stored in the form

Figure 1.4: A single-phase power-clock generator with single supply and a voltage divider.

of a magnetic field in the inductor. The amount of replenished energy required to maintain stable oscillations is thus governed by the equation:

$$E_{replenished} = \frac{1}{2}LI_n^2 + \frac{1}{2}LI_p^2. \tag{1.6}$$

Notice that, in this driven power-clock generator, the natural frequency of the oscillation is determined by Equation (1.3), and the actual frequency of the generated sinusoid waveform is determined by the frequency of the pulses. If this frequency is too far away from the natural frequency of the oscillation, the generated waveforms will be distorted.

Instead of the two-supply scheme in Figure 1.3, Figure 1.4 uses a single supply with a capacitive voltage divider to achieve a similar functionality. Large capacitors are used in the divider to provide stable voltage sources at the cost of capacitor area.

Various circuit topologies for power-clock generators have been proposed for different charge-recovery logic styles and for different applications. Figure 1.5 shows an H-bridge clock generator that generates a two-phase power-clock with cross-coupled

Figure 1.5: H-bridge two-phase power-clock generator.

Figure 1.6: (a) Basic scheme for a four-phase power-clock generator. (b) Circuit schematic related to C1-C3.

pairs of NMOS and PMOS transistors. It generates complementary power-clock waveforms using only one inductor.

A four-phase power clock generator has been presented in [11], and the schematic is shown in Figure 1.6. This circuit uses only one inductor to generate all four clock phases. The idea of using a single rotating inductor is shown in Figure 1.6(a). Rotation of inductor to transfer the energy between various clock phases is achieved by sequentially switching the transmission gates (TG), as shown in Figure 1.6(b) for

loads C1 and C3. One of the issues of this generator is that the power dissipation overhead of the controller circuit restricts its use to drive relatively smaller systems.

### 1.4 Charge-Recovery Systems

Charge recovery can be deployed various ways. The main two broad classifications are charge-recovery logic and resonant-clocked designs. Charge-recovery logic belongs to the class of fine-grain design, which employs charge-recovery techniques at the gate level to recover energy from load capacitance driven by all gates in a design. Resonant-clocked design is an example of coarse-grain design and recovers energy from the clock network in the design. Depending on the specific implementation of resonant-clocked designs, charge-recovery techniques may also be extended to the internal nodes of pipeline registers.

### 1.4.1 Fine-grain Systems

A fine-grain charge-recovery system is inherently gate-level pipelined with charge-recovery logic. This logic utilizes the idea of current-steering to conditionally charge or discharge load capacitance based on the outputs of its proceeding stage. To illustrate the structure, operation, and design of logic in a fine-grain charge-recovery system, we will use an early charge-recovery logic gate, 2N-2P [12] as an example. Even though the detailed implementations of various charge-recovery logic families differ, the underlying objectives, trade-offs and basic circuit topologies are quite similar.

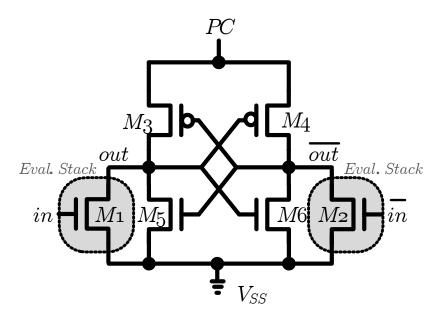

Figure 1.7(a) shows an inverter implemented in 2N-2P with idealized power-clock waveforms,  $\varphi_1$ ,  $\varphi_2$ ,  $\varphi_3$ , and  $\varphi_4$ , shown in Figure 1.7(b). The gate utilizes cross-coupled PMOS transistors to steer the current from the power-clock generator to one of the (ideally) balanced output nodes, *out* or  $\overline{out}$ . The initial resolution at output nodes is determined by the complementary pull-down evaluation trees. The losses in such a charge-recovery system are due to steering devices and parasitic

wiring resistance through which the load current flows. For simplicity, we consider the operation of the gate with two non-overlapping idealized power-clock waveforms shown in Figure 1.7(c), and ignore the effect of the threshold voltage  $V_{th}$  on the operation of the gate.

The operation of a 2N-2P gate can be divided into four phases: evaluation, hold, reset, and wait. For correct operation, all gates are cascaded in a way that gates driven by  $\varphi_1$  connect to gates driven by  $\varphi_2$  and so on, until gates driven by  $\varphi_4$  connect to gates driven by  $\varphi_1$ . At time t=0, the gate connected to  $\varphi_1$  is at the beginning of its evaluation phase. At this point, the input signal in, at its hold phase, provides full level inputs to transistor M1 and holds node out firmly to  $V_{SS}$ . Since in is low, transistor in is off, node in is floating during this time. As  $\varphi_1$  begins to ramp up, transistor in conducts more strongly. Since in is held to in is held to in increasing in i

In resonant systems, presenting a constant capacitive load C is important to provide a stable oscillation frequency, and the dual-rail property of 2N-2P logic can provide a near-constant load capacitance when looking into the  $\varphi$  node of the gate. As long as the effective capacitors at the 2N-2P output nodes are equal, the value of C in a resonant system is independent of the output state of gates, and stable LC oscillation is maintained. This is one of the salient advantages of using dual-rail logic in a fine-grain charge-recovery system. However, dual-rail logic has its limitations. One such limitation is the constant switching activity of each gate, which is

Figure 1.7: (a) Schematic of 2N-2P inverter. (b) Four-phase power-clock waveforms. (c) Operating waveforms of 2N-2P inverter.

50%, independent of the switching probability of the output state, since one of the two output nodes switches in every cycle. As a result, a fine-grain dual-rail charge-recovery system could cause low-switching activity gates to dissipate more compared to their conventional CMOS counterparts. A significant portion of energy savings is thus given up when applying fine-grain charge-recovery techniques to designs with

low switching activity.

The need of multiple clock phases for 2N-2P logic also increases the complexity and reduces the energy efficiency of the design. Use of multiple-clock phases requires more clock network broadcasting in physical design and thus increases design complexity. Gate cascading needs to follow a fixed phase order in 2N-2P operation, and only gates driven by specific phase-pairs can be connected. Furthermore, additional buffering is often required to phase-delay noncritical paths, balancing the paths so that they arrive at the same time as critical paths. This buffering results in additional power dissipation and affects the extent to which a design can be efficiently implemented using fine-grain charge-recovery techniques.

Fine-grain pipelining enables greater throughput but limits the range of designs that can be efficiently implemented. Charge-recovery techniques involve a fundamental trade-off between energy dissipation and latency, as suggested by Equation (1.4); however, they do not affect system throughput, since fine-grain systems are inherently gate-level pipelined. Moreover, the maximum number of evaluation stack height in each charge-recovery logic limits the function that can be implemented in each gate. As a result, deeper pipelining is sometimes needed compared to a traditional CMOS datapath. Fine-grain charge-recovery is therefore advantageous in systems that are throughput intensive and can tolerate increased latencies.

Implementing fine-grain charge-recovery techniques in sequential circuits with feedback is also a challenge, since both latency and throughput are adversely affected. With feedback loop in a design, no further computation can occur until the previous one is completed, so throughput and latency become correlated.

Although the majority of work in charge-recovery design has focused on fine-grain systems, these techniques are not limited to such logic gates. Charge-recovery techniques are particular effective in applications which involve nets with large switching activity. Regular datapath structures without feedback loops are also well-suited

to fine-grain charge-recovery implementations. In the next section, we will discuss designs that implement charge-recovery techniques on specific nets, leading to coarse-grain charge-recovery design.

### 1.4.2 Coarse-grain Systems

Unlike fine-grain designs, which employ charge-recovery techniques throughout the design, coarse-grain designs employ charge-recovery selectively in part of of the design, where the application of these techniques is more effective. In this section, a resonant-clocked pipeline is discussed as an example of coarse-grain system. In particular, resonant-clocked pipeline designs apply charge-recovery techniques on the parasitic capacitance of clock distribution network and in some cases, may extend to the internal capacitance of pipeline registers.

Figure 1.8: Resonant-clocked pipeline example.

Figure 1.8 shows an example of a resonant-clocked design where the timing ele-

ments (pipeline registers) are specially designed and clocked by a single-phase resonant clock, and combinational logic is identical to conventional CMOS design. An inductor L is used to resonate the capacitance of the entire clock network C in the system. Due to the high switching activity of the clock distribution network, substantial dynamic power reduction can be achieved with special pipeline register designs. In contrast to a fine-grain gate-level pipelined system, such designs are pipelined at a coarser level, which is similar to the conventional CMOS datapath with multi-stage pipelines. Consequently, coarse-grain systems can be designed to exhibit identical system-level timing properties with traditional clocked designs such as latency, throughput, and cycle time.

Unlike fine-grain charge-recovery systems, coarse-grain charge-recovery systems do not require additional buffers to balance delay, greatly increasing the range of designs that can be implemented in an energy manner. Furthermore, since logic gates in this system can be implemented with conventional CMOS logic, the design of resonant-clocked pipelines is more amenable to commercial tools, especially for synthesis and place-and-route.

#### 1.5 Contributions

This section outlines the contributions of this thesis. The main motivation of this thesis is to apply charge-recovery techniques on designs and achieve better energy/performance trade-offs than conventional CMOS design. We demonstrate charge-recovery techniques on two systems with different frequency points. Both designs provide high performance at their corresponding supply-levels and achieve higher energy efficiency than their conventional CMOS designs counterparts.

### 1.5.1 SBL and SBL-Based FIR Filter Design

In this work, we present Subthreshold Boost Logic (SBL), a new circuit family that relies on charge-recovery design techniques to achieve order-of-magnitude improvements in operating frequencies while still achieving high energy efficiency using subthreshold DC supply levels. Specifically, SBL uses an inductor and a two-phase power-clock to boost subthreshold supply levels, overdriving devices and operating them in linear mode. Charge-recovery switching is used to implement this boosting in an energy-efficient manner.

To demonstrate the performance and energy efficiency of SBL, we also present a 14-tap 8-bit finite-impulse response (FIR) filter test-chip fabricated in a  $0.13\mu m$  technology with  $V_{th,nmos} = 400 \text{mV}$ . The energy-efficient operation of the SBL-based FIR test-chip has been experimentally verified for clock frequencies in the 5MHz-187MHz range. With a single 0.27V supply, the test-chip achieves its most energy efficient operating point at 20MHz, consuming 15.57pJ per cycle with a recovery rate of 89% and a Figure of Merit (FoM) equal to 17.37nW/Tap/MHz/InBit/CoeffBit. With the introduction of a second subthreshold supply at 0.18V, energy consumption at 20MHz decreases further by 17.1%, yielding 14.40 nW/Tap/MHz/InBit/CoeffBit. At its maximum operating frequency of 187MHz, the test-chip achieves 35.31nW/Tap/MHz/InBit /CoeffBit and 34.47 nW/Tap/MHz/InBit/CoeffBit with one and two subthreshold supplies, respectively. To our knowledge, these figures of merit are the lowest published for FIR test-chips to date [13, 14]. In comparison with a static CMOS-based implementation derived by synthesis of the same FIR architecture and automatic place and route, the SBL-based FIR consumes 40% to 50% less energy per cycle in the 17MHz-187MHz range, based on device-level simulations, while incurring a 15%area overhead.

#### 1.5.2 Flash ADC with Resonant Clock Distribution

Resonant clocking has been shown to be an effective approach to the reduction of power consumption in GHz clock speed distribution networks [14, 15, 16]. In the ADC presented in this thesis, resonant clocking is deployed to decrease the power consumption of the network that distributes the clock signal to the analog and digital circuitry of the ADC. Specifically, a fully integrated inductor is used to resonate the parasitic capacitance of the entire clock distribution network all the way to the clocked timing elements. This technique is thus compatible and can be used in conjunction with previous power optimization approaches at the circuit and architecture levels.

Operating in the vicinity of its resonant frequency with sampling rate 5.5GS/s, the ADC dissipates 28mW with only 10.7% of total power on clock distribution and a FoM equal to 396fJ per conversion step. This FoM is lower than all previously-published ADCs operating above 2.2GHz [2]. Correct operation has been validated at the clock rates up to 7GHz with 45mW of total power consumption and 11.1% of total power on the clock.

#### 1.6 Thesis Outline

The remainder of this thesis is organized as follows: In Chapter 2, we give a brief introduction of reversible computing, which provides the main ideas and motivations of the charge-recovery design techniques. A summary of previous work is presented in the area of both charge-recovery logic and resonant-clocked designs.

In Chapter 3, we present our novel fine-grain charge-recovery circuit family, called SBL, that achieves high performance and high energy efficiency with a single subthreshold-level supply. We discuss its structure and operation, including high performance achievable through efficient signal boosting. We also give a detailed analysis of the energy consumption for SBL gates.

In Chapter 4, we describe an 8-bit 14-tap SBL FIR test-chip fabricated in  $0.13\mu m$  technology. Results from device-level simulation of the SBL FIR filter and its static CMOS counterpart with identical architecture are given and compared. Measurement results from our SBL test-chip with both single- and two-supply schemes are presented and discussed. This work was published in [17, 18].

Chapter 5 presents the architecture of our resonant-clock flash ADC design and its main building blocks. It also gives detailed designs, and discusses operations of resonant-clocked dynamic comparators and sense-amplifier flip-flops used in our resonant-clock flash ADC.

Chapter 6 presents the design, evaluation, and testing of a 7GSample/s resonant-clock flash ADC test-chip. The ADC has been designed and fabricated in a 65nm bulk CMOS process. An on-chip inductor is used to resonate the entire clock distribution network, and a detailed analysis of the inductor from a commercial 3D full-wave electromagnetic field solver is given. Measurement results from our resonant-clock ADC test-chip with ADC performance characterization are also presented. This work was published in [19].

Chapter 7 summarizes the contributions of this thesis and presents directions for future research in this area.

#### CHAPTER 2

# Background

In this chapter, we survey previous work on charge-recovery. In Section 2.1, we describe reversible computing, which inspired later charge-recovery techniques. Section 2.2 covers early research on charge-recovery logic. Section 2.3 discusses previous work in the area of resonant-clocked designs. Following these early work, we explore the techniques and challenges in charge-recovery area, which lead to the motivation of the work in this thesis.

## 2.1 Reversible Systems

#### 2.1.1 Reversible Computing

Long before energy dissipation emerged as a matter of interest in VLSI design, physicists inquired into the fundamentals of energy dissipation and the loss of information in a computing system [20]. In the early papers, researchers largely focused on discussing the possibility of having physical machines which consume zero energy while computing and tried to find a lower bound on energy consumption. One of the conclusions drawn by Landauer is that the minimum possible amount of energy required to change one bit of information is equal to kTln2 [21], where k is the Boltzmann constant, and T is the absolute temperature of the environment. This loss of energy becomes heat expelled into the surroundings.

Another result of early work in the area is that to achieve zero energy computation, the operation must be reversible or be implemented in reversible logic [22]. If the devices in a computing system are designed to change state in a way that is logically reversible, in which no known bits are erased, then in principle, arbitrarily little free energy needs to be used. Of course, in practice, there are other sources of energy dissipation such as leakage, or resistive loss. However, unlike the kTln2 energy dissipation for changing a bit operation, there are no fundamental lower bounds for these sources of dissipation.

#### 2.1.2 Reversible Logic

Reversible logic gates are digital circuits in which the number of inputs is equal to the number of outputs and there is a one-to-one mapping between vectors of inputs and outputs [23]. Therefore, in these gate, the input vectors can always be reconstructed from output vectors. A gate with k inputs and k outputs is called a  $k \times k$  gate, and all gates in a reversible circuit must be reversible. Reversible logic realizes balanced functions on all outputs, i.e., half of all minterms are mapped to 1 and the other half to 0. Consequently, garbage outputs are necessary to realize non balanced functions (e.g., AND, OR, XOR etc).

Consider a reversible logic gate with two inputs. A conventional XOR gate takes two single-bit inputs A and B, and yields one single-bit output X. If A = B, then X = 1; otherwise X = 0. However, the XOR gate is not reversible, since we cannot uniquely determine what the input vector (A, B) is from the output. For instance, the output X = 1 could have come from either one of the two possible input vectors, (0, 1) and (1, 0). Although a reversible gate must be a  $k \times k$  gate, not all gate with k-bit input and k-bit output are reversible. For example, consider a gate with input vector (A, B) and output vector (X, Y), where X = A XOR B, and Y = A OR B, as shown in Figure 2.1. Clearly, this is not a reversible gate, since there exists a 2-to-1

Figure 2.1: Truth table of an irreversible gate.

mapping from the input to the output.

For a two-bit input and two-bit output gate to be reversible, the mapping of its logic function should be such that the set of output vectors is a permutation of the set of input vectors, (00, 01, 10, 11). It then follows that there exist 4! = 24 possible reversible two-bit input and two-bit output logic gates. The Feynman gate is one of the most well known reversible two-bit input and two-bit output logic gates [24]. A Feynman gate with input vector (A, B) and output vector (X, Y) implements the logic functions: Y = B, and X = A XOR B. From input-to-output mappings, shown in Figure 2.2(a), it is evident that the Feynman gate is a reversible gate. In this example, one of the inputs B serves as a control signal. If B = 0, then the output X = A XOR B is simply duplicating the input A; if B = 1, then the output A = A B B inverse of the input A = A B B inverse of the input A = A B B inverse of the input A = A B B inverse of the input A = A B B inverse of the input A = A B B inverse of the input A = A B B inverse of the input A = A B B in the field of quantum computing.

Implementing reversible logic in integrated circuits has many challenges and issues. As suggested in [25], reversible computation requires all logic operations to be carried out once in the forward direction and once in the backward direction, yielding additional latency and circuit overhead. More importantly, it requires a large amount of temporary storage to maintain intermediate results until computation in

Figure 2.2: (a) Truth table and (b) symbol of the Feynman gate.

the backward direction is ready. Since storing these temporary values results in energy and circuitry overheads, implementing fully logically reversible logic in CMOS is not particularly attractive.

A practical alternative to full reversible logic is to use the idea of reversible computing in engineering systems with charge-recovery techniques, and try to approach the theoretical possibility of zero dissipation as closely as possible. If state information of a node in a circuit is available, and utilized when switching the state of that node, no information is lost. As a result, most of the free energy is conserved in the circuit and recycled for later reuse, rather than being dissipated.

# 2.2 Charge-Recovery Logic

Charge-recovery logic is a class of circuitry that recycles energy from the output load capacitance of logic gates to achieve ultra-low power operation. It utilizes the idea of current-steering to conditionally charge or discharge load capacitance based on the outputs of its proceeding stage. Each charge-recovery logic gate is a inherently gate-level pipeline stage, performing the role of both functional logic and timing elements in conventional CMOS designs.

Early charge-recovery logic, such as Split-level Charge-Recovery Logic (SCRL)

[26] and Reversible Energy Recovery Logic (RERL) [27], implemented fully logically reversible gates in CMOS. As pointed out in [25], the large number of temporary storage elements in a fully reversible circuit yields large circuit overheads. Later work in charge-recovery logic deviates from fully reversible circuits. These charge-recovery logic family retained the gradual transition of the charge between computation nodes but avoided design of reversible logic gates, keeping information around to reduce change in energy.

Figure 2.3 shows the structure of NMOS and PMOS inverters in Adiabatic Dynamic Logic(ADL). Proposed by Dickinson and Denker in 1995, ADL is a single rail adiabatic logic family [28]. ADL uses a diode to precharge the output node *out* to high when the power-clock rises, and the evaluation stack conditionally discharges the node *out* as the power-clock falls. The PMOS ADL inverter works in an opposite fashion. In an ADL system, ADL gates are cascaded by alternating the NMOS ADL and PMOS ADL gates. Both of them are synchronized by a two-phase power-clock with 180 degree phase difference to ensure that precharge and evaluation phases of all gates are synchronized. A chain of 64 inverters was successfully verified with an external 250MHz power-clock in 0.9µm process [29].

Figure 2.3: Schematic of (a) NMOS ADL inverter, and (b) PMOS ADL inverter.

Quasi-Static Energy Recovery Logic (QSERL) has been proposed by Ye and Roy [30] and has a similar diode structure to ADL, as shown in Figure 2.4. Instead

of precharging the output nodes with diodes, QSERL uses diodes to conditionally hold/discharge the voltage level at output nodes. This single-rail structure for both ADL and QSERL exhibits a data-dependent clock load, yielding high clock jitter and degrading system performance. Moreover, the use of diode in this logic may cause a substantial potential difference and generate large current flow, reducing energy efficiency.

Figure 2.4: Schematic of QSERL inverter.

2N-2P is another early charge-recovery logic [12], and is has been discussed in detail in Chapter 1. Unlike ADL, the dual-rail topology of 2N-2P gates provides a data independent clock load for charge-recovery systems. However, requiring of four-phase power-clock increases design complexity and limits its applicability.

Various charge-recovery logic families have been proposed since 2N-2P. 2N-2N2P [12] is a variation of 2N-2P, as shown in Figure 2.5. By adding an additional pair of cross-coupled NMOS devices at the bottom, 2N-2N2P eliminates floating outputs during the hold phase.

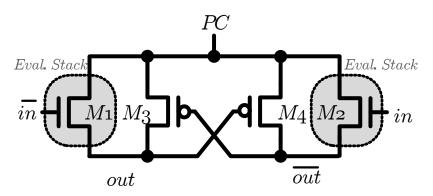

Pass-transistor Adiabatic Logic (PAL), proposed by Oklobdzija et al.[31], is shown in Figure 2.6. PAL retained the cross-coupled PMOS structure in 2N-2P, and moved its evaluation stacks in parallel to the PMOS devices. Instead of a four-phase power-

Figure 2.5: Schematic of 2N-2N2P inverter.

clock in 2N-2P, PAL can operate with a two-phase power-clock. A shift register with 1,600-stage PAL has been fabricated in a  $1.2\mu m$  technology and correct operation has been verified at 10MHz.

Figure 2.6: Schematic of PAL inverter.

Positive Feedback Adiabatic Logic (PFAL), shown in Figure 2.7, was proposed by Vetuli et al. [32]. PFAL is also a dual-rail charge recovery logic with a two-phase power-clock. Similar to 2N-2N2P, it eliminates floating outputs by using a pair if cross-coupled devices and its evaluation stacks are in parallel to PMOS devices. Compared to PAL, the cross-coupled NMOS and PMOS structure provides higher energy efficiency due to less leakage current. Compared to 2N-2P and 2N-2N2P,

PFAL has the potential to achieve higher operating frequency due to the full-rail input during evaluation phase.

Figure 2.7: Schematic of PFAL inverter.

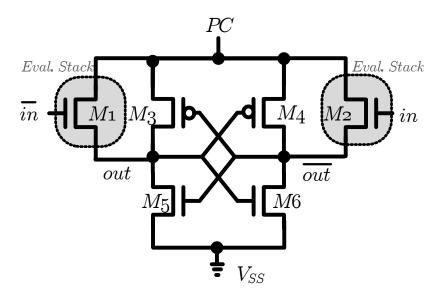

Figure 2.8 shows an inverter gate in True Single-Phase Energy-Recovering Logic (TSEL) [33]. TSEL cascades use alternating NMOS and PMOS stage and operate with a single-phase power-clock. A pair of current control switches (M3 and M4) and reference voltages ( $V_{PREF}$  and  $V_{NREF}$ ) are used to improve its energy efficiency.

A Source-Coupled Adiabatic Logic (SCAL) [7] is derived from TSEL gates by replacing each DC reference voltage with a current source (M7), shown in Figure 2.9. Each current source can be individually tuned by transistor sizing and globally adjusted with PMOS and NMOS biasing voltage to optimal operating condition. An 8×8 multiplier test-chip has been fabricated in  $0.5\mu$ m technology, and correct operation has been verified with operating frequency up to 130MHz [8].

The charge-recovery logic families discussed so far all face a common challenge of efficient operation at high frequency. To address this challenge, Sathe et al. proposed Boost Logic [34], which utilizes gate overdrive, reduced output swing, and charge-recovery techniques to achieve energy efficient operation at high operating frequency. Figure 2.10 shows the schematic of a buffer implemented in Boost Logic. Boost Logic

Figure 2.8: Schematic of (a) NMOS TSEL inverter, and (b) PMOS TSEL inverter.

Figure 2.9: Schematic of (a) NMOS SCAL inverter, and (b) PMOS SCAL inverter.

is a two-phase, dual-rail, partially charge-recovering logic. The structure of a Boost gate can be divided into two parts — logical evaluation (Logic) and charge-recovery amplification (Boost). Logic performs functional evaluation when power-clock is low. When power-clock rises, Boost amplifies the potential different at output nodes to a

full-rail signal. The output nodes of Boost Logic are precharged to near  $\frac{1}{2}V_{DD}$ , which reduces the output swing of the gate when power-clock rises and thus reduces the energy dissipated in the Boost stage.

Another feature of Boost Logic that enables its efficient high-frequency operation is the fact that the logic stage provides the complementary output nodes with an initial voltage difference. Voltage difference ( $\frac{1}{3}V_{DD}$ ) at outputs is pre-resolved at the onset of boost conversion, which precludes any 'fight' between cross-coupled inverters and results in efficient boost conversion. To demonstrate the high performance and energy efficiency of Boost Logic, a test-chip with eight chains of AND, OR, XOR, and INV gates was fabricated in  $0.13\mu m$  technology, and correct operation was verified at operating frequencies exceeding 1GHz.

Figure 2.10: Schematic of Boost Logic inverter.

Looking back at the evolution of prior work, one observes that many similar traits

are shared among various charge-recovery logic families. The first common trait is the pair of cross-coupled PMOS devices which are used to steer the current of the power-clock and bring output to a full-rail signal. Another common feature of these gates is the fact that multiple clock phases, supplies, or clock devices are used to reduce the short current caused by the gradual transition of power-clock. These common traits provide us with good guidance in designing future charge-recovery logic.

#### 2.3 Resonant-Clocked Designs

Resonant clocking is a charge-recovery design methodology that recovers energy from the clock distribution network. Due to the high switching activity and large capacitance of clock distribution networks, it becomes a good candidate for the application of charge-recovery techniques. Resonant-clock datapaths are similar to conventional-clock datapaths and combinational logic in resonant-clock designs can be implemented with conventional CMOS style logic.

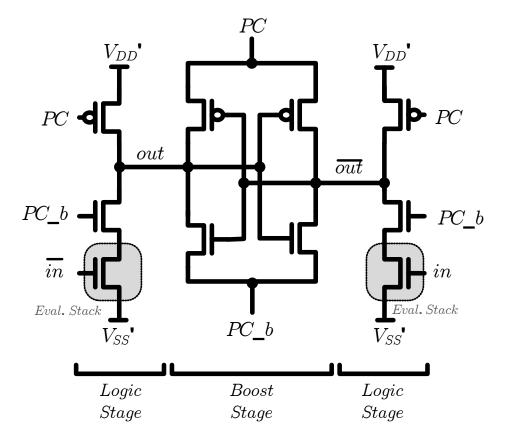

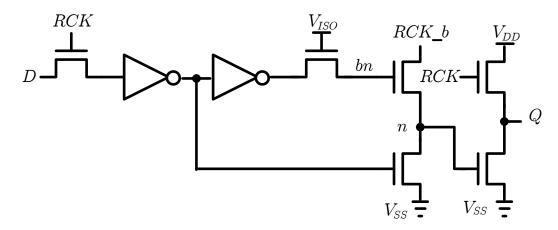

Most of the previous work in resonant-clock designs focuses on developing new timing elements to reduce the leakage current and improve the performance due to the slow transition of the resonant clock. Athas et al. presented the E-R latch [35], shown in Figure 2.11. The E-R latch uses the bootstrapping technique at node bn, and the resonant clock recycles charge at both clock nodes and from the internal node n. Charge recycling at node n improves the total amount of recoverable capacitance but at the expense of reduced recovery efficiency due to the series resistance from M3. Correct operation of the E-R latch has been verified in AC-1, a 58.5MHz resonant-clocked microprocessor in  $0.5\mu$ m technology [35].

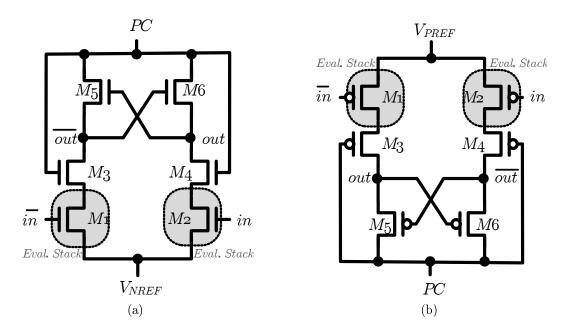

Figure 2.12 shows the PMOS energy recovering flip-flop (pTERF) and NMOS energy recovering flip-flop (nTERF) proposed by Ziesler et al. [10]. A cross coupled NOR/NAND gate is added to convert the internal resonant signals to static ones, and an inverter is introduced at output node Q to increase drive strength.

Figure 2.11: Schematic of Edge-Triggered (E-R) latch.

pTERF/nTERF has a similar issue to the E-R latch: the effective resistance of the cross-coupled devices dissipates energy during the charge and discharge cycles, limiting overall energy recovery efficiency. A 115MHz wavelet-transform test-chip has been fabricated in  $0.25\mu m$  technology with pTERF and achieved 25% to 30% of energy saving compared to  $CV^2$  [9].

Figure 2.12: Schematic of (a) pTERF flip-flop, and (b) nTERF flip-flop.

Ishii et al. [1] deployed resonant clocking in conjunction with sense-amplifier flip-

flops, shown in Figure 2.13. They successfully demonstrated energy efficient operation on an ARM926EJ-S<sup>TM</sup> microprocessor with operating frequency up to 200MHz. Clock-related power is reduced by 85%, and total power savings range from 20% to 35%, depending on application profile.

Figure 2.13: Schematic of sense-amplifier flip-flop used in [1].

Hansson et al. [36] have fabricated a 1.56GHz resonant-clock network in a 0.13  $\mu$ m technology with an integrated 1.2nH inductor. A single-phase resonant clock directly drives 896 conventional master-slave flip flops without any intermediate buffers. The relatively slower edge-rate of the sinusoidal clock is reported to increase the power consumption in the flip-flops by 34%. Despite the higher power consumption in the flip-flops, there is still a 57% clock power saving, resulting in a total power reduction of 20% compared to the conventional clock network.

Chan et al. [15] later applied the global resonant clock distribution topology to a commercial microprocessor. Their processor has 830 on-chip spiral inductors with a natural resonant frequency of 3.2GHz. Unlike the work in [36], which drives flip-flops directly, Chan inserted local clock buffers between the resonant clock mesh and the

timing elements, resulting in limited energy recovery.

Figure 2.14: Schematics of resonant-clocked latches used in RF1: (a) H-LAT, and (b) L-LAT.

Figure 2.15: Schematic of resonant-clocked latch used in RF1, B-LAT.

Other work in this area has focused on evaluating and characterizing variability on resonant clocks. Chueh et al. [37] implemented a two-phase resonant clock network with programmable drivers and loading to evaluate the effect of imbalanced clock load on clock skew. The 2mm×2mm distribution network with on-chip inductors fabricated in  $0.13\mu$ m technology performs a forced oscillation in the 900MHz to 1.2GHz

range. When running off-resonance by 10%, power dissipation increases by 3% and clock amplitude drops by 3%. Imbalanced loading impacts power and amplitude by less than 2%. When shifting from balanced to imbalanced loading, worst-case skew increases by 6% of cycle time.

More recent implementations of resonant-clocked designs focus on improving performance of timing elements. Sathe et al. have proposed a resonant-clock latch-based methodology and demonstrated its high performance and energy efficient operation with two FIR filter test-chips, RF1 and RF2, in a 0.13μm technology [38, 39]. Unlike flip-flops, which rely on sharp clock edges for effective operation, latch performance is primarily determined by the voltage level of the clock waveform. Moreover, latch-based designs have the potential to achieve higher performance than flip-flop-based designs, because the level-sensitive latches allow data to ripple through latch boundaries and enable time-borrowing across logic stages. Resonant-clocked latches used in RF1: H-LAT and L-LAT are shown in Figure 2.14 and B-LAT, used in RF2 is shown in Figure 2.15. RF1 and RF2 achieved 76% and 84% energy efficiency when operating their natural resonant frequencies of 1.03GHz and 1.01GHZ, respectively [14].

Figure 2.16: Schematic of DESL inverter.

Kao et al. introduced Dynamic Evaluation Static Latch (DESL) logic [16], a dy-

namic gate with a level-sensitive latch at the output stage, as shown in Figure 2.16. DESL mitigates performance degradation due to the resonant clock waveforms by relying on the voltage level of the clock. Moreover, a static latch provides a modest performance boost by relying on time borrowing and reduces dynamic power by reducing switching activity on large capacitance nets.

An 8-cycle reduced-latency fused-multiply-add single-precision FPU test-chip has been fabricated in a 90nm technology to demonstrate energy efficiency and performance of DESL. The resonant-clocked FPU operates with clock frequencies up to 2.07GHz, yielding 66.4% lower clock power and 31.5% lower total power over a conventionally-clocked version of the same architecture.

#### CHAPTER 3

# Subthreshold Boost Logic

In this chapter, we present Subthreshold Boost Logic (SBL), a new circuit family that relies on charge-recovery design techniques to achieve order-of-magnitude improvements in operating frequencies while still achieving high energy efficiency using subthreshold DC supply levels.

The remainder of this chapter is organized as follows: Section 3.1 describes previous work on subthreshold designs. Section 3.2 presents the structure of SBL and the two-phase power-clock generator used for SBL. Section 3.3 describes the two-phase operation of SBL gates and the overdrive property of cascaded SBL gates. Section 3.4 analyzes the energy consumption of SBL gates. Summary is in Section 3.5.

#### 3.1 Introduction

Early subthreshold circuit designs appeared in electronic watches in the 60s and 70s, driven by form factor limitations on battery size [40]. The recent emergence of untethered applications and energy scavenging devices has led to renewed interest in this field. A 1024-point FFT processor explored aggressive subthreshold designs for minimum energy operation, achieving a clock speed of 10KHz with a 350mV supply in a  $0.18\mu$ m process with  $V_{th} = 450$ mV [40]. The Subliminal subthreshold processor achieved 833KHz with a 360mV supply using a  $0.13\mu$ m process with  $V_{th} = 400$ mV

[41]. The Phoenix processor deployed leakage reduction techniques to achieve pW-level power consumption, targeting multi-year operation in sensor applications [5, 42]. Fabricated in a dual-threshold 0.18  $\mu$ m process with  $V_{th1} = 400$ mV and  $V_{th2} = 700$ mV, it achieved 2.8pJ/cycle at 106KHz with a 385mV supply.

A common issue underlying all subthreshold circuit designs is that the significant energy advantages achieved through deep voltage scaling result in subthreshold currents, typically resulting in sub-MHz clock frequencies. Recent subthreshold designs have deployed circuit and architecture techniques to improve circuit robustness by improving gate overdrive. The 32-bit RISC core in [43] and the 8×8 FIR filter in [44] both deployed body biasing techniques to enable increased operating frequency, achieving 375KHz at 230mV, and 12KHz at 200mV respectively. A high-speed variation-tolerant interconnect technique relied on capacitive boosting to elevate the critical gate supply voltage and was demonstrated through a 6MHz clock distribution network with 400mV voltage supply [45]. A super-pipelining approach was demonstrated in [46], where the multipliers in a 1024-point FFT were heavily pipelined to reduce stage delay, achieving 30MHz with a supply of 270mV.

Subthreshold Boost Logic, introduced in this chapter, is a circuit family capable of operating at multi-MHz clock frequencies using subthreshold supplies. Unlike subthreshold circuitry, in which computations are performed using subthreshold currents and clock frequencies are typically limited to sub-MHz levels, SBL gates are over-driven to operate in the linear region, achieving order-of-magnitude improvements in operating speed over subthreshold logic. Energy efficient operation is ensured through the use of aggressively-scaled DC supplies at sub-threshold levels and by deploying charge recovery design techniques to boost these subthreshold supply levels by 3X to 4X.

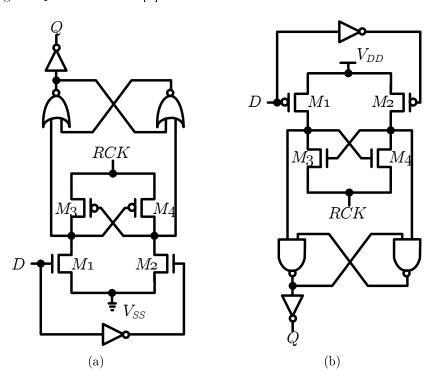

Figure 3.1: Schematic of an SBL gate.

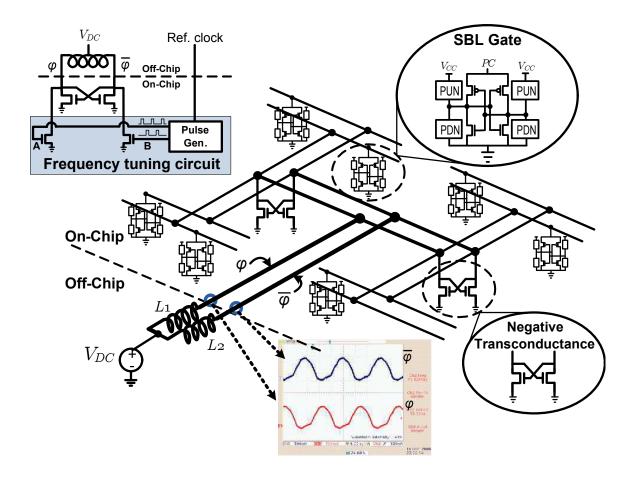

## 3.2 SBL Overview and Blip Clock Generator

The structure of a SBL gate is shown in Figure 3.1. Each SBL gate consists of two stages: Logic and Boost. The Logic stage has differential outputs out and out  $\_b$ . Each output is driven by a pull-up network (PUN) and a pull-down network (PDN), similar to static CMOS logic, except that an NMOS PUN is used instead of a PMOS one for increased gate overdrive ability. The Boost stage comprises a pair of cross-coupled inverters connected to ground  $(V_{SS})$  and a charge-recovery power-waveform PC. From a functional standpoint, each SBL gate consists of a combinational logic block driving a transparent latch. Cascades of SBL gates are formed by clocking the gates on alternating power-clock phases  $\varphi$  and  $\bar{\varphi}$ .

The power-clock waveforms required by SBL can be generated using a clock generator circuit similar to the "blip" circuit in [47], as shown in Figure 3.2. This circuit is formed by connecting two RLC oscillators back-to-back, using the output wave-

Figure 3.2: Simple "blip" clock generator: (a) Schematic. (b) Waveform.

form  $\varphi$  of one oscillator to drive the other, and vice versa. The two waveforms  $\varphi$  and  $\bar{\varphi}$  are partially overlapping, since the NMOS devices are not fully on until their output voltages exceed the threshold voltage  $V_{th}$ . One of the advantages of this clock generator is that it can provide a larger clock amplitude beyond its DC supply  $V_{DC}$ . As a result, it can share the same supply with the SBL gates, allowing a single DC supply operation. In our FIR test-chip, we used a clock generator that is a distributed injection-locked version of this circuit and is described in Section 4.2.