# 4.4: 200 dpi 3-a-Si:H TFTs Voltage-Driven AM-PLEDs

# Joo-Han Kim and Jerzy Kanicki

Solid-State Electronics Lab., Dept. of EECS, University of Michigan, Ann Arbor, Michigan, USA

#### **Abstract**

In this paper we describe opto-electronic properties of 200 dpi 3-a-Si:H TFT voltage-driven AM-PLEDs. In this display design the output current level drifts induced by either process variations or device aging can be reduced by adjusting the driver a-Si:H TFT operating point with the active resistor. Our first green lightentiting AM-PLED prototype had brightness of 50 cd/m² and fill factor of about 45%.

#### 1. Introduction

Active-matrix organic light-emitting displays (AM-OLEDs) are emerging as new flat panel display technology that one day could replace the active-matrix liquid-crystal displays (AM-LCDs). This new flat panel display technology has attributes such as high brightness, high contrast ratio, paper-like viewing angle, low power consumption, light weight, low fabrication cost, and the possibility of being integrated with the flexible substrates.

To achieve a low fabrication cost it is believed that the hydrogenated amorphous silicon (a-Si:H) thin-film transistor (TFT) active-matrix arrays should be combined with the organic light-emitting devices (OLEDs) [1-4]. It is also expected that in the near future a-Si:H TFTs mature technology could challenge today's poly-Si TFT AM-OLEDs [5-8].

The challenge for a-Si:H TFT technology lies in its relatively low current output and large device parameter shifts over time (bias stress induced effects [11]), under OLED illumination (light induced effects [12]) and with the operating temperature (thermal effects [13]).

However, the improved OLED efficiency [4, 9] combined with a-Si:H TFT high field-effect mobility [10], and proper pixel electrode circuits design and driving schemes could allow for a-Si:H technology to overcome its limitations with respect to AM-OLEDs.

In this paper, we describe fabrication and properties of 200 dpi 3-a-Si:H TFTs voltage-driven active-matrix organic polymer light-emitting display (AM-PLED).

### 2. 3-a-Si:H TFT pixel electrode circuit

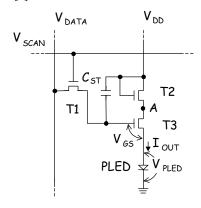

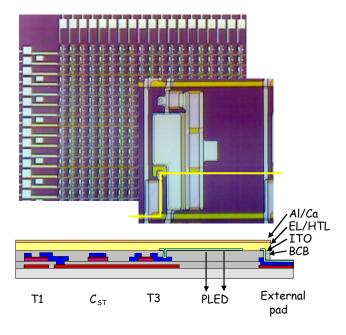

The 3-a-Si:H TFT pixel electrode circuit shown in Fig. 1 has five components:  $C_{\rm ST}$ , a storage capacitor; T1, a switching TFT; T2, an active resistor (AR); T3, a constant current driver TFT; and a PLED, an organic polymer light-emitting device. In this display the pixel is selected through the switching transistor while the scan voltage ( $V_{\rm SCAN}$ ) is "high". While  $V_{\rm SCAN}$  stays high, the switching TFT turns on, and then the data voltage,  $V_{\rm DATA}$ , is transferred and stored in the storage capacitor providing the turn-on signal to the gate electrode of the driver TFT, Fig. 2. This selecting operation of each pixel occurs during a very short period of time, called scan period. Usually this scan period is defined by the number of rows of the display. For instance, 21.7 and 16.3 µsec are the scan periods for SVGA and XGA displays operated at 60 Hz, respectively. In order to fully charge the storage capacitor up to the data voltage level, the speed of the switching

TFT is important. Depending on the data voltage level which is applied to gate electrode of the driver TFT, the driver a-Si:H TFT provides the corresponding continuous current (output current, I<sub>OUT</sub>) to the PLED, Figs. 1 and 2. For specific current level, the PLED will emit light with corresponding brightness level. Hence, the maximum brightness of the PLED depends on the current capacity of the driver TFT and the external luminance efficiency of the PLED [9].

Fig. 1. Schematic diagram of 3-a-Si:H TFT pixel electrode circuit.

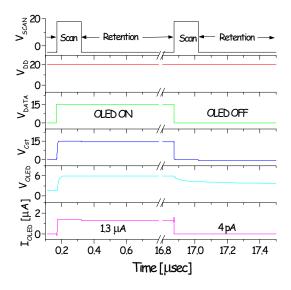

Fig. 2. An example of the voltage-driving scheme used for 200 dpi 3-a-Si:H TFTs AM-PLED.

An example of pixel driving scheme is shown in Fig. 2. In this specific case, the  $V_{SCAN}$  was 18 V and  $V_{DD}$  20 V. The  $V_{DATA}$  ranging from 0 to 15 V was maintained in  $C_{ST}$  during the retention period. The  $I_{OUT}$  was maximum 1.3  $\mu A$  and minimum 4 pA when PLED was ON and OFF, respectively.

The Iout at anode (ITO is positively biased) electrode will

establish an electrical potential difference between ITO and cathode electrode (Ca/Al is negatively biased). Established electrical field will induce electron injection into and extraction from cathode and anode into lowest unoccupied molecular orbital (LUMO) and highest occupied molecular orbital (HOMO) levels of the polymer, respectively. The process of removal of a negative charge (electron) from HOMO level leaves a positive charge (or hole) in the band. This process can be referred to as a "hole injection" into polymer HOMO levels. Under the influence of an electrical field, the oppositely charged radicals (anions and cations) will drift toward each other from polymer chain to polymer chain. Finally, when they combine on a single conjugated segment, singlet and triplet excitonic states are formed, of which the singlets can radiatively decay with the emission of visible green light that we measured. The intensity of this light (luminance) will depend on V<sub>DATA</sub>, Fig. 8.

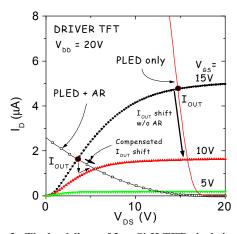

An example of measured a-Si:H TFT driver characteristics and calculated load-lines with  $(V_{AR} + V_{PLED})$  and without  $(V_{PLED})$ active resistor (AR) are shown in Fig. 3. The crossing point between I<sub>D</sub>-V<sub>DS</sub> and load-lines represent output current (I<sub>OUT</sub>) of the pixel electrode circuit. By adding an active resistor the output current level is reduced but better control of the pixel circuit is realized. In our pixel electrode circuit an active resistor forces the a-Si:H TFT driver to operate in linear regime for V<sub>DATA</sub> larger than 5 V, Fig. 3 [9]. In this operating regime the output current level drifts associated with the a-Si:H TFT driver and PLED characteristics shifts can be reduced in comparison with the a-Si:H TFT driver operating in saturation regime. Since the active resistor shares a high-voltage drop (VDD) with the driving TFT and PLED, any reduction in IOUT will be reflected by a voltage increase at node A ( $V_A$ = $V_{DD}$ - $V_{AR}$  where  $V_{AR}$  is the voltage drop across the active resistor), Fig. 1. As V<sub>A</sub> increases, V<sub>DS</sub> of T3 increases, resulting in an increase of IOUT. This represents partial compensation for an initial I<sub>OUT</sub> decrease that can be optimized for a given pixel electrode circuit design. In our initial not fully optimized case the simulated output current drifts were 6, 14, and 28 % for  $V_{DATA}$  of 5, 10, and 15 V, respectively. The operating point (and output current level) of the pixel electrode circuit can be optimized through optimization of active resistor dimensions (W/L) [9], [14-18].

Fig. 3. The load-lines of 3- a-Si:H TFT pixel circuit for  $V_{DD}$ =20V. The open symbol and solid line represent the load-line with ( $V_{AR}$ + $V_{PLED}$ ) and without ( $V_{PLED}$ ) active resistor.

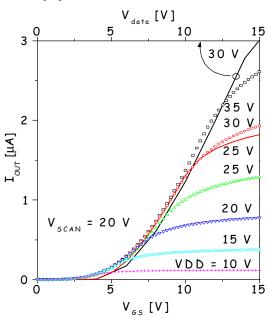

The variation of the output current of the pixel electrode circuit with  $V_{GS}$  of the driver TFT is shown in Figure 4; and the top-view of fabricated single pixel electrode circuit is shown in Figure 5 (inset).  $V_{SCAN}$  of 20 V and  $V_{DD}$  ranging from 10 to 35 V were applied during output current measurements. The current density between 2 and 50 mA/cm² was achieved for the pixel electrode aperture ratio of 45 % and the PLED area of 7500  $\mu m^2$ . The simulated curves are also shown in Figure 4 for  $V_{DATA}$  ranging from 0 to 15 V; in this case,  $\mu_{FE}$  of 0.5 cm²/V·sec and  $V_{T}$  of 1.76 V were used. The measured and simulated current-voltage transfer characteristics showed similar behavior with a small deviation. Based on our pixel electrode circuit performance, the output current density up to 100 mA/cm² can be achieved.

$\label{eq:fig:section} \begin{aligned} \text{Fig. 4. Measured (symbol-lines) and simulated (solid-lines)} \\ \text{pixel electrode output current versus input data voltage} \\ \text{characteristics ($V_{DATA} = V_{GS} + V_{OLED}$).} \end{aligned}$

## 2. 3-a-Si:H TFT 200 dpi AM-PLED

### A. Design and fabrication

To demonstrate an application of the above pixel circuit in an AM-PLED, we have fabricated a small size (1.27cm x 1.27cm) display as an engineering demonstration unit, Fig. 5. In this AM-PLED the active-resistor had a channel width of 15  $\mu$ m, and the driving and switching TFTs had channel widths of 105 and 30  $\mu$ m, respectively, with the same channel length of 10  $\mu$ m. The storage capacitance was 0.4pF. The top- and cross-section views of the 200 dpi AM-PLED backplane are shown in Fig. 5. The inset shows a blow-up of single pixel electrode circuit and its cross-section view. The light is emitted from the back side of the display through the glass substrate.

First, a chromium (Cr) gate electrode was defined on a Corning 1713 glass substrate (mask #1). Then the  $n^+$ -a-Si:H / a-Si:H / a-Sii:H / a-SiN<sub>x</sub>:H layers were deposited by plasma-enhanced chemical vapor deposition (PECVD) in a single pump down at a substrate temperature of 300°C. The active area for the TFT channel was

defined with RIE etching using CCl<sub>2</sub>F<sub>2</sub> and O<sub>2</sub> gas mixture (mask #2). The gate contact was opened through a-SiNx:H layer in buffered hydro-fluoric acid (mask #3). A Mo source/drain metal layer was deposited by DC magnetron sputtering at room temperature. The Mo source/drain electrodes were defined by wet etching, and the TFT channel etch-back of the n<sup>+</sup> a-Si:H using RIE method followed the source/drain patterning without additional photo mask. This step needs to be carefully optimized for the control of a-Si:H TFT OFF-current. Then, the Mo source/drain electrodes were planarized with spin-cast BCB which was cured in a furnace at 250°C in nitrogen ambient. The BCB layer was opened for anode contact with RIE etching using CF<sub>4</sub> and O<sub>2</sub> gas mixture (mask #5). An ITO (PLED anode) layer was deposited by DC magnetron sputtering at room temperature, and then cured in a furnace at 250°C in nitrogen ambient. The anode electrode was defined in a mixture of HCl, nitric acid, and DI water (mask #6). The typical thickness of each layer was 3000Å for Cr, 3000Å for a-SiN<sub>x</sub>:H, 1500Å for a-Si:H, 300Å for n<sup>+</sup> a-Si:H, 1000Å for Mo, 3000Å for BCB, and 1000Å for ITO.

Fig. 5. Top view of 200 dpi AM-PLED backplane. Inset shows single pixel circuit and the cross-section of active-matrix schematics.

Once the active-matrix array was fabricated, the backplane was cleaned in isoprophyl alcohol (IPA) and then, exposed to UV-ozone for 10min. Then a hole injection layer (HIL) was spin-coated and cured at 90°C for 20min. in a vacuum oven. A light emissive layer (LEL) was spin-coated over the HIL and cured at 90°C for 60min. in a vacuum oven. Poly(3,4-ethylene dioxythiophene) (PEDOT) doped with poly(styrenesulfonate) (PSS) and green light-emitting poly (fluorene) copolymer were used for HIL and LEL materials, respectively. Finally, a calcium/aluminum bi-layer cathode was thermally evaporated through a shadow mask without breaking vacuum under ~10<sup>-6</sup> Torr. Our display is a common-cathode type, in which the cathode

electrodes for each pixel are all connected together during the display operation. In addition, since the organic polymer active layers (HIL/LEL) in our prototype are not defined, we used swab tips soaked with solvent to remove the active layer on top of electrical contact leads around the display.

# **B.** Opto-electronic properties

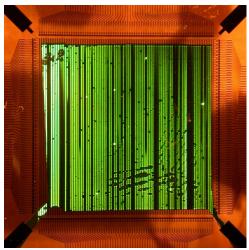

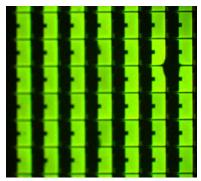

The test unit was operated to illuminate the whole display without packaging and driver electronics, Fig. 6. Overall the light intensity among pixels across the display was uniform due to the planarization of the active-matrix arrays, Fig. 7. However, there are a few line defects of the  $V_{\rm DD}$  bus or data signal bus lines and some pixel defects with bright spots, Fig. 6.

Fig. 6. Top-view of illuminated 200 dpi AM-PLED. The bright area on the left is glare from the light.

Fig. 7. Details of 200 dpi AM-PLED. The PLED is about 120  $\mu$ m x 62.5  $\mu$ m for pixel size of 127  $\mu$ m x 127  $\mu$ m.

The opto-electrical characteristics of 200 dpi AM-PLED have been measured using an integrating sphere and a calibrated photo-detector connected to a radiometer (International Light IL1700). The display was mounted on the input port of the integrating sphere and the total luminous flux was measured. This method ensured accurate measurement in spite of the small display size (1.27 cm×1.27 cm) [19].

For a real display operation, it is required that scanning signals are consecutively applied to every scan line and corresponding data signals are applied to each data line. However, in our case, we simultaneously applied a constant DC signal (30 V) to all the

scan lines and various constant DC signals (0 to 30 V) to all the data lines. The data voltage was applied using a programmable voltage source (Keithley 230) and the current flow through the PLED was measured by inserting an electrometer (Keithley 617) between the common cathode and ground electrodes. All the measurements have been performed in the air at room temperature.

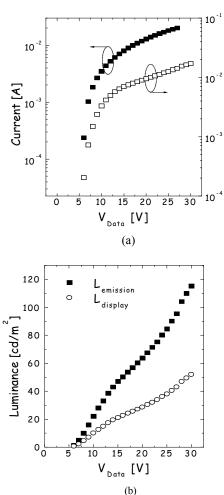

Fig. 8. (a) Measured current and luminous flux and (b) luminance of 200 dpi AM-PLED.

Fig. 8 shows the current and luminous flux versus data voltage characteristics. The initial light emission is observed when  $V_{DATA}$  is about 4~5 V. We can consider this data voltage as a turn-on data voltage that is closely related to the green PLED turn-on voltage, and the  $V_{DS}$  of the switching TFT and the  $V_{GS}$  of the driving TFT during selection time. We obtained up to  $2\times10^{-2}$  lumen at  $V_{DATA}=30$  V. The display luminance was estimated from the optical flux, assuming that the AM-PLED has Lambertian emission (the luminance is constant over the whole considered angular domain), which was experimentally verified [20]. The total display area of 1.27 cm×1.27 cm=1.62×10<sup>-4</sup> m<sup>2</sup> results in the display luminance:

$$L_{display} = \Phi / \left( p \times 1.6 \times 10^{-4} \right)$$

However, we also need to consider the actual light-emitting area to calculate the effective luminance of the light-emitting areas

( $L_{emission}$ ), which can be expressed as  $A_{emission} = (total \# of pixels) \times (yield of emitting pixels) \times (PLED area in each pixel). For our 200 dpi AM-PLED, this area is <math>A_{emission} = 4.74 \times 10^{-5} \, \text{m}^2$ , where the yield of emitted pixels ( $\sim 65\%$ ) was estimated from Fig. 6. The evolution of the luminances with the data voltage is shown in Fig. 8b. The estimated luminance values ( $L_{display}$  and  $L_{emission}$ ) at maximum luminous flux for our display are about 50 and 120 cd/m², respectively.

#### 3. Conclusion

We fabricated and evaluated a small size 200 dpi 3-a-Si:H TFTs voltage-driven AM-PLED. We have demonstrated experimentally that the output current level in our 3-a-Si:H TFTs pixel electrode circuit is sufficient for AM-PLED. The brightness of the green light-emitting AM-PLED increases almost linearly up to 50 cd/m² with  $V_{\rm DATA}$  ranging from 0 to 30 V.

## 4. Acknowledgment

The authors would like to thank Dr. I. French at Philips Research Laboratory (U.K.) for assistance with the PECVD, and Mr. Y. Hong at the University of Michigan for the assistance with the PLED fabrication and display evaluation. This work was supported by NIH grant. The 3-a-Si:H TFTs AM-PLED was lit up for the first time on September 18, 2002 in our laboratory.

#### 5. References

- [1] Y. He, R. Hattori, and J. Kanicki: *IEEE Electron Device Lett.*, vol. 21, pp. 590-592 (2000).

- [2] Y. He, R. Hattori, and J. Kanicki: *Jpn. J. Appl. Phys.*, vol. 40, pp. 1199-1208 (2001).

- [3] J.A. Nichols et al.: SID 02 Digest, pp. 1368-1371 (2002).

- [4] M. Hack et al.: Proc. 22<sup>nd</sup> IDRC, pp. 21-24 (2002).

- [5] S. Tamura: Proc. of EL 2002, pp. 321-325 (2002).

- [6] G. Rajeswaran et al.: SID 00 Digest, pp. 974-977 (2000).

- [7] M. Kimura et al.: IEEE Trans. On Elec. Dev., vol. 46, pp. 2282-2287 (1999).

- [8] T. Shimoda et al.: SID 99 Digest, pp. 372-375 (1999).

- [9] J. Kanicki and J. Kim: Proc. of AM-LCD 02, pp. (2002).

- [10] C.-Y. Chen and J. Kanicki: IEEE Electron Dev. Lett., vol. 17, pp. 437-439 (1996).

- [11] C.-S. Chiang, J. Kanicki and K. Takechi: Jpn. J. Appl. Phys., vol. 37, pp. 4704-4710 (1998).

- [12] J.D. Gallezot, S. Martin and J. Kanicki: *Proc. Asia Display / IDW 01*, pp. 407-410 (2001).

- [13] N. Lustig, J. Kanicki, R. Wisnieff and J. Griffith: Mat. Res. Soc. Symp. Proc.: vol. 118, pp. 267-272 (1988).

- [14] J.-H. Kim and J. Kanicki: Proc. of SID '02 Sym., pp. 614-617 (2002).

- [15] J.-H. Kim and J. Kanicki: *Proc. of SPIE*, vol. 4319, pp. 306-318 (2001).

- [16] J.-H. Kim and J. Kanicki: *Proc. of SPIE*, vol. 4681, pp. 314-321 (2002).

- [17] J.-H. Kim, D. Lee, and J. Kanicki: *Proc. of 22nd Int. Display Res. Conf.*, pp. 601–604 (2002).

- [18] J. Kanicki et al.: Proc. Asia Display / IDW '01, pp. 315-318 (2001).

- [19] Y. Hong and J. Kanicki: Proc. Asia Display / IDW '01, pp. 1443-1446 (2001).

- [20] S. Lee, A. Badano and J. Kanicki: *Proc. of SPIE*, vol. 4800, pp. 156-163 (2003).