# Active-matrix organic light-emitting displays employing two thin-film-transistor a-Si:H pixels on flexible stainless-steel foil

Alex Z. Kattamis Noel Giebink I-Chun Cheng Sigurd Wagner Stephen R. Forrest Yongtaek Hong Vincent Cannella

**Abstract** — An active-matrix organic light-emitting diode (AMOLED) display driven by hydrogenated amorphous-silicon thin-film transistors (a-Si:H TFTs) on flexible, stainless-steel foil was demonstrated. The 2-TFT voltage-programmed pixel circuits were fabricated using a standard a-Si:H process at maximum temperature of 280°C in a bottom-gate staggered source–drain geometry. The 70-ppi monochrome display consists of (48 × 4) × 48 subpixels of 92 × 369 µm each, with an aperture ratio of 48%. The a-Si:H TFT pixel circuits drive top-emitting green electrophosphorescent OLEDs to a peak luminance of 2000 cd/m<sup>2</sup>.

*Keywords* — *Stainless steel, flexible substrate, AMOLED, a-Si:H, thin-film transistor, electrophosphorescence.*

#### 1 Introduction

Growing interest in flexible displays has extended to thinfilm transistor (TFT) backplanes on stainless-steel-foil substrates. Steel foils are attractive because of their tolerance to high-temperature processing, dimensional stability, chemical resistance, impermeability to moisture and other atmospheric contaminants, and a relatively low coefficient of thermal expansion.<sup>1</sup> a-Si:H TFTs on steel foil have been demonstrated,<sup>2</sup> and single TFTs have been integrated with organic light-emitting diodes (OLEDs).<sup>3</sup> Polycrystalline silicon (poly-Si) TFTs, which exhibit higher electron mobilities than a-Si:H TFTs, have also been fabricated on steel foil.<sup>4-8</sup> Whether a-Si:H or poly-Si is the best choice for active-matrix organic light-emitting diode (AMOLED) display pixels on steel foil remains unclear. Because steel is opaque, it can only serve with top-emitting OLEDs. When integrated with top emitters, the a-Si:H pixel circuit, 2-TFTs plus a storage capacitor  $(C_s)$ , may occupy most of the pixel area without reducing the display aperture ratio. In this case, the ratio is set solely by the width of the interconnects. Here, we show that the a-Si:H TFTs width-to-length (W/L) ratio can be made large enough<sup>9,10</sup> to deliver sufficient current to drive a top-emitting electrophosphorescent OLED.

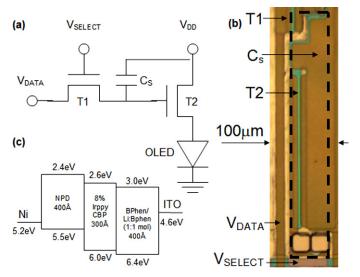

We fabricated AMOLED backplanes with an active pixel driver matrix of  $48 \times 48$  pixels and each pixel. Each pixel consists of four vertical strip subpixels with  $92 \times 369$ - $\mu$ m footprints for future application in a red-green-blue-white (RGBW) display. Each subpixel circuit is made with a switching TFT (T1) of gate width to length ratio W/L = 50  $\mu$ m/5  $\mu$ m, a driver TFT (T2), with  $W/L = 200 \ \mu$ m/5  $\mu$ m, and

**FIGURE 1** — (a) Circuit schematic of a display subpixel. (b) Optical micrograph of one pixel with the TFTs and capacitance,  $C_s$  indicated. The dashed-box outlines the location and size of the OLED. (c) Energy-level diagram of the OLED structure.

a storage capacitor  $C_S \cong 2$  pF, as shown in Fig. 1(a). For expedient evaluation, the data lines of four subpixels are connected such that one data signal lights up one full pixel at a time. Figure 1(b) is the optical micrograph of one subpixel. The active OLED area is denoted by the dashed rectangle. By employing 20-µm-wide interconnect lines leaves a pixel aperture ratio of 48% was employed. A blanket electrophosphorescent<sup>11,12</sup> top-emitting<sup>13,14</sup> green OLED array with a transparent indium tin oxide (ITO) cathode completes the display. The sequence, composition, thicknesses, and energy levels of the OLED layers are shown in Fig. 1(c).

A. Z. Kattamis, N. Giebink, I-C. Cheng, and S. Wagner, Department of Electrical Engineering and the Princeton Institute for the Science and Technology of Materials (PRISM), Princeton University, Princeton, University, Princeton, NJ 08544; telephone/fax 609/285-5902, e-mail: Kattamis@princeton.edu.

S. R. Forrest is with the Departments of Electrical Engineering and Computer Science, Physics, and Materials Science and Engineering, University of Michigan, Ann Arbor, MI.

Y-T. Hong is with the School of EECS, Seoul National University, Seoul, Korea.

V. Cannella is with Energy Conversion Devices, Inc., Rochester Hills, MI.

<sup>©</sup> Copyright 2007 Society for Information Display 1071-0922/07/1507-0433\$1.00

## 2 **Experiments**

The 125- $\mu$ m-thick 5 × 5 cm<sup>2</sup> stainless-steel-foil substrates had an "as-received" roughness of  $\sim 1.2 \ \mu m$  peak-to-peak. The roughness was due to unidirectional grooves formed when the steel is rolled into sheets. Along with this roughness, the substrate has point-defect-like inclusions with a height of  $\sim 1 \,\mu\text{m}$ . Because such roughness and defects decrease display yield by causing shorts in the OLEDs and breaks in the interconnect lines, we planarized the substrates with 2.5 µm of siloxane spin-on glass. Then, an electrically insulating layer of 200-nm-thick SiO<sub>2</sub> was deposited at 300°C by plasma-enhanced chemical vapor deposition (PE-CVD).<sup>15</sup> Next, a 90-nm-thick Cr gate metal layer was deposited by thermal evaporation and patterned using Cr-7S wet etch from Cyantek Corp.<sup>16</sup> The TFT stack of 340-nm-thick SiN<sub>x</sub>, 200-nm-thick intrinsic (i) a-Si:H, and 50-nm-thick doped  $n^+$ a-Si:H layer was deposited by PE-CVD at 500-mTorr using a 13.56-MHz RF power density of 66 mW/cm<sup>2</sup>. The gate SiN<sub>x</sub> was deposited at 280°C from SiH<sub>4</sub>:NH<sub>3</sub> at a flow ratio of 1:9, the a-Si:H from SiH<sub>4</sub> at 230°C, and the  $n^+$  a-Si:H from SiH<sub>4</sub>:PH<sub>3</sub> = 70:1 at 230°C. Next, a-Si:H islands and gate vias were patterned by reactive ion etching (RIE) at 100 mTorr and power density of 140 mW/cm<sup>2</sup>. A gas flow ratio of  $SF_6/CCl_2F_2 = 6:2$  was used to etch the a-Si:H, and  $CF_4/O_2 = 7:1$  for the gate vias. The source-drain and interconnect metal tri-layer of 50-nm-thick evaporated Cr, 200nm-thick sputtered Al-1% Si, and 50-nm-thick sputtered Cr layer were then deposited. Al-1% Si has a low tendency for hillock formation,<sup>17</sup> and sputtering ensures good step coverage and low via and interconnect resistances. The Cr was patterned with Cr-7S wet etch, and the Al-1% Si using a mixture of  $H_3PO_4$ :  $H_2O$ :  $HNO_3$ :  $CH_3CO_2H = 6:2:1:1$ . The  $n^+$ layer was etched with RIE at 100 mTorr and 140 mW/cm<sup>2</sup> by  $CCl_2F_2:O_2 = 7:1$ , which completed the TFT pixel circuits.

Prior to OLED deposition, the TFT backplanes were passivated with a 1- $\mu$ m-thick layer of SiN<sub>x</sub> deposited at 200°C by PE-CVD from SiH<sub>4</sub>:NH<sub>3</sub> = 1:9 at 500 mTorr using a power density of 66 mW/cm<sup>2</sup>. Next, vias for the T2 sourceto-OLED anode connection were etched by RIE using CF<sub>4</sub>/O<sub>2</sub> = 7:1. A bi-layer anode of 200-nm-thick Al–1%Si and 50-nm-thick Cr was then deposited and patterned. To planarize the TFT relief replicated in the SiN<sub>x</sub> layer, AZ5209 photoresist was spun on at 4000 rpm, patterned to form windows to the anode and baked at 200°C for 10 min to form windows to the anode. A 5-nm-thick layer of Ni was sputter-deposited and exposed to UV-generated O<sub>3</sub> for 5 min to oxidize the Ni surface in preparation for OLED deposition.

The organic layers, shown in Fig. 1(c), were sequentially deposited from pre-purified<sup>18</sup> source materials by thermal evaporation at rates of 2–3 Å/sec without breaking vacuum ( $1 \times 10^{-7}$  Torr). Hole transport between the oxidized Ni anode and the emissive layer was facilitated by a 400-Å-thick layer of 4,4'-bis[N-(1-naphthyl)-N-phenylamino]-biphenyl (NPD). The emissive layer consists of 300

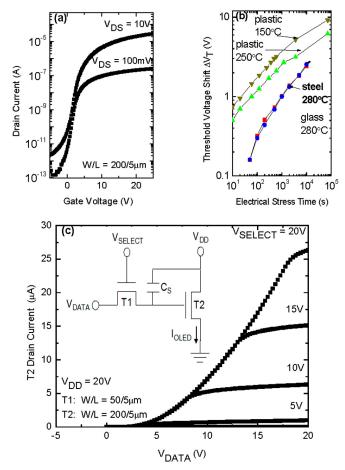

**FIGURE 2** — (a) Transfer characteristics for the a-Si:H TFT for drain-to-source voltages ( $V_{DS}$ ) of 100 mV and 10 V. (b) Threshold-voltage shift ( $\delta V_T$ ) vs. stress time for TFTs deposited at 280°C on steel and glass, including results for 150°C and 250°C TFTs on plastic for comparison.<sup>19</sup> The 280°C TFTs on steel and glass have almost the same  $\Delta V_T$ . (c) Source current for T2 (OLED) in a subpixel circuit versus  $V_{DATA}$  for  $V_{SELECT}$  = 0–20 V in 5-V steps.

Å of 4,4'-bis(N-carbazolyl)biphenyl (CBP) co-doped at 10 wt.% with the metalorganic phosphor, *fac*-tris(2-phenyl-pyridine) iridium [Ir(ppy)<sub>3</sub>].<sup>11,12</sup> A 200-Å-thick layer of 4,7-diphenyl-1,10-phenanthroline (BPhen), followed by a 200-Å-thick Li-doped BPhen layer at a 1:1 molar ratio,<sup>14</sup> serve to transport electrons from the cathode while confining excitons within the emissive layer. The structure was completed by depositing the transparent 50-nm ITO cathode through a shadow mask, using RF magnetron sputtering at a power of 100 mW/cm<sup>2</sup> to obtain a rate of 0.5 Å/sec.<sup>13</sup> Control devices of the same structure were grown on glass substrates. They had peak forward-emitted external quantum efficiency of  $(3.0 \pm 0.2)$ % at a luminance of 200 cd/m<sup>2</sup>.

#### 3 Pixel circuit and display results

Electrical characteristics were measured using an HP4145 parameter analyzer. The transfer characteristics of an a-Si:H driver TFT (T2) are shown in Fig. 2(a). The TFTs have a threshold voltage  $V_{\rm T} \cong 3$  V, current ON/OFF ratio  $I_{\rm ON}/I_{\rm OFF} \cong 10^7$ , sub-threshold slope  $S \cong 500$  mV/dec, and

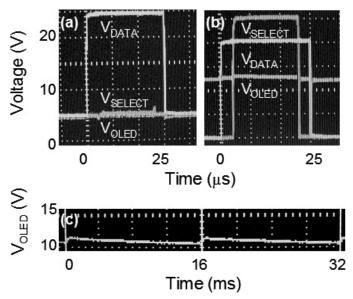

**FIGURE 3** — Transient measurements of  $V_{OLED}$  using a 16-msec frame time and  $V_{DATA}$  width of 26 µsec and 20 V for (a)  $V_{DATA}$  = 25 V and  $V_{SELECT}$  = 0 V, (b)  $V_{DATA}$  = 20 V and  $V_{SELECT}$  = 25 V, and (c) two frames.

saturation electron mobility  $\mu_{sat} \cong 0.5~{\rm cm}^2/{\rm V}\text{-sec}$ . The stability of the TFTs was tested at a fixed gate-to-source/drain field of  $10^6$  V/cm, applied in successive stress periods of 10–10,000 sec. After each period, the transfer curve was measured and the threshold voltage was extracted. Figure 2(b) is a plot of  $\Delta V_T$  vs. gate-bias stress time. The plot includes results for a-Si TFTs deposited at 150°C and 250°C<sup>19</sup> on plastic and at 280°C on glass. Deposition at high temperature clearly improves TFT stability. Steel-foil substrates have an advantage over most plastic substrates in their temperature tolerance.

The 2-TFT pixel circuits were evaluated before OLED deposition by grounding the source of T2 in the absence of an OLED load, with results shown in Fig. 2(c). The select line voltage ( $V_{\text{SELECT}}$ ) was stepped in 5-V intervals from 0 to 20 V, and the data input voltage ( $V_{\text{DATA}}$ ) was swept from 0 V to 20 V, at a power supply voltage  $V_{\text{DD}} = 20$  V. At an OLED terminal, the leakage current of the pixel at  $V_{\text{DATA}} = V_{\text{DD}} = 20$  V and  $V_{\text{SELECT}} = 0$  V lay below ~10 pA; the output current reached 26  $\mu$ A at  $V_{\text{DATA}} = V_{\text{SELECT}} = 20$  V.

Transient voltage measurements were performed on a pixel circuit within the array, to ascertain sufficiently low pixel leakage during a frame time. A 1-M $\Omega$  resistor substituted for the OLED. The pixel was biased with  $V_{DD} = 20$  V and was pulsed with  $V_{SELECT}$  between 0 and 25 V and  $V_{DATA}$  between 0 and 25 V. The pulse widths were 26 µsec for  $V_{DATA}$  and 20-µsec for  $V_{SELECT}$ , and the frame time was 16 msec. Figure 3(a) shows that  $V_{OLED}$  remains at 0 V when  $V_{SELECT} = 0$  V. Figure 3(b) is one in a sequence of identical frames, which show that  $V_{OLED} = 12.5$  V, corresponding to a T2 current of 12 µA at  $V_{SELECT} = 25$  V. Figure 3(c) shows two frames (32 msec) with a drop in  $V_{OLED}$  voltage of <350 mV per frame.

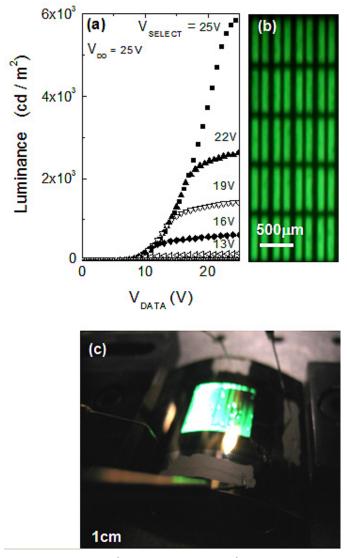

Completed OLED pixels were biased using an HP4145 analyzer, and the luminance of individual OLEDs was measured using a calibrated photodiode.<sup>20</sup> Figure 4(a) shows the luminance versus  $V_{DATA}$  and  $V_{SELECT}$  at  $V_{DD}$  = 25 V for one such pixel. For  $V_{SELECT} < 4$  V no luminance was observed and the maximum luminance of ~2000 cd/m<sup>2</sup> was reached at  $V_{DATA} = V_{SELECT} = 25$  V. A target luminance of ~100 cd/m<sup>2</sup>, which is a standard number for a desktop display.<sup>9,10</sup> is reached at  $V_{DATA} = 7$  V and  $V_{SELECT} = 10$  V. This turn-on voltage could be further reduced by using a more efficient OLED. To evaluate the functionality of the full display while it is flexed we tied all the address lines together, and bent it to a radius of ~50 cm. The pixel emission was uniform as evident from Fig. 4(b). The entire display is shown in Fig. 4(c).

**FIGURE 4** — (a) OLED luminance versus  $V_{\text{DATA}}$  for  $V_{\text{SELECT}} = 13-25$  V in 3-V steps. (b) Optical micrograph of a subarray of 8 × 5 active subpixels. (c) Entire display flexed to a radius of 50 cm.

## 4 Conclusions

We demonstrated an AMOLED display using 2-TFT a-Si:H pixels circuits fabricated at 280°C on flexible stainless-steel foil. We conclude that an a-Si:H TFT backplane based on flexible steel foil can power a bright top-emitting AMOLED display based on electrophosphorescent OLEDs. The stability of the TFTs on steel was measured and found to be superior to low-temperature a-Si:H TFTs on plastic and performs comparably to our results on display glass. The next step is to implement a design using 4-TFT pixel circuits for improved long-term stability of AMOLED operation.<sup>9,10</sup>

# **Acknowledgments**

A. Z. Kattamis and S. Wagner thank the Eastman Kodak Company, the Princeton Plasma Physics Laboratory, and the New Jersey Commission for Science and Technology for financial support. N. Giebink and S. R. Forrest thank Universal Display Corp. for support. Y. Hong thanks Mr. Dustin Winters at Eastman Kodak Company for technical discussion on AMOLED frontplane integration, and V. Cannella thanks the U.S. Display Consortium for supporting research on the preparation of stainless-steel-foil substrates.

## References

- V Cannella, M Izu, S Jones, S Wagner, and I-C Cheng, "Flexible substrates – Is steel real?" *Information Display*, 24–27 (June 2005).

- 2 S D Theiss and S Wagner, "Amorphous silicon thin-film transistors on steel foil substrates," *IEEE Electron Dev Lett* **17**, 578–580 (1996).

- 3 C C Wu, S D Theiss, G Gu, M H Lu, J C Sturm, S Wagner, and S R Forrest, "Integration of organic LEDs and amorphous Si TFTs onto flexible and lightweight metal foil substrates," *IEEE Electron Dev Lett* 18, 609–612 (1997).

- 4 T Serikawa and F Omata, "High-mobility poly-Si TFTs fabricated on flexible stainless-steel substrates," *IEEE Electron Dev Lett* 20, 574–576 (1999).

- 5 M Wu, K Pangal, J C Sturm, and S Wagner, "High temperature polycrystalline silicon thin film transistor on steel substrates," *IEDM Tech Dig*, 119–122 (1999).

- 6 R S Howell, M Stewart, S V Karnik, S K Saha, and M K Hatalis, "Poly-Si thin-film transistors on steel substrates," *IEEE Electron Dev Lett* 21, 70–72 (2000).

- 7 A Chwang, R Hewitt, K Urbanik, J Silvernail, K Rajan, M Hack, J Brown, J Lu, C Shih, J Ho, R Street, K Tognoni, B Anderson, D Huffman, T Ramos, L Moro, and N Rutherford, "Full color 100 dpi AMOLED displays on flexible stainless steel substrates," *SID Sympo*sium Digest Tech Papers 37, 1858–1861 (2006).

- 8 T Afentakis, M Hatalis, A T Voutsas, and J Hartzell, "Design and fabrication of high-performance polycrystalline silicon thin-film transistor circuits on flexible steel foils," *IEEE Trans Electron Dev* 53, 815–822 (2006).

- 9 P Servati, S Prakash, A Nathan, and P Christoph, "Amorphous silicon driver circuits for organic light-emitting diode displays," J Vac Sci Technol, A, 20, 1374–1378 (2002).

- 10 K Sakariya, S Sambandan, P Servati, and A Nathan, "Analysis and characterization of self-compensating current programmed a-Si:H active matrix organic light-emitting diode pixel circuits," J Vac Sci Technol, A 22, 1001–1004 (2004).

- 11 M A Baldo, D F O'Brien, Y You, A Shoustikov, S Sibley, M E Thompson, and S R Forrest, "Highly efficient phosphorescent emission from organic electroluminescent devices," *Nature* **395**, 151–154 (1998).

- 12 M A Baldo, S Lamansky, P E Burrows, M E Thompson, and S R Forrest, "Very high-efficiency green organic light-emitting devices based on electrophosphorescence," *Appl Phys Lett* **75**, 4–6 (1999).

- 13 G Parthasarathy, P E Burrows, V Khalfin, V G Kozlov, and S R Forrest, "A metal-free cathode for organic semiconductor devices," *Appl Phys Lett* 72, 2138–2140 (1998).

- 14 H Kanno, Y Sun, and S R Forrest, "High-efficiency top-emissive whitelight-emitting organic electrophosphorescent devices," *Appl Phys Lett* 86, 263502 (1–3) (2005).

- 15 M Wu, X Bo, J C Sturm, and S Wagner, "Complementary metal-oxidesemiconductor thin-film transistor circuits from a high-temperature polycrystalline silicon process on steel foil substrates," *IEEE Trans Electron Dev* **49**, 1993–2000 (2002).

- 16 Cyantek Corporation, Inc., 3055 Osgood Court, Fremont, CA 94539.

- 17 M Zaborowski and P Dumania, "Kinetics of Hillock growth in Al and Al-alloys," *Microelec Eng* 50, 301–309 (2000).

- 18 S R Forrest, "Ultrathin organic films grown by organic molecular beam deposition and related techniques," *Chem Rev* 97, 1793–1896 (1997).

- 19 K Long, A Z Kattamis, I-C Cheng, H Gleskova, S Wagner, and J C Sturm, "Stability of amorphous-silicon TFTs deposited on clear plastic substrates at 250°C to 280°C," *IEEE Electron Dev Lett* 27, No. 2, 111–113 (2006).

- 20 S R Forrest, D D C Bradley, and M E Thompson, "Measuring the efficiency of organic light-emitting devices," Adv Mater 15, No. 13, 1043–1048 (2003).

Alex Z. Kattamis is currently a Ph.D. candidate in the electrical engineering department at Princeton University, where he focuses on silicon thinfilm-transistor backplanes on flexible steel and polymer substrates. He received his M.A. degree in electrical engineering at Princeton University in 2004 and his B.S.E degree from the Electrical and Computer Engineering Department at the University of Connecticut in 2002.

I-Chun Cheng received her B.S. and M.S. degrees in mechanical engineering at National Taiwan University in 1996 and 1998, respectively. In 2004, she received her Ph.D. degree in electrical engineering from Princeton University and became a research staff at Princeton University. She has primarily worked in the field of flexible large-area electronics. She is currently on the faculty at National Taiwan University.

Sigurd Wagner is developing technology for flexible and conformally shaped large-area displays, electrotextiles, and elastic electronic skin. His work includes thin-film silicon on plastic and steel foil, the interdependence of electrical and mechanical properties in film-on-foil electronics, and functional cells for large-area electronics, including displays, multifunctional materials, and sensor skin. He received his Ph.D. from the University of Vienna in 1968, was a postdoctoral fel-

low at Ohio State University, a member of technical staff of the Bell Telephone Laboratories, Chief of the Photovoltaic Research Branch of the Solar Energy Research Institute, and since 1980 has been Professor of Electrical Engineering at Princeton University.

Yongtaek Hong received his B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, South Korea, in 1994 and 1996, and his Ph.D. in electrical engineering from the University of Michigan, Ann Arbor, Michigan, U.S.A., in 2003. He has more than 40 journal papers and conference presentations. He has been an Assistant Professor at the School of EECS, Seoul National University, Seoul, Korea, since 2006. From 2003 to 2006, he was a senior research sci-

entist at the Display Science & Technology Center, Eastman Kodak Company, Rochester, New York, U.S.A. His research interests are thin-film electronic devices and flexible electronics including flat-panel displays and digital radiography sensor arrays. Dr. Hong received the Korea Foundation for Advanced Studies Scholarship from 1997 to 2002 and College of Engineering Graduate Student Distinguished Achievement Awards from University of Michigan in 2003. He is a member of SID.

**Stephen R. Forrest** received his B.A. degree in physics in 1972 from the University of California, his M.Sc. and Ph.D. degrees in physics in 1974 and 1979, respectively, from the University of Michigan. First, at Bell Labs, he investigated photodetectors for optical communications. In 1985, he joined the Electrical Engineering and Materials Science Departments at USC where worked on optoelectronic integrated circuits and organic semiconductors. In 1992, Prof. Forrest became

the James S. McDonnell Distinguished University Professor of Electrical Engineering at Princeton University. He served as Director of the National Center for Integrated Photonic Technology and as Director of Princeton's Center for Photonics and Optoelectronic Materials (POEM). From 1997 to 2001, he served as the Chair of Princeton's Electrical Engineering Department. In 2006, he rejoined the University of Michigan as Vice President for Research and as the William Gould Dow Collegiate Professor in Electrical Engineering, Materials Science and Engineering, and Physics. He has authored ~400 papers in refereed journals and has 150 patents. He is co-founder or founding participant in several companies including Sensors Unlimited, Epitaxx, Inc., Global Photonic Energy Corp., Universal Display Corp., and ASIP, Inc.