# INTELLIGENT MANAGEMENT OF INTER-THREAD SYNCHRONIZATION DEPENDENCIES FOR CONCURRENT PROGRAMS

by

### Hyoun Kyu Cho

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2014

#### **Doctoral Committee:**

Professor Scott Mahlke, Chair Terence Kelly, HP Labs Professor Stéphane Lafortune Professor Trevor Mudge Assistant Professor Satish Narayanasamy © Hyoun Kyu Cho 2014 All Rights Reserved

To my family

#### **ACKNOWLEDGEMENTS**

First, I would like to express my sincerest gratitude to my advisor, Prof. Scott Mahlke, for his continuous guidance and support. In Korean culture, teacher-student relationships are thought to be very important and respected very much. They are often metaphorically compared to father-son relationships. While I think my relationship with Scott is quite close to the ideal, it is not because I am a traditional Korean but it is because Scott is a true mentor.

I also owe thanks to the remaining members of my dissertation committee, Prof. Stéphane Lafortune, Prof. Trevor Mudge, Prof. Satish Narayanasamy, and Dr. Terence Kelly. They gave me a lot of advices, supports, ideas, and encouragements. This dissertation also includes results from joint work with Dr. Yin Wang, Dr. Hongwei Liao, Dr. Tipp Moseley, Dr. Richard Hank, and Dr. Derek Bruening. I am grateful for these wonderful teachers that I could meet over the graduate school years.

I was fortunate to be among my fellow comrades in the Compilers Creating Custom Processors (CCCP) group. They not only helped me intellectually with the discussions and feedbacks, but also made my graduate school life much more fun and enjoyable with the endless kitchen runs and the actual runs. I would like to thank the members (and honorary members) of the CCCP group: Hyunchul Park, Mojtaba Mehrara, Amir Hormati, Shantanu

Gupta, Shuguang Feng, Ganesh Dasika, Amin Ansari, Sangwon Seo, Mark Woh, Yongjun Park, Jeff Hao, Po-Chun Hsu, Mehrzad Samadi, Ankit Sethia, Gaurav Chadha, Anoushe Jamshidi, Daya Khudia, Andrew Lukefahr, Janghaeng Lee, Jason Jong Kyu Park, Shruti Padmanabha, Silky Arora, and John Kloosterman.

Above all, the utmost of thanks go to my dear family. Whatever I am today, I exist thanks to the unconditional love and support of my parents, Hang Cheol Cho and Young Soo Kim. Learning how things work from my late grandfather, Myoung Kwon Kim, made me not hesitate a moment to choose becoming an engineer. I still remember the day my uncle, Joo Youn Kim, taught me how to use Norton Commander on MS-DOS 5.0 and such days led me to take computer engineering as my major. Finally and most importantly, I truly thank my wife, Hyo Jin Lee, for turning my life into the happiest one.

# TABLE OF CONTENTS

| <b>DEDICATION</b> | i                                                              |

|-------------------|----------------------------------------------------------------|

| ACKNOWLED         | GEMENTS                                                        |

| LIST OF FIGU      | RES vii                                                        |

| LIST OF TABL      | <b>ES</b>                                                      |

| ABSTRACT .        |                                                                |

| CHAPTERS          |                                                                |

| 1 Introdu         | action                                                         |

| 1.1               | Correctness Challenges                                         |

| 1.2               | Efficiency Challenges                                          |

| 1.3               | Contributions                                                  |

| 2 Practic         | al Lock/Unlock Pairing                                         |

| 2.1               | Introduction                                                   |

| 2.2               | Background and Motivation                                      |

|                   | 2.2.1 Gadara                                                   |

|                   | 2.2.2 Challenges for Lock/Unlock Pairing                       |

| 2.3               | Static Lock/Unlock Pairing Analysis                            |

|                   | 2.3.1 Simple Example of Analysis Flow                          |

|                   | 2.3.2 Mapping Lock to Set of Corresponding Unlocks 2           |

|                   | 2.3.3 Path Condition Calculation                               |

|                   | 2.3.4 Checking Lock/Unlock Pairing                             |

|                   | 2.3.5 CFG Pruning                                              |

| 2.4               | Inter-procedural Analysis                                      |

|                   | 2.4.1 Proximity-based Callgraph Partitioning                   |

|                   | 2.4.2 Extending Lock/Unlock Pairing for Inter-procedural Anal- |

|                   | ysis                                                           |

| 2.5               | Dynamic Checking                                               |

|                   | 2.5.1 Checking Lock-to-Unlocks Mapping                         |

|   |         | 2.5.2 Checking Semiflow Property                          | 31 |

|---|---------|-----------------------------------------------------------|----|

|   | 2.6     | Experimental Results                                      | 32 |

|   |         | 2.6.1 Effectiveness of Static Analysis                    | 32 |

|   |         | 2.6.2 Runtime Overhead of Dynamic Checking                | 35 |

|   |         | 2.6.3 Assumption Violation                                | 37 |

|   | 2.7     | Related Work                                              | 38 |

|   | 2.8     | Summary                                                   | 43 |

| 3 | Dynan   | ic Core Boosting and Per-Core Power Gating                | 44 |

|   | 3.1     | Introduction                                              | 44 |

|   | 3.2     | Motivation and Background                                 | 48 |

|   |         | 3.2.1 Low Utilization of Asymmetric CMPs                  | 48 |

|   |         | 3.2.2 Core Boosting                                       | 51 |

|   |         | 3.2.3 Per-Core Power Gating                               | 52 |

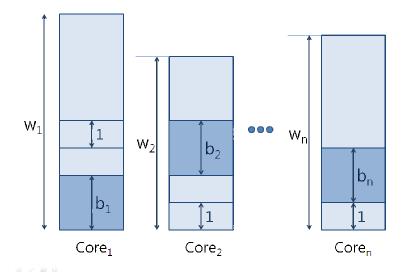

|   | 3.3     | Core Boosting Assignment                                  | 53 |

|   |         | 3.3.1 Modeling and Problem Formulation                    | 55 |

|   |         | 3.3.2 Assignment for Data Parallel Programs               | 57 |

|   |         | 3.3.3 Assignment for Pipeline Parallel Programs           | 59 |

|   | 3.4     | Synchronization-Aware Dynamic Core Boosting               | 61 |

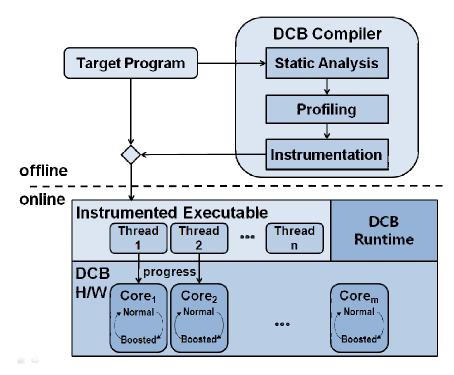

|   |         | 3.4.1 System Overview                                     | 61 |

|   |         | 3.4.2 DCB Architecture                                    | 62 |

|   |         | 3.4.3 DCB Compiler                                        | 64 |

|   |         | 3.4.4 DCB Runtime Subsystem                               | 67 |

|   | 3.5     | Synchronization-Aware Per-Core Power Gating               | 68 |

|   |         | 3.5.1 Operating System Support                            | 68 |

|   |         | 3.5.2 Profiling-based Selective Power Gating              | 69 |

|   |         | 3.5.3 Wakeup Hint and Prefetching                         | 70 |

|   | 3.6     | Evaluation Methodology                                    | 70 |

|   |         | 3.6.1 DBT-based Performance Evaluation                    | 71 |

|   |         | 3.6.2 Evaluation of Energy Saving                         | 74 |

|   | 3.7     | Experimental Results                                      | 74 |

|   |         | 3.7.1 Accuracy of DBT-based Performance Evaluation        | 75 |

|   |         | 3.7.2 DCB Performance Improvement                         | 76 |

|   |         | 3.7.3 Energy Saving of Synchronization-Aware Power Gating | 80 |

|   | 3.8     | Related Work                                              | 82 |

|   |         | 3.8.1 Performance Asymmetry in CMPs                       | 83 |

|   |         | 3.8.2 Dynamic Adaptation of Core Performance              | 83 |

|   |         | 3.8.3 Thread Criticality Assessment                       | 84 |

|   | 3.9     | Summary                                                   | 86 |

| 4 | Instrun | nentation Sampling for Lightweight Profiling              | 88 |

|   | 4.1     | Introduction                                              | 88 |

|   | 4.2     | Background                                                | 92 |

|   |         | 4.2.1 Dynamic Binary Instrumentation                      | 92 |

|   |         | 4.2.2 Overview of DynamoRIO                               | 93 |

| 4.3        | Instrumentation Sampling                               |

|------------|--------------------------------------------------------|

|            | 4.3.1 Context Switch                                   |

|            | 4.3.2 Temporal Unlinking and Relinking of Fragments 97 |

|            | 4.3.3 Multi-threaded Programs                          |

|            | 4.3.4 Summarizing Profile Data                         |

| 4.4        |                                                        |

|            | 4.4.1 Finding Basic Block Headers 100                  |

|            | 4.4.2 Affinity-based Pre-population                    |

| 4.5        | Performance Evaluation                                 |

|            | 4.5.1 Experimental Configuration                       |

|            | 4.5.2 Edge Profiling                                   |

|            | 4.5.3 Performance Overhead                             |

|            | 4.5.4 Profiling Accuracy                               |

| 4.6        | Related Work                                           |

| 4.7        | Summary                                                |

| 5 Concl    | usion                                                  |

| 5.1        | Summary                                                |

| 5.2        | Future Work                                            |

| RIRLIOGRAP | HV 110                                                 |

# LIST OF FIGURES

| Figure |                                                                                                       |    |

|--------|-------------------------------------------------------------------------------------------------------|----|

| 1.1    | Speedup of PARSEC [11] benchmarks with varying number of threads compared to single thread executions | ć  |

| 1.2    | CPU cycles spent blocked for synchronization operations                                               | 7  |

| 2.1    | Infeasible path example                                                                               | 10 |

| 2.2    | Challenges for lock/unlock pairing                                                                    |    |

| 2.3    | Simple example of lock/unlock pairing                                                                 | 18 |

| 2.4    | Finding unlock set corresponding to lock                                                              | 19 |

| 2.5    | Calculating path conditions                                                                           | 22 |

| 2.6    | Example of CFG pruning                                                                                | 25 |

| 2.7    | Example of uncaught infeasible path                                                                   | 28 |

| 2.8    | Instrumentation wrapper for lock and unlock                                                           | 30 |

| 2.9    | Example of unpaired lock due to type mismatch                                                         | 33 |

| 2.10   | Runtime overheads of dynamic checking                                                                 |    |

| 2.11   | Incorrectly paired lock due to pointer problem                                                        |    |

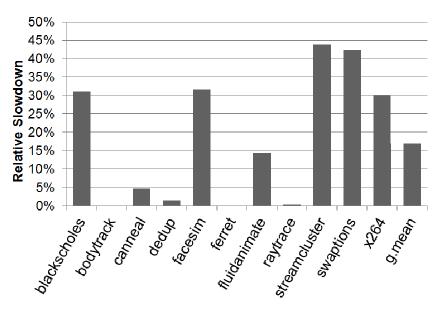

| 3.1    | Slowdown caused by performance asymmetry                                                              | 48 |

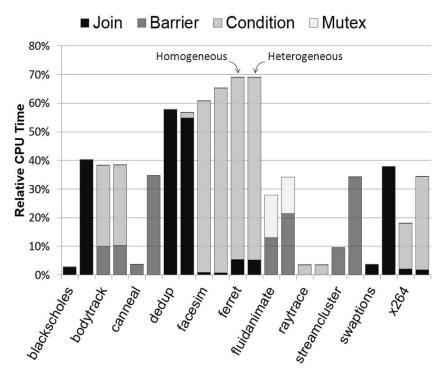

| 3.2    | CPU time wasted for synchronization                                                                   | 50 |

| 3.3    | Modeling of workload imbalance and core boosting                                                      | 55 |

| 3.4    | Dynamic Core Boosting system overview                                                                 | 61 |

| 3.5    | Example of progress reporting instrumentation                                                         | 65 |

| 3.6    | Core boosting emulation with dynamic binary translation                                               | 72 |

| 3.7    | Errors in the simulated execution time of the performance asymmetry eval-                             | 75 |

| 3.8    | uation platform.                                                                                      |    |

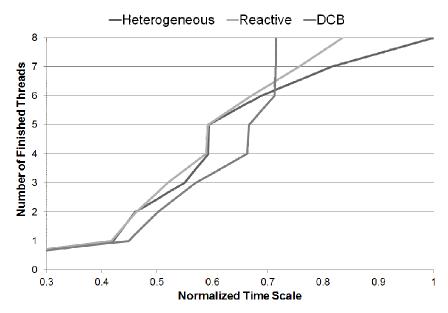

| 3.9    | Normalized execution time of Heterogeneous, Reactive, and DCB                                         | 76 |

|        | Synchronization overheads of Heterogeneous, Reactive and DCB                                          | 78 |

|        |                                                                                                       | 79 |

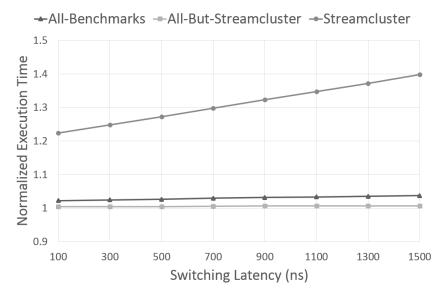

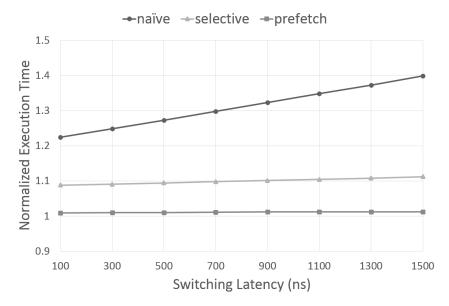

|        | Overhead of synchronization-aware per-core power gating                                               |    |

|        | Impact of optimization for streamcluster.                                                             |    |

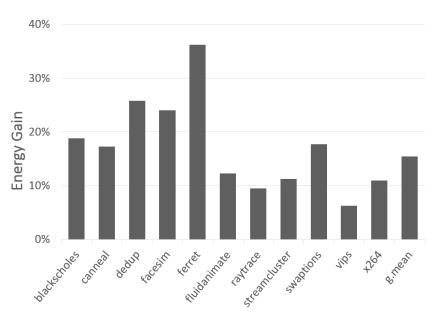

|        | Energy savings of synchronization-aware per-core power gating                                         |    |

| 4.1    | Control transfer for instrumentation sampling                                                         | 95 |

| Traditional vs. DynamoRIO's basic blocks                                    | 1                          |

|-----------------------------------------------------------------------------|----------------------------|

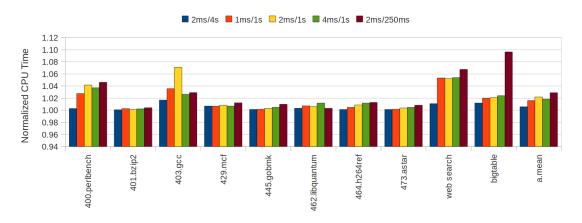

| Overhead of edge profiling                                                  | 13                         |

| Execution time overhead of the instant profiling framework across five con- |                            |

| figurations of (duration / frequency)                                       | 4                          |

| Computational overhead of the instant profiling framework across five con-  |                            |

| figurations of (duration / frequency)                                       | 4                          |

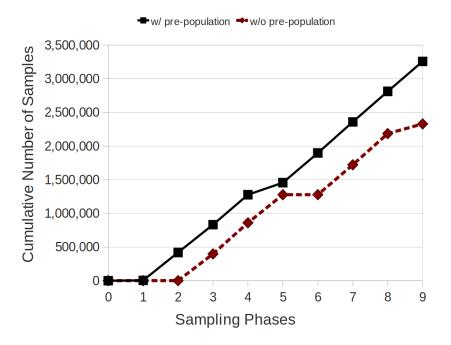

| Effect of pre-populating a software code cache                              | 6                          |

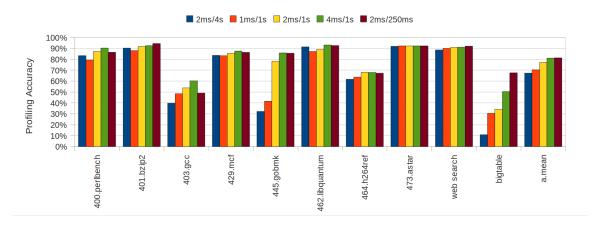

| Edge profiling accuracy of the instant profiling framework across five con- |                            |

| figurations of (duration / frequency)                                       | 7                          |

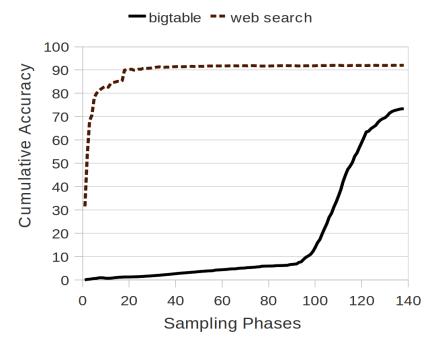

| Asymptotic edge profiling accuracy                                          | 0                          |

|                                                                             | Overhead of edge profiling |

# LIST OF TABLES

| Table |                                                 |    |

|-------|-------------------------------------------------|----|

| 2.1   | Number of annotations needed to model           | 12 |

| 2.2   | Coverage of static lock/unlock pairing analysis | 28 |

| 2.3   | Number of Basic Blocks before/after Pruning     | 35 |

| 2.4   | Number of Unlocks in Corresponding Unlock Sets  | 37 |

| 3.1   | Simulated architecture details                  | 74 |

**ABSTRACT**

INTELLIGENT MANAGEMENT OF INTER-THREAD

SYNCHRONIZATION DEPENDENCIES FOR CONCURRENT PROGRAMS

by

Hyoun Kyu Cho

Chair: Scott Mahlke

Power dissipation limits and design complexity have made the microprocessor industry

less successful in improving the performance of monolithic processors, even though semi-

conductor technology continues to scale. Consequently, chip multiprocessors (CMPs) have

become a standard for all ranges of computing from cellular phones to high-performance

servers. As sufficient thread level parallelism (TLP) is necessary to exploit the computa-

tional power provided by CMPs, most performance-aware programmers need to parallelize

their programs.

For shared memory multi-threaded programs, synchronization mechanisms such as mu-

texes, barriers, and condition variables, are used to enforce the threads to interact with each

other in the way the programmers intended. However, employing synchronization oper-

хi

ations in both correct and efficient way at the same time is extremely difficult, and there have been trade-offs between programmability and efficiency of using synchronizations.

This thesis proposes a collection of works that increase the programmability and efficiency of concurrent programs by intelligently managing the synchronization operations. First, we focus on mutex locks and unlocks. Many concurrency bug detection tools and automated bug fixers rely on the precise identification of critical sections guarded by lock/unlock operations. We suggest a practical lock/unlock pairing mechanism that combines static analysis with dynamic instrumentation to identify critical sections in POSIX multi-threaded C/C++ programs. Second, we present Dynamic Core Boosting (DCB) to accelerate critical paths in multi-thread programs. Inter-thread dependencies through synchronizations form critical paths. These critical paths are major performance bottlenecks for concurrent programs, and they are exacerbated by workload imbalances in performance asymmetric CMPs. DCB coordinates its compiler, runtime subsystem, and architecture to mitigate such performance bottlenecks. In addition, we propose exploiting synchronization operations for better energy efficiency through dynamic power management, while maintaining performance. Finally, combining instrumentation sampling with dynamic binary translation is suggested for low overhead profiling.

Although the works presented in this thesis address a variety of issues related to synchronizations from correctness to performance and energy efficiency, they are all inspired by the same observation that neither a static nor a dynamic approach is sufficient for intelligent management of synchronizations. Based on this observation, we combine compiler techniques to analyze programs without burdening the execution of programs and runtime techniques to adjust the execution with more accurate information. By applying this theme

of hybrid static/dynamic mechanism to managing synchronization dependencies, we explore the possibility of increasing programmability and efficiency of concurrent programs.

#### **CHAPTER 1**

#### Introduction

The semiconductor industry continues to scale down the size of individual transistor according to Moore's law. Increasing clock frequencies and exploiting instruction level parallelism (ILP) have been the main methodologies to turn the technology scaling into application performance gains for more than four decades. In recent years, however, CPU clock frequencies have flattened out due to power dissipation and thermal constraints. Similarly, design complexity and verification issues inhibit computer architects from exploiting more ILP. For these reasons, improving the performance of monolithic processors has become less successful, and chip multiprocessors (CMPs) have grown into a mainstream paradigm to improve application performance with the increased transistor counts, for all ranges of computing from cellular phones to high-performance servers. Since CMPs require sufficient thread level parallelism (TLP) to benefit from the provided computing power, most performance-conscious programmers face increasing pressure to parallelize their programs.

In shared-memory multi-threaded programs, which is the most prevalent programming model for CMPs, threads communicate with each other by reading from and writing to the

shared memory. The value read from the shared memory changes depending on the order of memory accesses to the location, and the order of memory accesses is decided according to the interleaving of threads. Therefore, controlling the thread interleaving is very important for making multi-threaded programs work in correspondence with the original intention, and programmers limit the legal interleavings of threads using synchronization operations such as mutexes, barriers, and condition variables.

While synchronization operations play an important role for multi-threaded programming by enforcing the threads to interact with each other in the way that the programmers intended, employing them in both correct and efficient way at the same time is very difficult. Faulty employment of synchronizations can result in errors (atomicity violations and order violations) or nontermination (deadlock). Such defects are collectively called concurrency bugs, and they are significantly more difficult to detect and fix than other types of bugs because they only manifest depending on specific thread interleavings.

Naïve placement of synchronization operations can also cause overly serialized executions. Synchronization operations sometimes can block the execution of threads and make them to wait until some conditions are satisfied. This blocking is necessary to prohibit illegal thread interleavings. However, blocking also limits the concurrency of parallel programs. If blocking is enforced more than necessary, it can be a performance bottleneck. Eyerman et al. [35] investigates a number of parallel benchmarks and discovers that synchronizations is the primary roadblock that prohibits the most number of benchmarks from scaling to many threads.

Programmers often make trade-offs between the programmability and the efficiency for employing synchronization operations. Since the fundamental purpose of synchronizations

is to limit a set of undesired thread interleavings, the more interleavings are prohibited, the more likely they cover all intended illegal thread interleavings. At the same time, however, larger set of illegal interleavings means higher possibility of blocking, limiting the concurrency of the execution. This trade-off can be seen in the familiar example of coarse-grained locking and fine-grained locking. Coarse-grained locking uses less number of mutexes and guards larger region of code with locks and unlocks. It is easier to use because it guarantees more atomicity and it is less prone to deadlocks. On the other hand, fine-grained locking is usually better for performance scaling because it serializes the execution less.

This thesis studies a collection of mechanisms that increase the programmability and efficiency of concurrent programs, without the intervention of programmers, by intelligently managing the synchronization operations. First, we focus on mutex locks and unlocks. Many concurrency bug detection tools and automated bug fixers rely on the precise identification of critical sections guarded by lock/unlock operations. We suggest a practical lock/unlock pairing mechanism that combines static analysis with dynamic instrumentation to identify critical sections in POSIX multi-threaded C/C++ programs. Second, we present Dynamic Core Boosting (DCB) to accelerate critical paths in multi-thread programs. Interthread dependencies through synchronizations form critical paths. These critical paths are major performance bottlenecks for concurrent programs, and they are exacerbated by workload imbalances in performance asymmetric CMPs. DCB coordinates its compiler, runtime subsystem, and architecture to mitigate such performance bottlenecks. Finally, we propose exploiting synchronization operations for better energy efficiency through dynamic power management, while maintaining performance.

In the following sections, the synchronization-related challenges for the programmabil-

ity and efficiency of concurrent programs are discussed. Next, we present our contribution for intelligent management of inter-thread synchronization dependencies. Finally, we describe the organization of this thesis.

## 1.1 Correctness Challenges

The foremost source that makes it so difficult to write correct concurrent programs is concurrency bugs. Concurrency bugs are synchronization defects allowing thread interleavings that are not expected by the programmers. They result in data corruption (atomicity violations and order violations) or nontermination (deadlock). They often survive thorough testing and introduce fatal errors in production, because they do not manifest very well depending on thread interleavings. In this section, we introduce the most common types of concurrency bugs [65].

**Deadlocks:** Synchronizations operations sometimes let threads wait for some conditions that must be satisfied by other threads, and these relations form inter-thread dependencies. If there exists a cycle of inter-thread dependencies, the set of involved threads cannot progress and the execution is said to be in a deadlock [88].

**Atomicity Violations:** Atomicity is a guarantee of isolation from different threads. If the data manipulation effect of a set of operations from one thread appears to be equivalent to that of a serial execution without intervention from other threads, the set of operations is told to bear atomicity. Programmers frequently expect atomicity of operations. For instance, consider the case where a counter variable needs to be incremented. It will consist of

three operations: load from the variable, increment, and store to the variable. These operations need to execute atomically, or the counter might have an unexpected value. Atomicity is usually enforced by mutex synchronizations. If the atomicity intention of a programmer is not satisfied by the actual implementation, it is called atomicity violation [66].

**Order Violations:** Programmers also expect certain orders among operations. For example, pointer dereferencing needs to occur after the allocation to the pointer but before freeing the pointer. Similarly, processing data is expected to happen after partitioning the input, followed by summarizing the results. Such orders are often placed with condition variables or barriers. If the programmer fails to enforce the order expectations, an order violation occurs [65].

## 1.2 Efficiency Challenges

Synchronizations are prone to become a performance bottleneck for multi-threaded programs since they limit concurrency. Naïve placement of them can overly serialize the executions. Eyerman et al. [35] studies the scaling bottlenecks of PARSEC [11] and SPLASH-2 [100] benchmarks, and identifies that synchronizations are the primary bottleneck for the largest number of benchmarks. In this section, we confirm the fact with some preliminary experiments on a machine with 32 cores.

Figure 1.1 shows the speedups of a subset of PARSEC [11] benchmarks with different number of threads normalized against their single thread execution. Ideally, an application that scales perfectly has to show the speedup equal to the number of threads. As can be

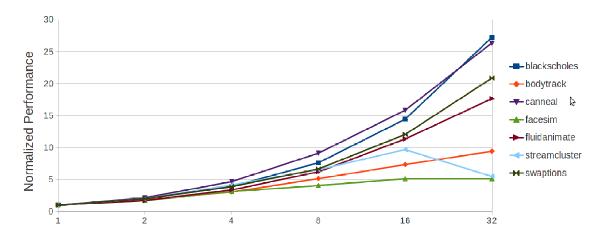

Figure 1.1: Speedup of PARSEC [11] benchmarks with varying number of threads compared to single thread executions.

seen, the benchmarks possess varying amount of scalability. While some programs such as *blackscholes* and *canneal* scale pretty close to the ideal, others like *streamcluster* or *facesim* do not scale very well. Regardless of whether they scale well or not, all of them show less performance improvement per thread as the number of threads increases.

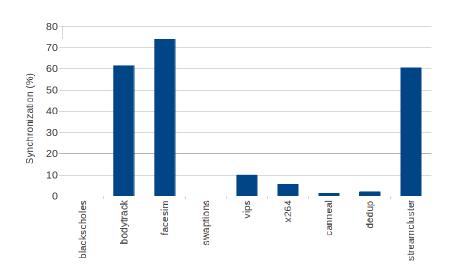

We focus on how much processor time is wasted waiting for synchronization operations including mutex locks, condition variable waits, and barrier waits. We intercept every Pthread library calls by overloading LD\_PRELOAD environment variable in Linux and measure waiting time for each operation. Figure 1.2 depicts the portion of time spent for synchronization. Comparing Figure 1.2 with Figure 1.1, we can see the benchmarks that spend more time for synchronization do not scale very well, which support the previous findings of Eyerman et al. [35]. Furthermore, this shows the potential of performance improvement if we can reduce the time spent for synchronization operations.

Figure 1.2: CPU cycles spent blocked for synchronization operations.

#### 1.3 Contributions

Although the works presented address a variety of different issues related to synchronizations from correctness to performance and energy efficiency, they are motivated by one observation that neither a static nor a dynamic approach is sufficient for intelligently managing synchronizations. Based on such observation, we combine compiler techniques and runtime techniques to increase programmability and efficiency of concurrent programs. In particular, the main contributions offered in this dissertation are as follows:

• First, practical lock/unlock pairing mechanism for C/C++ is presented. This mechanism combines static analysis and dynamic instrumentation to identify critical sections in POSIX multi-threaded programs. It first applies a conservative inter-procedural path-sensitive dataflow analysis to pair up all lock and unlock calls. When the static analysis fails, our method makes likely assumptions about the pairing using common heuristics. These assumptions are checked at runtime using lightweight instrumenta-

tion [25].

- The second part of this dissertation proposes Dynamic Core Boosting (DCB), a software-hardware cooperative system that accelerate critical paths formed by interthread synchronization dependencies. DCB coordinates its compiler, runtime subsystem, and architecture for near-optimal assignment of core boosting. The compiler instruments the program with instructions to give progress hints and the runtime subsystem monitors their execution, enabling the DCB architecture to assign a core boosting budget for better performance. Improving energy efficiency through synchronization-aware per-core power gating is also presented [22, 23].

- The third part presents Instant Profiling, a lightweight flexible profiling mechanism used for the other parts of the dissertation. Instant profiling maintains low overhead with instrumentation sampling technique using dynamic binary translation. Instead of instrumenting the entire execution, instant profiling periodically interleaves native execution and instrumented execution according to configurable profiling duration and frequency parameters. It further reduces the latency degradation by prepopulating a software code cache [24].

The rest of this dissertation is organized as follows. Chapter 2 introduces the practical lock/unlock pairing mechanism. The Dynamic Core Boosting and synchronization-aware per-core power gating is described in Chapter 3. Instrumentation sampling for lightweight flexible profiling is presented in Chapter 4. Finally, Chapter 5 concludes the dissertation.

#### **CHAPTER 2**

## **Practical Lock/Unlock Pairing**

### 2.1 Introduction

Most performance-aware programmers are experiencing ever growing pressure to parallelize their programs because uniprocessor performance has flattened out and multicore processors promise more cores in each successive hardware generation. Parallel programming, however, remains a daunting task for a variety of reasons. First of all, reasoning about concurrent events and synchronization is inherently challenging for human programmers, who think sequentially. In addition, concurrency bugs such as deadlocks, data races, and atomicity violations require global knowledge of the program. Finally, the nondeterministic execution of parallel programs makes these bugs hard to detect, reproduce, and fix.

There has been much effort to relieve the burden of parallel programming. For example, many automatic concurrency bug detection tools have been developed [84, 34, 66]. Automated bug fixing tools are also available [98, 53]. In addition, researchers are explor-

ing ways to adapt classical compiler optimization techniques for sequential programs to parallel programs [56, 87].

The aforementioned techniques often rely on if (x) or benefit from precise lock usage information, lock(L); which is very difficult to obtain for languages if (x) without lexically scoped critical sections. For unlock(L); instance, static bug detection tools using lockset

Figure 2.1: Infeasible path example

analysis [84] must map each statement to the set

of locks held by the thread of execution. Infeasible paths such as the one illustrated in Figure 2.1 are a major source of false positives [34]. Automated bug fix tools often add locks to avoid deadlock [98] or restore atomicity [53], which may introduce new deadlocks if the usage of existing locks is unknown. Finally, it is well known that many compiler optimization techniques cannot be directly applied to concurrent programs [87]. Currently compilers only optimize code sections that do not involve any lock operation, which can be quite conservative [56]. Correct identification of critical sections allows better optimization for concurrent programs.

Numerous static analysis approaches have been developed and many can be adapted to infer critical sections. In general, model checking based tools are precise but do not scale to practical programs [52], while scalable tools using specially designed algorithms are often imprecise [28, 19, 29]. For example, Saturn [29] is a scalable static analysis engine that is both sound and complete with respect to the user-provided analysis script. Writing a script that is sound and complete with respect to the target program, however, is as difficult as writing an analysis engine itself. The lock analysis script bundled with Saturn is neither sound nor complete, most notably because it lacks global alias analysis.

In this chapter, we propose a practical lock/unlock pairing mechanism that combines dataflow analysis with dynamic instrumentation. Our interprocedural path-sensitive dataflow analysis is a variant of existing tools [28, 19]. It conservatively identifies lock acquisition and release pairs. When the analysis is uncertain, we use heuristics such as those based on structure types and location proximity to determine the pair. Finally, we instrument the target program with light-weight checking instructions to monitor whether the pairing is correct at run-time. When a violation occurs, feedback information is provided to revise the pairing.

This chapter makes several contributions. We present a static lock/unlock pairing analysis algorithm which yields accurate results in most cases. We develop a lightweight dynamic checking mechanism to ensure our analysis is correct. We demonstrate the effectiveness of our lock/unlock pairing mechanism including both static analysis and dynamic checking with real-world multithreaded programs such as OpenLDAP, Apache, and MySQL.

The remainder of the chapter is organized as follows. We first present the challenges with motivating examples in Section 2.2. Next, Section 2.3 describes how our static lock/unlock pairing analysis works, and Section 2.4 discusses how to extend the analysis for inter-procedural cases. We explain the dynamic checking mechanism in Section 2.5. Section 2.6 presents the experimental results and Section 2.7 outlines related work. Finally, we summarize the contributions and conclude in Section 2.8.

| Benchmarks | Number of Annotations |

|------------|-----------------------|

| OpenLDAP   | 90                    |

| MySQL      | 71                    |

| Apache     | 19                    |

Table 2.1: Number of annotations needed to model

### 2.2 Background and Motivation

While our approach can help any tool that needs accurate static information about critical sections, we show its effectiveness in the context of deadlock avoidance. In this section, we briefly provide some background on dynamic deadlock avoidance in Gadara [98] and explain what kind of challenges exist for lock/unlock pairing.

#### 2.2.1 Gadara

Gadara is a tool that enables multithreaded programs to avoid circular-mutex-wait dead-locks at runtime. The basic idea is to intelligently postpone lock acquisition attempts when necessary to ensure that deadlock cannot occur. It proceeds in the following phases. First, Gadara constructs a Petri net model from program source code using compiler techniques. Based on structural analysis of the model, Gadara synthesizes feedback control logic for each structural construct in the model that contributes to a potential deadlock. Finally, it instruments the control logic into the target program.

Given that the model is correct, Gadara automatically synthesizes maximally permissive controllers that delay lock acquisitions only if the program model indicates that dead-lock might later result if the lock were granted immediately. Due to lack of accurate information about critical sections, however, Gadara's program analysis or control synthesis

could fail. In such cases, Gadara requires programmers to provide annotations. These annotations specify which unlocks match and that no mutex can be held at certain program points. Table 2.1 shows the number of annotations needed to model the benchmarks for Gadara. Providing annotations can be tedious, difficult, and error-prone even for programmers familiar with both the target program and Gadara.

#### 2.2.2 Challenges for Lock/Unlock Pairing

This subsection discusses the major challenges that a static lock/unlock pairing analysis should address in order to model programs accurately in the context of deadlock avoidance. We illustrate the challenges via simplified code examples.

#### 2.2.2.1 Infeasible Path

One of the challenges for static lock/unlock pairing is the ambiguity caused by infeasible paths. The traditional way in which compilers abstract programs' control path is to represent programs with control flow graphs (CFGs). Each vertex in a CFG represents a basic block and each edge corresponds to a branch from one basic block to another. Thus, a sequence of basic blocks connected with edges in a CFG represents a control path. Not all sequences, however, are actually possible control paths in program execution; some are *infeasible paths*.

Infeasible paths are a challenge for lock/unlock pairing because there can be cases where a lock is paired up with unlocks for all feasible paths but not paired up for some infeasible paths. This can be seen in the example of Figure 2.2 (a). If we assume the value of variable flag is not changed throughout the snippet, all the branches corresponding

```

if (flag) lock(node->mutex);

2:

while (condition) {

3:

. . .

4:

if (flag) unlock(node->mutex);

5:

. . .

6:

node = node->next;

7:

8:

if (flag) lock(node->mutex);

9:

10:

11:

if (flag) unlock(node->mutex);

(a)

1:

void callee(task *ptr) {

2:

unlock(ptr->mutex);

3:

4:

lock(ptr->mutex);

5:

6:

7:

void caller(task *ptr) {

8:

lock(ptr->mutex);

9:

. . .

callee(ptr);

10:

11:

12:

unlock(ptr->mutex);

13:

}

(b)

1:

lock(parent->mutex);

2:

3:

if (condition1) {

4:

lock(child->mutex);

5:

6:

unlock(child->mutex);

}

7:

8:

unlock(parent->mutex);

(C)

```

Figure 2.2: Challenges for lock/unlock pairing

to the if statements should follow the same direction. However, a naive static analysis would consider all possible combinations of branch directions, if it cannot correlate branch conditions. Another example of infeasible path is infinite loops, since we can assume a finite number of iterations for all reasonable executions. In the same example, if the analysis considers the infinite loop, the lock of line 8 might not be paired up.

This challenge is especially problematic for Gadara, whose models must have the semi-flow property [99]. Intuitively, the semiflow property means that a mutex acquired by a thread should be released later in the model. It is not always satisfied, however, if we directly translate the CFG to a Gadara model due to the infeasible path problem as described above. The semiflow property is one of the most important characteristics of Gadara models, and it is the main reason why accurate lock/unlock pairing is important in the context of deadlock avoidance.

#### 2.2.2.2 Spanning Function Boundaries

Another challenge arises from the fact that locks and unlocks need not reside in the same function. For widely used concurrent programs, it is not rare for locks and unlocks to span multiple levels of call chains. If a lock/unlock pairing analysis operates only within function boundaries it is not possible to pair up such cases.

Figure 2.2 (b) illustrates such a case. An intra-procedural lock/unlock pairing analysis would conclude that the lock in function caller() is paired up inside the function and the lock in function callee() is not paired up. However, actually the lock in line 8 is paired up with the unlock in line 2 and the lock in line 4 is paired up with the unlock in line 12, in this calling context.

It gets even more complicated since there can be many calling contexts. Gadara models function calls by substituting into the call site a copy of the callee's Petri net model [98], thus the model of one function can be analyzed differently depending on the calling contexts. Therefore, in order to handle this kind of cases, the lock/unlock pairing analysis should be inter-procedural and context-sensitive.

#### **2.2.2.3** Pointers

Imperfect pointer analysis imposes another challenge. Mutex variables are usually passed to lock/unlock functions via pointers. Since only locks and unlocks on the same mutex variable pair up, it is important to figure out which lock pointers point to the same location and which pointers do not. As widely known, however, even state-of-the-art pointer analyses cannot provide perfect information. For some cases, they can only conservatively tell that two pointers *may* alias.

Figure 2.2 (c) illustrates how pointers can cause problems for lock/unlock pairing analysis. Assume that the pointer analysis concludes that the pointer parent and child may alias, which is the normal case for heap variables. In this case, although it is reasonable for a human programmer to pair up the lock in line 1 and the unlock in line 9, it is not trivial for a static analysis to reach the same conclusion.

In order to model concurrent programs accurately, the lock/unlock pairing analysis should work well under such circumstances with imperfect information about pointers. Furthermore, Gadara conservatively approximates mutex pointers based on types [98]. More specifically, it models the mutexes accessed by pointers, which are enclosed in the same type of structure, as one resource place. The lock/unlock pairing analysis can relieve the

impact of this kind of approximation.

## 2.3 Static Lock/Unlock Pairing Analysis

In Sections 2.3 and 2.4, we discuss how our static analysis pairs up locks and unlocks to cope with the challenges described in the previous section. Section 2.3 first covers the detailed steps for intra-procedural cases and we show how to extend it for inter-procedural cases in Section 2.4.

Our static lock/unlock pairing analysis is carried out in four steps. First, the analyzer extracts an enhanced control flow graph (CFG) from source code and prunes it. This CFG is augmented with information about function calls and branch conditions. It prunes the CFG for computational efficiency, leaving only relevant branches. Second, it maps each lock to a set of corresponding unlocks through dataflow analysis traversing the CFG in a depth first manner while managing lock stack data structures. Third, it calculates Boolean expressions that express the conditions under which each lock and unlock is executed. Finally, using a SAT solver [32], it examines whether all locks are paired up with unlocks on every feasible path. Section 2.3.1 shows how the analysis works with a simple example, then the rest of the section describes each of these steps in detail.

## 2.3.1 Simple Example of Analysis Flow

This section presents the conceptual flow of our lock/unlock pairing analysis with a simple example in Figure 2.3. In this example, the mutex acquired by the lock in line 3 is always released before the function handle\_task() returns by either the unlock in line 7

```

1:

int handle task(task *job) {

2:

if(job->has mutex)

3:

lock(job->mutex);

4:

if(job->is_special) {

5:

// Handle special case

6:

if(job->has_mutex) {

7:

unlock(job->mutex);

8:

return result;

9:

10:

}

11:

//Handle normal cases

if(job->has_mutex)

12:

13:

unlock(job->mutex);

14:

return result;

15: }

```

Figure 2.3: Simple example of lock/unlock pairing.

or the unlock in line 13. However, directly translating the CFG of this example to Petri net violates the semiflow property due to infeasible paths as described in Section 2.2.2. Our analysis rules out the infeasible paths and gives accurate lock/unlock pairing results through the following process.

After pruning the CFG, the corresponding unlock set mapping decides that both the unlock in line 7 and the unlock in line 13 can release the mutex acquired by the lock in line 3. Then, the path condition calculation step determines the Boolean expressions that represent path conditions for each lock and unlock. In this example, path condition  $(job \rightarrow has\_mutex \neq 0)$  must be true for the lock to be executed. Similarly, the unlock in line 7 has  $(job \rightarrow is\_special \neq 0) \land (job \rightarrow has\_mutex \neq 0)$ , and the unlock in line 13 has  $(job \rightarrow is\_special = 0) \land (job \rightarrow has\_mutex \neq 0)$  as their path conditions. The analysis then translates them into Boolean expressions by assigning a Boolean variable to each branch condition. In order to encode the branch correlations into the expressions, this assignment process assigns the same Boolean variable to branch conditions that must have the same value. As a result, the Boolean expression of the lock is  $(x_1)$ , and the unlock in

```

1 : // Apply analysis to all functions

2 : void traverse function(fn)

// Traverse CFG to calculate GEN and KILL sets

traverse_bb(entry);

for(each lock discovered)

6:

corresponding_unlocks[lock]

7:

= GEN[lock] - KILL[lock];

8 : end

9:

10: // Compute GEN and KILL sets for all locks traversing

11: // CFG in a depth first manner while managing lock

12: // stack data structure

13: void traverse bb(bb)

14:

for(each instruction s in bb in order)

15:

if(s is a lock)

16:

push s to lock stack;

17:

else if(s is an unlock)

18:

top = top element of lock stack;

19:

add s in GEN[top];

20:

for(each element e in lock stack, e!=top)

21:

add s in KILL[e];

22:

pop from lock stack;

23:

for(each successor child of bb)

24:

traverse bb(child);

25: end

```

Figure 2.4: Finding unlock set corresponding to lock

line 7 and the unlock in line 13 receive  $(x_2 \wedge x_1)$  and  $(\neg x_2 \wedge x_1)$ , respectively.

The final step of the analysis is to check whether the lock and the corresponding unlocks pair up for all feasible paths. This can be done by determining whether the statement "if the path condition for the lock is true, then the disjunction of the path conditions for corresponding unlocks is true" is always true or not. In this example, the statement is interpreted as the Boolean expression  $(\neg x_1) \lor (x_2 \land x_1) \lor (\neg x_2 \land x_1)$ . In order to verify if it is always true, we apply a SAT solver on the negation of the Boolean expression. If it is unsatisfiable, then the statement is always true, and the lock and the corresponding unlocks are paired. Otherwise, they are not paired up. In this example, the negation of the Boolean expression is unsatisfiable and the lock is paired up with the unlock in line 7 and line 13.

#### 2.3.2 Mapping Lock to Set of Corresponding Unlocks

Before applying the infeasible path analysis, this step groups corresponding locks and unlocks. More specifically, it maps a set of corresponding unlocks to each lock. We say an unlock corresponds to a lock if it can release the mutex acquired by the lock on any path. Since the mutex acquired by a lock can be released at different program points, we map a set of corresponding unlocks and not just a single unlock. This step is necessary because the same mutex can be acquired and released multiple times.

This analysis algorithm traverses the CFG in a depth first manner while managing a stack of locks for each mutex. The core analysis algorithm is given in Figure 2.4. Although we only show it for one mutex in this version, the actual analysis simultaneously works on all mutexes.

The underlying idea is to add an unlock to the corresponding unlock set of a lock, if there is a path in which the unlock follows the lock but there is no path in which there is another lock of the same mutex between the lock and unlock. The top element of the lock stack is the most recent lock that the traversal encountered, so it adds the unlock to the GEN set of the top element. Other elements in the lock stack are the locks that the traversal met before the last lock along the traversal, so it adds the unlock to the KILL sets of them. Ultimately, the corresponding unlocks of each lock are the unlocks that are in the GEN set but not in the KILL set.

#### 2.3.3 Path Condition Calculation

This step calculates the Boolean expressions for path conditions that must be true for each lock and unlock to execute. It first calculates path conditions and translates them by assigning a Boolean variable for each branch condition. We define the path condition of a statement as the Boolean combination, i.e.,  $AND(\land)$ ,  $OR(\lor)$ ,  $NOT(\neg)$ , of branch conditions, which must be true for the statement to be executed.

The core path condition calculation algorithm is illustrated in Figure 2.5. With this algorithm, the path condition of a statement is the path condition from the entry basic block to the basic block that the statement belongs to. The underlying idea of this algorithm is that the path condition from the CFG node 'src' to 'dest' is the disjunction (OR) of the conditions along the paths which go through 'child', for all children of 'src'. This idea is reflected in line 18.

This algorithm uses caching and post dominator information for computational efficiency. Since there can be an exponential number of paths to the number of basic blocks, the naive recursive algorithm is not feasible for real programs. In order to avoid repetitive computation for the same path, it uses a path condition cache indexed by (src,dest) pair. In addition, it uses post dominator (PDOM) information as a shortcut, to simplify the resulting conditions.

After path condition calculation, the analysis translates the path conditions to Boolean expressions by assigning a Boolean variable to each branch condition. To reveal the branch correlations in the Boolean expressions, our analysis assigns the same Boolean variable to the branch conditions that must have the same value. This is possible by using global value

```

1 : // Recursively calculates path condition from

2 : // src to dest

3 : condition calculate path cond(CFG, src, dest)

// Consult path condition cache for efficiency

if (src, dest) is in cache

6:

return condition from cache;

// Always reaches dest if it post-dominate src

8:

if dest PDOM src

return TRUE;

10:

// Dead end

11:

if src has no successor

12:

return FALSE;

13:

// The control can reach dest following

14:

// each successor

15:

for(each successor c of src)

cond1 = branch condition of branch (src->c);

16:

17:

cond2 = calculate_path_cond(CFG, c, dest);

18:

condition = condition OR (cond1 AND cond2);

19:

put condition in cache with index (src, dest);

20:

return condition;

21: end

```

Figure 2.5: Calculating path conditions

numbering (GVN) and hashing them to map to Boolean variables.

### 2.3.4 Checking Lock/Unlock Pairing

Using the analysis results of the previous steps, this step finally verifies whether all locks are paired up with the corresponding unlocks on every feasible path. To achieve this goal, we use an open source SAT solver MiniSAT [32]. For each lock, through the previous steps, we have the set of corresponding unlocks and the relevant Boolean expressions for the path conditions of them and the lock. With these analysis results, to verify the statement "the lock is paired up with the corresponding unlocks on every feasible path" is equivalent to checking the proposition "if the Boolean expression for the lock is true, the disjunction of the corresponding unlocks' Boolean expressions is always true." Let L be the Boolean expression for the lock, and  $U_1, U_2, ..., U_n$  be the Boolean expressions for the corresponding

unlocks. Then our analysis tries to check if the following expression is always true.

$$L \Rightarrow U_1 \lor U_2 \lor \dots \lor U_n \tag{2.1}$$

or equivalently

$$\neg L \lor (U_1 \lor U_2 \lor \dots \lor U_n) \tag{2.2}$$

Checking whether a Boolean expression is always true or not can be done with a SAT solver. If the expression is always true, its negation always evaluates false, which in turn implies that the negation of the expression is unsatisfiable. Therefore, we can check whether the lock is paired up with the corresponding unlocks by applying a SAT solver to the negation of (2.2), which is

$$L \wedge \neg U_1 \wedge \neg U_2 \wedge \dots \wedge \neg U_n \tag{2.3}$$

### 2.3.5 CFG Pruning

One of the hurdles that the static lock/unlock pairing analysis must overcome is computational complexity. In real world server programs, the number of basic blocks in a function easily grows to several hundreds. In addition, the Boolean satisfiability problem is well known to be NP complete. For these reasons, we must carefully minimize the number of clauses in the Boolean expressions, in order to make our analysis scale to real programs. We achieve this by pruning the CFG.

Our analysis tool prunes the CFG without losing any relevant information needed for the analysis based on control dependence analysis [38]. Intuitively, CFG node X is control dependent on node Y if the outgoing edges from Y determine whether X is executed or not, and control dependencies can be calculated by finding post-dominator frontiers in the CFG. Given this property of control dependence, when we calculate the path condition for a basic block X, we must consider the basic blocks on which X is control dependent, the basic blocks on which those basic blocks are dependent, and so forth. Therefore, if we calculate the control dependence closure for the basic block, the basic blocks in the closure are the only ones that are relevant for the path condition calculation. We calculate the control dependence closure by iteratively including basic blocks until it converges.

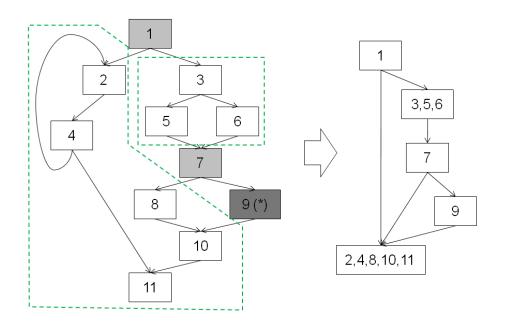

The CFG pruning algorithm works as follows. It starts with the basic blocks of interest as input. Then, it calculates the control dependence closure for them, i.e., the closure relevant basic blocks. Finally, we prune the CFG by maximally merging irrelevant basic blocks that are connected. The CFG pruning algorithm can be easily understood with the example in Figure 2.6. In this example, basic block 9 is the basic block of interest. It is control dependent on basic block 7; furthermore basic block 7 is control dependent on basic block 1. After calculating the control dependence closure {1,7,9}, the rest of the basic blocks can be merged if they are connected. The simplified CFG on the right results from pruning. By working on this pruned CFG, the path condition calculation and the resulting Boolean expressions get much simpler.

# 2.4 Inter-procedural Analysis

As discussed in Section 2.2.2.2, many lock/unlock pairs span function boundaries. In order to model concurrent programs for most cases, our lock/unlock pairing analysis must be inter-procedural and context-sensitive. In this section, we describe how to extend the

Figure 2.6: Example of CFG pruning.

analysis presented in the previous section for inter-procedural cases.

One straightforward way to make the analysis inter-procedural is a top-down approach that performs the analysis on the whole program CFG by conceptually replacing call instruction with the CFG of callee function at every call site, starting from the main() function. However, this can cause a computational complexity problem by producing an excessively large CFG to analyze.

Instead of flattening out the CFG for the entire program, we divide the problem into small pieces and perform the analysis on subgraphs in order to limit the analysis time. We first partition the callgraph with a proximity-based heuristic, and analyze the subgraphs in a bottom-up manner. We describe the details of this analysis in the following subsections.

#### 2.4.1 Proximity-based Callgraph Partitioning

We made two observations while we were trying to manually pair up locks and unlocks across function boundaries. The first observation is that the calling contexts of a lock and paired unlocks differ from a lowest common ancestor in the callgraph with respect to the root node main (), in most cases. Suppose that a mutex acquired by a lock with the calling context of  $main \Rightarrow f_1 \Rightarrow ... \Rightarrow f_n \Rightarrow f_{l1} \Rightarrow ... \Rightarrow f_{ln}$  is released by an unlock with the calling context of  $main \Rightarrow f_1 \Rightarrow ... \Rightarrow f_n \Rightarrow f_{u1} \Rightarrow ... \Rightarrow f_{un}$  on a path, then the other unlocks, if any, that pair up with the lock usually have calling context that shares  $main \Rightarrow f_1 \Rightarrow ... \Rightarrow f_n$  and  $f_n$  is a lowest common ancestor of them in the callgraph. The second observation is that the depths from locks and unlocks to the lowest common ancestor of the pairing context are relatively small (< 5) for most cases.

Based on the above observations we use a heuristic of proximity-based callgraph partitioning to keep the inter-procedural lock/unlock pairing analysis tractable. The partitioning algorithm works as follows. It starts from functions that have unpaired locks and follows upward the callgraph. It continues until it reaches a node that has the nodes with potentially pairing unlocks as descendants or a predefined depth threshold. Then, it cuts the subgraph from the node as a root. In this way, we can limit the size of Boolean expressions to be small enough to analyze.

## 2.4.2 Extending Lock/Unlock Pairing for Inter-procedural Analysis

For inter-procedural lock/unlock pairing, we apply the analysis described in Section 2.3 on the subgraph partitioned in the previous subsection. The inter-procedural lock/unlock

pairing analysis must handle function calls in a different way from the intra-procedural analysis, which just ignores function calls except locks and unlocks. The information about locks and unlocks in callee functions must be considered when the analysis meets a function call. Our analysis takes two different approaches to do so for mapping a lock to the set of corresponding unlocks and for path condition calculation.

Mapping a lock to the set of corresponding unlocks can be modified to be inter-procedural in a relatively straightforward way. It can be considered as conceptually inlining function calls. When it meets a function call it follows the CFG of the callee function. When the function returns it goes back to the caller function's CFG. Other than that, it is identical to the mapping algorithm explained in Section 2.3.2. It is a simple extension but it is enabled by the proximity-based callgraph partitioning.

On the other hand, path conditions are calculated in a bottom-up manner. In order to calculate the path condition that decides the execution of a lock, it first calculates the lock's path condition in the leaf node function that contains the lock. Then, following the context recognized in the partitioning, it calculates the path condition of the function call in its caller function, and its caller function, and so forth until it reaches the root function of the partition. These conditions get merged with a conjunction operator to finally calculate the context-sensitive path condition for the lock. After it calculates the context-sensitive path conditions for the locks and the unlocks, the remaining steps are identical to the intraprocedural analysis.

```

1 : Connection *c = NULL;

2 : for(; index < tblsize; index++) {

3 : ...

4 : if (connections[index].state == C_USED) {

5 : c = &connections[index];

6 : lock(&c->c_mutex);

7 : break;

8 : }

9 : }

10: ...

11: if (c!=NULL) unlock(&c->c_mutex);

```

Figure 2.7: Example of uncaught infeasible path.

|            |         |         |         |     | Our Approach |               |        |          |          |

|------------|---------|---------|---------|-----|--------------|---------------|--------|----------|----------|

| Benchmarks | LOC     | Number  | Trivial | DFT | Statically   | Speculatively | Total  | Unpaired | Static   |

|            |         | of lock |         |     | Paired       | Paired        | Paired |          | Analysis |

| OpenLDAP   | 271,546 | 357     | 110     | 267 | 319          | 34            | 353    | 4        | 152.7%   |

| MySQL      | 926,111 | 499     | 147     | 428 | 463          | 26            | 489    | 10       | 211.8%   |

| Apache     | 224,884 | 19      | 0       | 0   | 17           | 0             | 17     | 2        | 33.9%    |

| pbzip2     | 4,011   | 3       | 0       | 1   | 2            | 1             | 3      | 0        | 23.4%    |

| pfscan     | 752     | 11      | 8       | 10  | 10           | 1             | 11     | 0        | 50.0%    |

| aget       | 835     | 2       | 2       | 2   | 2            | 0             | 2      | 0        | 43.8%    |

Table 2.2: Coverage of static lock/unlock pairing analysis

## 2.5 Dynamic Checking

Our static lock/unlock pairing analysis can be potentially incorrect in some cases due to the assumptions and heuristics it uses. In this section, we discuss these potential sources of incorrect analysis results and explain how our dynamic checking instrumentation can detect them.

One important reason why our analysis might yield potentially incorrect results is pointers as described in Section 2.2.2.3. Due to the limitations of the default memory dependency analysis, we augment it with generic aggressive refinements. Although the probability is very low, they can result in incorrect analysis results.

The second source of potentially incorrect analysis results is the proximity-based call-

graph partitioning heuristic. Although we could not find a real example, it is theoretically possible that one lock has two pairing unlocks whose lowest common ancestors with the lock differ. In that case, our partitioning algorithm can give an incorrect subgraph to analyze and end up with an incorrect analysis result.

Lastly, there are cases where our analysis maps unlocks correctly but cannot guarantee the lock is paired up with unlocks for all feasible paths due to the limitations of our analysis. An example of this case is shown in Figure 2.7. Our analysis can map the unlock in line 11 as the corresponding unlock of the lock in line 6. However, it cannot guarantee the lock is paired up for all feasible paths due to the lack of understanding about program semantics. A human programmer can easily figure out that the variable c is not NULL when the lock in line 6 is executed, thus the lock is paired up with the unlock in line 11 if the value of c is not modified in between. However, it is difficult for a static analysis to understand such program semantics. In this case, our analysis provides the mapping for the modeling as the best effort result. However, this type of best effort analysis result might be incorrect for other cases.

For these reasons, our lock/unlock pairing mechanism needs a way to verify whether all of the analysis results are correct or there exists any violation of the assumptions it made. In order to do that, we need to check two types of conditions. First, the mapping of unlocks to each lock should be checked. If the mutex acquired by a lock is released by an unlock that is not in the corresponding unlock set, it should be detected. Second, the semiflow requirement has to be checked. In other words, whether each lock is paired up with an unlock for all feasible paths or not is to be checked. In the following subsections, we discuss these two types of checking in detail.

```

lock wrapper(mutex, callsite, callstack) {

1:

2:

lock(mutex);

3:

LOCK ID = get id(callsite, callstack);

4:

mutex_to_lock_id[mutex] = LOCK_ID;

5:

ROOT FID = SEMIFLOW RESULT[LOCK ID];

held_mutex[ROOT_FID].insert(mutex);

6:

7:

}

8 : unlock wrapper(mutex, callsite, callstack) {

9:

UNLOCK_ID = get_id(callsite, callstack);

10:

LOCK_ID = mutex_to_lock_id[mutex];

11:

mutex_to_lock_id.erase(mutex);

12:

assert(LOCK_UNLOCK_PAIR[LOCK_ID][UNLOCK_ID]);

13:

ROOT_FID = SEMIFLOW_RESULT[LOCK_ID];

14:

held_mutex[ROOT_FID].erase(mutex);

unlock(mutex);

15:

16: }

```

Figure 2.8: Instrumentation wrapper for lock and unlock

#### 2.5.1 Checking Lock-to-Unlocks Mapping

We instrument all locks and unlocks to check whether the mapping of each lock to corresponding unlocks is correct or not. We first assign a unique ID to each lock and unlock. At runtime, the instrumented code manages a thread-local data structure that keeps the acquiring lock's ID of each mutex. Since the data structure is thread local, it does not need to synchronize with other threads to access the data structure. When an unlock releases the mutex, the instrumented code looks up the acquiring lock's ID of the mutex and checks whether its own ID is in the corresponding unlock set of the lock.

The IDs of locks and unlocks can be simply assigned as a unique number to each calling instruction for intra-procedural cases. However, if they are paired up by the interprocedural analysis, we need to manage different IDs for different calling contexts even for the same lock or unlock. This is achieved by managing private call stacks. For the functions that appear in the subgraph analyzed by the inter-procedural analysis, we assign IDs and instrument the entrances and exits to push and pop the ID in the private call stack.

This call stack information is concatenated to the IDs of locks and unlocks in order to make it context sensitive.

Figure 2.8 is the pseudo code for our locks and unlock wrapper functions. It obtains context sensitive IDs of the locks used by the acquisition and release functions at lines 3 and 9, respectively. We verify whether the released lock is in the unlock set corresponding to the acquired lock at line 12.

#### 2.5.2 Checking Semiflow Property

Another condition that we need to check dynamically is the semiflow property. As described in Section 2.2.2.1, the semiflow property guarantees that a mutex acquired by a thread will always be released later. With the static analysis we check this property by testing whether locks are paired with unlocks for all feasible paths. If the condition is not satisfied due to incorrect analysis, the dynamic checking should be able to detect it.

We also check this property by instrumenting locks, unlocks, and function exits. For this type of check, the instrumented code maintains the information about held mutexes indexed with the acquiring lock's ID. Again, these IDs are concatenated with call stack information for context-sensitive cases. We instrument the root node functions of the subgraphs partitioned by the proximity-based partitioning to check whether it is holding any lock that should be paired up inside the calling context when it returns. This is done by checking whether the held\_mutex[FID] set (kept in line 6 of Figure 2.8) is empty when the root node function (FID) returns.

## 2.6 Experimental Results

We have implemented the lock/unlock pairing mechanism including both the static analysis and checking instrumentation as a pass of the LLVM compiler infrastructure [59]. Our implementation operates on the LLVM intermediate representation and provides both analysis results and instrumented code. For the aggressive refinement of LLVM's memory dependency analysis, we use Gadara's type-based method for mutex pointers and memory profiling for other variables.

All of our experiments were executed on a 2.50GHz Intel Core 2 Quad machine with 8GB of memory running Linux 2.6.32. We evaluate the effectiveness of our lock/unlock pairing with Apache 2.2.11 web server [5], MySQL 5.0.91 database server [77], OpenL-DAP 2.4.21 lightweight directory access protocol server [79], pbzip2 1.1.4, pfscan 1.0, and aget 0.4.

## 2.6.1 Effectiveness of Static Analysis

Table 2.2 shows the effectiveness of our static lock/unlock pairing analysis. The third column is the total number of locks and the fourth column is the number of locks trivially paired up in a basic block. We also compare our approach against depth first traversal (DFT) of control flow graph, which is used by previous static lockset-based tools such as RacerX [34]. Statically paired locks mean the number of locks that could be paired up with infeasible path analysis. Speculatively paired locks are the ones that our analysis could successfully map the corresponding unlock sets but could not guarantee pairing for all feasible paths due to the limitation described in Section 2.5. Thus the sums of the sixth

```

1 : class THD {

struct st_my_thread_var *mysys_var;

3:

4:

char* enter_cond(mutex_t* mutex) {

5:

6:

mysys_var->current_mutex = mutex;

7:

8:

}

9:

void exit_cond(char* old_msg) {

10:

unlock(mysys var->current mutex);

12:

13:

}

14: };

15:

16: bool wait_for_relay_log_space(RELAY_LOG_INFO* rli) {

THD *thd = rli->mi->io_thd;

17:

18:

char *save proc info;

19:

. . .

20:

lock(&rli->log_space_lock);

21:

save_proc_info = thd->enter_cond(&rli->log_space_lock);

22:

23:

thd->exit_cond(save_proc_info);

24:

25: }

```

Figure 2.9: Example of unpaired lock due to type mismatch.

and seventh columns are the numbers of locks that our static analysis could pair up with unlocks. As can be seen in the table, our static analysis works effectively for nearly all of the cases. Overall, trivial pairing fails to handle 70% of locks and DFT fails to handle 20.5% of locks. By contrast, our approach handles all but 1.8% of locks—an eleven-fold improvement compared with DFT.

There are still unpaired locks, although the number of such cases is relatively small.

There are three types of causes for these cases. First, there are inherently unpaired locks in the programs. Three unpaired locks of OpenLDAP are from one function, ldap\_new\_connection(), and in this category. When the function is called in certain contexts, these locks are paired up and our analysis can catch those cases. In other contexts, however, they are not paired

up and thus our analysis cannot pair them up.

The second category of unpaired locks is due to the type-based memory dependency analysis refinement that we use for mutex pointers. This refinement assumes that two mutex pointers do not alias if the types of wrapper structures enclosing the mutex variables are different. With this assumption our analysis cannot pair up a lock and unlocks if they have different types. The example in Figure 2.9 shows how this can cause a problem. In this example, the lock in line 20 and the unlock in line 11 are called on the same mutex, because the call of enter\_cond() in line 21 saves the mutex in a pointer and passes it to exit\_cond(). The problem is that the types of wrapping structure for the lock and the unlock are different. The wrapping type is RELAY\_LOG\_INFO for the lock and st\_my\_thread\_var for the unlock. The type based memory dependency refinement would consider them not to alias, and consequently our lock/unlock pairing analysis cannot pair them. Among the unpaired locks of MySQL, eight of them are in this category.

The last cause of unpaired unlocks is function pointers. The current implementation of our lock/unlock pairing analysis cannot track the inter-procedural cases in which a function is called via a function pointer, since it uses the callgraph information which only puts edges for direct function calls. One of OpenLDAP's locks, two of MySQL's locks, and two of Apache's locks could not be paired up for this reason.

Static analysis time as a percentage of compilation time is presented in the last column of Table 2.2. Analyzing MySQL and OpenLDAP takes considerably longer than analyzing other benchmarks because they have more complex control flows and include more lock/unlock function calls. Table 2.3 presents the number of basic blocks in a function before and after CFG pruning, as described in Section 2.3.5. Our CFG pruning signifi-

| Benchmarks | Before  | Pruning | After Pruning |         |  |

|------------|---------|---------|---------------|---------|--|

|            | Average | Maximum | Average       | Maximum |  |

| OpenLDAP   | 20.19   | 818     | 2.22          | 80      |  |

| MySQL      | 5.88    | 3513    | 1.18          | 112     |  |

| Apache     | 12.12   | 465     | 1.02          | 13      |  |

| pbzip2     | 6.16    | 431     | 1.06          | 10      |  |

| pfscan     | 10.57   | 48      | 3.61          | 33      |  |

| aget       | 12.11   | 35      | 1.83          | 16      |  |

Table 2.3: Number of Basic Blocks before/after Pruning

cantly reduces both average and maximum number of basic blocks, which is essential for the scalability of our static analysis procedure.

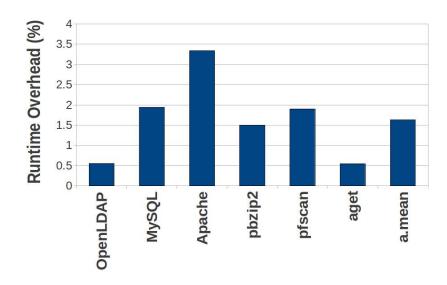

#### 2.6.2 Runtime Overhead of Dynamic Checking

Figure 2.10 presents the runtime overheads of the dynamic checking instrumentation. For server programs, it is measured as the comparison of average response time to clients on the same machine. For pbzip2, pfscan, and aget, the execution times are compared. Four parallel clients and worker threads are used for the servers and the other programs, respectively. As can be seen in the graph, our checking instrumentation imposes very small overheads for the programs. The runtime overheads range from 0.5% to 3.4% and the average is 1.6%.

As discussed in Section 2.6.1, our static analysis yields three types of results: statically paired, speculatively paired, and unpaired. For both statically and speculatively paired locks, our framework instruments the checking mechanism presented in Section 2.5, whose major overhead comes from the executions of locks and unlocks. Therefore, even if our analysis does not work well so that it yields more speculatively paired locks, the runtime overhead would not be drastically increased. For unpaired locks, the current implemen-

Figure 2.10: Runtime overheads of dynamic checking.

tation of our framework falls back to programmer annotations and does not add checking instrumentation. It is possible to add more heuristics to make guesses for unpaired locks, but the dynamic checking overhead would be still roughly proportional to the number of the executions of locks and unlocks even for those cases.

Compared to the native implementation of lock and unlock, our instrumentation slows down a pair of lock and unlock by roughly 18×. Thus, it is possible that our dynamic checking incurs excessive overhead if the target program locks and unlocks too many times without doing much work. However, it is not a common practice to make programs lock and unlock too often, and such programs would already suffer poor performance. Furthermore our current instrumentation implementation is a simple un-optimized use of the C++ STL library, and overheads can be further reduced by optimizing the implementation of instrumented code.

| Benchmarks | Average | Maximum |

|------------|---------|---------|

| OpenLDAP   | 1.37    | 7       |

| MySQL      | 1.37    | 10      |

| Apache     | 1.35    | 2       |

| pbzip2     | 1.67    | 2       |

| pfscan     | 1.09    | 2       |

| aget       | 1.00    | 1       |

**Table 2.4: Number of Unlocks in Corresponding Unlock Sets**

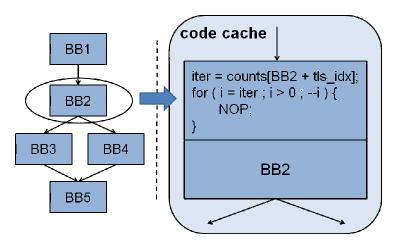

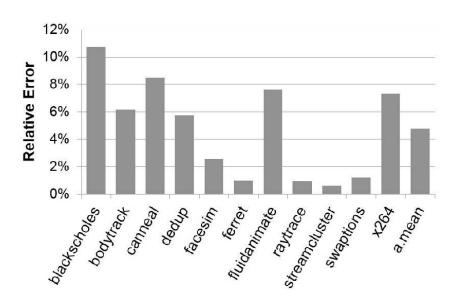

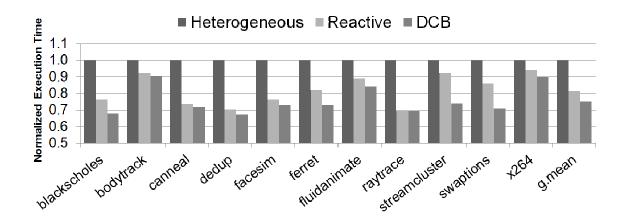

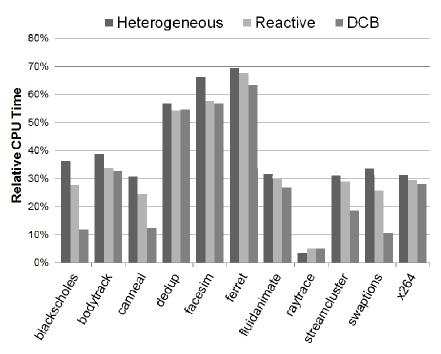

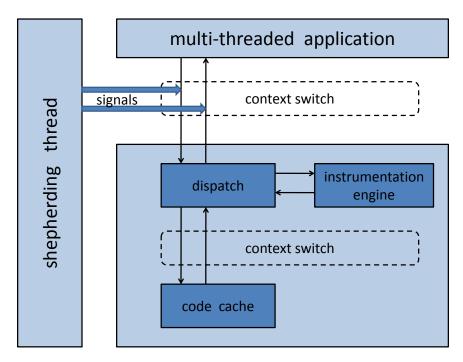

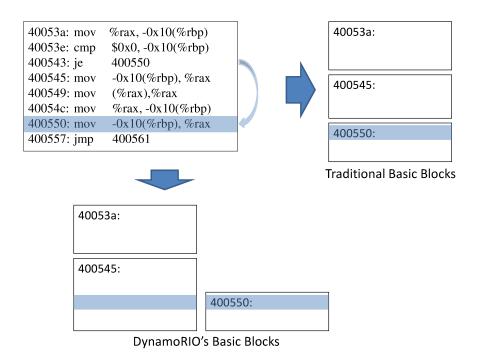

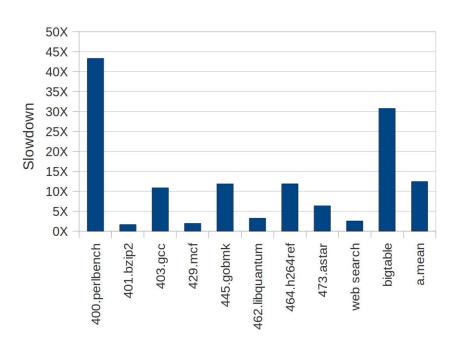

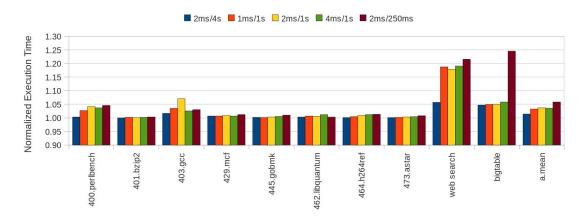

### 2.6.3 Assumption Violation