## Amorphous In-Ga-Zn-O Thin-Film Transistors for Next Generation Ultra-High Definition Active-Matrix Liquid Crystal Displays

by

## Eric Kai-Hsiang Yu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2015

### **Doctoral Committee:**

Professor Jerzy Kanicki, Chair Associate Professor Dae Hwan Kim, Kookmin University Professor Jamie Dean Phillips Professor Kevin Patrick Pipe

To my family, especially my parents, Yung-Fu Yu and Hsiu-Ming Liu, for all the sacrifices they have made to provide for our family.

### **ACKNOWLEDGEMENTS**

I am forever indebted to my thesis advisor, Professor Jerzy Kanicki, for his guidance throughout the years and for introducing me to the exciting world of thin-film transistors. Without his support and patience, I would not have been able to finish my degree. I also sincerely thank my dissertation committee, Professor Dae Hwan Kim (Kookmin University, Korea), Professor Jamie Phillips, and Professor Kevin Pipe, for their time and helpful comments.

Credit goes to our collaborators for their contributions: Professor Dae Hwan Kim's group at Kookmin University for the extraction of a-IGZO DOS from multi-frequency *C–V* in chapter 3; Dr. Yong-Su Lee and his colleagues at Samsung Display for sample preparation and DOS extraction in chapter 4; Dr. Chihyu Chen, Thomas Frost, and Arnab Hazari for assistance with photoluminescence measurements in chapter 5; Dr. Hideya Kumomi and Dr. Abe Katsumi at the Tokyo Institute of Technology for sample preparation in chapter 6. Much gratitude is due to Dave Sebastian, Dr. Brian Armstrong, and other staff at the Lurie Nanofabrication Facility. I also would like to show my appreciation to EECS graduate coordinators Steven Pejuan and Beth Stalnaker.

I am very grateful for having had the opportunity to work with all current and former members of the Displays and Detectors Laboratory: Dr. Gwang Hyeon Baek, Linsen Bie, Kai-Chen (Kevin) Cheng, Che-Lin Huang, Hyunsoo Kim, Gokul Prakash, Rui Zhang, and Chumin Zhao, and the visiting scholars at our lab: Taku Fukumura (Japan Patent

Office), Dr. Soo Chang Kim (Samsung Display), Professor Robert Mroczyński (Warsaw University of Technology, Poland), and Dr. Mitsuru Nakata (NHK). I am thankful for advice from Professor Duncan Steel and Professor Zhaohui Zhong and initial guidance from Dr. Jeramy Zimmerman and Professor Stephen Forrest.

I cannot thank Dr. Tallis Chang, Dr. Tze-Ching (Richard) Fung, Dr. John Hong, and Dr. Cheonhong Kim from Qualcomm Inc. enough for financial support and guidance during my internship. I also appreciate financial support from the EECS department and Asahi Glass Company. I am very grateful for the mentoring I have received during my undergraduate years at Cornell University from Dr. Derek Stewart and Professor Sandip Tiwari, as they influenced my decision to start my Ph.D.

I highly appreciate the technical discussions with current and former colleagues at the University of Michigan: You-Chia Chang, Chih-Wei Chien, Dr. Shafat Jahangir, Dr. Hsun-Chih (Michael) Kuo, Dr. Chi-Sen Lee, Che-Hung Liu, Chun-Li Lo, and Chu-Hsiang Teng. My friends are very important to me and I appreciate their companionship: Sou-Chi Chang, Eric Chao-Huei Chen, Inn-Tung Chen, Yen-Po Chen, Chate Eamrungroj, Tien-Hao Gan, Frank Gu, Chuan-Yuan (Franke) Hsu, Dr. Simon Huang, David Hwu, Bor-Chau Juang, Yung-Hao Kung, Po-Chia Lai, Albert KJ Liang, Miao-Bin Lien, Chien-Chung (Oliver) Lin, Hsu-Kuei Lin, Wen-Chi Lin, Wise Ongg, Yi Ouyang, Ricky Ching-Yen Pai, Dr. Noah Smith, Dr. Grace Tsai, Dr. Jun-Chieh (Jerry) Wang, and Fei Zhao. There are too many to list and I apologize for any unintended omissions.

I am very thankful for the life-changing opportunity to be a Michigan Wolverine. **GO BLUE!** Last but not least, I am eternally grateful to my parents, my sister, and Pei-Ju Sung, for their unconditional love, support, patience, and encouragement.

## **TABLE OF CONTENTS**

| DEDICATION   | ON                                                                    | ii   |

|--------------|-----------------------------------------------------------------------|------|

| ACKNOWI      | LEDGEMENTS                                                            | iii  |

| LIST OF FI   | GURES                                                                 | viii |

| LIST OF TA   | ABLES                                                                 | xiv  |

| ABSTRACT     | Γ                                                                     | XV   |

| CHAPTER      |                                                                       |      |

| 1. Introduct | tion                                                                  | 1    |

| 1.1 Ove      | rview and Background                                                  | 1    |

| 1.1.1        | Current status of backplane technology for ultra-high definition acti | ve-  |

| matrix 1     | liquid crystal displays                                               | 1    |

| 1.1.2        | Requirements for UHD AM-LCD Backplane Technology                      | 5    |

| 1.1.3        | Current Status of Amorphous In-Ga-Zn-O TFTs for UHD AM-LCD            | s 8  |

| 1.2 Thes     | sis Organization                                                      | 12   |

| 2. Fabricati | on of a-IGZO Thin-Film Transistors                                    | 13   |

| 2.1 Intro    | oduction                                                              | 13   |

| 2.2 Com      | nmon Gate a-IGZO TFTs by Shadow Masking                               | 14   |

| 2.2.1        | Impact of Thermal Annealing                                           | 16   |

| 2.2.2        | Impact of Oxygen Partial Pressure                                     | 17   |

| 2.2.3        | Impact of Active-Wide vs. Contact-Wide TFT Configurations             | 18   |

| 2.3 Defi     | ned Gate a-IGZO TFTs by Shadow Masking                                | 20   |

| 2.4 Bacl     | Channel Etch a-IGZO TFTs by Photolithography                          | 21   |

| 2.4.1        | Gate Electrode Deposition and Definition                              | 23   |

| 2.4.2        | Gate Insulators and Active Layer Deposition and Definition            | 26   |

| 2.4.3        | Source/Drain Electrode Definition                                     | 27   |

| 2.5 Chai     | nnel Protection Layer a-IGZO TFTs by Photolithography                 | 31   |

| 2      | 2.5.1      | Impact of Passivation Layer on a-IGZO TFTs by Photolithography             | . 33 |

|--------|------------|----------------------------------------------------------------------------|------|

| 2.6    | $S/\Gamma$ | O-Recessed a-IGZO TFTs by Photolithography                                 | . 35 |

| 2.7    | Sur        | nmary of TFT Structures Fabricated                                         | . 36 |

| 3. Dei | nsity      | of States of Amorphous In-Ga-Zn-O from Electrical and Optical              |      |

|        | •          | ization                                                                    | . 38 |

| 3.1    | Intı       | oduction                                                                   | . 38 |

| 3.2    |            | perimental Setup                                                           |      |

| 3.3    | Res        | sults and Discussion                                                       | . 40 |

| 3.4    | DO         | S Model of a-IGZO                                                          | . 47 |

|        |            | Flow Effects on Electrical Properties and Stability of a-IGZO Thin-        |      |

|        |            | sistors                                                                    |      |

| 4.1    |            | oduction                                                                   |      |

| 4.2    |            | perimental                                                                 |      |

|        | 1.2.1      | Fabrication of a-IGZO TFTs with Various Oxygen Partial Pressures           |      |

|        | .2.2       | Measurement of a-IGZO TFT <i>I–V</i> and <i>C–V</i> Characteristics        |      |

|        |            | sults and Discussion                                                       |      |

|        | 1.3.1      | Impact of Bias-Temperature Stress on a-IGZO TFT <i>C-V</i> Characteristic  |      |

|        | 1.3.2      | Impact of Bias-Temperature Stress on a-IGZO TFT <i>I–V</i> Characteristics |      |

| 4      | 1.3.3      | Extraction of DOS of a-IGZO TFTs from Multi-frequency <i>C–V</i>           | . 62 |

| 5. Ph  | otoluı     | minescence of a-IGZO Thin-Film Transistors                                 | . 67 |

| 5.1    | Intı       | oduction                                                                   | . 67 |

| 5.2    | Exp        | perimental                                                                 | . 69 |

| 5      | 5.2.1      | Fabrication of a-IGZO TFTs and Thin Films for Photoluminescence            |      |

| S      | Spectr     | oscopy                                                                     | . 69 |

| 5      | 5.2.2      | Measurement of Electrical Properties and Photoluminescence Spectra         | . 70 |

| 5.3    | Pho        | otoluminescence Spectra of a-IGZO Thin Films and TFTs                      | . 72 |

| 5.4    | Dis        | cussion of the Photoluminescence Spectra                                   | . 77 |

|        |            | -Temperature Stability of a-IGZO TFTs with Metal Source/Drain              | 02   |

| Reces  |            | Clectrodes                                                                 |      |

| 6.1    |            | roduction                                                                  |      |

| 6.2    |            | perimental                                                                 |      |

|        | 5.2.1      | Fabrication of Source/Drain-Recessed a-IGZO TFTs                           |      |

|        | 5.2.2      | Characterization of TFT Electrical Properties and AC BTS Stability         |      |

| 6.3    |            | sults and Discussion                                                       |      |

|        | 5.3.1      | Electrical Properties of Source/Drain Recessed a-IGZO TFTs                 |      |

| 6      | 5.3.2      | Unipolar AC Bias-Temperature Stress Stability of a-IGZO TFTs               | . 89 |

| 6.3.3      | Bipolar AC Bias-Temperature Stress Stability of a-IGZO TFTs  | 94     |

|------------|--------------------------------------------------------------|--------|

| 6.4 AC     | C BTS Stability of a-IGZO TFTs for 4K UHD AM-LCD             | 97     |

| 7. Dynami  | c Response of a-IGZO and a-Si:H Thin-Film Transistors for U  | ltra-  |

| •          | nition AM-LCDs                                               |        |

| 7.1 Int    | roduction                                                    | 101    |

| 7.2 Ex     | perimental                                                   | 102    |

| 7.2.1      | Fabrication of 1T1C a-Si:H TFT Test Circuits                 | 102    |

| 7.2.2      | Fabrication of 1T1C a-IGZO TFT Test Circuits                 | 103    |

| 7.2.3      | Electrical Properties of a-IGZO and a-Si:H TFTs              | 104    |

| 7.2.4      | TFT Dynamic Response Measurement Setup                       | 106    |

| 7.3 Re     | sults and Discussion                                         | 108    |

| 7.3.1      | Charging Characteristics of a-Si:H and a-IGZO TFTs for UHD A | M-LCDs |

|            | 108                                                          |        |

| 7.3.2      | Feedthrough Voltage of a-Si:H and a-IGZO TFTs                |        |

| 7.3.3      | a-IGZO TFT Gate Overdrive Operation                          | 120    |

| 8. Conclus | ions and Future Work                                         | 123    |

| 8.1 Su     | mmary of Results and Conclusions                             | 123    |

| 8.2 Re     | commendations for Future Work                                | 127    |

| APPENDE    | X – List of Publications                                     | 128    |

| BIBLIOGI   | RAPHV                                                        | 130    |

# LIST OF FIGURES

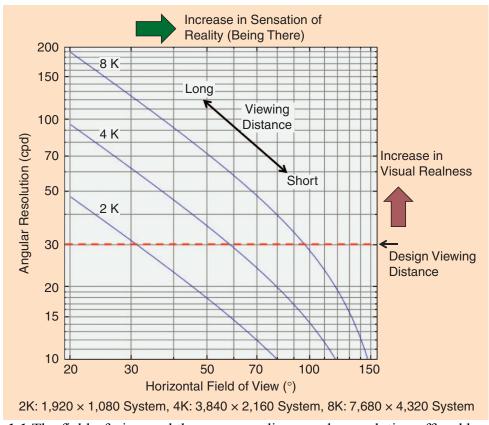

| Figure 1.1 The field-of-view and the corresponding angular resolution offered by variou AM-FPD resolutions when viewed at the optical distance for any given display size [6]                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

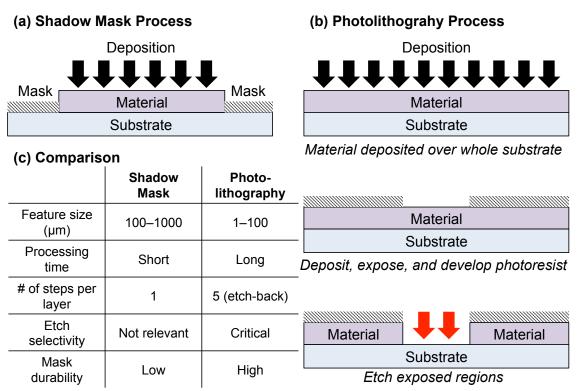

| Figure 2.1 A generic description of the (a) shadow mask and (b) photolithography fabrication process. A high-level comparison of the two processes are shown in (c)                                                                                                                                                 |

| Figure 2.2 Top view photograph of the shadow mask a-IGZO TFT                                                                                                                                                                                                                                                        |

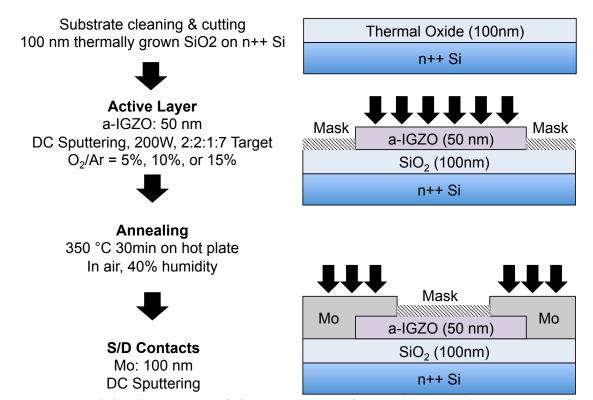

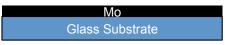

| Figure 2.3 Fabrication process of the common gate inverted-staggered a-IGZO TFT by shadow mask process1                                                                                                                                                                                                             |

| Figure 2.4 Common gate a-IGZO TFTs with (a) one post-S/D deposition annealing and (b) one pre-S/D deposition annealing                                                                                                                                                                                              |

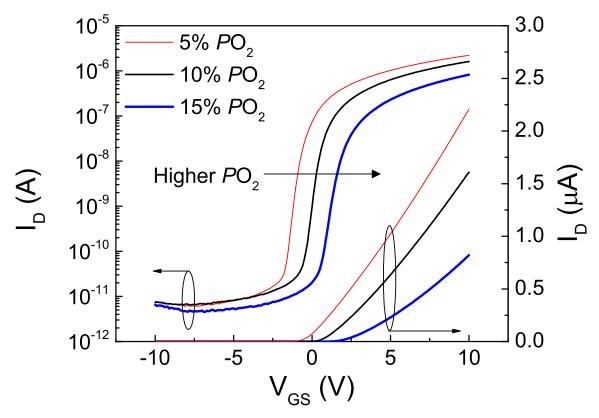

| <b>Figure 2.5</b> Impact of $p_{O_2}$ during a-IGZO sputtering on the electrical properties of common gate a-IGZO TFTs fabricated by shadow mask                                                                                                                                                                    |

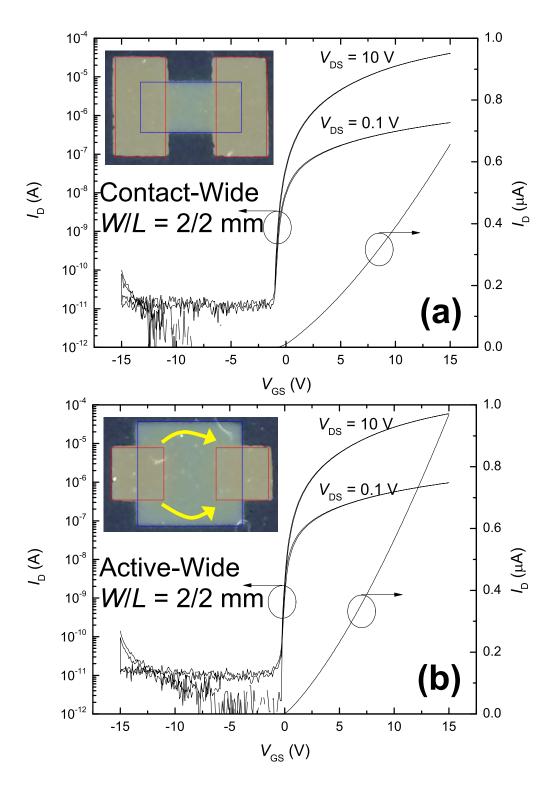

| <b>Figure 2.6</b> The $I_D$ – $V_{GS}$ at $V_{DS}$ = 0.1 and 10 V for the common gate a-IGZO TFTs fabricated by shadow mask process with $W/L$ = 2/2 mm in the (a) contact-wide and (b) active-wide configurations. The arrows in (b) indicate the path of the fringe field effect                                  |

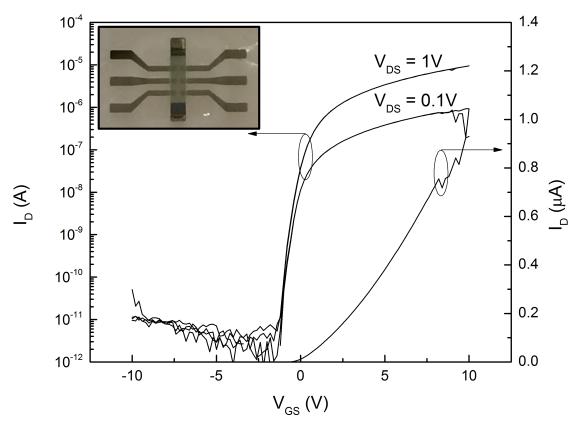

| Figure 2.7 The $I_D$ – $V_{GS}$ at $V_{DS}$ = 0.1 and 1 V of defined gate a-IGZO TFTs fabricated by shadow masking. The top-view photograph of the fabricated device is shown in the figure inset                                                                                                                   |

| Figure 2.8 Process flow of the back channel etch a-IGZO TFTs fabricated by photolithography at the University of Michigan Lurie Nanofabrication Facility 2                                                                                                                                                          |

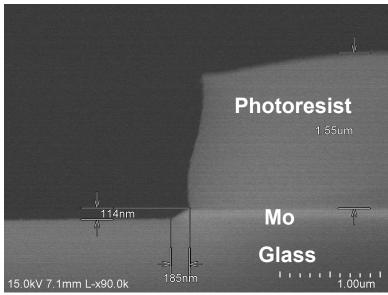

| Figure 2.9 Side-view SEM image of Mo gate electrode on glass after dry etching 2                                                                                                                                                                                                                                    |

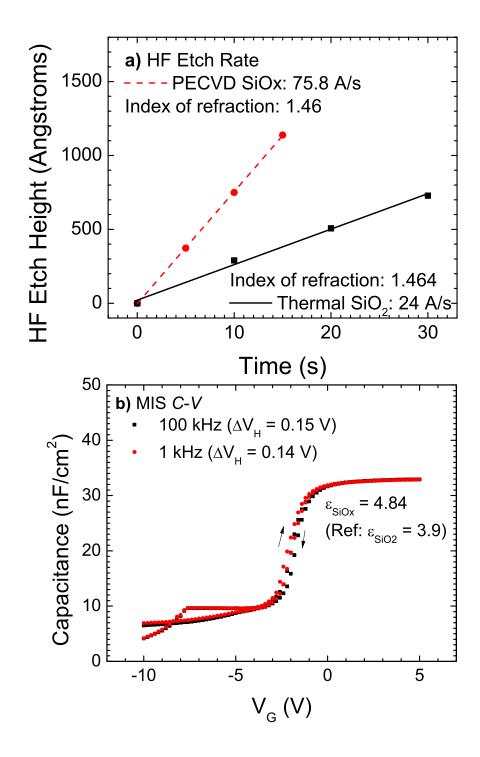

| <b>Figure 2.10</b> (a) The HF etch rate and refractive index of PECVD a-SiO <sub>X</sub> used throughouthis study for gate insulator purposes, compared with those of thermally grown SiO <sub>2</sub> on a Si substrate. (b) The <i>C</i> – <i>V</i> characteristics of the PECVD a-SiO <sub>X</sub> MOS structure |

|                                                                                                                                                                                                                                                                                                                     |

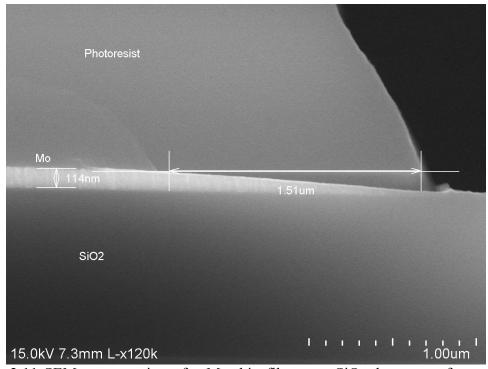

| <b>Figure 2.11</b> SEM cross-section of a Mo thin film on a SiO <sub>2</sub> dummy wafer etched by H <sub>2</sub> O <sub>2</sub> + NH <sub>4</sub> OH                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

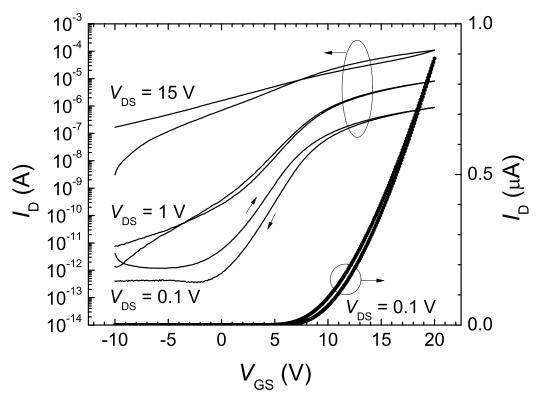

| <b>Figure 2.12</b> The $I_D$ – $V_{GS}$ of the BCE a-IGZO TFT with S/D defined by dry etching 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

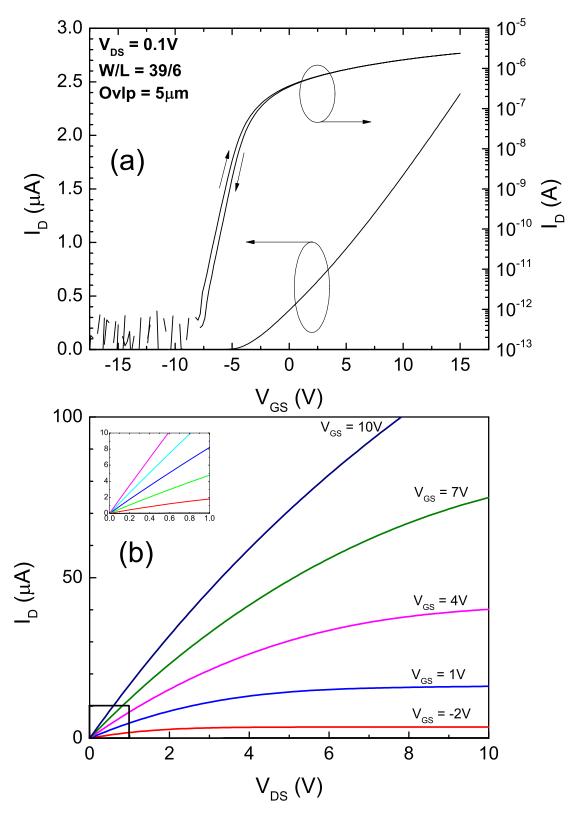

| <b>Figure 2.13</b> The (a) $I_{\rm D}$ – $V_{\rm GS}$ characteristics and (b) $I_{\rm D}$ – $V_{\rm DS}$ characteristics of the BCE a-IGZO TFT fabricated by photolithography for this dissertation                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Figure 2.14</b> The TFT $I_D$ – $V_{GS}$ characteristics of the CPL a-IGZO TFT fabricated by photolithography with PECVD a-SiO <sub>X</sub> passivation layer (300 nm)                                                                                                                                                                                                                                                                                                                                                                                                            |

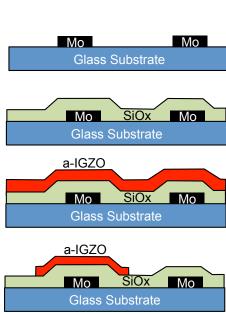

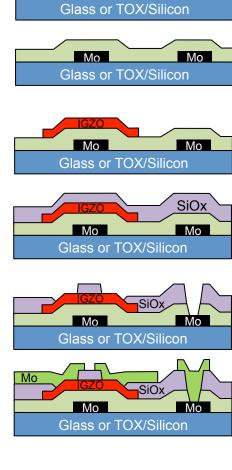

| Figure 2.15 Process flow of the Channel Protection Layer (CPL) a-IGZO TFT fabricated by photolithography                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

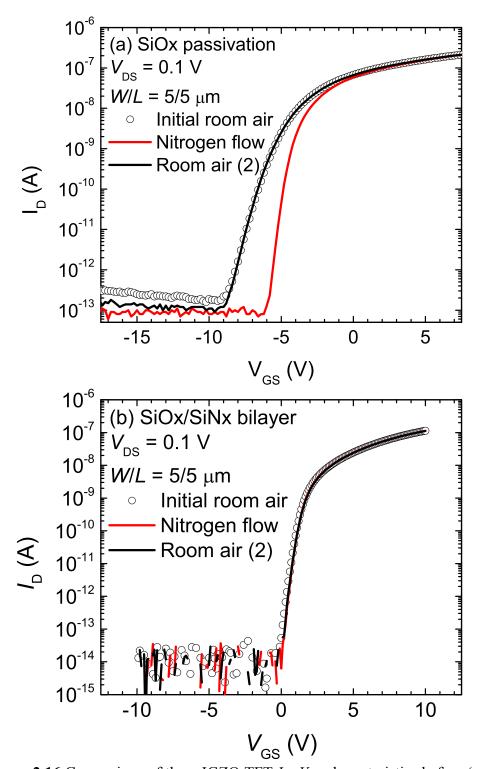

| <b>Figure 2.16</b> Comparison of the a-IGZO TFT $I_D$ – $V_{\rm GS}$ characteristics before (open circles), during (solid red line), and after (solid black line) nitrogen purging for TFTs with (a only PECVD a-SiO <sub>X</sub> passivation and (b) PECVD a-SiO <sub>X</sub> /a-SiN <sub>X</sub> bilayer passivation $3^2$                                                                                                                                                                                                                                                         |

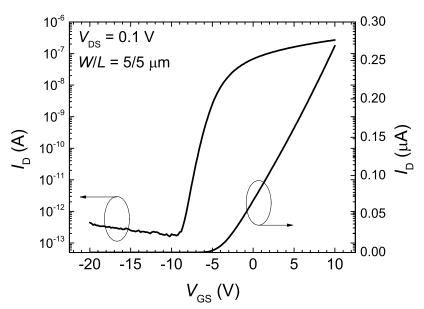

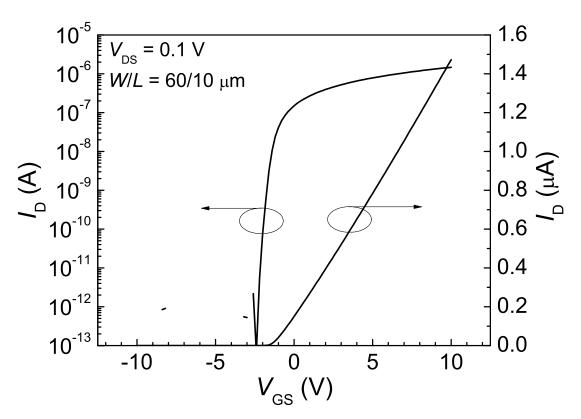

| Figure 2.17 The $I_D$ – $V_{GS}$ at $V_{DS}$ = 0.1 V of the S/D-recessed coplanar homojunction a-IGZO TFT fabricated by photolithography                                                                                                                                                                                                                                                                                                                                                                                                                                             |

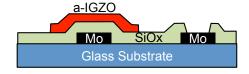

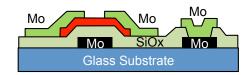

| <b>Figure 2.18</b> Process flow of the S/D-recessed coplanar homojunction a-IGZO TFT fabricated by photolithography                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

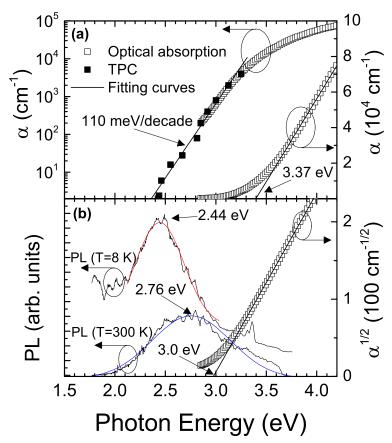

| <b>Figure 3.1</b> (a) The absorption spectrum of a-IGZO thin film is shown in linear and semi-logarithmic scale as empty squares ( $\square$ ). The transient photocapacitance (TPC) spectroscopy data from literature are reproduced in the figure as solid squares ( $\blacksquare$ ) [80]. The absorption edge in linear scale is used to extract the optical gap by extrapolating the <i>x</i> -intercept. (b) The PL emission at $T=8$ K and $T=300$ K are shown and fitted to Gaussian functions. The Tauc gap energy is extracted from the square root of optical absorption. |

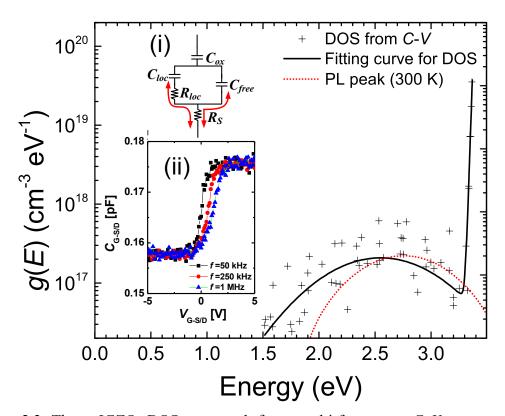

| <b>Figure 3.2</b> The a-IGZO DOS extracted from multi-frequency <i>C–V</i> measurements (crosshairs, +) and the associated fitting curve. Inset (i) shows the equivalent RC model used to extract the DOS from multi-frequency <i>C–V</i> measurements of a-IGZO TFTs. Inset (ii) shows the frequency-dependent <i>C–V</i> for one of the six a-IGZO TFTs as measured                                                                                                                                                                                                                |

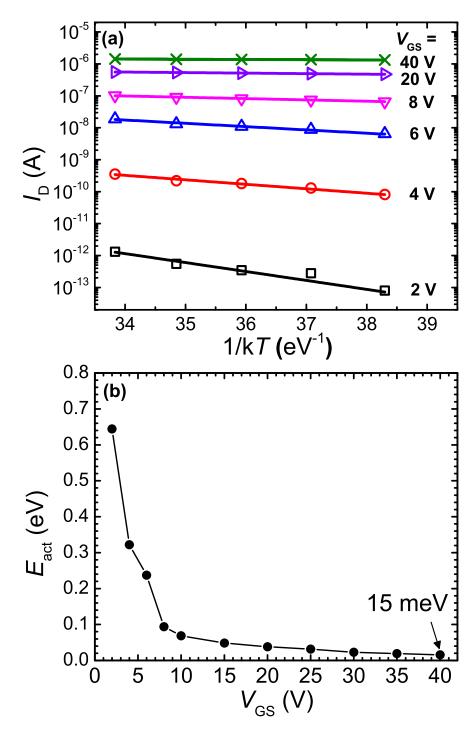

| <b>Figure 3.3</b> (a) The Arrhenius plot used to extract the a-IGZO activation energy $E_{\rm act}$ from the temperature-dependent TFT $I-V$ characteristics from 30 °C to 70 °C. (b) The activation energy of a-IGZO as a function of TFT gate-source voltage. The activation energy saturates at $E_{\rm act} = 15$ meV for high gate biases                                                                                                                                                                                                                                       |

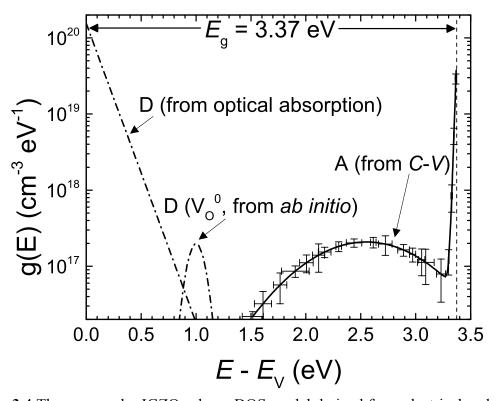

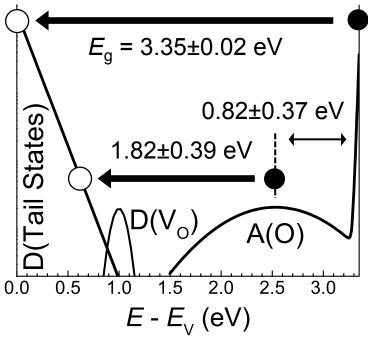

| <b>Figure 3.4</b> The proposed a-IGZO subgap DOS model derived from electrical and optical characterization. In this figure, D denotes donor-like states and A denotes acceptor-like states. The fully occupied deep-gap donor states $(V_0^0)$ are adopted from first-principles calculations in the literature [31]                                                                                                                                                                                                                                                                |

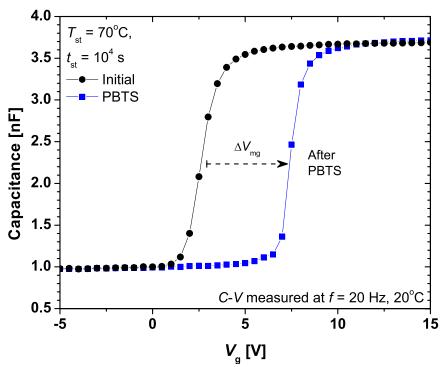

| <b>Figure 4.1</b> $C$ – $V$ curves before and after BTS. $\Delta V_{\rm mg}$ is the shift of mid-gap voltage before and after BTS with 10% O <sub>2</sub> /Ar flow ratio                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

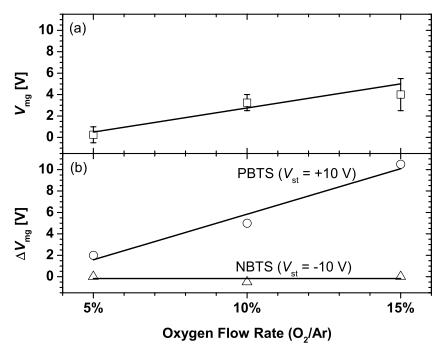

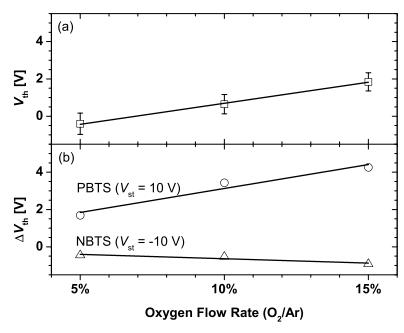

| <b>Figure 4.2</b> (a) The $V_{\text{mg}}$ variation before BTS ( $\bigcirc$ ) and (b) the shift of $V_{\text{mg}}$ after PBTS ( $\blacksquare$ ) and NBTS ( $\blacksquare$ ) with the oxygen flow rate                                                                                                                                                                                                      |

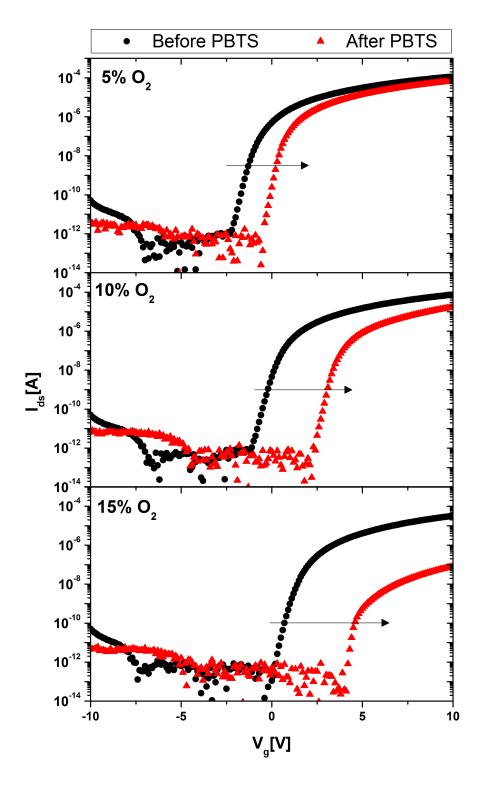

| <b>Figure 4.3</b> The device transfer characteristics for TFTs with different oxygen flow during sputtering. The solid circles and triangles represent before and after positive BTS $(V_{st} = 10 \text{ V})$ for 10,000 s at 70 °C respectively                                                                                                                                                           |

| <b>Figure 4.4</b> The device transfer characteristics for TFTs with different oxygen flow during sputtering. The solid circles and triangles represent before and after negative BTS $(V_{st} = -10 \text{ V})$ for 10,000 s at 70 °C respectively                                                                                                                                                          |

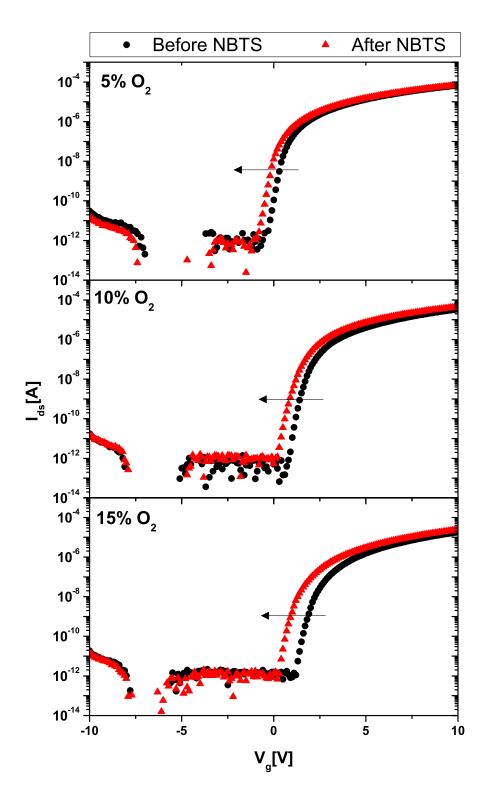

| Figure 4.5 (a) Variation of $V_{\text{th}}$ before BTS ( $\bigcirc$ ) and (b) after PBTS ( $\blacksquare$ ) and NBTS ( $\bigcirc$ ) with oxygen flow rate                                                                                                                                                                                                                                                   |

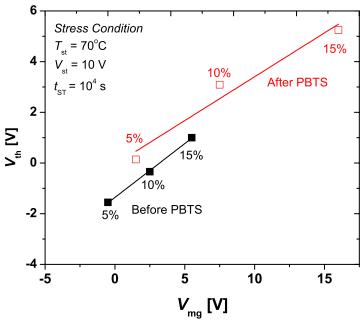

| <b>Figure 4.6</b> The relation between $V_{\rm th}$ and $V_{\rm mg}$ with oxygen flow rate before/after PBTS. 61                                                                                                                                                                                                                                                                                            |

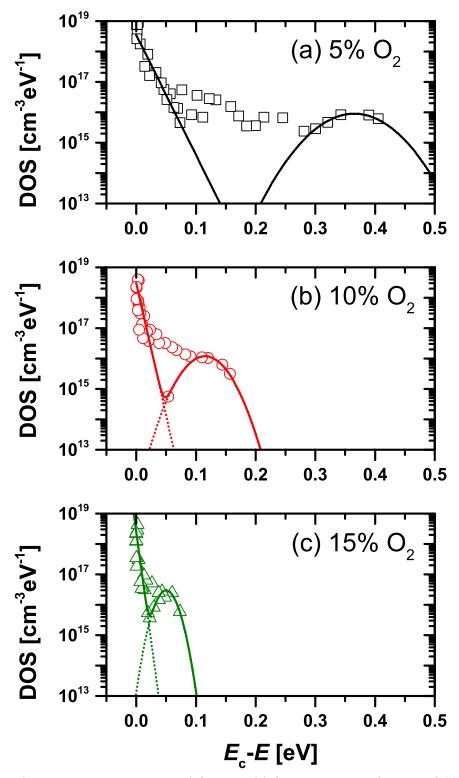

| <b>Figure 4.7</b> The a-IGZO DOS extracted from multi-frequency $C-V$ for $p_{O_2}$ of (a) 5%, (b) 10%, and (c) 15%. The solid lines are calculated from Equations (4-1) and (4-2), and the symbols are experimental data                                                                                                                                                                                   |

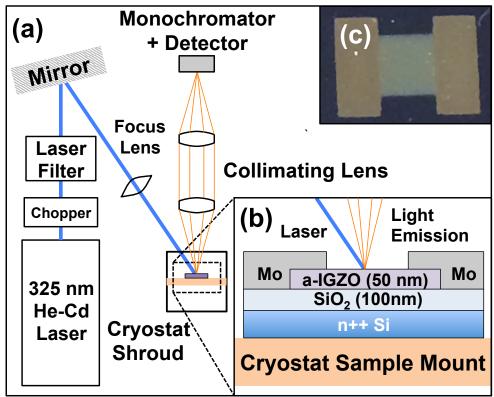

| <b>Figure 5.1</b> (a) The experimental setup for the photoluminescence spectroscopy performed in this study on a-IGZO thin-film transistor channel regions. (b) The topview diagram showing the sample mounted on the cryostat sample mount and a cross section diagram of the a-IGZO TFT with the channel region irradiated. (c) A photograph of the a-IGZO TFT fabricated by shadow masking in this study |

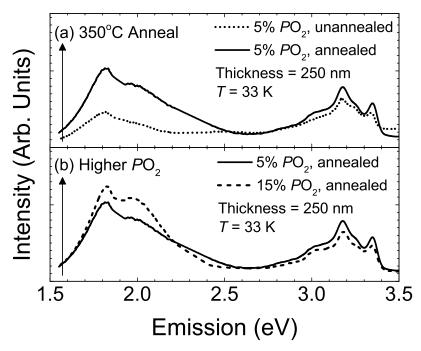

| <b>Figure 5.2</b> The PL emission spectrum of 250-nm a-IGZO films with (a) $p_{O_2} = 5\%$ annealed vs. unannealed and (b) $p_{O_2} = 5\%$ vs. 15%, both annealed                                                                                                                                                                                                                                           |

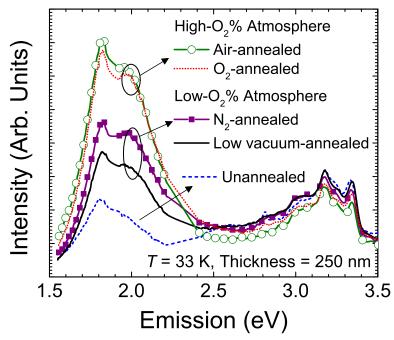

| <b>Figure 5.3</b> The PL emission spectrum for 250-nm a-IGZO thin film with $p_{\rm O_2} = 15\%$ annealed in ambient air (open green circles), O <sub>2</sub> (red dotted line), N <sub>2</sub> (purple solid squares), vacuum (black solid line), or as-deposited (blue dashed line)                                                                                                                       |

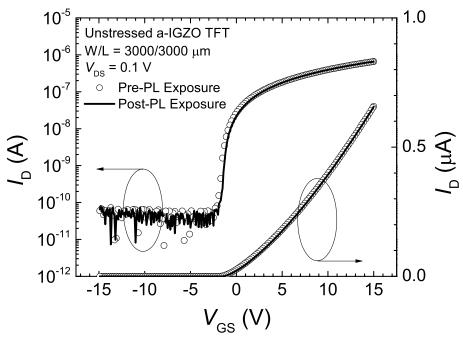

| <b>Figure 5.4</b> The a-IGZO TFT $I_D$ – $V_{GS}$ characteristics before and after exposure to the 325 nm laser. Time of exposure is between 5 and 10 minutes                                                                                                                                                                                                                                               |

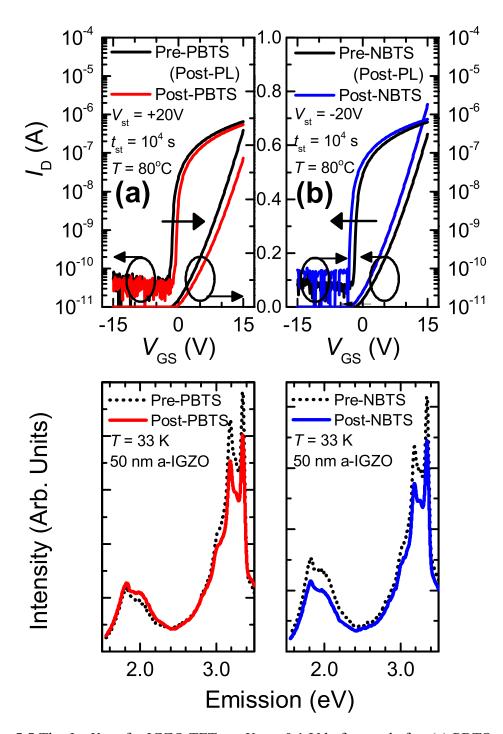

| <b>Figure 5.5</b> The $I_{\rm D}$ – $V_{\rm GS}$ of a-IGZO TFTs at $V_{\rm DS}$ = 0.1 V before and after (a) PBTS and (b) NBTS. The BTS applied are +20 V for PBTS and -20 V for NBTS, both at 80 °C with $V_{\rm DS}$ = 0 V for 10,000 s. The PL deep-level emissions are shown in (c) for PBTS and (d) for PBTS as figure insets. Directions of the arrows indicate the shift induced by the BTS          |

| T        | <b>e 5.6</b> A diagram showing the a-IGZO density of states model we have adopted [97]. The thicker arrows show the two proposed radiative transitions in a-IGZO. In the igure, D indicates donor-like states and A indicates acceptor-like states                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

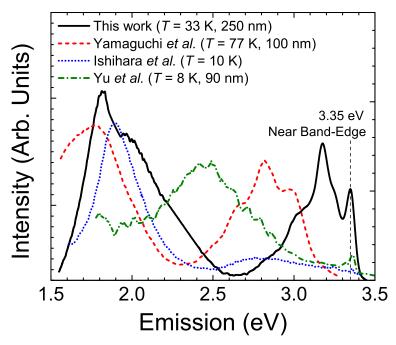

| th<br>ei | <b>e 5.7</b> The photoluminescence emission spectrum of a-IGZO thin film measured in his study (solid black line) superimposed with data from the literature: Yamaguchi <i>t al.</i> (dashed red line) [76], Ishihara <i>et al.</i> (dotted blue line) [78], and Yu <i>et al.</i> dash-dotted green line) [97]                         |

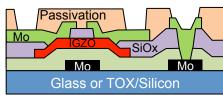

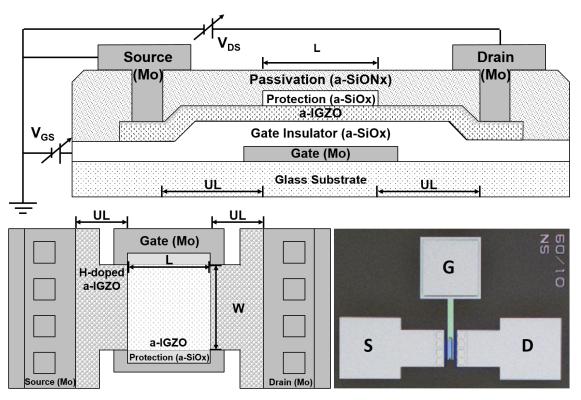

| us       | e 6.1 (Top) Cross-section and (Lower left) top-view diagram of the a-IGZO TFT sed throughout this study. (Lower right) Top-view micrograph of the fabricated evice                                                                                                                                                                     |

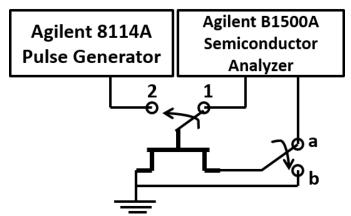

| po       | e 6.2 Diagram showing the experimental setup switching between stressing (switch ositions 1,a) and characterization (switch positions 2,b) steps by the E5250A witching matrix                                                                                                                                                         |

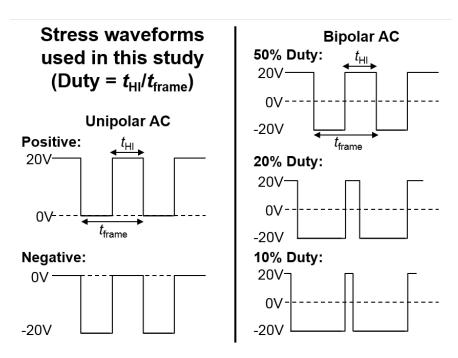

| sł       | e 6.3 The different gate bias stress waveforms used in this study. The left half hows unipolar positive and negative pulses. The right half shows bipolar pulses of ifferent duty cycles                                                                                                                                               |

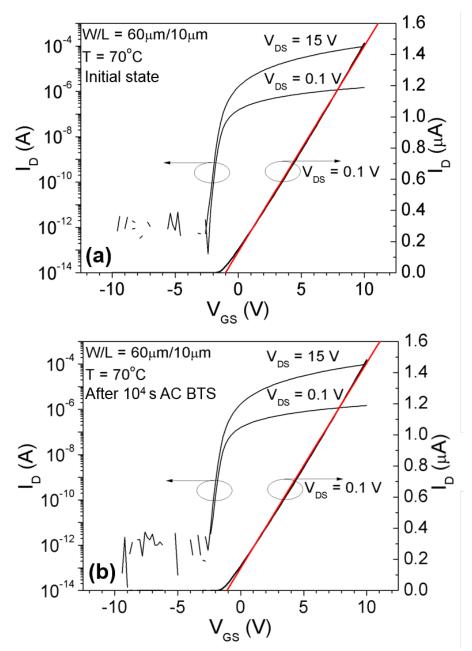

| re<br>at | <b>e 6.4</b> The transfer characteristics in the linear region ( $V_{\rm DS}$ = 0.1 V) and saturation egion ( $V_{\rm DS}$ = 15 V) of (a) the a-IGZO TFT used in this study and (b) the same TFT fter receiving 10 <sup>4</sup> s of ac BTS. The red line indicates the linear fit of the device $I_{\rm D}$ t the 20% and 80% points. |

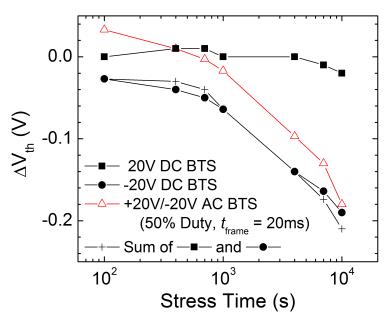

| (0       | <b>e 6.5</b> Side-by-side comparison of bipolar ac BTS (open triangles) and the sum crosshairs) of positive (solid squares) and negative (solid circles) dc BTS. Stressing nd measurements are done at $T_{\rm st} = 70$ °C in ambient air in the dark                                                                                 |

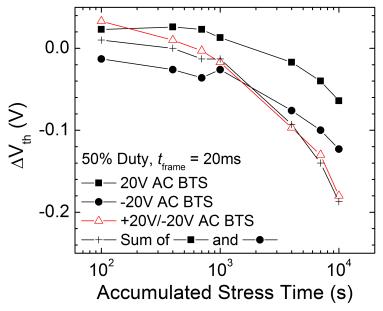

| (0       | <b>e 6.6</b> Side-by-side comparison of bipolar ac BTS (open triangles) and the sum crosshairs) of positive (solid squares) and negative (solid circles) unipolar ac BTS. tressing and measurements are done at $T_{\rm st} = 70$ °C in ambient air in the dark 90                                                                     |

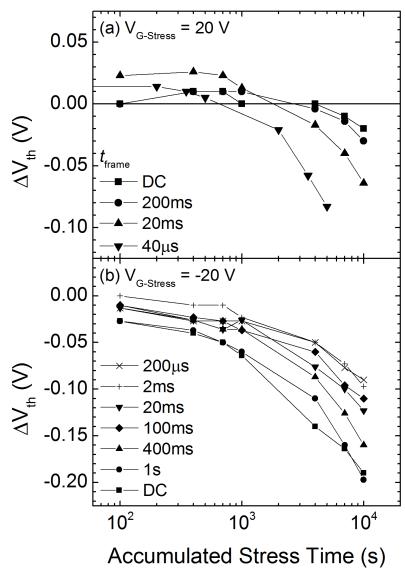

| u        | <b>e 6.7</b> Frame-time dependence of the a-IGZO TFT threshold voltage instability nder (a) positive unipolar ac BTS (b) negative unipolar ac BTS. Stressing and neasurements are done at $T_{\rm st} = 70$ °C in ambient air in the dark                                                                                              |

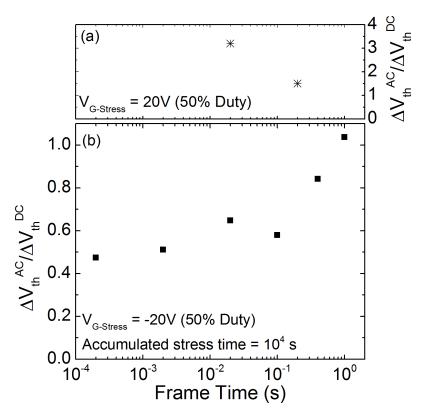

| ti       | <b>e 6.8</b> The ac BTS-induced threshold voltage shift as a function of ac stress frame times, normalized to the (a) positive or (b) negative dc BTS shift. Stressing and neasurements are done at $T_{\rm st} = 70$ °C in ambient air in the dark                                                                                    |

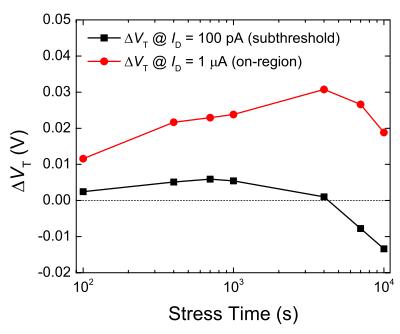

| th       | <b>e 6.9</b> The dc BTS-induced ( $V_{\text{G-Stress}} = +20 \text{ V}$ ) threshold voltage shift extracted by the constant current method ( $\Delta V_{\text{T}}$ ) at $I_{\text{D}} = 100 \text{ pA}$ for subtreshold region (solid red ircles) and $I_{\text{D}} = 1 \mu\text{A}$ for on-region (solid black squares)               |

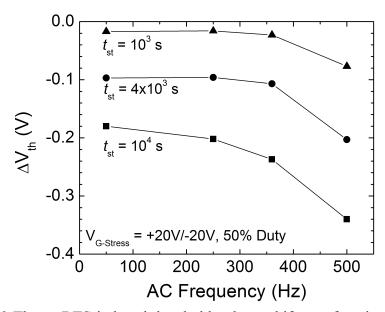

| <b>Figure 6.10</b> The ac BTS-induced threshold voltage shift as a function of applied bipolar stress frequency ( $1/t_{\rm frame}$ ). The duty cycle is kept at 50% for all frequencies. Stressing and measurements are done at $T_{\rm st} = 70$ °C in ambient air in the dark 95                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

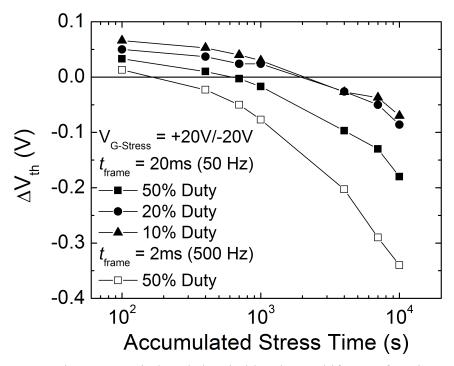

| <b>Figure 6.11</b> The ac BTS-induced threshold voltage shift as a function of accumulated stress time for different bipolar stress duty cycles (10, 20, and 50%) at $t_{\text{frame}} = 20 \text{ ms}$ (50 Hz). The $\Delta V_{\text{th}}$ induced by ac stress with $t_{\text{frame}} = 2 \text{ ms}$ (500 Hz) is reproduced here for reference. Stressing and measurements are done at $T_{\text{st}} = 70 ^{\circ}\text{C}$ in ambient air in the dark.                                                                                                                                          |

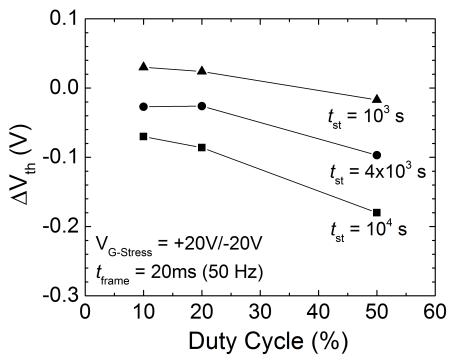

| <b>Figure 6.12</b> The ac BTS-induced threshold voltage shift as a function of duty cycle at $t_{\text{frame}} = 20 \text{ ms } (50 \text{ Hz})$ for different accumulated stress times. Stressing and measurements are done at $T_{\text{st}} = 70 ^{\circ}\text{C}$ in ambient air in the dark                                                                                                                                                                                                                                                                                                     |

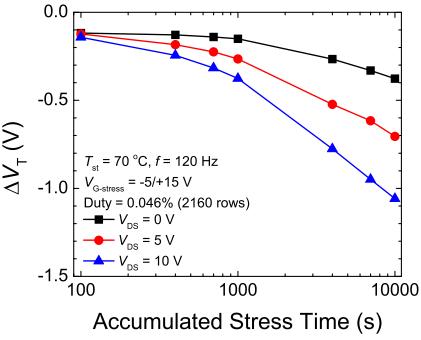

| Figure 6.13 The threshold voltage shift ( $\Delta V_{\rm T}$ ) extracted by the constant current method for a-IGZO TFT subject to various constant $V_{\rm DS}$ bias while voltage pulses are applied to the gate terminal. In this figure, stress temperature 70 °C and the frequency of the gate pulses is 120 Hz. Duty cycle of 0.046% represents 2160 rows of 4K UHD specification                                                                                                                                                                                                               |

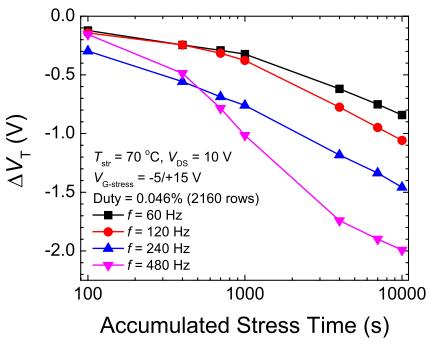

| Figure 6.14 The threshold voltage shift ( $\Delta V_{\rm T}$ ) extracted by the constant current method for a-IGZO TFT subject to constant $V_{\rm DS}=10~\rm V$ while voltage pulses are applied to the gate terminal. In this figure, stress temperature 70 °C and the frequency of the gate pulses is varied. Duty cycle of 0.046% represents the 2160 rows in 4K UHD specifications.                                                                                                                                                                                                             |

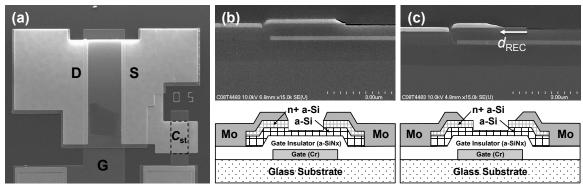

| <b>Figure 7.1</b> (a) Top-view micrograph and (b) SEM image and cross-section diagram of the bottom-gate a-Si:H TFT used in this study. The SEM image and cross-section diagram of the a-Si:H TFT with the S/D-recess is shown in (c), where the recess length ( $d_{REC}$ ) is 1 $\mu$ m                                                                                                                                                                                                                                                                                                            |

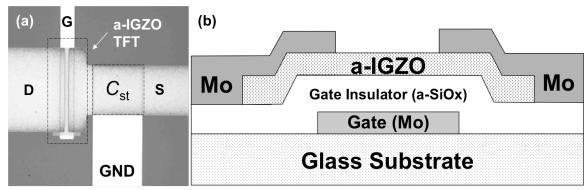

| <b>Figure 7.2</b> (a) Top-view micrograph and (b) cross-sectional diagrams and SEM images of the bottom-gate a-IGZO TFT used in this study                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

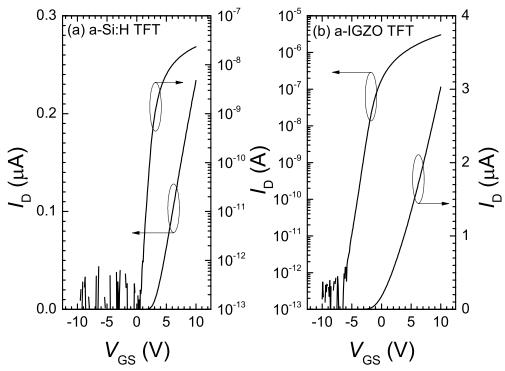

| <b>Figure 7.3</b> The TFT transfer characteristics ( $I_D$ – $V_{GS}$ ) of the (a) a-Si:H (normal) and (b) a-IGZO TFTs. In both subfigures, $V_{DS}$ = 0.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                         |

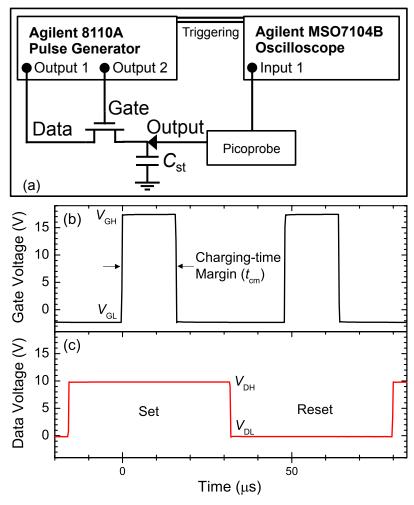

| <b>Figure 7.4</b> (a) The schematic for the setup used to evaluate the dynamic response of the one-TFT-one-capacitor test circuit. (b) The gate voltage applied is $V_{\rm GH} = 18$ V when charging/discharging and $V_{\rm GL} = -2$ V at all other times. The charging-time margin $t_{\rm cm}$ is the time available for the storage capacitor to completely charge/discharge. (c) The data voltage applied is $V_{\rm DH} = 10$ V for set and $V_{\rm DL} = 0$ V for reset. The set/reset duration is $3 \times t_{\rm cm}$ . The falling edge of the waveforms is 10 ns except where specified |

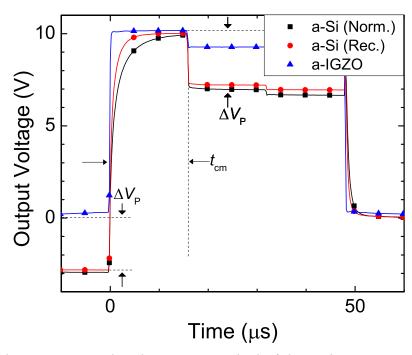

| <b>Figure 7.5</b> The $V_{\text{out}}$ measured at the source terminal of the a-Si:H or a-IGZO TFTs with the data and gate waveform applied. The feedthrough voltage $\Delta V_{\text{P}}$ is the output                                                                                                                                                                                                                                                                                                                                                                                             |

| voltage drop at the end of $t_{\rm cm}$ after the gate voltage is flipped from $V_{\rm GH}$ to $V_{\rm GL}$ . Storage capacitances are 0.19 pF for a-Si:H TFTs and 1.15 pF for a-IGZO TFT 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

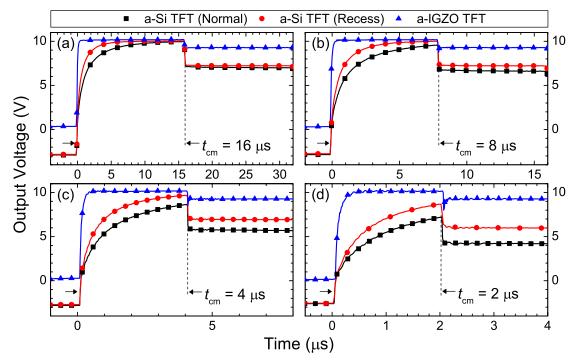

| <b>Figure 7.6</b> The output voltage at the source terminal of the a-Si:H and a-IGZO TFTs after applying the gate and data voltage waveforms based on (a) $t_{\rm cm} = 16 \mu \rm s$ , (b) $t_{\rm cm} = 8 \mu \rm s$ , (c) $t_{\rm cm} = 4 \mu \rm s$ , (d) $t_{\rm cm} = 2 \mu \rm s$ , corresponding to the AM-LCD specifications in Table 7.2. $C_{\rm st}$ is 1.15 pF for a-IGZO TFTs and 0.19 pF for a-Si:H TFTs                                                                                                                                                                                                                                                                                                                                              |

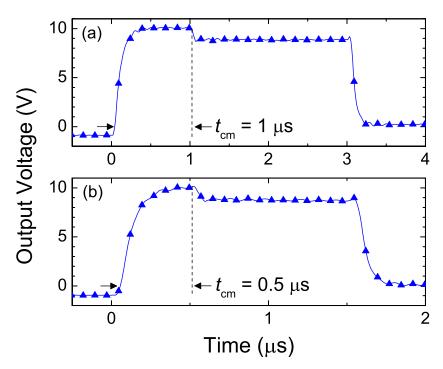

| <b>Figure 7.7</b> The output voltage at the source terminal of the a-IGZO TFTs after applying the gate and data voltage waveforms based on (a) $t_{\rm cm} = 1~\mu \rm s$ and (b) $t_{\rm cm} = 0.5~\mu \rm s$ corresponding to 8K×4K resolution at 240 and 480 Hz. For this figure, $C_{\rm st} = 1.15~\mu \rm s$                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

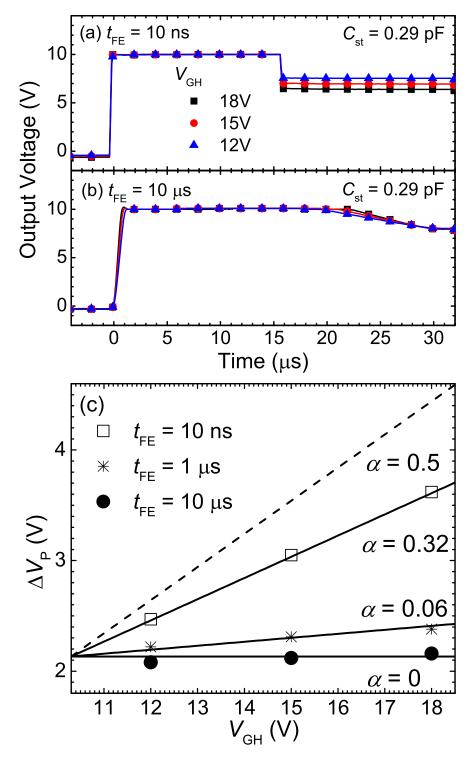

| <b>Figure 7.8</b> The output voltage of the a-IGZO TFT test circuit for waveforms with $V_{\rm GH}$ varied from 18 V to 12 V for (a) $t_{\rm FE} = 10$ ns and (b) $t_{\rm FE} = 10$ µs. The storage capacitance tested in this figure is 0.29 pF. In (c), the $\Delta V_{\rm P}$ extracted for $t_{\rm FE} = 10$ ns (empty squares), 1 µs (solid circles), and 10 µs (asterisks) are shown. The calculated $\Delta V_{\rm P}$ values are also shown in the figure for $\alpha = 0$ to 0.5                                                                                                                                                                                                                                                                            |

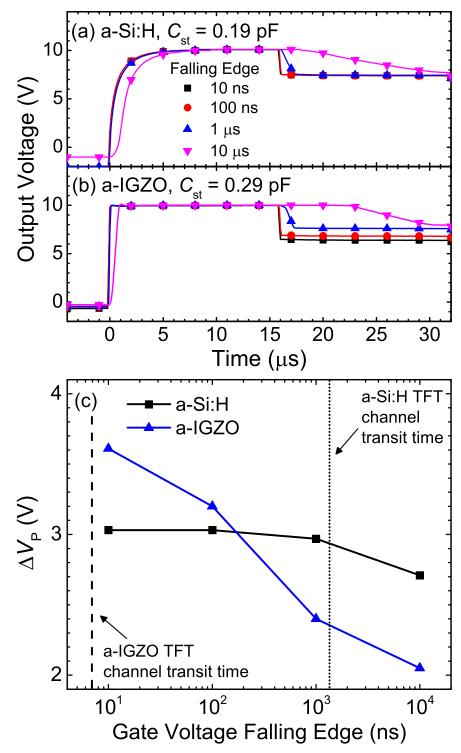

| <b>Figure 7.9</b> The $V_{\text{out}}$ of the (a) a-Si:H and (b) a-IGZO TFT test circuits for waveforms with $t_{\text{FE}}$ varied from 10 ns to 10 μs. The $C_{\text{st}}$ evaluated in this figure is 0.19 pF and 0.29 pF for the a-IGZO and a-Si:H TFTs, respectively. The $\Delta V_{\text{P}}$ are extracted from (a) and (b) and shown in (c). Using Equation (7-14), channel transit times is calculated and denoted in (c) as dashed line and dotted line for the a-IGZO and a-Si:H TFTs, respectively                                                                                                                                                                                                                                                      |

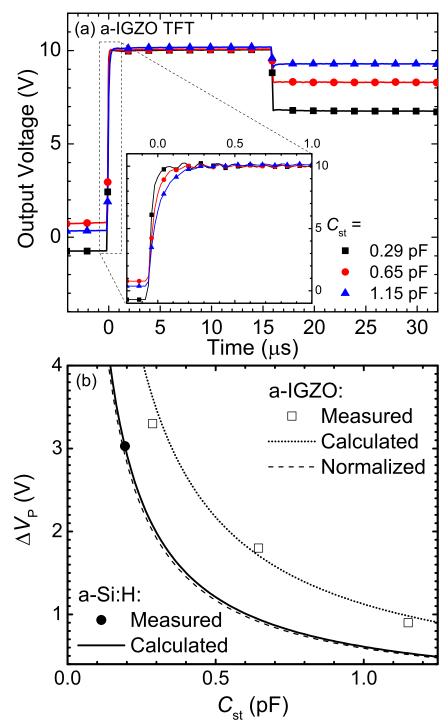

| <b>Figure 7.10</b> (a) The $V_{\text{out}}$ of a-IGZO TFT test circuits with different $C_{\text{st}}$ . The charging-time margin used for this figure is $t_{\text{cm}} = 16  \mu \text{s}$ . (b) The $\Delta V_{\text{P}}$ for a-IGZO TFTs with different $C_{\text{st}}$ extracted from (a) is shown as empty squares. The $\Delta V_{\text{P}}$ is calculated using Equation (7-13) and shown in the figure as a dotted line ( $\alpha = 0.32$ ). The normal a-Si:H TFT $\Delta V_{\text{P}}$ is also shown in the figure as a solid circle, with the calculated values ( $\alpha = 0.5$ ) represented as a solid line. The same calculation is performed after normalizing the a-IGZO TFT for $W$ , $L$ , $OVLP$ , and $C_{\text{GI}}$ and shown a dashed line. |

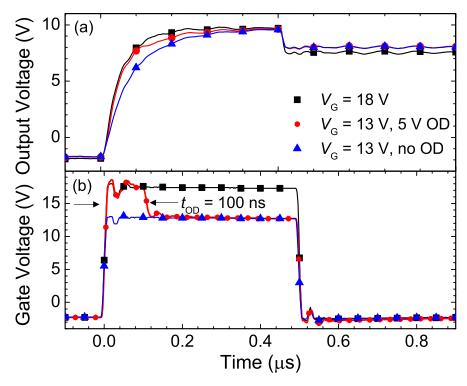

| <b>Figure 7.11</b> The overdrive operation of the a-IGZO TFT in the test circle is shown in (a) The waveforms for baseline, overdrive, and full overdrive are shown in (b). Overdrive operation adds $t_{\rm OD} = 100$ ns of $V_{\rm OD} = 5$ V on top of the baseline $V_{\rm GH} = 13$ V at the beginning of $t_{\rm cm}$ . In full overdrive, the entire duration of $t_{\rm cm}$ is $V_{\rm GH} = 18$ V. For this experiment, a test circuit with $C_{\rm st} = 0.65$ pF was evaluated                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## LIST OF TABLES

| Table 1.1 List of commercially available 4K UHD TVs as of April 2015    2                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2 Comparison of different active-matrix flat panel display backplane technologies for ultra-high definition television                                                                                   |

| <b>Table 2.1</b> Extracted device parameters in the linear region ( $V_{DS} = 0.1 \text{ V}$ ) for the a-IGZO TFT with PECVD a-SiO <sub>X</sub> or a-SiO <sub>X</sub> /a-SiN <sub>X</sub> bilayer as passivation |

| Table 3.1 Parameters used in the proposed a-IGZO subgap DOS model                                                                                                                                                |

| Table 4.1 The initial parameters of I–V curves with O2/Ar flow ratios during deposition      60                                                                                                                  |

| <b>Table 4.2</b> Linear fitting curve parameters $(V_{th} = aV_{mg} + b)$                                                                                                                                        |

| Table 4.3 Exponential subgap DOS fitting parameters for O2/Ar flow rate    64                                                                                                                                    |

| <b>Table 4.4</b> Gaussian subgap DOS fitting parameter for O <sub>2</sub> /Ar flow rate                                                                                                                          |

| <b>Table 6.1</b> Extracted parameters of the a-IGZO TFT in the linear region ( $V_{DS} = 0.1 \text{ V}$ ) 88                                                                                                     |

| Table 7.1 Parameters of the thin-film transistors and test circuits fabricated                                                                                                                                   |

| Table 7.2 The calculated charging-time margins calculate from various HD and UHD         AM-LCD resolution and frame rate specifications                                                                         |

**ABSTRACT**

Title: Amorphous In-Ga-Zn-O Thin-Film Transistors for Next Generation Ultra-High

Definition Active-Matrix Liquid Crystal Displays

Chair: Professor Jerzy Kanicki

Next generation ultra-high definition (UHD) active-matrix flat-panel displays have

resolutions of 3840×2160 (4K) or 7680×4320 (8K) pixels shown at 120 Hz. The UHD

display is expected to bring about immersive viewing experiences and perceived realness.

The amorphous In-Ga-Zn-O (a-IGZO) thin-film transistor (TFT) is a prime candidate to

be the backplane technology for UHD active-matrix liquid crystal displays (AM-LCDs)

because it simultaneously fulfills two critical requirements: (i) sufficiently high field-

effect mobility ( $\mu_{FE} = 10 \text{ cm}^2/\text{V} \cdot \text{s}$ ) and (ii) uniform deposition in the amorphous phase

over a large area.

We have developed a robust a-IGZO density of states (DOS) model based on a

combination of experimental results and information available in the literature. The

impact of oxygen partial pressure during a-IGZO deposition on TFT electrical

properties/instability is studied. Photoluminescence (PL) spectra are measured for

a-IGZO thin films of different processing conditions to identify the most likely electron-

hole recombination. For the first time, we report the PL spectra measured within the

XV

a-IGZO TFT channel region, and differences before/after bias-temperature stress (BTS) are compared.

To evaluate the reliability of a-IGZO TFTs for UHD AM-LCD backplane, we have studied its ac BTS instability using a comprehensive set of conditions including unipolar/bipolar pulses, frequency, duty cycle, and drain biases. The TFT dynamic response, including charging characteristics and feedthrough voltage ( $\Delta V_P$ ), are studied within the context of 4K and 8K UHD AM-LCD and compared with hydrogenated amorphous silicon technology. We show that the a-IGZO TFT is fully capable of supporting 8K UHD at 480 Hz. In addition, it is feasible to reduce a-IGZO TFT  $\Delta V_P$  by controlling for non-abrupt TFT switch-off.

### **CHAPTER 1**

#### Introduction

## 1.1 Overview and Background

# 1.1.1 Current status of backplane technology for ultra-high definition activematrix liquid crystal displays

In the first decade of the twenty-first century, the active-matrix liquid crystal display (AM-LCD) became the dominant display technology over the plasma display panel and the cathode-ray tube monitor. During the same period, video image specifications made the leap from 480i standard definition (640×480 pixels, interlaced) to 1080p full high-definition (Full HD, 1920×1080 pixels, progressive scan) recorded/shown at 60 frames per second. Despite the emergence of active-matrix organic light-emitting diode (AM-OLED) technology, the AM-LCD is expected to hold over 95% of the TV market and 70% of the mobile display market by 2017 [1].

In 1995, the NHK (Japan Broadcasting Corporation) Science & Technology Research Institute started research on the next generation digital video format, dubbed Super Hi-Vision [2]. It was defined as 3840×2160 pixels (4K) or 7680×4320 pixels (8K) displayed at a frame rate of up to 120 Hz. Studies in human visual perception have shown that the sensation of immersion ("being-there") and perceived realness (real objects and images become indistinguishable) can be achieved when field-of-view (FOV) approaches

**Figure 1.1** The field-of-view and the corresponding angular resolution offered by various AM-FPD resolutions when viewed at the optical distance for any given display size [6].

100° and angular resolution exceeds 30 cycles/degree (cpd) [3]–[5]. For a fixed angular resolution and viewing distance, FOV is increased for greater pixel count. According to Figure 1.1, assuming the minimal 30 cpd and a fixed optimal viewing distance for any given panel size, the FOV increases to 60° and 100° for 4K and 8K resolutions, respectively [6]. In addition, the frame rate is increased to 120 Hz to reduce the motion blur of moving images, further enhancing the viewing experience. In 2012, Super Hi-Vision, or Ultra High Definition (UHD) everywhere outside of Japan, was formally adopted by the International Telecommunications Union as Recommendation BT.2020 for next generation information displays [6], [7].

At time of writing, 4K UHD TVs are just beginning to enter the market while 8K UHD TVs are several years away from commercialization. Table 1.1 lists the

| Manufacturer | Model  | Size | Resolution @ Frame<br>Rate | MSRP   |

|--------------|--------|------|----------------------------|--------|

| Sharp        | UD27U  | 70"  | 3840×2160 @ 60 Hz          | \$3600 |

| Sony         | X950B  | 65"  | 3840×2160 @ 60 Hz          | \$6000 |

| Samsung      | HU9000 | 65"  | 3840×2160 @ 60 Hz          | \$6000 |

| LG           | UB9800 | 65"  | 3840×2160 @ 60 Hz          | \$6000 |

**Table 1.1** List of commercially available 4K UHD TVs as of April 2015.

4K TVs from the major manufacturers on the market as of April 2015, along with their size, suggested retail price, and maximum supported display specifications. The challenge with very high resolution on a large area (over 40") display is multifaceted. Manufacturing yield decreases with higher number of pixels—a single defective pixel could potentially ruin an entire substrate. Another issue is RC line delay on the select and data bus lines, where a large number of pixels makes the margin of error for accommodating signal propagation delays on a large substrate even smaller [8]. These are all solvable with process engineering or design improvements, such as low-resistivity Cu bus lines [9] and dual-sided row drivers [10]. A more fundamental problem, and one more difficult to overcome without modifying display production lines, is the AM-LCD thin-film transistor (TFT) backplane. In active-matrix addressing, an array of TFT pixel circuits directly drives and charges the individual liquid crystal cells. This addressing method significantly reduces cross talk between neighboring pixels and enables far greater resolution compared to passive-matrix addressing. Presently, the two mainstream TFT backplane technologies are hydrogenated amorphous silicon (a-Si:H) and lowtemperature poly-silicon (LTPS).

A-Si:H TFTs can be fabricated with a simple 4–5 mask process, enabling low production costs with very high throughput. Its uniform amorphous deposition over a

large area makes it suitable for large LCD TVs, currently produced on Gen 10 (2.8 m  $\times$  3 m) glass substrates. However, its low field-effect mobility ( $\mu_{FE}$ ) of 0.5–1 cm<sup>2</sup>/V·s is only adequate for up to 1080p Full HD and insufficient for UHD TV specifications.

On the other hand, the LTPS TFT has  $\mu_{\rm FE}$  of around 100–200 cm<sup>2</sup>/V·s, which well exceeds the requirements for 4K and 8K UHD at 120 Hz. Electrical stability, which directly impacts display lifetime and pixel circuit complexity, is also much better for LTPS than a-Si:H TFTs. The biggest weakness of LTPS TFT technology is the non-uniformity of electrical properties due to polycrystalline grain boundaries, which are typically on the order of 0.3-3 µm depending on process conditions. The single most critical step in the fabrication of LTPS TFT is the crystallization of amorphous silicon into polysilicon. Today, this can be achieved by several different methods, each with its own advantage and disadvantages: excimer-laser annealing (ELA) [11], sequential lateral solidification (SLS) [12], metal seeding [13], or solid-phase recrystallization [14]. Despite its excellent electrical properties and stability, LTPS recrystallized from any growth method suffers from the necessary trade-off between cost and performance. This is particularly evident in the well-established ELA process: uniformity improves with more irradiations by the excimer laser at a cost of reduced productivity and throughput. In order to produce uniform LTPS TFTs with  $\mu_{FE} = 100 \text{ cm}^2/\text{V} \cdot \text{s}$  on a Gen 4 glass substrate, two scans across the whole substrate is required due to the limited beam length, with each unit processing area irradiated 10-20 times by the laser for each scan—more irradiations corresponds to better electrical properties. Furthermore, additional nonuniformity is introduced in the area of overlap between each scan, making production of large area displays extremely challenging. Non-uniformity of electrical properties over a

| Requirement               | a-Si:H                                          | LTPS                                      | a-IGZO                             |

|---------------------------|-------------------------------------------------|-------------------------------------------|------------------------------------|

| Large-Area<br>Uniformity  | Good                                            | Poor                                      | Good                               |

| Mobility                  | Poor $0.5-1 \text{ cm}^2/\text{V}\cdot\text{s}$ | Excellent<br>100-200 cm <sup>2</sup> /V·s | Good<br>10-20 cm <sup>2</sup> /V·s |

| Electrical Stability      | Poor                                            | Excellent                                 | Better than a-Si:H                 |

| Process Complexity & Cost | Low                                             | High                                      | Lower than LTPS                    |

**Table 1.2** Comparison of different active-matrix flat panel display backplane technologies for ultra-high definition television.

large substrate will manifest itself as uneven patches of changes in luminance, known as *mura* (Japanese for blemish). It is evident that a new backplane technology is needed to satisfy the requirements of backplane technology for large-area UHD AM-LCDs.

Since the publication of the seminal paper by Nomura *et al.* in 2004 [15], the ternary oxide semiconductor amorphous In-Ga-Zn-O (a-IGZO) has emerged as a strong candidate to be the backplane technology for next-generation UHD AM-LCDs. The a-IGZO has  $\mu_{FE} = 10 \text{ cm}^2/\text{V} \cdot \text{s}$ , which is substantially higher than that of a-Si:H, and it can be uniformly deposited in the amorphous phase over a large substrate area. In amorphous covalent semiconductors such as a-Si:H, electrons conduct through highly directional sp<sup>3</sup> bonds, which are severely impacted by bonding angle variations and thus have very low  $\mu_{FE}$  [16]. In an ionic semiconductor like a-IGZO, the  $\mu_{FE}$  is higher than most other amorphous materials because conduction occurs through the overlapping s orbital of the metal ions—in this case the large In<sup>3+</sup> ion. In addition, a-IGZO TFT has a low off-state leakage current ( $I_{off}$ ), can be processed with 4–5 masks, is transparent within the visible-light spectrum, and has better electrical stability than a-Si:H TFTs [15], [17]–[19]. The

pros and cons of each backplane technology in the context of requirements for UHD AM-LCD are summarized in Table 1.2.

#### 1.1.2 Requirements for UHD AM-LCD Backplane Technology

In evaluating TFT backplane technology for application to next generation UHD AM-LCDs, the following should be considered:

For large-area UHD LCD TVs, the  $\mu_{FE}$  should be sufficiently high to ensure that each row of liquid crystal is charged/discharged to the correct data voltage level within one gate selection time. The gate selection time is simply equal to  $1/(Frame\ Rate \times Number\ of\ Rows)$ , which would correspond to 3.8 µs for 4K UHD at 120 Hz. Incomplete charging/discharging directly leads to grayscale errors and image retention. The charging characteristics can be roughly estimated as a RC exponential effect i.e.  $V = V_{data}\ (1-\exp(-t/RC))$ . After t = 5RC, V would have reached 99.3% of the target  $V_{data}$  and can be considered as fully charged. The effective resistance and capacitance are given by

$$R = R_{data} + R_{on} = R_{data} + \frac{L}{WC_G \mu_{FE}(V_{GS} - V_{th})}, \tag{1-1}$$

and

$$C = C_{st} + C_{LC} + C_{GS} + C_{data}, (1-2)$$

where  $R_{\rm data}$  is the data bus line resistance,  $R_{\rm on}$  the TFT on-resistance, W and L the TFT channel width and length,  $C_{\rm G}$  the TFT gate insulator capacitance,  $V_{\rm GS}$  the applied gate pulse amplitude,  $C_{\rm st}$  the storage capacitance,  $C_{\rm LC}$  the liquid crystal capacitance,  $C_{\rm GS}$  the TFT parasitic capacitance, and  $C_{\rm data}$  the data bus line parasitic capacitance. Assuming a 50" AM-LCD with Cu bus lines, and negligible

$C_{\text{data}}$  and  $C_{\text{GS}}$ , we can estimate that  $\mu_{\text{FE}}$  should be at least 1.5 cm<sup>2</sup>/V·s in order to fully charge all the pixels in a 4K UHD AM-LCD operating at 120 Hz. This value is just above the typical 1 cm<sup>2</sup>/V·s achievable for a-Si:H TFTs, but can be easily fulfilled with the a-IGZO TFT.

- In order to support a very large display (> 50") in which the gate and data bus line resistances may become significant, adoption of low resistivity metals such Al ( $\rho$  = 4  $\mu\Omega$ ·cm) or Cu ( $\rho$  = 2.5  $\mu\Omega$ ·cm) may become necessary. Because Cu has been shown to be relatively unstable and may diffuse during device processing [20], a compatible TFT fabrication process should be developed if not already available.

- To achieve higher pixel density for UHD AM-LCD resolution without sacrificing the aperture ratio, the TFT should be scaled down accordingly. As mentioned in the previous section, when the resolution on a 50" LCD TV increases from Full HD to 8K UHD, the size of each subpixel reduces by a factor of 16 to 144  $\mu$ m × 48  $\mu$ m. In the same way, the TFT W and L should both be reduced to 1/4 to maintain similar  $I_D$ – $V_{GS}$  characteristics while keeping aperture ratio the same. In this case, to ensure proper TFT operation, the source/drain (S/D) contact resistance should be as low as possible and/or the TFT  $\mu_{FE}$  needs to be sufficiently high. In a short-channel TFT,  $\mu_{FE}$  becomes lower because the S/D contact resistance ( $R_{SD}$ ) dominates channel on-resistance. Back *et al.* has shown that in the high-performance coplanar homojunction a-IGZO TFT with highly-conductive S/D contact regions formed by hydrogen doping, the S/D contact resistance is negligible [21]. In such a device configuration, the a-IGZO TFT  $\mu_{FE}$  = 13.1 cm<sup>2</sup>/V·s did not degrade even when L = 5  $\mu$ m.

The pixel feedthrough voltage ( $\Delta V_P$ ), a dc voltage drop at the pixel electrode that is responsible for flicker and image retention, should be made as low as possible. While flicker may be offset with row-, line-, or dot-inversion driving methods, reducing  $\Delta V_P$  to approximately 0.1 V is critical for minimizing image retention. In addition, it would be beneficial to display engineers if the magnitude of  $\Delta V_P$  can be reliably predicted based on driving waveform and TFT configuration. A typical voltage divider equation

$$\Delta V_P = (V_{GH} - V_{GL}) \frac{c_{GS}}{c_{GS} + c_{St} + c_{LC}}$$

$$\tag{1-3}$$

can be used to estimate  $\Delta V_{\rm P}$  to the first order, but is inadequate for in-depth analysis due to contributions from accumulated channel charge. A more robust model should be developed and evaluated for the UHD AM-LCD TFT backplane technology.

The TFT backplane should be sufficiently reliable against pulsed (ac) biastemperature stress (BTS) corresponding to AM-LCD addressing conditions. In a previous-generation 60-Hz Full HD (1920×1080) AM-LCD display, the select (gate) pulse for each row has pulse width of 16  $\mu$ s, and the pulse amplitude is typically +13/-13 V. For such an operating condition, Chiang *et al.* showed that it would take approximately 10 years for the a-Si:H TFT threshold voltage shift ( $\Delta V_{th}$ ) to reach the nominal end-of-life limit for AM-LCDs [22]. In UHD AM-LCD operation, the gate driving waveform is expected to have higher frequencies (for higher refresh rates), shorter pulse widths (for larger number of rows), and higher gate bias amplitude (for faster pixel charging). These are all

stress conditions that should be addressed in the TFT backplane technology for UHD AM-LCDs.

- A robust DOS model based on experimental observations should be developed for

use in numerical simulations. The model should be able to accommodate a wide

variety of fabrication conditions and reflect them on the DOS parameters.

- For low-cost mass-production, the fabrication process should be simple and the

mask count should be as low as possible while preserving electrical properties and

reliability.

#### 1.1.3 Current Status of Amorphous In-Ga-Zn-O TFTs for UHD AM-LCDs

Despite its obvious advantages, the a-IGZO TFT is still not yet the mainstream backplane technology for AM-LCDs. This is primarily due to the need to improve manufacturing yield and uncertainties in both device processing and achieving consistent electrical performance and stability. Although companies such as LG [23], AU Optronics [24], and Sharp [25] have demonstrated large-area 4K or 8K UHD AM-LCD prototypes with a-IGZO TFT backplanes, much work remains to be done towards their large-scale commercial production.

In amorphous semiconductors such as a-Si:H, localized states within the energy band gap arise from structural disorder (bond angles and length variations), dangling bonds, non-stoichiometry, and carrier scattering at defect sites [16], [26]. Such subgap density of states (DOS) dominates the electrical properties and stability of a-Si:H TFTs. Today it is generally accepted that the DOS can also impact a-IGZO TFT electrical performance, although the microscopic origin of DOS in a-Si:H and a-IGZO should be very different. Hsieh *et al.* extracted the density of acceptor-like states near the conduction band

minimum  $(E_C)$  in a-IGZO by fitting TFT current-voltage (I-V) data to technology computer-aided design (TCAD) simulations originally developed for a-Si:H technology [27]. Nomura et al. observed a large density of subgap states near the valence band maximum  $(E_{\rm V})$ , possibly the origin for the lack of p-type operation, using hard X-ray photoelectron spectroscopy [28]. Below the band gap, optical absorption spectrum showed tail-like decay that can be described by the Urbach relation, although its characteristic energy slope in the literature varies with sample quality and preparation [28]–[30]. Kamiya et al. and Chen et al. performed first-principles calculations using density functional theory and found that for IGZO, oxygen vacancies form fully occupied donor levels located at 1 eV above  $E_V$  [29], [31]. Temperature-dependent TFT characteristics can also be used to extract DOS near the  $E_{\rm C}$ , as shown by Chen et al. with the Meyer-Neldel rule [32] and Lee et al. with trap-limited conduction at lowtemperature (77 K) [33]. For the next-generation a-IGZO-backplane active-matrix flatpanel display to be realized, a robust a-IGZO DOS model is needed for the design of devices and circuits using 2D numerical and SPICE simulations, respectively.

In order for a-IGZO TFTs to be widely adopted as the backplane technology for UHD AM-LCDs, its threshold voltage ( $V_{th}$ ) stability under BTS, a critical factor for robust AM-LCDs with long lifetimes, should be evaluated in detail. Steady state (dc) positive and negative BTS, both in the dark and illuminated, have been the subject of much theoretical and experimental research effort and are well-documented [34]–[37]. Our group previously reported that the dc BTS-induced  $\Delta V_{th}$  instability of the a-IGZO TFT is significantly lower than that of the a-Si:H TFT [38], in agreement with experimental data in published literature. Although there is substantial work on the dc BTS stability of a-

IGZO TFTs, the steady-state condition is not an accurate representation of AM-LCD operation, which biases the transistors in positive and negative alternating (ac) pulses. A direct comparison of ac and dc BTS on a-Si:H TFTs shows that dc BTS reliability is a poor predictor of ac BTS  $\Delta V_{th}$  [22]. Thus there is strong motivation to study and verify ac BTS behavior such that the lifetime of UHD displays with a-IGZO TFT backplane technology may be properly evaluated.

Several methods have been proposed to improve TFT electrical stability, such as thermal annealing [28], [39], [40], hydrogen incorporation [41], nitrogenation [42], [43], passivation [44]–[46], among other methods [47]–[51]. However, the microscopic origin of  $V_{th}$  shift is still not yet completely understood. A hypothesis proposed in the literature suggests that oxygen-related sub-band gap states, such as oxygen vacancies, are responsible for the  $V_{th}$  instability under BTS [52], [53]. To clarify the origin of  $V_{th}$  shift from an atomic-bonding point of view, X-ray photoelectron spectroscopy studies have been reported for oxygen 1s states [40], [41], [54]–[56]. Results indicated that the higher binding energy peak of oxygen 1s states is related to smaller  $\Delta V_{th}$  induced by BTS. It was assumed that higher oxygen flow during channel layer formation caused more oxygen to be incorporated into the final a-IGZO thin film, and this was found to significantly impact device BTS stability [57], [58]. However, more work is needed to ascertain the role of oxygen incorporation in a-IGZO thin film and its impact on device performance and stability.

In addition to electrical reliability, the actual dynamic operation characteristics of a-IGZO TFTs for AM-LCD pixel electrodes should be fully evaluated. Improvements to display resolution and frame rate both correspond to shorter time margin available for each pixel to complete charging, thus placing stringent requirements on TFT dynamic response. The dynamic response of the a-Si:H TFT pixel electrode has been studied extensively in literature. The  $\Delta V_{\rm P}$ , which results from gate-source overlap capacitance  $(C_{GS})$  and channel charge redistribution, is the main source of image flickering in AM-LCD operation and a key metric in TFT dynamic response [59]. Takabatake et al. reported a robust analytical model for  $\Delta V_{\rm P}$  that is very consistent with experimental values [60]. Kitazawa et al. investigated the impact of a-Si:H TFT device structural differences on  $\Delta V_{\rm P}$  [61]. Aoki conducted a comprehensive study detailing an analytical model of a-Si:H TFT dynamic operation with the liquid-crystal cell capacitance included, and the model has been verified by experimental data [62]. Lee et al. studied the dynamic response of a-Si:H TFT for AM-OLED pixel electrode, and reported in detail  $\Delta V_P$  and charging time ( $t_{ch}$ ) for various TFT structures and waveform parameters [63]. Our group has previously described preliminary results on the dynamic response of a-IGZO TFT pixel electrodes in terms of its  $C_{\rm st}$  and TFT dimension dependences [64]. Initial data suggest that a-IGZO TFT showed very favorable dynamic characteristics when operated at a very high frequency. To date, however, comprehensive studies of a-IGZO TFT dynamic response are still lacking.

In this dissertation, our goal is to address the issues directly related to TFT electrical properties and stability under UHD dynamic operation, which include dynamic charging behavior, pixel  $\Delta V_P$ , and ac BTS. A robust DOS model will also be developed to enable the development of a-IGZO TFTs suitable for dynamic operation in the active-matrix backplane of UHD AM-LCDs. Various experimental evidence will be used to support the DOS model.

## 1.2 Thesis Organization

This thesis begins with a detailed description in chapter 2 of a-IGZO TFT fabrication by shadow masking and by photolithography. Our proposed a-IGZO TFT DOS model is presented in chapter 3. The DOS model we have developed is derived from a combination of electrical and optical measurements and data from published literature. Oxygen-related states, such as oxygen vacancies or excess oxygen in the a-IGZO microstructure, are often discussed as the source of the subgap states in a-IGZO. Chapter 4 investigates the effect of oxygen incorporation into the a-IGZO thin film in terms of electrical properties and stability. In chapter 5, possible radiative transitions for photoluminescence (PL) in a-IGZO are proposed and discussed based on the spectra of a-IGZO thin films processed under different conditions. The PL is used as a nondestructive tool to probe the TFT channel region for changes to the subgap DOS. The PL spectra of a-IGZO TFTs before and after application of BTS are measured and discussed. Chapter 6 discusses the ac BTS of metal S/D recessed a-IGZO TFTs fabricated by photolithography on glass substrates. Both unipolar (positive or negative) and bipolar pulse waveforms with different pulse periods and duty cycles are investigated. In chapter 7, we fabricate one-transistor-one-capacitor test circuits with a-Si:H or a-IGZO TFTs and evaluate their dynamic characteristics side-by-side in the context of UHD display specifications. Lastly, chapter 8 summarizes the findings of this dissertation and future research directions are recommended.

### **CHAPTER 2**

## Fabrication of a-IGZO Thin-Film Transistors

**Figure 2.1** A generic description of the (a) shadow mask and (b) photolithography fabrication process. A high-level comparison of the two processes are shown in (c).

#### 2.1 Introduction

This dissertation utilizes a-IGZO TFTs fabricated by both shadow masking and photolithography at the Michigan Lurie Nanofabrication Facility and elsewhere. The main difference between shadow masking and photolithography can be seen in Figure 2.1. Fabrication by shadow masking is most suited for rapid prototyping of simple TFT

structures to investigate fundamental properties and optimize process parameters. In chapters 4 and 5, the common gate shadow mask a-IGZO TFT is used to reduce fabrication time and eliminate process variations unrelated to the a-IGZO layer. To investigate a-IGZO TFT dynamic response for real-world applications, TFTs of the back channel etch (BCE) inverted-staggered structure are fabricated by photolithography in chapter 7. For the ac bias-temperature stress studies, source/drain (S/D) recessed coplanar homojunction a-IGZO TFTs are fabricated elsewhere by our collaborators and will be discussed in chapter 6.

Within this chapter, the field-effect mobility ( $\mu_{FE}$ ) is extracted from a linear fit of the TFT transfer ( $I_D$ – $V_{GS}$ ) characteristics to the simplified ideal MOSFET equation

$$I_D = \frac{W}{I} \mu_{FE} C_{GI} (V_{GS} - V_{th}) V_{DS}$$

(2-1)

in the linear region (small drain bias  $V_{\rm DS}$ ) and threshold voltage ( $V_{\rm th}$ ) from extrapolating the fitted line to the x-axis. In Equation (2-1), W and L are the TFT width and length,  $C_{\rm GI}$  is the gate insulator capacitance per unit area, and  $V_{\rm GS}$  is the gate bias. The subthreshold swing (SS) is derived from an average of three values around the maximum transconductance ( $dI_{\rm D}/dV_{\rm GS}$ ) point of semi-log  $I_{\rm D}$ - $V_{\rm GS}$  characteristics.

## 2.2 Common Gate a-IGZO TFTs by Shadow Masking

The common gate inverted-staggered a-IGZO TFT is a simple TFT structure consisting of S/D contacts and a-IGZO islands all defined by shadow masking on a SiO<sub>2</sub>/Si substrate. A top-view image is shown in Figure 2.2. The Si substrate is heavily doped n<sup>++</sup> silicon and serves as a single common gate for multiple TFTs. The individual devices can be physically separated by cleaving the substrate with a diamond cutter. The common gate a-IGZO TFT can be considered a "textbook" device in that the SiO<sub>2</sub> and Si

**Figure 2.2** Top view photograph of the shadow mask a-IGZO TFT.

**Figure 2.3** Fabrication process of the common gate inverted-staggered a-IGZO TFT by shadow mask process.

layers are very well understood and deviations are not expected. Therefore any changes to device properties and stability are directly representative of changes to the fabrication process in the channel and contact layers. It is very suitable for investigating the critical a-IGZO active layer process parameters. Its fabrication process is summarized in Figure 2.3. Depending on the thickness of the  $SiO_2$  used (generally 100 or 200 nm), there is possibility that the gate and S/D contacts may be shorted due to physical damage to the gate oxide during the fabrication process. In the device transfer characteristics ( $I_D$ – $V_{GS}$ ), this may appear as the S/D currents tracking the gate current.

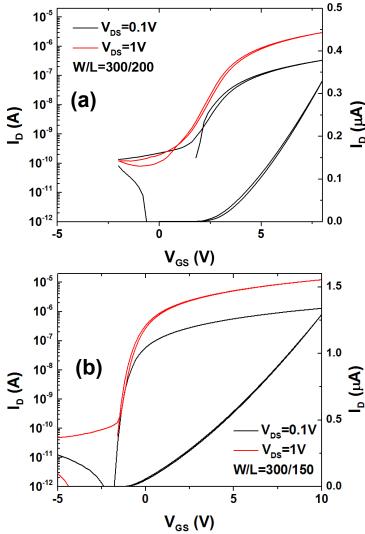

**Figure 2.4** Common gate a-IGZO TFTs with (a) one post-S/D deposition annealing and (b) one pre-S/D deposition annealing.

#### 2.2.1 Impact of Thermal Annealing

Annealing is essential for the fabrication of a-IGZO TFTs with good electrical properties [28], [65]. Without annealing, as-fabricated a-IGZO TFTs have very negative  $V_{th}$  and very high SS. We observed no significant differences between 30 and 60 minutes of annealing. We have also studied the impact of the order of annealing on a-IGZO TFT electrical properties. Within the literature, some reported annealing before S/D deposition [27], [66] while some are done after [67], [68]. In our investigations, we fabricated two