## CHARACTERISTICS AND APPLICATIONS OF NON-VOLATILE RESISTIVE SWITCHING (MEMRISTOR) DEVICE

by

## Shinhyun Choi

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2015

#### **Doctoral Committee:**

Associate Professor Wei D. Lu, Chair Professor L. Jay Guo Professor Cagliyan Kurdak Associate Professor Zhaohui Zhong

## **DEDICATION**

To my wife Hae-Ryung, my family and friends

## **ACKNOWLEDGEMENTS**

I gratefully acknowledge all the support I've been given during my time at the University of Michigan. I would like to extend special thanks to my mentor Dr. Wei Lu. He has guided me through this process with kindness, patience, and understanding. This dissertation would not have been possible without the many thoughtful conversations we have had over the years. I would also like to thank my committee members, Dr. Cagliyan Kurdak, Dr. L. Gay Guo, and Dr. Zhaohui Zhong for their mentorship and critical assessment of my work, and for generously sharing their knowledge and time.

I would like to thank my parents, family, and friends for supporting me through this challenging quest. A special thank you goes to my wife Hae-Ryung Park for providing me with unwavering love, support, and encouragement. This work would not have been possible without you.

I would like to express my gratitude to past and present members of the laboratory.

Thank you to Dr. Siddharth Gaba, Dr. Taeho Moon, Dr. Sungho Kim, Dr. Yuchao Yang, Lin

Chen, Patrick Sheridan, Chao Du, Jiantao Zhou, Ugo Otuonye, Jihang Lee, Wen Ma, Fuxi Cai,

Jonghoon Shin, and Yeonjoo Jeong for friendship, support, assistance and encouragement.

In addition, I would like to extend my thanks to friends and colleagues in the Electrical Engineering and Computer Science who have provided me with assistance, support, and advice through my graduate career.

I am very thankful and fortunate to have received funding to support my graduate work through a variety of sources. These sources include JeongSong Cultural Foundation (2009 Sep. ~ 2011 Apr.) and SamSung Scholarship (2011 Sep. ~ 2015 Apr.) for financial support and advice.

## **Table of Contents**

| DEDICATION                                                                                   | ii   |

|----------------------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                             | iii  |

| List of Figures                                                                              | viii |

| ABSTRACT                                                                                     | xv   |

| Chapter 1.Introduction                                                                       | 1    |

| 1.1 Non-Volatile Memory                                                                      |      |

| 1.2 Flash Memory Market                                                                      |      |

| 1.3 Flash Memory and its scaling issue                                                       |      |

| 1.4 Emerging Non-Volatile memories                                                           |      |

| 1.4.1 Phase-change RAM                                                                       |      |

| 1.4.2 Ferroelectric RAM                                                                      |      |

| 1.4.3 Magnetic RAM                                                                           | 8    |

| 1.5 RRAM                                                                                     |      |

| 1.5.1 Bipolar Switching vs. Unipolar Switching                                               |      |

| 1.5.2 Cation Migration vs. Anion Migration                                                   |      |

| 1.5.3 Memristor                                                                              |      |

| 1.5.4 Research on RRAM                                                                       |      |

| 1.6 Organization of the Thesis                                                               |      |

| 1.7 References                                                                               | 18   |

| Chapter 2. Comprehensive Physical Model of Dynamic Resistive Switching in an Oxid            | e    |

| Based RRAM                                                                                   | 22   |

| 2.1 Introduction                                                                             | 22   |

| 2.2 Resistive switching behavior of TaO <sub>x</sub> /Ta <sub>2</sub> O <sub>5</sub> bilayer | 23   |

| 2.3 Details of the model                                                                     | 25   |

| 2.4 Conclusion                                                                               | 30   |

| 2.5 References                                                                               | 32   |

| Chapter 3.Random Telegraph Noise and Resistance Switching Analysis of Oxide Base             | γd   |

| RRAM                                                                                         |      |

| 3.1 Introduction                                                                             |      |

| 3.2 Device Fabrication and Measurement Setup                                                 |      |

| 3.3 Statistical and Temperature Dependent Studies of RTN                                     |      |

| 3.4 Electron Transport Experiment in LRS and HRS.                                            |      |

| 3.5 Analysis based on noise and transport data                                               |      |

| 3.6 Conclusion.                                                                              |      |

| 3.7 References                                                                               |      |

|                                                                                              |      |

| Chapter 4.Retention Failure Experiments and Modeling of Metal-Oxide B                   | ased RRAM 51  |

|-----------------------------------------------------------------------------------------|---------------|

| 4.1 Introduction                                                                        | 51            |

| 4.2 Device Fabrication and Measurement Setup                                            | 51            |

| 4.3 Experimental Data                                                                   | 53            |

| 4.4 Multiphysics Simulation                                                             | 57            |

| 4.5 Monotonic Current Increase Behavior                                                 | 59            |

| 4.6 Multi-filament Effects                                                              | 60            |

| 4.7 Conclusion                                                                          | 61            |

| 4.8 References                                                                          | 62            |

| <b>Chapter 5. Tuning Resistive Switching Characteristics of Tantalum-Oxide</b>          | RRAM Devices  |

| through Si Doping                                                                       |               |

| 5.1 Introduction                                                                        |               |

| 5.2 Device Fabrication                                                                  |               |

| 5.3 Resistive Switching Behavior                                                        | 66            |

| 5.4 Switching Dynamics Analysis                                                         |               |

| 5.5 Evaluation of the Effective Hopping Distance                                        |               |

| 5.6 Details of the model                                                                |               |

| 5.7 Ab Initio Study                                                                     |               |

| 5.8 Analog Switching Behavior                                                           |               |

| 5.9 Conclusion                                                                          |               |

| 5.10 References                                                                         | 80            |

| Chanton ( Data Chatowing using DD AM Naturally                                          | 0.4           |

| Chapter 6.Data Clustering using RRAM Network                                            |               |

| 6.2 Device Fabrication and Measurement Setup                                            |               |

| 6.3 Analog RRAM Behavior                                                                |               |

| 6.4 Learning in Crossbar Arrays                                                         |               |

| 6.5 Details of the Training Process                                                     |               |

| 6.6 Effect of Applied Voltage Amplitude and the Learning Rate                           |               |

|                                                                                         |               |

| 6.7 The Effect of Device Non-Uniformity 6.8 Analysis of Performance of the RRAM Network |               |

| 6.9 Conclusion                                                                          |               |

|                                                                                         |               |

| 6.10 Appendix                                                                           |               |

| 6.10.1 Appendix A- Device Modeling                                                      |               |

| 6.10.3 Appendix C- Details of the measured data and modelling                           |               |

| 6.11 References                                                                         |               |

| Chapter 7.Experimental Demonstration of Unsupervised Learning Using 1                   | RRAM Networks |

|                                                                                         | 110           |

| 7.1 Introduction                                                                        |               |

| 7.2 Device Fabrication and Analog switching behavior                                    | 110           |

| 7.3 Peripheral Circuitry                                                                |               |

| 7.4 Learning in the RRAM array                                                          | 113           |

| 7.5 Data Clustering before and after Applying Unsupervised Learning Rule | 116 |

|--------------------------------------------------------------------------|-----|

| 7.6 Conclusion                                                           | 120 |

| 7.7 References                                                           | 121 |

| Chapter 8.Summary and Future Work                                        | 122 |

| 8.1 Discussion                                                           |     |

| 8.2 Future work                                                          | 124 |

| 8.2.1 RRAM Crossbar Array for Preprocessing of Neural Signal             | 124 |

| 8.2.2 Device Optimization – Analog Switching                             |     |

| 8.3 References                                                           | 126 |

# **List of Figures**

| Figure 1.1. Applications of non-volatile memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. The demand of non-volatile memories from 2012 to 2017.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 1.3. Schematic of floating gate flash memory. R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 1.4. (a) Cross-section schematic of the conventional phase-change memory cell. (b) Temperature- applied electrical pulses widths for SET, RESET and Read pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

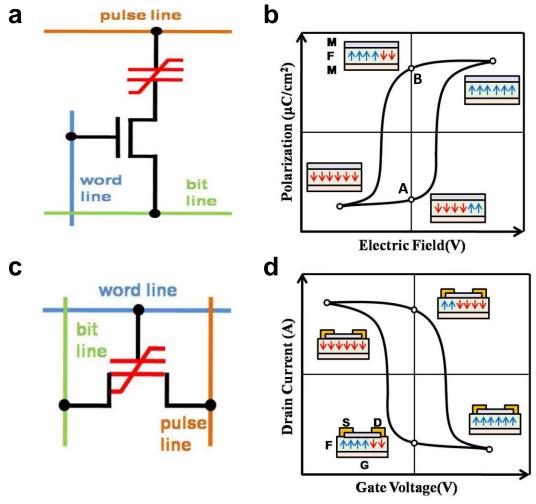

| Figure 1.5. (a) A schematic circuit diagram for a typical 1T1C FeRAM cell. (b) Polarization-voltage hysteresis of a MFM capacitor. (c) A schematic circuit diagram for a 1T FeFET device. (d) Source-drain current vs. gate voltage hysteresis of a FEFET device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

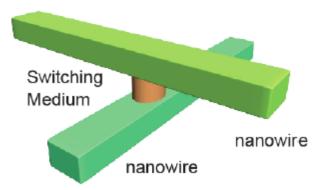

| Figure 1.6. a two-terminal switch can be formed with a switching medium sandwiched between a pair of electodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

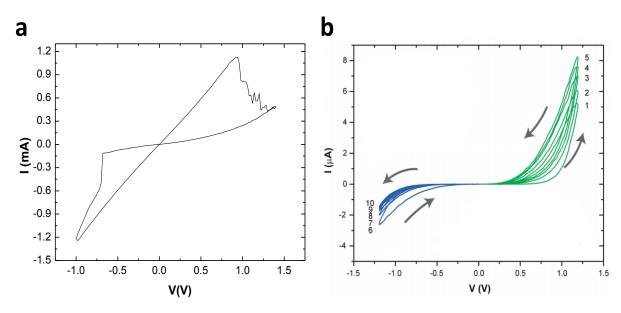

| Figure 1.7. DC I-V characteristics. (a) Digital-like type device. Obtained from stack of Pd/ TaO <sub>x</sub> /Ta <sub>2</sub> O <sub>5</sub> /Pd. (b) Analog-like type device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

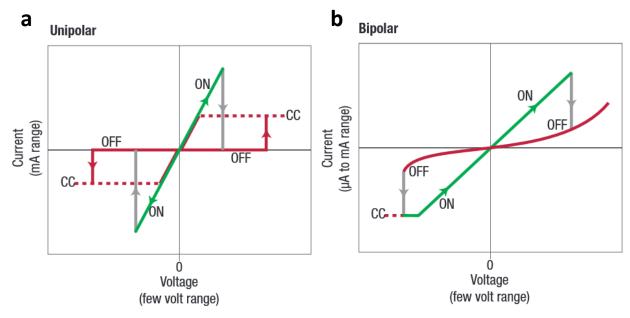

| Figure 1.8. Classification of the switching characteristics in a voltage sweeping experiment. (a) Unipolar switching. (b) Bipolar switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

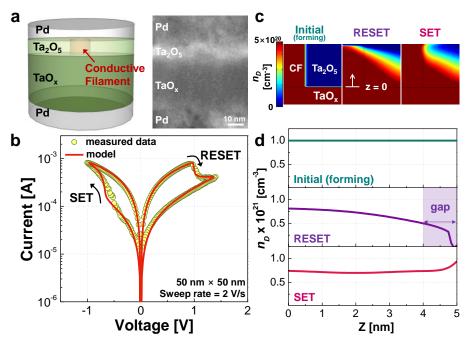

| Figure 2.1. Modeling a tantalum oxide RRAM during set/reset. (a) Schematic and cross-sectional TEM images of the Pd/Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> /Pd bilayer RRAM device. (b) Measured and calculated DC <i>I-V</i> characteristics of the Pd/Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> /Pd device. The measured device size is 50 nm × 50 nm, and the voltage sweep speed is 2 V/s. (c) Calculated 2-D maps of $n_D$ as well as (d) 1-D profiles of $n_D$ along the center of the CF in the initial state, after reset, and after the set process. The depleted gap is determined as the position where $n_D = 5 \times 10^{20}$ cm <sup>-3</sup> . The $z = 0$ position is the Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> interface 24 |

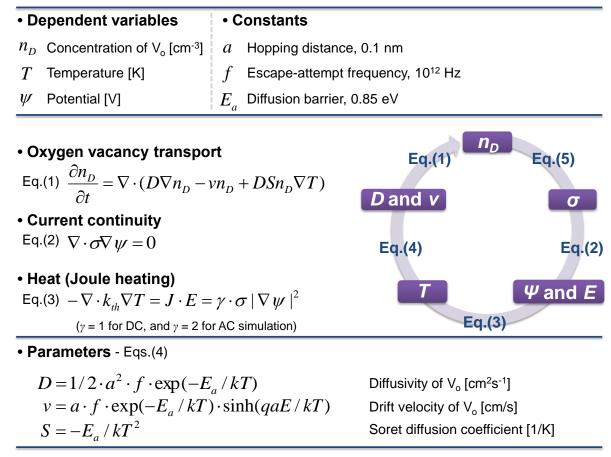

| Figure 2.2. Equations and parameters in the proposed model. Three PDEs are self-consistently solved with a numerical solver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ex                             | 3. Parameters from measurements and assumptions. (a) Electrical conductivity pre-<br>xponential factor $\sigma_0$ , (b) assumed activation energy for conduction $E_{AC}$ , and (c)<br>ssumed thermal conductivity $k_{th}$ as a function of local $V_0$ density $n_D$                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

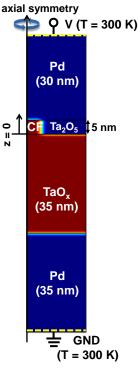

| th<br>w                        | 4. Simulated geometry used in the calculation. The axisymmetric geometry reduces ne problem from 3-D to 2-D. A uniform doping concentration of $n_D = 1 \times 10^{21}$ cm <sup>-3</sup> was assumed within the CF and the TaO <sub>x</sub> layer as the initial state right after lectroforming.                                                                                                                                                                                                                                                                                                                                           |

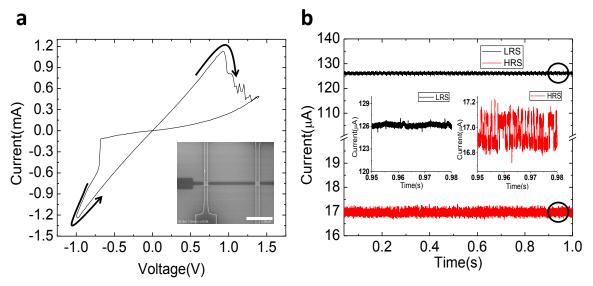

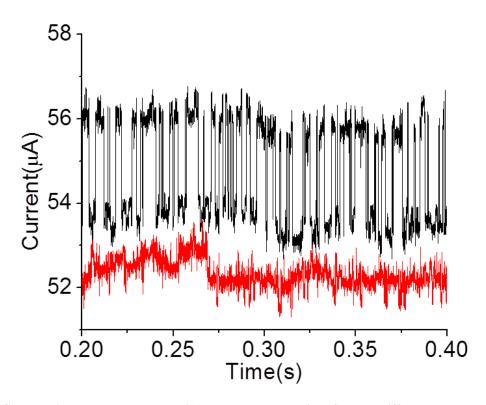

| Ir<br>0.                       | 1. (a) I-V characteristics of a typical device showing the bipolar switching effects.  nset: SEM image of the device. Scale bar is 5μm. (b) Current-time plots measured at  1. V for LRS and HRS, respectively. Insets: zoomed-in plots of the circled areas for RS (left) and HRS (right), showing pronounced RTN in HRS                                                                                                                                                                                                                                                                                                                   |

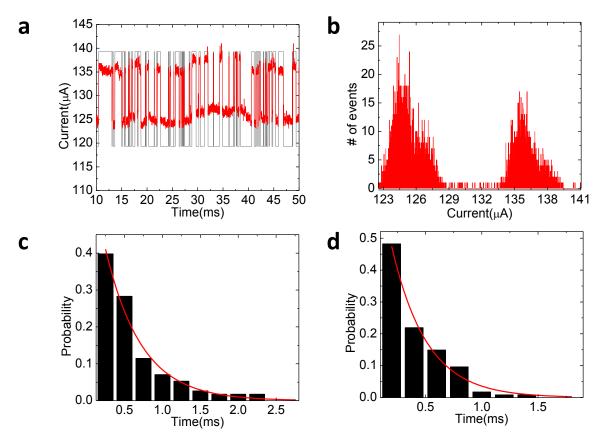

| re<br>oo<br>ca                 | 2. (a) Time-domain analysis of the RTN behavior showing raw data (red) and eproduced data (grey) based on the capture program. (b) Histograms of current vs. ccurrence showing a bimodal distribution corresponding to the two current levels ausing RTN. (c), (d) Histograms of the dwell times in the upper (c) and lower (d) urrent levels. The red lines are Poisson fits using as the only fitting parameter                                                                                                                                                                                                                           |

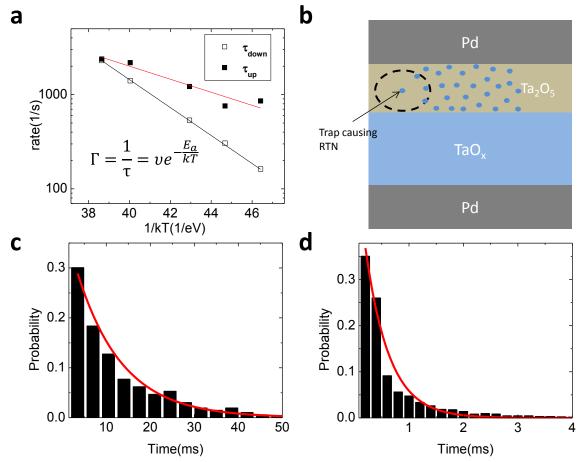

| lo<br>Se<br>cl<br>th           | 3. (a) Temperature dependence of the characteristic dwell times in the upper and ower current levels. The lines are fits following the Arrhenius equation. (b) chematic of the cause for RTN. The trapping and detrapping of a trap site near the hannel leads to jumps in discrete current levels. The dashed circle represents the area nat may be electrostatically depleted by the trapped electron. (c),(d) Histograms and ts of the dwell times at the upper current levels at 250 K and 300 K, respectively 39                                                                                                                       |

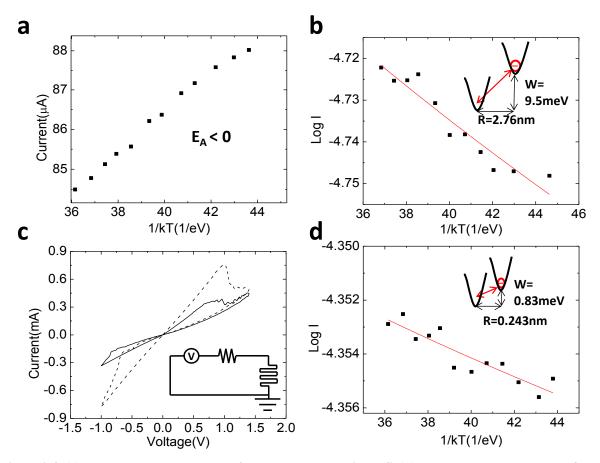

| de<br>Se<br>H<br>is<br>Te<br>H | 4. (a) Temperature dependence of electron transport in LRS. (b) Temperature ependence of electron transport in HRS. Inset: Schematic of the hopping process. (c) olid line: I-V characteristics without the series resistor, showing switching between IRS and LRS; dashed line: I-V characteristics with a 1 k $\Omega$ series resistor. The device a programmed to an intermediate state instead. Inset: The circuit schematic. (d) remperature dependence of electron transport in the intermediate state. Inset: It lopping with more closely spaced trap sites and lower hopping energy in the intermediate state compared to the HRS. |

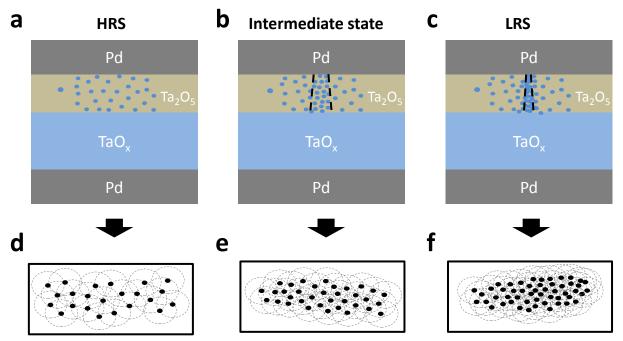

| in<br>li:<br>th<br>w           | 5. (a) Schematics showing the changes in V <sub>O</sub> distribution for the HRS, the intermediate state and the LRS in the Ta <sub>2</sub> O <sub>5</sub> switching layer, respectively. The dashed nes in (b) and (c) highlight the filament region with higher V <sub>O</sub> concentration than he rest of the film. (d-f) Corresponding changes in the overlap of electron vavefunctions lead to different resistance values for the HRS, intermediate state and RS. dots: localized states, Gray dashed circle: the localization radii                                                                                                |

| Figure 3.6. Current-time plots measured at 0.1 V on the same device after two different set and reset process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

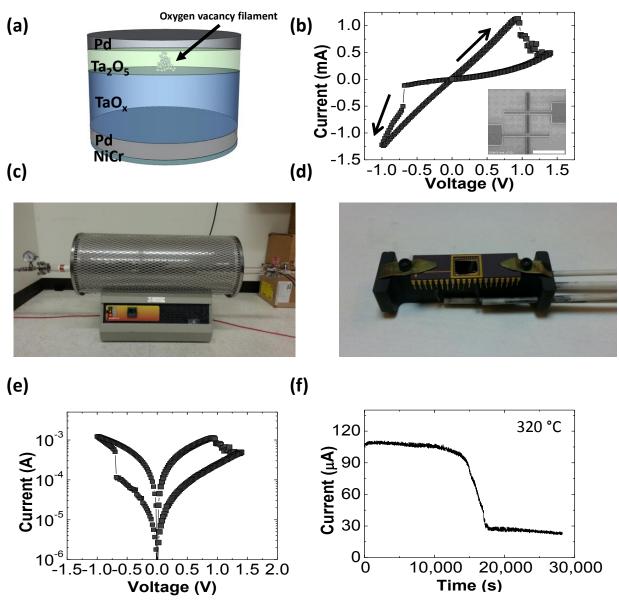

| Figure 4.1. (a) Schematic of the Pd/Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> /Pd bilayer RRAM device. (b) DC I-V characteristics of the device showing the bipolar switching behavior. Inset: SEM image of the device. Scale bar is 20 μm. (c) A custom-built high temperature measurement setup using a tube furnace. The left part of the tube is connected to a vacuum pump and the right part of the tube is connected to electrical feedthroughs. (d)The wirebonded devices on a chip carrier in the furnace connected to electrical feedthroughs. (e) I-V characteristics of the device in log scale. (f) Retention measurement results at 320 °C. A read pulse (0.1 V/10 ms) was applied every 6s during the test.     |

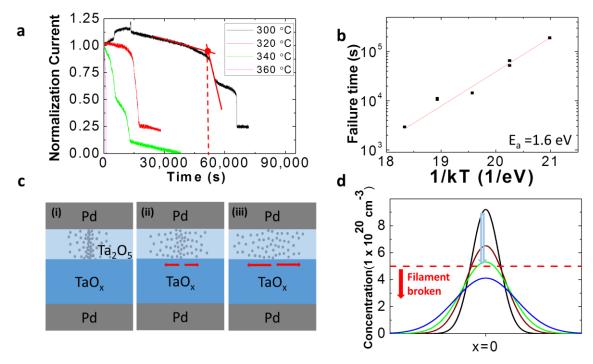

| Figure 4.2. (a) Temperature dependent retention measurements at 300 °C, 320 °C, 340 °C and 360 °C. (b) Temperature dependence of the characteristic retention failure time (squares) and fitting (line) following the Arrhenius equation. (c) Schematics showing the changes in $V_0$ distribution from the LRS (i), after VO out diffusion (ii), and eventual rupture of the filament (iii). (d) Oxygen vacancy concentration profile predicted from the simple analytical model as a function of time. Dashed red line indicates the critical oxygen vacancies density (defined as $5 \times 10^{20}/\text{cm}^3$ )                                                                                                                 |

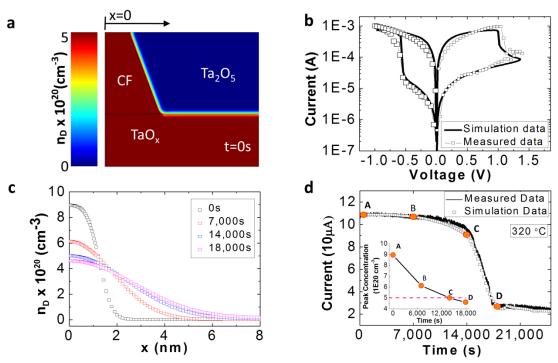

| Figure 4.3. (a) 2-D map of oxygen vacancy concentration obtained through numerical simulations, for in the initial state (LRS). The x=0 position is the center of the conductive filament. (b) Measured and calculated DC I- V characteristics of the device at 320 °C showing the model can capture the essential dynamic $V_0$ migration processes. (c) Oxygen vacancy concentration profile calculated from the numerical simulation as a function of time. (d) Measured and simulation results showing the device retention behavior at 320 °C inset: Peak $V_0$ concentration at different time instants (A- D). Dashed red line indicates the critical oxygen vacancies density (defined as $5 \times 10^{20} / \text{cm}^3$ ). |

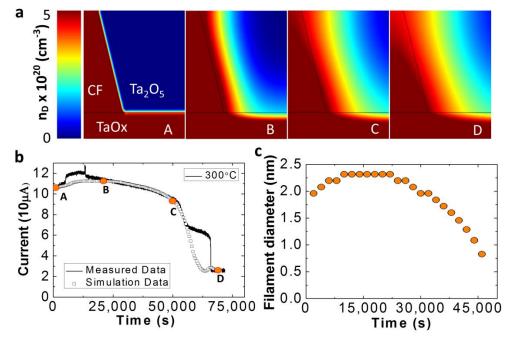

| Figure 4.4. (a) 2-D map of oxygen vacancy concentration showing the evolution of the filament at different time scales (corresponding to points A-D in Figure 4b) (b) Measured and calculated device conductance as a function of time at 300 °C. (c) Effective filament diameter as a function of time. The filament was defined as the region with oxygen vacancy concentration higher than 5× 10 <sup>20</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                    |

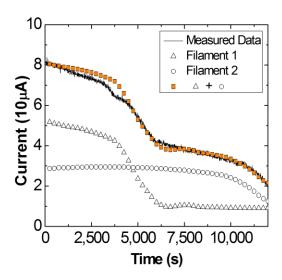

| Figure 4.5. Measured (black line) and calculated (squares) conductance as a function of time at 340 °C, showing the possible existence of multiple filaments. Evolutions of the two filaments (triangles and circles) were obtained through simulation and the overall conductance (squares) is the sum of the two filaments.                                                                                                                                                                                                                                                                                                                                                                                                         |

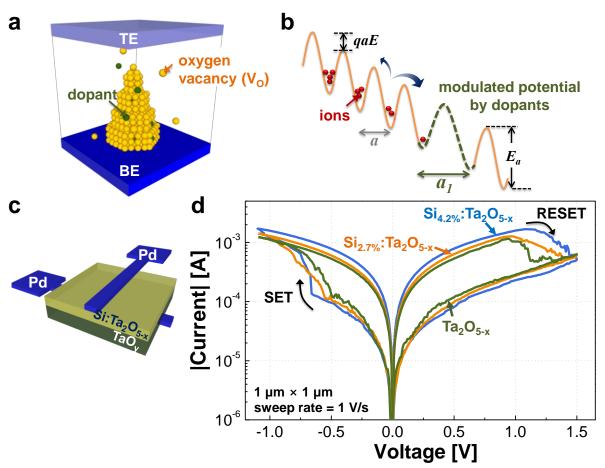

| Figure 5.1. (a) Conceptual schematic of the oxide RRAM during RS. The agglomerated V <sub>OS</sub> enhance the local electrical conductivity and form the CF. (b) Schematic of the potential energy landscape for ion hopping under electric field <i>E</i> . (c) Schematic plot of the Pd/Si:Ta <sub>2</sub> O <sub>5</sub> /TaO <sub>x</sub> /Pd bilayer RRAM device. (d) DC <i>I–V</i> characteristics of undoped Ta <sub>2</sub> O <sub>5</sub> , Si <sub>2.7%</sub> :Ta <sub>2</sub> O <sub>5</sub> , and Si <sub>4.2%</sub> :Ta <sub>2</sub> O <sub>5</sub> devices. The measured device size is 1 μm × 1 μm, and the voltage sweep speed is 1 V/s                    | 65         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

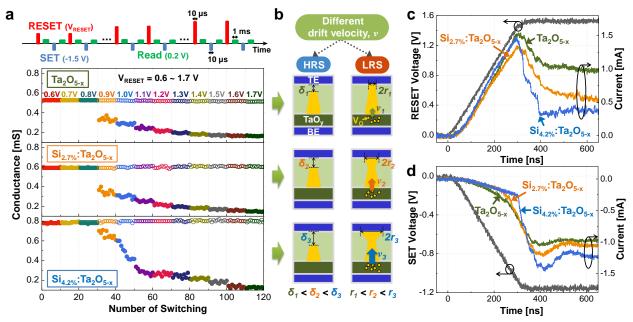

| Figure 5.2. (a) Switching dynamics characterized by pulse measurements with increasing reset pulse amplitudes. The set-pulse amplitude is fixed at -1.5 V. Before the pulse measurements, the devices are set to LRS with a DC voltage sweep. (b) Schematic of the HRS and LRS for different $V_0$ drift velocities. $\delta$ and $r$ increase as $v$ is increased through Si doping. (c) Time-dependent switching transient during the reset and (d) set processes.                                                                                                                                                                                                        |            |

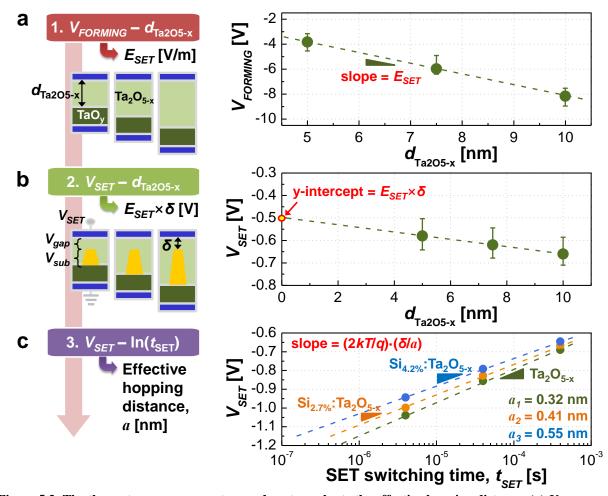

| Figure 5.3. The three-step measurement procedure to evaluate the effective hopping distance. (a) $V_{FORMING}$ — $d_{oxide}$ plot to evaluate $E_{SET}$ ; the slope represents $E_{SET}$ . (b) $V_{SET}$ — $d_{oxide}$ plot to estimate $\delta$ ; the y-intercept represents $E_{SET}$ . $\delta$ . (c) $V_{SET}$ — $\ln(t_{SET})$ plot to extract $a$ ; the slope represents $(2kT/q) \cdot (\delta/a)$ .                                                                                                                                                                                                                                                                 | 70         |

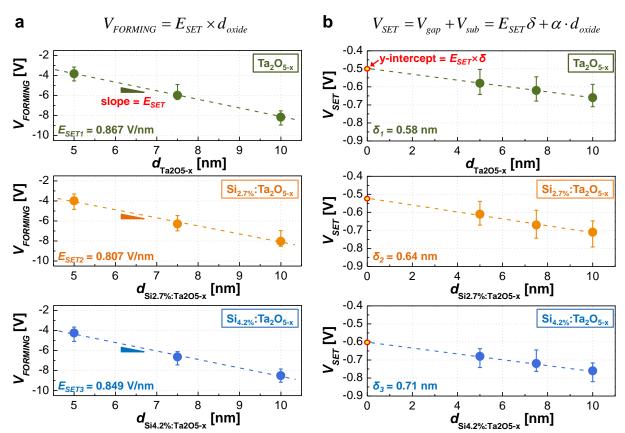

| Figure 5.4. Measurement results of (a) $V_{FORMING}$ — $d_{oxide}$ to extract $E_{SET}$ and (b) $V_{SET}$ — $d_{oxide}$ to extract $\delta$ in the three different samples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72         |

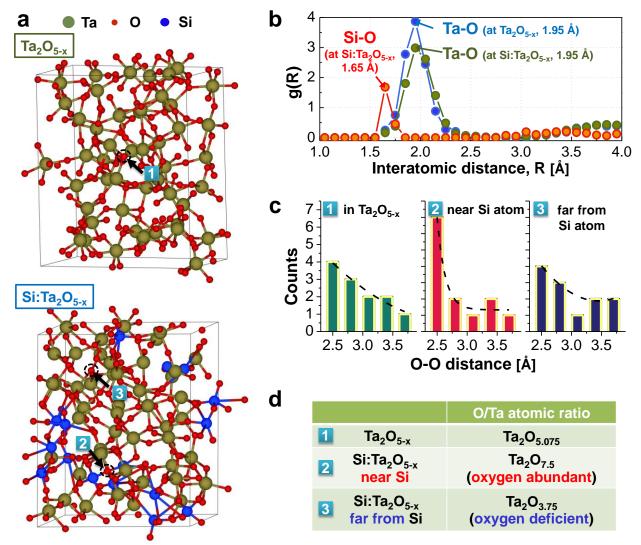

| Figure 5.5. (a) Snapshots of the amorphous Ta <sub>2</sub> O <sub>5</sub> and Si-doped Ta <sub>2</sub> O <sub>5</sub> structures obtained in the <i>ab initio</i> simulation. The Ta, O, and Si atoms are colored in dark green, red, and blue, respectively. (b) Pair-correlation functions of the amorphous Ta <sub>2</sub> O <sub>5</sub> and Si-doped Ta <sub>2</sub> O <sub>5</sub> calculated at room temperature. (c) Histograms of the O–O distance from a selected oxygen atom to a neighboring oxygen atom. Three oxygen atoms are selected randomly, as shown in panel a. (d) O and Ta atomic ratio near the selected oxygen atoms.                              | <b>7</b> 4 |

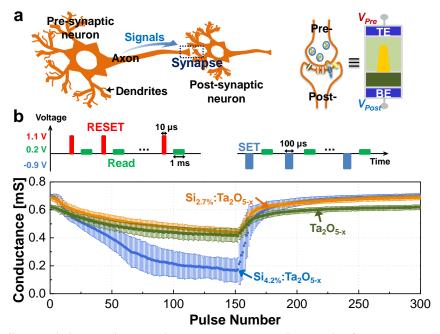

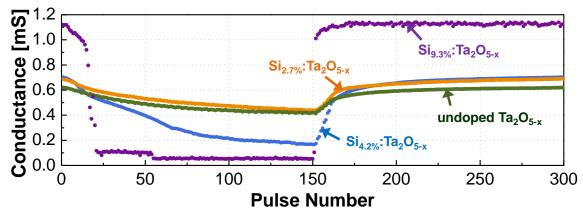

| Figure 5.6. (a) Schematic illustration showing a synapse connecting a pair of neurons, where the synaptic functions can be emulated by RRAM devices. (b) Analog switching behavior obtained by pulse trains consisting of 150 reset pulses (1.1 V, 10 μs) followed by 150 set pulses (-0.9 V, 100 μs) with small, nonperturbative read voltage pulses (0.2 V, 1 ms) applied in the intervals. The conductance changes are measured during the read pulse and plotted as a function of applied pulse number. The error bars indicate the standard deviation from the measured data set, which are collected from 50 such test cycles in five different devices in each case. | 7 <i>6</i> |

| Figure 5.7. Analog switching behaviors obtained by pulse trains in four different cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77         |

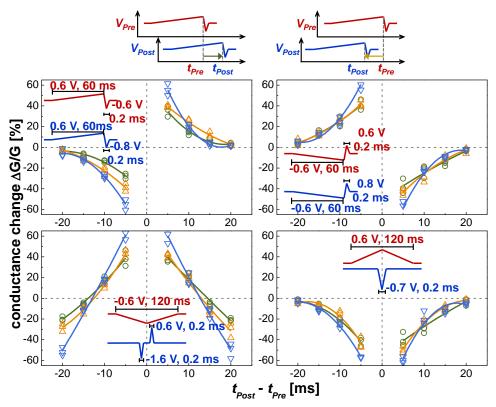

| Figure 5.8. Implementing four different types of STDP using tantalum oxide RRAM. The prespike voltage ( $V_{Pre}$ ) and post-spike voltage ( $V_{Post}$ ) are applied to the TE and BE of the RRAM, respectively. The net programming voltage ( $V_{Pre} - V_{Post}$ ) applied across the device depends on the positive or negative moments $t_{Post} - t_{Pre}$ . The dots indicate the experimental data, and the lines are guides to the eye. The insets show the (red) preand (blue) postsynaptic spike schemes.                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

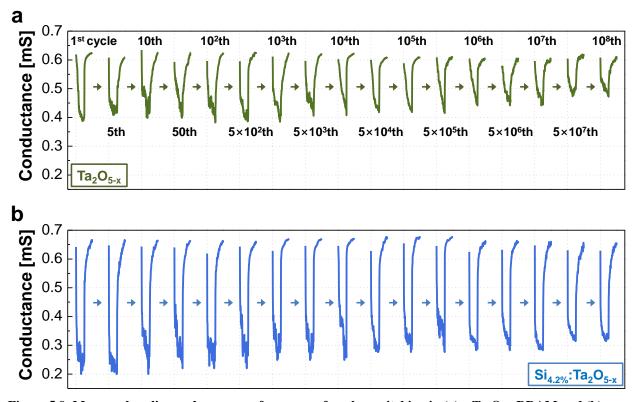

| Figure 5.9. Measured cycling endurance performance of analog switching in (a) a $Ta_2O_{5-x}$ RRAM and (b) a $Si_{4.2\%}$ : $Ta_2O_{5-x}$ RRAM. Each test cycle consists of a pulse train including 50 reset (1.25 V, 10 $\mu$ s) pulses followed by 50 set (-1.0 V, 10 $\mu$ s) pulses 79                                                                                                                                                                                                                                                                                                                                     |

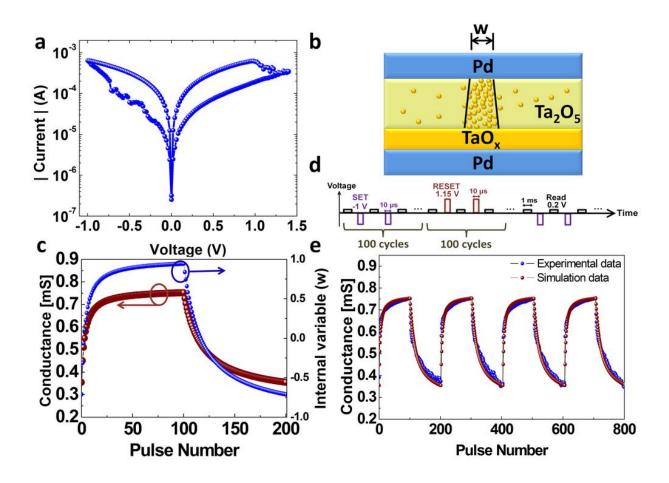

| Figure 6.1. Modelling the switching performance of a RRAM. (a) DC I-V characteristics of a typical RRAM device showing the bipolar switching. (b) Schematic image of a RRAM device having oxygen vacancy filament. (c) Calculated conductance and internal state variable with 100 pulses of potentiation (-1 V, 10μs) and depression (1.15 V, 10μs), consecutively. (d) The sequences of the applied pulses showing 4 sets of 100 pulses of potentiation and 100 pulses of depression. (e) The measured and calculated conductance changes measured by read (0.2V) pulse with the set and reset processes shown in Fig. 1(d). |

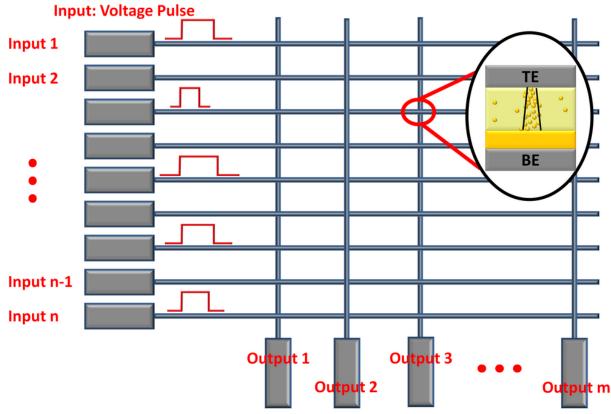

| Figure 6.2. The network schematic. The column electrodes represent inputs and the row columns represent outputs. The RRAM devices are located at the intersections where the column electrodes and row electrodes connected                                                                                                                                                                                                                                                                                                                                                                                                    |

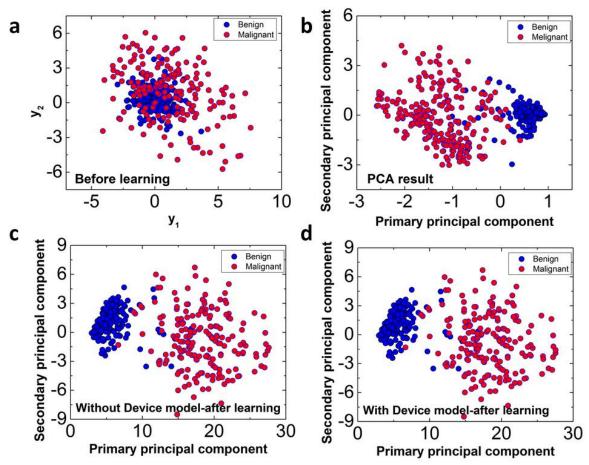

| Figure 6.3. The result of principal component analysis. (a) The result of read process through RRAM devices showing y <sub>1</sub> at horizontal axis and y <sub>2</sub> at vertical axis before learning process. (b) Principal component analysis using traditional covariance matrix of the data. (c) Principal component analysis using Sanger's rule without the RRAM model. (d) Principal component analysis using Sanger's rule with the RRAM model                                                                                                                                                                     |

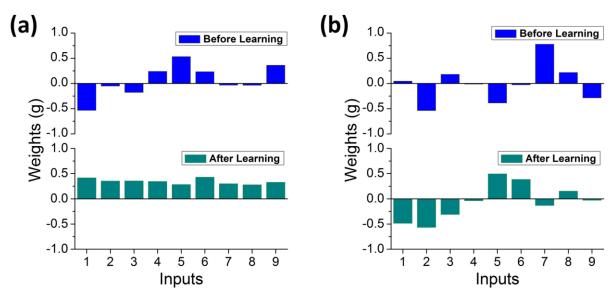

| Figure 6.4. Weights distribution changes for (a) the primary principal component, (b) the second principal component before and after learning process                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

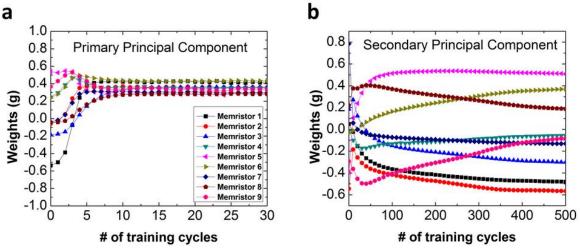

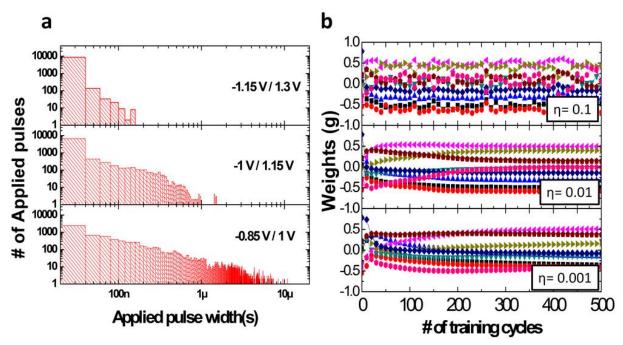

| Figure 6.5. Weights changes with individual learning cycles for (a) the primary principal component, (b) the secondary principal component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6.6. The effects of potentiation/depression voltage amplitudes and learning rate changes. (a) The histogram of applied pulse widths as a function of potentiation/depression voltage amplitude. (b) The weight changes as a function of learning rate.                                                                                                                                                                                                                                                                                                                                                                  |

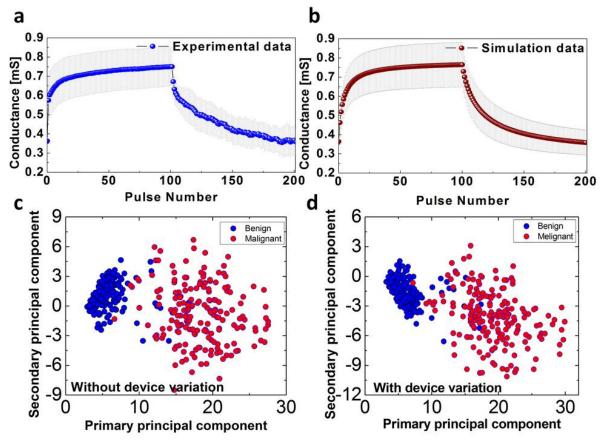

| a<br>c<br>t      | 7. The effect of non-uniformity issue of the devices. (a) The measured data for the malog switching. The blue line and error bar represent the average and standard deviation, respectively. (b) Calculated analog behaviors adding the non-uniformity of the devices. (c) The result of the principal component analysis without device non-uniformity. (d) The result of the principal component analysis with device uniformity. 98                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

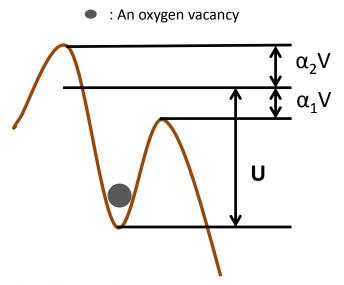

| Figure 6.        | 8. Energy barrier of ion hopping process                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

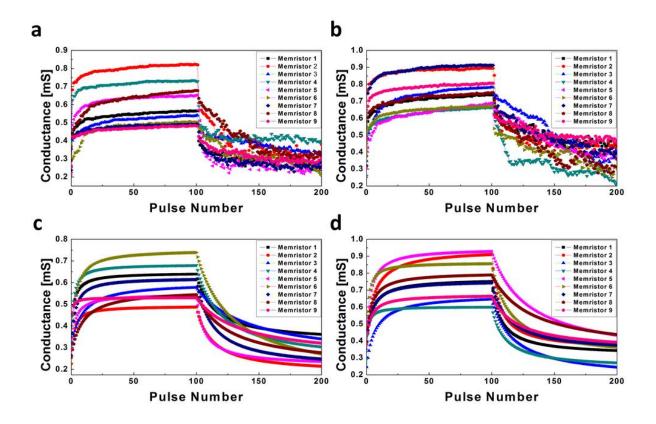

| r<br>r<br>r<br>s | 9. The details of conductance change measured at 0.2 V with 100 pulses of potentiation (-1 V) and 100 pulses of depression (1.15 V), consecutively for (a) measured conductance for 9 RRAM devices of the primary principal component (b) measured conductance for 9 RRAM devices of the second principal component (c) simulated conductance for 9 RRAM devices of the primary principal component (d) calculated conductance for 9 RRAM devices for the secondary principal component. 105 |

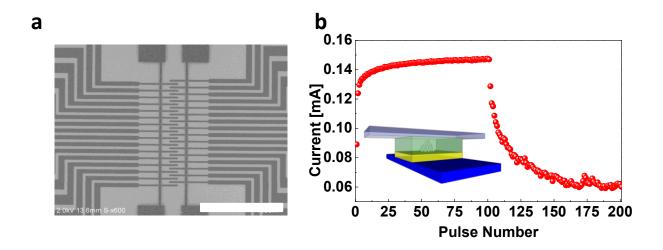

| f<br>c<br>F<br>s | 1 Device fabrication and analog switching behavior. (a) SEM images of the fabricated two sets of 16 by 1 RRAM devices. Scale bar: 100 μm. (b) DC I-V characteristics of a typical RRAM device showing the bipolar switching with 100 bulses of potentiation (-1 V, 10μs) and depression (1.15 V, 10μs), consecutively. Inset: schematic image of a RRAM device having oxygen vacancy filament. This is not to scale.                                                                         |

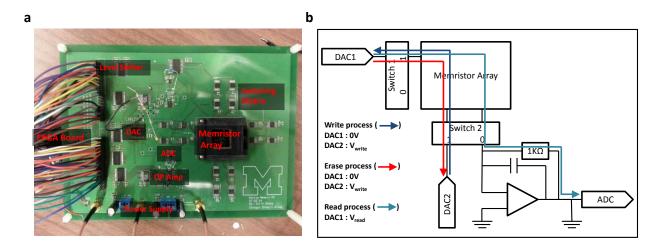

|                  | 2 Peripheral circuitry (a) the photo image of the board with label parts. (b) schematic of the procedure of the board operation                                                                                                                                                                                                                                                                                                                                                              |

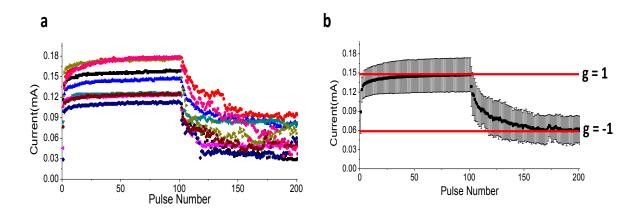

| S<br>C<br>V      | 3 (a) Experimental measurements collected by the board for 9 RRAM devices in the same column (corresponding to the second principle component), showing the analog conductance change and device-device variations. The conductance was measured with 0.2 V, 1 ms pulses, and the devices were subject to 100 pulses of potentiation (-1 V, 10 µs) and 100 pulses of depression (1.15 V, 10 µs). (b) The solid line and the error pars represent the average and standard deviation.         |

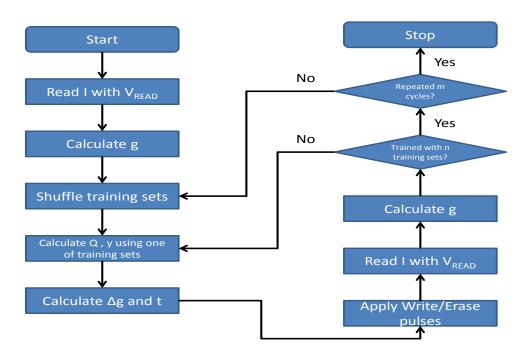

| Figure 7.        | 4 Flowchart showing the overall operation procedure                                                                                                                                                                                                                                                                                                                                                                                                                                          |

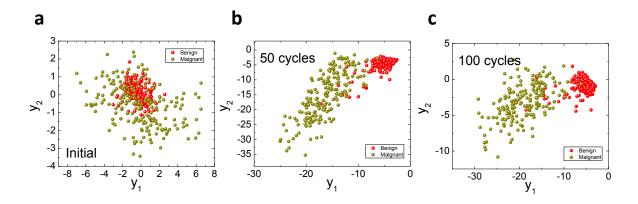

| I                | 5 Results of principal component analysis. The data are plotted on y <sub>1</sub> and y <sub>2</sub> axis. (a) initial results of an untrained RRAM network. (b) Results of a partially trained RRAM network. (c) Results of a fully trained RRAM network                                                                                                                                                                                                                                    |

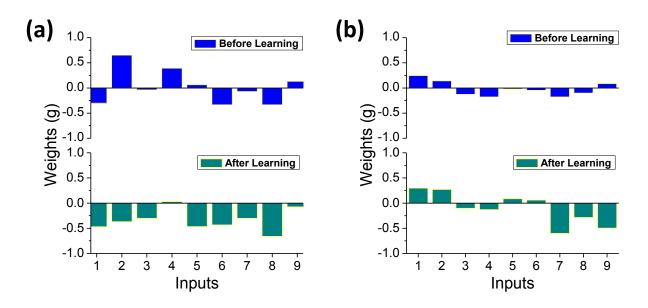

| ŗ                | 6 Weights constituting (a) the primary principal component and (b) the secondary principal component before (upper graph) and after (lower graph) the learning process.                                                                                                                                                                                                                                                                                                                      |

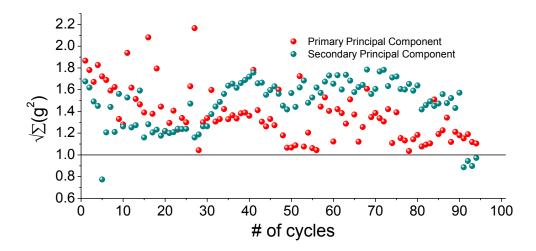

| Figure 7.7 Evolution of the Euclidean norm of weights during learning. Red dots represents the norm value of the weights for the primary principal component and dark cyan dots shows the norm value of the weights for the secondary principal component118 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

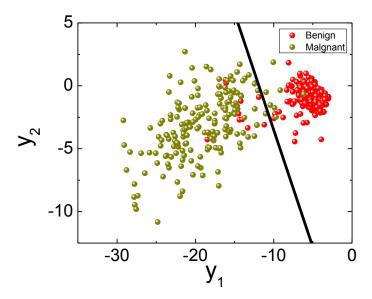

| Figure 7.8 Classification based on linear decision boundary (black line) on the clustered data. 119                                                                                                                                                          |

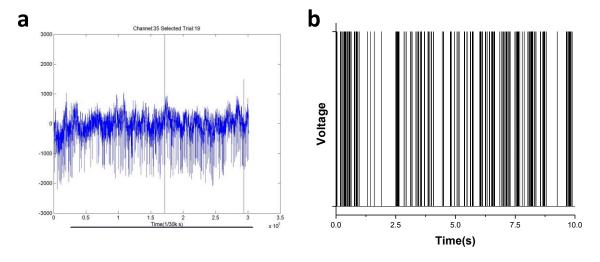

| Figure 8.1. (a) Measured neural signals in motor cortex from a Monkey. Data obtained from Cortical Neural Prosthetics Lab from Biomedical Engineering in University of Michigan. (b) Extracted spikes with constant voltage from Fig. 1(a)                   |

### **ABSTRACT**

Non-volatile memory technology scaling has been driven by the ever increasing needs of high-capacity and low-cost data storage. Scaling the conventional floating gate device structure, however, has faced with several technical challenges due to constraints of electrostatics and reliability. Alternative memory approaches based on non-transistor structures has been extensively studied. Among the new approaches, resistive switching devices (RRAM) have attracted tremendous attention due to their high endurance, sub-nanosecond switching, long retention, scalability, low power consumption, high ON/OFF ratio and CMOS compatibility.

In this thesis, we present a systematic study on the fundamental understanding and potential applications of RRAMs. Firstly, we introduce a quantitative and accurate model of the dynamic resistive switching processes, by solving the coupled equations for oxygen vacancy transport, current continuity and Joule heating. Secondly, we show systematic investigations on the resistance switching mechanism through detailed noise and transport analysis, and develop a unified model to explain the conduction path and account for the resistance switching effects. Thirdly, we perform detailed retention studies of oxide-based RRAMs at elevated temperatures and develop an oxygen diffusion reliability model of RRAM devices. The activation energy for oxygen vacancy diffusion is directly calculated from the measurement. Analytical modeling and detailed numerical multi-physics simulation is discussed. Fourthly, we report that doping tantalum oxide based RRAM with silicon atoms leads to larger dynamic ranges with improved accessibility to the intermediate states which is suited for neuromorphic computing applications.

Lastly, we investigate the application of RRAMs in neuromorphic computing by showing data clustering based on unsupervised learning. Through both simulation and experimental studies, we demonstrate that a crossbar array of RRAM devices can perform data clustering through unsupervised learning and enable effective data classification in a real-world problem.

These studies have not only helped the development and optimization of RRAM devices but also highlighted their application potential beyond simple memory. We believe continued development of this emerging device structure may lead to future high-performance and energy efficient memory and logic hardware systems.

## Chapter 1.

## Introduction

### 1.1 Non-Volatile Memory

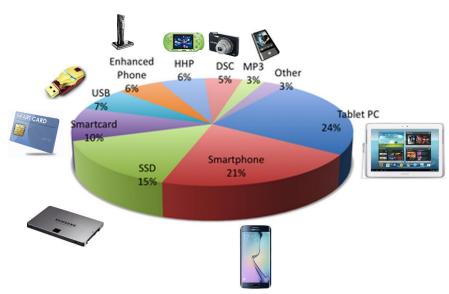

Figure 1.1. Applications of non-volatile memories. Figure adapted and modified from [1].

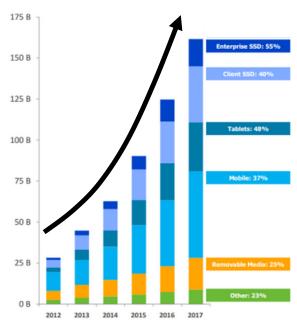

Non-volatile memories are widely used in many applications such as tablet PCs, smart phones, and solid state drives as shown in figure 1.1. The market of non-volatile memory is rapidly growing and has become a main driver for the semiconductor industry. For example, 38% annual growth is expected from 2013 to 2017, as shown in figure 1.2.

Figure 1.2. The demand of non-volatile memories from 2012 to 2017. Reproduced from [2].

## 1.2 Flash Memory Market

Flash memory is currently the unquestionable leader of the non-volatile market. The demand of flash memory market has been rapidly increasing because of the advantages such as relatively low cost, small size, and fast speed (compared to hard drives). Flash memory has been a popular choice for the mobile platforms from digital camera to tablets and smart phones. The exponential growth of flash memory is expected to continue due to data explosion from personal communication to large commercial data.

### 1.3 Flash Memory and its scaling issue

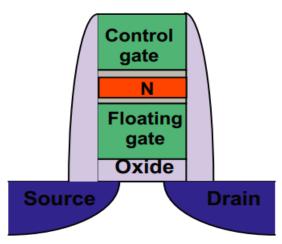

A non-volatile flash memory cell based on a floating gate is shown in Fig 1.3. It is based on a normal metal oxide semiconductor (MOS) structure with a floating gate and tunneling oxide. The control gate and the floating gate are made of polysilicon and the tunneling oxide thickness is  $\sim 100$  Å. The inter poly dielectric layer between the two gates is made of oxide/nitride/oxide (ONO) structure and the thickness is  $120 \sim 140$  Å. To program the device, hot electrons in the channel with high kinetic energy can overcome the tunneling oxide/silicon barrier ( $V_{GS} = \sim 10$  V,

Figure 1.3. Schematic of floating gate flash memory. Reproduced from [3].

$V_{DS} = \sim 4 \text{ V}$ ). The electrons captured in the floating gate modulate the threshold voltage ( $V_t$ ) of the cell. To erase the device, Fowler-Nordheim (FN) tunneling is utilized. By applying high negative bias ( $\sim$  -8 V) to the control gate and high positive bias ( $\sim$  -8V) to the substrate, the electrons are driven back into the silicon layer [4].

Flash memory scaling is driven by the market needs of high-capacity, low-cost data storage capabilities. Scaling the Flash device structure has however encountered several technical challenges [5,6]. First, floating gate interference is the one of the main problems. The space between the floating gate in one cell and the floating gate in an adjacent cell has become small enough that it may cause the charges in one float gate to cause V<sub>t</sub> shift in the adjacent cell hence leading to a read error.

Second, tunnel oxide scaling is also a limitation factor. Flash memory utilizes tunneling effect which can cause damage to the tunnel oxide. The operation of flash memory is limited by stress induced leakage current (SILC) related charge transfer problems. Scaling (e.g. reducing the thickness of) the tunnel oxide exacerbates SILC effect.

Third, flash memory scaling increases the impact of single-electron trapping/detrapping in tunnel oxide which causes random telegraph noise (RTN). This results in large  $V_t$  instabilities. Additionally, with the scaled flash memory with constant  $V_t$ , small number of stored electrons are involved, resulting in large error with the loss of even a few electrons.

Fourth, the reduction of the number of electrons in the floating gate causes few electron phenomena, resulting in stochastic operation in the program, erase, and retention that lead to large variability and unreliable operations.

## 1.4 Emerging Non-Volatile memories

To address the issues related with Flash memory scaling, alternative memory approaches are being explored. In this section, candidates including Phase-change RAM, Ferroelectric RAM and Magnetoresistive RAM as emerging non-volatile memories are introduced.

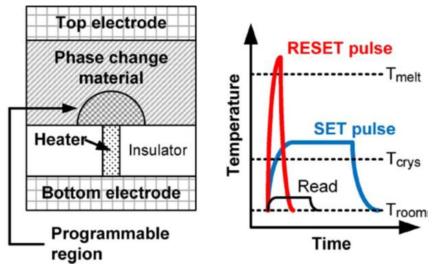

#### 1.4.1 Phase-change RAM

Phase-change random access memory (also known as PCRAM, PRAM or Chalcogenide RAM) utilizes the memory effect from the phase change of a material. This material switches back and forth between the amorphous (high resistivity) and crystalline (low resistivity) states. The device structure is shown is Fig.1.4(a). For the phage change material (PCM), a chalcogenide alloy of germanium, antimony and tellurium (GeSbTe or GST) is used [8]. As the device is fabricated, the PCM is usually in the crystalline phase due to the processing temperature. To change the PCM to the amorphous phase, the programming region shown in Fig. 1.4(a) is melted by Joule heating and quenched rapidly to room temperature. As shown in Fig.

Figure 1.4. (a) Cross-section schematic of the conventional phase-change memory cell. (b) Temperature-applied electrical pulses widths for SET, RESET and Read pulses. Reproduced from [7].

1.4(b), the applied pulse is large to achieve high temperature (600 °C) for a short time. In this process, the PCM loses its crystallinity and stays in an amorphous glass-like state. This amorphous region, along with the remaining crystalline region in the rest of the film in series,

determines the resistance of the cell. On the other hand, to change the PCM back to the crystalline state, a current pulse with medium amplitude is applied to achieve a temperature between the melting point and the crystallization point. Additionally, the pulse is applied for a long enough time (in the order of 100ns) to ensure the film has enough time to fully crystallize. To read the device state (high resistivity or low resistivity), a low read current pulse is applied to keep the device from disturbance as shown in Fig. 1.4(b). However, the continuous heating and quenching process causes void formation (stuck at high resistivity) or elemental segregation. Additionally, thermal coupling between adjacent cells also limits the scaling potential of PCM devices.

#### 1.4.2 Ferroelectric RAM

Figure 1.5. (a) A schematic circuit diagram for a typical 1T1C FeRAM cell. (b) Polarization-voltage hysteresis of a MFM capacitor. (c) A schematic circuit diagram for a 1T FeFET device. (d) Source-drain current vs. gate voltage hysteresis of a FEFET device. Reproduced from [9].

Ferroelectric RAM (Ferroelectric random access memory or FeRRAM) is another non-volatile RAM structure. In a conventional 1T1C structure, the device resembles conventional DRAM cells consisting of a transistor structure and a capacitor, whereas the FeRAM utilizes a ferroelectric layer instead of a dielectric layer in the capacitor as shown in Fig. 1.5(a). Typically

lead zirconate titanate (PZT) is used in FeRAM. The polarization properties of a ferroelectric layer are used to achieve non-volatile memory effect. When the external electric field is applied across the ferroelectric layer, the dipole moments inside the ferroelectric layer align to the field direction above the coercive field and leading to a hysteresis effect in the polarization-electric field measuremnets as shown is Fig 1.5(b). After the external electric field is removed, the ferroelectric material retains its polarization as shown in points A and B of Fig. 1.5(b). FeRAM shows low power consumption, fast speed and high endurance. However, the main problem of FeRAM is the destructive read process. The read process utilizes writing process to the cell. If a small (displacement) current pulse is detected, it implies that the device state (polarization) changes and it was OFF state. The low density associated with the capacitor structure is also another bottleneck of a FeRAM.

To overcome the limitation of destructive read process and scaling issues, FeRAM structures without the capacitor (1T structure) have been proposed, as shown in Fig. 1.5(c). This structure utilizes ferroelectric materials as the gate insulator. The polarity of ferroelectric materials modulates the channel conductance of the underlying semiconductor, so the memory effect is obtained as a shift in threshold voltage as shown in Fig. 1.5(d). However, new challenges such as chemical reactions and intermixing between Si and the ferroelectric stack and the short retention time prevent it from challenging the current flash memory market.

#### 1.4.3 Magnetic RAM

Magnetic RAM (MRAM) uses magnetic effects instead of electrical charges currently used in memory technology. A MRAM cell has two ferromagnetic electrodes. While one has a

fixed magnetic polarity, the polarity of the other can be switchable. Between the two layers, there is a thin insulating tunnel barrier. If the polarities of the two electrodes are parallel to each other, the tunnel resistance of the device is low (ON state). On the other hand, if the polarities are antiparallel to each other, a high tunnel resistance state (OFF state) is obtained [10-12]. To switch the magnetization of the free layer, a large current (on the order of 10mA) is needed to produce the required external magnetic field, which is disadvantage of MRAM. The crosstalk issue at high density due to the spread of the magnetic field into neighboring cells is also a problem, even though MRAM has advantages of high speed and very long endurance.

Alternatively, instead of using an external magnetic field, the magnetization of the free layer can be switched by the spin transfer torque (STT) effect. In this case, a simple two-terminal structure can be used and STT-based memory (STT-MRAM) has attracted significant interest because the switching current in STT-MRAM decreases when the technology scales down. The basic structure consists of one transistor connected in series with the magnetic tunnel junction (MTJ). However, the switching current is still too high for most commercial applications. Additionally, the energy barrier for spontaneous magnetization relaxation is reduced as the magnetic electrode size is scaled, leading to higher error rates.

In the following section, we will discuss resistive memory which has recently emerged as a leading candidate of future non-volatile memory.

#### **1.5 RRAM**

Figure 1.6. a two-terminal switch can be formed with a switching medium sandwiched between a pair of electodes. Reproduced from [13].

RRAM (resistive random access memory) is a two terminal device which consists of a top electrode, a switching medium, and a bottom electrode, as shown in Fig 1.6. The top and bottom electrodes can be metal or compound material with high conductivity. The switching medium sandwiched by the two electrodes is normally an insulating material. This memory cell can be integrated in high-density because a device can be formed at each point in which the top electrode and bottom electrode are crossed to each other. The resistance of the switching medium material can be modulated by applying voltage or current between the electrodes and be reset (high resistivity) and set (low resistivity) repeatedly.

In Fig. 1.7(a), digital-type switching behavior with abrupt resistance changes is shown. This type of device has been utilized for non-volatile memory used for data storage. To date, RRAM has demonstrated endurance up to  $10^{12}$  [14,15], subnanosecond switching [16], device size scaling down to 10nm [17], long retention [18], low energy consumption [19], high ON/OFF ratio [20], 3D structure [21], and CMOS compatibility [22,23].

Figure 1.7. DC I-V characteristics. (a) Digital-like type device. Obtained from stack of Pd/  $TaO_x/Ta_2O_5/Pd$ . (b) Analog-like type device. Reproduced from [22].

Figure 1.7(b) illustrates analog-type behavior which has continuous resistance changes. While the digital-type switching has been utilized for non-volatile memory used for data storage, analog-type switching is being investigated for other applications such as neuromorphic computing. The continuous resistance change can mimic the tunable synaptic weight that modulates signals between neurons. This allows synaptic functions to be directly implemented to hardware based neuromorphic systems [25,26]. Several groups including us have demonstrated fundamental synaptic learning functions such as spike-timing-dependent-plasticity (STDP) [27], short-term and long-term plasticity [24,26], and frequency-dependent plasticity [24,28].

There are different ways to classify RRAM devices. The most natural classifications are based on switching characteristics (Unipolar vs. Bipolar) and switching mechanisms (Electrochemical metallization vs. valence change).

#### 1.5.1 Bipolar Switching vs. Unipolar Switching

Figure 1.8. Classification of the switching characteristics in a voltage sweeping experiment. (a) Unipolar switching. (b) Bipolar switching. Reproduced from [29].

RRAM devices can be divided into two categories with respect to the electrical polarity required for the switching: bipolar switching device and unipolar switching device as shown in Fig. 1.8. For the unipolar devices, the switching behavior does not rely on the polarity of the applied programming voltage. With a single voltage polarity, the device can switch from ON to OFF or from OFF to ON. As shown in Fig. 1.8(a) the set voltage is always higher than reset voltage. For the unipolar device, Joule heating is believed as the main reason of the resistance switching as conducting filaments can form and rupture inside the switching layer assisted by thermal effects. During the set transition, a partial breakdown occurs in the dielectric layer, followed by conductive filament formation which is modulated by Joule heat, leading to the low-resistance state (LRS). During the reset transition, the filaments are ruptured thermally due to the

high current density as shown in Fig. 1.8(a), leading to the high-resistance state (HRS). For the bipolar devices, the switching behavior depends critically on the polarity of the programming voltage. As shown in Fig. 1.8(b), opposite voltage polarities are required for the reset and the set processes. This implies that the switching mechanism is an electric-field driven process that leads to the formation and rupture of the filaments in the dielectric. More detailed discussions on the switching mechanism will be presented in chapter 2.

#### 1.5.2 Cation Migration vs. Anion Migration

Based on the active species that lead to resistive switching, RRAM devices can be characterized as electrochemical metallization (ECM) or valency change (VCM) devices. Resistive switching devices based on cation migration are called electrochemical metallization (ECM) or conductive bridge random access memory (CBRAM). The structure consists of an electrochemically active electrode (e.g. Ag or Cu) as the top electrode, an electrochemically inert electrode including W, TiN, doped-poly Si [13,30] as the bottom electrode. For the switching medium, an electrolyte material (e.g. chalcogenide materials) or conventional dielectric material (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> or a-Si) is used. When a positive voltage is applied to the electrochemically active electrode (Ag or Cu), the electrode can be oxidized. Here "oxidation" is defined broadly as the process of a metal atom losing an electron or electrons and forming a cation. The oxidized cations will migrate inside the switching medium in the direction towards the inert bottom electrode and eventually become reduced and deposited either inside the switching material or on top of the inert electrode. This leads to the growth of metal filaments that modulate the overall resistance of the device. Instead of cations, the other class of RRAM is based on anion migration, mainly oxygen ions, and are termed as VCM or simply oxide-RRAM. Here inert electrodes are

used, and binary transition metal oxides or complex perovskite oxides are used as the switching medium. The resistance modulation is achieved by the migration and relocation of oxygen ions, or equivalently, positively charged oxygen vacancies ( $V_{OS}$ ). There are possibly two effects in general. In one case, the accumulation of the  $V_{OS}$  at the electrode/switching medium interface can change the Schottky barrier height hence resulting in a change of the resistance of the device. In the other case, the redistribution of  $V_{OS}$  can lead the formation and rupture of filaments consisting of  $V_{O}$ -rich regions. To date, high endurance up to  $10^{12}$  [15], long retention of < 10 years, fast switching speed of <1ns [16], device size scaling down up 10 nm [17] has been demonstrated in oxide-based RRAM.

#### 1.5.3 Memristor

The RRAM also falls in the category of memristor [31]. A mathematical framework of memristor (memristive systems) has been used to explain resistive switching effects in RRAM [30]. The resistance of memristor is determined by the instantaneous input (i) and one or a set of internal state variables (w) as shown in equation Eq. (1):

$$i = G(w, v)v \tag{1}$$

While a normal resistor (linear or non-linear, e.g. diode) may also be determined by an internal state variable (e.g. depletion width in a diode), the state of a normal resistor is determined directly by the instantaneous input (current or voltage). On the other hand, for a memristor, the input only determines the change rate of the state variable, rather than its overall value. The state variable equation of a memristor is shown in Eq. (2).

$$\dot{w} = f(w, v) \tag{2}$$

Eq. (2) essentially states that the device state is determined by a time integral of the input conditions, thus leading to a history-dependent resistance. Specifically, RRAM device operations such as ionic diffusion and drift during conduction path formation or rupture can be effectively modeled within the memristor framework, which not only explains the experimentally observed hysteresis effects but also provides a framework for fundamental understanding of the device physics and allows effective analytical and numerical models to be developed that can help predict device operation in a circuit and guide device optimization as shown in chapter 6 and chapter 7.

#### 1.5.4 Research on RRAM

As mentioned in the previous section, RRAM has attracted significant interest among academia and industry due to its properties such as low switching voltage [13], non-volatility [16], high endurance [15], and multi-level characteristics [33-35]. In this thesis, we first focus on the fundamental understanding of RRAM operation through systematic experimental studies and multi-physics modeling, including detailed standard transport studies as well as non-standard methods such as noise analysis and retention failure studies. Following the mechanism analysis, we show enhanced performance of analog switching behavior through a doping process. Finally, we demonstrate potential application of RRAM devices in computing through a principal component analysis (PCA) network using RRAM arrays.

## 1.6 Organization of the Thesis

In chapter 1, we have discussed several topics related to current and alternative non-volatile memory technologies. In chapter 2, we focus on modeling of the dynamic resistive switching processes in RRAM. Specifically, by solving the three equations for oxygen vacancy transport, current continuity and Joule heating, we present a quantitative and accurate dynamic switching model that fully accounts for the resistive switching behaviors in RRAM in a unified framework.

In chapter 3, we perform systematic investigations on the resistance switching mechanism through detailed noise analysis, and show the resistance switching from high-resistance to low-resistance is accompanied by a semiconductor-to-metal transition mediated by the accumulation of oxygen-vacancies in the conduction path. From noise and transport analysis, we discuss the density of states and average distance of the Vos at different resistance states, and develop a unified model to explain the conduction in both the HRS and the LRS and account for the resistance switching effects in these devices. Significantly, it is found that even though the conduction channel area is larger in the HRS, during resistive switching a localized region gains significantly higher Vo and dominates the conduction process.

In chapter 4, we report detailed retention studies of RRAM at high temperatures and the development of oxygen diffusion reliability model of oxide-RRAM devices. The device conductance in low resistance state (LRS) is constantly monitored at several temperatures (above 300°C). Specifically, the activation energy for oxygen vacancy diffusion can be directly calculated from the failure time versus temperature relationship. The experimental result is well explained by both analytical modeling and detailed numerical multi-physics simulation, which

confirm the filamentary nature of the conduction path in LRS. Finally, this experiment reveals the existence of multiple filaments in the same device.

In chapter 5, we show that doping tantalum oxide based RRAM with silicon atoms can facilitate oxygen vacancy formation and transport in the switching layer with adjustable ion hopping distance and drift velocity. The devices show larger dynamic ranges with easier access to the intermediate states while maintaining the extremely high cycling endurance (> 10<sup>10</sup> set and reset), and are well suited for neuromorphic computing applications. We further provide a characterization methodology to quantitatively estimate the effective hopping distance of the oxygen vacancies.

In chapter 6, we investigate the feasibility of using RRAM devices to implement PCA network. First, the conductance changes of RRAM devices in a response of voltage pulses is studied and modelled with one internal state variable to trace the analog behavior of a RRAM. Secondly, we utilize Sanger's learning rule, which is derived from Hebb's learning rule, to a crossbar array of RRAM devices to perform PCA network and the weights distribution of the array is re-adjusted by the applied pulses calculated by the rule. We also examine the effect of device non-uniformity issue on the PCA network. In chapter 7, we discuss the experimental demonstration of unsupervised learning using RRAM networks and periphery circuitry based on the result of chapter 6.

In chapter 8, a brief discussion of this thesis and future works are mentioned.

#### 1.7 References

- [1] IC insights. (2015). Report Contents and Summaries. [Online] Avaiable: http://www.icinsights.com/services/mcclean-report/report-contents/. [2014, March 1].

- [2] S. Nielson. (2014). Why oversupply could affect Micron's NAND flash products. [Online] Available: http://marketrealist.com/2014/04/micron-nand-flash-products/. [2014, March 1].

- [3] C.-Y. Lu, K.-Y. Hsieh, and R. Liu, "Future Challenges of Flash Memory Technologies," *Microelectron. Eng.*, vol. 86, no. 3, pp. 283-86, Mar. 2009.

- [4] A. Fazio, "Flash Memory Scaling," MRS Bulletin, vol. 29, no. 11, pp 814-17, Nov. 2004.

- [5] K. Prall, "Scaling Non-Volatile Memory Below 30nm," *Non-Volatile Semicond. Mem. Work.* 200

- 22<sup>nd</sup> IEEE, pp. 5-10, Aug. 2007.

- [6] K. Prall, and K. Parat, "25nm 64Gb MLC NAND Technology and Scaling Challenges," *Int. Elec. Dev. Meet. (IEDM), 2010 IEEE Inter.*, pp. 5.2.1–5.2.4, 2010.

- [7] H.-S. P. Wong, S. Raoux, S. Kim, J. Liang, J. P. Reifenberg, B. Rajendran, M. Asheghi, and K. E. Goodson, "Phase Change Memory," *Proc. IEEE*, vol. 98, no. 12, pp. 2201–27, Dec. 2010.

- [8] G.W. Burr, M. J. Breitwisch, M. Franceschini, D. Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, L. A. Lastras, A. Padilla, B. Rajendran, S. Raoux, and R. S. Shenoy, "Phase Change Memory Technology," *J. Vac. Sci. Technol. B Microelec. Nanom. Struct.* vol. 28, no. 2, pp. 223–62, Mar. 2010.

- [9] Y. J. Park, I. Bae, S. J. Kang, J. Chang, C. Park, "Control of Thin Ferroelectric Polymer Films for Non-Volatile Memory Applications," vol. 17, no. 4, pp. 1135–1163, 2010.

- [10] Y. Huai and Y. Huai, "Spin-Transfer Torque MRAM (STT-MRAM): Challenges and Prospects," *AAPPS Bulletin*, vol. 18, no. 6, pp. 33–40, Dec. 2008.

- [11] S. Tehrani, B. Engel, J. M. Slaughter, E. Chen, M. Deherrera, M. Durlam, P. Naji, R. Whig, J. Janesky, and J. Calder, "Recent Developments in Magnetic Tunnel Junction MRAM," *IEEE Trans. Magn.*, vol. 36, no. 5, pp. 2752–57, Sep 2000.

- [12] J. M. Slaughter, R. W. Dave, M. Deherrera, M. Durlam, B. N. Engel, J. Janesky, N. D. Rizzo, and S. Tehrani, "Fundamentals of MRAM Technology," *J. Supercond: Incor. Nov. Magn.*, vol. 15, no. 1, Feb. 2002.

- [13] S. H. Jo, K. Kim, and W. Lu, "High-Density Crossbar Arrays Based on a Si Memristive System," *Nano lett.*, vol. 9, no. 2, pp. 870–74, Jan. 2009.

- [14] M.-J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y.-B. Kim, C.-J. Kim, D. H. Seo, S. Seo, U.-I. Chung, I.-K. Yoo, and K. Kim, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>(5-x)</sub>/TaO<sub>(2-x)</sub> bilayer structures.," *Nat. Mater.*, vol. 10, no. 8, pp. 625–30, Aug. 2011.

- [15] J. J. Yang, M.-X. Zhang, J. P. Strachan, F. Miao, M. D. Pickett, R. D. Kelley, G. Medeiros-Ribeiro, and R. S. Williams, "High switching endurance in TaO<sub>x</sub> memristive devices," *Appl. Phys. Lett.*, vol. 97, no. 23, p. 232102, Dec. 2010.

- [16] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Subnanosecond switching of a tantalum oxide memristor.," *Nanotechnology*, vol. 22, no. 48, p. 485203, Dec. 2011.

- [17] B. Govoreanu, G. S. Kar, Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I. P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, K. Seo, P. Hendrickx, G. Pourtois, H. Bender, L. Altimime, D. J. Wouters, J. A. Kittl, M. Jurczak, B.- Leuven, and K. U. Leuven, "10x10nm<sup>2</sup> Hf/HfO<sub>x</sub> Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation," *Int. Elect. Dev. Meet. (IEDM)*, 2011 IEEE Inter., pp. 31.6.1–4, Dec. 2011.

- [18] S. H. Jo, K.-H. Kim, and W. Lu, "Programmable resistance switching in nanoscale two-terminal devices.," *Nano Lett.*, vol. 9, no. 1, pp. 496–500, Jan. 2009.

- [19] B. V. V Zhirnov, R. K. Cavin, L. F. Ieee, S. Menzel, E. Linn, S. Schmelzer, D. Bra, C. Schindler, and R. Waser, "Memory Devices: Energy Space Time Tradeoffs," *Proc. IEEE*, vol. 98, no. 12, pp. 2185–2200, Oct. 2010.

- [20] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–84, May 2008.

- [21] S. Yu, H. Chen, B. Gao, J. Kang, and H. P. Wong, "HfO<sub>x</sub>-Based Vertical Resistive Switching Random Access Memory Suitable for Bit-Cost-Effective Three-Dimensional Cross-Point Architecture," *ACS Nano*,vol. 7, no. 3, pp. 2320–2325, 2013.

- [22] K. Kim, S. Gaba, D. Wheeler, J. M. Cruz-albrecht, T. Hussain, N. Srinivasa, and W. Lu, "A Functional Hybrid Memristor Crossbar-Array/CMOS System for Data Storage and Neuromorphic Applications," *Nano Lett.*, vol. 12, pp. 389-395, 2012.

- [23] Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinali, J. J. Yang, W. Wu, X. Li, W. M. Tong, D. B. Strukov, G. S. Snider, G. Medeiros-Ribeiro, and R. S. Williams, "Memristor CMOS Hybrid Integrated Circuits for Reconfigurable Logic," *Nano Lett.*, vol.9, no. 10, pp. 3640-3645, 2009.

- [24] T. Chang, S. Jo, and W. Lu, "Short-Term Memory to Long-Term Memory Transition in a Nanoscale Memristor," *ACS Nano*, vol. 5, no. 9, pp. 7669–7676, 2011.

- [25] D. B. Strukov and K. K. Likharev, "CMOL FPGA: a reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices," *Nanotechnology*, vol. 16, no. 6, pp. 888–900, Jun. 2005.

- [26] T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski, and M. Aono, "Short-term plasticity and long-term potentiation mimicked in single inorganic synapses.," *Nat. Mater.*, vol. 10, no. 8, pp. 591–5, Aug. 2011.

- [27] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale Memristor Device as Synapse in Neuromorphic Systems," *Nano Lett.*, vol. 10, pp. 1297–1301, 2010.

- [28] F. Alibart, S. Pleutin, D. Guérin, C. Novembre, S. Lenfant, K. Lmimouni, C. Gamrat, and D. Vuillaume, "An Organic Nanoparticle Transistor Behaving as a Biological Spiking Synapse," *Adv. Funct. Mater.*, vol. 20, no. 2, pp. 330–337, Jan. 2010.

- [29] R. Waser and M. Aono, "Nanoionics-based resistive switching memories.," *Nat. Mater.*, vol. 6, no. 11, pp. 833–40, Nov. 2007.

- [30] S. H. Jo and W. Lu, "CMOS Compatible Nanoscale Nonvolatile Resistance Switching Memory," *Nano Lett.*, vol. 8, no. 2, pp. 392–397, 2008.

- [31] L. O. Chua, "Memristor The missing circuit element," *IEEE Trans. Circuit Theory*, vol. CT-18, no. 5, pp. 507-519, 1971.

- [32] L. O. Chua, and S.M. Kang, "Memristive Devices and Systems," *Proc. IEEE*, vol. 64, no. 2, Feb. 1976.

- [33] K. Kim, S. H. Jo, S. Gaba, and W. Lu, "Nanoscale resistive memory with intrinsic diode characteristics and long endurance," *Appl. Phys. Lett.*, vol. 96, p. 053106, 2010.