# **Designing Accurate and Low-Cost Stochastic Circuits**

by

Te-Hsuan Chen

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2016

**Doctoral Committee:**

Professor John P. Hayes, Chair Professor Scott Mahlke Professor Karem A. Sakallah Professor Zhengya Zhang © Te-Hsuan Chen All rights reserved 2016 To my family and friends

#### ACKNOWLEDGEMENTS

I am deeply grateful to all the numerous, wise and caring people who have supported me through my Ph.D. and earlier education. I wish to thank my advisor Professor John P. Hayes for his invaluable advice and encouragement in all aspect of research, including critical thinking, identifying and solving research problems, technical writing, and oral presentation. It has been an honor to be his student. Financial support from the National Science Foundation is also gratefully acknowledged.

I would like to thank the members of my Ph.D. committee, Professors Scott Mahlke, Karem A. Sakallah, and Zhengya Zhang for their helpful feedback. I am also grateful to all the professors I have worked with as a student, including Professors David Blaauw, Edmund H. Durfee, Mingyan Liu, and Valeria Bertacco. Their courses provided a solid foundation to my research. I also wish to thank Christine Feak and Judy Dyer from the English Language Institute at the University of Michigan. I have learned a lot about academic writing from them. I am thankful to Professor Cheng-Wen Wu, my former advisor at National Tsing Hua University, who has been a mentor for research and life.

I am grateful to the members of our research group with whom I have had many wonderful discussions, including Dr. Chien-Chih Yu, Dr. Dae Young Lee, I-Che Chen, Pai-Shun Ting, and William Sullivan. A special thanks to Dr. Armin Alaghi who helped me a lot with the topic of stochastic computing and shared much of his research experience with me. Thank you to all of the valuable friends I met in Ann Arbor for being there for me through the tough journey to my Ph.D. and for lots of great moments we have shared. Finally, I wish to thank my family who have given me unconditional support for all the decisions I have made. Thanks especially to my parents and my sister for encouraging me to pursue whatever I wanted. Your emotional support has been the strength helping me get through tough times.

## **TABLE OF CONTENTS**

| DEDICATI                                        | ON    | ii                                     |  |

|-------------------------------------------------|-------|----------------------------------------|--|

| ACKNOWI                                         | LEDG  | EMENTSiii                              |  |

| LIST OF FI                                      | GURI  | ESvii                                  |  |

| LIST OF TA                                      | ABLE  | sxi                                    |  |

| LIST OF A                                       | BBRE  | VIATIONS xii                           |  |

| LIST OF SY                                      | MBC   | DLSxiii                                |  |

| ABSTRACT                                        | Г     |                                        |  |

| CHAPTER                                         | 1 Int | roduction1                             |  |

|                                                 | 1.1   | Motivation1                            |  |

|                                                 | 1.2   | Stochastic Computing                   |  |

|                                                 | 1.3   | Research Challenges                    |  |

|                                                 | 1.4   | Dissertation Outline                   |  |

| CHAPTER                                         | 2 Ac  | curacy and Soft Errors                 |  |

|                                                 | 2.1   | Soft Errors                            |  |

|                                                 | 2.2   | Probability Model 15                   |  |

|                                                 | 2.3   | Probabilistic Transfer Matrices (PTMs) |  |

|                                                 | 2.4   | Impact on Stochastic Numbers 21        |  |

|                                                 | 2.5   | Impact on Stochastic Circuits          |  |

|                                                 | 2.6   | Case Study: Image Edge Detection       |  |

|                                                 | 2.7   | Summary                                |  |

| CHAPTER                                         | 3 Co  | rrelation                              |  |

|                                                 | 3.1   | Analysis Framework                     |  |

|                                                 | 3.2   | Representation                         |  |

|                                                 | 3.3   | Impact on Stochastic Circuits          |  |

|                                                 | 3.4   | De-correlation Methods                 |  |

|                                                 | 3.5   | Summary                                |  |

| CHAPTER 4 Design of General Stochastic Circuits |       |                                        |  |

|          | 4.1  | Stochastic Equivalence         | 50  |

|----------|------|--------------------------------|-----|

|          | 4.2  | SEC-based Synthesis            |     |

|          | 4.3  | Search-based Optimization      |     |

|          | 4.4  | Cover-based Optimization       |     |

|          | 4.5  | Summary                        | 82  |

| CHAPTER  | 5 De | esign of Dividers              |     |

|          | 5.1  | Stochastic Dividers            |     |

|          | 5.2  | CORDIV Method                  |     |

|          | 5.3  | Experimental Results           |     |

|          | 5.4  | Summary                        | 101 |

| CHAPTER  | 6 Mo | onotonic Progressive Precision | 102 |

|          | 6.1  | Exact Stochastic Computing     | 102 |

|          | 6.2  | Progressive Precision          | 112 |

|          | 6.3  | Case Study                     | 118 |

|          | 6.4  | Summary                        | 122 |

| CHAPTER  | 7 Co | onclusions                     | 124 |

|          | 7.1  | Summary of Contributions       | 124 |

|          | 7.2  | Directions for Future Work     | 127 |

| BIBLIOGR | APHY | Υ                              | 132 |

# LIST OF FIGURES

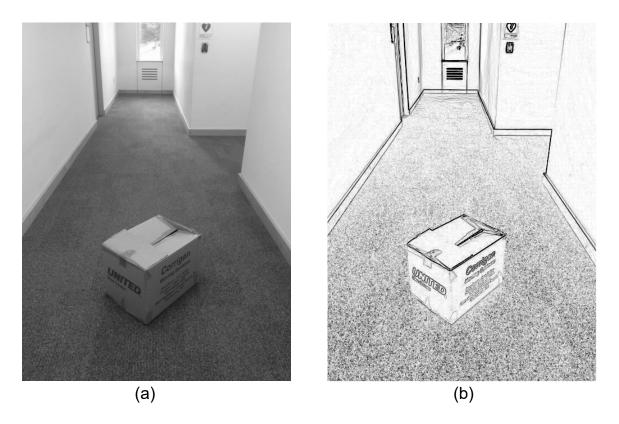

| Figure 1.1: An example of edge detection to convert (a) a greyscale image of a corridor with an obstacle into (b) a high-contrast image                                                                                                                                                                       | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

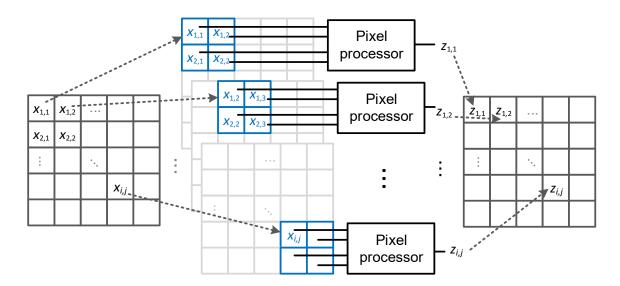

| Figure 1.2: Edge detection using an array of pixel processors and a four-pixel window.                                                                                                                                                                                                                        | 3  |

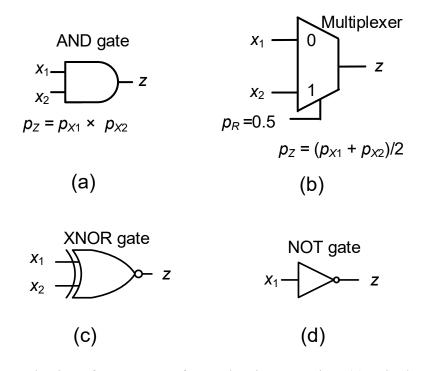

| Figure 1.3: A selection of components for stochastic computing: (a) unipolar<br>multiplier, (b) unipolar and bipolar scaled adder, (c) bipolar<br>multiplier, and (d) bipolar negater                                                                                                                         | 6  |

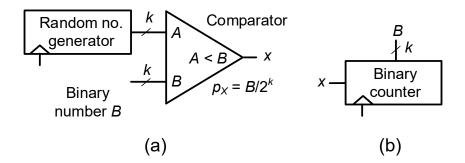

| Figure 1.4: Number converters (a) binary-to-stochastic and (b) stochastic-to-<br>binary.                                                                                                                                                                                                                      | 8  |

| Figure 1.5: Update node for LDPC decoder.                                                                                                                                                                                                                                                                     | 10 |

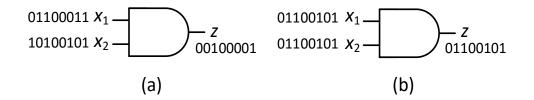

| Figure 1.6: Stochastic multiplication with (a) uncorrelated inputs, and (b) highly correlated inputs.                                                                                                                                                                                                         | 11 |

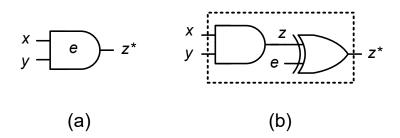

| Figure 2.1: Circuit models for a stochastic multiplier with a bit-flip error <i>e</i> affecting its output: (a) internal or built-in error, and (b) externally injected error                                                                                                                                 | 17 |

| <ul><li>Figure 2.2: Representative PTMs: (a) NAND gate with four distinct input-<br/>dependent bit-flip error rates, (b) NAND gate with its first input<br/>stuck-at-1, (c) fanout wiring network with two output branches, and<br/>(d) swap or crossover gate that switches the order of two wires</li></ul> | 19 |

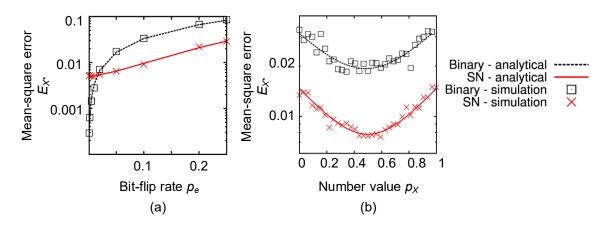

| Figure 2.3: MSE of a stochastic and a binary number in the presence of bit-flips calculated using analytical and simulation methods: (a) for different values of $p_e$ , and (b) for different values of $p_X$ .                                                                                              | 23 |

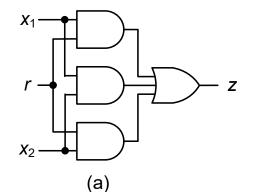

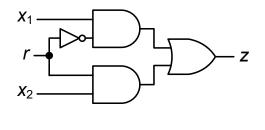

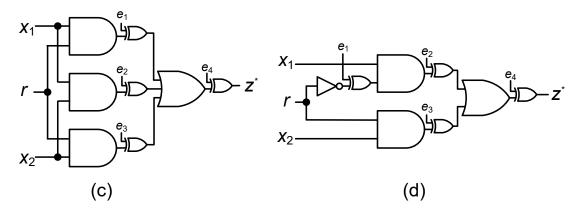

| Figure 2.4: Stochastic circuits for the scaled addition $p_Z = 0.5 (p_{X1} + p_{X2})$ : (a)<br>majority-based, (b) multiplexer-based, (c) majority-based with error<br>injection, and (d) multiplexer-based with error injection                                                                              | 25 |

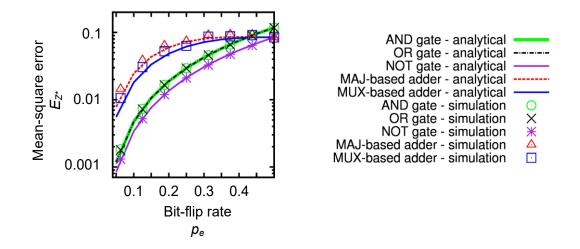

| Figure 2.5: MSE at the outputs of representative stochastic circuits in the presence of soft errors calculated using analytical and simulation methods                                                                                                                                                        | 26 |

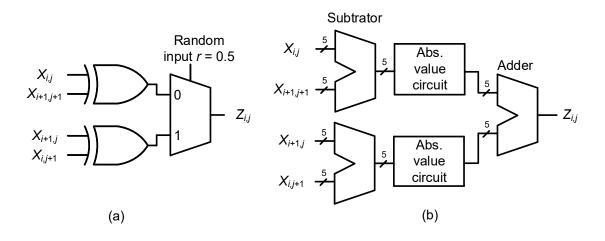

| Figure 2.6: Edge detectors: (a) stochastic and (b) conventional                                                                                                                                                                                                                                               | 28 |

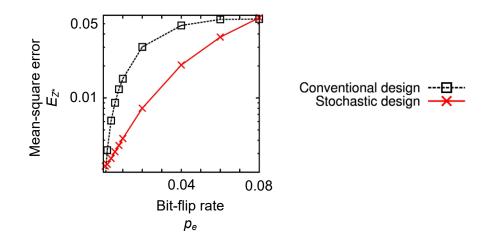

| Figure 2.7: MSE of stochastic and conventional edge-detection circuits in the presence of soft-errors.                                                                                                                                                                                                        | 29 |

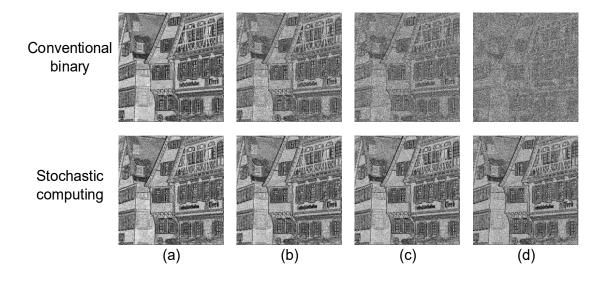

| Figure 2.8: | Comparison of stochastic and conventional edge detection for various soft-error rates (bit-flips percentages) in the edge-detection circuits: (a) 0.1%, (b) 0.5%, (c) 1% and (d) 2%                                                                                               | 30 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

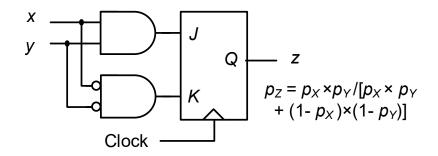

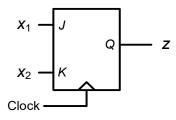

| Figure 3.1: | JK flip-flop performing the stochastic operation $p_Z = p_{X1} / (p_{X1} + p_{X2})$                                                                                                                                                                                               | 33 |

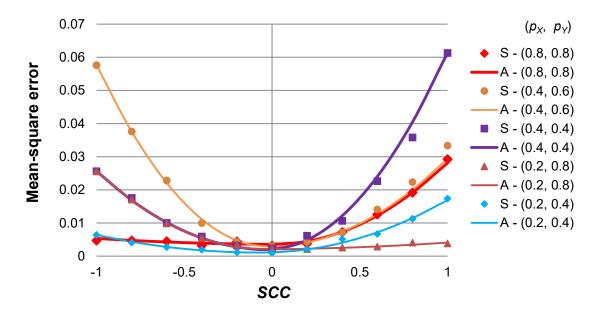

| Figure 3.2: | MSE of the AND multiplier calculated by analysis (A) and simulation (S) for various combinations of $p_X$ , $p_Y$ and SCC.                                                                                                                                                        | 39 |

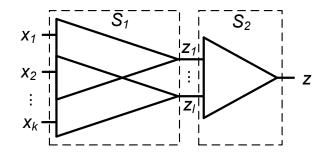

| Figure 3.3: | Circuit model S for correlation analysis; the triangles are the fan-in cones seen on backtracing from $Z_1,, Z_l$ and Z                                                                                                                                                           | 40 |

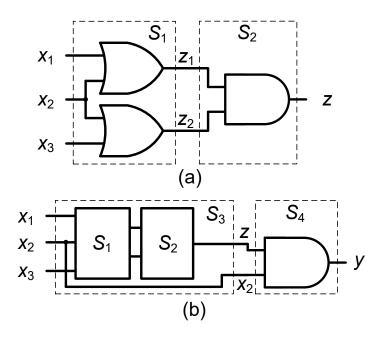

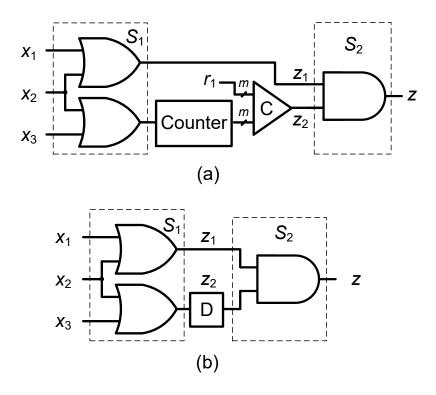

| Figure 3.4: | Stochastic circuits affected by correlation due to re-convergent signals. The target arithmetic functions are: $p_{Z1} = p_{X1} + p_{X2} - p_{X1} \times p_{X2}$ , $p_{Z2} = p_{X2} + p_{X3} - p_{X2} \times p_{X3}$ , $p_Z = p_{Z1} \times p_{Z2}$ and $p_Y = p_Z \times p_{X2}$ | 42 |

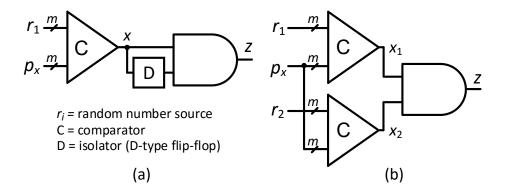

| Figure 3.5: | Multiplier used as a squarer (a) with one SNG and a stochastic isolator; (b) with two SNGs                                                                                                                                                                                        | 44 |

| Figure 3.6: | Reducing correlation in the circuit of Figure 3.4 <i>a</i> (a) by regeneration, and (b) by isolation.                                                                                                                                                                             | 46 |

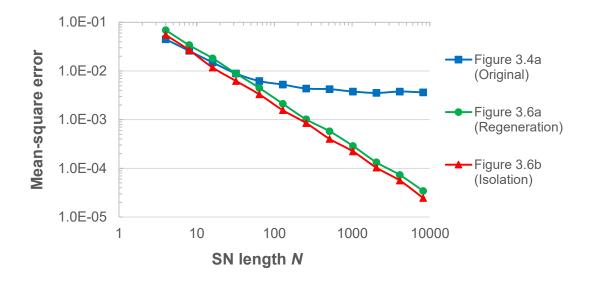

| Figure 3.7: | MSEs for the circuits of Figure 3.4 <i>a</i> and Figure 3.6 obtained by simulation.                                                                                                                                                                                               | 47 |

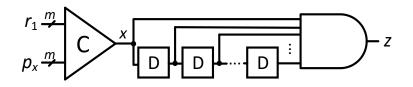

| Figure 3.8: | Stochastic circuit to generate $z = x^r$ with a single SNG                                                                                                                                                                                                                        | 48 |

| Figure 4.1: | Two implementations of scaled addition: (a) a multiplexer (MUX), and (b) an equivalent majority circuit (MAJ)                                                                                                                                                                     | 51 |

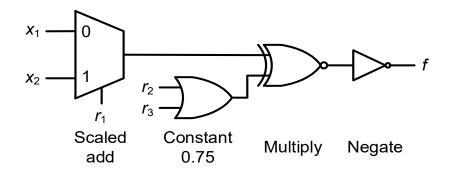

| Figure 4.2: | Direct-mapped implementation of Example 4.5.                                                                                                                                                                                                                                      | 64 |

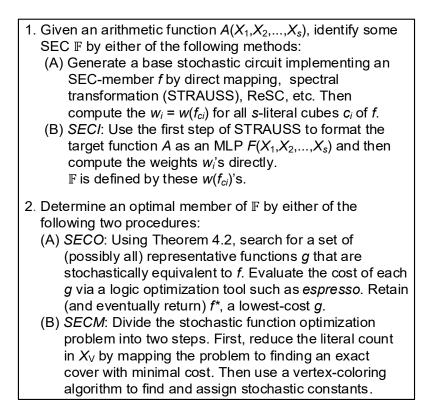

| Figure 4.3: | Overview of the extended SEC-based algorithm <i>ESECS</i> to determine a low-cost stochastic circuit.                                                                                                                                                                             | 65 |

| Figure 4.4: | Overview of <i>SECI</i> used by <i>ESECS</i> to identify an SEC for a given MLP.                                                                                                                                                                                                  | 66 |

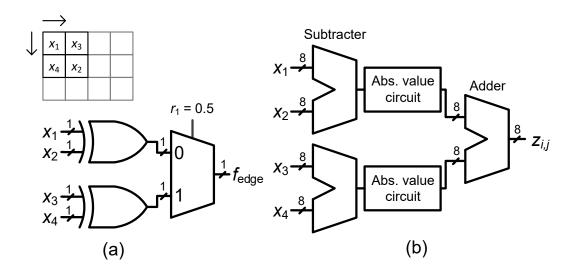

| Figure 4.5: | Edge detectors: (a) stochastic, (b) conventional [3]                                                                                                                                                                                                                              | 67 |

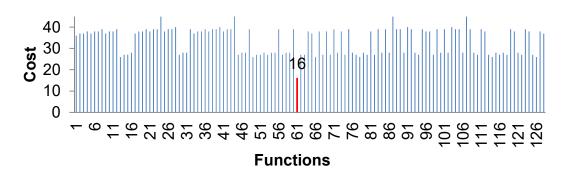

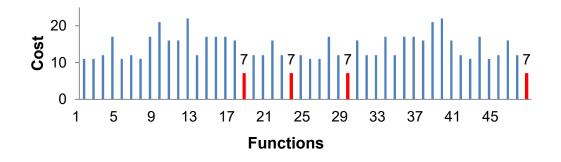

|             | Cost of the equivalent edge-detector functions.                                                                                                                                                                                                                                   |    |

| Figure 4.7: | Cost of the equivalent 2-bit WBG functions.                                                                                                                                                                                                                                       | 69 |

| Figure 4.8: | Procedure <i>SECO</i> used by <i>ESECS</i> to find a lowest-cost member of an SEC                                                                                                                                                                                                 | 71 |

| Figure 4.9: | Average minimum cost of functions found by <i>SECO</i> (blue) and random sampling (red).                                                                                                                                                                                          | 73 |

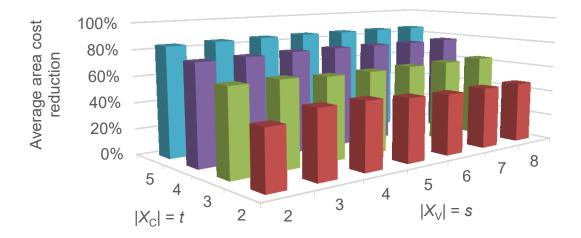

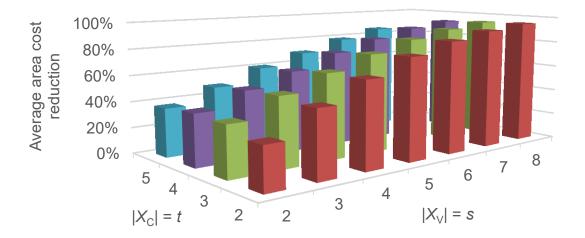

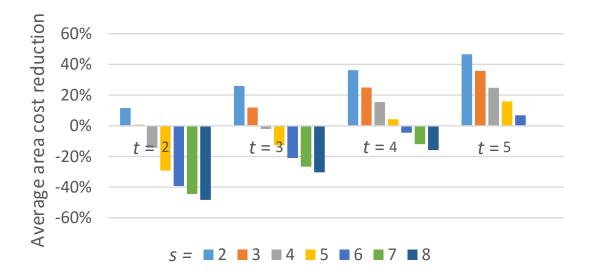

| Figure 4.10 | : Average area cost reduction achieved by SECO.                                                                                                                                                                                                                                   | 74 |

| Figure 4.11 | : Truth table for the SEC of the BFs realizing stochastic addition; (b) weight-table representation.                                                                                                                                                                              | 76 |

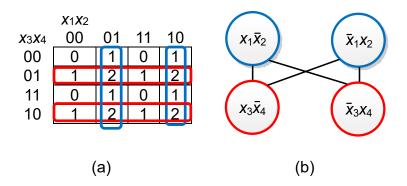

| Figure 4.12 | 2: (a) Weight table in K-map format, and (b) implicant covering graph for the edge detector in Figure 4.5 <i>a</i>                                                                                                                                                                | 77 |

| Figure 4.13: Procedure <i>SECM</i> used by <i>ESECS</i> to generate a low-cost stochastic circuit.                                                                           | 78  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

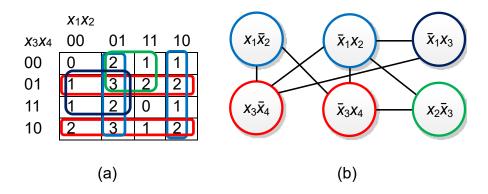

| Figure 4.14: (a) Weight table in K-map format for Example 12, and (b) its implicant covering graph                                                                           | 80  |

| Figure 4.15: Average area cost reduction achieved by SECM                                                                                                                    | 81  |

| Figure 4.16: Average area cost reduction when SECO is replaced by SECM                                                                                                       | 82  |

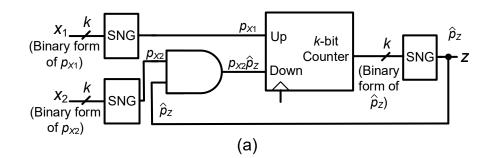

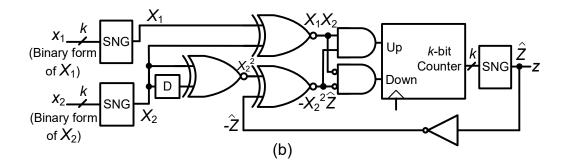

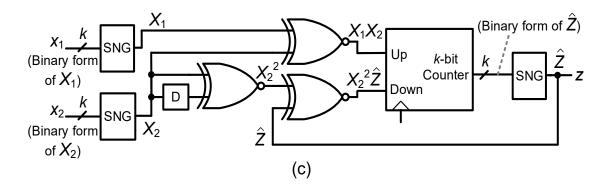

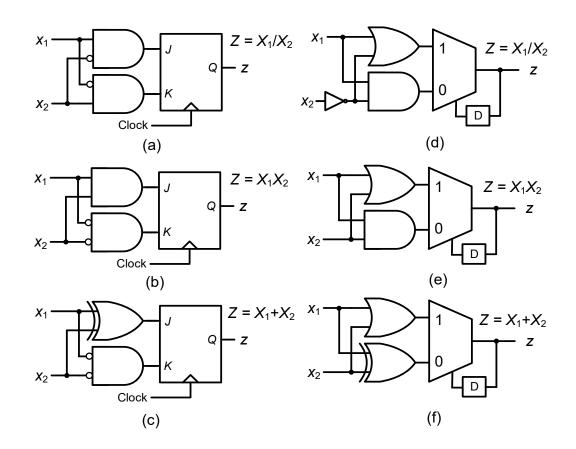

| Figure 5.1: Gaines' ADDIE-based (a) unipolar and (b) bipolar stochastic dividers [31]; (c) equivalent circuit for Figure 5.1 <i>b</i>                                        | 86  |

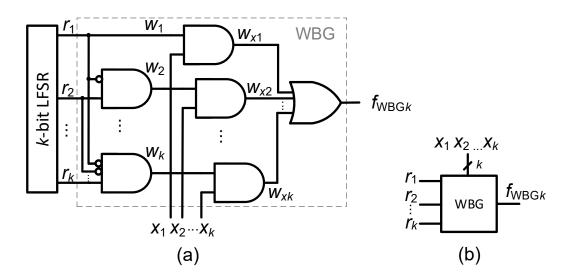

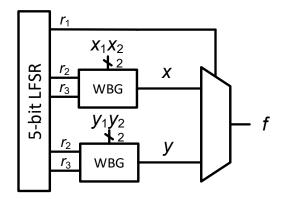

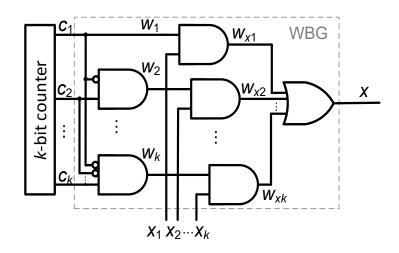

| Figure 5.2: (a) The <i>k</i> -bit weighted binary generator (WBG) of SNs [38] and (b) its symbol                                                                             | 87  |

| Figure 5.3: Ananth's ADDIE-based unipolar stochastic divider                                                                                                                 | 87  |

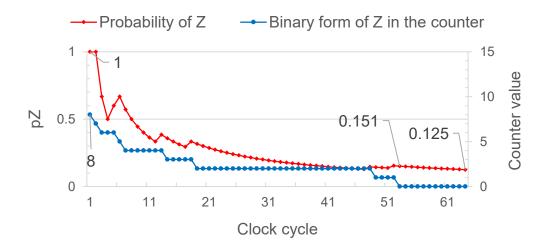

| Figure 5.4: Convergence behavior of Gaines' unipolar ADDIE-based divider in<br>Figure 5.1 <i>a</i> with $k = 4$ , $p_{X1} = 0$ and $p_{X2} = 1$                              | 88  |

| Figure 5.5: Gaines' basic components for the ratio format: (a) divider, (b)<br>multiplier and (c) adder [31]; Min et al.'s (d) divider, (e) multiplier<br>and (f) adder [64] | 89  |

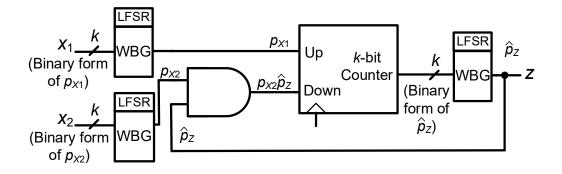

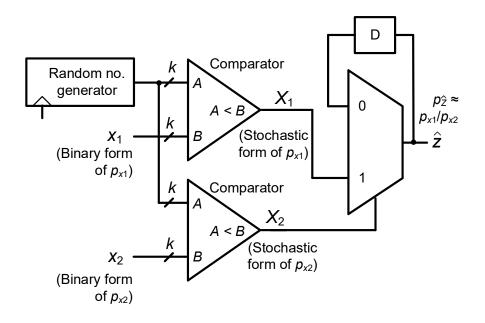

| Figure 5.6: Basic design for a CORDIV stochastic divider                                                                                                                     | 94  |

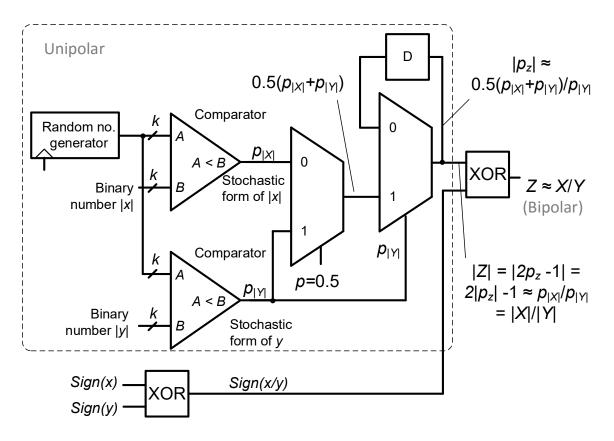

| Figure 5.7: Design for a bipolar CORDIV stochastic divider                                                                                                                   | 95  |

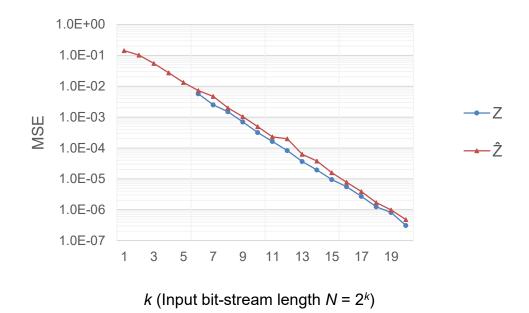

| Figure 5.8: Accuracy comparison between the unpadded conditional SN $Z = X1 X2$ (blue) and the padded SN Z (red)                                                             | 96  |

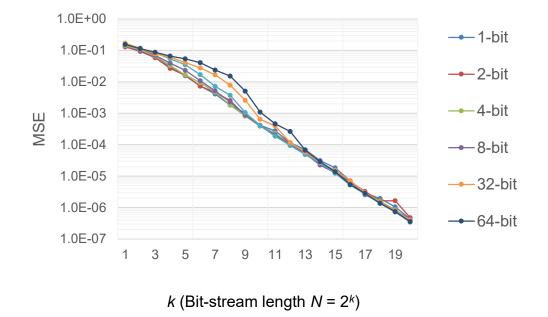

| Figure 5.9: Accuracy of the CORDIV divider for different sizes of the padding memory                                                                                         | 97  |

| Figure 5.10: Accuracy of the CORDIV divider for different values of <i>pX2</i>                                                                                               | 98  |

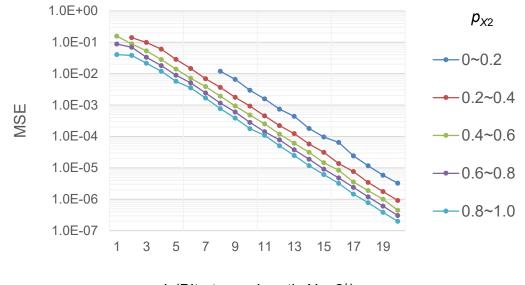

| Figure 5.11: Accuracy of Gaines' ADDIE-based divider as counter size k varies                                                                                                | 99  |

| Figure 5.12: Accuracy of Ananth's ADDIE-based divider as counter size k varies                                                                                               | 99  |

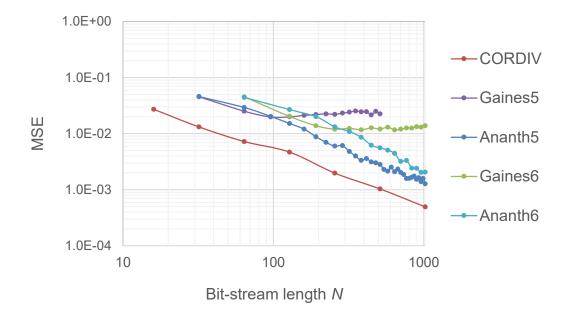

| Figure 5.13: Accuracy comparison between CORDIV, and Ananth's and Gaines' dividers with 5- and 6-bit counters                                                                | 100 |

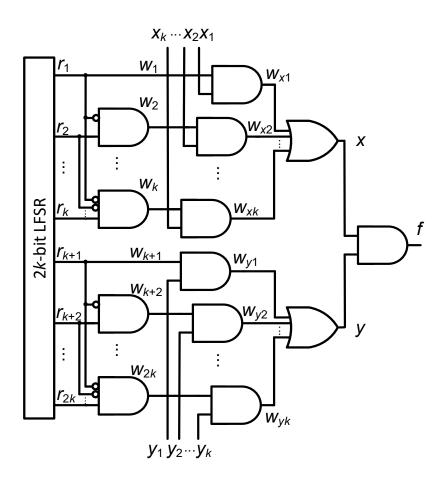

| Figure 6.1: The <i>k</i> -bit exact stochastic multiplier [38]                                                                                                               | 104 |

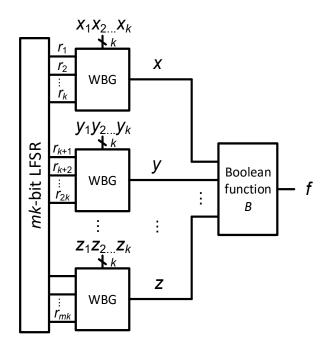

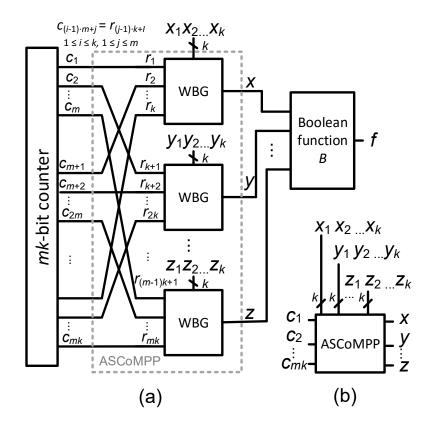

| Figure 6.2: ASC design for exact implementation of $F(p_X, p_Y,, p_Z)$                                                                                                       | 106 |

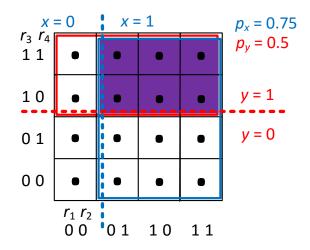

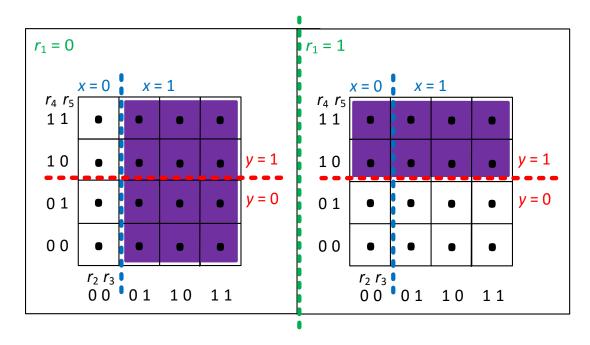

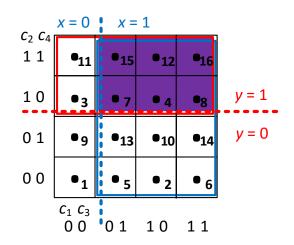

| Figure 6.3: The sample space <i>S</i> of the 2-bit exact stochastic multiplier in Example 6.3.                                                                               | 110 |

| Figure 6.4: Two-bit exact stochastic scaled adder.                                                                                                                           | 111 |

| Figure 6.5: Sample space of the 2-bit stochastic scaled adder in Example 6.4                                                                                                 | 111 |

| Figure 6.6: A <i>k</i> -bit weighted binary SNG with strict MPP                                                                                                              | 115 |

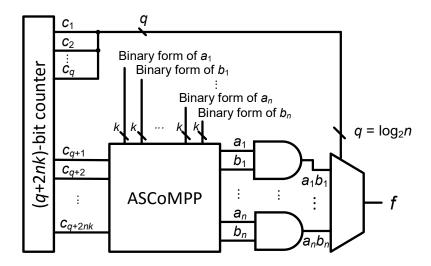

| Figure 6.7: (a) <i>ASCoMPP</i> design for accurate stochastic computing with strict MPP, and (b) its symbol.                                                                                                                | 116 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.8: Counting sequence of the 2-bit exact stochastic multiplier in Example 6.3.                                                                                                                                      | 117 |

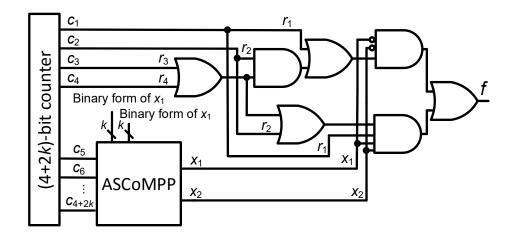

| Figure 6.9: Stochastic inner product circuit designed using ASCoMPP                                                                                                                                                         | 119 |

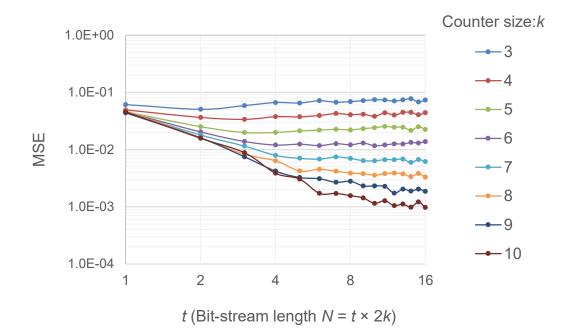

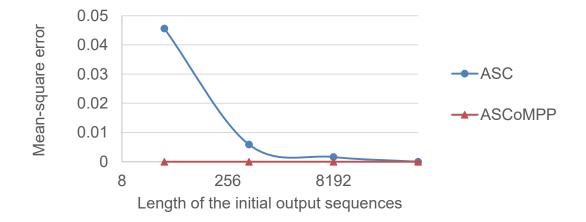

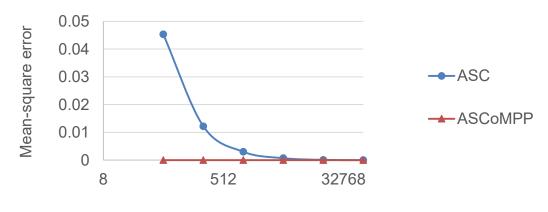

| Figure 6.10: MSE of the stochastic inner products for different bit-streams of length using ASC and ASCoMPP designs.                                                                                                        | 120 |

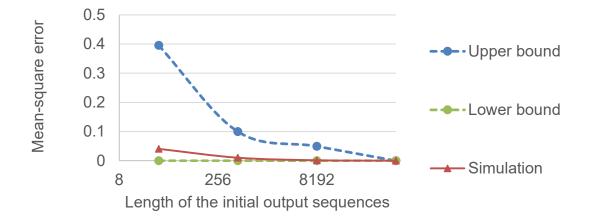

| Figure 6.11: Inner-product MSE for various bit-stream lengths, compared to the expected values for 4-bit precision                                                                                                          | 121 |

| Figure 6.12: ASCoMPP implementation of $p_F = 0.6875 - 0.6875 \times (p_{X1} + p_{X2}) + 1.125 \times p_{X1} \times p_{X2}$                                                                                                 | 122 |

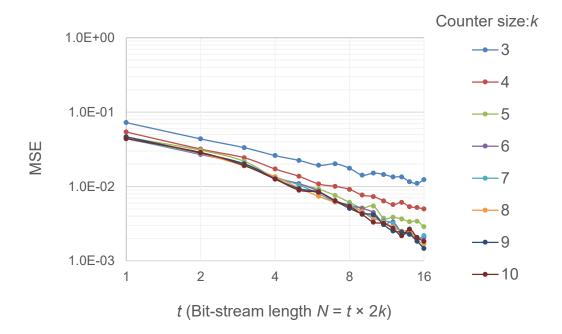

| Figure 6.13: MSE of the stochastic circuit of $p_F = 0.6875 - 0.6875 \times (p_{X1} + p_{X2}) + 1.125 \times p_{X1} \times p_{X2}$ products for different bit-streams of length using <i>ASC</i> and <i>ASCoMPP</i> designs | 122 |

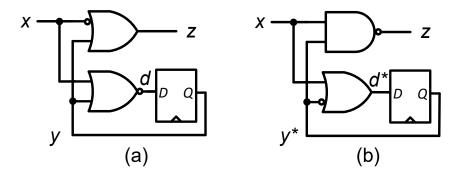

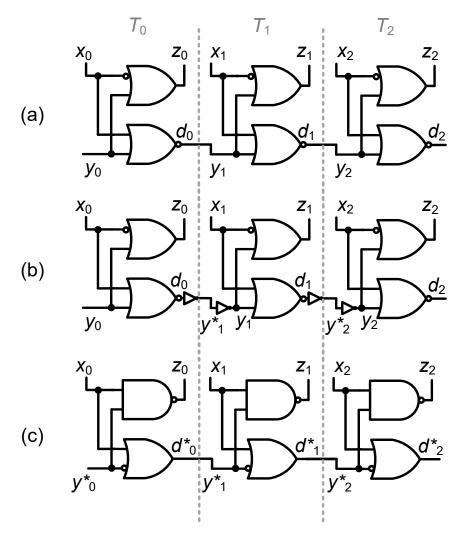

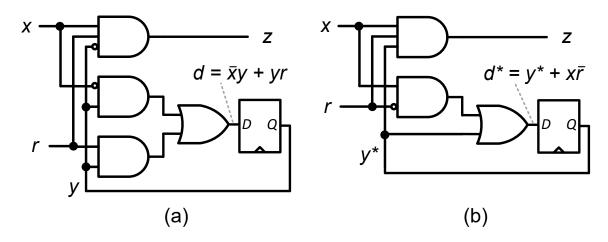

| Figure 7.1: Sequential stochastic circuits implementing $p_Z = (2p_X - 2) / (p_X - 2)$<br>[6]                                                                                                                               | 127 |

| Figure 7.2: Expanded circuits with three time frames for the sequential circuits in Figure 7.1                                                                                                                              | 128 |

| Figure 7.3: Stochastically equivalent sequential circuits with different costs                                                                                                                                              | 129 |

# LIST OF TABLES

| Table 1.1: Numerical values of an N-bit bit-stream X in the unipolar and bipolar formats.                        | 5   |

|------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1: Mean square error (MSE) of two stochastic squarer designs                                             | 45  |

| Table 3.2: MSEs of some power functions.                                                                         | 48  |

| Table 4.1: All SECs for the 2-variable logic functions $f(x_1; r_1)$ with $X_V = x_1$ and $X_C = r_1$            | 62  |

| Table 5.1: Area comparison between CORDIV, and Ananth's and Gaines'         dividers with 5- and 6-bit counters. | 101 |

| Table 6.1: Bit-streams for the exact 2-bit multiplication of Example 6.1.                                        | 105 |

| Table 6.2: Bit-streams for the 2-bit multiplication using ASCoMPP.                                               | 118 |

## LIST OF ABBREVIATIONS

| ADDIE | Adaptive Digital Element                         |  |  |  |  |

|-------|--------------------------------------------------|--|--|--|--|

| BF    | Boolean Function                                 |  |  |  |  |

| ITM   | Ideal Transfer Matrix                            |  |  |  |  |

| LDPC  | Low-Density Parity-Check                         |  |  |  |  |

| LFSR  | Linear Feedback Shift Register                   |  |  |  |  |

| MPP   | Monotonic Progressive Precision                  |  |  |  |  |

| MSE   | Mean Square Error                                |  |  |  |  |

| PP    | Progressive Precision                            |  |  |  |  |

| SC    | Stochastic Computing                             |  |  |  |  |

| SCC   | Stochastic Computing Correlation                 |  |  |  |  |

| SE    | Stochastically Equivalent                        |  |  |  |  |

| SEC   | Stochastic Equivalence Class                     |  |  |  |  |

| SN    | Stochastic Number                                |  |  |  |  |

| SNG   | Stochastic Number Generator                      |  |  |  |  |

| PTM   | Probabilistic Transfer Matrix                    |  |  |  |  |

| ReSC  | Reconfigurable Stochastic Computing Architecture |  |  |  |  |

| RV    | Random Variable                                  |  |  |  |  |

| TT    | Truth Table                                      |  |  |  |  |

| WBG   | Weighted Binary Generator                        |  |  |  |  |

| WT    | Weight Table                                     |  |  |  |  |

## LIST OF SYMBOLS

| Symbol              | Meaning                                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | The dot sign or juxtaposition denotes multiply and OR in arithmetic and logic expressions, respectively.                                              |

| +                   | The plus sign denotes add and AND in arithmetic and logic expressions, respectively.                                                                  |

| $\equiv_{\kappa}$   | Stochastic equivalence with respect to a set of constants K. It is simplified to $\equiv$ when $K = (0.5, 0.5,, 0.5)$ .                               |

| $arepsilon_Z^{(i)}$ | The stage- <i>i</i> bit-error of an SN Z. It is defined as $2^i \times  \hat{p}_Z^{(i)} - p_Z^{(i)} $ .                                               |

| $\mathbb{F}$        | An SEC, i.e., a set of stochastically equivalent functions.                                                                                           |

| Κ                   | A set of constant numbers in the unit interval [0,1]. Each number in $K$ corresponds to the numerical value of a stochastic constant in $X_{\rm C}$ . |

| n                   | The size of X, so $n = s + t$ .                                                                                                                       |

| N                   | The length of an SN.                                                                                                                                  |

| $p_Z$               | The probability of seeing a 1 on a wire z. It is also the numerical value of a unipolar SN Z. If Z is bipolar, its numerical value is $2p_Z - 1$ .    |

| $\hat{p}_Z$         | The measured value when $N$ bits of a unipolar SN $Z$ are collected.                                                                                  |

| $p_Z^{(i)}$         | The numerical value of a unipolar SN Z to <i>i</i> -bit precision.                                                                                    |

| $\hat{p}_Z^{(i)}$   | The measured value of a unipolar SN Z when $2^i$ bits are sampled.                                                                                    |

| S                   | The size of $X_{V_{-}}$                                                                                                                               |

| t                   | The size of $X_{C.}$                                                                                                                                  |

| w(f)                | The weight of a Boolean function $f(x_1, x_2,, x_n)$ is the number of its minterms i.e., $w(f) = f(0,, 0, 0) + + f(1,, 1, 0) + f(1,, 1, 1)$ .         |

| X                   | The set of inputs of a stochastic circuit.                                                                                                            |

| Xv                  | The subset of the set of inputs $X$ of a stochastic circuit with variable signal probabilities.                                                       |

- $X_{\rm C}$  The subset of the set of inputs X of a stochastic circuit with constant signal probabilities.

- *z* A lowercase letter denotes a wire in a circuit or a literal in a logic expression.

- *Z* An uppercase letter denotes a bit-stream, i.e. a stochastic number (SN), or the numerical value of the SN *Z* in an arithmetic expression.

#### ABSTRACT

#### **Designing Accurate and Low-Cost Stochastic Circuits**

by

#### **Te-Hsuan Chen**

#### Chair: John P. Hayes

Stochastic computing (SC) is an unconventional computing approach that processes data represented by pseudo-random bit-streams called stochastic numbers (SNs). It enables arithmetic functions to be implemented by tiny, low-power logic circuits, and is highly error-tolerant. These properties make SC practical for applications that need massive parallelism or operate in noisy environments where conventional binary designs are too costly or too unreliable. SC has recently come to be seen as an attractive choice for tasks such as biomedical image processing and decoding complex error-correcting codes. Despite its desirable properties, SC has features that limit its usefulness, including insufficient accuracy and an inadequate design theory. Accuracy is especially vulnerable to correlation among interacting SNs and to the random fluctuations inherent in SC's data representation. This dissertation examines the major factors affecting accuracy using analytical and experimental approaches based on probability theory and circuit simulation, respectively. We devise methods to quantify the error effects in stochastic circuits by means of probabilistic transfer matrices and Bernouilli processes. These methods make it possible to compare the impact of errors on conventional and stochastic circuits under various conditions. We then analyze correlation in detail and show that correlation-induced errors can be reduced by the careful insertion of delay elements, a de-correlation technique called isolation. Noting that different logic functions can have the same stochastic behavior when constant SNs are applied to their inputs, we show how to partition logic functions into stochastic equivalence classes (SECs). We derive a procedure for identifying SECs, and apply SEC concepts to the synthesis and optimization of stochastic circuits. While addition, subtraction and multiplication have well-known and simple SC implementations, this is not true for division. We study stochastic division methods and propose a new type of stochastic divider that combines low cost with high accuracy. Finally, we turn to the design of general stochastic circuits and investigate a desirable property of SNs called monotonic progressive precision (MPP) whereby accuracy increases steadily with bit-stream length. We develop an SC design technique which produces results that are accurate and have good MPP. The dissertation concludes with some ideas for future research.

# CHAPTER 1 Introduction

Stochastic computing (SC) is a computing paradigm that provides an alternative to computing with conventional binary numbers. Its distinguishing feature is that numbers are represented by random bit-streams that can be interpreted as probabilities. This unusual number representation scheme enables SC to perform low-cost, low-power and error-tolerant computing. SC has recently attracted the attention of researchers interested in applications such as decoding modern error-correcting codes, biomedical image processing, and neuromorphic networks. This chapter introduces SC and its applications. It also discusses the challenges that motivate our research.

### 1.1 Motivation

The steadily increasing density of integrated circuits (ICs) allows billions of components and complex applications to be packed into small, portable devices. At the same time, it introduces some new design challenges to deal with power and energy consumption. Consequently, a great deal of attention is being paid to low-power design<del>,</del> especially for battery-powered applications [27][54].

A growing applications area with very strict power budgets is the so-called Internet of Things (IoT). IoT refers to large networks of electronic devices with sensors, processors and their associated software embedded in physical objects like buildings and vehicles. Unlike conventional computing platforms that are directly accessible by users, such as desktop computers or smartphones, IoT devices are often deployed in physical environments that are hard to reach, a problem that heightens the importance of low power

Figure 1.1: An example of edge detection to convert (a) a greyscale image of a corridor with an obstacle into (b) a high-contrast image.

consumption [11] [25]. To illustrate, long lifetime water quality sensors in reservoirs, forest fire detectors, and chemical leakage detectors in rivers all require low-power designs. To be able to deploy them in large and noisy physical environments, these devices must be robust, and the cost per device must be very low [25].

Another class of extremely power-sensitive applications are electronic biomedical implants. Examples here include retinal implants for the visually impaired, heart-rhythm monitors, and nerve implants to help paralyzed people perform basic tasks. For instance, retinal implants acquire and process images to extract information that can be used by the brain. One such image-processing task is edge detection, which generates a high-contrast black-and-white image highlighting the boundaries or edges of objects. For visually impaired people who can only distinguish very bright from very dark features, this processed image can make obstacle detection, avoidance, and the like possible; see Figure 1.1.

The ability of massive parallelism to enhance performance at low cost is also important in biomedical devices like retinal implants for several reasons. A typical retinal implant chip contains a large array of sensors, one per pixel, and each sensor requires some processing capability, ideally a dedicated pixel processor [65][66]. As there may be thousands of pixels, the pixel processors must be tiny in size and have extremely low power needs. They should also be fast enough to process data or images in real-time. Figure 1.2 illustrates how edge detection can be performed by an array of pixel processors. For a certain standard edge-detection method (the Roberts cross algorithm [37]), a moving average of light intensity  $z_{i,j}$  is computed on a window of size  $2 \times 2$  surrounding each pixel  $x_{i,j}$  according to the relatively complex arithmetic formula

$$z_{i,j} = |x_{i,j} - x_{i+1,j+1}| + |x_{i,j+1} - x_{i+1,j}|$$

(1.1)

Figure 1.2: Edge detection using an array of pixel processors and a four-pixel window.

A small processor implementing Equation (1.1) and using conventional hardware designs is unlikely to meet the size and power constraints imposed by a retinal implant. However, as we will see later, a design based on stochastic computing can easily do so [3].

Since implantation of biomedical devices requires invasive surgery, they must have long lifetime and very small size [43]. The size requirement also renders high-capacity batteries to ensure long-term operation impractical. Moreover, because human tissues like the retina are very sensitive to temperature, if a biomedical implant dissipates too much power, vital organs can suffer heat damage. To avoid such problems, extremely low-power and small-size circuits are critical. In addition, implanted devices must be robust and insensitive to environmental noise [19].

Many approaches have been proposed to achieve some or all of the foregoing design goals, but each has its own limitations. For example, low-power semiconductor techniques, such as transistors with multiple threshold voltages and oxide thicknesses, reduce power consumption but they require special manufacturing processes that increase IC area and delay [84]. One promising technology that addresses all these issues is stochastic computing (SC), which is the subject of this dissertation. In SC, numbers are represented by random bit-streams which are interpreted as probabilities. For instance, the number 0.25 is represented by the bit-stream X = 0010100001000010 which contains four 1s and has length N = 16. If bits are randomly sampled in this bit-stream, then the probability of seeing a 1 in any position is 0.25. This probability is easily estimated by counting the number of 1s in X and dividing it by the bit-stream length N. As we will see, within the framework of SC, this unusual number representation scheme has the potential to produce small, low-power, low-cost, and error-tolerant circuits. Furthermore, these circuits can be built using standard digital logic manufacturing methods.

#### **1.2** Stochastic Computing

As noted above, SC operates on random bit-streams using conventional logic circuits; we will refer to such circuits as *stochastic circuits*. The data value associated with

a logic signal (wire) x in a stochastic circuit is the probability  $p_X$  of seeing a 1 on x, i.e., x's signal probability. If a stream X of random bits, called a *stochastic number* (SN), is applied to x in some N-bit time-frame (window) W, then X's *numerical value*  $p_X$  is defined to be the frequency of 1s in W. Hence, when X contains  $N_1$  1s,  $p_X$  is approximated by  $N_1/N$ , which we denote by  $\hat{p}_X$ . In general,  $\hat{p}_X \approx p_X$ , and the precision of this approximation tends to increase with N. For instance, when N is 4, 8, and 16, the bit-streams 0101, 01011010 and 1010011001010011 are some of the many possible representations of  $p_X = 1/2$ . Note that  $\hat{p}_X$  represents the measured value when N bits are collected, while  $p_X$  is the theoretical or "exact" value of interest. To approximate a bit-stream's value we can also sample some part of it. For example, if we reduce N from 16 to 8 bits, we change X from 1010011001010101 to 10100110, but  $p_X$  is unchanged. However, reducing Y =1001001101001010 from 16 to 8 bits introduces an error of |7/16 - 4/8| = 1/16.

SC can also process arbitrary (real) numbers if they are suitably approximated and scaled to lie in the unit interval [0, 1]. To handle signed numbers, it is common to interpret the numerical value of a bit-stream X as  $2p_X - 1$ , in which case the SN format is called

|              |                                 | Numerical value                |                                    | No. of bit-streams                                  |

|--------------|---------------------------------|--------------------------------|------------------------------------|-----------------------------------------------------|

| Bit-stream X | No. of 1s <i>N</i> <sub>1</sub> | Unipolar <i>p</i> <sub>X</sub> | Bipolar 2 <i>p<sub>x</sub></i> – 1 | with the same<br>numerical value                    |

| 000000       | 0                               | 0                              | -1                                 | 1                                                   |

| 000001       |                                 |                                |                                    |                                                     |

| 000010       | 1                               | 1/N                            | 2/N – 1                            | Ν                                                   |

| :            |                                 | 1//1                           | 2/// – 1                           | / 1                                                 |

| 100000       |                                 |                                |                                    |                                                     |

| :            | •••                             | :                              | :                                  | :                                                   |

| 000111       |                                 |                                |                                    | $N(N-1)\cdots (N/2+1)$                              |

| :            | N/2                             | 0.5                            | 0                                  | $\frac{N(N-1) - (N/2 + 1)}{N/2 (N/2 - 1) \cdots 1}$ |

| 111000       |                                 |                                |                                    | $N/2 (N/2 - 1) \cdots 1$                            |

| :            | •••                             | :                              | :                                  |                                                     |

| 111111       | N                               | 1                              | 1                                  | 1                                                   |

Table 1.1: Numerical values of an *N*-bit bit-stream *X* in the unipolar and bipolar formats.

*bipolar*, and the effective number range becomes [-1, 1]. The basic format in which X's numerical value is taken to be  $p_X$  is called *unipolar*. Table 1.1 summarizes the numerical values of unipolar and bipolar SNs for different bit-streams of length N. For instance, the bit-stream 000...001, in which there is only one 1, has the value 1/N in unipolar format. On the other hand, the same bit-stream is interpreted as 2/N - 1 if it is bipolar. Table 1.1 also shows that SC has a highly redundant encoding format that allows multiple bit-streams to represent the same  $p_X$  value. To illustrate, in addition to 000...001, the bit-streams 000...010, 000...100, ..., and 100...000 also have the same numerical values, 1/N and 2/N - 1, in the unipolar and bipolar formats, respectively.

Simple logic operations applied to bit-streams can perform useful arithmetic operations on their probability values. Figure 1.3a-b shows stochastic circuits for unipolar multiplication and addition. The two-input AND gate performs the multiplication  $p_{X_1} \times p_{X_2}$  on two *N*-bit bit-streams  $X_1$  and  $X_2$  in *N* clock cycles because the output *z* is 1 if and

Figure 1.3: A selection of components for stochastic computing: (a) unipolar multiplier, (b) unipolar and bipolar scaled adder, (c) bipolar multiplier, and (d) bipolar negater.

only if both  $x_1$  and  $x_2$  are 1 in the same cycle. Note that for high accuracy, the input bitstreams  $X_1$  and  $X_2$  must be statistically independent (uncorrelated) and sufficiently long to provide acceptable precision, issues we will discuss in detail later.

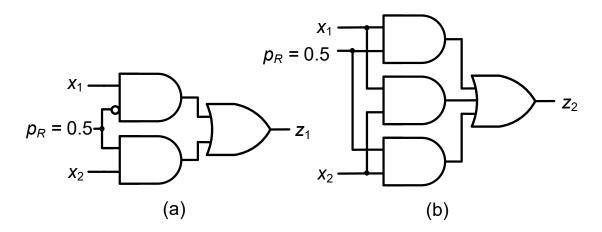

Addition is implemented by a two-way multiplexer (MUX) in the scaled form  $0.5(p_{X_1} + p_{X_2})$  which ensures that the sum always lies in the probability interval [0, 1]. The idea behind the MUX-based adder is that the output *z* randomly receives half its bits from  $X_1$  and half from  $X_2$ , so the number of 1s at *z* is the average number of 1s in  $X_1$  and  $X_2$ . The selection of the input bits to be transferred to the output is controlled by applying to the MUX's select input a stochastic number *R* of constant value  $p_R = 0.5$ , i.e., a purely random sequence of 0s and 1s. *R* can also be seen as the source of the scaling factor in the sum.

In the bipolar format, an XNOR gate performs multiplication (Figure 1.3*c*), while a MUX continues to act as a scaled adder. The output *z* of the MUX is then the scaled sum  $2p_z - 1 = 0.5((2p_{X_1} - 1) + (2p_{X_2} - 1))$ . Bitwise inversion of an SN *X* via a NOT gate (Figure 1.3*d*) negates *X*'s numerical value in the bipolar format thus:  $(2p_F - 1) = -(2p_{X_1} - 1)$ . Subtraction is easily implemented by combining a multiplexer and a NOT gate. In Figure 1.3 (and in the rest of this dissertation), circuit wires and the signals (Boolean variables) they carry are denoted by small letters *x*, *y*, *z*,...; bit-streams or SNs are denoted by capital letters *X*, *Y*, *Z*,..., and their numerical values are denoted by  $p_X$ ,  $p_Y$ ,  $p_Z$ , etc.

Number conversion circuits are necessary at any interface between standard binary circuits and stochastic circuits. Figure 1.4*a* shows a typical binary-to-stochastic converter that generates a 2<sup>*k*</sup>-bit SN *X* with the value  $p_X = B/2^k$  from a *k*-bit binary integer *B*. This converter is called a *stochastic number generator* (SNG). An SNG contains a comparator that compares *B* with a random number and generates a 1 when *B* is larger than the random number. SC typically requires many randomness sources that can produce independent bit-streams with prescribed probability values. A simple binary counter (Figure 1.4*b*) converts

Figure 1.4: Number converters (a) binary-to-stochastic and (b) stochastic-to-binary.

an SN to a conventional binary number as the numerical value of the SN depends solely on the number of its 1s. The bit-stream length *N* is selected based on accuracy and precision considerations. If *N* is chosen to be  $2^k$  for some *k*, as is often the case, then *X* is considered to have *k*-bit precision, i.e. the same precision as a *k*-bit binary number *B*. For instance, bitstreams 0101, 01011010 and 1010011001010011 are three of the many possible SNs representing X = 0.5, with 2-, 3- and 4-bit precision, respectively. This notion of precision means that  $2^k$  bits suffice for *X* to represent *B* exactly.

To achieve *k*-bit precision, bit-streams of length  $2^k$  or more are required, so high precision SC is difficult to achieve and requires long computational times. This fact, as well as the rapidly decreasing cost and increasing speed of conventional binary circuits, caused a loss of interest in SC shortly after it was first proposed back to 1960s [30][69][76]. A few attempts of building stochastic computers were made around that time, and they revealed the aforementioned drawbacks of SC.

However, SC has recently made a come-back as an attractive choice for applications requiring very small, low-power and low-cost hardware [2]. Several studies also have shown the success of applying SC to tasks such as image processing [3][57]. Because of the simplicity of SC computing units, massive parallelism becomes feasible. For example, we can simply use a large number l of AND gates to speed up multiplication l times and still have a very small multiplier. Massive parallelism of this kind makes SC extremely suitable for applications performing the same computation iteratively with different groups of inputs such as the retinal implants discussed earlier. Using SC, the

implant's many pixel processors can be made so small that even when they are replicated thousands of times, they have relatively low power consumption.

Another application that can benefit from SC's massive parallelism is the design of bio-inspired neuromorphic networks [15][16][46][77]. These are special-purpose computing systems that can potentially contain enormous numbers of small, highly interconnected processors called neurons. Messages are passed between the neurons, and a neuron is activated when a combination of its inputs exceeds some threshold [78]. All the neurons have essentially the same structure, so neuromorphic networks also tend to repeat the same computation on many different neurons with different message sets. Since the neurons must be small and low-power, SC is a good candidate for implementing large-scale neuromorphic networks. Another fact that make SC suitable to neuromorphic networks is the similarity between biological neural signals and stochastic numbers. Biological neurons communicate by means of noisy voltage spikes which loosely resemble bit-streams [81]. Furthermore, the frequency or rate of the spikes in a spike train encodes information (although the precise encoding scheme is not understood). Hence, because of the way it encodes information and its ability to realize massive parallelism, SC has great potential for building circuits that connect natural and artificial neural networks.

The first of the recent wave of successful applications of SC was to decode lowdensity parity-check (LDPC) codes, a class of error-correcting codes that enable data to be transmitted over a noisy transmission channel at rates close to the theoretical maximum (the Shannon limit) [33]. Decoding LDPC codes requires many complex probability computations, which make it difficult to implement in practice. Equation (1.2) shows one such computation called node updating.

$$p_Z = \frac{p_X \times p_Y}{p_X \times p_Y + (1 - p_X) \times (1 - p_Y)}$$

(1.2)

Figure 1.5 shows a sequential stochastic circuit that computes the arithmetic function defined by Equation (1.2) [67]. This small component is called an update node and was

Figure 1.5: Update node for LDPC decoder.

designed for an LDPC decoder employing SC. An equivalent circuit using conventional (weighted-binary) arithmetic circuits contains hundreds of gates, as opposed to just a few gates in the stochastic implementation. Similarly, a stochastic edge detector realizing Robert cross formula of Equation (1.1) is much smaller than an equivalent circuit using conventional arithmetic circuits; it will be investigated in detail in Section 2.6.

SC can also tolerate soft errors caused by environmental noise. Because of its inherently redundant encoding scheme which we discussed earlier, soft errors of the bit-flip type have little effect on the value of an SN. For example, a single bit-flip occurring in an *N*-bit SN changes the output value by 1/N, a relatively small error, whose significance diminishes as *N* increases. Furthermore, if the errors are bidirectional, e.g., if 0-to-1 and 1-to-0 bit-flips are equally likely, then the errors tend to cancel one another. This suggests that stochastic computing can outperform binary in certain applications [21][22].

The main advantages of SC can be summarized as follows. Mainly because of its pseudo-random number representation, SC enables small and low-power computing units using standard logic circuits. It is also extremely suitable for applications that need massive parallelism because the cost of the computing units is so low. Their inherently redundant number encoding format makes SNs less sensitive to environmental noise. On the other hand, SC has some disadvantages which we consider in the next section.

#### **1.3 Research Challenges**

Despite its recent successful applications, SC has several features that limit its usefulness. For instance, the need for many number conversion circuits offsets the advantage of SC's small computing units [28][67]. SC's long computational time and precision limitations make SC impractical to use for general-purpose computation [8]. Bit-stream length tends to grow exponentially as precision requirements increase. Inaccuracies caused by random bit fluctuations [31], and awkward scaling requirements [31] also make SC less desirable.

SC requires statistically independent or uncorrelated inputs to generate accurate results [23][31]. In other words, the bit-patterns of SNs that are being processed together should be unrelated. The effect of correlation on accuracy is illustrated by the example in Figure 1.6. The input bit-streams to the AND-gate stochastic multiplier all have the same numerical value  $p_{X_i} = 0.5$ . In Figure 1.6*a*, the two input streams  $X_1$  and  $X_2$  have very different bit-patterns reflecting a uniform, random-like distribution of their bits; in this case,  $X_1$  and  $X_2$  are intuitively uncorrelated. In Figure 1.6*b*, on the other hand,  $X_1$  and  $X_2$  have identical bit-patterns, implying they are highly correlated. If  $x_1 = 0$  (1), then  $x_2 = 0$  (1) and the input bit-patterns 01 and 10 never occur; hence,  $p_{\bar{X}_1\bar{X}_2} = p_{X_1\bar{X}_2} = 0.5$  and  $p_{\bar{X}_1X_2} = p_{X_1\bar{X}_2} = 0$ . The output probability  $p_Z$  is 0.25 for Figure 1.6*a* and 0.5 for Figure 1.6*b*. Thus, instead of the accurate result  $p_Z = p_{X_1} \times p_{X_2} = 0.25$ , Figure 1.6*b* produces a highly inaccurate value  $p_Z = 0.5$ . SNs that have become unduly correlated are commonly rerandomized or *de-correlated* by converting them back to binary numbers and regenerating

Figure 1.6: Stochastic multiplication with (a) uncorrelated inputs, and (b) highly correlated inputs.

independent versions of the SNs by means of expensive number converters like those in Figure 1.4. The impact of (de) correlation on accuracy has received little attention, and designing efficient stochastic circuits that achieve guaranteed accuracy levels in the presence of correlation is by no means easy.

Error tolerance is another aspect of SC which is not well understood; SC is known for its tolerance to soft errors, but a full and systematic analysis of this property has not been done. Yet another SC's research challenge is formalizing the design requirements of stochastic circuits. For example, the circuit in Figure 1.5 computes a complex and useful arithmetic function, but systematic ways to design sequential stochastic circuits like it are unknown. It is also unclear, for example, whether other stochastic circuits exist that can perform the same arithmetic function as that of Figure 1.5 with greater accuracy or at lower cost. Another problem of SC is that while addition, subtraction and multiplication have simple and well-known SC implementations, this is not true for an operation as basic as division. As a result, a stochastic divider is conspicuously absent from the basic SC component set in Figure 1.3, and division is usually avoided or approximated in SC design. These issues all suggest that finding a general theoretical framework for designing stochastic circuits is essential for achieving low-cost and accurate SC designs.

### **1.4 Dissertation Outline**

When designing computation circuits, many requirements and constraints need to be considered: power consumption, area cost, computation speed or run-time, and the accuracy of the results. Because stochastic circuits are constructed from simple logic circuits, they are usually small and low-power. Computation time is related to the required precision, but very high precision results are not always necessary. Furthermore, stochastic circuits can operate at very high clock speed, which can mitigate the computing time problem. Achieving results of acceptable accuracy is probably the most important and least understood aspect of SC. Accuracy is therefore the main focus of this dissertation, which is divided to two major parts: (1) accuracy analysis and (2) accurate design. Chapters 2 and 3 cover the analysis of factors affecting SC's accuracy, while Chapters 4-6 discuss the design of accurate stochastic circuits.

Chapter 2 introduces an analysis framework to evaluate the impact of soft errors on stochastic circuits. This framework is based on a well-developed probabilistic transfer matrix (PTM) algebra [53] which is well suited to analyzing signal probabilities in SC. A PTM is a matrix in which element  $E_{ij}$  is a real number in the interval [0, 1] that denotes the conditional probability of producing output *j* in response to input *i*. As discussed earlier, correlation among interacting bit-streams is also a key factor affecting accuracy. We use PTM algebra to analyze the impact of correlation on SC accuracy in Chapter 3.

Next, we move to the design of accurate stochastic circuits. Chapter 4 presents a new way of classifying stochastic circuits, namely the stochastic equivalence class (SEC). Based on the SEC concept, we develop a general stochastic circuit synthesis method and area-cost optimization algorithms. These algorithms can reduce the area cost of stochastic circuits while keeping their accuracy unchanged. Chapter 5 reviews known stochastic division methods and presents a new and more efficient divider design. This design uses standard stochastic number representations and has better accuracy than previous designs. We tackle the issue of inaccuracy due to random fluctuations in Chapter 6. We present a general design method that generate exact results when bit-stream lengths are properly chosen. This method also addresses the reduction of SC's long computation times. Finally, Chapter 7 draws some conclusions and discusses some directions for future work.

# CHAPTER 2 Accuracy and Soft Errors

The previous chapter pointed to accuracy as one of the major challenges facing SC. The factors affecting SC negatively including environmental noise, fluctuation of its sources of randomness, and correlation among interacting SNs. This chapter addresses the impact on accuracy of soft errors due to noise and random fluctuations. We first develop a mathematical framework for the analysis in terms Bernoulli random variables (RVs) and probabilistic transfer matrices (PTMs). Bernoulli RVs are widely employed in probability studies [80] and are well-suited to analyzing SN sources. PTMs are specifically intended for analyzing the probabilistic properties of logic circuits such as reliability or soft-error rate [53]. We present a case study in real-time image processing, which shows that stochastic circuits can outperform conventional ones under severe error conditions. The material presented here has been published in [22] and includes contributions by Armin Alaghi.

### 2.1 Soft Errors

Non-deterministic behavior is becoming common in digital circuits implemented using conventional CMOS transistors or novel nanotechnologies that can potentially replace CMOS [12]. Because of their small physical size, these circuits are easily affected by manufacturing defects and by transient errors due to environmental noise called soft errors, both of which tend to be probabilistic in nature. For example, carbon nanotube fieldeffect transistors (CNFETs), an emerging alternative to CMOS, exhibit behavioral variations that are difficult to identify and control [79]. Methods of designing circuits that tolerate errors are also of increasing interest. Von Neumann took the first steps in designing reliable circuits using unreliable switches in the 1950s [82]. Since then, many error-tolerant design techniques have been proposed, ranging from error-correcting codes [59], to replication of hardware, software and/or data [49][71]. Most of these approaches impose high circuit overhead, and tend to be used only in the most cost-insensitive applications.

The ability of stochastic circuits to tolerate soft errors has long been recognized [31], but it has never been thoroughly analyzed. Under extremely noisy conditions, this property may even allow stochastic circuits to generate more accurate results than conventional circuits. In [74], a soft-error analysis of SC circuits is carried out which, however, is limited to bit-flips occurring in the circuit's input data; the stochastic circuits themselves are assumed to be fault- or error-free. In this chapter, we attempt to provide a more general error analysis for stochastic circuits, especially in the presence of high error rates such as are encountered in avionics or spacecraft instrumentation [32].

### 2.2 Probability Model

To obtain a better understanding of SC, especially with regard to its error behavior, probability theory is useful. A stochastic number X is a bit-stream carrying a probability value  $p_X$  where 1 denotes success and 0 denote failure. A stochastic number can therefore be viewed as a set of samples from a real-valued random variable (RV) with a Bernoulli distribution in which the probability of success is  $p_X$  [80]. Since probabilistic behavior can be easily modeled and analyzed in terms of Bernoulli RVs, we now use these RVs to give a formal definition of a stochastic number that abstracts away from bit-stream formatting issues: a stochastic number X is a Bernoulli random variable with parameter  $p_X$ .

When dealing with RVs, we usually need to sample them in order to estimate their values. This sampling process is, in fact, a very basic form of stochastic computing. For instance, assume that the AND-gate multiplier of Figure 1.3*a* has two input SNs X and Y with known values  $p_X$  and  $p_Y$ , but the output is an SN Z of unknown value  $p_Z$ . Stochastic computation with this circuit involves generating samples for X and Y and measuring the

success rate at *z*, and thus estimating  $p_Z$ . The expected rate of success at *z* can be calculated by the expected value operator denoted  $\mathbb{E}[Z]$ . Consequently,

$$p_Z = \mathbb{E}[Z] = \mathbb{E}[X \times Y] = \mathbb{E}[X] \times \mathbb{E}[Y] = p_X \times p_Y$$

assuming X and Y are independent RVs. For example, if  $p_X = 0.2$  and  $p_Y = 0.3$ , then  $p_Z = 0.06$ , which is the expected rate of success at z. In practice, the success rate is affected by random fluctuations of the data, and usually has a different value  $\hat{p}_Z$ , which we refer to as the estimated value, in contrast with the exact value  $p_Z$ . The estimated value  $\hat{p}_Z$  is obtained by sampling the circuit/RV N times and recording the number  $N_1$  of 1s appearing at the output; this yields  $\hat{p}_Z = N_1/N$ . For example, if the RV Z, with the expected value  $p_Z = 0.3$ , is sampled 8 times, one possible outcome is 01100000, and the resulting estimate is  $\hat{p}_Z = 2/8 = 0.25$ .

In general,  $\hat{p}_Z$  can be any of the  $2^N$  different bit-streams derived from random sources, which allows  $p_Z$  and  $\hat{p}_Z$  to differ, sometimes significantly, from one another. This difference between  $p_Z$  and  $\hat{p}_Z$  is considered to be an error caused by randomness in the bit-stream representation of  $p_Z$ . Such random-fluctuation errors are usually measured by the mean square error (MSE)  $E_Z = \mathbb{E}[(\hat{p}_Z - p_Z)^2]$ . In the case of the Bernoulli RV's of interest here, we have the MSE of the RV Z [80]

$$E_Z = p_Z (1 - p_Z) / N (2.1)$$

This equation implies that the MSE of an SN estimate can be reduced by increasing the number of samples i.e., the bit-stream length N. Also note that  $E_Z$  is a function of  $p_Z$  and N only, implying that no matter what the circuit is (whether the AND of Figure 1.3a or any other circuit), once the expected rate of success  $p_Z$  at the output is calculated, we can use Equation (2.1) to calculate its MSE.

Besides the random fluctuations inherent in the selection of a particular bit-stream to represent Z in a stochastic circuit C, various non-deterministic physical phenomena

Figure 2.1: Circuit models for a stochastic multiplier with a bit-flip error *e* affecting its output: (a) internal or built-in error, and (b) externally injected error.

associated with C itself and its environment affect the sampling process and distort the expected values of Z. It is convenient to lump such effects into a bit-flip error e that occurs with some probability  $p_e$ . For example, it is often assumed in the literature [10] that e causes bit-flips in Z, which affect 0s and 1s with equal probability  $p_e$ . Whatever the error behavior assumed, two basic questions should be addressed: How do we model the impact of e on z, and how do we introduce e into a previously error-free stochastic circuit C? First, we assume the error e to be a Bernoulli RV with parameter  $p_e$  (the bit-flip rate), so it can be treated like another SN associated with C. Given this assumption, the circuit's fault-free output z then changes to an erroneous function  $z^*$ , as illustrated in Figure 2.1a for the ANDgate stochastic multiplier. For simulation purposes, it is convenient to have a mechanism for injecting the error in a way that flips the normal signal z with probability  $p_e$ , resulting in the erroneous output  $z^*$ . Figure 2.1b shows how to do this by inserting an XOR gate with input e into C's output line. For example, a bit-flip rate of  $p_e = 0.05$  with input values  $p_X =$ 0.2 and  $p_Y = 0.3$  changes the expected success rate at the output of the AND multiplier from 0.06 to 0.104. An analytical method of calculating the expected value  $p_{Z^*}$  and its MSE will be developed later.

In addition to random fluctuations and soft errors, the accuracy of SC can also be affected by correlated SNs. For instance, the AND gate shown in Figure 1.3*a* will not be an accurate multiplier if its inputs X and Y are correlated. Since interacting signals are not independent,  $\mathbb{E}[X \times Y] \neq \mathbb{E}[X] \times \mathbb{E}[Y]$  and the resulting SN Z has the property

$$p_Z = \mathbb{E}[Z] = \mathbb{E}[X \times Y] \neq \mathbb{E}[X] \times \mathbb{E}[Y] = p_X \times p_Y$$

The correlation between X and Y, determines the corresponding MSE. For example, if X and Y are the same bit-stream, they are highly positively correlated and the MSE will be  $(p_X^2 - p_X)^2$ . Such correlation errors have been investigated in [23] and will be discussed in detail later in Chapter 3.

### 2.3 Probabilistic Transfer Matrices (PTMs)

A convenient tool for analyzing the probabilistic behavior of logic circuits is the probabilistic transfer matrix (PTM) and its associated algebra [53]. PTMs were introduced at the University of Michigan to analyze the reliability of conventional logic circuits. Although their practical use may be limited by the fact that PTM size grows exponentially with circuit size, this is less of a problem with stochastic circuits, however, which typically consist of just a handful of gates.

In the PTM formulation, the behavior of an *n*-input *m*-output combinational circuit is represented by a  $2^n \times 2^m$  zero-one matrix whose rows correspond to all input combinations and whose columns correspond to all output combinations. This matrix, which is referred to an *ideal transfer matrix* (ITM), is a slightly modified truth table. For instance, a two-input AND gate has the ITM

$$J_{\rm AND} = \begin{bmatrix} 1 & 0\\ 1 & 0\\ 1 & 0\\ 0 & 1 \end{bmatrix}$$

(2.2)

where the rows correspond to xy = 00,01,10,11 and the columns correspond to z = 0,1. A general PTM is obtained from the ITM by allowing the entry in row r and column c to become any real number in the interval [0, 1] that denotes the conditional probability of producing output c in response to input r. In the AND gate's ITM  $J_{AND}$  shown in Equation (2.2), the top row tells us that in response to the input xy = 00, the AND produces output z = 0 with probability 1, and output z = 1 with probability 0.

Another basic arithmetic operation, addition, must be done approximately (by an OR gate, for example) or else the result must be scaled to ensure that it lies between 0.0 and 1.0, as required for probabilities. A common solution is the scaled addition  $p_Z = 0.5(p_{X_1} + p_{X_2})$  performed by the multiplexer of Figure 1.3*b*, whose ITM is

$$M_{\rm MUX} = \begin{bmatrix} 1 & 0\\ 0.5 & 0.5\\ 0.5 & 0.5\\ 0 & 1 \end{bmatrix}$$

(2.3)

Observe that the multiplexer's select input carries a constant SN R with probability value 0.5 that affects the entries, but not the size, of  $M_{MUX}$ . Because R is an SN, it must be generated by a stochastic number generator (SNG) like that of Figure 1.3c and so has a significant impact on hardware cost.

By choosing suitable probability values, PTMs can be constructed to represent a remarkably wide range of error scenarios [53]. For example, the effect of a bit-flip error e with rate  $p_e$  on the output of the AND gate model in Figure 2.1a, is represented by the PTM

$$M_{\rm AND} = \begin{bmatrix} 1 - p_e & p_e \\ 1 - p_e & p_e \\ 1 - p_e & p_e \\ p_e & 1 - p_e \end{bmatrix}$$

(2.4)

$$\begin{bmatrix} p_{e0} & 1 - p_{e0} \\ p_{e1} & 1 - p_{e1} \\ p_{e2} & 1 - p_{e2} \\ 1 - p_{e3} & p_{e3} \end{bmatrix} \begin{bmatrix} 0 & 1 \\ 1 & 0 \\ 0 & 1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(a) (b) (c) (d)

Figure 2.2: Representative PTMs: (a) NAND gate with four distinct input-dependent bitflip error rates, (b) NAND gate with its first input stuck-at-1, (c) fanout wiring network with two output branches, and (d) swap or crossover gate that switches the order of two wires.

Input-dependent bit-flips can be modeled by associating a different  $p_e$  value with every row. Observe that a PTM must satisfy the stochastic requirement that all entries in each row add up to 1, and that the ITM is just the PTM for the error-free case.

Circuit PTMs can be manipulated by means of a well-defined algebra which loosely resembles linear algebra. Every element of a circuit *C* is representable by a PTM that describes *C*'s logic function and error status; see Figure 2.2. PTMs can be combined in two basic ways corresponding to the two basic circuit interconnection structures, series and parallel. The PTM of two circuits  $C_1$  and  $C_2$  connected in series is the ordinary matrix product of their PTMs, i.e.,  $M_1 \times M_2$ . The PTM of two circuits connected in parallel is the tensor product of the PTMs, denoted  $M_1 \otimes M_2$ . In the tensor product, each element of the first matrix  $M_1$  is multiplied by the entire second matrix  $M_2$ , which leads to rapid growth in matrix size. A wire corresponds to a 2 × 2 PTM; its ITM case is simply the 2 × 2 identity matrix. A signal is represented by a 1 × 2 row vector  $[p_0 \ p_1]$ , where  $p_0$  and  $p_1$  are the probabilities of the signal being 0 and 1, respectively. Signal vectors may be treated as a special kind of PTM, and can be manipulated with the same basic PTM operations.

The PTM of an SN X is processed like a signal vector because we treat it as an RV with a Bernoulli distribution and a parameter  $p_X$  denoting the expected probability that a bit of X is 1. For PTM analysis, X is written as the 2-element row vector  $M_X = [1 - p_X \ p_X]$ . The joint probability distribution of two uncorrelated SNs X and Y is given by their tensor product  $M_X \otimes M_Y$ , which evaluates to the 4-element vector

$$M_{XY} = M_X \otimes M_Y$$

=  $[(1 - p_X)(1 - p_Y) \quad (1 - p_X)p_Y \quad p_X(1 - p_Y) \quad p_Xp_Y]$  (2.5)

The entries of  $M_{XY}$  are the probabilities of the input combinations  $x_1x_2 = 00,01,10,11$ . For example, consider again the faulty AND-gate multiplier of Figure 2.1*a* with  $p_X = 0.2$ ,  $p_Y = 0.3$ , and  $p_e = 0.05$ . To determine the probability of getting a 1 at the gate's output, the input

vectors, namely,  $M_X = \begin{bmatrix} 0.8 & 0.2 \end{bmatrix}$  and  $M_Y = \begin{bmatrix} 0.7 & 0.3 \end{bmatrix}$  are formed first. These vectors are then combined via the tensor product of Equation (2.5)

$$M_{XY} = M_X \otimes M_Y = \begin{bmatrix} 0.56 & 0.24 & 0.14 & 0.06 \end{bmatrix}$$

(2.6)

to give the probabilities associated with all four possible input combinations. The resulting input vector is multiplied by the PTM of the error-affected AND gate to obtain the circuit's output vector.

$$M_{Z^*} = M_{XY} \times M_{\text{AND}} = \begin{bmatrix} 0.56 & 0.24 & 0.14 & 0.06 \end{bmatrix} \times \begin{bmatrix} 0.95 & 0.05 \\ 0.95 & 0.05 \\ 0.95 & 0.05 \\ 0.05 & 0.95 \end{bmatrix} = \begin{bmatrix} 0.896 & 0.104 \end{bmatrix}$$

From this, we conclude that  $p_{Z^*}$ , i.e., the probability of getting a 1 at  $z^*$ , is 0.104. Note that the PTM  $M_{AND}$  of the AND gate implicitly incorporates the bit-flip error, so there is no need for the XOR gate of Figure 2.1*b*, as is also the case in Equation (2.4).

# 2.4 Impact on Stochastic Numbers

Consider a stochastic number X with the expected value  $\mathbb{E}[X] = p_X$ . In a noisy environment, if X is affected by bit-flip error e with expected value  $p_e$ , the SN becomes  $X^* = X \oplus e$ . We therefore have

$$p_{X^*} = \mathbb{E}[X^*] = p_X + p_e(1 - 2p_X) \tag{2.7}$$

Besides the expected value of  $X^*$ , we are interested in  $E_{X^*}$ , the mean square error of  $X^*$ , which denotes the average error occurring in a stochastic circuit, i.e., the average difference between the estimated value  $\hat{p}_{X^*}$  and the exact value  $p_X$ .

$$E_{X^*} = \mathbb{E}[(\hat{p}_{X^*} - p_X)^2]$$

Note that  $E_{X^*}$  reflects both the random fluctuations of the bit-stream representation and the error *e* due to bit-flips. As mentioned earlier,  $X^*$  is a Bernoulli RV defined by its expected value, so using only Equation (2.7), we should be able to find  $p_{X^*}$  and hence  $E_{X^*}$  analytically. Assuming the estimated value  $\hat{p}_{X^*} = 1/N \sum_{i=1}^N X_i^*$  obtained by summing N independent samples of  $X^*$ , we obtain

$$E_{X^*} = \mathbb{E}[(\hat{p}_{X^*} - p_X)^2] = \mathbb{E}[\hat{p}_{X^*}^2 + p_X^2 - 2p_X\hat{p}_{X^*}]$$

$$= \mathbb{E}[\hat{p}_{X^*}^2] + \mathbb{E}[p_X^2] + \mathbb{E}[-2p_X\hat{p}_{X^*}]$$

$$= \frac{N^2 p_{X^*}^2 + N p_{X^*} (1 - p_{X^*})}{N^2} + p_X^2 - 2p_X p_{X^*}$$

$$= (p_{X^*} - p_X)^2 + \frac{p_{X^*} (1 - p_{X^*})}{N}$$

(2.8)

The first term in Equation (2.8) is the difference between the expected values of X and X<sup>\*</sup>, and its only cause is the bit-flip *e*. The second term is a random-fluctuation error that diminishes with increasing *n*. We can re-write  $E_{X^*}$  in terms of  $p_X$  and  $p_e$  by substituting Equation (2.7) into Equation (2.8) thus:

$$E_{X^*} = p_e^2 (1 - 2p_X)^2 + \frac{1}{N} \left[ p_X (1 - p_X) + p_e (1 - p_e) \left( 1 - 4p_X (1 - p_X) \right) \right]$$

Observe that the MSE error depends on both  $p_X$  and  $p_e$ . For sufficiently large N,  $E_{X^*}$  becomes 0 when  $p_X = 1/2$ , while it becomes  $p_e$  for  $p_X = 1$ .

In a similar way, we can analyze the effect of bit-flip errors on conventional (nonstochastic) binary numbers. An *m*-bit binary number *B* affected by independent and identically distributed bit-flips on each bit becomes  $B^*$ , which can potentially be any *m*-bit number with some probability. The error of  $B^*$  and its probability of occurrence depend on the number of bit-flips  $m_{bf}$ . To find the MSE  $E_{B^*}$  in this case, we calculate the weighted average error over all possible  $B^*$  values.

Figure 2.3: MSE of a stochastic and a binary number in the presence of bit-flips calculated using analytical and simulation methods: (a) for different values of  $p_e$ , and (b) for different values of  $p_X$ .

$$E_{B^*} = \sum_{B_i^*=0}^{2^m} (B_i^* - B)^2 p_e^{m_{bf}} (1 - p_e)^{m - m_{bf}}$$

Using the above equations, we compare the effect of bit-flips on a 5-bit binary number and an SN of length 32 whose precision is also 5 bits. Figure 2.3*a* shows the MSEs  $E_{X^*}$  and  $E_{B^*}$  at different bit-flips rates. Initially, the SN has a higher error due to its random fluctuations. However, as  $p_e$  increases, SN outperforms the binary number with respect to error tolerance. Figure 2.3*b* shows the MSEs  $E_{X^*}$  and  $E_{B^*}$  at different values of  $p_X$ ; the MSEs in this case are averaged over several bit-flip rates ranging from  $p_e = 0.001$  to 0.25. As can be seen,  $E_{X^*}$  is approximately 50% less than  $E_{B^*}$ . These analytical results are also confirmed in Figure 2.3 by Monte Carlo simulation.

#### 2.5 Impact on Stochastic Circuits

A key feature of our error analysis is the use of PTMs to estimate the impact of errors on stochastic behavior. PTMs can be used to calculate the probability distribution of all output combinations of a stochastic circuit *C*. Given specific input signal probabilities, the input vector is multiplied by the PTM of the circuit *C* to obtain the output probabilities.

For example, consider again the AND gate Figure 1.3*a* which multiplies two SNs  $p_X$  and  $p_Y$ , and has output error  $p_e$ . Generalizing Equation (2.6) gives the 1 × 4 input vector

$$M_{XY} = [(1 - p_X)(1 - p_Y) \quad (1 - p_X)p_Y \quad p_X(1 - p_Y) \quad p_Xp_Y]$$