# **Architecting Persistent Memory Systems**

by

Aasheesh Kolli

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2017

**Doctoral Committee:**

Associate Professor Thomas F. Wenisch , Chair Associate Professor Luis Ceze Professor Peter M. Chen Assistant Professor Karthik Duraisamy Associate Professor Satish Narayanasamy Aasheesh Kolli

akolli@umich.edu

ORCID iD: 0000-0001-5355-5542

© Aasheesh Kolli 2017

To Venkata Subbamma, my nayanamma, Madan Mohan Rao, my tathayya, and

Krishnamurthy, my mavayya.

### ACKNOWLEDGEMENTS

My PhD experience was full of ups and downs, it was rarely flat. For all the fun times when bugs were solving themselves, reviewers were increasing their scores, and papers were getting accepted, there were just as many, if not more, dark times when papers were getting rejected, Reviewer-C was being unreasonable, and I was doubting myself. However, the many wonderful people in my life made the dark times surmountable and the fun times truly memorable and I'd like to express my deepest gratitude to them.

I would first like to thank my parents, Ravi Kumar and Nagamani, and my sister, Sahithi, for their unconditional love, for encouraging me to pursue my dreams, and for making sure that I never had to worry about anything other than achieving my goals. My father is an educator and my mother is a computer scientist, so, looking back, its not very surprising that I chose to get a PhD in computer science. Thanks also to my uncle and aunt, Subbarao and Krishna, for helping me immigrate to the US. Immigrating to the US unlocked opportunities to me that were not available to many of peers back in India.

This thesis would obviously not have been possible without the mentorship from my advisor, Thomas Wenisch. Tom's technical acumen, generosity with time, and irrepressible enthusiasm made working with him an absolute blast. I will forever be indebted to him for all that I have learnt from him. When I was a confused undergrad wondering what to do next, several people helped me realize that I want to earn a PhD. Without them, I would not have even applied to a PhD program. My cousins, Vamsi, Prabha, Srihari, and Sowjanya inspired me by example and with their work ethic. Rajeev Balasubramonian generously offered me an internship in the UtahArch lab at the University of Utah and helped me gain necessary technical skills. During the internship, I learnt about the life a grad student from Rajeev's grad students Nil, Manu, Kshitij, Ani, and Manju.

I worked closely with Peter Chen and Satish Narayanasamy during my time at Michigan. Pete's critical analysis of my work and patient answers to all my questions, about work or life, were instrumental in me having a fulfilling PhD experience. Satish brought a programmer-centric perspective to my research which markedly improved the quality of my work. Satish also greatly helped me navigate the challenging waters of teaching an undergraduate course with over five hundred students. I would also like to thank Luis Ceze and Karthik Duraisamy for serving on my dissertation committee and their invaluable feedback on my dissertation.

I was fortunate to work with many amazing collaborators, Ali Saidi, Steven Pelley, Vaibhav Gogte, Stephan Diestelhorst, Joe Izraelevitz, Jeff Rosen, Andreas Hansson, Dhruva Chakrabarty, and Terence Kelly, who helped me formulate new research projects, debug code, write papers, and deal with reviewers.

Thanks to all of my lab mates and department friends, Faissal Sleiman, Neha Agarwal, Richard Sampson, Prateek Tandon, Akshitha Shriraman, Amlan Nayak, David Meisner, Andrew Lukefahr, Nilmini Abeyratne, Shaizeen Aga, Mehrzad Samadi, and David Devecsery, who assisted me with my projects, brainstormed ideas with me, listened to my problems over coffee, gave me advise, and attended my many (bad) practice talks.

A special thanks to my cousins Bobby and Sireesha, for helping me get my first laptop and my first car, the two best purchases I have made in my life.

I would also like to thank all my friends who made life in Ann Arbor an absolute pleasure; Shruti, for all the half-eaten cookies, kitchen runs, and impromptu conversations; Vimal, for all the parties, board games, and introducing me to Ann Arbor Ultimate; Shamitha, for sharing my interests in whiskey, politics, and philosophy; Miloni, for your genuineness, sympathetic ear, and for hosting me on my trips to California; Shankar, for being my tolerant roommate; Navneet Sarathy, for all the jokes and fun conversations; Daya, Ankit, Gaurav, Abhay, Divya, and Ritesh, for all the parties, tea, and card games; Mike, Ben, and Biruk, for all the basketball games.

# TABLE OF CONTENTS

| DEDICATION               | ii ii                                                                                                                                                                                                          |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLED                | GEMENTS                                                                                                                                                                                                        |

| LIST OF FIGU             | RES ix                                                                                                                                                                                                         |

| LIST OF TABL             | <b>ES</b>                                                                                                                                                                                                      |

| ABSTRACT                 | xii                                                                                                                                                                                                            |

| CHAPTER                  |                                                                                                                                                                                                                |

| I. Introd                | uction                                                                                                                                                                                                         |

| 1.1<br>1.2<br>1.3<br>1.4 | High-performance transactions for persistent memories4Delegated persist ordering5Language-level persistency7Summary9                                                                                           |

| II. Backg                | round                                                                                                                                                                                                          |

| 2.1<br>2.2<br>2.3<br>2.4 | Persistent memory technologies11Ordering constraints12Memory persistency models132.3.1Strict persistency142.3.2Epoch persistency142.3.3Strand persistency152.3.4Buffering16Coding patterns to order persists17 |

| 2.5<br>2.6               | Synchronous Ordering19Formalism for non-multi-copy-atomic models202.6.1Relaxed Consistency Buffered Strict Persistency232.6.2Discussion26                                                                      |

| III. High | -performance transactions for persistent memories | 28 |

|-----------|---------------------------------------------------|----|

| 3.1       | Introduction                                      | 28 |

| 3.2       |                                                   |    |

|           | 3.2.1 Transaction design                          |    |

|           | 3.2.2 Minimal Persist Dependencies                |    |

|           | 3.2.3 Persist critical path analysis              |    |

| 3.3       |                                                   |    |

|           | 3.3.1 SCT under Epoch Persistency                 |    |

|           | 3.3.2 SCT under Synchronous Ordering              |    |

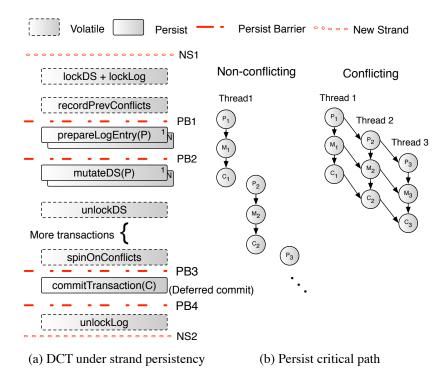

|           | 3.3.3 SCT under Strand Persistency                |    |

| 3.4       |                                                   |    |

|           | 3.4.1 DCT under Epoch Persistency                 |    |

|           | 3.4.2 DCT under Synchronous Ordering              |    |

|           | 3.4.3 DCT under Strand persistency                |    |

| 3.5       |                                                   |    |

|           | 3.5.1 Methodology                                 |    |

|           | 3.5.2 Performance analysis                        |    |

|           |                                                   |    |

| IV. Deleg | gated persist ordering                            | 57 |

| 4.1       | Introduction                                      | 57 |

| 4.2       |                                                   |    |

|           | 4.2.1 Semantics                                   |    |

|           | 4.2.2 Performance                                 |    |

|           | 4.2.3 Discussion                                  |    |

| 4.3       | Delegated persist ordering                        | 63 |

|           | 4.3.1 Design goals                                |    |

|           | 4.3.2 System Architecture                         |    |

|           | 4.3.3 Enforcing Dependencies                      |    |

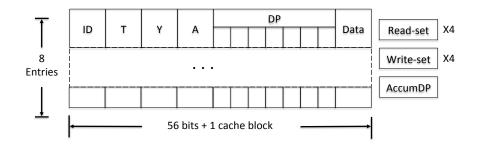

|           | 4.3.4 Hardware Structures                         |    |

|           | 4.3.5 Detailed Examples                           | 74 |

|           | 4.3.6 Coalescing Persists                         |    |

| 4.4       | Evaluation                                        | 78 |

|           | 4.4.1 Performance Comparison                      |    |

| V. Lang   | uage-level persistency                            | 83 |

| 5.1       | Introduction                                      | 83 |

| 5.2       |                                                   |    |

|           | 5.2.1 Failure and recovery                        |    |

|           | 5.2.2 Atomicity and ordering                      |    |

|           | 5.2.3 A Taxonomy of Persistency Guarantees        |    |

|           | 5.2.4 Discussion                                  |    |

| 5.3       |                                                   |    |

| 2.00      | 1                                                 |    |

|             | 5.3.1     | Definition                                             |

|-------------|-----------|--------------------------------------------------------|

|             | 5.3.2     | Mapping to ISA-level persistency                       |

|             | 5.3.3     | Fence directionality                                   |

|             | 5.3.4     | Conflating concurrency control with recoverability 103 |

| 5.4         | Extending | g RCBSP for ARP                                        |

|             | 5.4.1     | Enforcing unidirectional fences                        |

|             | 5.4.2     | Extensions for volatile annotations                    |

| 5.5         | Evaluatio | n                                                      |

|             | 5.5.1     | Performance comparison                                 |

|             | 5.5.2     | Persist scheduling                                     |

|             |           |                                                        |

| VI. Related | d Works S | <b>urvey</b>                                           |

| 6.1         | Polotod v | vorka softwara 115                                     |

| 011         |           | vorks - software                                       |

| 6.2         | Related w | vorks - hardware                                       |

| VII. Conclu | isions    |                                                        |

| 7.1         | Summari   | es of contributions                                    |

| 7.2         | Future we | ork                                                    |

| BIBLIOGRAPH | IY        |                                                        |

# LIST OF FIGURES

# Figure

| 2.1 | Ordering persists across threads/strands: Common coding patterns to        |            |

|-----|----------------------------------------------------------------------------|------------|

|     | specify inter-thread persist dependencies.                                 | 17         |

| 2.2 | Fence cumulativity example: This example shows shows how memory            |            |

|     | events on different cores may be ordered via fence cumulativity            | 26         |

| 3.1 | Ideal undo-loggins transactions: (a) Steps in an undo transaction. (b)     |            |

|     | Persist dependencies in a transaction sequence.                            | 32         |

| 3.2 | Synchronous-commit transaction designs: Synchronous-commit trans-          |            |

|     | actions under epoch persistency, synchronous ordering, and strand persis-  |            |

|     | tency. The red arrows in (d) represent the unnecessary dependencies en-    |            |

|     | forced when compared to the minimal dependencies shown in Figure 3.1(b).   | 37         |

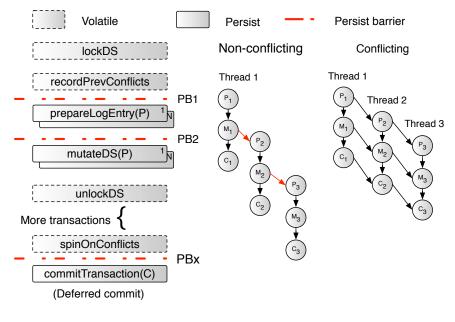

| 3.3 | Deferred-commit transaction design for epoch persistency: Deferred-        |            |

|     | commit transactions under epoch persistency and the resulting persist or-  |            |

|     | dering constraints.                                                        | 43         |

| 3.4 | Deferred-commit transaction design for synchronous ordering: Deferred      | <i>.</i> - |

|     | commit transactions under synchronous ordering and the resulting persist   |            |

|     | ordering constraints                                                       | 47         |

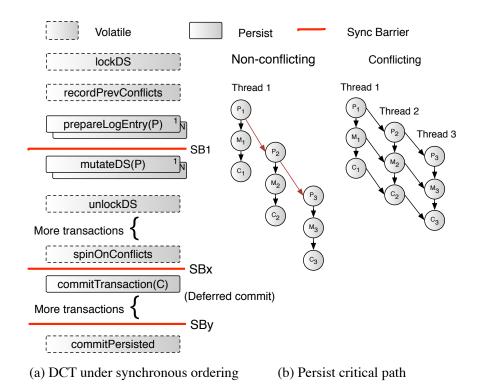

| 3.5 | Deferred-commit transaction design for strand-persistency: Deferred-       |            |

|     | commit transactions under strand persistency and the resulting persist or- |            |

|     | dering constraints.                                                        | 49         |

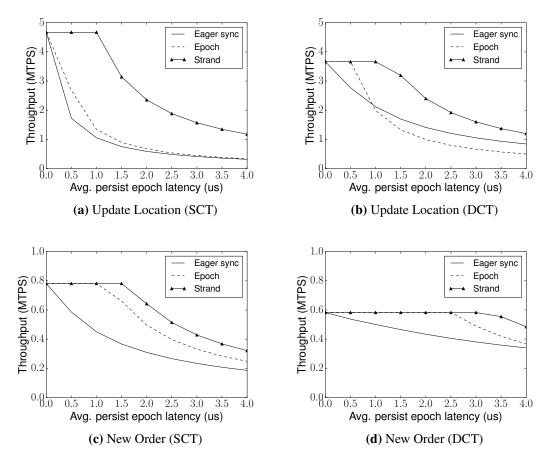

| 3.6 | Evaluation of SCT vs DCT: SCT and DCT performance for Update Lo-           |            |

|     | cation and New Order under various persistency models                      | 51         |

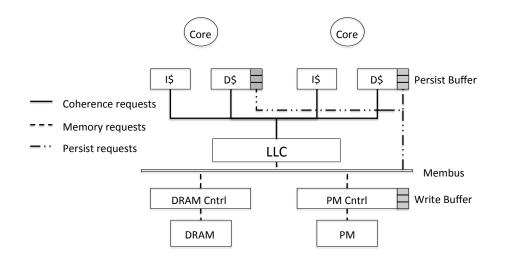

| 4.1 | Proposed architecture design: Our system architecture implementing         |            |

|     | delegated ordering for RCBSP, with a persist buffer at the L1 D-cache for  |            |

|     | every core and write queue at the PM controller                            | 66         |

| 4.2 | Examples of persist dependencies: Persist-persist dependency and epoch-    |            |

|     | persist dependency                                                         | 69         |

| 4.3 | Persist buffer design: Hardware structures required at each core           | 72         |

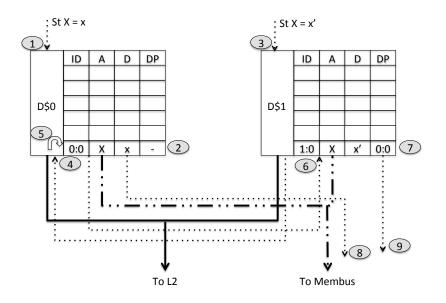

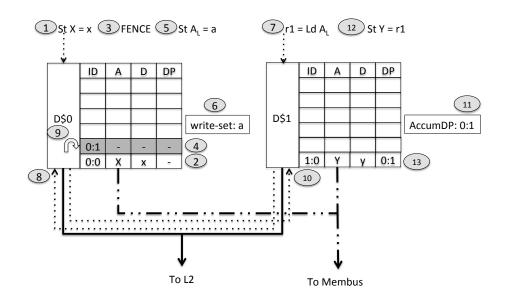

| 4.4 | <b>RCBSP in action - 1:</b> Resolving a persist-persist dependency         | 74         |

| 4.5 | <b>RCBSP in action - 2:</b> Resolving an epoch-persist dependency          | 76         |

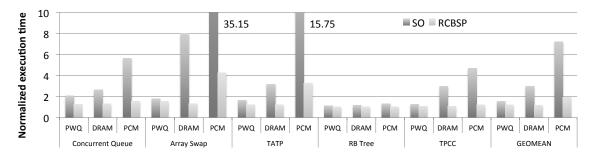

| 4.6 | Evaluating SO vs RCBSP: Normalized execution time for PWQ, DRAM,           |            |

|     | and PCM                                                                    | 80         |

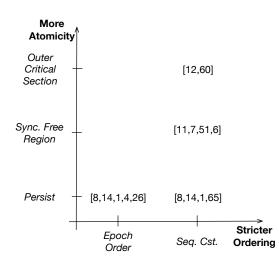

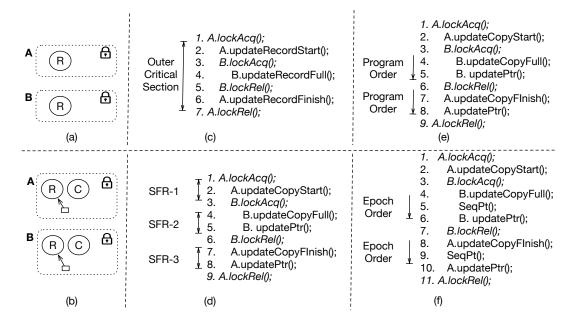

| 5.1 | Design space of persistency guarantees: Persistency guarantees ex-               |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | plored along two dimensions, atomicity and ordering                              | 87  |

| 5.2 | The taxonomy of persistency guarantees analyzed via a running ex-                |     |

|     | ample: (a) Two objects (A,B), each with a record (R) and lock assum-             |     |

|     | ing the language provides failure-atomicity of outer critical sections. (b)      |     |

|     | Two objects (A,B), each with a record (R), a lock, a shadow copy (C),            |     |

|     | and a pointer to ensure failure-atomicity assuming the language does             |     |

|     | not provide failure-atomicity of outer critical sections. (c) Code and           |     |

|     | failure-atomic region when the language guarantees sequentially consis-          |     |

|     | tent failure-atomic outer critical sections. (d) Code and failure atomic re-     |     |

|     | gions when the language guarantees sequentially consistent failure-atomic        |     |

|     | synchronization free regions. (e) Code and orderings when the language           |     |

|     | guarantees sequentially consistent persists. (f) Code and orderings when         | 00  |

| 5.0 | the language guarantees epoch ordered persists.                                  | 90  |

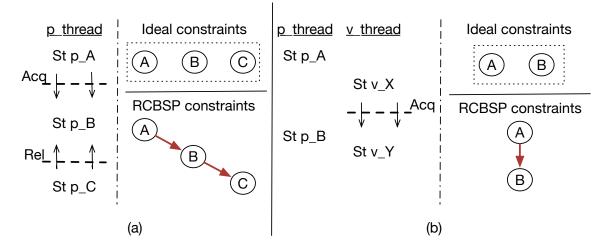

| 5.3 | <b>Unnecessary persist constraints enforced by RCBSP:</b> (a) Unnecessary        |     |

|     | constraints enforced due to hardware being oblivious to <i>fence</i> directions. |     |

|     | (b) Unnecessary constraints enforced due to lack of language level se-           | 100 |

|     | mantics to express volatile <i>fences</i> .                                      |     |

| 5.4 | Allocation of epochs for unidirectional fences in the PM controller              | 105 |

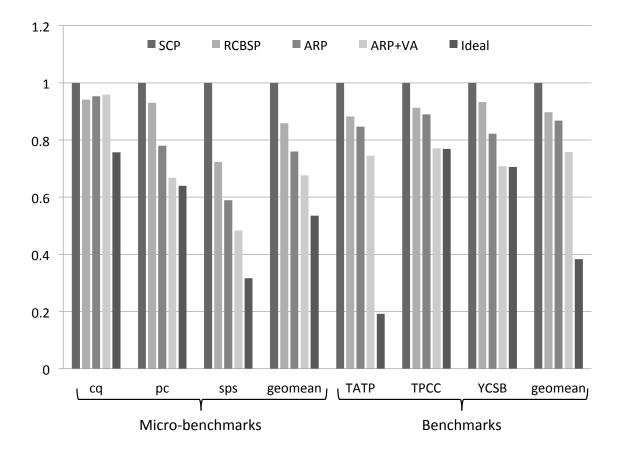

| 5.5 | Execution time normalized to SCP: The graph compares execution time              |     |

|     | of ARP and ARP+VA with SCP and RCBSP for micro-benchmarks and                    |     |

|     | benchmarks.                                                                      | 111 |

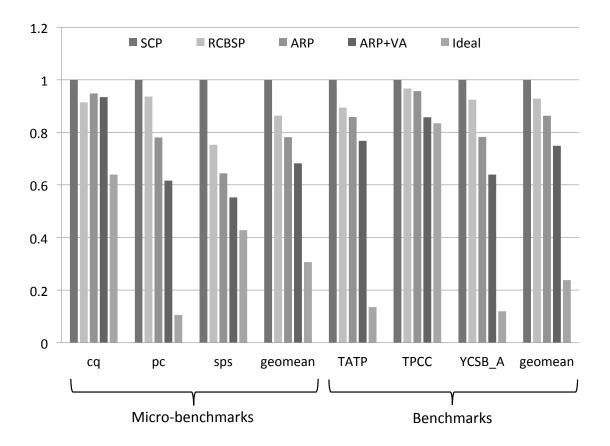

| 5.6 | Page miss rate normalized to SCP: Lower page miss rate in the PM                 |     |

|     | controller implies better persist scheduling                                     | 113 |

# LIST OF TABLES

# Table

| 3.1 | Persist critical path lengths summary: Summary of the persist critical   |    |

|-----|--------------------------------------------------------------------------|----|

|     | path lengths observed with SCT and DCT for different persistency models. | 50 |

| 3.2 | SCT vs DCT performance break-even: The average persist epoch la-         |    |

|     | tency (in $\mu$ s), at which DCT breaks even with SCT                    | 56 |

| 4.1 | Synchronous ordering performance: Slowdowns due to SO over volatile      |    |

|     | execution.                                                               | 62 |

| 4.2 | Simulator Configuration                                                  | 78 |

| 4.3 | <b>Benchmark descriptions</b> (CKC = clwbs per 1000 cycles)              | 79 |

| 5.1 | Compiler transformations from ARP to RCBSP: Mapping from ARP             |    |

|     | memory events to RCBSP [1], which is based on ARMv7a. Ideal map-         |    |

|     | pings from ARP would be to an ISA which supports release consistency 10  | 01 |

| 5.2 | Effect of removing unnecessary persist constraints: Increase in per-     |    |

|     | sists per epoch when the memory controller is aware of FENCE direc-      |    |

|     | tionality and volatile FENCEs                                            | 04 |

| 5.3 | <b>Benchmark characteristics</b> (PKC = persists per 1000 cycles) 1      | 10 |

| 5.4 | Persists per epoch: The persists per epoch observed at the PM controller |    |

|     | for various persistency model implementations                            | 10 |

|     |                                                                          |    |

## ABSTRACT

Architecting Persistent Memory Systems

by

Aasheesh Kolli

Chair: Thomas F. Wenisch

The imminent release of 3D XPoint memory by Intel and Micron looks set to end the long wait for affordable *persistent memory*. Persistent memories combine the persistence of disk with DRAM-like performance, blurring the traditional divide between a byte-addressable, volatile main memory and a block-addressable, persistent storage (e.g., SSDs). One of the most disruptive potential use cases for persistent memories is to host *in-memory recoverable data structures*. These recoverable data structures may be directly modified by programmers using user-level processor load and store instructions, rather than relying on performance sapping software intermediaries like the operating and file systems.

Ensuring the recoverability of these data structures requires programmers to have the ability to control the order of updates to persistent memory. Current systems do not provide efficient mechanisms (if any) to enforce the order in which store instructions update the physical main memory. Recently proposed *memory persistency models* allow programmers

to specify constraints on the order in which stores can be written-back to main memory. While ordering constraints are necessary for recoverability, they are expensive to enforce due to the high write-latencies exhibited by popular persistent memory technologies. Moreover, reasoning about recovery correctness using memory persistency models in addition to ensuring necessary concurrency control in multi-threaded programs drastically increases programming burden. This thesis aims at increasing the adoption of persistent memories through a) improving the performance of recoverable data structures and b) simplifying persistent memory programming.

Software transaction abstractions developed using recently proposed memory persistency models are expected to be widely used by regular programmers to exploit the advantages of persistent memory. This thesis shows that a straightforward implementation of transactions imposes many unnecessary constraints on stores to persistent memory. This thesis also shows how to reduce these constraints through a variety of techniques, notably, deferring transaction commit until after locks are released, resulting in substantial performance improvements.

Next, this thesis shows the high cost of enforcing ordering constraints using recent x86 ISA extensions to enable persistent memory programming, an ordering model referred to as *synchronous ordering*. Synchronous ordering tightly couples enforcing order with writing back stores to main memory, but this tight coupling is often unnecessary to ensure recoverablity. Instead, this thesis proposes *delegated persist ordering*, wherein ordering requirements are communicated explicitly to the persistent memory controller via novel enhancements to the cache hierarchy. Delegated persist ordering decouples store ordering

from processor execution and cache management, significantly reducing processor stalls, and hence, the cost of enforcing constraints.

Finally, existing memory persistency models have all been specified to be used in conjunction with ISA-level memory models. That is, programmers must reason about recovery correctness at the abstraction of assembly instructions, an approach which is error prone and places an unreasonable burden on the programmer. This thesis argues for a *languagelevel persistency model* that provides mechanisms to specify the semantics of accesses to persistent memory as an integral part of the programming language and proposes a concrete model, *acquire-release persistency*, that extends C++11s memory model to provide persistency semantics.

# **CHAPTER I**

# Introduction

New *persistent memory* (PM) technologies with the potential to transform software's management of persistent data will soon be available. For example, Intel and Micron have announced their 3D XPoint memory technology for availability in 2017 [2], and competing offerings may follow [3]. Such devices are expected to provide much lower access latencies than NAND Flash, enabling access to persistent data with a load-store interface like DRAM rather than the block-based I/O interface of Flash and disk. Persistent memory systems will allow programmers to maintain *in-memory recoverable data structures*.

Ensuring recoverability of these data structures requires constraints on the order writes become persistent [4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16]. At the same time, it is desirable that PM accesses are cacheable, both to hide access latency and to enable write coalescing to conserve write bandwidth and lifetime for devices subject to wearout. Conventional memory systems delay, combine, and reorder writes to memory at multiple levels, and do not enforce any particular correspondence between the order stores become visible in multi-core systems and the order in which they are written back to main-memory. Recent work proposes that programming systems be extended with a *memory persistency model*; an explicit specification and programming interface to constrain the order writes to PM become persistent [5, 14, 4, 8]. A memory persistency model is analogous to the memory consistency model [17] that governs the ordering of reads and writes to shared memory, but instead constrains the order PM writes become persistent, an operation referred to as a *persist* henceforth. And, constraints on the order of persists are referred to as *persist dependencies*.

While PMs offer exciting new possibilities, the following challenges, if not addressed, will hinder them from being widely adopted:

- Whereas specifying and honoring persist dependencies is essential for recovery correctness, enforcing persist dependencies is likely to be expensive. PM technologies are expected to be slower than DRAM [18], and will only be able to keep up with CPU speeds through techniques that exploit parallelism, batching, and reordering [9], all of which are possible only in the absence of persist dependencies. Mechanisms to reduce the cost of enforcing persist dependencies, and hence, improve the performance of recoverable data structures are necessary.

- Writing correct parallel programs is hard. Ensuring recovery correctness requires

programmers to reason about persist dependencies (via the memory persistency model)

in addition to concurrency control mechanisms, exacerbating programming burden.

Developing simple, precise, and high-performing programming abstractions to ease

programming burden could go a long way towards increasing the adoption of persistent memories.

This thesis comprises of three thrusts, all aiming to address one or both of the challenges described above. The three thrusts are:

- High-performance transactions for persistent memories: Software transactional libraries are expected to be widely used by regular programmers to maintain recoverable data structures in PM. We expose the unnecessary persist dependencies resulting from a straight-forward implementation of transactions. We further show how to reduce these unnecessary persist dependencies, resulting in significant performance gains.

- **Delegated persist ordering:** The cost of enforcing individual persist dependencies plays a major role in determining the performance of recoverable data structures. We show how the semantics of the recently proposed x86 ISA extensions for persistent memory programming cause substantial overheads to enforce individual persist dependencies. Subsequently, we also propose an alternative implementation strategy to reduce the cost of enforcing persist dependencies.

- Language-level persistency: All of the recently proposed memory persistency models [5, 14, 4, 8] have been specified in conjunction with the ISA-level memory consistency models. However, programmers predominantly reason about parallel programs using language-level memory models exposed by high-level programming languages (e.g. C++11). We propose to expose persistency semantics at the language level, allowing programmers to reason about recovery correctness without concerning themselves with the ISA-level memory consistency and persistency models.

The rest of this chapter provides a brief overview of the proposals in each of the three thrusts mentioned above.

#### **1.1** High-performance transactions for persistent memories

Ensuring that persistent data is consistent despite power failures and crashes is difficult, especially when manipulating complex data structures with fine-grained accesses. One way to ease this difficulty is to access persistent data through atomic, durable transactions, which make groups of updates appear as one atomic unit with respect to failure. Because of the power and convenience of transactions, they are expected to be widely used by regular programmers [11, 7, 6, 19]. Please note that transactions also provide mechanisms for controlling concurrency; in this thesis, we assume that transactions use locks in volatile memory for concurrency control.

Implementing transactions requires the ability to order writes to the PM. For example, in write-ahead logging [20], the commit record for a transaction may persist only after after all log records for that transaction have been persisted; otherwise a failure may cause the system to recover to a state in which only some of the updates are present.

We consider how to implement transactions for PM in a way that minimizes persist dependencies. We show that a simple transaction system design enforces many unnecessary persist dependencies and that these dependencies greatly slow down common transaction workloads. And, that most of the unnecessary dependencies arise as a consequence of performing the commit step of the transaction while locks are held, and how to remove these dependencies by deferring this commit until after locks are released. Deferring commits leads to the new challenge of correctly ordering the deferred commit operations across all outstanding transactions. To ensure transaction serializability, commit order must match the order in which locks were originally acquired during transaction execution. We show how to minimize persist dependencies through a combination of techniques, including distributed logs [21], deferred commit [22, 23], Lamport/vector clocks to serialize transactions [24], a subtle epoch-based mechanism to recycle log storage, and memory persistency models [5].

While prior works like like *NV-Heaps* [11] and *Mnemosyne* [7] implement transactions for persistent memories, they focus on optimizing transaction design for a particular persistency model. We instead take a more fundamental approach to transaction design that can be applied to many different persistency models. We evaluate the performance of a transaction system that defers commits on simulated PM with a range of device speeds. For two transaction-processing workloads, we show that performance improves from 50%-150% for various memory persistency models [5].

## **1.2** Delegated persist ordering

Apart from the total number of persist dependencies, the cost of enforcing individual persist dependencies also plays a major role in determining overall performance. We quantify the high costs of enforcing persist dependencies using recent x86 ISA extensions for PM and also proposes an alternative persistency model implementation strategy to reduce said costs.

To complement upcoming memory technology offerings, Intel [4] has announced instruction set extensions to enable programmer control of data persistence. The clwb instruction allows programmers to initiate write back of specific addresses to PM, and the pcommit and sfence instructions enable order enforcement among these writebacks and subsequent execution. we describe the persistency model implied by the semantics of these instructions. This new persistency model is referred to as *synchronous ordering* henceforth.

Synchronous ordering enforces order by stalling execution, preventing instructions ordered after a pcommit from retiring until prior PM writes persist. However, this approach tightly couples volatile execution and persistent writes, placing PM write latency on the execution critical path. As we will will show, these stalls can result in a 7.21× slowdown in workloads with frequent PM writes.

Synchronous ordering couples two orthogonal operations: prescribing an order of persists and ensuring that persists complete (i.e. the corresponding store has been written back to PM). However, coupling these operations is often unnecessary for software system recoverability, as data structure consistency depends principally upon the order of persists [25, 10, 5, 14]. In many contexts, volatile execution may proceed ahead of properly ordered persists without compromising recoverability or waiting for the persists to complete, allowing PM latency to be hidden. When rare failures occur, some writes may be lost, but data structure consistency is maintained (e.g., journaling file systems maintained on disks [10]).

We explore a new implementation approach to enforcing persist dependencies. Instead of enforcing order through stalls, the proposed solution, *delegated persist ordering*, com-

municates partial ordering requirements mandated by the persistency model explicitly to the PM controller. Delegated persist ordering decouples persistency model implementation from both volatile execution and cache management. Execution and communication via shared memory proceed while PM writes drain. Caches remain volatile and may communicate through cache coherence and evict blocks at will. Instead, our approach maintains writes to PM alongside the cache hierarchy in per-core *persist buffers*.

Using annotations added to coherence transactions, the persist buffers observe and track persist dependencies mandated by the persistency model. Together, they serialize PM writes into a partially ordered buffer at the PM controller, which may then schedule PM writes to exploit available bank concurrency. Execution does not stall unless buffering resources in the persist buffers and at the PM controller are exhausted or the programmer explicitly requests the stall (e.g., before issuing an irrecoverable action). An evaluation of delegated persist ordering demonstrates that it improves performance by 3.73× on average over synchronous ordering for PM-write-intensive benchmarks, coming within 1.93× of volatile execution without order enforcement.

### **1.3 Language-level persistency**

All of the persistency models that have been proposed until now [5, 14, 1, 8, 4, 26] have been specified at the instruction set architecture (ISA) level. That is, programmers must reason about recovery correctness at the abstraction of assembly instructions, an approach which is error prone and places an unreasonable burden on the programmer. The programmer must invoke ISA-specific mechanisms (via library calls or inline assembly) to ensure persist order, and often must reason carefully about compiler optimizations that may affect the relevant code. Since the ISA mechanisms differ in sometimes subtle ways, it is hard to write portable recoverable programs.

We argue for a *language-level persistency model* that provides mechanisms to specify the semantics of accesses to PM (including with respect to program failures) as an integral part of the programming language, just as language-level memory consistency models enable precise specification of the semantics of memory accesses from concurrent threads. A language-level persistency model provides a single, ISA-agnostic framework for reasoning about persistency and can enable portability of recoverable software across language implementations (compiler, runtime, ISA, and hardware). Furthermore, a language-level model prescribes precise requirements on the implementation, allowing implementers to reason about the correctness of compiler and hardware optimizations.

We explore a taxonomy of guarantees that a language-level persistency model might provide. Stronger guarantees (e.g., *failure-atomicity* of critical sections) make writing recoverable software easier but impose substantial requirements on the implementation, which entail performance penalties. Weaker guarantees complicate reasoning about recovery, but provide greater implementation freedom and performance. The weaker guarantees relax atomicity of critical sections and instead provide only *ordering* guarantees for individual persists. Ordering guarantees on individual persists allow synthesis of higher granularities of atomicity via logging.

Based on our taxonomy, we propose a concrete model, *acquire-release persistency*, to extend the C++11 memory model. We describe how to compile ARP to an existing ISA-level persistency model [1]. Ideally, the language and ISA persistency models work in

concert to enforce only the minimal guarantees required for correct recovery. However, we find that mismatch between ARP and the ISA-level model lead to extra constraints that hamper performance. We then propose modifications to the C++11 language, compiler, ISA, and hardware to resolve these mismatches, increasing available persist concurrency and scheduling flexibility. The greater flexibility allows the PM controller to reduce page miss rates, improving application performance by up to 33.2% and by 19.8% on average.

## 1.4 Summary

Soon to be available persistent memories have the potential to transform how software manages persistent data. However, before persistent memories can be widely adopted, a couple of challenges need to be addressed: 1) improve the performance of in-memory recoverable data structures and 2) develop simple and precise programming abstractions to enable persistent memory programming. In this thesis, we identify three different ways to address one or both of these challenges. First, we develop high-performance transactions for persistent memories by reducing the number of unnecessary persist dependencies enforced. Second, we reduce the cost of enforcing individual persist dependencies by decoupling the enforcement of persist dependencies from execution at the core. And finally, we expose the persistency model at the language-level (similar to language-level memory models) to alleviate programmers of the burden to reason about ISA-specific memory consistency and persistency models.

In the reminder of this thesis, Chapter 2 provides the necessary background to better understand the contributions of this thesis. Chapter 3 describes how we improve transaction performance. Chapter 4 details how we reduce the cost of enforcing individual persist requests. Chapter 5, presents the design of a language-level persistency model. Chapter 6 presents a brief summary of related works and Chapter7 the conclusions from this thesis.

# **CHAPTER II**

# Background

This chapter provides details necessary to understand the following chapters in this thesis. First, we talk about different persistent memory technologies, followed by an overview of the various different memory persistency models that have been recently proposed.

### 2.1 Persistent memory technologies

Various memory technologies offer both byte-addressable accesses and non-volatility (or durability). For example, phase change memory (PCM) [18] uses a chalcogenide glass whose resistence can be programmed by varying electrical inputs to the cell. Resistive RAM (ReRAM) [27] is similar to PCM except that instead of using a chalcogenide glass, ReRAM uses metal oxide, whose ressistence can also be programmed via varying electrical inputs. Spin-transfer torque memory (STT-RAM) is a magnetic memory that stores state in electron spin [28]. Storage capacity increases by storing more than two states per cell in Multi-level Cells (MLC) (e.g., four distinct resistivity levels provide storage of 2 bits per cell). While it remains unclear which of these technologies will eventually gain traction, many share common characteristics. In particular, PMs will likely provide somewhat higher access latency relative to DRAM. Furthermore, several technologies are expected to have asymmetric read-write latencies, where writes are much more expensive than reads [29]. Write latency worsens with MLC, where slow, iterative writes are necessary to reliably write to cells.

Resistive technologies suffer from limited write endurance, that is, memory cells may be written reliably only a limited number of times. While write endurance is an important consideration, proposed hardware mechanisms (e.g., Start-Gap [30]) are effective in distributing writes across cells, mitigating write endurance concerns.

### 2.2 Ordering constraints

The ability to order writes is critical to all software that uses persistent storage. Constraining the order that writes persist is essential to ensure correct recovery, and minimizing these constraints is key to enabling high performance.

Formally, we express an ordering relation over memory events *loads* and *stores*, which we collectively refer to as *accesses*. The term *persist* refers to the act of durably writing a store to persistent memory. We assume persists are performed atomically (with respect to failures) at 8-byte granularity. By "thread", we refer to execution contexts—cores or hardware threads. We use the following notation (originally presented here [31]):

- $L_a^i$ : A load from thread *i* to address *a*

- $S_a^i$ : A store from thread *i* to address *a*

•  $M_a^i$ : A load or store by thread *i* to address *a*

We reason about two ordering relations over memory events, *volatile memory order* and *persist memory order*. Volatile memory order (VMO) is an ordering relation over all memory events (loads and stores) as prescribed by the memory consistency model for multiprocessors [17]. Persist memory order (PMO) deals with the same events but may have different ordering constraints than VMO. [5] uses the term *memory persistency model* to describe the types of constraints that hardware allows software to express on the persist memory order.

We denote these ordering relations as:

- $A \leq_{v} B$ : A occurs no later than B in VMO

- $A \leq_p B$ : A occurs no later than B in PMO

An ordering relation between stores in PMO implies the corresponding persist actions are ordered; that is,  $A \leq_p B \rightarrow B$  may not persist before *A*.

### 2.3 Memory persistency models

In currently shipping processor architectures, persist dependencies must be enforced either by using a write-through cache or by explicitly flushing individual cache lines (e.g., using the *clflush* instruction on x86). Moreover, these flush operations must be carefully annotated with fences to prevent hardware and compiler reorderings (details appear in [32]). These mechanisms are quite slow because they give up much of the performance benefits of CPU caches. Because cache flushes are so slow, Intel has recently announced extensions to its x86 ISA to optimize cache line flushing [4]. Researchers have proposed other means to express persist dependencies. Condit and co-authors propose an *epoch barrier*, which ensures writes before the barrier are ordered before writes after the barrier [8]. Pelley and co-authors liken the problem of ordering persists to the problem of ordering memory accesses in a multiprocessor [5]. Just as there is a design space for multiprocessor memory consistency models, Pelley lays out a design space for memory *persistency* models. We use *sequential consistency* (SC) as the underlying consistency model in this section. We briefly summarize all of the three persistency models proposed by Pelley.

#### 2.3.1 Strict persistency

Under strict persistency, PMO is identical to VMO. So, for any two stores ordered by the consistency model, the corresponding persists are also ordered. Formally,

$$M_a^i \leq_v M_b^j \leftrightarrow M_a^i \leq_p M_b^j \tag{2.1}$$

Whereas strict persistency is the most intuitive persistency model, it is not the best performing. By ordering persists per VMO, strict persistency enforces orderings typically not required for recovery correctness [5]. Thus, researchers have proposed more relaxed persistency models, in which PMO may have fewer ordering constraints than VMO.

#### 2.3.2 Epoch persistency

The *epoch persistency model* introduces a new memory event, the "persist barrier" (different from memory consistency barriers). We denote persist barriers issued by thread *i*

as  $PB^i$ . Under epoch persistency, any two memory accesses on the same thread that are separated by a persist barrier in VMO are ordered in PMO.

$$M_a^i \leq_v PB^i \leq_v M_b^i \to M_a^i \leq_p M_b^i \tag{2.2}$$

Persist barriers separate a thread's execution into ordered epochs (persists within an epoch are concurrent). While persist barriers order persists from one thread, epoch persistency relies on another property, *strong persist atomicity*, to order persists from different threads.

#### 2.3.2.1 Strong persist atomicity:

Memory consistency models often guarantee that stores to the same address by different processors are serialized (this is called *store atomicity*). Pelley argues persistency models should similarly provide *strong persist atomicity* (SPA), to preclude non-intuitive behavior, such as recovering to states unreachable under fault-free execution [5]. SPA requires that conflicting accesses (accesses to the same address, at least one being a store) must persist in the order they executed.

$$S_{a}^{i} \leq_{v} M_{a}^{j} \rightarrow S_{a}^{i} \leq_{p} M_{a}^{j}$$

$$M_{a}^{i} \leq_{v} S_{a}^{j} \rightarrow M_{a}^{i} \leq_{p} S_{a}^{j}$$

(2.3)

#### **2.3.3** Strand persistency

Strand persistency divides program execution into *strands*. Strands are logically independent segments of execution that happen to execute in the same thread. Strands are separated by the *new strand* (NS) memory event. New strand events from thread *i* are denoted as *NS<sup>i</sup>*. The new strand event clears all prior PMO constraints from prior instructions, effectively making each strand behave as if it were a separate thread (with respect to persistency). Memory accesses within a strand are ordered using persist barriers (Eq. 2.2). Under strand persistency, two memory accesses on the same thread separated by a persist barrier are ordered in PMO only if there is no intervening strand barrier. Memory accesses across strands continue to be ordered via SPA (Eq. 2.3).

$$(M_a^i \leq_{v} PB^i \leq_{v} M_b^i) \land (\not\exists NS^i : M_a^i \leq_{v} NS^i \leq_{v} M_b^i) \to M_a^i \leq_{p} M_b^i$$

(2.4)

#### 2.3.4 Buffering

Pelley further suggests that buffering persists in hardware will expose more opportunities to re-order and coalesce, thus improving performance. Buffering implies that some stores, which have already been executed by a processor and are visible to other processors, might not yet have been persisted to PM. However, the hardware (memory hierarchy) guarantees that, eventually, all these stores will persist *in the order dictated by the PMO*.

Buffering improves performance by ensuring that the memory hierarchy does not have to persist an executed store immediately, but can perform the persist eventually, as long as the correct order is maintained [5, 14]. Volatile execution and cache coherence may proceed while the persist operation is drained lazily to PM.

| Thread 1 Thread 2<br>lock L<br>store A<br>PB | Thread 1 Thread 2<br>lock L<br>store A<br>unlock L |

|----------------------------------------------|----------------------------------------------------|

| unlock L                                     | lock L                                             |

| lock L                                       | load A                                             |

| PB                                           | PB                                                 |

| store B                                      | store B                                            |

| unlock L                                     | unlock L                                           |

| (a) Lock                                     | ( <b>b</b> ) Observe                               |

Figure 2.1: Ordering persists across threads/strands: Common coding patterns to specify interthread persist dependencies.

## 2.4 Coding patterns to order persists

The previous section described different persistency models that software can use to specify ordering constraints among persists. We next discuss a few canonical examples to show how software can use these interfaces. Persists on a single thread (or strand under strand persistency) are ordered either by VMO (strict persistency) or by persist barriers (epoch and strand persistency).

Enforcing persist order across threads is more complex; as with VMO, these orderings must be established using conflicting accesses.

Figure 2.1 illustrates coding patterns to establish order for a simple scenario under each model. Consider two stores to addresses A and B, executed on different threads (or strands), which are protected by a single lock L, we assume thread 1 wins:  $S_A^1 \leq_v S_B^2$ . Our objective is to use the persistency models to ensure that the persists of A and B follow the same order:  $S_A^1 \leq_p S_B^2$ .

The definition of strict persistency (Eq. 2.1) ensures the desired order of persists. Below, we describe two techniques *lock* and *observe*, employed under epoch and strand persistency models to achieve the desired persist ordering.

**Lock:** The central intuition is to leverage the conflicting accesses of the concurrency control mechanism (i.e., locks), which establish required constraints (e.g., mutual exclusion) in VMO, to also establish the required ordering constraints in PMO. Figure 2.1a shows how to order persists to A and B under epoch persistency using persist barriers  $PB^1$  and  $PB^2$ . We denote the unlock operation on thread 1 as  $S_L^1$  and the lock operation on thread 2 as  $S_L^2$ . The program orders of thread 1, thread 2 and the ordering property of persist barriers (Eq. 2.2) ensures that:

$$S_A^1 \leq_{\nu} PB^1 \leq_{\nu} S_L^1 \to S_A^1 \leq_p S_L^1 \tag{2.5}$$

$$S_L^2 \leq_v PB^2 \leq_v S_B^2 \to S_L^2 \leq_p S_B^2 \tag{2.6}$$

From conflicting accesses to lock L and SPA (eq 2.3)

$$S_L^1 \leq_{\nu} S_L^2 \to S_L^1 \leq_p S_L^2 \tag{2.7}$$

By transitivity and Eqs. 2.5-2.7, we ensure that  $S_A^1 \leq_p S_B^2$ . This same reasoning extends to strands (instead of threads) under strand persistency.

**Observe:** Instead of relying on lock L for conflicting accesses, we can explicitly *observe* (using loads) the specific addresses after which subsequent persists should be ordered, and then issue a persist barrier. Figure 2.1b illustrates this pattern.  $S_A^1$ 's persist is unordered with respect to any other persist on Thread 1 or (absent  $L_A^2$  and  $PB^2$  we have included) Thread 2. Note that the lock L still ensures mutual exclusion and ordering of the (volatile)

execution of the critical sections but, by itself, will not order the persists of A and B. Since thread 1 acquires lock L first, from VMO and SPA (Eq. 2.3), we have:

$$S_A^1 \leq_{\nu} L_A^2 \to S_A^1 \leq_p L_A^2 \tag{2.8}$$

From the program order of Thread 2 and the ordering property of persist barriers (Eq. 2.2), we have:

$$(L_A^2 \le_{\nu} PB^2 \le_{\nu} S_B^2) \to L_A^2 \le_p S_B^2$$

(2.9)

By transitivity and Eqs. 2.8 and 2.9, we have  $S_A^1 \leq_p S_B^2$ . Again, the above reasoning extends to strands as well. In fact, by placing all persists on their own strands and using the observe technique, it is possible to enforce only the required ordering constraints, even under SC.

## 2.5 Synchronous Ordering

Intel's recently announced extensions [4] provide mechanisms to guarantee recovery correctness and improve upon the performance deficiencies of clflush. *Synchronous ordering* (SO) is our attempt to describe the persistency model implied by the semantics of Intel's ISA extensions [4]. We briefly describe the most relevant of these new instructions:

- clwb: Requests writeback of modified cache line to memory; clean copy of cache line may be retained.

- pcommit: Ensures that stores that have been accepted to memory are persistent when the pcommit becomes globally visible.

Executing a clwb instruction, by itself, does not ensure data persistence because the PM controller is permitted to have volatile write queues that may delay a PM write even after the clwb operation is complete. The semantics of pcommit are subtle; it is a request to the PM controller to flush its write queues. However, pcommit execution is not implicitly ordered with respect to preceding or following stores or clwb operations. Hence, neither pcommit nor clwb alone assure persistence.

A store operation to cacheable ("write back") memory is assured to be "accepted to memory" when a clwb operation ordered after the store becomes globally visible ([4] p. 10-8). However, since pcommit is not ordered with respect to the completion of clwb operations, an intervening sfence is needed to ensure the clwb is globally visible. Similarly, a fence operation is required after the pcommit to order its global visibility with respect to subsequent stores.

With these two instructions, stores on one thread to addresses A and B can be guaranteed to to be updated in PM in the order A < B, using the following pseudo-code:

```

st A;clwb A;sfence;pcommit;sfence;st B;

```

We refer to the code sequence sfence; pcommit; sfence as a *sync barrier*. The first sfence orders the pcommit with earlier stores and clwbs, while the second orders later stores with the pcommit.

### 2.6 Formalism for non-multi-copy-atomic models

In this section, we detail the semantics of buffered strict persistency when applied to ARMv7 consistency, yielding a model that we call *relaxed consistency buffered strict per-*

*sistency*, or RCBSP. Because ARMv7 already allows store reordering between memory fences, RCBSP enables concurrency among persist operations similar to what is allowed under epoch persistency in sequentially consistent systems, without the need to introduce new fence instructions for persists. Moreover, to account for the fact that ARMv7a is a non-multi-copy-atomic model (unlike total store order in previous sections), we introduce new notations to formally specify RCBSP. Next, we precisely specify RCBSP using nomenclature from Pelley [5] and notation similar to that presented in chapter 2.2.

First, we add a new memory event a *fence* to the set of *accesses* (i.e. *loads*  $(L_a^i)$  and *stores*  $(S_a^i)$ ). Note that we use a full strength *dmb* [33] as our *fence*, details later in this section. Further, we use the following notation for dependencies between memory events:

- $M_a^i \xrightarrow{d} M_b^i$ : An addr/data/control dependence from  $M_a^i$  to  $M_b^i$ , two accesses on the same thread.

- $S_a^i \xrightarrow{rf} L_a^j$ : A load "reads from" [34] a prior store.

- $L_a^i \xrightarrow{fr} S_a^j$ : A store "from reads" [34] a prior load.

We reason about three ordering relations over memory events, *local memory order*, *volatile memory order* and *persist memory order*.

Local memory order (LMO<sup>*i*</sup>) is an ordering relation over all memory events (loads and stores), observed by thread i, prescribed by the memory consistency model [17]. In relaxed consistency models, especially non-multi-copy-atomic models like ARMv7 [34, 35], different threads may legally disagree on the order in which stores become visible. It is important to note that, *no thread disagrees* with at least a subset of ordering relations, for example, coherence order and orderings enforced by fence cumulativity [35, 34, 36, 37]. In order to account for the fact that ARMv7a is a non-multi-copy-atomic model, we use a more precise definition of Volatile memory order (VMO). VMO is an ordering relation over all memory events as observed by a hypothetical thread that atomically reads all contents of persistent memory at the moment of failure (defined as "recovery observer" in [5]). Note that VMO agrees with all other threads w.r.t. coherence order and fence cumulativity. Persist memory order (PMO) is an ordering relation over all memory events but may have different ordering constraints than any LMO<sup>*i*</sup> or VMO. PMO is governed by the "memory persistency model" [5].

We denote these ordering relations as:

- $A \leq_{li} B$ : A occurs no later than B in LMO<sup>*i*</sup>

- $A \leq_{v} B$ : A occurs no later than B in VMO

- $A \leq_p B$ : A occurs no later than B in PMO

An ordering relation between stores in PMO continues to imply that the corresponding persists are ordered; that is,

$A \leq_p B \to B$  may not persist before A.

Based on the relationship between VMO and PMO, Pelley classifies persistency models into two types: *strict* and *relaxed*. Under strict persistency, the PMO is the same as VMO, that is, a programmer uses the memory consistency model to govern both store visibility and the order in which stores persist. Under relaxed persistency, PMO and VMO may differ, that is, a programmer needs to reason separately about store visibility and the order in which stores persist. The motivation for relaxed persistency arises because of the use of conservative consistency models such as sequential consistency (SC) and total store order (TSO). These consistency models require a strict order (in VMO) for all stores and allow little re-ordering or coalescing. Pelley shows that following the same strict order for persists (each of which could take 100s of nano-seconds [18]), hinders performance, much like synchronous ordering. Relaxed persistency models allow programmers to impose a different set of constraints for the PMO than the VMO, thereby allowing more re-order-ing and coalescing in the PMO. Pelley shows that the additional parallelism afforded to persists by relaxed persistency models significantly improves performance.

Even though relaxed persistency models improve performance by exposing additional parallelism, they increase the burden on the programmer by forcing her to reason about two different memory models. ARMv7 consistency already enables parallelism among memory accesses and requires reasoning about proper ordering of shared memory accesses (including non-multi-copy-atomic stores). In this context, we consider the alternate choice of using strict persistency. This choice of relaxed consistency and strict persistency exposes persist parallelism but does not saddle the programmer with an additional memory model. Instead, reasoning about recovery is akin to reasoning about an additional thread.

#### 2.6.1 Relaxed Consistency Buffered Strict Persistency

We describe the semantics of buffered strict persistency under ARMv7 relaxed consistency. Memory events on the same thread are locally ordered by: • Executing a *FENCE* instruction between them in program order. Formally:

$$M_a^i; F^i; M_b^i \to M_a^i \leq_{li} F^i \leq_{li} M_b^i$$

(2.10)

• Using an address/data/control dependence between a memory access and a subsequent memory access in program order. Formally:

$$M_a^i \xrightarrow{d} M_b^i \to M_a^i \leq_{li} M_b^i$$

(2.11)

Further, a thread may "observe" memory events on an another thread using "reads from" and "from reads" dependencies [34]. Formally:

$$S_a^i \xrightarrow{rf} L_a^j \to S_a^i \leq_{lj} L_a^j \tag{2.12}$$

$$L_a^i \xrightarrow{fr} S_a^j \to L_a^i \leq_{lj} S_a^j \tag{2.13}$$

Memory events are globally ordered across threads using coherence and fence cumulativity [35, 36, 34, 37].

**Coherence:** Two stores to the same address are globally ordered, that is, all threads agree on the order of stores (from any thread) to the same address.

$$\forall (S_a^i, S_a^j), (S_a^i \leq_{\nu} S_a^j) \lor (S_a^j \leq_{\nu} S_a^i)$$

$$(2.14)$$

**Fence Cumulativity:** Loosely, a FENCE ( $F_i$ ) instruction provides ordering in VMO between the set of all memory accesses (from any thread) ordered before the FENCE (Group  $G_A$ ) and the set of all memory accesses (from any thread) ordered after the FENCE (Group  $G_B$ ). The set of memory accesses belonging to  $G_A$  can be constructed using the following algorithm [38, 35]:

- (1)  $\forall M_a^i \mid M_a^i \leq_{li} F^i, G_A = G_A \cup M_a^i$

- (2) Repeat:

(3)

$$\forall (M_a^i \in G_A, M_b^j) | M_b^j \leq_{\nu} M_a^i, G_A = G_A \cup M_b^j$$

(4)

$$\forall (M_a^i \in G_A, M_b^j) | M_b^j \leq_{li} M_a^i, G_A = G_A \cup M_b^j$$

Line (1) indicates all memory accesses thread-locally ordered before the FENCE belong to Group  $G_A$ . The next steps recursively add to  $G_A$  additional accesses transitively observed before the FENCE. Line (3) adds all accesses ordered by VMO before any in  $G_A$ . Line (4) for each access in  $G_A$ , adds accesses ordered before it w.r.t its thread's LMO in  $G_A$ . The algorithm stops when no new accesses can be added to  $G_A$ .

Group  $G_B$  is similarly constructed from accesses after the FENCE. Once  $G_A$  and  $G_B$  are constructed, fence cumulativity offers the following guarantee:

$$\forall (M_a^i \in G_A, M_b^j \in G_B), M_a^i \leq_v M_b^j$$

(2.15)

The example in Figure 2.2 (a variant of the ISA2 litmus test from [34]) highlights fence cumulativity. A FENCE ( $F^0$ ) instruction is executed on Core-0. So,  $S_X^0$ , preceding  $F^0$ , is

$$\begin{array}{ccc} \underline{\textbf{Core-0}} & \underline{\textbf{Core-1}} \\ S_X^0: & St \; X = x \\ F^0: & FENCE \\ S_Y^0: & St \; Y = y \\ & & L_Y^1: & r1 = Ld \; Y \\ & & S_Z^1: & St \; Z = r1 \end{array}$$

**Figure 2.2:** *Fence cumulativity example: This example shows how memory events on different cores may be ordered via fence cumulativity.*

placed in  $G_A$ . Note that  $S_X^0$  is the only member of  $G_A$ .  $S_Y^0$  is placed in  $G_B$ . We assume that  $L_Y^1$  "reads from"  $S_Y^0$ , and hence gets added to  $G_B$ . The data dependency between  $L_Y^1$  and  $S_Z^1$ , requires that  $S_Z^1$  gets added to  $G_B$ . So, from Eq 2.15, we have that  $S_X^0 \leq_v S_Z^1$ , implying that all threads can only observe  $S_Z^1$  after  $S_X^0$ . Interestingly,  $S_Y^0$  and  $S_Z^i$  are not ordered in VMO as they both belong to the  $G_B$ .

Specifically under RCBSP, strict persistency (Eq 2.1), allows two behaviors:

1) Two stores to the same persistent address on different threads will persist in coherence order.

2) Two stores to persistent addresses, one belonging to  $G_A$ , and the other belonging to  $G_B$  of a *FENCE* (on any thread), will persist in order ( $G_A$  before  $G_B$ )

### 2.6.2 Discussion

When programming for persistence, to guarantee two stores persist in order, the programmer must ensure that a hypothetical thread would observe the stores in the desired order. This requirement even holds for single-threaded applications, where programmers rarely concern themselves with memory consistency models. Formally defining a consistency model is a complex task [35, 36, 34, 37]. The intent behind the definitions above is not to fully and precisely specify ARMv7, but rather to highlight the ways in which a programmer can use the memory consistency model to order persists. We have manually verified that our RCBSP definitions enforce required persist order for each of the litmus tests presented in [34]. (More specifically, we confirmed that RCBSP precludes recovery from observing outcomes forbidden by any litmus test). Nevertheless, automatic formal verification (e.g., via a proof assistant), is beyond the scope of this thesis.

Next, we present how to implement high-performance transactions for persistent memories implemented using the persistency models described in this chapter.

## **CHAPTER III**

# **High-performance transactions for persistent memories**

### 3.1 Introduction

Ensuring that persistent data is consistent despite power failures and crashes is difficult, especially when manipulating complex data structures with fine-grained accesses. One way to ease this difficulty is to access persistent data through atomic, durable transactions, which make groups of updates appear as one atomic unit with respect to failure. Because of the power and convenience of transactions, many prior works propose providing them on top of PM [11, 7, 6, 19]. We focus our analysis on static transactions (transactions for which lock sets are known a priori), as detailed in Section 3.2.

Implementing transactions on PM requires the ability to order writes to the NVRAM.<sup>1</sup> Memory persistency models described in the previous chapter allow developers to specify the desired order of persists, and its the responsibility of the hardware to enforce the persist order. This chapter considers how to implement PM transactions in a way that minimizes persist dependencies using various persistency models. We show that a simple transaction

<sup>&</sup>lt;sup>1</sup>Ensuring recoverability without transactions also requires the ability to order writes.

system design enforces many unnecessary persist dependencies and that these dependencies greatly slow down common transaction workloads. And, that most of the unnecessary dependencies arise as a consequence of performing the commit step of the transaction while locks are held, and how to remove these dependencies by deferring this commit until after locks are released.

We first derive the minimal persist ordering requirements to implement correct transactions under an idealized programming interface that can specify arbitrary ordering constraints to hardware (Section 3.2). However, such a programming interface is unrealistic; we use practical persistency models from Chapter II to express persist dependencies. We then analyze a straightforward transaction implementation, synchronous commit transactions (SCT), demonstrating how it overconstrains persist ordering (Section 3.3). Instead, we propose deferred commit transactions (DCT), which can achieve minimal ordering constraints under sufficiently expressive interfaces (Section 3.4). We evaluate our transaction implementations using the TPCC and TATP transaction processing workloads (Section 4.4) and end with a survey of related work (Section VI).

### **3.2 Transactions under Idealized Ordering**

It is not easy for software to express persist dependencies. Simply ordering the instructions that store data to PM is not sufficient: writes to memory (including PM) are cached and may not be written from the CPU cache to PM in the same order the corresponding instructions were executed [32]. In this section, we suppose that software has the ability to specify precisely the persist dependencies for all writes to PM. While this is unrealistically expressive, it provides a useful baseline upon which to build an idealized transaction system that minimizes persist dependencies. In later sections, we implement transactions built on more realistic interfaces and show how a naive implementation of transactions on these interfaces introduces unnecessary ordering constraints.

The most precise way to specify persist dependencies is as a partial order over all persists. This partial order can be expressed as a directed acyclic graph (DAG), where a node in the graph represents a persist, and an edge exists from node A to node B iff the persist represented by node A must occur no later than the persist represented by node B (note that this condition can be satisfied by performing the two persists atomically). In a system with idealized ordering, the software can express a constraint between any two persists, including persists that occur on separate threads.

We next describe how to build a simple transaction system, given the ability to express general partial orders over all PM writes.

#### **3.2.1** Transaction design

There are many ways to implement transactions [39], with one basic design choice being which version to log of the data being modified in a transaction: the data before the modification (undo logging [40, 11, 41]), the data after the modification (redo logging [7]), or both (e.g., ARIES [20]). In this chapter, we implement transactions with undo logging. We believe this design fits well with storing data directly in PM: both committed and uncommitted data are stored in place, so software can always read the most recent data directly from the in-place data structure (assuming appropriate locks are held). In contrast, if transactions are implemented with a redo log, reads of uncommitted data must be intercepted and redirected to the redo log.

We further implement several common optimizations required to achieve high transaction concurrency. We implement per-thread, distributed logs [7, 21], to avoid the scalability constraints of a centralized log. Our undo log records a copy of data (physical undo records) before it is mutated rather than a "synchronous log-and-update" approach (like PMFS [41]), as the latter requires more persist ordering constraints. We leverage checksum-based log entry validation [42] so that non-atomic writes to a log entry can proceed in parallel, but recovery software can deduce whether a log record was fully written without requiring a separate "valid" bit. This optimization eliminates one persist ordering constraint and is similar to the torn-bit optimization in Mnemosyne [7] and eager commit [19]. We assume concurrency control via arbitrarily fine-grain locking-a transaction must hold all required locks before executing (i.e. static transactions). Requiring a transaction to hold all locks before executing implies that all the data that can possibly be modified by the transaction is known a priori. If such knowledge is not available, a program must execute a read phase to identify all regions it might touch and acquire all locks, and then begin execution (similar to the approach used to implement deterministic transactions [43]).

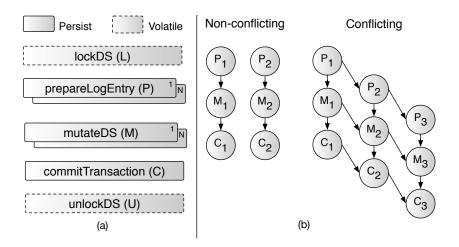

Figure 3.1(a) depicts the high-level steps of an undo-logging transaction. Steps outlined in a dotted box modify only volatile memory locations; those outlined in a solid box write to persistent memory. We briefly describe each step:

**Figure 3.1:** *Ideal undo-loggins transactions:* (*a*) *Steps in an undo transaction.* (*b*) *Persist dependencies in a transaction sequence.*

- lockDS (L): Acquire all locks to ensure mutual exclusion of the transaction. Locks are held in volatile memory.

- **prepareLogEntry** (**P**): Allocate log space and copy the prior state of all data that will be mutated to the log.

- mutateDS (M): Modify the data structure in place.

- **commitTransaction** (**C**): Commit the transaction by marking the undo log entry invalid; the transaction will no longer be undone during recovery.

- unlockDS (U): Release all locks acquired by lockDS.

We represent transactions with three persist nodes, corresponding to the three steps that perform durable writes, *prepareLogEntry* (P), *mutateDS* (M) and *commitTransaction* (C).

### 3.2.2 Minimal Persist Dependencies

We next analyze the minimal persist dependencies required for correct recovery of an undo-logging transaction. We consider two transactions,  $T_m$  and  $T_n$ , which acquire lock sets *Locks<sub>m</sub>* and *Locks<sub>n</sub>*, respectively. The transactions conflict if their lock sets intersect (i.e., they mutate overlapping data). We require order across conflicting transactions (the order in which they acquire locks); the subscripts indicate this order—in our example, m < n. *transactionStep<sub>m</sub>* indicates completion of a particular step in the transaction  $T_m$  (and all its associated persists). Recovery correctness requires the following order relationships:

$$prepareLogEntry_m \leq_p mutateDS_m$$

(3.1)

$$mutateDS_m \leq_p commitTransaction_m$$

(3.2)

$\forall (m,n)$ :

$$(unlockDS_m \leq_v lockDS_n) \land (Locks_m \cap Locks_n \neq \phi)$$

$$prepareLogEntry_m \leq_p prepareLogEntry_n$$

(3.3)

$$mutateDS_m \leq_p mutateDS_n$$

(3.4)

$$commitTransaction_m \leq_p commitTransaction_n$$

(3.5)

• Within one transaction, the log entry must be complete before data structure mutation (Eq. 3.1), and mutation must be complete before the transaction commits (Eq. 3.2). These dependencies ensure that any incomplete transaction can be rolled-back during recovery.

• Between conflicting transactions, preparing the log, mutating data, and commit must be ordered (Eqs. 3.3, 3.4, 3.5). These dependencies ensure that: (1) Mutations from conflicting transactions persist in lock-acquisition order (Eq. 3.4). (2) During recovery, active log entries from conflicting transactions can be undone in the appropriate order (Eqs. 3.3, and 3.5). Note that no dependencies exist between non-conflicting transactions.

Next, we discuss how the above constraints ensure recovery correctness.

**Intra-transaction:** Once a transaction begins, if failure occurs, one of two scenarios arise.

- No valid log entry: As per Eqs. 3.1 and 3.2, the transaction has either successfully committed or hasn't finished preparing a log. In either case, the data structure is in a consistent state; no recovery is required.

- Valid log entry: In this case, the data structure is recovered to a consistent state using the log entry, which undoes all mutations.

Note that it is unnecessary to distinguish a partially from a fully written log entry, since an incomplete undo record has no effect.

**Inter-transaction:** Since persists from multiple conflicting transactions may be inflight at the same time, a situation might arise where a particular region of the data structure has multiple associated log entries during recovery. We analyze the scenario with two conflicting log entries, which readily generalizes to additional entries. As above, let  $T_m$  and  $T_n$  be the conflicting transactions, such that m < n and let  $Log_m$  and  $Log_n$  be the corresponding log entries. Since we know log entries of conflicting transactions are created and

committed in order (Eqs. 3.3 and 3.5), one of three possible scenarios might arise during recovery:

- Both *Log<sub>m</sub>* and *Log<sub>n</sub>* exist: If multiple undo logs exist, the recovery system should undo the transactions from youngest to oldest, according to the order locks were acquired. It determines this order by consulting lock-acquisition timestamps, which are recorded in the log entries. *Log<sub>n</sub>* must be undone before *Log<sub>m</sub>*. Therefore, the recovery mechanism must know the order of the transactions (i.e., the order locks were acquired).

- Only  $Log_n$  exists: In this case, only one log entry has to be undone. Eq. 3.5 precludes the case where  $Log_m$  exists but transaction *n* has committed.

- Neither exist: In this case, both the transactions have successfully committed and hence no undo operations are required.

The "mutate in order" constraint (Eq. 3.4) ensures that the data structure mutations are performed in the serialized order of the conflicting transactions, which is required in the common case where no failure occurs. Hence, we have shown that the all the constraints mentioned in this section are required by the recovery mechanism.

#### **3.2.3** Persist critical path analysis

In later sections, we evaluate alternative transaction implementations by comparing their persist dependency critical path to the ideal persist dependency DAG. Conflicting transactions incur additional dependencies that are absent among non-conflicting transactions. Hence, we characterize the critical path under two extreme scenarios, one where all transactions are non-conflicting, and one where all transactions conflict. Figure 3.1(b) depicts the ideal DAG for conflicting and non-conflicting transaction sequences. Nodes in this figure correspond to the (concurrent) sets of persist operations performed in each transaction step (we omit steps that modify only volatile state). Edges indicate persist dependency between nodes (more precisely, pairwise persist dependencies between all persists represented by each node).

Under each scenario, we assume x transactions are performed, and t threads concurrently execute those transactions. In the non-conflicting scenario, the x transactions all acquire disjoint locks and modify disjoint data. Therefore, there are no persist order dependencies across threads; the critical path is determined solely by persist ordering constraints that arise on a single thread. In this scenario, the ideal persist critical path length is 3—the intra-transaction ordering constraints—independent of x or t.

In the conflicting scenario, we assume all x transactions mutually conflict (they all require a lock in common). Therefore, the persist critical path follows the total order of these x transactions, as established by the order the locks are acquired. In this case, the persist critical path propagates through the commit node of each transaction, resulting in a critical path length of x + 2 persist operations. Again, the critical path is independent of the number of threads *t*.

While persist critical paths for an ideal DAG are quite short, achieving this ideal is difficult with currently proposed programing interfaces, as we show next.

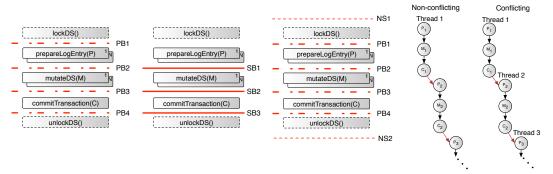

(a) SCT under epoch persistency (b) SCT under synchronous ordering (c) SCT under strand persistency (d) Persist critical path (epoch persistency)

**Figure 3.2:** Synchronous-commit transaction designs: Synchronous-commit transactions under epoch persistency, synchronous ordering, and strand persistency. The red arrows in (d) represent the unnecessary dependencies enforced when compared to the minimal dependencies shown in Figure 3.1(b).

### **3.3** Synchronous commit transactions (SCT)

Section 3.2 showed how to implement transactions under an idealized programming model allowing arbitrary persist dependencies. We next examine how to implement transactions using more realistic mechanisms.