# Heterogeneous Mobile Platform Characterization and Accelerator Design

by

Cao Gao

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2017

#### **Doctoral Committee:**

Professor Trevor N. Mudge, Co-Chair Assistant Professor Ronald G. Dreslinski Jr., Co-Chair Professor David Blaauw Assistant Professor Hun-Seok Kim Assistant Professor Jason Mars

### Cao Gao

caogao@umich.edu

ORCID iD: 0000-0001-6858-1655

© Cao Gao 2017

All Rights Reserved

To my family.

#### ACKNOWLEDGMENTS

First and foremost I would like to thank my advisor Professor Trevor Mudge. It was very fortunate for me to have him as an advisor who taught me so much on so many things, both about research and life. If I have to pick one of his many advises that had influenced me, it would be to focus the limited time on topics that are really important and meaningful. In addition, his laid back style and connections allowed me to explore a wide range of research projects and collaborate with different people. I am also really grateful for his support, guidance and patience during those hard times in my PhD. I also would like to thank my advisor Professor Ronald Dreslinski. From the first the day I joined the TRON (Trev + Ron) group, he has been very helpful in getting me started on research topics, designing experiments, organizing results and stories, and many other things. Those nights of paper editing together in CSE are very memorable to me. This thesis would not be possible with them.

I would like to thank several other faculty members that I have worked with during my PhD. It was a great experience collaborating with Professor Jason Mars and Professor Lingjia Tang. Their enthusiasm towards research was always an inspiration for me. In addition, it was Jason who introduced me to Professor David Blaauw and Professor Hun-Seok Kim, which led to a great collaboration during the last one and half years of my PhD. I learned great deal from David and Hun-Seok from our inter-group weekly meetings with Trev and Ron. Professor Carole-Jean Wu, Professor Valeria Bertacco, and Professor Todd Austin have all helped me with their valuable suggestions and feedback.

To my lab-mates in TRON lab: Yajing Chen (and Shengshuo Lv), Nilmini Aberaytne,

Yiping Kang, Johann Hauswald, Tony Gutierrez, Joseph Pusdesris, Kuangyuan Chen, Byoungchan Oh, Jonathan Beaumont, Dong-Heyon Park, and Qi (Chi-master) Zheng. Knowing them is the best treasure I found here at Michigan. Not only did I get meaningful and insightful discussion about research, but also antidotes about all the other countries and cultures, continuous encouragement and support, and most importantly, a lot of fun time together. I would also like to thank Chris Emmons and Dam Sunwoo, who helped me had a good summer internship at ARM research.

Outside my group, there are many friends who helped me enjoy my life in Ann Arbor, for which I am very grateful. I would like to thank all my friends in the CSE department, especially Chang-Hong Hsu and Doowon Lee, for exchanging interesting information and ideas on research and graduate student life in general. I also am grateful to my Chinese friends outside the department, especially Xiang Yin and Zhaojian Li, for all the fun times together. It was wonderful to have them here far away from our home country.

Finally, I would like to thank my family. My mother have always been supporting and encouraging me these years, and special thanks to her. Together with my late father, they shaped me to become the person I am today. My extended family has been very supportive to me as well, and I cannot thank them enough.

# TABLE OF CONTENTS

| Dedicatio   | n                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowle    | edgments                                                                                                                                                                                                           |

| List of Fig | gures                                                                                                                                                                                                              |

| List of Ta  | bles                                                                                                                                                                                                               |

| Abstract    |                                                                                                                                                                                                                    |

| Chapter     |                                                                                                                                                                                                                    |

| 1 Introdu   | ıction                                                                                                                                                                                                             |

| 1.2         | Heterogeneous Mobile Platforms1Contributions2Organization5                                                                                                                                                         |

| 2 Backgr    | ound                                                                                                                                                                                                               |

|             | Mobile Platforms62.1.1 Mobile Device Utilization62.1.2 The status quo for wearables10Wearable Applications112.2.1 Deep Learning Algorithms112.2.2 Always-on applications for wearables13                           |

| 3 An Ana    | alysis of Mobile Device Utilization                                                                                                                                                                                |

| 3.1 3.2     | Introduction       16         Methodology       18         3.2.1 System Setup       18         3.2.2 Measurement       19         3.2.3 Benchmarks       20                                                        |

| 3.3         | Results       26         3.3.1 Overall Results       26         3.3.2 Core Scaling       30         3.3.3 Heavy Load Scenarios       32         3.3.4 Alternative Architecture       35         3.3.5 GPU       36 |

| 3.4       | Suggestions                                                           |

|-----------|-----------------------------------------------------------------------|

|           | 3.4.1 TLP vs. Time                                                    |

|           | 3.4.2 Energy Efficiency of Big and Little Cores                       |

|           | 3.4.3 Thread CPU Time Distribution                                    |

| 3.5       | Related works                                                         |

|           | 3.5.1 Mobile Device Workload Characterization                         |

|           | 3.5.2 Mobile Benchmarks                                               |

|           | 3.5.3 Parallelism in Programs                                         |

|           | 3.5.4 Mobile Device Power Consumption                                 |

| 3.6       | Conclusion and Discussion                                             |

| 4 A Low   | Power Accelerator for Always-On Applications in Wearable Devices . 49 |

| 4.1       |                                                                       |

| 4.2       |                                                                       |

| 7.2       | 4.2.1 Always-on applications                                          |

|           | 4.2.2 The status quo for wearables                                    |

|           | 4.2.3 Non-uniform scratchpad architecture                             |

| 4.3       | 1                                                                     |

| 1.5       | 4.3.1 Pre-silicon                                                     |

|           | 4.3.2 Post-silicon                                                    |

| 4.4       | Accelerator design example                                            |

|           | 4.4.1 Architecture                                                    |

|           | 4.4.2 Operation                                                       |

|           | 4.4.3 Instruction set                                                 |

| 4.5       | Design evaluation                                                     |

|           | 4.5.1 Accelerator                                                     |

|           | 4.5.2 Baseline                                                        |

|           | 4.5.3 Benchmarks                                                      |

| 4.6       | Results                                                               |

|           | 4.6.1 Pre-silicon NUSA design                                         |

|           | 4.6.2 Multi-application scheduling                                    |

|           | 4.6.3 Post-silicon NUSA assignment                                    |

|           | 4.6.4 Post-silicon runtime scheduling                                 |

|           | 4.6.5 End-to-end applications                                         |

| 4.7       | Related works                                                         |

| 4.8       | Conclusion                                                            |

| 5 Conclu  | sions                                                                 |

| 5.1       | Summary                                                               |

|           | Future Directions                                                     |

|           | phy                                                                   |

| Piningi a | hmi                                                                   |

# LIST OF FIGURES

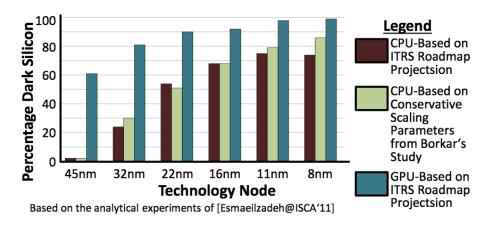

| 1.1<br>1.2 | Dark silicon trends for different technology nodes [1]                                                                                                                                                                                                                                                                                                                                                                                                                   | 3        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

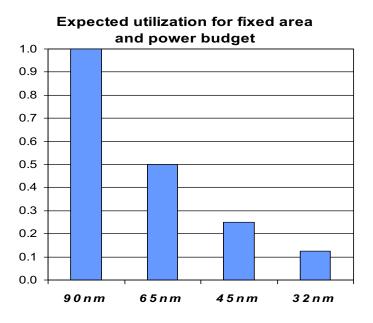

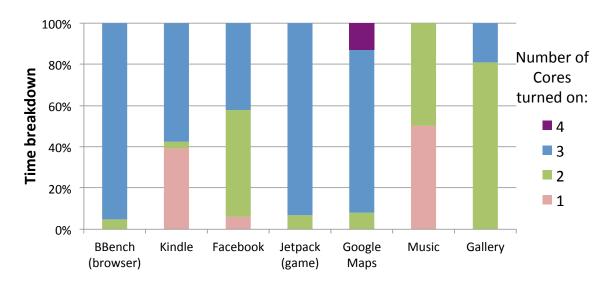

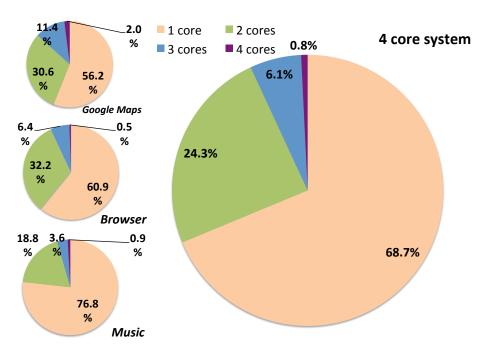

| 2.1 2.2    | Time breakdown of number of cores activated by the Android OS                                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>8   |

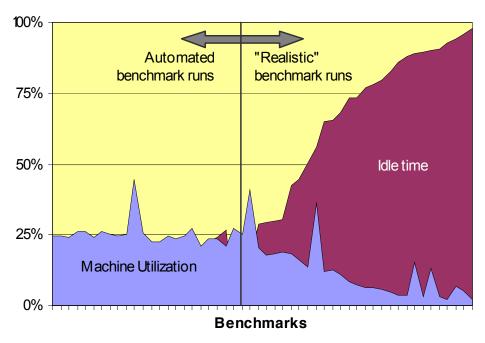

| 2.3        | Figure qualitatively describing the utilization differences between automated                                                                                                                                                                                                                                                                                                                                                                                            | 9        |

| 2.4        | desktop workloads and "realistic" runs performed by a user [3]                                                                                                                                                                                                                                                                                                                                                                                                           | 12       |

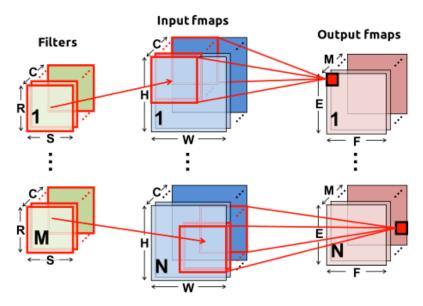

| 2.5        | Convolutional Neural Network                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13       |

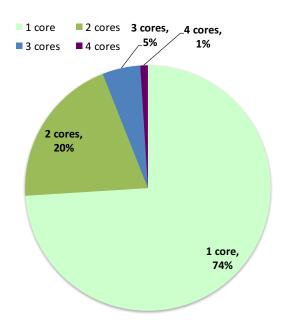

| 3.1        | Time breakdown of how the multi-core is utilized. The big pie chart on the right shows an average result of all application categories we tested. The smaller pie charts show the breakdown of three representative kinds of apps: Google Maps with the highest TLP, stock Browser, and stock Music with a law TLP.                                                                                                                                                      | 20       |

| 3.2        | low TLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28       |

| 3.3        | do not reflect actual results                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29<br>30 |

| 3.4        | Increase of TLP with background apps (shown as red regions)                                                                                                                                                                                                                                                                                                                                                                                                              | 31       |

| 3.5        | CPU breakdown for 3-core and 2-core system. This result is the average of all                                                                                                                                                                                                                                                                                                                                                                                            |          |

|            | applications                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31       |

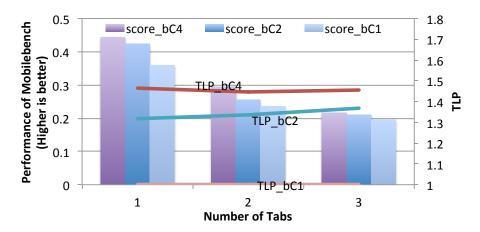

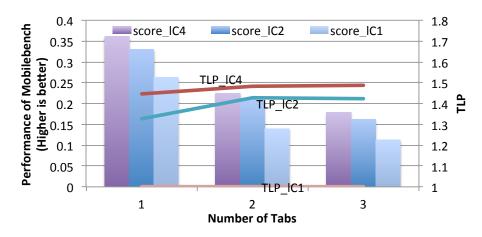

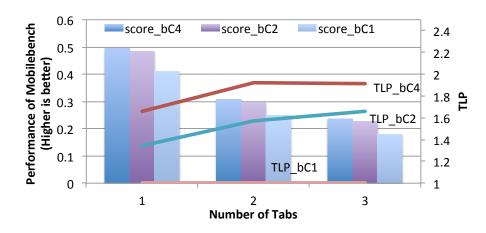

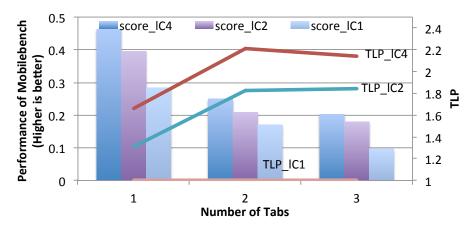

| 3.6        | Performance and TLP results for browser. Performance are shown in columns and TLP in lines. Performance scores are calculated by taking the inverse of MobileBench rendering time then normalize against the worst score in each graphs. For instance, score_bC4 stands for performance of four big cores, IC2 for two little cores, etc. For each CPU configuration, we test three scenarios: 1, 2 and 3 tabs running MobileBench on Chrome. This graph shows big cores |          |

|            | with stock Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33       |

| 3.7        | Performance and TLP: little cores with stock Browser                                                                                                                                                                                                                                                                                                                                                                                                                     | 34       |

| 3.8        | Performance and TLP: big cores with Chrome                                                                                                                                                                                                                                                                                                                                                                                                                               | 34       |

| 3.9        | Performance and TLP: little cores with Chrome                                                                                                                                                                                                                                                                                                                                                                                                                            | 34       |

| 3.10       | TLP result for the little cores                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35       |

| 3.11       | Average CPU Time breakdown: little cores                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35       |

| 3.12       | TLP result for the Origenboard (Quad-core 1.4 GHz A9)                                                                                                                                                                                                                                                                                                                                                                                                                    | 36       |

| 3.13 | Average CPU Time breakdown: Origenboard                                                                                                                  | 37  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 | TLP result for the Dragonboard (Quad-core 2.15 GHz Krait 300)                                                                                            | 37  |

| 3.15 | Average CPU Time breakdown: Dragonboard                                                                                                                  | 38  |

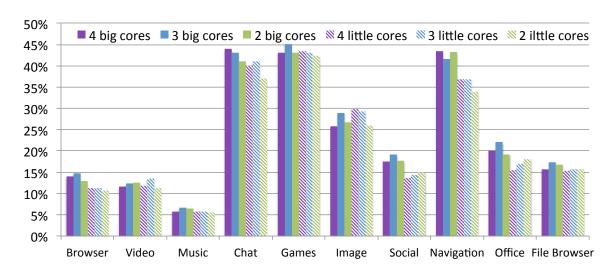

| 3.16 | GPU utilization of different category of apps. Columns with different colors                                                                             | 20  |

| 2 17 | 1 5 6                                                                                                                                                    | 39  |

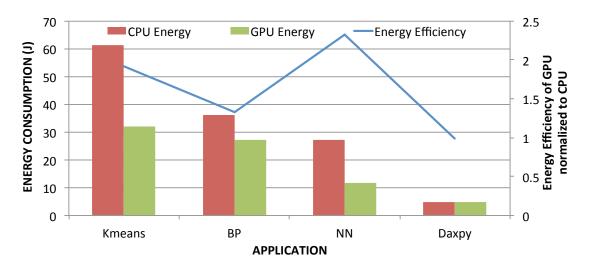

| 3.17 | Energy consumption and energy efficiency (defined as performance per watt)                                                                               | 40  |

| 2 10 | comparison for Krait CPU vs. Adreno GPU                                                                                                                  | 40  |

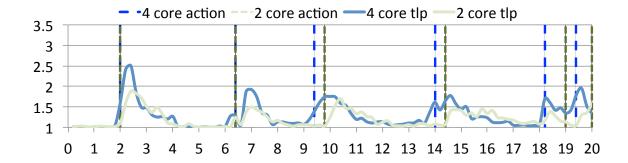

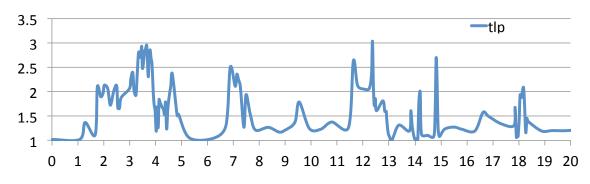

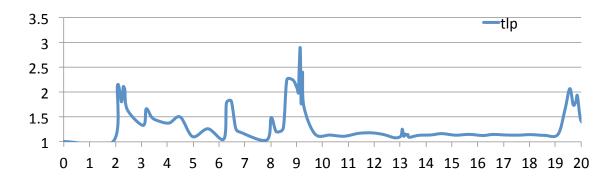

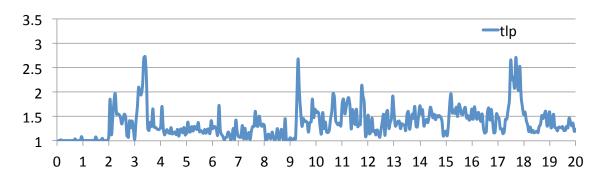

| 3.18 | TLP vs. time in seconds for mobile applications. For Browser, the solid lines represent TLP, and the dashed vertical lines show when there is an action, |     |

|      | such as application startup or opening a new webpage. Actions are labeled by                                                                             |     |

|      | circled numbers. This graph is for stock browser (using 4 cores)                                                                                         | 42  |

| 3.19 | TLP vs. time: chrome                                                                                                                                     | 42  |

| 3.20 | TLP vs. time: MXPlayer                                                                                                                                   | 43  |

| 3.21 | TLP vs. time: Angry Birds                                                                                                                                | 43  |

| 3.22 | Performance and power under different frequency and cores (tested using Mo-                                                                              | 7.7 |

| J.22 | bileBench). Lines represent different cores configurations; dots on lines repre-                                                                         |     |

|      | sent different frequencies, with lower frequencies (thus poor performance) on                                                                            |     |

|      | the left. Error bars are drawn to a show range of scores for each dot                                                                                    | 43  |

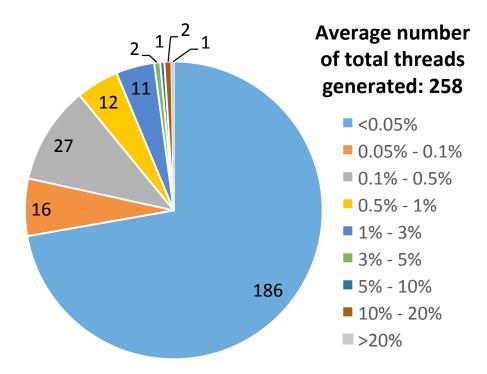

| 3.23 | Thread CPU time distribution. We break down the threads by their CPU time                                                                                |     |

|      | into 8 categories, which are shown in the legend. For instance, "<0.05%"                                                                                 |     |

|      | means this thread only occupies less than 0.05% of all CPU time, ">5%-10%"                                                                               |     |

|      | means larger than 5% but less than 10%. For the applications we tested, the                                                                              |     |

|      | average number of total threads generated is 258. Each area for the pie chart                                                                            |     |

|      | shows the average number of threads that fall into this category. It shows that                                                                          |     |

|      | most threads are short living.                                                                                                                           | 45  |

| 4.1  | Battery constraint in wearable devices                                                                                                                   | 50  |

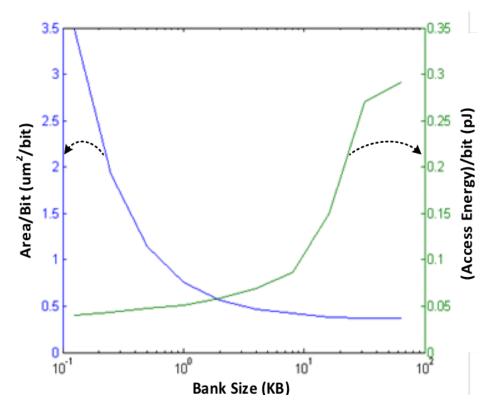

| 4.2  | Trade-off between area and energy (data from SRAM compiler)                                                                                              | 56  |

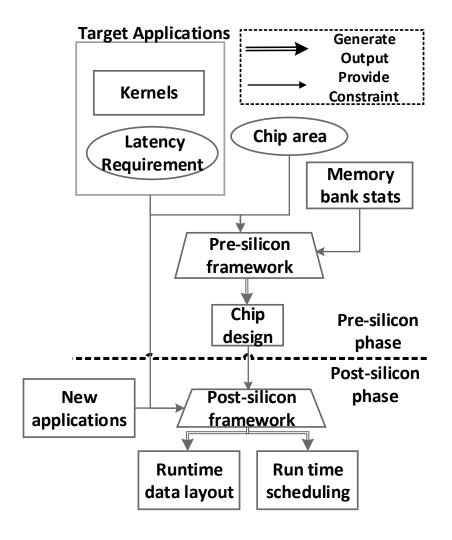

| 4.3  | Overall description of framework                                                                                                                         | 58  |

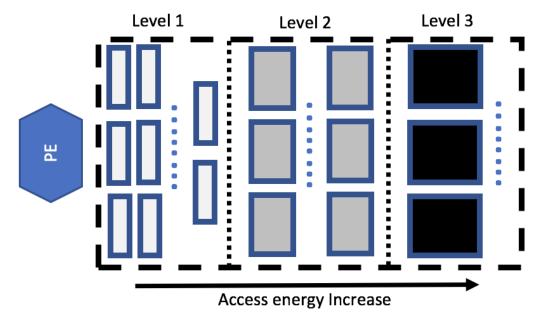

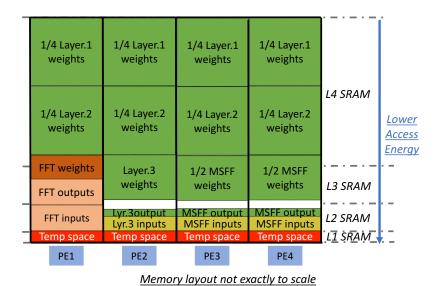

| 4.4  | Example memory layout. Banks are stacked on one side of the processing ele-                                                                              |     |

|      | ment (PE), starting from smaller banks. The height of the stack is determined                                                                            |     |

|      | by the framework, striking a balance between average wire distance and total                                                                             |     |

|      | area                                                                                                                                                     | 59  |

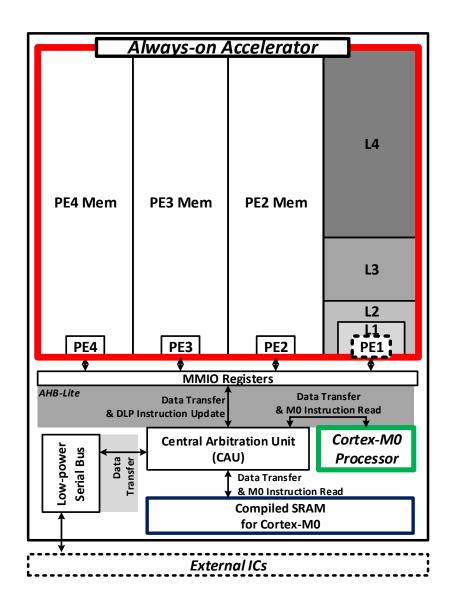

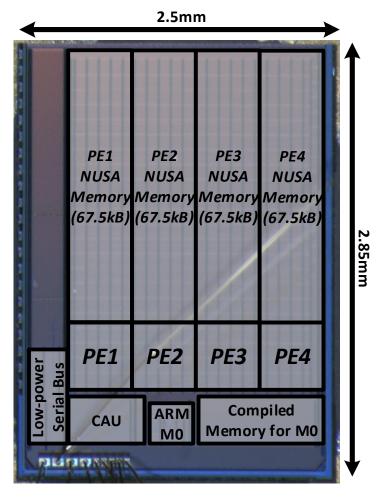

| 4.5  | Overall architecture of the accelerator                                                                                                                  | 62  |

| 4.6  | Die photo and specifications of the accelerator chip                                                                                                     | 63  |

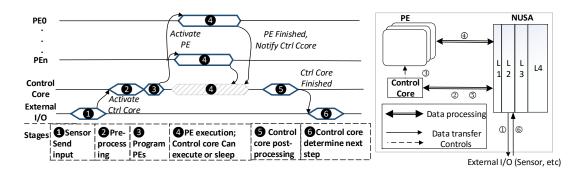

| 4.7  | Timing and block diagram of accelerator operation                                                                                                        | 68  |

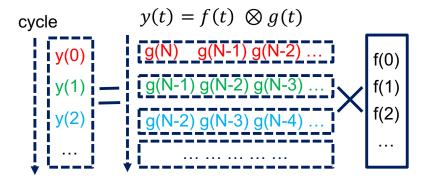

| 4.8  | Convolution using MAC instruction                                                                                                                        | 71  |

| 4.9  | Convolution using FFT instruction                                                                                                                        | 71  |

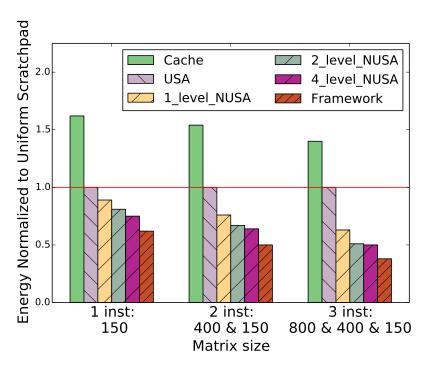

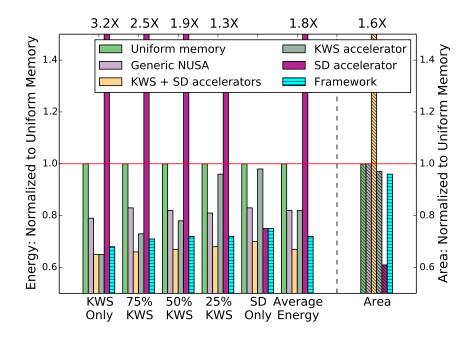

| 4.10 | Energy reduction with NUSA framework: MAC instructions                                                                                                   | 77  |

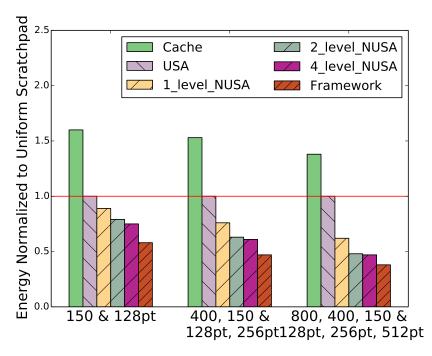

| 4.11 |                                                                                                                                                          | 77  |

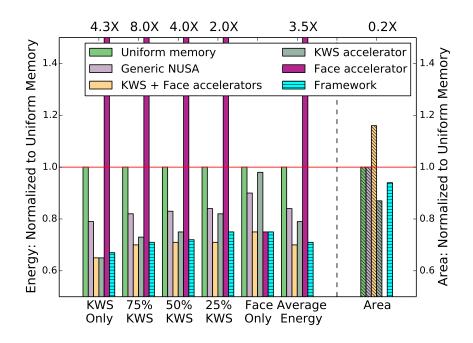

| 4.12 | Multi-application scheduling. Smartglass: Key Word Spotting (KWS) and                                                                                    |     |

|      | Face Detection (Face)                                                                                                                                    | 79  |

| 4.13 | Multi-application scheduling. Smartwatch: Key Word Spotting (KWS) and                                                                                    |     |

|      | Seizure Detection (SD)                                                                                                                                   | 79  |

| 4.14 | NUSA assignment for keyword spotting: data analysis                                                                                                      | 81  |

| 4.15 | NUSA assignment for keyword spotting: data assignment                       | 81 |

|------|-----------------------------------------------------------------------------|----|

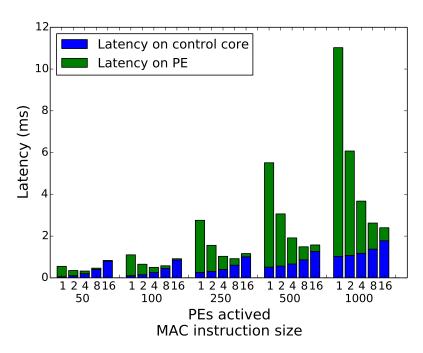

| 4.16 | Runtime scheduling for MAC instruction: latency for different number of PEs |    |

|      | activated                                                                   | 83 |

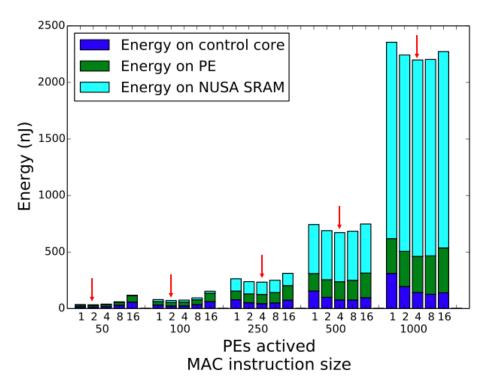

| 4.17 | Runtime scheduling for MAC instruction: energy for different number of PEs  |    |

|      | activated                                                                   | 83 |

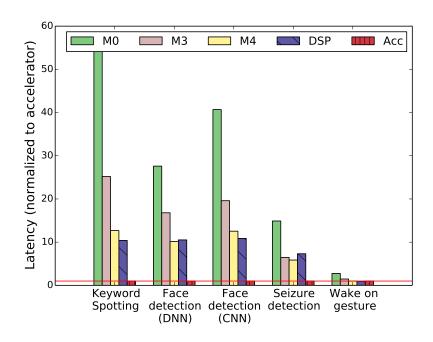

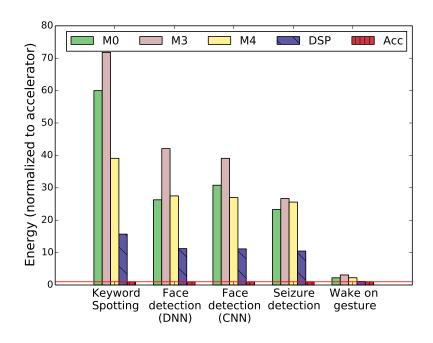

| 4.18 | End-to-end application: latency                                             | 85 |

| 4.19 | End-to-end application: energy                                              | 85 |

# LIST OF TABLES

| 3.1 | Applications                                                                  | 22 |

|-----|-------------------------------------------------------------------------------|----|

| 3.2 | TLP results for the Odroid board — using ondemand governor                    | 27 |

| 4.1 | Expected battery life target for wearable devices [4]                         | 51 |

| 4.2 | Accelerator instruction set. For "configurable fields", common fields such as |    |

|     | data location or precision are not included                                   | 69 |

| 4.3 | Always-on applications evaluated in this work                                 | 74 |

#### **ABSTRACT**

Due to power constraints, growing sections of a chip need to remain passive. This is often referred to as the "dark silicon" problem. This problem is more severe on mobile platforms, especially on emerging IoT and wearable devices, due to their strict power envelope and energy budget. Heterogeneous architecture with specialized hardware is an effective way to utilize the limited active transistor count. To guide heterogeneous mobile platform design, analyzing current and near-future mobile workloads and building specialized hardware based on the analysis is essential. To this end, this dissertation starts with a quantitative analysis of current mobile applications on smartphones, followed by an accelerator-based solution for efficient execution of wearable workloads, with an emphasis on machine learning and signal processing kernels.

The first part of the thesis focuses on a study of mobile device utilization, where the results argue against using many (more than 4) cores in mobile devices, and suggest a flexible heterogeneous architecture to accommodate utilization variations. To meet the increasing computational need of mobile devices, many vendors try to increase the number of CPU cores in mobile device SoCs. However, it does not translate proportionally into performance gain and power reduction. This work analyzes the behavior of a wide range of commonly used mobile applications, using *Thread Level Parallelism* (TLP) as a major metric. The results demonstrate that mobile applications have TLP less than 2 on average, and we observe a small return on utilization when the number of cores is increased. Further analysis shows that TLP tends to appear in peaks and valleys, which gives opportunity for using flexible, heterogeneous mobile architecture for better energy efficiency.

The second part of the thesis consists of a low-power accelerator design for always-on applications used in wearable devices. A large class of these always-on applications, including many deep learning and signal processing applications, execute in a deterministic and repeatable fashion. This design takes advantage of this determinism by replacing the traditional cache based architecture with a non-uniform scratchpad architecture (NUSA). A framework is developed, which determines the most energy efficient NUSA scratchpad design within area constraints, and identifies the most energy efficient data assignment and runtime schedule given the target application. A fabricated prototype accelerator is also presented as an illustration of the technique. On average, a  $2.1 \times$  reduction in energy can be achieved by using a NUSA architecture compared to a uniform scratchpad architecture, and a  $10 \times$  to  $36 \times$  reduction compared to general purpose ARM M-class cores and DSP.

### **CHAPTER 1**

# Introduction

# 1.1 Heterogeneous Mobile Platforms

The scaling of CMOS technology had been enabling faster switching and lower power consumption for the past decades. The traditional Dennard scaling [5] states that as transistors get smaller, their power density stays constant, so the power consumption stays in proportion with area. Therefore, as we shrink the transistors down in size in conjunction to Moore's law [6], we would proportionally achieve lower power consumption per transistor, maintaining the overall power density.

However, Dennard scaling is reaching its physical limits to an extent that voltage cannot be scaled down as much as transistor gate length. Along with a rise in leakage current, this results in increased power density, rather than a constant power density. To ensure a safe operation, it is essential for the chip to perform within a fixed power budget [7], usually called the thermal design power (TDP) constraint. Increased power density under the same power budget means in order to avoid too high power dissipation, a certain part of computation, communication, and memory resources of an on-chip system cannot simultaneously be powered-on (at the peak performance level), and thus must stay "dark" [8, 9, 10]. The problem, therefore, is how to best utilize the abundance of transistors in the dark silicon era to continue to reap the rewards of Moore's Law down to the sub-10 nm node [11].

Mobile platforms with their even more strict power envelope and energy budget, suffers

Figure 1.1: Dark silicon trends for different technology nodes [1]

more from the dark-silicon problem. For instance, the TDP for a mobile SoC is 2.5 to 3W for smartphones, 5W for tablets [12], while the TDP for desktop CPU alone is around 100W [13].

An effective way to utilize the limited active transistor count is to user heterogeneous architecture with specialized hardware. In dark silicon era, there is a choice about which parts of the chip should be powered on, so optimal performance can be achieved under peak power and temperature constraints. Specialized hardware usually have much superior performance and energy efficiency than general purpose cores, which can be powered on when executing its target task.

## 1.2 Contributions

In order to guide heterogeneous mobile platform design, this thesis first analyzes current mobile applications on a smartphone platform. Mobile devices are becoming more powerful and versatile than ever, calling for better embedded processors. Following the trend in desktop CPUs, microprocessor vendors are trying to meet such needs by increasing the number of cores in mobile device SoCs. However, increasing the number does not translate proportionally into performance gain and power reduction. In the past, studies have shown that there exists little parallelism to be exploited by a multi-core processor in desktop plat-

Figure 1.2: Utilization wall [2]

form applications, and many cores sit idle during runtime. We investigate whether the same is true for current mobile applications, and ask the question if quad- and octa- core designs are beneficial. We analyze the behavior of a wide range of commonly used mobile applications. We measure their *Thread Level Parallelism* (TLP), which is the machine utilization over the non-idle runtime. Our results demonstrate that mobile applications have TLP less than 2 on average, and we observe a small return on utilization when the number of cores is increased. Test on high load scenarios suggest that this is due to the nature of mobile devices and utilization cannot be increased easily. However, further analysis shows that TLP tends to appear in peaks, which gives opportunity for multi-core devices to gain better power efficiency. In all, we suggest that increasing cores aggressively may not be the right choice, and looking into the interactive nature of mobile applications can a good direction.

Next, this thesis discuss a design of an ultra low-power accelerator for always-on applications in wearable devices. These applications, such as keyword detection or heart rate monitoring, pose a significant challenge in energy-efficient design. A large class of always-on applications execute in a deterministic and repeatable fashion. Determinism and repeatability mean that the optimal memory access pattern can be pre-computed statically,

removing the need for a cache and providing an opportunity to tailor the memory layout directly to the application. We present a non-uniform scratchpad architecture (NUSA) accelerator designed for this class of applications. To fully utilized the proposed NUSA, we develops a framework, which when given the target applications can: a) determines the most energy efficient NUSA scratchpad design within area constraints; and b) determines the most energy efficient data arrangement and runtime schedule given the target application. A fabricated prototype accelerator is presented as an illustration of our technique. We then generalize this prototype into an architecture that is used to evaluate a wider range of applications, and compare against traditional approaches. We show that, on average, a  $2.1\times$  reduction in energy can be achieved by using a NUSA architecture compared to a uniform scratchpad architecture, and a  $30\times$  reduction compared to a general purpose ARM M-class core.

In summary, this dissertation makes the following contributions:

- We construct a suite containing representative Android applications from a variety of categories, as well as their corresponding test actions.

- We measure the Thread Level Parallelism (TLP) of mobile applications on current mobile device platforms and show it is less than 2 on average.

- We observe diminishing returns of TLP when increasing the number of cores. Heavy-load test cases also show low TLPs, which suggests there is not a lack of hardware resources. Both demonstrate that having many powerful cores is over-provisioning.

- We make the case for the need of a flexible system that can accommodate both high performance and good energy-efficiency for different program phases.

- We suggest that a heterogeneous system is an adequate and energy-efficient solution for mobile devices.

- Identify the opportunity of utilizing the deterministic behavior of always-on applications in wearable devices, and the benefit of utilizing a non-uniform scratchpad architecture (NUSA).

- Design a framework which can generate a NUSA design for a wide set of applications, as well as tailor and map the applications to the target NUSA for the best energy-efficiency.

- Design a low power programmable accelerator for always-on wearable applications,

which has been fabricated as a prototype chip.

- Evaluate the framework by generalizing the accelerator design and comparing to general purpose core baselines, as well as cache and USA based accelerators.

# 1.3 Organization

This dissertation is organized as follows. In Chapter 2, background information about mobile and wearable devices is provided. Chapter 3 discuss an analysis of mobile device utilization. It demonstrates diminishing returns of TLP with increasing the number of cores, motivates a heterogeneous design for energy efficiency and accommodating Chapter 4 introduce an low-power accelerator design for always-on application in wearable devices. Finally, Chapter 5 provides concluding remarks and future research directions.

### **CHAPTER 2**

# **Background**

This chapter outlines some of the background information regarding mobile platform and common applications. First, a discussion regarding the utilization of mobile devices and are discussed. Next, some common applications. Specifically, applications on deep learning algorithm are introduced.

### 2.1 Mobile Platforms

#### 2.1.1 Mobile Device Utilization

Quite a number of mobile processors are made with four or even more cores today, which offer impressive computational potential to users. However, there are still high-end mobile SoCs that include only a dual-core CPU, and that still successfully provides desirable performance for its host mobile device. In order to make design choices, it is beneficial to analyze how much of the quad-core potential is being utilized.

We perform two preliminary experiments on an Origen board, a current mobile device platform with a quad-core 1.4GHz ARM Cortex-A9 CPU. First, we measure how many cores are actually activated by the OS when running an application. The Android system employs a CPU governor which turns individual cores on or off and changes their frequencies based on CPU loads. When it finds that a core sits idle for most of the time, it will turn it off to save power. We run a suite of commonly used applications with the default

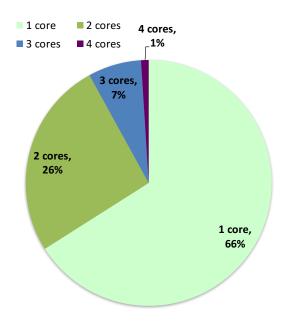

Figure 2.1: Time breakdown of number of cores activated by the Android OS

governor—ondemand. We find that the fourth core is only activated in 2 out of the 21 apps we tested. For nearly half of the apps, the OS also shuts off the third core for most of the time. We show part of our results in Fig. 2.1. We plot a breakdown of the time percentage that each system configuration spends for these applications. Different colors represent system configurations with different numbers of cores activated. For most of the applications, the fourth core is always shut down, For some of them, namely Email, Facebook, Music and Gallery in this graph, most of the time the third core is not activated as well. The only app in this graph that activates the fourth core is Google Maps. Browser and Jetpack (a game) do activate three cores for most of the time, but Facebook does so only for half of the time, and Email never. Note that activation does not mean utilization; it only means the OS thinks that this core *might* be utilized. The core could still sit activated and idle at the same time. We will show the core utilization in the results section.

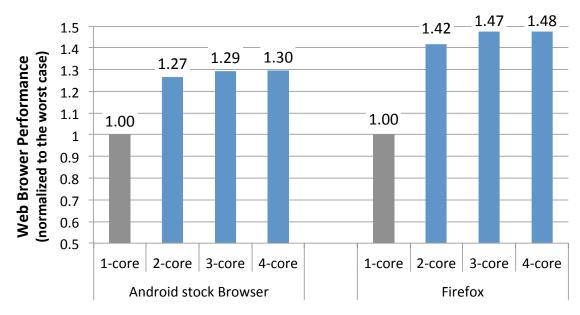

In the second experiment, we override system setup and manually set the number of cores activated in the system. Since web-browsing is among the most commonly used features on mobile devices [14], we run a browser benchmark, BBench [15] on two browsers, and compare the performance of different CPU configurations. We plot the results in Fig. 2.2. The score is the time taken to render the complete set of webpages in BBench,

Figure 2.2: BBench score for different number of cores.

and lower score means better performance. It is clear from the graph that a single-core system suffers from poor performance. However, the performance gain is negligible from dual-core to triple-core and quad-core. It may seem confusing why the OS activates 3 cores for BBench when there is such little performance improvement. Actually it again proves that activation does not mean utilization; the *ondemand* CPU governor in Android OS is performance-aware and will keep the core activated unless it is very unlikely to be utilized [16].

Both of these tests suggest a more thorough quantitative investigation of quad-core CPU utilization.

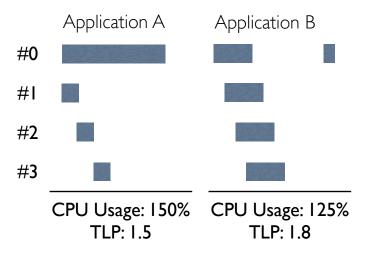

#### **2.1.1.1** Metrics

To evaluate the utilization of a multi-core system, we need a good metric for system profiling. A commonly used and accessible metric would be CPU utilization, which is simply the overall average CPU usage during runtime. However, it would underestimate the parallelism in mobile applications. Most of these apps are interactive, and there is a large portion of idle time for interactive applications, as shown in Fig. 2.3. The program itself

Figure 2.3: Figure qualitatively describing the utilization differences between automated desktop workloads and "realistic" runs performed by a user [3].

could be well parallelized and have a high machine utilization number during busy time. However, it sits on idle and waits for user input for most of the total running time, which drags down the average utilization number. To avoid that, we use *Thread Level Parallelism* (*TLP*) [17, 3]. TLP is defined as the machine utilization over the non-idle portions of the benchmark's execution. The formula for TLP is given by Equation. 2.1:

$$TLP = \frac{\sum_{i=1}^{n} c_i i}{1 - c_0} \tag{2.1}$$

where  $c_i$  is the fraction of time that i cores are concurrently running different threads, and n is the number of cores. Specifically,  $c_0$  represents idle time fraction, which is excluded because it does not count towards the program's parallelism. Note that TLP is not a performance metric; the software could still spawn threads that do not perform useful work. Nevertheless, it is the natural metric to measure multi-core utilization, especially for interactive applications like the ones on a smartphone. The TLP serves as a good indicator of the number of processors needed to support the execution of a parallelized workload.

#### 2.1.1.2 Early Studies on TLP

Flautner et al. [3] proposed the definition of TLP in 2000. At that time, multi-core was mostly exploited in research labs and appeared only in workstations and servers. They performed a study of TLP on desktop applications and found that a dual-core system improves the responsiveness of interactive programs. However, they also showed that desktop applications leveraged TLP very sparingly. This result was echoed 10 years later by Blake et al. [17] with a similar study of TLP of contemporary software and hardware, when multi-core had become the norm rather than the exception in home and office desktops. They reported that 2-3 cores were more than adequate for almost all but a few domain specific applications like Video Authoring. After observing low single-thread performance could have a small impact on the TLP, they claimed that software is lagging behind and is the main limiting factor in TLP.

Smartphones were already becoming popular during the time when Blake et al. presented their results, and they have continued to supplant desktops for many applications. To reflect this it is important to analyze TLP behavior on mobile devices because the original studies did not. Besides exploring a different hardware platform, we are also using a slightly different set of benchmarks from the original work. Some categories of desktop applications are rarely seen on mobile devices, such as Video Authoring and professional Image Authoring. We also make some investigations into frequency scaling, which is especially interesting for smartphones and tablets due to their tight power budget.

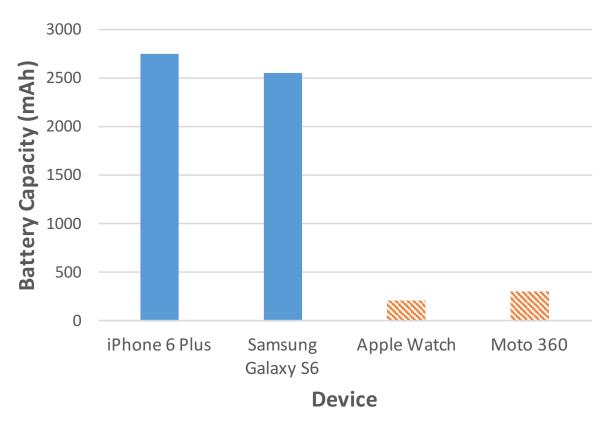

## 2.1.2 The status quo for wearables

Battery life is still a major constraint for current wearable devices (Table. 4.1.) One typical method of reducing power consumption in smartphones is to reduce the brightness or resolution of the screen, which takes up a large portion of the total power consumption. However, the display in wearable devices already consumes a much lower portion of total energy than those in a smartphone. It can be as much as  $20-40\times$  fewer pixels and has only

a relatively simple color scheme [18, 19]. Another major power consumer in wearables is the wireless connectivity module, which is usually implemented in very specific communication ASICs and is difficult to further optimize [20]. Therefore, optimizing the power consumption of the compute stack becomes critical.

# 2.2 Wearable Applications

In this section we discuss some of the common mobile applications, mostly used in Chapter 4. First, we introduce some recent deep learning algorithms used in near-future applications, namely Multilayer Perceptron (MLP) and Convolutional Neural Network (CNN). Then, we introduce some common always-on applications used in wearable devices.

### 2.2.1 Deep Learning Algorithms

Neural networks have been around for many decades[21, 22]. However, until 2006, deep, fully connected neural networks were commonly outperformed by shallow architectures that used feature engineering[23]. Three additional reasons have recently helped deep architectures obtain state of the art performance: large datasets, faster, parallel computers and new machine learning insights. In this time of "big data", huge datasets can be collected rather easily and cheaply by institutions, which can be used to train deep models with many parameters. Improvement of multi-core CPU and GPU computing architectures gives opportunity to execute a large number of matrix multiplications, which are required by these algorithms. All these leads to an increase of application using deep learning algorithms.

#### 2.2.1.1 General Structures

Even though Deep and Convolutional Neural Networks come in various forms, they share enough properties that a generic formulation can be defined. In general, these algorithms are made of a (possibly large) number of layers; these layers are executed in sequence so

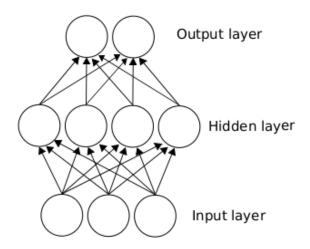

Figure 2.4: Multilayer Perceptron

they can be considered (and optimized) independently.

#### 2.2.1.2 MLP (Multilayer Perceptron)

The Multilayer perceptron (MLP) is a neural network consisting of multiple mutually interconnected layers of neurons. Every neuron in one layer is connected to every neuron in the following layer. A non-linear function is applied to the neurons output of each layer.

#### 2.2.1.3 CNN (Convolutional Neural Network)

Convolutional neural networks (CNNs) are mostly designed to recognize features in 2-dimensional image data, but are used for various other purposes as well. CNNs are primarily used for 2D image recognition, so we will illustrate their architecture on a 2D rectangular image consisting of pixels. Each pixel generally carries colour information. Colour can be represented by multiple channels (e.g. 3 RGB channels). For the sake of simplicity, we will consider only one single channel (shades of gray) while explaining the model. The neurons in CNNs work by considering a small portion of the image, let us call it subimage. The subimages are then inspected for features that can be recognized by the network. As a simple example, a feature may be a verticalline, an arch, or a circle. These features are then captured by the respective feature maps of the network. A combination of features is

Figure 2.5: Convolutional Neural Network

then used to classify the image. Furthermore, multiple different feature maps are used to make the network robust to varying levels of contrast, brightness, colour saturation levels, noise, etc.

## 2.2.2 Always-on applications for wearables

We examine several example categories of always-on applications, which are summarized in the following subsections.

#### 2.2.2.1 Keyword spotting

Keyword spotting is a detection task to identify the presence of specific spoken words in a stream of speech signals. It is often used to trigger automatic speech recognition and spoken dialog systems. It is common in wearable devices when hands-free activation is desired. Examples include detecting "OK Google" when wearing a Google Glass or "Hey Siri" when wearing an Apple watch. Keyword spotting can be implemented using classification techniques, such as hidden Markov models (HMM) [27] to identify different keywords. More recently machine learning algorithms based on Deep Neural Networks [28] and Re-

current Neural Networks [29] are being deployed because their better detection accuracy.

#### 2.2.2.2 Seizure detection

Epileptic seizure detection refers to the use of algorithms to recognize the occurrence of a seizure. Typically these algorithms are based on the analysis of biological signals from a patient with epilepsy. They can be deployed in smartwatches or health wristbands for quick, always-on detection. The algorithms are typically based on a nearest-neighbor classifier of EEG features [30, 31], or the RNN technology mentioned above [32, 33].

#### 2.2.2.3 Face detection

Face detection is the detection of a face in a scene. It is commonly used as a front-end to trigger facial recognition. It appears in Google Glass and smart home detection devices. Due to its wide range of application, face detection algorithms have been studied heavily. Recent implementations include DNNs [34] or Convolution Neural Networks (CNN) [35, 36]. The former is easier in terms of memory access patterns but the latter is usually more suitable for image processing.

#### 2.2.2.4 Wake on user gesture

Wake-on user gesture is the feature of some wearable devices which can be activated using certain user-specified gestures. This enables the device to recognize who is interacting. For an entertainment device, it can recognize the user and load the right game profile or music play list. For a home climate control, it can adjust the environment to the wearer's preference. This feature can be implemented using one-vs-all classification [37] or margin classifiers [38].

### **CHAPTER 3**

# An Analysis of Mobile Device Utilization

Mobile devices are becoming more powerful and versatile than ever, calling for better embedded processors. Following the trend in desktop CPUs, microprocessor vendors are trying to meet such needs by increasing the number of cores in mobile device SoCs. However, increasing the number does not translate proportionally into performance gain and power reduction. In the past, studies have shown that there exists little parallelism to be exploited by a multi-core processor in desktop platform applications, and many cores sit idle during runtime. In this chapter, we investigate whether the same is true for current mobile applications, and ask the question if quad- and octa- core designs are beneficial.

We analyze the behavior of a wide range of commonly used mobile applications. We measure their *Thread Level Parallelism* (TLP), which is the machine utilization over the non-idle runtime. Our results demonstrate that mobile applications have TLP less than 2 on average, and we observe a small return on utilization when the number of cores is increased. Test on high load scenarios suggest that this is due to the nature of mobile devices and utilization cannot be increased easily. However, further analysis shows that TLP tends to appear in peaks, which gives opportunity for multi-core devices to gain better power efficiency. In all, we suggest that increasing cores aggressively may not be the right choice, and looking into the interactive nature of mobile applications can a good direction.

### 3.1 Introduction

Nowadays, mobile devices are gradually taking over the functions of traditional desktop applications. High-definition video playback, interactive games and web browsing are commonly supported by the latest smartphones and tablets. These performance-intensive tasks need powerful hardware support, which drives microprocessor vendors to continuously produce better mobile CPUs. Given the strict power budget of mobile devices, vendors reached the limits of frequency scaling quickly and turned to multi-processors. The first dual-core smartphones, such as Galaxy S II and HTC Sensation, came to market in 2011. Most of the high-end smartphones released in 2012 were dual-core or quad-core; in April 2013, the Samsung Galaxy S4 was released with the *Exynos 5 Octa*, which uses ARM's big.LITTLE architecture and has a total of eight cores. Mediatek shipped their octa-core SoC in late 2013, and Qualcomm announced their octa-core CPU with eight A53s in early 2014 as well.

However, some recent smartphones are still equipped with dual cores. Apple's new A8 Chip for the iPhone 6, released in September 2014, uses a dual-core CPU and still provides satisfactory performance. This leads to the question: How much of the computation potential residing in multi-core CPUs is actually being utilized? On the desktop end, Blake et al. [17] did a study on *Thread Level Parallelism* (TLP) on a suite of representative desktop applications. Their work was to measure the core utilization in modern multi-core CPUs, and they suggested that the number of cores that can be profitably used is less than 3 for most commonly used applications. It is possible that mobile device applications have similar characteristics and cannot effectively utilize a quad-core CPU, let alone hexa- and octa-core. Moreover, the GPU, DSPs, and ASICs in these systems already exploit much of the parallelism, leaving little for the CPU.

To make some observations about the benefit of multi-core, we performed two preliminary experiments on an up-to-date quad-core mobile device platform. First, we measured how many cores are actually activated by the Android OS when running an application.

We found that the fourth core was only activated in 2 out of 21 apps, and the OS also shut off the third core for nearly half of the apps. Note that activation does not mean the core is in use; it only means the OS thinks that the core *might* be used. Second, we overrode system setup and manually set the number of activated cores in the system. Then we ran a browser benchmark [15]; we saw a significant performance improvement from single-core to dual-core, but negligible improvements from dual-core to triple- and quad-core. Both of these results show rather modest gains from high numbers of cores (here more than 2). In all, to measure how much parallelism actually exists is helpful to: a) inform vendors and prevent them from over-provisioning hardware that cannot be effectively used, b) highlight the need to find more parallelism, c) provide suggestions for a better design.

In this work, we analyze a broad range of popular mobile applications to determine how the growing number of cores are utilized. We measure the Thread Level Parallelism (TLP) of these applications. The results show that mobile apps are utilizing less than 2 cores on average, which means multiple cores are used rather infrequently. A small TLP scalability is observed for most applications, and increasing the number of cores has diminishing return on TLP. Even in heavy-load real-world scenarios with background applications or multi-tab browsing, there is still not enough work to keep utilization high. Due to the physical constraint and interactive user pattern, mobile applications tend to have less parallelism to exploit than desktop applications. The GPU and mobile co-processors on chip also reduce CPU load. All these factors, and the history of the slow pace of exploiting parallelism in desktop and mobile software environments [17, 40], indicate that having many powerful cores is over-provisioning. Further analysis suggests that current mobile applications can benefit from a system with the flexbility to satisfy high performance and good energy-efficiency for different application phases. We find that TLP behavior exhibits short peaks and long valleys rather than remaining constant. Peaks require high performance, but not necessary good energy-efficiency because these peaks are usually short, meaning that power has less affect on overall energy consumption. Valleys, on the other hand, desire

better energy-efficiency because they do not require high performance but usually dominate the application execution. There is also a number of other research opportunities that arise, such as building accelerators or customized hardware to further reduce the thread's TLP peaks with better energy efficiency, or building better OS infrastructure to utilize mobile heterogeneous systems.

To summarize, we make the following contributions:

- We construct a suite containing representative Android applications from a variety of categories, as well as their corresponding test actions.

- We measure the Thread Level Parallelism (TLP) of mobile applications on current mobile device platforms and show it is less than 2 on average.

- We observe diminishing returns of TLP when increasing the number of cores. Heavy-load test cases also show low TLPs, which suggests there is not a lack of hardware resources. Both demonstrate that having many powerful cores is over-provisioning.

- We make the case for the need of a flexible system that can accommodate both high performance and good energy-efficiency for different program phases.

The rest of the chapter is organized as follows: In Section 3.2 we describe the system setup, measurement method, and benchmarks used. Section 3.3 presents and analyzes the results. We discuss the related works in Section 3.5 and conclude the chapter in Section 3.6.

# 3.2 Methodology

## 3.2.1 System Setup

We use the Odroid XU+E board [41]. It has a Samsung Exynos 5410 SoC, which contains an ARM big.LITTLE octa core of four 1.6GHz A15s and four 1.2GHz A7s. Each core has

its own 32KB/32KB L1 instruction and data cache; the four A15s share a 2MB L2 cache and the A7s share a 512KB L2 cache. Either four A15s or four A7s can be enabled at the same time, but not a mixture of them. The Odroid board has a PowerVR tri-core GPU running at 480MHz and with 2GB main memory. It also has an on-board current/power semiconductor sensor which measures the current/power consumption of CPUs, GPU and memory separately<sup>1</sup>. We run Android version 4.4.2 (Kitkat) and Linux kernel version 3.4.5. We choose the use the ART runtime instead of the older Dalvik. A web-cam is connected as smartphone camera.

#### 3.2.2 Measurement

#### 3.2.2.1 TLP

To get the TLP number, we track all the context switches that happen in the system, which reveals the information about the status of each core. For instance, a context switch from *SurfaceFlinger* to *swapper* on Core #0 indicates this core has turned from busy to idle. This information gives us the number of running cores at any time, which is sufficient to calculate TLP. Moreover, we can get information about which thread is running and filter out observation overhead threads. For example, we treat *adbd*, the Android Debug Bridge thread, as *swapper*. The core that is running *adbd* would then be treated as idle, preventing an overestimation of TLP. We use *ftrace* [42], a Linux kernel internal trace, to get context switches. The data we gathered contains task names, ids, CPU Number, and timestamp.

#### 3.2.2.2 GPU utilization

For the PowerVR on the Odroid board, we directly read GPU utilization numbers from the sysfs interface provided. For the Mali GPU on the Origen board, we directly use a function from Mali GPU driver which monitors GPU utilization. This function is originally used for GPU dynamic voltage and frequency scaling.

<sup>&</sup>lt;sup>1</sup>For CPU power, we measure the sum of power of big and little clusters.

#### 3.2.3 Benchmarks

In this work we test a diverse range of real-world Android applications. We prefer applications that are: a) most widely used by users; b) from a broad range of diversified categories. Applications are also categorized in the Play Store, which make us easy to find applications in different categories. We choose not to use existing Android benchmark applications; the reason is that they mostly focus more on CPU or GPU performances and do not reflect the real scenarios. The tests are usually very CPU-intensive in order to test its peak performance; however, in real application this happens rather infrequently. We will show relevant result in Section. 3.3.1. Based on these requirements, we choose 18 top-pick applications from the Google Play Android App store, and 4 native ones in the Android OS. Most Android users download and install their applications using the Android Play Store, therefore its scores and ranking can be used as an credible indication of the popularity of Android applications. This means they are the applications commonly used in their category and are thus representative of current mobile software. They come from 10 different categories: browser, video player, music player, image viewer, communication, games, social networking, navigation, office, and file browser. They make use of important hardware resources on a mobile device (CPU, GPU, co-processors, etc).

We then perform test actions on each of the testing applications. Three applications (browser, Adobe reader and MX Player) are so widely used that they have already been included in some benchmarks [15, 43, 44], therefore we leverage the existing work and use their implementation directly. For other applications, we design a series of actions that cover most typical functions of the application under test. We also refer to the study in [45] on mobile applications usages, including what the popular applications are and how long each session (from opening to closing) normally last. Test actions on the Odroid board are automated using android adb commands and RERAN, a record and replay tool for Android OS [46]. These actions usually last for 30 seconds, and covers most typical functions of the application under test. We found 30 seconds is long and effective enough to cover all

common actions for the benchmark applications we have chosen. Meanwhile, we keep them as simple as possible to maximize the operator's ability to produce a repeatable input. All experiments are repeated at least 5 times for more accurate results, and applications that require an Internet connection are repeated for at least 10 runs. We observe a low standard deviation of TLP results as shown in Section. 3.3.1.

It is also important to test TLP of scenarios with background applications, to reflect common daily usage. We also test three applications with a set of other applications running in the background. The three applications under test are Angry Birds, Adobe reader, and Chrome, while the background applications are Hangout, Spotify, and Email.

Except for multi-tasking tests, we kill all the running and background applications before testing to reduce experimental errors. We also never test the application in the same category consecutively; for instance, after a test run of Browser (no matter on stock Android Browser or Chrome), we will start testing applications in a new category like Gallery or Fruit Ninja but not testing either browser again immediately. We do this to avoid cache thrashes. In our suite, most of the applications does not require an Internet connection.

We briefly introduce each application, and its corresponding test actions in the following subsections. We summarize our benchmark in Table. 3.1.

#### **3.2.3.1** Web browser

Web browsing has always been one of the most common usages since the introduction of smartphones. We use the Realistic General Web Browsing (R-GWB)[44], an automatic webpage rendering benchmark. It comprises offline pages of several most popular webpages, all of which utilize modern web technology such as CSS, HTML, ash, and multimedia. During the experiment, MobileBench uses JavaScript to load each webpage and then scroll over it with a pre-set speed. By doing so, it simulates an actual web browsing scenario. We run MobileBench on three popular browsers: the Android stock web browser, Firefox, and Chrome. For each test, we iterate through the MobileBench webpage set five

| Category              | Application     |

|-----------------------|-----------------|

| Browser (MobileBench) | Stock Browser   |

|                       | Firefox         |

|                       | Chrome          |

| Video Player          | MXPlayer        |

|                       | Netflix         |

| Music Player          | Stock Music     |

|                       | Spotify         |

| Image Viewer          | Stock Gallery   |

|                       | Instagram       |

| Communication         | Skype           |

|                       | Google Hangout  |

| Games                 | Angry Bird      |

|                       | Fruit Ninja     |

|                       | Jetpack         |

| SNS                   | Facebook        |

|                       | Twitter         |

| Navigation            | Google Maps     |

| Office                | Adobe reader    |

|                       | Stock Email     |

|                       | Kindle          |

| File Manager          | Dropbox         |

|                       | ES File Browser |

Table 3.1: Applications

times, and profile the third one. We do not impose any other user input as MobileBench is automatic itself.

#### 3.2.3.2 Video Player

Video playback is another commonly used application for smartphones. Specialized decoders and DSPs have made high-definition video easily available on current mobile devices. We use two applications: MXPlayer, a video playback application and Netflix, an online streaming application. We test both applications by playing a video for 30 seconds, with a 1 second pause at the 15th second of each of the tests.

#### 3.2.3.3 Music Player

People are gradually replacing traditional music players with phones. We use the Android stock music player and Spotify for testing music players. Spotify is a music player that supports online music streamling. We test both of the two apps by running a series of actions including open new song, jump to an arbitrary position of the song (not in spotify), and open another song.

#### 3.2.3.4 Image Viewer

One important function of modern smartphone is taking photos. Image viewers, in turn, become one of the commonly used application categories. We use Android stock image viewer (Gallery) and Instagram for testing image viewers. We test it by opening images, scrolling between images, opening another image and new folders, and playing a slideshow for a couple of seconds. Instagram is mobile photo-sharing service. Users take pictures share them on a variety of social networking platforms. We test it by scrolling new feeds, opening a picture, applying Amaro filter and changing brightness to 75, and then sharing the picture.

#### 3.2.3.5 Communication

We use Google Hangout and Skype here. We test both of these applications by initialing a 1 minute video call, 30 seconds in foreground and 30 seconds in background (approximating an audio call).

#### 3.2.3.6 Games

Mobile Games are becoming extremely popular these days. Many of them are actually very performance and graphic intensive, which makes them a good testing benchmark for CPU and GPU. The three games we choose are Angry Birds, Fruit Ninja, and Jetpack. Angry Bird is a puzzle video game; in the game, players use a slingshot to launch birds at pigs stationed on or within various structures, with the intent of killing all the pigs on the playing field. We play this game by entering the first stage, firing two birds with one miss and one hit. Fruit Ninja is an action game with lots of floating objects and high-frequency user input. It represents a more intensive mobile game comparing to Angry Birds. We play this game in the "zen mode", where fruit keeps spawning for 90 seconds. During testing, the tester keeps sliding with a constant frequency horizontally in the upper middle of the screen. Jetpack Joyride is a game where the player tries to control the rider to avoid barriers and collect coins. We play this game by tapping the screen at a regular frequency for 45 seconds.

### 3.2.3.7 Social Networking

We choose the apps from two major Social networking service providers, Facebook and Twitter. When testing Facebook, we scroll feeds, open up the pictures in the feeds and browse the profile of the user. The action of testing Twitter includes clicks on tweets, checking out picture in the tweets and looking at the profile of the tweeter.

## 3.2.3.8 Navigation

GPS are ubiquitous on mobile devices. People use navigation apps to help them find places or guide routes. The most popular navigation application on Android platform is Google Maps. We test Google Maps by searching directions between airports in New York city: we search driving directions from Newark to JFK, then public transportation from JFK to LaGuardia. We also save an offline map of New York city to avoid fetching map data from the Internet during testing.

#### 3.2.3.9 Office

The office category contains a broad range of commonly used apps. We test the following:

1) Android stock Email — we test it by writing an email and save that as a draft, sending it, checking and downloading new email. 2) Adobe reader — actions here include opening a pdf, zooming in and out, scrolling pages and searching for a keyword. 3) Amazon Kindle — actions here include opening a book, scrolling and jumping to arbitrary positions.

#### **3.2.3.10** File Browser

The increasing storage capacity of mobile devices lead people to use that as a mass storage. File browsers are then helpful in organizing files. We test Dropbox and ES File Browser. For Dropbox, we open and change folders, sort the content in the folder, do searching and editing new text file. For ES File Browser, we open the folders on the SD cards, scroll the images in it, sort and change the view of the folder.

## 3.2.3.11 Background

The background applications we choose are Google Hangout (video chatting), Spotify (playing music), Email (checking emails)<sup>2</sup>. With those applications we test Fruit Ninja,

<sup>&</sup>lt;sup>2</sup>During the test we automatically send an email to the account on board from the host machine every half minute

Maps, and Adobe Reader.

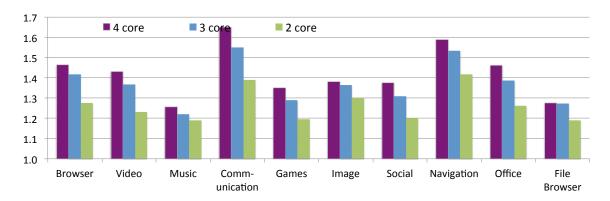

## 3.3 Results

In this section, we present our experimental results and analysis of mobile device utilization, specifically on CPU and GPU. First, we show that current mobile applications have a rather low average TLP on modern mobile device platforms. We show that increasing the number of cores has diminishing returns on TLP. Even some heavy-load real-world scenarios do not use many cores. High GPU utilization also indicates that some of the parallelism is already offloaded from the CPU to the GPU. All these factors, and the history of the slow pace of exploiting parallelism in desktop environments [17], suggests that having many powerful cores is likely to be over-provisioning.

## 3.3.1 Overall Results

We list a summary of the results in Table. 3.2. Each row in the table shows the TLP and standard deviation ( $\sigma$ ) for an application type. The first line, "System", refers to the plain Android OS testing environment without any application running; the last line, "Average", is the average of the statistics of all tested applications. The standard deviation of the TLP over runs for each application is low. This indicates the tests are reproducible and insensitive to user input variation.

We make two observations based on these results:

#### 1) All the applications demonstrate some, but quite limited TLP.

For Android, even in a case where a developer writes code with no awareness of multithreading, a number of threads are still created for external I/O, garbage collection, graphics rendering, etc. This means that even a programmer with no idea about multithreading could benefit from parallel processing on different CPU cores. Moreover, many software developers are aware of the multi-core hardware they are using and write applications explicitly

| Category       | App             | TLP  | $\sigma$ (TLP) |

|----------------|-----------------|------|----------------|

| System         | [None]          | 1.03 | 0.00           |

| Browser        | Stock Browser   | 1.47 | 0.03           |

|                | Firefox         | 1.31 | 0.02           |

|                | Chrome          | 1.66 | 0.01           |

| Video Player   | MXPlayer        | 1.34 | 0.01           |

|                | Netflix         | 1.53 | 0.07           |

| Music Player   | Stock Music     | 1.29 | 0.03           |

|                | Spotify         | 1.23 | 0.05           |

| Image Viewer   | Stock Gallery   | 1.46 | 0.03           |

|                | Instagram       | 1.31 | 0.03           |

| Communication  | Google Hangout  | 1.82 | 0.15           |

|                | Skype           | 1.55 | 0.13           |

| Games          | Angry Birds     | 1.31 | 0.08           |

|                | Fruit Ninja     | 1.40 | 0.12           |

|                | Jetpack         | 1.54 | 0.09           |

| Social Network | Facebook        | 1.43 | 0.04           |

|                | Twitter         | 1.32 | 0.04           |

| Navigation     | Google Maps     | 1.59 | 0.06           |

| Office         | Stock Email     | 1.52 | 0.04           |

|                | Adobe Reader    | 1.30 | 0.05           |

|                | Kindle          | 1.45 | 0.01           |

| File Browser   | Dropbox         | 1.33 | 0.02           |

|                | ES file browser | 1.22 | 0.02           |

| Background     | Back_Fruit      | 1.65 | 0.12           |

|                | Back_Maps       | 1.91 | 0.11           |

|                | Back_Adobe      | 1.60 | 0.14           |

| Average        |                 | 1.46 | 0.06           |

Table 3.2: TLP results for the Odroid board — using ondemand governor.

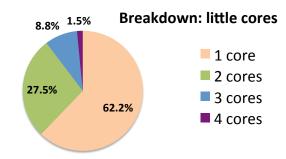

Figure 3.1: Time breakdown of how the multi-core is utilized. The big pie chart on the right shows an average result of all application categories we tested. The smaller pie charts show the breakdown of three representative kinds of apps: Google Maps with the highest TLP, stock Browser, and stock Music with a low TLP.

with multiple threads.

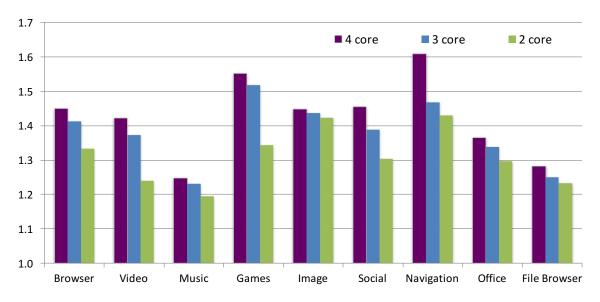

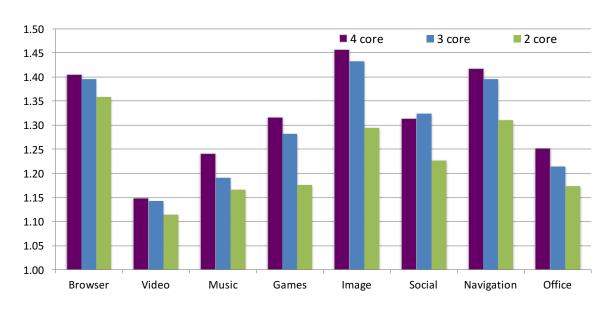

However, the parallelism we observed is generally still quite low. On average, we see a TLP of 1.46. The application with the highest TLP, Google Hangout, has a TLP of just 1.8. Applications like Music and File Browser have rather low TLP, around 1.2 to 1.3. This result shows, on average, the system is using less than 2 cores.

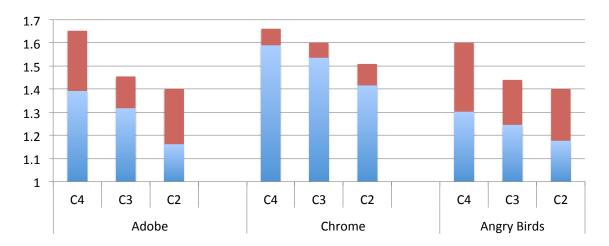

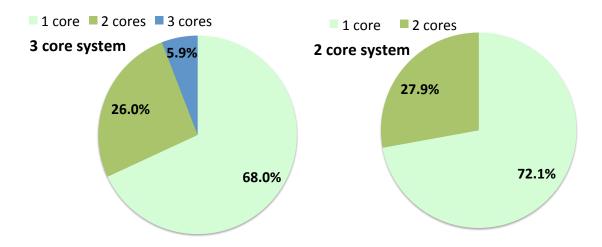

## 2) Multi-core is utilized infrequently.

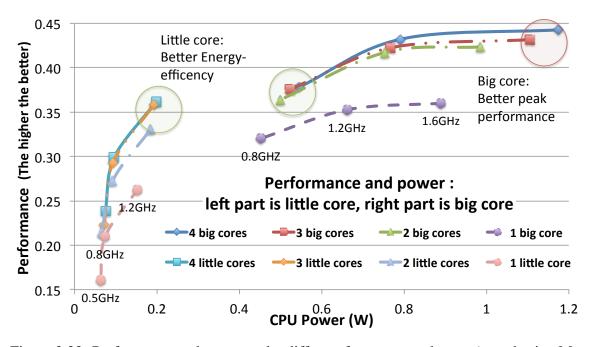

We present a time breakdown of how the multi-core system is utilized in Fig. 3.1. The big pie chart on the right shows an average result of all application categories we tested. The smaller pie charts show the breakdown of three representative application categories. We observe a very low 4-core and 3-core utilization; on average only 0.68% of all the non-idle time is the system fully utilized (all four cores running), and 5.81% of the time when three cores are used — this means there is only a small amount of time that four or three cores are being utilized at the same time.