# **Architecting Memory Systems for Emerging Technologies**

by

Byoungchan Oh

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2018

#### **Doctoral Committee:**

Professor Trevor N. Mudge, Co-Chair Assistant Professor Ronald G. Dreslinski Jr., Co-Chair Professor David Blaauw Professor William R. Martin Byoungchan Oh bcoh@umich.edu

ORCID iD: 0000-0001-9612-2501

© Byoungchan Oh 2018 All Rights Reserved To my family and all those who wished me well.

#### **ACKNOWLEDGMENTS**

I would like to thank my primary advisor, Professor Trevor Mudge, for his invaluable support and guidance. I appreciate everything he has done for me. No words can express my gratitude to him. Professor Ronald Dreslinski, my co-advisor, has perfectly complemented Trev. I also would like to thank my dissertation committee members, Professor David Blaauw and William Martin, for their wisdom and guidance in the final steps of my studies.

I am pleased to have met lifelong friends in TRON lab: Antony Gutierrez, Qi Zheng, Nilmini Aberaytne, Yajing Chen, Cao Gao, Jonathan Beaumont, Dong-Hyeon Park, Yiping Kang, and Johann Hauswald. I shall never forget the countless hours and moments together. I especially appreciate the kindness, consideration, and help of Nilmini during whole my Ph.D. study and life. I would like to thank all those who directly and indirectly have helped my studies: Doowon Lee, Yongkee Kwon, Jihyae Bae, Dong-Keun Kim, Professor Jeongseob Ahn, and Professor Nam Sung Kim.

Lastly and most importantly, I would like to thank my parents and brother. I am forever grateful for their unwavering faith and support. To my loves, Blue, Berry and Mijung, I could finish my studies thanks to you. I owe much of my successes to my wife and her devotion to my family.

Thank you.

# TABLE OF CONTENTS

| <b>Dedication</b>                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgments                                                                                                                                                                                              |

| List of Figures                                                                                                                                                                                              |

| List of Tables                                                                                                                                                                                               |

| Abstract                                                                                                                                                                                                     |

| Chapter                                                                                                                                                                                                      |

| 1 Introduction                                                                                                                                                                                               |

| 1.1 Memory System          1.2 Memory Technology          1.3 Emerging Memory Technology          1.4 Dissertation Organization                                                                              |

| 2 STT-MRAM Architecture for Smart Activation and Sensing                                                                                                                                                     |

| 2.1 Introduction       1         2.2 Challenges in Architecting STT-MRAM       1         2.2.1 Large Sense Amps with High Power Consumption       1         2.2.2 Limitations with Shared Sense Amps       1 |

| 2.3 SMART Architecture       1         2.3.1 Re-architecting STT-MRAM       1         2.3.2 Benefits       2         2.3.3 Discussion       2                                                                |

| 2.4 Device Modeling                                                                                                                                                                                          |

| 2.5 Evaluation       3.         2.5.1 Evaluation Methodology       3.         2.5.2 Performance       3.         2.5.3 Energy       3.                                                                       |

| 2.5.4 Sensitivity Analysis       3         2.6 Related Work       3                                                                                                                                          |

| 2.7       | Summary                                                  | 40 |

|-----------|----------------------------------------------------------|----|

| 3 Improv  | ring Load Balancing for Memory Channels                  | 41 |

| 3.1       | Introduction                                             | 42 |

| 3.2       | Background                                               | 44 |

|           | 3.2.1 Increasing Demand of Memory Capacity and Bandwidth | 44 |

|           | 3.2.2 High Bandwidth Memory                              | 44 |

| 3.3       | Challenges in Many Channel Memory Systems                | 48 |

|           | 3.3.1 Imbalanced Channel Utilization                     | 48 |

|           | 3.3.2 Implementation Challenges of Memory Controllers    | 50 |

| 3.4       |                                                          |    |

|           | 3.4.1 Re-architecting Memory Controllers                 |    |

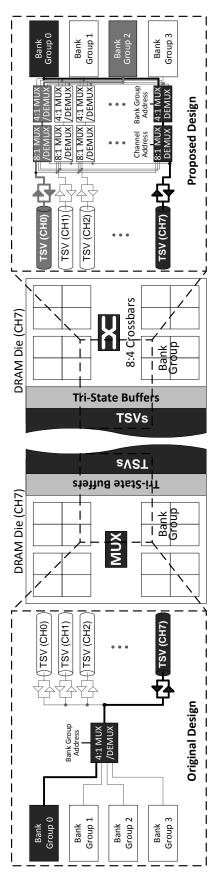

|           | 3.4.2 Re-architecting HBM                                | 58 |

|           | 3.4.3 Overhead                                           | 59 |

| 3.5       | Evaluation                                               | 61 |

|           | 3.5.1 Methodology                                        | 61 |

|           | 3.5.2 Performance Analysis                               | 62 |

|           | 3.5.3 Area Overhead                                      | 65 |

| 3.6       | Related Work                                             | 66 |

| 3.7       | Summary                                                  | 67 |

| 4 Conclu  | sion                                                     | 69 |

| Bibliogra |                                                          | 71 |

# LIST OF FIGURES

| 1.1  | Von Neumann architecture                                                                     | 1  |

|------|----------------------------------------------------------------------------------------------|----|

| 1.2  | Memory hierarchy                                                                             | 2  |

| 1.3  | DRAM scaling trend [1]                                                                       | 3  |

| 1.4  | Increasing throughput loss and power consumption by refresh [2]                              | 3  |

| 1.5  | Impacts of the DRAM page size in STREAM benchmark [3]                                        | 4  |

| 1.6  | Increasing data rate from SDR to DDR4                                                        | 5  |

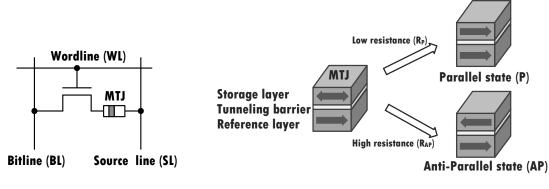

| 1.7  | STT-MRAM cell structure and MTJ                                                              | 6  |

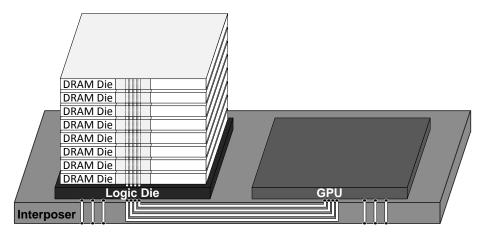

| 1.8  | 2.5D integration between HBM and GPU through a interposer                                    | 7  |

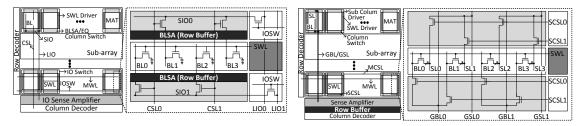

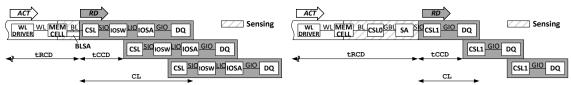

| 2.1  | Bank architecture and operation of DRAM (left) and conventional STT-MRAM (right)             | 15 |

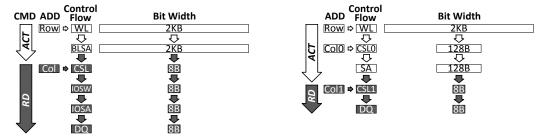

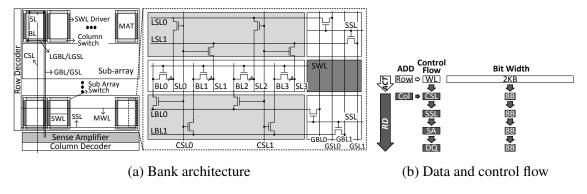

| 2.2  | SMART bank architecture and data/control flow                                                | 18 |

| 2.3  | Change of read and write accesses after making sensing operation triggered by                |    |

|      | a RD command                                                                                 | 19 |

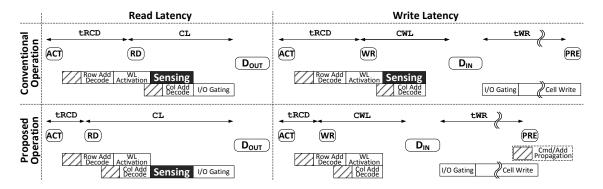

| 2.4  | SMART page mode and enhanced bank architecture                                               | 20 |

| 2.5  | Relation between page size and ACT energy                                                    | 21 |

| 2.6  | Impact of tRRD on bank-level parallelism                                                     | 22 |

| 2.7  | trrd and traw for various page sizes. trrd and traw for DRAM are                             |    |

|      | obtained from a DDR3 datasheet [4]                                                           | 23 |

| 2.8  | Comparison of the three repair schemes                                                       |    |

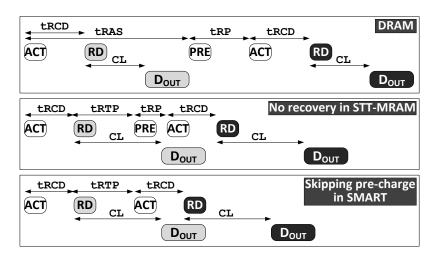

| 2.9  | Change of row access cycle on row misses                                                     |    |

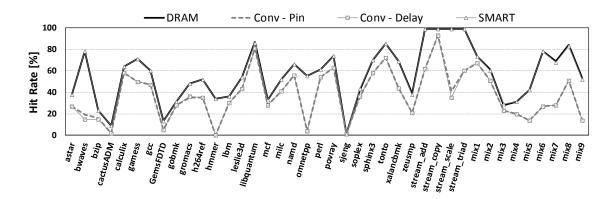

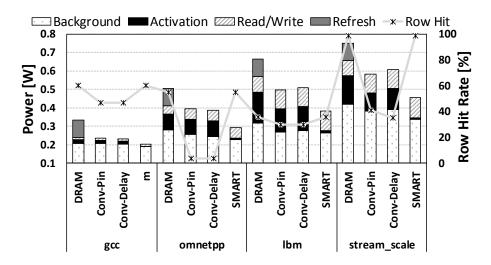

| 2.10 | Row hit rate in various workloads                                                            |    |

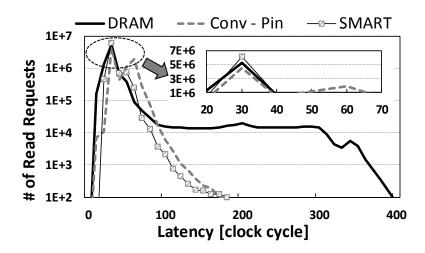

| 2.11 | Read latency profile of mix6 workload                                                        |    |

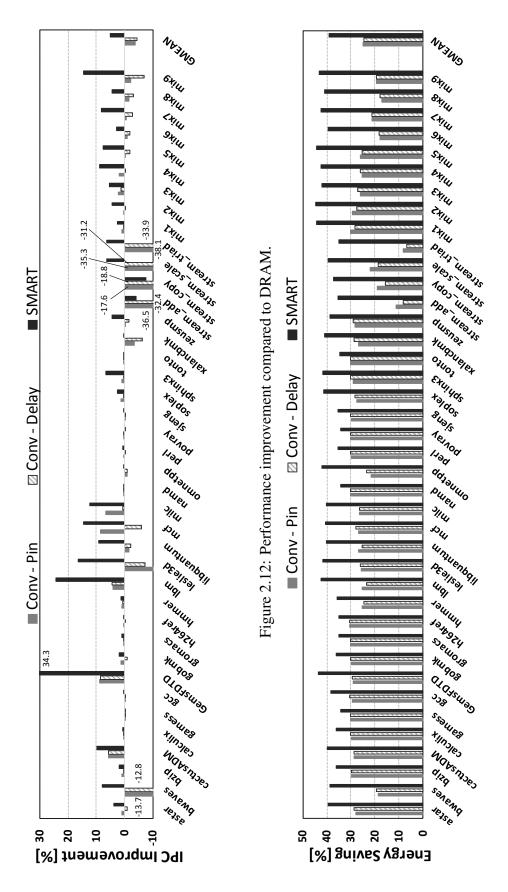

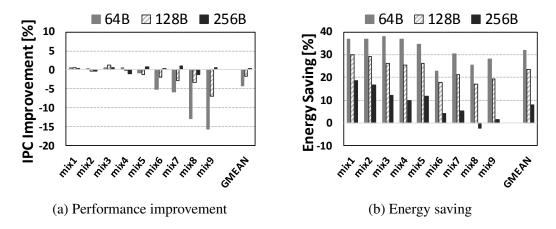

| 2.12 | Performance improvement compared to DRAM                                                     | 36 |

| 2.13 | Energy savings over DRAM                                                                     | 36 |

| 2.14 | Breakdown of average memory power                                                            | 37 |

| 2.15 | Normalized performance improvement and energy saving of the conventional                     |    |

|      | STT-MRAM (Conv-Delay) to the baseline DRAM with various page size                            | 38 |

| 2.16 | Normalized IPC and energy to DRAM with various configurations (average of all mix workloads) | 39 |

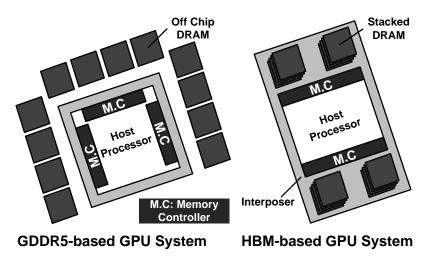

| 3.1  | GPU systems with GDDR5 and HBM                                                               | 45 |

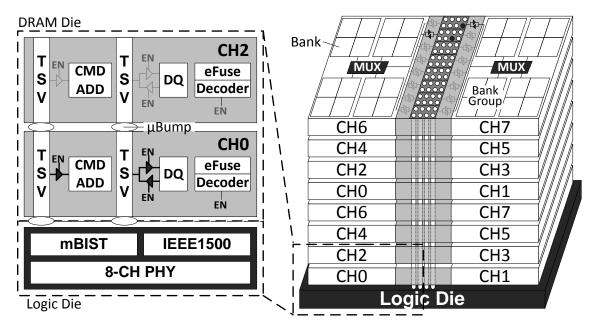

| 3.2  | 3D structure of HBM and a simple example of TSV connection to DRAM dies.                     | 46 |

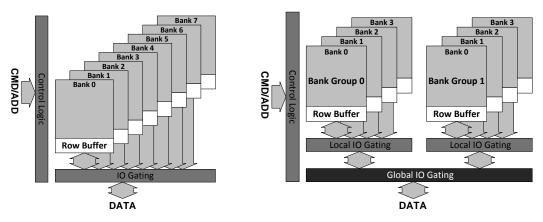

| 3.3  | Comparison between two memory organizations [5]                                              | 47 |

| 3.4  | Channel Utilization.                                                                         | 48 |

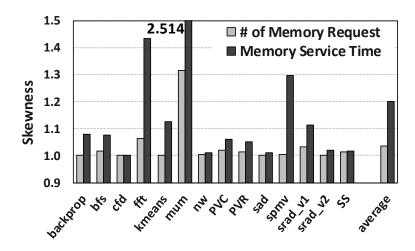

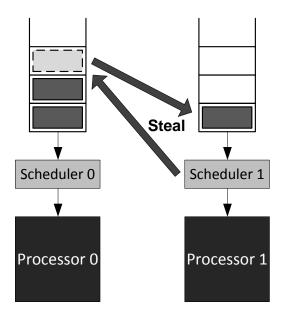

| 3.5  | Simple diagram for work stealing                                       | 49 |

|------|------------------------------------------------------------------------|----|

| 3.6  | Performance according to queue depth                                   | 50 |

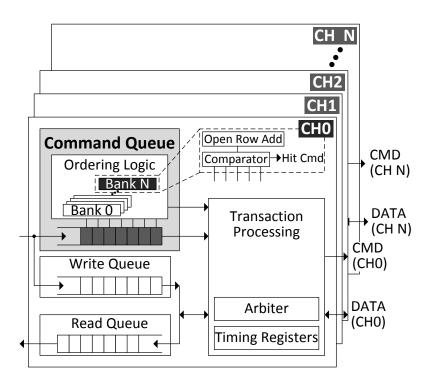

| 3.7  | Schedulers of the memory controller in many channel memory systems [6] | 51 |

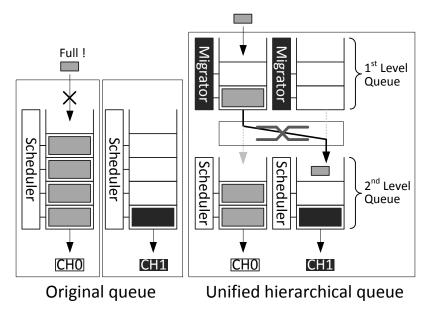

| 3.8  | Hierarchical queue structure                                           | 53 |

| 3.9  | Limited scheduling                                                     | 55 |

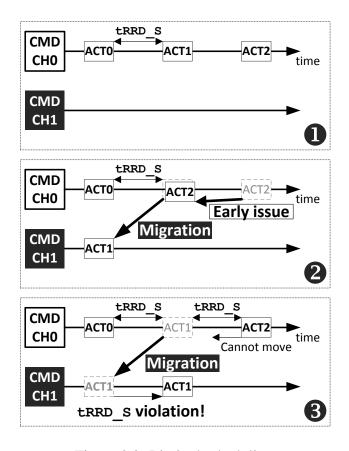

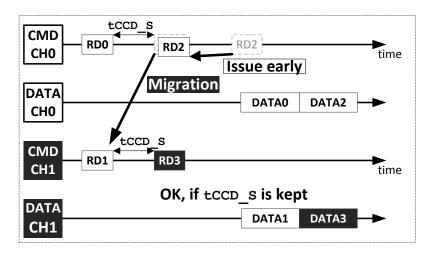

| 3.10 | Avoiding timing constraint                                             | 56 |

| 3.11 | HBM with crossbars                                                     | 60 |

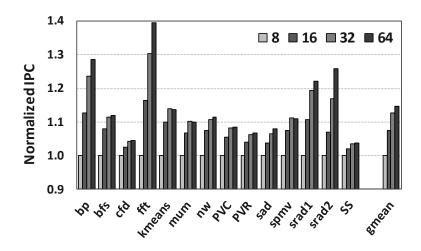

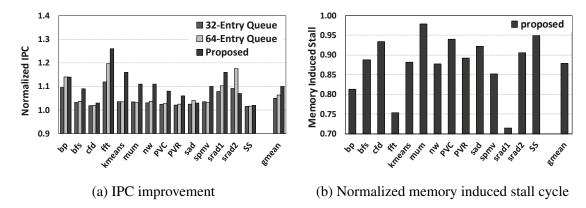

| 3.12 | Performance improvement after the migration                            | 63 |

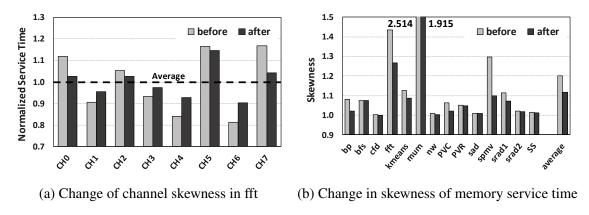

| 3.13 | Change of imbalanced memory service time                               | 63 |

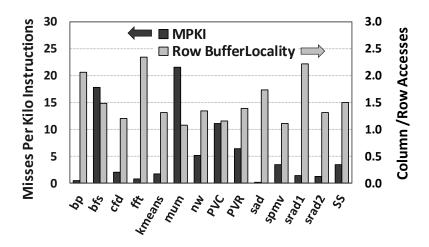

| 3.14 | MPKI and locality.                                                     | 64 |

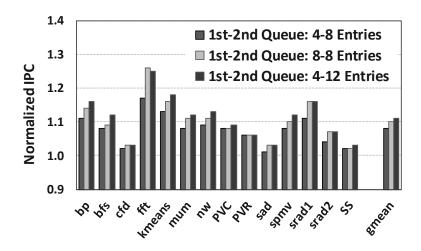

| 3.15 | Performance according to different queue configuration                 | 65 |

# LIST OF TABLES

| 2.1 | Comparison with previous studies     |

|-----|--------------------------------------|

| 2.2 | Area comparison                      |

| 2.3 | Timing and latency comparison        |

| 2.4 | Energy and current comparison        |

| 2.5 | Default system configuration         |

| 2.6 | Workloads for multi-core simulations |

| 3.1 | Configured System                    |

| 3.2 | Workload list                        |

| 3.3 | Estimated area                       |

#### **ABSTRACT**

The advance of traditional dynamic random access memory (DRAM) technology has slowed down, while the capacity and performance needs of memory system have continued to increase. This is a result of increasing data volume from emerging applications, such as machine learning and big data analytics. In addition to such demands, increasing energy consumption is becoming a major constraint on the capabilities of computer systems. As a result, emerging non-volatile memories, for example, Spin Torque Transfer Magnetic RAM (STT-MRAM), and new memory interfaces, for example, High Bandwidth Memory (HBM), have been developed as an alternative. Thus far, most previous studies have retained a DRAM-like memory architecture and management policy. This preserves compatibility but hides the true benefits of those new memory technologies.

In this research, we proposed the co-design of memory architectures and their management policies for emerging technologies. First, we introduced a new memory architecture for an STT-MRAM main memory. In particular, we defined a new page mode operation for efficient activation and sensing. By fully exploiting the non-destructive nature of STT-MRAM, our design achieved higher performance, lower energy consumption, and a smaller area than the traditional designs. Second, we developed a cost-effective technique to improve load balancing for HBM memory channels. We showed that the proposed technique was capable of efficiently redistributing memory requests across multiple memory channels to improve the channel utilization, resulting in improved performance.

#### **CHAPTER 1**

## Introduction

## 1.1 Memory System

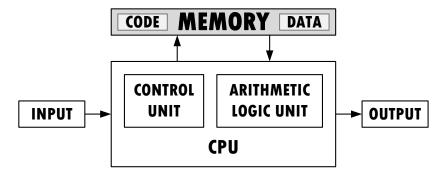

A memory system is one of the core sub-systems in modern computer architectures. Modern computer architectures are based on Von Neumann architecture which mainly consists of memory, input/output, the arithmetic/logic unit, and the control unit as shown in Fig. 1.1 [7,8]. The memory in Von Neumann architecture stores program data and instruction data. Thus, this architecture is sometimes called to a stored-program computer [9]. Because storing data to memory and loading data from memory are essential operations in this architecture, performance and energy consumption of the memory system significantly affect overall system performance and energy consumption [10–12]. Moreover, the importance of a memory system continuously is increasing with emerging applications and services which need more memory capacity and bandwidth [13–15].

Figure 1.1: Von Neumann architecture.

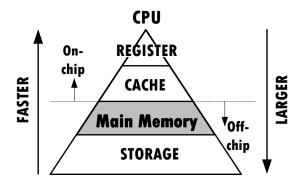

Figure 1.2: Memory hierarchy.

Memory systems have evolved with a hierarchical structure as shown in Fig. 1.2 [16]. This structure can take both advantages of short access time offered from small memories (*e.g.*, register files and caches) and area efficiency provided from large memories (*e.g.*, main memory and storage). A main memory is not too fast, but not too small. Because the different process technology from that of CPU is used for main memories, they are typically off-chip devices. Generally, the main memory holds whole program code and data whereas caches temporally hold partial code and data<sup>1</sup>. Thus, there are frequent accesses to the main memory in irregular applications, where cached data are not reused well. Besides, recent in-memory database techniques increase use of the main memory [14, 17].

## 1.2 Memory Technology

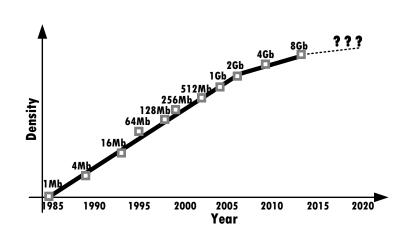

**Memory Cell.** Dynamic Random Access Memory (DRAM) is a type of random access semiconductor memory that stores each bit of data in a separate tiny capacitor. It is used as the main memory in most computing systems. As the *de facto* standard in the past several decades, DRAM has been continuously increased in capacity as shown in Fig. 1.3. However, after increasing for decades, the capacity of DRAM nowadays has now stopped at 8 Gb. The root cause resulting in this trend is DRAM's refresh operation. Because the cell capacitor is leaky, DRAM cells must be periodically refreshed to prevent data loss

<sup>&</sup>lt;sup>1</sup>If a main memory space is not enough, storage can be used as the main memory by the page swap

Figure 1.3: DRAM scaling trend [1].

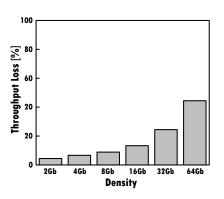

- (a) Throughput loss by refresh

- (b) Relative power consumption of refresh

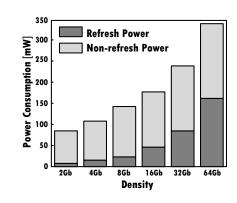

Figure 1.4: Increasing throughput loss and power consumption by refresh [2].

within their retention time (typically 64 *ms*). Unfortunately, this retention time has not improved.<sup>2</sup> If DRAM capacity is increased without improvement of retention time, more DRAM cells must be refreshed within the same period. Thus, the relative time spent for refresh is increased according to the capacity. This increased refresh time can be converted to throughput loss as shown in Fig. 1.4a. Furthermore, the power consumption for refresh is also increased in proportion to capacity. The refresh power consumption, which does not contribute to computation, will become comparable with the dynamic power consumption, which is directly involved with the computation as shown in Fig. 1.4b.

Memory Interface. Double Date Rate (DDR), which is successors to Single Data Rate

$<sup>^2</sup>$ In fact, the retention time is becoming worse and thus some recent DRAM devices have shorter retention time (32 ms) than the normal 64 ms [18].

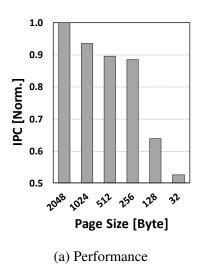

Figure 1.5: Impacts of the DRAM page size in STREAM benchmark [3].

(SDR), is the most widely used interface standard for a main memory. In DDR memories, a memory access is divided into two types of accesses, row access and column access. A row access command activates or deactivates a row in a memory array. When a row is activated, all cells connected to that row are sensed by sense amps and the sensed data are stored in row buffers. Because data are already stored in the row buffer, a following column access command can be served from the row buffer without additional array access.<sup>3</sup> Also, a following column access going to the same row can be served without additional row access, because all data for the row are already stored in the row buffer. This operation is called *page mode* operation and still remains unchanged in modern DDR devices. The size of data sensed by a row activation command is defined as page size. In general, page mode increases performance by avoiding repeated activation of the same row to access different columns. Thus, the large page size is good for performance especially when data locality is high. However, the wasted energy is increased in large pages because all data in a page (i.e., the row buffer) are not used always. As shown in Fig. 1.5, it is hard to capture both high performance offered by large pages and low power consumption offered by small pages at the same time [19-22].

<sup>&</sup>lt;sup>3</sup>A read command can immediately read out data stored in the row buffer, but a write command needs to access the array after updating data in the row buffer. However, after updating the row buffer but before finishing array access, another column access is allowed.

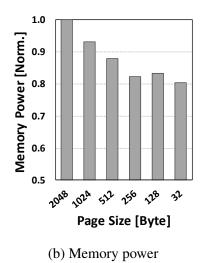

Figure 1.6: Increasing data rate from SDR to DDR4.

Total peak memory bandwidth is defined as,

$$Memory\ Bandwidth = Data\ Rate \times Bus\ Width \times Number\ of\ Channels$$

(1.1)

where data rate is equal to memory bus clock speed in SDR and double of the clock speed in DDR, bus width is traditionally is 64 bits, and the number of channels is typically 1~6 for main memory systems. As shown in Fig. 1.6, data rate from SDR to DDR4 has been continuously increased. That is, traditionally memory bandwidth has been increased by increasing data rate (*i.e.*, clock speed). However, increasing the clock speed has several challenges. First, the clock speed in latest DDR generation is already 1.2 GHz and it is fast enough. There will be some degree of increase in the clock speed, but that would not be an order of magnitude increase. That is, it is hard to achieve an order of magnitude higher memory bandwidth by increasing the clock speed. Second, generally faster clock requires higher supply voltage. Although technology improvements such as low voltage swing termination logic (LVSTL) suppress the increase of the supply voltage, increasing clock speed cannot save power consumption.

(a) Bit-cell structure of STT-MRAM

(b) Magnetic Tunneling Junction

Figure 1.7: STT-MRAM cell structure and MTJ.

## 1.3 Emerging Memory Technology

**Memory Cells Technology.** Because of DRAM's refresh and the limitations caused by it, emerging non-volatile memories such as Resistive RAM (ReRAM), Phase Change Memory (PCM) and Spin Transfer Torque Magnetic RAM (STT-MRAM) have been receiving more attention. However, unlike other emerging non-volatile memories, STT-MRAM is considered to be a replacement candidate for a main memory because of its fast access speed and high endurance [23–29]. An STT-MRAM cell consists of an access transistor and a Magnetic Tunneling Junction (MTJ) to store data as shown in Fig. 1.7a. There are three layers in an MTJ: two magnetic layers and one tunneling barrier between them as shown in Fig. 1.7b. The "reference" magnetic layer has a fixed magnetization and the "free/storage" layer has a variable magnetization. When their magnetization directions are the same (parallel state, P), an MTJ shows low electrical resistance  $(R_P)$ . When their magnetization directions are different (anti-parallel state, AP), they show high resistance  $(R_{AP})$ . This change in the resistance is called the tunneling magnetoresistance effect. The spin transfer torque (STT) force is exerted by injecting a spin-polarized current to change the magnetization direction of the free/storage layer. In order to enable bi-directional change, a bi-directional current should flow through an STT-MRAM cell. Therefore, one terminal of an MTJ is connected to a bit-line (BL) through a selection transistor and the other terminal is connected to a

Figure 1.8: 2.5D integration between HBM and GPU through a interposer.

source-line (SL) for the write operation as shown in Fig. 1.7a [30, 31]. Although this cell structure is similar to a DRAM cell structure, the STT-MRAM cell is larger due to the larger access transistor. The larger access transistor is required to drive enough current to switch the magnetization direction. Alternatively, increasing the write time (pulse width) can reduce the amount of current required and thus the cell size can be smaller [32, 33]. Memory Interface Technology. There are variants of DDR standard for specialized applications: Low Power DDR (LPDDR) optimized for power consumption and Graphic DDR (GDDR) optimized for performance. Although several unique features exist in LPDDR or GDDR such as Partial Array Self Refresh (PASR) in LPDDR and separate higher speed Write Clock (WCK) in GDDR, their basic operations are almost same as normal DRAM [5, 18,34]. Besides, they all use narrow ( $32\sim64$  bits per channel) and fast (up to 7Gbps per pin) memory channels. Because of this narrow and fast channel, increasing memory capacity and bandwidth is limited by the power budget. Moreover, accommodating more memory chips to achieve higher the capacity and bandwidth can limit the form factor. In order to overcome this issues, 3D stacked DRAM memories, such as High Bandwidth Memory (HBM) and Wide I/O (WIO), have been developed [35,36]. In Fig. 1.8, an example of 2.5D integration between a processor (GPU) and a stacked DRAM (HBM) through a silicon interposer is described. Because the interconnections through the interposer are much shorter than the interconnections between off chips on PCB, the data transfer energy is lower on the interposer. In addition, a stack of DRAM dies in HBM provides multiple channels (up to 8) within a small space and the interposer can accommodate all I/Os for the channels. Because the bandwidth is linearly proportional to the data rate and total number of I/Os for all channels, HBM's large number of I/Os (1024 vs. 32 for GDDR5) allows to lower the data rate (2Gbps vs. 7Gbps for GDDR5) while increasing the bandwidth (256GB/s vs. 28GB/s for GDDR5).

## 1.4 Dissertation Organization

The research work is organized as follows. Chapter 2 presents a co-design of memory architecture and its management policy for an STT-MRAM main memory. Chapter 3 presents a cost-effective technique to improve load balancing for HBM channels. Finally, Chapter. 4 includes the summary of this work and conclusions.

#### **CHAPTER 2**

# STT-MRAM Architecture for Smart Activation and Sensing

STT-MRAM is a promising memory technology as a drop-in replacement of DRAM for main memory, because it can offer higher energy efficiency than DRAM with latency comparable to DRAM. However, STT-MRAM needs to employ current sense amps which consume an order of magnitude larger space and power than voltage sense amps adopted by DRAM. Consequently, to manage the high cost of sense amps, STT-MRAM decouples bit-lines from sense amps and shares one sense amp with  $16\sim128\times$  bit-lines, exploiting the non-destructive nature of its read operation. However, such STT-MRAM reduces the size of row buffers and incurs more row-buffer misses (*i.e.*, higher activation energy and lower performance) than DRAM along with other issues, especially when it follows interfaces and policies designed for DRAM.

To cost-effectively address these issues, we propose SMART, co-designing STT-MRAM architecture and its management policy in this study. Specifically, unlike DRAM and conventional STT-MRAM, SMART proposes to sense bit-lines after receiving a column access command instead of a row activation command. This can provide several benefits including larger pages, fewer sense amps, lower activation/sensing power, shorter latency, fewer address pins and more efficient repairs of defective columns than conventional STT-MRAM. Our evaluation shows that SMART consumes 11% (39%) lower energy while providing 9% (5%) higher performance than conventional STT-MRAM (DRAM) on average. In addition

to these benefits, SMART is 6% smaller than conventional STT-MRAM.

#### 2.1 Introduction

STT-MRAM is one of the promising emerging non-volatile memory (NVM) technologies as a drop-in replacement of DRAM for main memory because of its faster speed and higher endurance than other NVM technologies [23–29]. However, STT-MRAM has some disadvantages over DRAM. One of such disadvantages is a need to use large and high-power sense amps in STT-MRAM. Specifically, STT-MRAM needs current sense amps consuming an order of magnitude larger space and higher power than voltage sense amps adopted by DRAM. To manage the cost of implementing such sense amps, STT-MRAM leverages the non-destructive nature of its read operation and shares one sense amp with 16~128 bit-lines in each bank [37–42]. Such STT-MRAM architectures, nonetheless, suffer from two limitations.

First, STT-MRAM with fewer sense amps provides smaller row buffers and thus pages than DRAM, as the number of sense amps determines the size of row buffers [16]. Larger pages provide higher performance with more row-buffer hits when data locality is high, but they consume more energy when data locality is poor, which is also known as the overfetching problem. In contrast, smaller pages consume less energy when data locality is poor, but they give lower performance with more row-buffer misses when data locality is good. The size of STT-MRAM row buffers is far smaller than that of DRAM row buffers but much larger than that of a column access. Therefore, STT-MRAM suffers from more row-buffer misses than DRAM without completely eliminating the overfetching problem.

Second, when such STT-MRAM uses interfaces and policies designed for DRAM, it suffers from a column address fragmentation problem [27, 42]. Specifically, DRAM requires sense amps to sense all 16,384 bit-lines in a sub-array and latch the data until open-

ing another row due to the destructive nature of its read operation. Therefore, for a given row address, DRAM performs both activation and sensing at the same time with a single row activation (ACT) command. However, it becomes problematic to directly apply such an activation/sensing approach to STT-MRAM with fewer sense amps than the number of bit-lines (*i.e.*, size of a row), because STT-MRAM must receive both a row address and some of a column address at the same time to connect a sub-set of chosen bit-lines to the sense amps through multiplexers when activating a row. That is, STT-MRAM with the same capacity as DRAM requires more address pins to send not only a row address but also some of a column address together with a row command. Besides, such a fragmentation of a column address between row and column commands considerably worsens efficiency and flexibility of column repair mechanisms as a row or column command has only partial column address information [43, 44].

To cost-effectively address these issues, we propose SMART, STT-MRAM ARchiTecture supporting smart activation/sensing. Specifically, exploiting one of the advantages of STT-MRAM, non-destructive nature of its read operation, we propose to provide only 64 sense amps<sup>2</sup> for each bank and make a column access command instead of a row activation command sense bit-lines. This deceptively simple change, which is not possible for DRAM with the destructive nature of its read operation, can offer the following advantages over conventional STT-MRAM.

(1) SMART offers the illusion of providing  $16 \times$  larger row buffers with  $16 \times$  fewer sense amps than conventional STT-MRAM. That is, SMART provides 2KB pages with only 64 sense amps per bank, whereas conventional STT-MRAM gives 128B pages with 1,024 sense amps per bank. Furthermore, conventional STT-MRAM repeatedly consumes long time (tRC = 27.5ns) and high power to access the same row but columns which

<sup>&</sup>lt;sup>1</sup>DRAM uses the same set of address pins to receive both row and columns addresses in a time multiplexed manner. Since a row address typically needs more bits than a column address, the number of row address bits determines the number of address pins in DRAM.

$<sup>^2</sup>$ In this study, we assume DRAM and STT-MRAM modules, each consisting of eight  $\times 8$  devices for 64-bit I/O. Therefore, each device must sense 64 bits to support the burst length of 8 for a single column access command.

were not selected and sensed by the previous row command. This is because conventional STT-MRAM needs to recognize such memory accesses as row-buffer misses to select and sense different bit-lines. In contrast, SMART can recognize such memory accesses as row-buffer hits and it only needs another column access command because it selects and senses different bit-lines which were already connected to the necessary cells by the previous row activation command.

- (2) SMART consumes ~88% lower activation power than conventional STT-MRAM. Specifically, conventional STT-MRAM senses 1,024 bit-lines as part of a row activation, and sensing power dominates the activation power. In contrast, SMART consumes 16× less sensing power than conventional STT-MRAM because it senses only 64 bit-lines (*i.e.*, granularity of a column access) as part of a column access. Hence, SMART practically eliminates the overfetching problem. Furthermore, whenever a memory write access demands an activation of another row, conventional STT-MRAM unnecessarily consumes sensing power because sensing is part of the row activation. However, SMART does not consume any sensing power for such a memory write access, because sensing is not part of a row activation but part of a column read access.

- (3) SMART offers shorter latency for memory accesses. Specifically, high sensing power imposes trrd and trrd constraints in DRAM and STT-MRAM and limits the number of row activation commands in a certain time period. As SMART significantly reduces sensing power, it can eliminates these two constraints and handle more row activation commands in a shorter time period than conventional STT-MRAM. As previously mentioned, conventional STT-MRAM performs sensing as part of row activation while sensing is unnecessary for memory write accesses. Moreover, sensing constitutes a notable fraction of activation time. Therefore, SMART can also reduce latency of memory write accesses especially to different rows compared with conventional STT-MRAM.

- (4) SMART needs fewer pins and offer  $10.7 \times$  more efficient repairs of defective columns than conventional STT-MRAM. Particularly, SMART does not sense bit-lines as part of

row activation. Therefore, it does not need to select and connect specific bit-lines to sense amps as part of row activation. That is, it only needs to receive a row address for activation like DRAM. Besides, SMART receives the full column address with a column command, it can use the same efficient mechanism as DRAM for repairing defective bit-lines.

(5) SMART eliminates the need for sending separate pre-charge commands since a column command can comprise the function of a pre-charge command. As a result, SMART not only offers 11% shorter latency for memory accesses which are directed to the same bank but incur row-buffer misses, but also consumes less command bus bandwidth than conventional STT-MRAM.

In summary, (1)–(5) not only reduce energy but also improve performance. Our evaluation shows that SMART consumes 11% (39%) lower energy while providing 9% (5%) higher performance than conventional STT-MRAM (DRAM) on average. In addition to these benefits, SMART is 6% smaller than conventional STT-MRAM.

# 2.2 Challenges in Architecting STT-MRAM

In this section, we compare STT-MRAM with DRAM and explicate challenges and limitations in conventional STT-MRAM.

#### 2.2.1 Large Sense Amps with High Power Consumption

STT-MRAM is expected to offer cell read/write speed comparable to DRAM and good endurance (>  $10^{15}$ ) [45–49]. A recent study demonstrated 4Gb LPDDR2-compatible STT-MRAM with  $9F^2$  cell size and sub-50ns read/write speed [27]. Such characteristics make STT-MRAM a promising alternative to  $\sim 7F^2$  DRAM. However, STT-MRAM poses unique challenges especially in implementing a sense amps (SA) [37,50–54].

First, STT-MRAM needs a large current SA with a reference current generator because sensing small difference in on/off resistance is challenging, which is further worsened by process variations. This requires STT-MRAM to adopt a very complex current SA which consumes an order of magnitude larger space than a voltage SA employed by DRAM.

Second, sensing in STT-MRAM consumes high power. DRAM SAs simply charge or discharge bit-lines (BLs) once per sensing, whereas STT-MRAM SAs need to continuously flow current to BLs until they reach a level sufficient for sensing. To eliminate the power consumed by the continuous current flow, separate buffers are implemented and data in SAs are copied to the buffers so that the SAs can be turned off immediately after sensing bit-lines [41,50].

#### 2.2.2 Limitations with Shared Sense Amps

DRAM needs to directly couple every BL with a dedicated SA in each sub-array, as shown in Fig. 2.1a due to its destructive nature of read operation. STT-MRAM, however, shares one SA with 16~128 BLs after it decouples SAs from BLs with multiplexers [27,37,38,42], as depicted in Fig. 2.1b. This is to manage the cost of SAs, exploiting its non-destructive nature of its read operation.

DRAM operating in page mode senses cell states of a row and stores them into a row buffer<sup>3</sup> when an ACT command is received. This allows DRAM to pre-charge/activate a row once for multiple column accesses, as depicted in Fig. 2.1c. Such an operating mode has not changed in modern DRAM architectures [34,55–57]. Fig. 2.1d describes the steps of serving a read request in STT-MRAM following the same page mode as DRAM but sharing one SA with 16 BLs to reduce the cost. A row activation command first asserts a word-line (WL) connected to 16,384 cells (2KB). Since there are only 1,024 SAs (*i.e.*, 128B row buffer), a column selection signal (CSL0) uses part of the column address (Col0) to select one BL out of 16 BLs. The column selection signal (MCSL-SCSL) in an STT-MRAM bank shown in Fig. 2.1b corresponds to the WL selection signal (MWL-SWL). The remaining part of the column address (Col1) selects global bit-lines (GBLs) and it is

<sup>&</sup>lt;sup>3</sup>The 16,384 SAs shared by two adjacent sub-arrays serve as a row buffer.

(a) Bank architecture and interconnect of (b) Bank architecture and interconnect of con-DRAM ventional STT-MRAM

(c) Data/control flows for a single read operation (d) Data/control flows for a single read operation in DRAM in STT-MRAM

(e) Page mode and pipelined RD operations in (f) Page mode and pipelined RD operations in DRAM STT-MRAM

Figure 2.1: Bank architecture and operation of DRAM (left) and conventional STT-MRAM (right).

determined by a column access command (RD or WR). Such STT-MRAM, however, suffers from the following limitations.

Limitation 1: Longer latency. DRAM places bit-line sense amps (BLSAs) [25,27] above and below a sub-array because the charge sharing limits the BL length in DRAM [58,59]. Because the local I/O (LIO) lines are too long to be driven by small BLSAs, larger I/O sense amps (IOSAs) are placed near the column decoder of each bank to assist the transfer of data through the LIO lines. In contrast, STT-MRAM does not require BLSAs [25, 27], placing only column multiplexers above and below a sub-array with one set of SAs at the bottom of a bank consisting of 128 sub-arrays. The column multiplexers connect one BL in a group of BLs to a SA through a GBL, which makes the sensing path of STT-MRAM

longer than that of DRAM. That is, the sensing path of STT-MRAM is the height of a bank while that of DRAM is the height of a sub-array. This in turn increases tRCD, minimum time from ACT to RD or WR while decreasing CL as shown in Fig. 2.1f [42].

Limitation 2: Smaller pages. Consider STT-MRAM sharing one SA with N BLs where N is  $16\sim128$  in prior work [27, 37, 60]. When STT-MRAM has 16,384 cells connected to a WL like DRAM, the page size of such STT-MRAM becomes 1/N of that of DRAM. Although not all data in pages are always used, smaller pages degrade performance of applications especially with high data locality such as streaming. Furthermore, with fewer SAs than BLs (i.e. cells in a row), STT-MRAM encounters the following three cases: (1) an access to another row (i.e. row miss); (2) an access to the same row with BLs selected and sensed by previous ACT (i.e. row hit); or (3) an access to the same row but BLs which are not selected and sensed by previous ACT yet (i.e. row hit but row buffer miss). The third case needs to be handled like a row miss because connecting appropriate BLs to SAs and sensing them are coupled with ACT in STT-MRAM sharing one SA with many BLs. That is, some of a column address becomes part of a row address since they are needed before sensing appropriate BLs. Consequently, selecting different BLs which were not selected by previous ACT always demands another ACT.

Limitation 3: Lower repair efficiency. The fact that a column address is split between row activation and column access commands, referred to as column address fragmentation in this study, creates two important challenges in managing chip yield and compatibility with existing DDR interfaces. Typically, the minimum repair granularity is a row or a column. For the sake of repair efficiency, any redundant WL can replace any defective WL in the same bank and any redundant BL can replace any faulty BL in the same mat. This technique is known as any-to-any replacement [61]. In STT-MRAM architecture sharing one SA with multiple BLs, however, both ACT and RD/WR do not have the full column address information. STT-MRAM uses the partial column address from ACT to select one BL in every BL group. That is, it selects one BL from each BL group and each mat has 64

BL groups. Therefore, if the partial column address to replace a defective BL in a BL group, it needs to replace every BL selected by the same partial column address. Consequently, STT-MRAM needs at least one redundant BL for every BL group (*i.e.*, 64 redundant BLs per mat). On the other hand, STT-MRAM uses the partial column address from RD or WR to select 64 BL groups from 1,024 BL groups (*i.e.*, the number of SAs). Hence, if it uses the partial column address to replace a defective BL in a BL group, it needs to replace every BL in the BL group. That is, STT-MRAM needs at least one redundant BL group in each mat, (*i.e.*, 16 BLs per group). Both cases negatively affect chip yield because they limit the flexibility of any-to-any replacement and increasing the minimum repair granularity.

Limitation 4: Higher pin cost. In DRAM, row and column addresses share the same address pins because they are delivered at different times [34, 56]. The number of address pins is equal to the number of row address bits because there are typically more rows than columns (e.g, 64K rows and 2K columns in  $\times$ 8-8Gb DRAM). In STT-MRAM, however, more address pins are needed to send some of a column address with a row address. For example, we need 4 more pins for STT-MRAM with N=16. Therefore, STT-MRAM with the shared SA architecture is not compatible with conventional DDR interfaces. To solve this problem, comboAS [27, 42] proposes to start actual row activation only after RD or WR sends a column address, but it always increases CL by the row activation time. LPDDR2-NVM [62, 63] proposes another command, PREACT to deliver a part of the row address before sending ACT so that STT-MRAM can compose a complete row address after receiving the ACT command. This also increases row activation time while consuming more command bus bandwidth.

## 2.3 SMART Architecture

Due to the destructive nature of read operation, DRAM requires an ACT command to sense the state of every cell in a row after the WL is asserted. This demands the number of SAs to

Figure 2.2: SMART bank architecture and data/control flow.

be equal to the number of cells in a row. Therefore, the number of cells in a row determines both the page size and the activation power in DRAM. This makes it impossible for DRAM to offer both high performance of large pages and low power of small pages at the same time. In contrast to DRAM, because of the non-destructive nature of read operation, STT-MRAM does not need to make an ACT command sense the state of every cell in a row after asserting the WL. Exploiting such a property, we propose to re-architect STT-MRAM which senses BLs as part of RD instead of ACT and re-define its page mode operation. In the remainder of this section, we first present the detail of SMART architecture and then discuss the five key benefits of SMART over conventional STT-MRAM and/or DRAM.

#### 2.3.1 Re-architecting STT-MRAM

In SMART a given ACT command completes its operation immediately after asserting a WL. That is, the ACT command does not sense any BL but it is a subsequent RD command that senses 64 BLs specified by the column address of the RD command. This, in turn, allows SMART to provide 2KB pages with only 64 SAs per bank along with other significant benefits which will be discussed in Sec. 2.3.2. To efficiently support such ACT and RD commands for SMART, we propose a bank architecture depicted in Fig. 2.2a.

Traditionally, the I/O interconnect of DRAM has a hierarchy as depicted in Fig 2.1a. Specifically, the interconnect from a memory cell to a SA is called BL. For a given column access, 64 BLs/BLSAs are selected by column selection lines (CSLs) and connected to

Figure 2.3: Change of read and write accesses after making sensing operation triggered by a RD command.

segmented I/O (SIO) lines in a sub-array through column switches (*i.e*, multiplexers). Then, the SIO lines are connected to local I/O (LIO) lines running vertically across a bank through I/O switches (IOSWs) [64]. The SIO, LIO and IOSW in DRAM correspond to local BL (LBL), GBL, and sub-array selection line (SSL), respectively, in SMART. Lastly, 64 SAs are placed at the bottom of each bank where IOSAs (*cf*, Sec. 2.2.2) are located in DRAM. In summary, SMART has a bank architecture similar to DRAM, but SMART has only 64 SAs per bank whereas DRAM has 16,384 SAs per sub-array.

This SMART bank architecture does not increase latency of memory read accesses, because the total amount of time for performing ACT and RD remains the same as conventional STT-MRAM. As shown in Fig. 2.3(left), compared with conventional STT-MRAM, SMART simply reduces the amount of time for ACT (tRCD) while increasing the amount of time for RD (CL). On the other hand, as shown in Fig. 2.3(right), SMART can decrease latency of memory write accesses. Specifically, compared with STT-MRAM, ACT-WR does not consume any time for sensing BLs without affecting CWL, time between the moment at which a WR command is sent and the moment at which its first data ( $D_{IN}$ ) is placed.

In DRAM, the SIO-LIO lines are electrically isolated from the GIO lines, as shown in Fig. 2.1a. This allows DRAM to internally pipeline more than two consecutive RD commands which can be issued at every tCCD interval (typically  $\sim 5$ ns) without waiting for long CL (typically  $\sim 13.75$ ns), as shown in Fig. 2.1e. SMART, however, has longer

Figure 2.4: SMART page mode and enhanced bank architecture.

read time than  $\protect\operatorname{CCD}$  because RD also senses BLs, as shown in Fig. 2.4a. To hide such long sensing time for consecutive RD commands, we propose to double the number of LBL and GBL lines, column multiplexers, and SAs, as shown in Fig. 2.4b. The two sensing paths take turns to serve consecutive RD commands so that SMART can handle one RD command at every  $\protect\operatorname{CCD}$  interval, as depicted in Fig. 2.4a. Our analysis in Sec. 2.4.1 shows that the cost of doubling the number of sensing paths does not increase the cost of STT-MRAM. In fact, SMART decreases the cost by  $\sim$ 6% because SMART still uses  $8\times$  fewer SAs than conventional STT-MRAM.

#### 2.3.2 Benefits

With the bank architecture presented in Sec. 2.3.1, SMART can provide the following notable benefits over conventional STT-MRAM.

Benefit 1: Larger pages and fewer SAs. SMART with a re-defined page mode can give the illusion of providing larger pages but demanding fewer SAs than conventional STT-MRAM. Specifically, an ACT command of SMART simply asserts a WL to connect every cell in the row to 16,384 BLs, and it is a subsequent RD command that selects appropriate 64 BLs and senses them. That is, SMART needs only 64 SAs per bank for 2KB pages whereas conventional STT-MRAM implements 1,024 SAs per bank for 128B pages. Because conventional STT-MRAM implements  $16\times$  fewer SAs than BLs, it repeatedly consumes long time ( $\pm$ RC = 27.5ns) for accessing the same row but columns which were not selected and sensed by the previous ACT command. SMART, however, does not consume  $\pm$ RC for such

Figure 2.5: Relation between page size and ACT energy.

column accesses because it only needs another RD command to connect and sense these columns. This can significantly reduce the latency of sequential memory accesses. Note that the SAs in conventional STT-MRAM consume ~9% of STT-MRAM space based on an adapted version of DRAMSpec [65]. That is, SMART can reduce the space and activation power consumed by SAs to 12.5% of conventional STT-MRAM. This is sufficient not only to negate the cost increased by another read path but also to significantly reduce sensing power and memory access latency, as elaborated below.

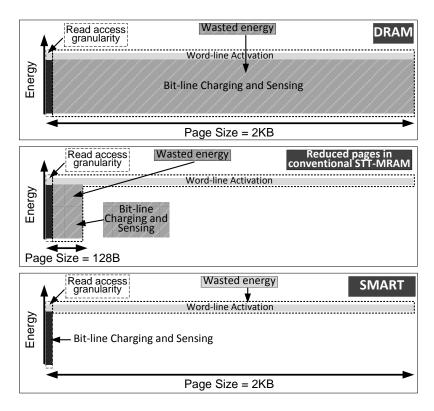

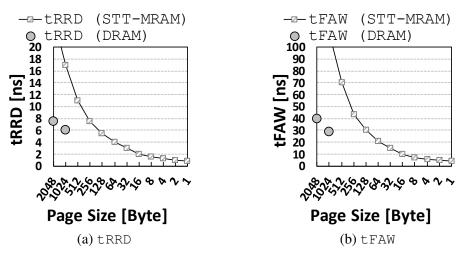

Benefit 2: Lower activation power with fewer SAs. ACT energy is a major contributor to total DRAM energy in DRAM. To reduce the ACT energy, DRAM architectures with smaller pages and fine-grained activation have been proposed [19–22]. In contrast, SMART reduces ACT energy while providing larger pages with fine-grained activation at a smaller cost than STT-DRAM. Fig. 2.5 illustrates the relationship between page size and ACT energy in DRAM, STT-MRAM and SMART. In a DRAM device providing 2KB pages, ACT

Figure 2.6: Impact of tRRD on bank-level parallelism.

asserts a WL, connecting 16,384 cells to 16,384 BLs. Although we consider higher WL voltage  $(V_{PP})$  than the BL voltage  $(V_{DD})$  and low efficiency of the charge pump to generate  $V_{PP}$  ( $\sim$ 30% [66]), we see that charging/discharging the BLs still dominates the ACT energy because of the large number of BLs. Since a RD command accesses only  $\sim$ 0.4% (= 64/16,384) of cells in a row, sensing 16,384 BLs for only a few RD accesses, referred to as the overfetching problem, wastes a significant amount of energy in DRAM, as shown in Fig. 2.5(top).

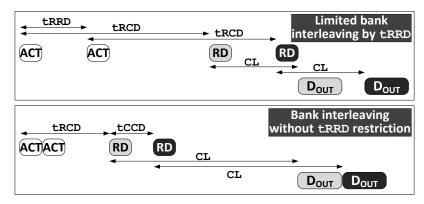

Benefit 3: Shorter latency with lower activation power. High ACT power affects not only total memory energy but also overall memory performance. Specifically, simultaneous activation of multiple rows, each charging/discharging 16,384 BLs, draws a large amount of current. This requires some time to recover from the voltage drop of the power delivery network, which is enforced by trrd (RAS to RAS delay) and trrd (four activation window). If there are two read accesses to different banks, the second ACT command can be scheduled between the first ACT and RD commands, but not until trrd has elapsed from the first ACT command, as depicted in Fig. 2.6(top). trrd limits the number of ACT commands to four within a trrd time window. Therefore, these constraints limit bank-level parallelism and they are imposed on not only DRAM but also other memory technologies. For example, LPDDR2-NVM also defines trrd and trrd [63].

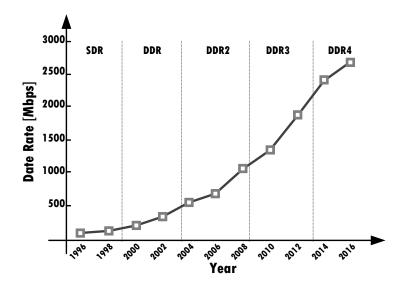

We plot tRRD and tFAW for various page sizes in Fig. 2.7, where the maximum activation current values are determined by a method of prior work [67]. This shows that tRRD

Figure 2.7: tRRD and tFAW for various page sizes. tRRD and tFAW for DRAM are obtained from a DDR3 datasheet [4].

and tFAW of conventional STT-MRAM with the page size of 128B are  $\sim$ 6.2ns and  $\sim$ 30ns, respectively. Since a current SA consumes far more power than a voltage SA, STT-MRAM needs longer tRRD than DRAM for the same page size. In contrast, SMART activates  $16\times$  fewer SAs and thus consumes less power than conventional STT-MRAM. Note that SMART ACT does not consume any sensing power and the recovery time for activating 64 SAs is short enough compared to tCCD ( $\sim$ 5ns). Hence, SMART can practically eliminate these two constraints and handle multiple ACT-RD commands to different banks back to back. This significantly reduces the latency of memory accesses especially for memory-intensive applications. For example, SMART can serve two ACT-RD commands to two different banks without consuming tRRD, as shown in Fig. 2.6(bottom).

Lastly, SMART also consume shorter time and less power than conventional STT-MRAM for memory write accesses. This is because an ACT command of SMART does not consume time and power for sensing which is unnecessary for memory write accesses, whereas conventional STT-MRAM still does.

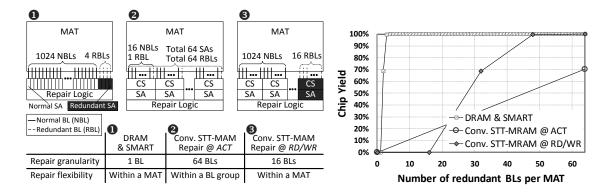

**Benefit 4: Fewer pins and more efficient repair.** Unlike conventional STT-MRAM, SMART does not demand any part of a column address with ACT, and thus it needs the same number of address pins as DRAM. That is, SMART does not suffer from the column address fragmentation problem discussed in Sec. 2.2.2. As discussed in Sec. 2.2.2, repair-

- (a) Example of various column repair schemes

- (b) Chip yield according to repair schemes

Figure 2.8: Comparison of the three repair schemes.

ing a mat of conventional STT-MRAM is not as efficient and flexible as DRAM because the column address fragmentation problem splits a column address between ACT and RD. This can significantly increase the cost of repairing mats or decrease the yield of STT-MRAM chips. Fig. 2.8a describes the column repair schemes for DRAM and conventional STT-MRAM. In DRAM (1), we can replace any 1,024 BLs with any 4 redundant BLs in a mat, and we repair a BL with a RD or WR command comprising a complete column address [68]. As SMART also exposes a complete column address to a RD or WR command, it can adopt the same column repair scheme as DRAM. In conventional STT-MRAM, however, neither a ACT command nor a RD/WR command has a complete column address. This makes repairing BLs far less efficient and flexible than DRAM or SMART.

Consider STT-MRAM with 1,024 BLs per mat and N (= 16) BLs per SA, (*i.e*, 1,024/N = 64 BL groups). If we are to repair a BL with ACT (②), we need one redundant BL for every N BLs (= 64 redundant BLs) as ACT can select only one BL in each BL group. On the other hand, if we are to repair a BL with RD or WR (③), we need to replace the entire BL group including a defective BL with a redundant BL group (= 16 redundant BLs) because RD or WR can select only BL groups.

We analyze the chip yield for various numbers of redundant BLs in Fig. 2.8b where we assumed that capacity of a chip is 8Gb, the number of mats is 16,384 in a chip where each

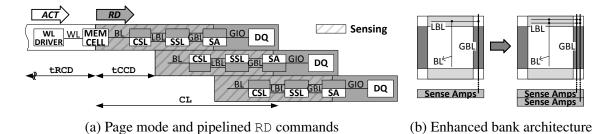

Figure 2.9: Change of row access cycle on row misses.

mat has 512 WLs and 1024 BLs, N is 16 for conventional STT-MRAM, memory defects follow a Poisson distribution [68, 69], the target bit error rate (BER) after row repair is  $10^{-7}$  and both DRAM/SMART and conventional STT-MRAM use the same row repair scheme. This shows that conventional STT-MRAM has a lower chip yield than DRAM or SMART for the same number of redundant BLs. In other words, to accomplish the same chip yield (99%) under the same BER ( $10^{7}$ ), conventional STT-MRAM requires  $10.7 \times$  more redundant BLs than DRAM and SMART.

Benefit 5: Eliminating precharge commands. To activate another row in the same bank (handle a row-buffer miss), a precharge (PRE) command needs to be sent to DRAM before an ACT command. Specifically, PRE in DRAM consists of two phases: (1) deactivating an asserted WL and (2) initializing BLs before ACT senses BLs. (2) also destroys cell states if it is performed before the WL is completely deactivated. Therefore, (1) should be completely done before (2) is started, and the amount of time for (1) and (2) (tRP) increases latency of memory accesses when row-buffer misses occur, as shown in Fig. 2.9(top). Furthermore, when STT-MRAM follows the same page mode operation as DRAM, it experiences more row-buffer misses with smaller pages and thus it pays this penalty more frequently than DRAM.

Unlike DRAM, however, STT-MRAM does not need to sequentially perform (1) and

(2) because of the non-destructive nature of its read operation. Moreover, STT-MRAM immediately transfers the cell states sensed by SAs to registers serving as a row buffer (Sec. 2.2.1). This allows STT-MRAM to initialize the BLs and SAs immediately after sensing BLs as part of ACT and reduce tRP. Note that STT-MRAM initializes its BLs by discharging them to  $V_{SS}$ . The driving strength of charging BLs is limited to prevent unexpected changes of cell states (read disturbance) [40, 70], but that of discharging BL is not limited. Hence, the amount of time for (2) can be much shorter than DRAM and it is already included in tras instead of trp [27, 42, 50]. This reduces trp of STT-MRAM by the amount of time for (2). Consequently, as shown in Fig. 2.9(middle), STT-MRAM can serve the second RD command faster than DRAM, but it does not reduce or hide the amount of time for (1), still demanding a separate PRE command. In contrast, SMART can overlap the amount of time for (1) ( $\sim 3.7 ns$ ) with the amount of time to decode a given row address and compare the address with addresses in a row repair table [68] during the early phase of ACT for the next row ( $\sim 4.2ns$ )<sup>4</sup>. This allows SMART to completely remove PRE right before ACT, further reducing the latency to handle row-buffer misses. Note that prior work only reduces tRP [42,59] while SMART does not consume tRP at all to handle row-buffer misses.

#### 2.3.3 Discussion

SMART can consume far less space for SAs and redundant BLs than conventional STT-MRAM but more space for another sensing path per bank. Overall, SMART is  $\sim$ 6% smaller than conventional STT-MRAM (Sec. 2.4.1). We summarize the key differences among DRAM, LPDDR2-NVM, conventional STT-MRAM and SMART in Table 2.1

SMART does not increase the latency of serving a single read request or consecutive read requests issued at the tCCD interval but it still increases CL. This may increase overall

$<sup>^4</sup>$ In this case, we leverage the  $\sim 0.5 ns$  difference, but some overlap between deactivating the previous WL and activating the current WL is still acceptable because such overlap does not destroy the cell states.

Table 2.1: Comparison with previous studies

|                             | DRAM                    | LPDDR2-NVM [38, 63] Conv-Delay [27, 42]    | Conv-Delay [27, 42]      | Conv-Pin [24, 41] | Conv-Pin [24, 41] This work (SMART)    |

|-----------------------------|-------------------------|--------------------------------------------|--------------------------|-------------------|----------------------------------------|

| Page size                   | Large (2KB)             | Small (32B)                                | Small (128B)             | Small (128B)      | Large (2KB)                            |

| Activation energy           | High                    | Medium                                     | Medium                   | Medium            | Extremely low                          |

| Bank-level parallelism      | Limited by tRRD/tFAW    | Same as DRAM                               | Same as DRAM             | Same as DRAM      | No limitation                          |

| Pin-compatible with DDR     | Yes                     | Yes (3-phase addressing) Yes (delayed ACT) | Yes (delayed ACT)        | No                | Yes                                    |

| Repair flexibility          | High                    | Low                                        | Low                      | Low               | High                                   |

|                             | SALP [59]: Can violate  |                                            | EarlyPA [42]: Internally |                   | רייייייייייייייייייייייייייייייייייייי |

| PRE technique               | tRP to access different | No                                         | perform PRE after the    | No                | NO PRE COMMAND                         |

|                             | sub-array               |                                            | sensing and set tRP=1    |                   | and no cre                             |

| Need software/OS support No | No                      | Yes, for write operation                   | No                       | No                | No                                     |

Highlighted green: good features, highlighted yellow: good, but limited, (Conv-Delay and Conv-Pin are the conventional STT-MRAM designs)

read latency of serving multiple read requests issued at longer intervals than tCCD. However, our evaluation shows that the performance degradation caused by the increased CL is outweighed by the performance increase by larger pages, higher bank-level parallelism, and lower row-buffer miss latency.

Since a row buffer holds data only for a previously accessed column, SMART cannot compare-before-write when a WR command is sent to a different column of the activated row. Comparing data before writing reduces write energy and improves the endurance by not overwriting the same data [27,71]. However, the high endurance of STT-MRAM cells ( $>10^{15}$ ) guarantees practically unlimited write operations (Sec. 2.2.1). Moreover, cell write energy is not a major component in overall write energy. Therefore, such a technique has limited impact on giga-bit scale STT-MRAM (Sec. 2.4.3).

Lastly, as this work focuses on re-architecting STT-MRAM for higher performance and lower energy, we do not discuss challenges related to its cells, such as thermal stability, write endurance, and read disturbance in detail [47, 70]. Nonetheless, recent studies have demonstrated small (sub-20nm) STT-MRAM cells that can offer fast switching time (sub-10ns) under low write current (sub-10uA), high write endurance (> 10<sup>15</sup>), thermal stability and read disturbance [72–74].

# 2.4 Device Modeling

To evaluate DRAM, STT-MRAM and SMART, we take DRAMSpec [65], a detailed timing, power, and area exploration tool which is originally developed for DRAM but can be adapted for other memory technologies such as STT-MRAM. For the baseline DRAM, we consider  $\times 8$  8Gb DRAM devices. While keeping the same chip floor-plan as DRAM, we adapt the bank architecture and interconnect models to model STT-MRAM and SMART with parameters taken from NVSim [75] and prior work [27,28,32,33,46] and then extrapolated to 30nm technology.

Table 2.2: Area comparison

|                       | DRAM        | Conventional STT-MRAM | SMART                |

|-----------------------|-------------|-----------------------|----------------------|

| Cell size             | $7.2F^{2}$  | $10.9F^{2}$           | $10.9F^{2}$          |

| SA size               | $1,213F^2$  | $27,111F^2$           | $27,111F^2$          |

| # of SA per bank      | 1,048,576   | 1,024                 | 128                  |

| Bank area $(\mu m^2)$ | 2,914×7,512 | $3,132 \times 8,695$  | $2,980 \times 8,390$ |

| Chip area $(mm^2)$    | 185.65      | 224.19 (21% †)        | 211.48 (14% †)       |

#### 2.4.1 Area Model

We assume a  $7.2F^2$  DRAM cell (2F×3.6F = WL×BL) provided by the DRAMSpec's 30nm technology model and a  $10.9F^2$  (3F×3.6F) STT-MRAM cell. For conventional STT-MRAM, we take N=16 which is from an industry STT-MRAM chip [27]. Following the JEDEC standard for DRAM, SMART has the same number of rows and columns as DRAM. However, SMART can implement any page size with the number of SAs equal to the number of bits per column access.

We also assume 12 redundant WLs and BLs per mat for DRAM and SMART (default in DRAMSpec) whereas we suppose 32 redundant BLs per mat for conventional STT-MRAM (Sec. 2.3.2). Prior work [50] demonstrated the layout area of various SAs for STT-MRAM, but it designed the SAs with a logic technology. Thus, we convert transistor sizes and design rules to those of a memory technology based on the ITRS roadmap to re-estimate the area [76].

We summarize the analyzed area of key memory components in Table 2.2. The total height of the BLSA blocks in DRAM is  $\sim$ 20% of the total chip height in a 20nm 8Gb DRAM device [77]. Therefore, the number and size of SAs greatly affect the total chip size. SMART has  $2\times$  more sensing paths than conventional STT-MRAM, but it consumes  $\sim$ 6% smaller space because it needs  $8\times$  fewer SAs. Albeit SMART uses  $1.5\times$  and  $21.4\times$  larger cells and SAs than DRAM, it uses  $8,192\times$  fewer SAs. This is because that a bank has 128 sub-arrays and a pair of two sub-arrays shares 16,384 SA in DRAM. SMART is

only 14% larger than DRAM whereas conventional STT-MRAM is 21% larger.

#### 2.4.2 Timing Model

Table. 2.3 summarizes the timing parameters and read access latency of DRAM, conventional STT-MRAM and SMART, based on the memory clock frequency of 800MHz. DRAM gives the shortest latency for a single read access because the sensing speed of DRAM is faster than that of STT-MRAM. However, the overall latency of multiple read accesses is not determined not only by the sensing speed but also by other timing parameters such as trrd, tray, tray and trp, especially when different banks and rows need to be accessed.

Table 2.3: Timing and latency comparison

|                                                       | DRAM | Conventional STT-MRAM | SMART |

|-------------------------------------------------------|------|-----------------------|-------|

| tRCD (clock cycle)                                    | 11   | 17 (1)                | 8     |

| tRAS (cc)                                             | 27   | 18 (19)               | 9     |

| tWR (cc)                                              | 12   | 19 (19)               | 19    |

| tRP (cc)                                              | 11   | 4 (4)                 | 4     |

| tRTP (cc)                                             | 6    | 1 (18)                | 9     |

| tRRD (cc)                                             | 6    | 5 (5)                 | 1     |

| tFAW(cc)                                              | 32   | 24 (24)               | 4     |

| CL (cc)                                               | 11   | 8 (25)                | 17    |

| Latency for single read                               | 22   | 25 (26)               | 25    |

| Latency for five reads - all different banks          | 54   | 49 (50)               | 41    |

| Latency for two reads - same bank, but different rows | 60   | 47 (48)               | 42    |

The numbers in ( ) are for the delaying ACT like comboAS [27,42].

# 2.4.3 Energy Model

In conventional STT-MRAM, activating fewer SAs reduces the energy consumption of a single ACT command. SMART, however, completely removes sensing energy from ACT

and thus it gives much smaller ACT energy than conventional STT-MRAM, as shown in Table 2.4. Instead, SMART includes the sensing energy in RD and thus the RD energy is higher than DRAM and conventional STT-MRAM. The conventional STT-MRAM has the lowest RD energy because of the reduced read path. Besides, STT-MRAM consumes higher WR energy than DRAM because of higher write current per cell. However, considering the energy consumption to transfer data across the chip through long interconnects, the impact of the cell write energy on the total write energy is limited.

Table 2.4: Energy and current comparison

|                                  | DRAM  | Conventional STT-MRAM | SMART |

|----------------------------------|-------|-----------------------|-------|

| ACT $(nJ)$                       | 1.28  | 0.45                  | 0.09  |

| Single RD $(nJ)$                 | 0.27  | 0.26                  | 0.31  |

| Single WR $(nJ)$                 | 0.28  | 0.35                  | 0.34  |

| Energy for 8B read $(nJ)$        | 1.54  | 0.71                  | 0.39  |

| Energy for 2KB read $(nJ)$       | 69.99 | 86.56                 | 78.19 |

| Energy for 8B write $(nJ)$       | 1.55  | 0.81                  | 0.43  |

| Energy for 2KB write $(nJ)$      | 72.79 | 96.80                 | 87.40 |

| IDDO $(mA)$                      | 67    | 64                    | 43    |

| IDD2P $(mA)$                     | 14    | 17                    | 16    |

| IDD2N $(mA)$                     | 36    | 39                    | 38    |

| IDD3N $(mA)$                     | 51    | 39                    | 38    |

| $\mathtt{IDD4R}\left( mA\right)$ | 122   | 121                   | 127   |

| $\mathtt{IDD4W}\left( mA\right)$ | 122   | 132                   | 131   |

| IDD5 $(mA)$                      | 245   | -                     | _     |

Table 2.4 shows the dynamic energy consumption of a single memory device for a single column (8B) request and a single page (2KB) request. If all columns in a page are accessed, STT-MRAM consumes more energy because of its inherent higher sensing and cell write energies. However, a single read/write access in STT-MRAM consumes less energy than DRAM because of the low ACT energy consumption. Comparing the two STT-MRAM's energies, SMART is more energy-efficient in all cases. This is because there is no wasted energy for the single column access and there are fewer ACT commands for the 2KB access. In addition, because SMART does not include sensing energy in write

requests, the gap between the two STT-MRAM designs in a 2KB write is larger than that in a 2KB read.

IDD2P is the power-down current and it is close to the sum of total transistor leakage. Thus, IDD2P is usually proportional to the total transistor width under the same technology. For simplicity, we increase IDD2P of STT-MRAM linearly with chip size. IDD2N and IDD3N are background current under precharge-standby and active-standby, respectively. The difference between IDD2P and IDD2N mainly results from the address/clock buffer current components. Thus, we assume the same increment for STT-MRAM's IDD2N. However, IDD3N stems from DRAM's unique leakage component. When a row in a bank is activated, 32,768 BLs are fully charged or discharged, whereas all BLs are precharged to  $V_{DD}/2$  level when the row is deactivated. If the BL length is 512, then 16,777,216 cells are connected to the 32,768 BLs. The increased voltage difference between BL to a cell transistor increases leakage current, which is mostly GIDL and junction leakage current [78]. Because of this large number, small leakage current changes cause huge increases in IDD3N. However, the BL/SL condition of STT-MRAM is different from that of DRAM during active-standby, because BLs and SLs are always discharged except during sensing and writing. Therefore, we assume IDD3N is the same as IDD2N in STT-MRAM.

#### 2.5 Evaluation

# 2.5.1 Evaluation Methodology

We evaluate SMART using MARSSx86 [79] and DRAMSim2 [80]. The configured system for the evaluation is shown in Table 2.5. Power-down mode is enabled to minimize standby power when there are no pending requests in the memory controller.

We employ two benchmark suites: SPEC2006 [82] and STREAM [3]. For multi-core simulations, multi-program workloads are composed as shown in Table 2.6. Misses-per-

Table 2.5: Default system configuration

| Component         | Specification                           |

|-------------------|-----------------------------------------|

| Processor         | single and quad core                    |

| Last Level Cache  | 2MB-8 way (single), 4MB-16 way (quad)   |

| Memory Controller | FR-FCFS [81], open-page, Ch:Ra:Ro:Ba:Co |

| Memory System     | 8GB single rank/ch (8Gb x8-DDR3L-1600)  |

kilo-instructions (MPKI) increases from mix1 to mix9. For all workloads, one billion instructions are simulated in their region of interest. In our evaluation, there are two conventional STT-MRAM designs with the shared SA structure: Conv-Pin and Conv-Delay. Conv-Pin emulates the designs proposed in [24,41]. However, they have no consideration for the expanded address pins which result from the shared SA structure and are not compatible with JEDEC DDR. On the other hand, Conv-Delay internally delays the activation instead of increasing pin count [27,42].

Table 2.6: Workloads for multi-core simulations

| Workload | Application list                         |

|----------|------------------------------------------|

| mix1     | bzip, povray, astar, libquantum          |

| mix2     | hmmer, sjeng, xalancbmk, libquantum      |

| mix3     | gobmk, h264ref, astar, lbm               |

| mix4     | povray, omnetpp, soplex, lbm             |

| mix5     | sjeng, xalancbmk, mcf, stream_scale      |

| mix6     | h264ref, povray, hmmer, lbm              |

| mix7     | bzip, omnetpp, stream_copy, stream_scale |

| mix8     | gobmk, milc, stream_add, stream_copy     |

| mix9     | hmmer, mcf, stream_triad, stream_add     |

#### 2.5.2 Performance

In SMART, we strive to implement large pages (2KB) with low cost. Memory performance is affected by row buffer hit rate and page size. Both DRAM and SMART can implement 2KB pages, while the conventional STT-MRAM designs can implement only 128B pages. The row buffer hit rates are shown in Fig. 2.10. SMART has a row hit rate within 1% of

Figure 2.10: Row hit rate in various workloads.

DRAM's. However, both conventional designs have significantly lower hit rates, especially in STREAM workloads. Although all designs show low hit rate in a few workloads, the designs with the larger pages still perform better.

Fig. 2.11 shows the overall read latency distribution of the three devices under the mix6 workload. DRAM has a long tail latency because of refresh, but STT-MRAM has a short tail. In the Conv-Pin, we clearly observe two peaks in its distribution corresponding to read latency under row hits and misses. In SMART, there is no clear second peak because row misses are serviced faster and their read latency is partially overlapped with read latency under row hits. Although SMART has no data in 10~19 cc range due to its long CL, it mostly falls within 30~39 cc, implying that it is neither too quick nor too slow. DRAM also has most of its latency within 30~39 cc, but its long tail negatively affects the overall latency. The average read latency of DRAM, Conv-Pin, and SMART is 52.6, 57.9 and 47.1 cc, respectively.

Fig. 2.12 shows system IPC improvement over DRAM. Conv-Pin and Conv-Delay degrade IPC on average by 3.7% and 4.3%. For some memory intensive workloads IPC degrades more than 30%. The biggest drawback in conventional STT-MRAM designs is the small page size. A substantial drop in row hit rate as compared to DRAM (*e.g.*, bwaves, sphinx3 and STREAMs) significantly degrades their IPC. For workloads with similar row hit rate (*e.g.*, lbm and milc), IPC is better than DRAM due to the removed refresh and

Figure 2.11: Read latency profile of mix6 workload.

restoration operations and the reduced precharge time. For non-memory-intensive work-loads, regardless of hit rate, the IPC difference is negligible. Between the two conventional designs, Conv-Delay shows worse overall performance than the Conv-Pin because of its long CL.

SMART, on the other hand, improves IPC on average by 5.1% over DRAM. Because SMART has the same page size as DRAM, it achieves row hit rates as high as DRAM for applications having sequential memory accesses. In addition, SMART improves performance for applications having random memory accesses (low row hit rate) due to better row-miss latency and bank-level parallelism. As a result, MPKI is correlated to the IPC difference. In memory intensive workloads with (MPKI >15) (e.g, GemsFDTD, lbm and libquantum), there is up to a 34% IPC improvement over DRAM. Non-memory intensive workloads with (MPKI < 1) (e.g, gamess, and namd), show no significant IPC improvement.

# **2.5.3** Energy

SMART has three advantages in energy over DRAM. First, ACT energy is extremely low, because sensing, which was the main energy contributor to ACT, was moved to RD. Second, cell leakage current is eliminated while the bank is activated (low active-standby power).

Figure 2.13: Energy savings over DRAM.

Figure 2.14: Breakdown of average memory power.

Last, STT-MRAM cells are non-volatile and have no refresh. While both the conventional STT-MRAM designs enjoy similar advantages over DRAM, they saved ACT energy by reducing the page size and impacted the row hits.

Fig. 2.14 breaks down average memory power. ACT power is higher than RD/WR power in DRAM. The average refresh power is  $14\sim29\%$  of the total memory average power and its relative portion increases in non-memory intensive workloads (*e.g.*, gcc). Although ACT power in the conventional STT-MRAM is less than in DRAM, the difference decreases when the conventional designs have low row hit rates (*e.g.*, omnetpp and stream\_scale). In these workloads, because memory has fewer chances to enter power-down mode due to row misses, the background power becomes higher than in DRAM in spite of the lower  $I_{DD3N}$ . RD/WR power is also higher than DRAM because of higher cell write current. In contrast, in SMART, the ACT power does not dominate total memory power. Although its RD/WR power is the highest among the four devices, the total dynamic power, which is the sum of ACT and RD/WR power, is the lowest. In addition, because SMART enters power-down mode as often as DRAM, background power stays low.

Fig. 2.13 shows the energy savings over DRAM. On average, the Conv-Pin and Conv-Delay save 24.9% and 24.5% of energy and SMART saves 38.9%. Due to small page size, energy savings of the conventional STT-MRAM is more sensitive to the row hit rate

Figure 2.15: Normalized performance improvement and energy saving of the conventional STT-MRAM (Conv-Delay) to the baseline DRAM with various page size.

difference than SMART.

#### 2.5.4 Sensitivity Analysis

**Page size.** Fig. 2.15 shows performance improvement and energy savings for various page sizes in conventional STT-MRAM. Overall, large pages improve performance while small pages save energy. The 256B page size slightly outperforms DRAM while saving less than 10% of energy. However, 256B (N=8) is not a practical page size considering the large size and high power consumption of the SAs. In prior STT-MRAM chip demonstrations, N ranges from 16 to 128 [27, 33, 37, 40, 48]. N=16 was conservatively selected for the baseline STT-MRAM.

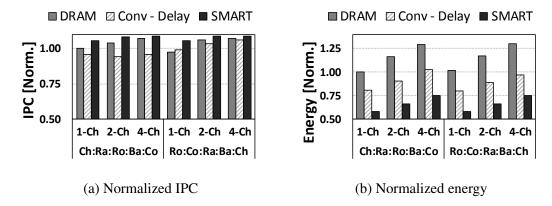

Address mapping and channels. The results for two mapping schemes with  $1\sim4$  channels are shown in Fig. 2.16. DRAM is sensitive to the number of channels and performs the worst with a single channel because it is completely blocked during refresh. Generally, more channels increase the total bandwidth, but they also increase the number of memory chips and energy.

Conventional STT-MRAM is sensitive to the address mapping scheme. It performs better under Ro:Co:Ra:Ba:Ch because of its small pages. In general, the page size and row buffer locality are important to the Ch:Ra:Ro:Ba:Co mapping and the number of banks,

Figure 2.16: Normalized IPC and energy to DRAM with various configurations (average of all mix workloads).

ranks, and channels plays a primary role under the Ro:Co:Ra:Ba:Ch mapping.

In contrast, SMART is less sensitive to address mapping and channels, because it has large pages, short row-miss latency, and no ACT to ACT constraint. In addition, there is no significant difference in energy savings according to the number of channels, because SMART reduces both dynamic and static energies.

#### 2.6 Related Work