# **Bidirectional Neural Interface Circuits with On-Chip Stimulation Artifact Reduction Schemes**

by

Adam Ernest Mendrela

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2018

#### **Doctoral Committee:**

Professor Michael P. Flynn, Co-chair Professor Euisik Yoon, Co-chair Assistant Professor Omar Ahmed Assistant Research Scientist John Seymour Professor Emeritus Kensall D. Wise

# Adam Ernest Mendrela

mendrela@umich.edu

ORCID® iD: 0000-0003-1114-2891

© Adam Mendrela 2018

To my parents, Elżbieta and Ernest

To God and mankind

# **ACKNOWLEDGMENTS**

I find it ironic that doctoral studies are a time of great personal struggle, self-imposed solitude, and reliance on one's own motivation, yet they truly are an embodiment of the proverb "it takes a village ..." It is thus my duty to acknowledge and thank everyone in this proverbial village.

First and foremost, I thank my co-advisors, Professors Euisik Yoon and Michael Flynn. Prof. Yoon "scouted" my graduate school application and was the first person at Michigan to put faith in me. He has shown me how to inspire and be inspired by my own work and strove to bring out in me the qualities of an independent researcher. I am grateful that Prof. Flynn has also co-adopted me into his group. His technical understanding of integrated circuits has helped shape a major part of this work. His infectious research optimism and his values as an advisor are essential reasons why I have gotten this far in my studies.

I would like to thank the rest of the committee. Prof. Omar Ahmed, as a neuroscientist, has provided important insight into the "user" perspective of this work. Prof. Kensall Wise gave me key advice and pointers when I was writing important sections of this dissertation. I offer special thanks to Dr. John Seymour, with whom I also had the pleasure of working in the same lab. I have learned many things from our numerous conversations about neurotechnology and the biomedical industry.

I am grateful to all my hands-on collaborators. Kanghwan "Khan" Kim and Drs. Mihály "Misi" Vöröslakos, Sung-Yun Park, Vivek Nagaraj, Daniel English, and Sam McKenzie are all responsible for portions of the dissertation's content and have co-authored related publications. I am also proud to call them my friends. Mine and their efforts would also not have been possible without the support of the collaborating PIs, Profs. Tay Netoff of University of Minnesota and György Buzsáki of NYU, both of whom I also personally thank. I want to express my gratitude to all the Flynn Group and Yoon Lab colleagues with whom I became friends over the years and who were indispensable to any success of mine. To all those who have graduated, I thank for all the help and advice. To those who will graduate after me, I root for you with all my heart.

I am grateful for the support I have had from my Ann Arbor friends. I would like to give special shout outs to my colleagues in the EECS department, "the Ann Arbor brunch club," Saint Mary Student Parish, and certain recent medical school graduates. However, two friends deserve a special treatment from me: Drs. Gopal Nataraj and John "Trey" Ruppe. We were roommates in Ann Arbor for many years and they have seen me at my best and my worst. It is difficult for me to imagine my path without their unwavering support.

And I think it goes without saying how much I owe of this work to my family, especially my parents, Ela and Ernest, who were the first Electrical Engineers I had ever met. As they are my childhood *and* adulthood heroes, it is difficult to put into words how much they have and still continue to inspire me.

I reserve my last "thank you" to God. While I have resigned myself to never be sure of his existence, it is to him I have turned to in the bleakest moments. Through him, I add my own little brick to the betterment of the world.

# TABLE OF CONTENTS

| DEDICATION                                              | ii    |

|---------------------------------------------------------|-------|

| ACKNOWLEDGMENTS                                         | iii   |

| LIST OF FIGURES                                         | ix    |

| LIST OF TABLES                                          | xvii  |

| ABSTRACT                                                | xviii |

| CHAPTER 1 Introduction                                  | 1     |

| 1.1 Background and Motivation                           | 1     |

| 1.2 Current State-of-the-Art Neural Interfacing Systems | 2     |

| 1.3 Outline                                             | 4     |

| CHAPTER 2 Neuroscience and Neurotechnology Background   | 5     |

| 2.1 Introduction to Neuroscience                        | 5     |

| 2.2 Neuromodulation and Closed-loop Control             | 7     |

| 2.2.1 Neuromodulation                                   | 7     |

| 2.2.2 Closed-loop Modulation                            | 9     |

| 2.3 Neural Interface Modalities                         | 10    |

| 2.3.1 Neural Recording                                  | 10    |

| 2.3.2 Neural Stimulation                                | 13    |

| CHAPTER 3 Bidirectional Neural Interface IC with Active Stimulation Artifact Rejection | 16 |

|----------------------------------------------------------------------------------------|----|

| 3.1 Introduction                                                                       | 16 |

| 3.2 Theory of Stimulation Artifact Cancellation                                        | 17 |

| 3.2.1 Artifact Coupling                                                                | 17 |

| 3.2.2 Prior Art                                                                        | 18 |

| 3.2.3 Artifact Cancellation Algorithm                                                  | 20 |

| 3.3 Common Mode Noise Rejection                                                        | 24 |

| 3.4 Circuit Implementation                                                             | 26 |

| 3.4.1 Stimulation Artifact Cancellation Circuit                                        | 28 |

| 3.4.2 Common Average Referencing (CAR) Circuit                                         | 31 |

| 3.4.3 Range Adapting (RA) SAR ADC                                                      | 32 |

| 3.4.3.1 Range-Adapting Algorithm                                                       | 32 |

| 3.4.3.2 Range Adapting SAR Switching Scheme                                            | 33 |

| 3.4.3.3 ADC Power Consumption                                                          | 34 |

| 3.4.3.4 ADC Circuit Implementation                                                     | 35 |

| 3.5 Measurements                                                                       | 37 |

| 3.5.1 System Performance                                                               | 37 |

| 3.5.2 CAR Circuit Measurements                                                         | 38 |

| 3.5.3 ADC Measurements                                                                 | 38 |

| 3.6 In vivo Magguraments                                                               | 30 |

| 3.7 Conclusions                                                            | 41 |

|----------------------------------------------------------------------------|----|

| CHAPTER 4 Miniature Headstage for High Resolution Closed-Loop Optogenetics | 43 |

| 4.1 Introduction                                                           | 43 |

| 4.2 System Architecture                                                    | 46 |

| 4.2.1 Headstage                                                            | 46 |

| 4.2.2 Peripheral Components                                                | 47 |

| 4.3 Headstage Hardware Design                                              | 48 |

| 4.3.2 LED Driver ASIC                                                      | 50 |

| 4.3.3 Headstage Assembly                                                   | 52 |

| 4.4 System Characterization                                                | 54 |

| 4.4.2 LED Driver Characterization                                          | 55 |

| 4.4.3 Integrated System Measurements                                       | 57 |

| 4.5 In Vivo Validation                                                     | 59 |

| 4.5.1 Validation of Optical Induction of Neuronal Activities               | 61 |

| 4.5.2 Validation of Selective Local Stimulation Capability                 | 62 |

| 4.6 Discussion                                                             | 63 |

| 4.6.1 Reduction of Communication Latency                                   | 64 |

| 4.6.2 Reduction of Stimulation Artifact                                    | 65 |

| 4.7 Conclusion                                                             | 66 |

| CHAPTER 5 Opto-Electrophysiology Neural Interface IC with Artifact-Preven | ting Optical Pulse |

|---------------------------------------------------------------------------|--------------------|

| Shaping                                                                   | 67                 |

| 5.1 Introduction                                                          | 67                 |

| 5.2 Optical Artifact Analysis and Prevention                              | 69                 |

| 5.2.1 Artifact Formation                                                  | 70                 |

| 5.2.2 Artifact Prevention                                                 | 73                 |

| 5.3 System Architecture                                                   | 79                 |

| 5.4 Circuit Implementation                                                | 82                 |

| 5.4.1 LED Driver with current pulse modulation                            | 82                 |

| 5.4.2 Fully-Integrated Step-up Voltage Regulator                          | 87                 |

| 5.5 Benchtop Measurements                                                 | 89                 |

| 5.6 <i>In Vivo</i> Measurements                                           | 93                 |

| 5.7 Conclusion                                                            | 100                |

| CHAPTER 6 Contributions and Future Work                                   | 101                |

| 6.1 Contributions                                                         | 101                |

| 6.2 Future Research Directions                                            | 103                |

| RIRI IOGRAPHY                                                             | 106                |

# LIST OF FIGURES

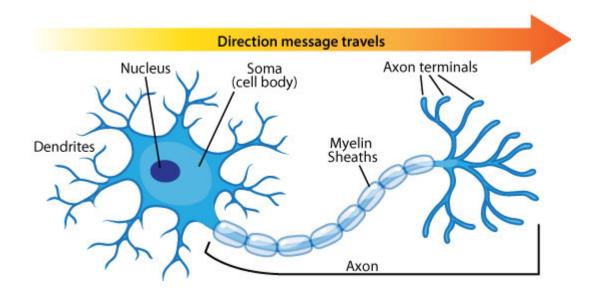

| Figure 2-1. Simplified neuron diagram. (Source: https://askabiologist.asu.edu/neuron-anatomy     | 6. (' |

|--------------------------------------------------------------------------------------------------|-------|

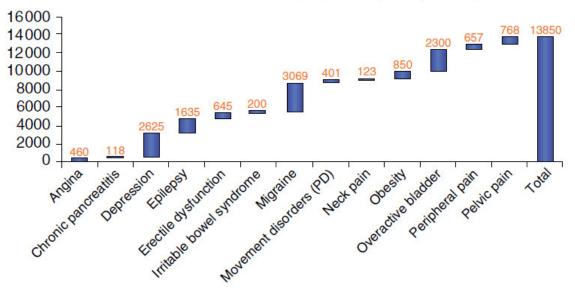

| Figure 2-2. Disorders and estimated population in USA affected by disorders which can be         |       |

| treated by neurostimulation. [63]                                                                | 8     |

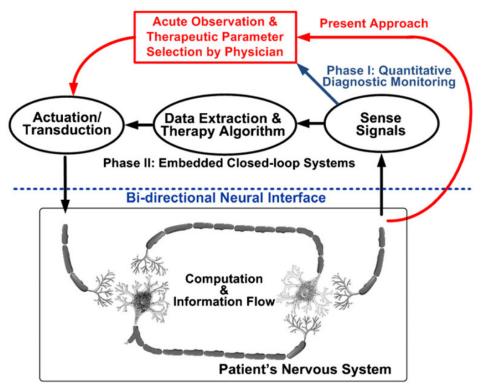

| Figure 2-3. Diagram comparing open-loop (in red) and closed-loop (in black) neuromodulation      | n     |

| approach. [28]                                                                                   | 9     |

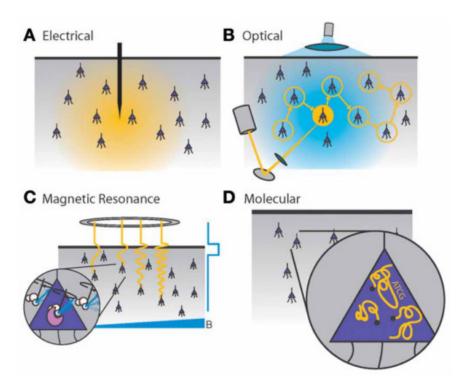

| Figure 2-4. Four major neural signal recording modalities: (A) electrical recording, (B) optical | l     |

| recording, (C) MRI recording, and (D) molecular recording. [72]                                  | .11   |

| Figure 2-5. Illustration of various electrophysiological neural recording technologies implanted | d     |

| in a mouse brain. Adapted from [125].                                                            | .12   |

| Figure 2-6. Pictorial explanation of the optogenetics technique. [126]                           | .14   |

| Figure 3-1. (a) Diagram showing formation and addition of stimulation artifacts in the recorder  | d     |

| signal, and (b) comparison of similar characteristics of a seizure and stimulation artifac       | et    |

| signal                                                                                           | .18   |

| Figure 3-2. System-level approaches to artifact removal.                                         | .19   |

| Figure 3-3. Previous front-end artifact rejection methods: (a) signal blanking and (b) symmetri  | ic    |

| sensing                                                                                          | .20   |

| Figure 3-4. System diagram of stimulation artifact addition and cancellation through adaptive    |       |

| filtering. The recorded signal, $yt$ , is the corrupted neural signal picked up at the tissue-   |       |

| circuit interface while the recovered signal vt is the on-chin recovered neural signal           | 21    |

| Figure 3-5. Simulation of the stimulation artifact cancellation algorithm with artificial neural    |    |

|-----------------------------------------------------------------------------------------------------|----|

| data showing the system learning the response of the tissue.                                        | 2  |

| Figure 3-6. The final impulse response of the adaptive filter after training resembles the artifact |    |

| waveform2                                                                                           | .3 |

| Figure 3-7 Top-level diagram of common average referencing (CAR) algorithm2                         | 4  |

| Figure 3-8. (a) CAR-4 4-channel groupings mapped onto an ECoG electrode grid, and (b)               |    |

| comparison in SNR of ECoG recordings between raw data, active CAR-4, and active                     |    |

| CAR-16 algorithms.                                                                                  | 5  |

| Figure 3-9. Top-level system architecture                                                           | 6  |

| Figure 3-10. Schematic of stimulation artifact cancellation circuit. Analog subtraction is framed   |    |

| in gray while the adaptive filter is framed in black.                                               | 7  |

| Figure 3-11. Schematic of a single filter tap implementing LMS update and filter multiply and       |    |

| accumulate                                                                                          | 9  |

| Figure 3-12. CAR circuit implementation: the averaging CAR network is implemented for each          |    |

| channel in the group as shown for channel 1                                                         | 0  |

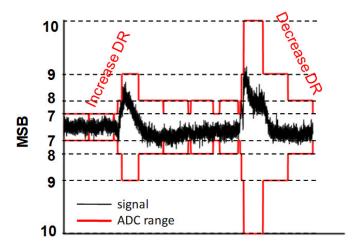

| Figure 3-13. Example of Range-Adapting (RA) SAR ADC range (MSB) following the shape of              | a  |

| neural signal3                                                                                      | 2  |

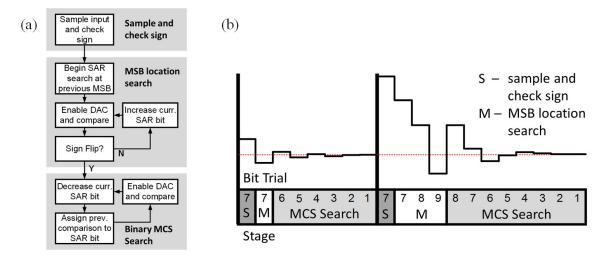

| Figure 3-14. (a) Range-Adapting (RA) SAR algorithm logic flowchart and (b) comparator input         |    |

| voltage during RA SAR A-to-D conversions for in-range and out-of-range samples                      |    |

| respectively. The conversion phases and bit cycles are also shown                                   | 3  |

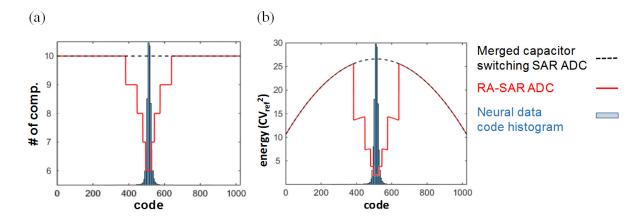

| Figure 3-15. Simulated minimum (a) number of comparisons and (b) capacitive DAC switching           |    |

| energy for 10 bit RA SAR ADC as compared to a merged capacitor switching SAR ADC                    | J. |

| Overlaid neural data code histogram snow most data fans within the most efficient co                   | ae    |

|--------------------------------------------------------------------------------------------------------|-------|

| range                                                                                                  | 34    |

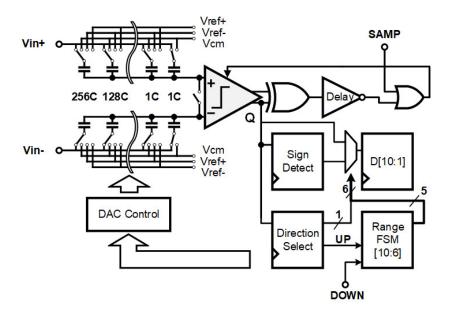

| Figure 3-16. RA SAR ADC architecture schematic.                                                        | 35    |

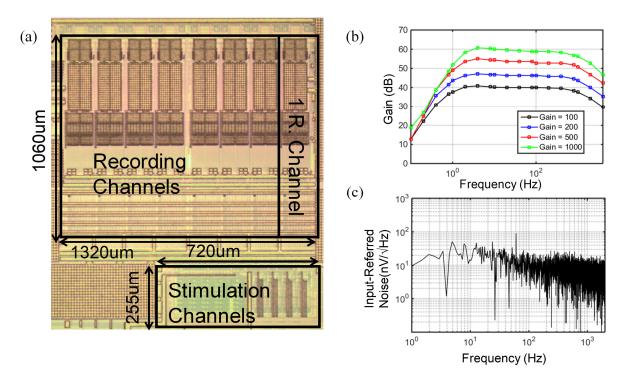

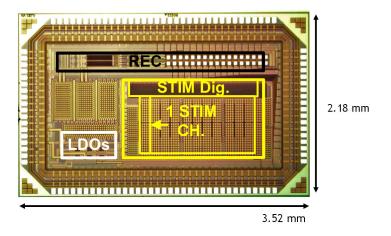

| Figure 3-17. (a) Chip microphotograph, (b) Recording channel frequency response for 4 gain             | 1     |

| settings measured at ADC output and (c) input-referred noise of the full recording                     |       |

| channel                                                                                                | 36    |

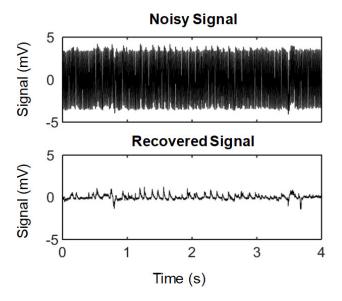

| Figure 3-18. Full channel recording before and after activating the 4 channel CAR circuit,             |       |

| showing the common mode (60 Hz) noise reduction in <i>in-vitro</i> recording                           | 37    |

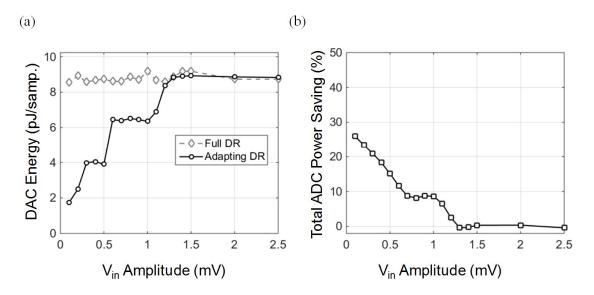

| Figure 3-19. ADC measurements showing (a) capacitive DAC energy consumption per samp                   | le    |

| for enabled/disabled adapting DR algorithm for amplitude-swept sinusoid input and (                    | b)    |

| the ADC total power savings.                                                                           | 38    |

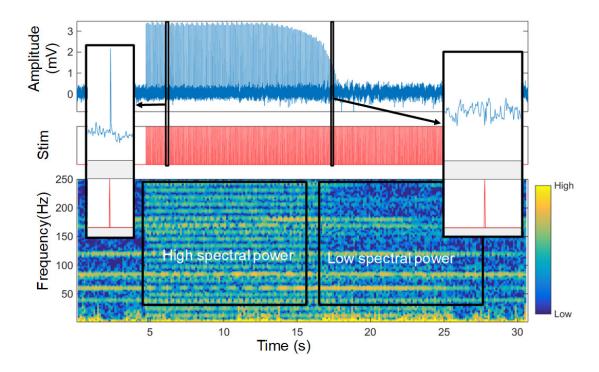

| Figure 3-20. <i>In-vivo</i> experiment results showing stimulation artifact cancellation learning pro- | ocess |

| for 12 Hz 600 $\mu$ A biphasic stimulation. Top plot shows the raw time-domain plot of t               | he    |

| recording output, middle plot shows the stimulation timing, and the bottom plot show                   | 'S    |

| the recorded output spectrogram.                                                                       | 39    |

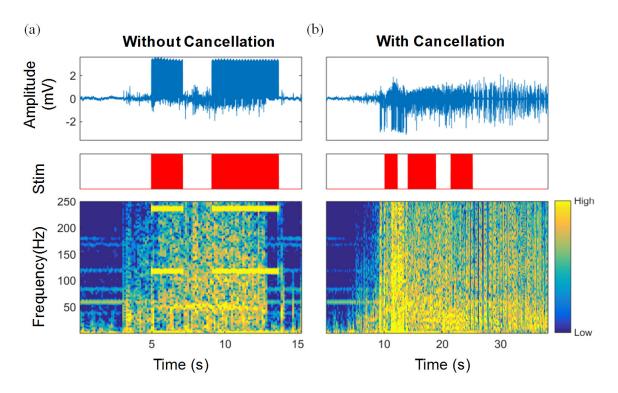

| Figure 3-21. Neural recordings of 120 Hz 600 μA biphasic stimulation during seizure activity           | y (a) |

| without activate artifact cancellation and (b) with active artifact cancellation.                      | 40    |

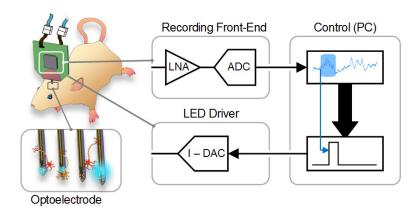

| Figure 4-1. Schematic diagram of the opto-electrophysiology system in closed-loop                      |       |

| configuration.                                                                                         | 45    |

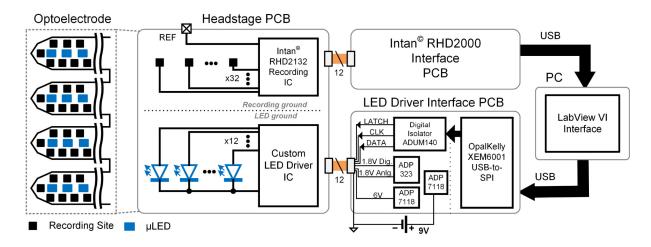

| Figure 4-2. System circuit diagram showing the connections between the headstage PCB with              | h     |

| integrated optoelectrode and recording and LED driver ICs, interface boards providing                  | g     |

| power and communication for the recording and LED driver ICs, and the PC-based                         |       |

| LahView VI Interface                                                                                   | 46    |

| Figure 4-3. LabVIEW-based user interface for individual μLED control. In the inset, the channel     |

|-----------------------------------------------------------------------------------------------------|

| 1 $\mu\text{LED}$ located on top of the leftmost shank is configured to pulse at 1Hz frequency with |

| 50% duty cycle and 10μA current amplitude                                                           |

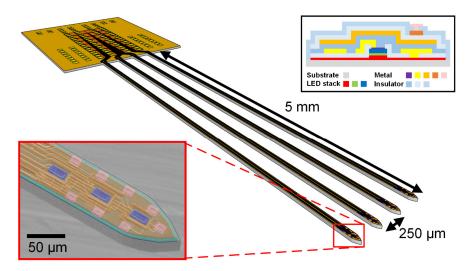

| Figure 4-4. Schematic diagram of the $\mu LED$ optoelectrode. The insets show (bottom left) SEM     |

| image of the tip of a shank of the fabricated optoelectrode with coloring for visualization         |

| and (top right) the cross-section of the optoelectrode                                              |

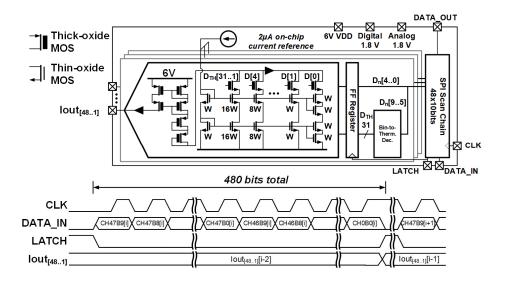

| Figure 4-5. LED driver ASIC schematic and input/output signal timing diagram50                      |

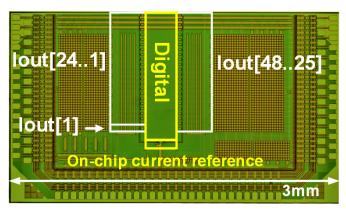

| Figure 4-6. Chip microphotograph of μLED Driver ASIC chip                                           |

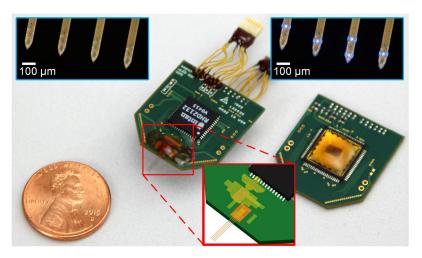

| Figure 4-7. Photographs of the assembled headstages. Insets show(top) micropho- tographies of       |

| the tips of the optoelectrodes, and (bottom) the schematic diagram of the polyimide-based           |

| flexible cable interposer. The light leakage from the sides of the optoelectrode shank,             |

| shown in the top right inset, is an artifact due to the combination of poor light coupling          |

| efficiency in the air and high optical output power53                                               |

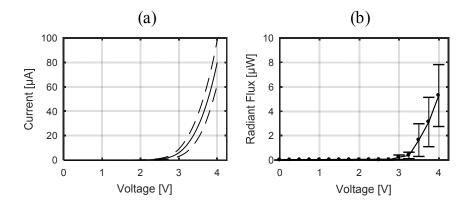

| Figure 4-8. The opto-electrical characteristics of $\mu LEDs$ (n = 7) on the fabri- cated $\mu LED$ |

| optoelectrode: (a) I vs. V curves and (b) output radiant optical flux vs. V curves. Dotted          |

| lines and the error bars represent one standard deviations from the mean                            |

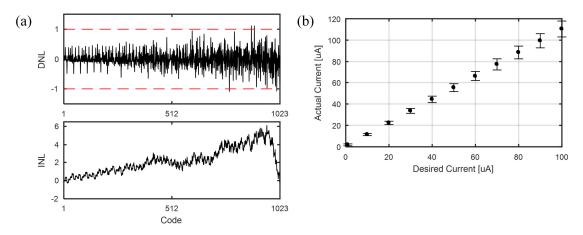

| Figure 4-9. DC output current measurements of the fabricated LED driver chip showing (a)            |

| differential and integral non-linearity plots, and (b) mean current measurements across 19          |

| dies. Error bars represent one standard deviation from the mean                                     |

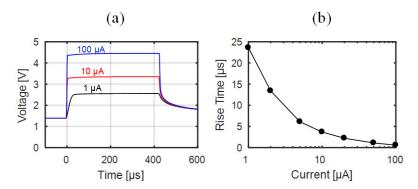

| Figure 4-10. (a) μLED anode voltage transient response to 3 current pulses of varying amplitudes    |

| and (b) plot of changing $\mu LED$ anode voltage rise timewith increasing driving current           |

| pulse amplitude 57                                                                                  |

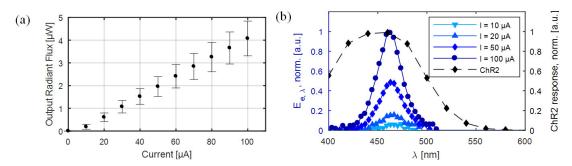

| Figure 4-11. The optical characteristics of the $\mu$ LEDs on the fabricated $\mu$ LED optoelectrode   |

|--------------------------------------------------------------------------------------------------------|

| showing (a) average $\Phi e$ vs. I curve (n = 7) and (b) the normalized spectral radiant flux of       |

| the $\mu LED$ at different forward current (with the spectral response of ChR2)59                      |

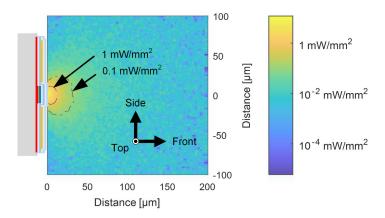

| Figure 4-12. Irradiance distribution inside the brain tissue by $\mu LED$ illumination, on the axial   |

| cross-sectional plane with the origin located at the center of the $\mu LED$ surface. The              |

| thickness of the LED, metal, and dielectric layers are not drawn to scale59                            |

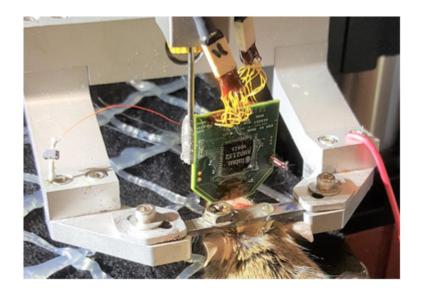

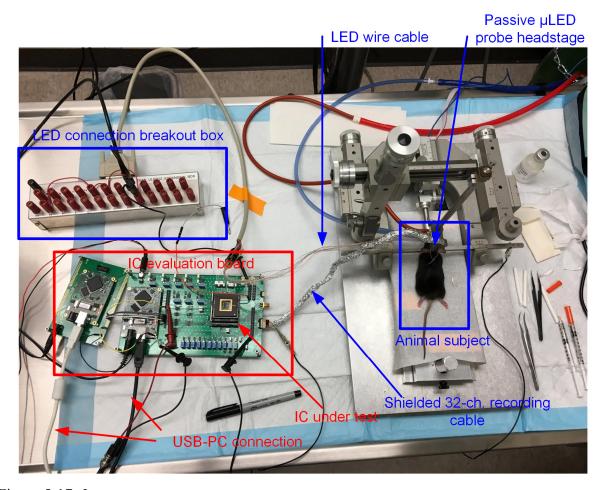

| Figure 4-13. <i>In vivo</i> measurement setup of the headstage. The optoelectrode is implanted into an |

| anesthetized mouse.                                                                                    |

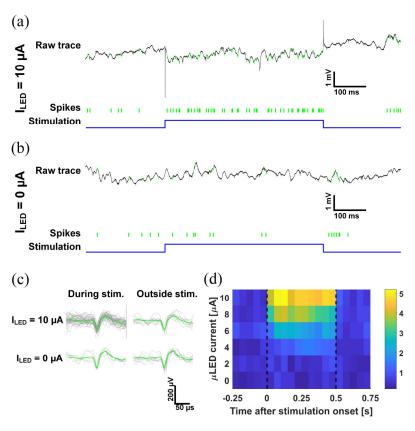

| Figure 4-14. <i>In vivo</i> measurements validating the light-induced neuronal activity: raw signals   |

| recorded from an electrode as well as the raster plots of spikes from an optically excited             |

| neuron during a pulsed stimulation with (a) 10 $\mu A$ and (b) 0 $\mu A$ forward currents, (c)         |

| waveform of the action potential during the off- and the on-time of the pulse, and (d)                 |

| peristimulus time histograms of the neuron at different on-time forward currents62                     |

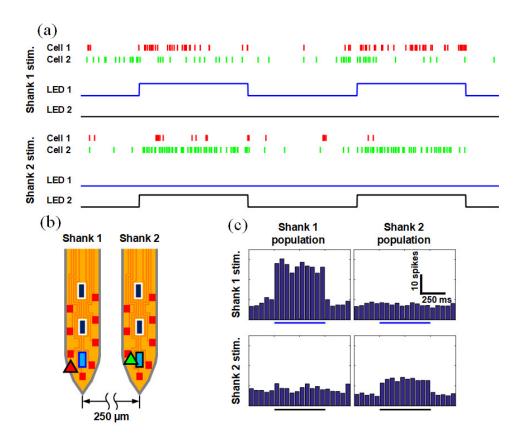

| Figure 4-15. In vivo measurements validating selective location neural stimulation: (a) raster         |

| plots of spikes from two optically excited neurons responding to different $\mu LEDs$ , (b)            |

| estimated locations of the neurons and the $\mu \text{LEDs},$ and (c) peristimulus time histograms     |

| of the neurons around shanks with the respective µLEDs                                                 |

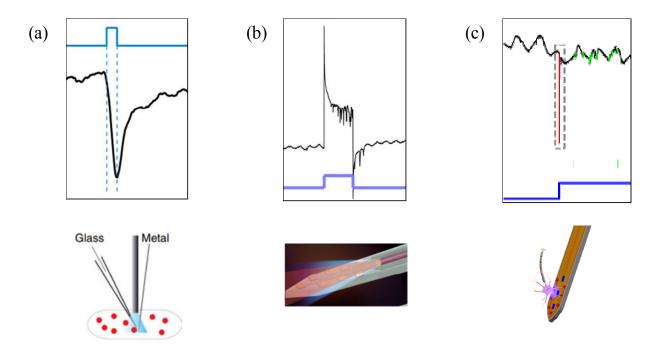

| Figure 5-1. (a) Stimulation artifact forms when a fiber-guided laser light hits the surface of a       |

| metal wire electrode inside the neural tissue [113], (b) stimulation artifact observed on an           |

| integrated laser waveguide probe with recording electrodes in [114], and (c) stimulation               |

| artifacts observed on an integrated μLED probe with recording electrodes [99]70                        |

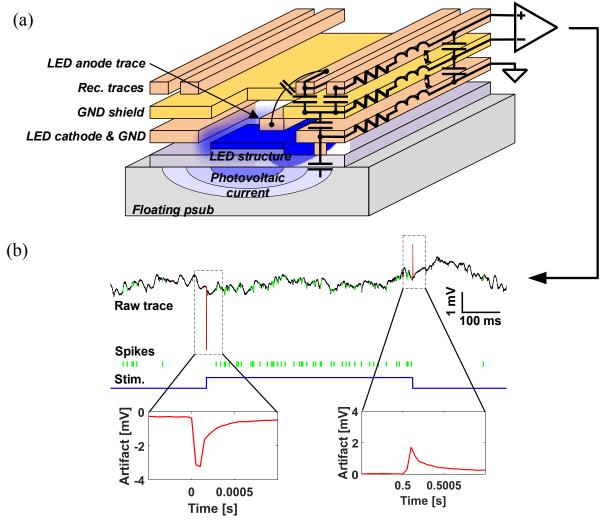

| Figure 5 | 5-2. (a) Simplified μLED optoelectrode cross-sectional diagram highlighting the artifact      |

|----------|-----------------------------------------------------------------------------------------------|

| (        | coupling mechanisms and (b) recording snippet from a 2-layer optoelectrode showing            |

| :        | artifacts (in red) at stimulation activation and deactivation                                 |

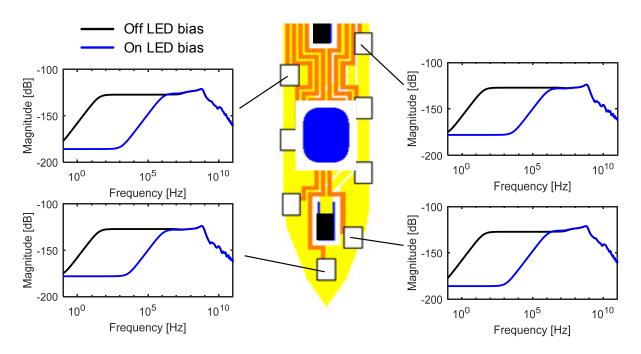

| Figure 5 | 5-3. SPICE simulation results of on-probe EMI coupling between the $\mu LED$ and              |

| 1        | recording channels. A current sinusoid of 1 $\mu A$ was injected into the middle $\mu LED$    |

| (        | channel and its frequency was swept from 0.1 Hz to 100 GHz. This was performed at two         |

| 1        | bias points: 0 μA (off μLED) and 100 μA (on μLED)73                                           |

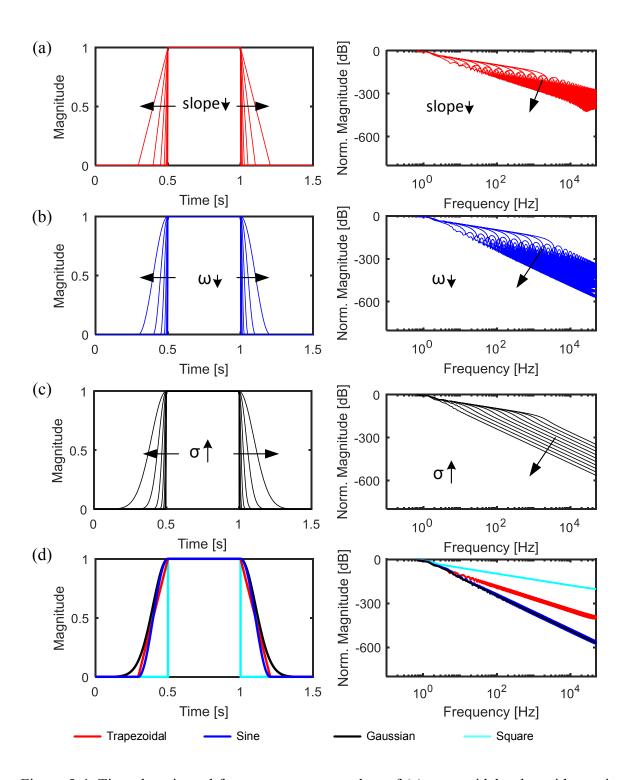

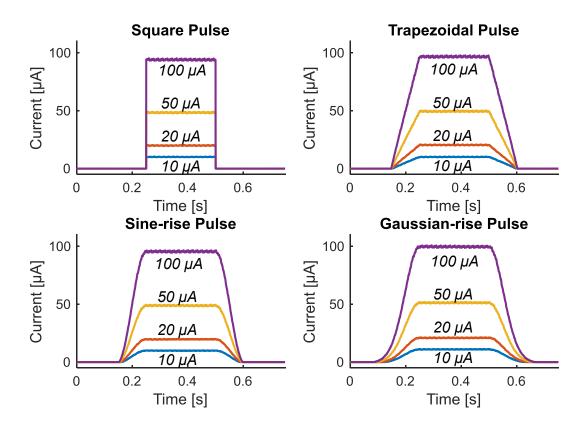

| Figure 5 | 5-4. Time-domain and frequency spectrum plots of (a) trapezoidal pulse with varying           |

| \$       | slope, (b) sine-rise pulse with varying transition frequencies, (c) Gaussian-rise pulse with  |

| ,        | varying $\sigma$ parameters, and (d) comparison of 3 pulse types with similar rise times to a |

| 1        | rectangular pulse78                                                                           |

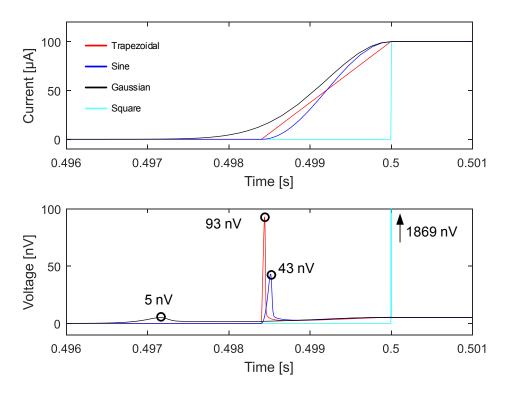

| Figure 5 | 5-5. Time-domain simulation of LED current pulse-related artifact. Plot on top shows the      |

| j        | input current and bottom plot shows the artifact simulated on a same-shank recording          |

| (        | channel with annotated peak voltages79                                                        |

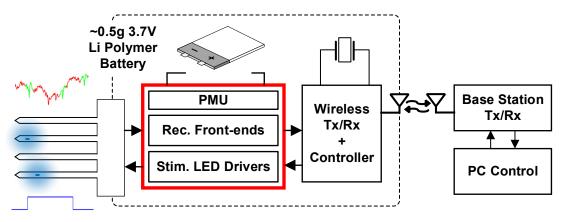

| Figure 5 | 5-6. Proposed wireless opto-electrophysiology system with interface IC outlined in red. 80    |

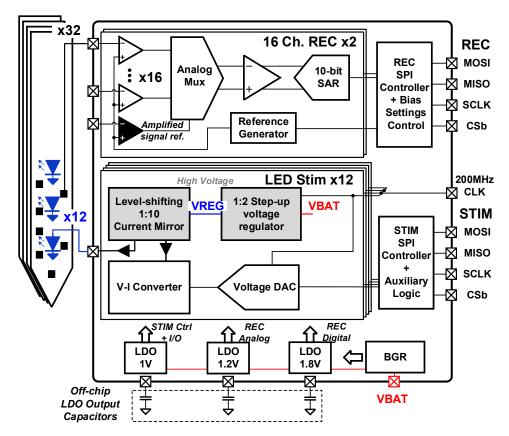

| Figure 5 | 5-7. Proposed chip architecture block diagram. Blocks in grey utilize thick-oxide             |

| 1        | transistors for high voltage operation                                                        |

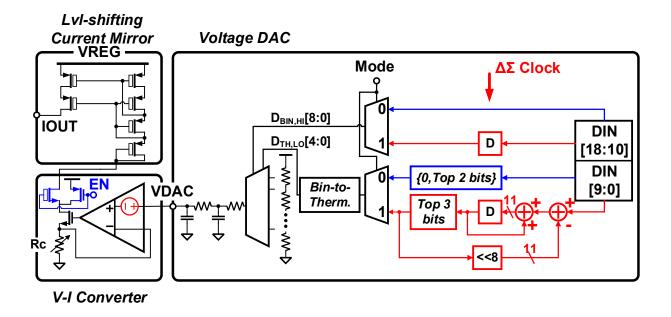

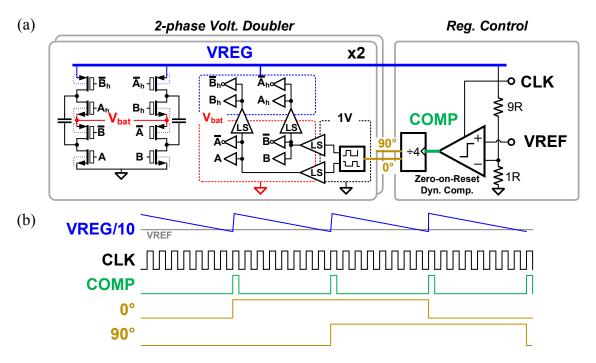

| Figure 5 | 5-8. Circuit schematics of voltage DAC, V-I converter, and the level-shifting current         |

| 1        | mirror. Regular PWM mode DAC settings are shown in blue, while PS mode DAC                    |

| \$       | settings are shown in red83                                                                   |

| Figure 5 | 5-9. Pulse-shaped pulse train current output showing the switching between PS and PWM         |

| 1        | modes. Duty-cyling between the modes in the shown example can lead to 25% reduction           |

| j        | in power consumption85                                                                        |

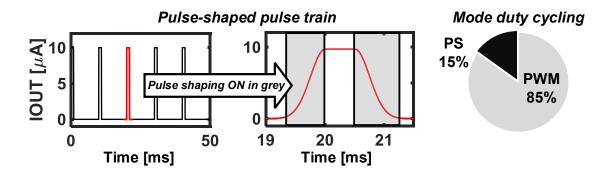

| Figure | 5-10. Circuit schematic of the V-I converter amplifier (inside the dotted line) and the V-I               |

|--------|-----------------------------------------------------------------------------------------------------------|

|        | convert transistor and resistor. Transistors in red are not symmetrical to introduce offset.              |

|        | Miller compensation capacitor and resistor is highlighted in blue                                         |

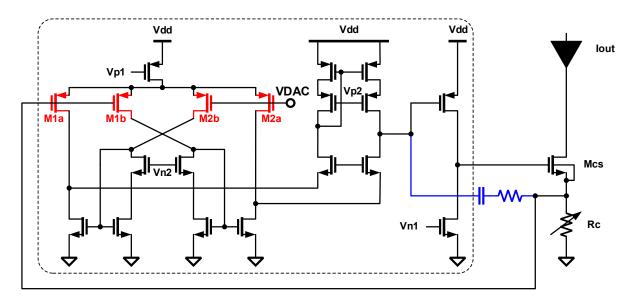

| Figure | 5-11. (a) integrated step-up voltage regulator circuit schematic and (b) control signal                   |

|        | timing diagram88                                                                                          |

| Figure | 5-12. Die photo                                                                                           |

| Figure | 5-13. Measured recording circuit input referred noise and gain output frequency spectrum.                 |

|        | 91                                                                                                        |

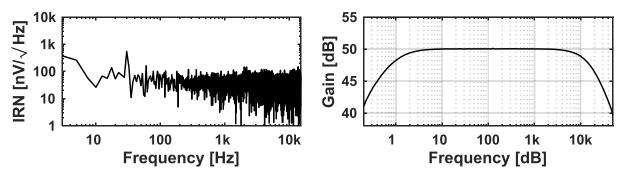

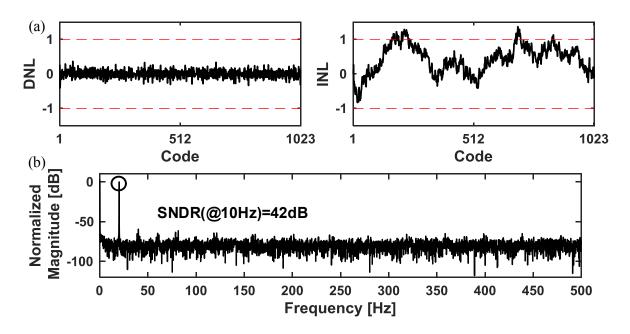

| Figure | 5-14. (a) LED Driver linearity measurements including DNL and INL; (b) normalized                         |

|        | frequency-spectrum of LED channel generated sine wave at 10 Hz                                            |

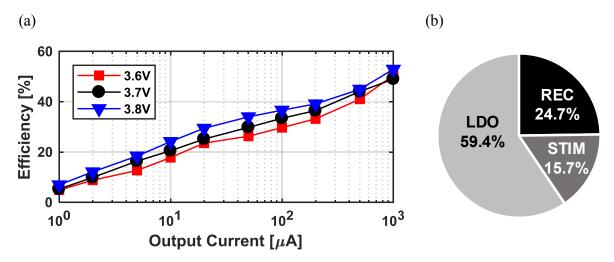

| Figure | 5-15. (a) LED driver total efficiency measured across a range of output currents and input                |

|        | voltages; (b) power consumption distribution of the interface IC when driving one $\mu \text{LED}$        |

|        | device at 100 µA and 10% duty cycle.                                                                      |

| Figure | 5-16. Current pulse shapes driven across the $\mu$ LEDs with the LED driver operating in <i>PS</i>        |

|        | <i>mode.</i> 92                                                                                           |

| Figure | 5-17. <i>In vivo</i> test setup.                                                                          |

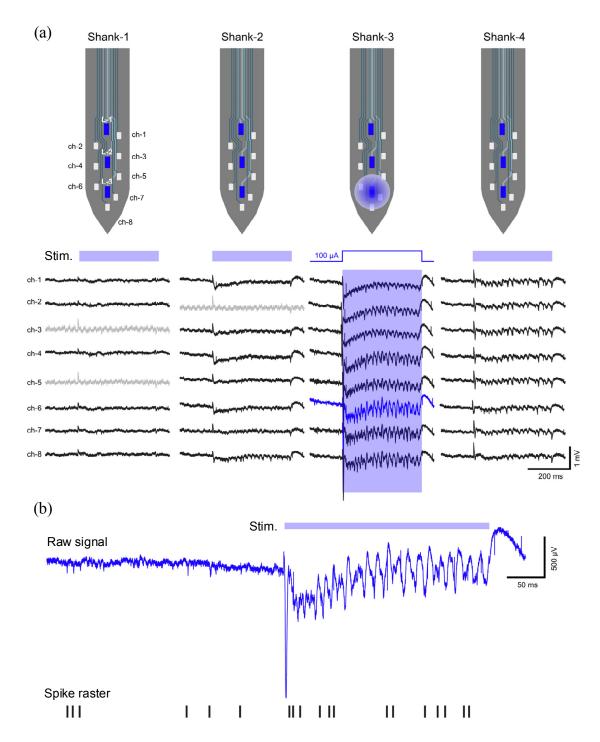

| Figure | 5-18. (a) Wideband (1-3000 Hz) spiking activity recorded on a four-shank μLED probe                       |

|        | from CA1 pyramidal layer of the hippocampus of an anesthetized mouse expressing                           |

|        | ChR2 in pyramidal cells. Light-induced artifacts are visible on all channels during                       |

|        | rectangular 100 μA-driven light pulses. Note the most prominent artifacts appear on                       |

|        | shank-3 (shank-3, LED-3 was used). Stimulation induced local field potential change and                   |

|        | spiking. Grey channels connect to broken recording sites ( $Z_{el} > 10 \text{ M}\Omega$ ). (b) High-pass |

|          | filtered signal of the blue highlighted channel. Rasters at the bottom show multi-unit            |

|----------|---------------------------------------------------------------------------------------------------|

|          | activity which is altered by light stimulation96                                                  |

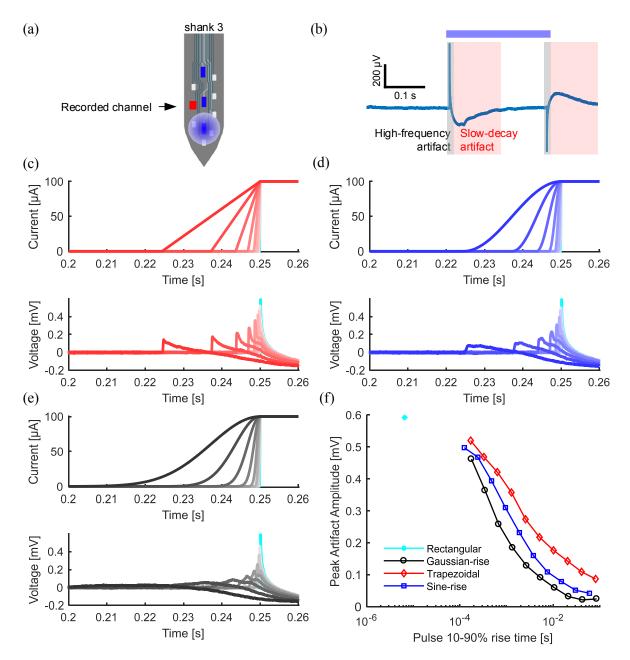

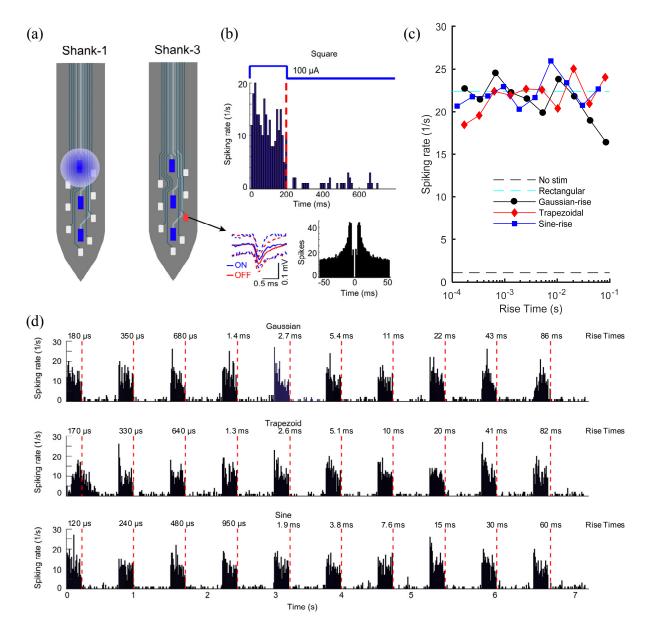

| Figure : | 5-19. (a) artifact analysis stimulation is performed on bottom μLED on shank 3 while              |

|          | recordings are taken from the ch-4 on shank 3. (b) in vivo recordings are averaged over           |

|          | each corresponding pulse-shaped stimulation period (peaking at 100 μA). Artifacts                 |

|          | appear both at light activation and deactivation. Averaged artifact waveform shows a              |

|          | high-frequency component and pulse-shape-independent slow-decay component. (c)-(e)                |

|          | show the trapezoidal, sine-rise, and Gaussian-rise current pulse shapes and the mean              |

|          | high-frequency artifacts, respectively. Rectangular pulse artifact is shown in cyan for           |

|          | comparison. Peak artifact amplitudes versus pulse rise time are shown for different pulse         |

|          | shapes in (f)97                                                                                   |

| Figure 3 | 5-20. (a) Shank schematic shows the location of stimulation (shank-1 LED-1) and the               |

|          | recording site where the modulated neuron was recorded (shank-3 channel-5). The light             |

|          | sensitive neuron on shank-3 is probably driven by another neuron close to shank-1, which          |

|          | we did not record from (the recorded neuron is 500 $\mu m$ from the $\mu LED$ ). (b) Peristimulus |

|          | time histogram (PSTH) shows strong firing rate modulation due to 100 $\mu A$ 200 ms               |

|          | rectangular pulse stimulation. Bottom inset shows identical spike waveforms during                |

|          | stimulation (100 µA, 460 nm) and control periods (blue and red, respectively).                    |

|          | Autocorrelation histogram is shown for the same neuron during light stimulation. (c)              |

|          | Mean spiking rate altered by light stimulation does not depend on the applied pulse shape         |

|          | nor its rise time (n = 56 trials). (d) Full PSTHs at different pulse shapes. Red lines mark       |

|          | the falling edge of each pulse.                                                                   |

# LIST OF TABLES

| Table 2-1 Electrophysiological Neural Signal Modalities (adapted from [92]) | 12 |

|-----------------------------------------------------------------------------|----|

| Table 3-1. Performance Summary and Comparison with Other Recent Works       | 41 |

| Table 4-1. System specifications and performance summary                    | 60 |

| Table 4-2. Comparison with Other Opto-Electrophysiology Headstage Systems   | 64 |

| Table 5-1. Optogenetic-specific ASIC system comparison table.               | 93 |

### **ABSTRACT**

Bidirectional neural interfaces are tools designed to "communicate" with the brain via recording and modulation of neuronal activity. The bidirectional interface systems have been adopted for many applications. Neuroscientists employ them to map neuronal circuits through precise stimulation and recording. Medical doctors deploy them as adaptable medical devices which control therapeutic stimulation parameters based on monitoring real-time neural activity. Brain-machine-interface (BMI) researchers use neural interfaces to bypass the nervous system and directly control neuroprosthetics or brain-computer-interface (BCI) spellers.

In bidirectional interfaces, the implantable transducers as well as the corresponding electronic circuits and systems face several challenges. A high channel count, low power consumption, and reduced system size are desirable for potential chronic deployment and wider applicability. Moreover, a neural interface designed for robust closed-loop operation requires the mitigation of stimulation artifacts which corrupt the recorded signals. This dissertation introduces several techniques targeting low power consumption, small size, and reduction of stimulation artifacts. These techniques are implemented for extracellular electrophysiological recording and two stimulation modalities: direct current stimulation for closed-loop control of seizure detection/quench and optical stimulation for optogenetic studies. While the two modalities differ in their mechanisms, hardware implementation, and applications, they share many crucial system-level challenges.

The first method aims at solving the critical issue of stimulation artifacts saturating the preamplifier in the recording front-end. To prevent saturation, a novel mixed-signal stimulation artifact cancellation circuit is devised to subtract the artifact before amplification and maintain the standard input range of a power-hungry preamplifier. Additional novel techniques have been also implemented to lower the noise and power consumption. A common average referencing (CAR) front-end circuit eliminates the cross-channel common mode noise by averaging and subtracting it in analog domain. A range-adapting SAR ADC saves additional power by eliminating unnecessary conversion cycles when the input signal is small. Measurements of an integrated circuit (IC) prototype demonstrate the attenuation of stimulation artifacts by up to 42 dB and cross-channel noise suppression by up to 39.8 dB. The power consumption per channel is maintained at 330 nW, while the area per channel is only 0.17 mm<sup>2</sup>.

The second system implements a compact headstage for closed-loop optogenetic stimulation and electrophysiological recording. This design targets a miniaturized form factor, high channel count, and high-precision stimulation control suitable for rodent in-vivo optogenetic studies. Monolithically integrated optoelectrodes (which include 12  $\mu$ LEDs for optical stimulation and 12 electrical recording sites) are combined with an off-the-shelf recording IC and a custom-designed high-precision LED driver. 32 recording and 12 stimulation channels can be individually accessed and controlled on a small headstage with dimensions of 2.16 x 2.38 x 0.35 cm and mass of 1.9 g.

A third system prototype improves the optogenetic headstage prototype by furthering system integration and improving power efficiency facilitating wireless operation. The custom application-specific integrated circuit (ASIC) combines recording and stimulation channels with a power management unit, allowing the system to be powered by an ultra-light Li-ion battery.

Additionally, the  $\mu$ LED drivers include a high-resolution arbitrary waveform generation mode for shaping of  $\mu$ LED current pulses to preemptively reduce artifacts. A prototype IC occupies 7.66 mm<sup>2</sup>, consumes 3.04 mW under typical operating conditions, and the optical pulse shaping scheme can attenuate stimulation artifacts by up to 3x with a Gaussian-rise pulse rise time under 1 ms.

## **CHAPTER 1**

# Introduction

## 1.1 Background and Motivation

Over the past century, there have been tremendous advances in our understanding of animal and human brain function. One of the greatest accelerators of this research is the rapid development of technology that measures, analyzes, and interacts with the brain and the nervous system. Moreover, neural interfacing technology not only helps satisfy the scientific curiosity, but also provides powerful clinical tools for treating widespread neurological disorders and for control of prosthetic limbs in amputees. The concept of implanting electronic microchips into a brain to correct or alter its function not long ago would have been considered a science-fiction fantasy; now it has an entire dedicated research field and industry. Commercial electronic medical devices such as Medtronics' Activa® Neurostimulator for deep brain stimulation or NeuroPace's RNS® device for epilepsy treatment have already been implanted into patients to help them cope with life-debilitating disorders.

Neural interfacing technology is concerned with two major tasks: recording from neurons and controlling, or stimulating, neurons. Neural recording is a necessary tool for most neuroscientific research as it provides concrete validation for theories ranging from synapse-level activity to large-scale biological neural circuits and networks. Neural stimulation, or neuromodulation, is used in medical devices where an artificial activation of neurons can treat or alleviate symptoms of neurological disorders. These two tasks can also be used in conjunction to

provide an even more powerful set of tools. Localized stimulation can trigger or alter a neural circuit that is simultaneously being recorded for a study. Conversely, neural recordings can help control a neuromodulation system by giving real-time feedback and automatically adjusting stimulation parameters. The direct and on-line combination of recording and stimulation is commonly referred to as closed-loop neuromodulation and has gained increasing popularity.

## 1.2 Current State-of-the-Art Neural Interfacing Systems

Engineers and scientists have been building and utilizing neural interfaces for almost a century. One of the earliest accounts of neural recording was provided by Hans Berger's discovery of electroencephalography (EEG) in 1924 [1]. Further on, the adoption of silicon-based integrated circuit technology allowed significant size reduction and improved reliability of neural interface devices. In the late 1960s, the introduction of the silicon probe enabled neuroscientists to reliably record action potentials (AP) at a micro-scale distance from the neurons [2]. The introduction of miniature low-cost neural recording amplifier ICs in early 2000s allowed the design of compact and low-power recording systems [3].

As simple unidirectional system design blocks are gaining maturity, further advancements often rely on effectively combining recording and stimulation. True integrated bidirectional neural interfaces which combine recording and stimulation circuitry within the same package (shared PCB or chip die space) have now been reported for over a decade [4]. Majority of these systems utilize electrical recording and electrical stimulation modalities. Bidirectional systems without closed-loop algorithm implementations have been built from commercial-off-the-shelf (COTS) devices [5] or custom application-specific integrated circuits (ASICs) [6], [7], [16]–[18], [8]–[15]. Further integration of bidirectional interfaces with DSP-based closed-loop algorithms has been shown with COTS devices [19]–[27] and custom ASICs [28], [29], [38], [30]–[37].

Bidirectional neural interfaces also incorporate alternative recording or stimulation modalities. In this dissertation, we will additionally focus on interfaces for optogenetics studies. In optogenetics, artificial light sources generate visible light that stimulates genetically-engineered light-sensitive neurons [39]. When combined with high resolution electrical recording, this creates a powerful tool that utilizes the advantages of the two techniques. At University of Michigan, a novel probe has been developed which monolithically integrates electrical recording sites with micro-light-emitting-diodes (μLEDs) onto a single implantable shank for multi-channel optogenetic studies [40]. Several miniaturized LED- and LD- (laser-diode) based interface system publications have also appeared in recent years. In [41]–[43], optical probes are combined with wirelessly-controlled LED/LD driver electronic backends, while [44]–[48] also added recording capability. Due to the technique's novelty, there is considerable room for improvement in terms of system size, power consumption, and number of channels, which are all focus of the proposed systems in Chapter 4 and Chapter 5.

A fundamental challenge of a bidirectional interface (especially in closed-loop operation) is the concurrent recording of high-fidelity neural signal and stimulation [49]. When a system is recording a neural response to a stimulus, unwanted stimulation artifacts directly couple onto recording channels. By corrupting the recorded signal, these artifacts negatively impact data processing and proper functionality of closed-loop algorithms which rely on detecting features from the recorded signals. Despite the substantial research accomplished to prevent or mitigate the effects of stimulation artifacts, there is no consensus on the most robust technique that does not sacrifice basic system constraints. Current state-of-the-art artifact cancelation or mitigation techniques can be subdivided into analog front-end techniques which prevent channel saturation and digital back-end algorithms which subtract artifacts if they are within the input range. The

former include quick-recovery amplifiers with a reset control input [6], [10], [15], [17]–[19], [23], [29], [35], [38], signal-blanking systems which disconnect input during stimulation [20], [24], [36], [50], or symmetrically-implanted electrodes for common mode artifact rejection [28]. The digital back-end techniques include filtering and template subtraction algorithms [26], [32], [51]–[58]. This work introduces two novel artifact cancellation and prevention schemes for low-power IC integration: a mixed-signal cancellation approach for electrical stimulation in Chapter 3, and an optical stimulus pulse-shaping approach for optical stimulation in Chapter 5.

#### 1.3 Outline

The rest of the thesis is organized as follows. Chapter 2 provides basic neuroscience and neurotechnology background. Chapter 3 describes a bidirectional electrical neural interface IC architecture with stimulation artifact rejection circuit and additional noise and power reduction schemes. Chapter 4 introduces a new opto-electrophysiology system that combines the Michigan optoelectrode with custom and off-the-shelf application-specific integrated circuits (ASICs) yielding a highest-channel-count miniature headstage. Chapter 5 introduces a new custom ASIC which combines LED driving and electrical recording capabilities with a power management unit (PMU) and a new optical-artifact preventive technique based on optical pulse shaping. Finally, contributions and future research directions are discussed in Chapter 6.

## **CHAPTER 2**

# **Neuroscience and Neurotechnology Background**

#### 2.1 Introduction to Neuroscience<sup>1</sup>

While weighing only 1.5 kg, the brain is an immensely complex computing machine which controls most human functions, behaviors, and thought processes. The basic unit of the brain is a neuron cell (shown in Figure 2-1) which performs computations inside of its center, or *soma*, based on the electrochemical inputs to the cell at the *dendrites*. The neuron carries a signal through the physical space in an elongated part, called the *axon*, and delivers the output to other neurons through micro-scale connections called *synapses*. The signaling modality of the neuron is a spike or *action potential* (AP) in the cellular membrane voltage potential. An AP is formed by the fluctuating ionic concentrations inside and outside of the cell caused by electrochemical forces. The movement of these ions is governed by ion channels or *gates* embedded in neural walls which react to changes in potential. A change in membrane potential activates neighboring gates that in themselves increase its surrounding potential. This creates a "chain reaction" of activated gates and changing potentials that travels down the neuron as an action potential. It is this process that can be triggered or inhibited through therapeutic neuromodulation techniques. The APs can be externally and artificially triggered through depolarization, or by significantly changing cell

<sup>&</sup>lt;sup>1</sup> Information in Section Chapter 2 is excerpted from a textbook "Principles of Neural Science" by E. Kandel, T. Jessel, and J. Schwartz. [124]

Figure 2-1. Simplified neuron diagram. (Source: https://askabiologist.asu.edu/neuron-anatomy)

potential, either with current or voltage stimulation, or through modification of ion channels to react to other stimuli such as light (optogenetics).

While the discovery of neuron cell activity is still one of the major breakthroughs of modern science, the mapping of high-level neuronal circuits has become an even greater challenge. After all, there are over 80 billion nerve cells in an average human brain with over 1000 connections (synapses) per each neuron [59]. Neuron cells communicate with one another through APs and create larger neural circuits which control specific functions, all the way from basic motor skills to forming memories and abstract concepts. Moreover, many common neurological disorders arise from malfunctions of these circuits. A reduced level of dopamine neurotransmitters which are responsible for connections between neurons is generally considered as the cause of Parkinson's Disease (PD). Excessive synchronization of neuron firings is often correlated with epileptic seizures. Active monitoring of these circuits and targeted external modulation through electronic hardware has already been introduced in clinical fields with a relatively high degree of success

[60], [61]. The potential for impact is high: PD in 2015 has affected about 6.2 million people globally, while epilepsy has affected more than 39 million [62].

We must not forget that the nervous system is not just constrained to the brain, but it covers almost every part of the human body. The spinal cord provides an information highway between the brain and major organs and limbs, as well as it performs some low-level control. The nervous system extends to most organs, controlling their functionality, either consciously, such as in muscles, or subconsciously, such as in the digestive system. This subset of the nervous system is called the peripheral nervous system (PNS). There is substantial research in mapping and understanding of PNS, as it is also often easier to access than the brain itself.

#### 2.2 Neuromodulation and Closed-loop Control

#### 2.2.1 Neuromodulation

As defined in [63], neuromodulation is any technology that interfaces with and affects the nervous system. Processes related to neuromodulation include stimulation, inhibition, modification, or regulation in the central or peripheral nervous systems. While most of the technological advances in neuromodulation began taking place in latter half of the 20<sup>th</sup> century, one of the earliest accounts of "neuromodulation therapy" dates to 15 AD. According to a reported story, a freed slave of Roman Emperor Tiberius was suffering from chronic pain until he had accidentally stepped on an electric torpedo fish and experienced an electric shock; afterwards, he claimed that the pain has substantially decreased. Unfortunately, it took almost 2 millennia for our society to grasp the underlying mechanism of this unlikely cure.

#### Neurostimulation addressable population (000's patients)

Figure 2-2. Disorders and estimated population in USA affected by disorders which can be treated by neurostimulation. [63]

Neuromodulation is most often associated with therapeutic devices, and quite understandably, most research focuses on such applications. Neuromodulation devices are being introduced or are already utilized for a wide range of neurological disorders, ranging from epilepsy and PD to obesity and erectile dysfunction (see Figure 2-2). A two-year study of a responsive neurostimulation system (NeuroPace) observed an average seizure reduction of 50% in 191 epilepsy patients [61]. Likewise, Deep Brain Stimulation (DBS), a popular neurostimulation technique for treatment of various neurological diseases, has improved the quality of life for many patients worldwide [64]. An estimated 14 million people in United States alone may benefit from neurostimulation devices. However, neuromodulation may also be used for other purposes. It is already a common basic science tool allowing triggering of neuronal circuits under test, often through electrical or optogenetic means [65]. Neural interface has also become the talk of the start-

Figure 2-3. Diagram comparing open-loop (in red) and closed-loop (in black) neuromodulation approach. [28]

up world as entrepreneurs, scientists, and engineers have recently founded companies aiming at improving and enhancing the human brain functions through implantable hardware [66], [67].

#### 2.2.2 Closed-loop Modulation

The process of implanting and controlling neuromodulation devices is most often an open-loop task. The surgeon inserts the stimulating device into the tissue and fine-tunes the parameters of stimulation to provide the desired effect. A patient who undergoes such treatment has to report back to the clinic on a regular basis to change the stimulation settings in order to adapt to his or her changing symptoms. The only feedback in this system – as shown in red in Figure 2-3 – is the physician making an acute observation and selecting proper stimulation parameters. An obvious way to improve the procedure is to introduce an automated control of the neuromodulation device – this would minimize patients' need for medical supervision and hospital visits. In an automated

system, a closed-loop neural interface controls current stimulation to a brain region by monitoring the recorded neural signal from the neighboring neural tissue and adjusting stimulation parameters in a feedback fashion (as shown in black in Figure 2-3). Closed-loop operation may not only alleviate the problems of more established experimental techniques but also enable new experiment techniques in basic science [68], [69]. Quick and precise feedback can be used to guide perturbations of neural systems, generating and confirming circuit-based models of underlying neuronal networks. In chronic applications such as neuroprosthetics control, closed-loop feedback can adapt stimulation to changing neural dynamics caused by brain's neuroplasticity, relieving the need for periodic manual parameter updates. This philosophy has been shown in studies [70], [71] and has been carefully introduced to a number of neuromodulation devices such as [28] and [61].

#### 2.3 Neural Interface Modalities

In this section, different neural recording and stimulation techniques will be reviewed, with extra emphasis on the ones implemented in this work. First subsection describes the different neural recording modalities and analyze the signal properties of electrical neural recording. The second subsection overviews various neural stimulation modalities, in particular, electrical stimulation and optogenetic stimulation.

#### 2.3.1 Neural Recording

Neural recording can be categorized into 4 general modalities, as shown in Figure 2-4 [72]. (1) Electrical recording probes measure changes in voltage around (or inside) neuronal cells. (2) In optical recording, a microscope is used to detect light emission from neural activity chemical indicators (such as fluorescent indicators). (3) Magnetic resonance imaging (MRI) can detect neural activity through measuring magnetic changes of various agents inside the brain. (4) In molecular recording devices, a record of neural activity is stored in a biomolecular polymer.

Figure 2-4. Four major neural signal recording modalities: (A) electrical recording, (B) optical recording, (C) MRI recording, and (D) molecular recording. [72]

Each modality has its advantages and disadvantages, and can be differentiated by 3 major quantitative parameters: the number of neurons monitored, the spatial resolution, and temporal resolution. Multi-electrode arrays can record > 1000 neurons with single neuron resolution and sub-millisecond temporal resolution. Optical recording can currently monitor ~100,000 neurons at a 1s temporal resolution. MRI is able to non-invasively scan the entire brain at 1s scale but does not have a single neuron spatial resolution. In following chapters, only electrical recording is considered in the proposed devices as it is most widespread and easily implantable with microfabrication technologies, and we will thus refer to it as simply "recording."

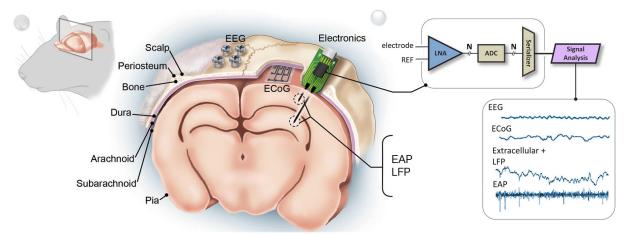

Figure 2-5. Illustration of various electrophysiological neural recording technologies implanted in a mouse brain. Adapted from [125].

Table 2-1 Electrophysiological Neural Signal Modalities (adapted from [92])

| Signal Type   | EEG         | ECoG                         | LFP                       | AP                        |

|---------------|-------------|------------------------------|---------------------------|---------------------------|

| Bandwidth     | 0.5-50Hz    | 1-500Hz                      | 1-500Hz                   | 250Hz-10kHz               |

| Amplitude     | 1-50μ       | 1-500μ                       | 10μ-5mV                   | 10μ-1mV                   |

| Spacing       | 3cm         | 0.2-10mm                     | 0.1-1mm                   | 0.1-1mm                   |

| Invasive      | No          | Craniotomy, no neural damage | Craniotomy, neural damage | Craniotomy, neural damage |

| Area Coverage | Whole Brain | ~ cm2,<br>whole brain        | ~ mm2                     | ~ mm2                     |

| Stability     | Decades     | Decades                      | Years                     | Months                    |

We can further classify electrical recording in terms of recording site location and signal characteristics. Figure 2-5 illustrates the placement of the various electrophysiological recording technologies in a mouse brain cross-section. Electroencephalogram (EEG) signals contain information from a large cortical area and are sensed through non-invasive electrodes placed on a scalp. Unfortunately, due to distance between the neural signal sources and the scalp as well as the large attenuation inside the bone skull, the signal is level is very low (below 50  $\mu$ V) and high temporal and spatial resolution is lost. Most EEG systems cover the entire brain and can theoretically (using dry electrode setup) maintain its signal fidelity over a very long time.

Electrocorticography (ECoG) retains more temporal and spatial content, as well as higher signal amplitude. It can be recorder from large electrodes (but smaller than EEG electrodes) implanted at the surface of the brain, but underneath the skull. This modality is popular for many human-use biomedical devices since the neural tissue is not directly damaged during the implantation process. It also provides good area coverage when using large grid arrays and may provide stable recording for many years. Intracortical implants are the most invasive technology because they are inserted directly into the neural tissue, displacing a portion of neural tissue in the process. However, they do provide the most precise neural information and are the only well-proven technique of capturing single-neuron information. Intracortical electrodes detect 2 kinds of signals, local field potentials (LFPs) and extracellular action potentials (EAPs). EAPs give a direct insight into neural activity and are therefore the most important modality for basic science research. Spikes require large recording bandwidth (up to 10kHz) and dynamic range (up to 1mV). LFPs are slow local potential fluctuations which form as a result of aggregate neural activity. They can be recorded with the same intracortical probes but capture a larger area of neural activity, albeit at lower time and spatial resolution.

Systems implemented in this thesis will focus on ECoG, LFP, and EAP recordings. In Chapter 3, the bidirectional interface implements ECoG recording channels since they are commonly used in epilepsy and Parkinson's suppression devices. The optogenetics systems described in Chapter 4 and Chapter 5 are designed as basic science research tools and implement intracortical LFP and EAP recording front-ends.

#### 2.3.2 Neural Stimulation

Like neural recording, neural stimulation can be implemented through a variety of techniques and modalities. In this thesis, we will focus on two stimulation techniques: electrical

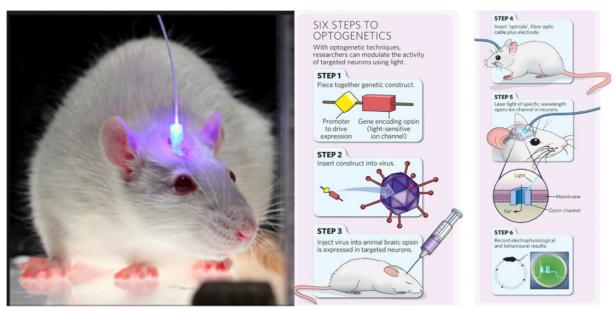

Figure 2-6. Pictorial explanation of the optogenetics technique. [126]

and optical stimulation. The two methods are popular in the neuroscientific community as they demonstrate high spatial and temporal resolution.

Electrical stimulation provides the most direct method for activating neurons inside neural tissue [73]. An electrical stimulator injects current into the tissue, creating an electric field gradient between the stimulating site and the ground. If the voltage potential around a neuron increases above a certain threshold, the neuron will depolarize and it will fire an action potential.

Optogenetics has become a popular and powerful tool for neuroscience research since its introduction in 2005 [39]. The technique utilizes advances in genetic engineering and optics to provide superior resolution and specificity. Shown in Figure 2-6, it involves genetically modifying specific types of neurons to express light-sensitive ion channels, called opsins, on their membranes. The light-sensitive ion channels then provide means to selectively excite or silence neurons with light at specific wavelengths. Neural activity can thus be precisely modulated by controlling the light output from the sources in neurons' vicinity. Optical stimulation offers several

advantages over electrical stimulation: cell type specificity, multi-modality, and greatly reduced stimulation artifact. Only the neurons of the specific types that express opsins can be stimulated with light. Cells can be either activated or silenced by light of specific wavelength based on the type of opsin expressed. Finally, light stimulation produces little or no artifact in the recorded signal since it does not directly inject current into the tissue. These advantages combined make optical stimulation an exceptional choice for stimulation in neuroscience experiments.

# **CHAPTER 3**

# Bidirectional Neural Interface IC with Active Stimulation Artifact Rejection

#### 3.1 Introduction

Continuous brain monitoring during stimulation presents a challenge due to large artifacts which appear alongside the neural signal. These artifacts distort useful information in the recorded signal and can disrupt closed-loop system operation. Many published works have attempted to mitigate this problem in a variety of ways, especially in pure electrical stimulation and recording systems where these artifacts are substantially larger than the recorded signal itself. In this chapter, we will present a novel neural interface circuit architecture and an IC prototype incorporating signal conditioning front-end features to reduce aforementioned artifacts without a substantial sacrifice in system performance [74]. The mixed-signal adaptive approach removes the artifacts at the front-end of the recording channels in order to prevent preamplifier saturation. The chapter will also introduce additional system features to increase signal fidelity and lower the power consumption. A noise removal technique called Common Average Referencing (CAR), implemented at the front-end, removes cross-channel common-mode noise and improves channel SNR. In addition, a new Range-Adapting (RA) SAR ADC architecture provides a more power efficient digitization of the neural signal.

The chapter is subdivided in the following format: Section 3.2 discusses the prior art of artifact prevention and removal and provides the theoretical background for the proposed

stimulation artifact cancellation algorithm. Section 3.3 analyzes the sources of common mode noise and introduces the CAR algorithm. Section 3.4 describes the circuit implementation of the new architectural elements as well as the new RA SAR ADC. Sections 3.5 and 3.6 show recording channel characterization and *in-vivo* measurements respectively. Finally, conclusions are drawn in Section 3.7.

# 3.2 Theory of Stimulation Artifact Cancellation

# 3.2.1 Artifact Coupling

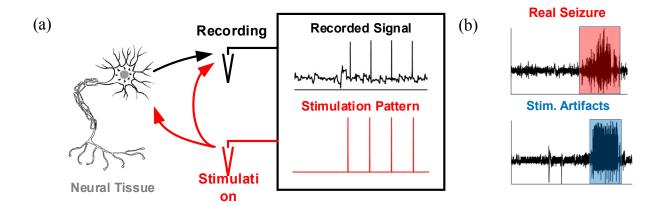

Proper operation of a closed-loop neural interface microsystem requires simultaneous recording and stimulation. In practice, continuous monitoring during stimulation presents a challenge due to large saturating artifacts appearing with the signal. Stimulation artifacts inherently form at the recording interface during concurrent sensing and stimulation. Figure 3-1 (a) depicts simultaneous stimulation and recording and shows the corrupted recorded signal. We expect a stimulation-injected current to travel to a nearby neuron to affect its state by either triggering or inhibiting its spiking activity, while the recording probe monitors the neuron's activity throughout this process. Unfortunately, due to proximity of the recording and stimulation probes, a fraction of the stimulation current bypasses the neural tissue and directly couples onto the recording probe. Because the direct path is short and the stimulus current is usually larger than the neural extracellular ionic currents, the resulting stimulation artifact dominates the recorded signal. This leads to two problems. First, the large artifact current can saturate the sensitive preamplifier, causing signal loss and lowering the biomarker detection rate. An increased dynamic range might mitigate this problem but at the cost of high power consumption. Second, even if the artifacts do not saturate the amplifier, they might be mistaken for the biomarkers themselves, as it is shown in Figure 3-1 (b), leading to a high false biomarker detection rate.

Figure 3-1. (a) Diagram showing formation and addition of stimulation artifacts in the recorded signal, and (b) comparison of similar characteristics of a seizure and stimulation artifact signal.

#### 3.2.2 Prior Art

Many closed-loop systems that suffer from large artifacts do implement some sort of artifact cancellation. This can be done in various ways, and it usually depends on the application and system constraints. Let us first assume a number of constraints before we continue with analysis. The ultimate system that we would like to implement is wireless, therefore we want to minimize power consumption and area. The location of the artifact removal module within the system will have significant impact on these parameters.

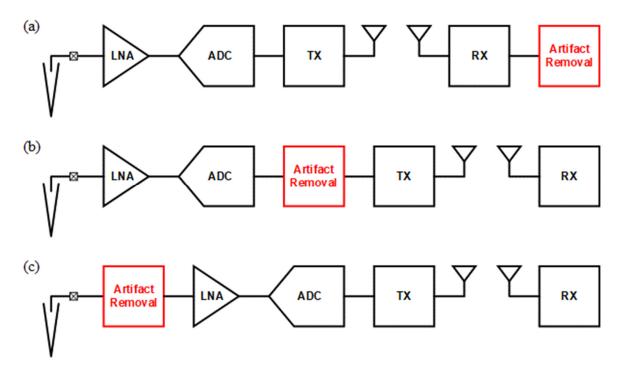

As shown in Figure 3-2, we can generalize the placement into 3 different types. In a), the artifact removal takes place at the very back-end of the system. It can be implemented in software and computed at the processor level, or in a dedicated DSP engine that handles the computational load before being fed into a closed-loop controller. This approach has been used in [51]–[53], [55], [56], [58]. The advantages of this approach are complete reconfigurability and access to virtually limitless resources. However, due to our assumption of the large dynamic range consumed by the artifact, the entire analog-front-end (AFE) in the wireless module has to consume more power to accommodate an extra 30dB of dynamic range [75]. Second, the transceiver will need to accommodate higher bandwidth (BW) and thus also consume more power. In the second approach,

Figure 3-2. System-level approaches to artifact removal.

published in [32], the artifact removal algorithm is placed directly after the analog-to-digital converter (ADC). In this approach, the wireless module does not have to consume extra BW to accommodate the artifacts. In fact, this approach will also allow a full implementation of the closed-loop algorithm module within the node. Unfortunately, the power-hungry front-end module still needs to properly digitize the full signal with artifacts. This leaves us with the option of placing artifact removal before the initial amplification, as shown in Figure 3-2 (c). A proper implementation in the analog domain can greatly relax the constraints of the analog front-end amplification and analog-to-digital conversion.

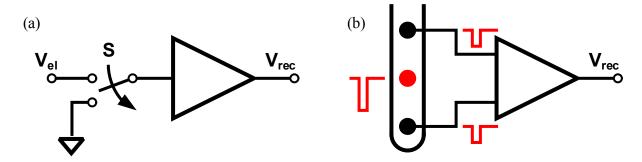

Previous approaches to front-end artifact cancellation include signal blanking and symmetric sensing. In signal blanking, the input to the recording amplifier is simply turned off during stimulation [76], as shown in Figure 3-3 (a). While this prevents the amplifier from saturating and temporarily losing its input voltage bias, any signal appearing during the off-period is lost. In symmetric sensing (Figure 3-3 (b)), the recording and stimulation electrodes are placed

Figure 3-3. Previous front-end artifact rejection methods: (a) signal blanking and (b) symmetric sensing.

in a particular configuration to differentially cancel the artifact [77]. Here, the stimulation site is placed equidistantly between two differential recording sites so that the artifact equally couples onto each recording channel is rejected by the differential amplifier. While the neural signal is preserved in this scheme, it requires an inflexible electrode configuration that possibly hinders the effectiveness of the stimulation. Instead, we propose a universal architecture for artifact cancellation, which can be used in a wide variety of applications while preserving the recorded neural signal and avoiding the shortcomings of previous works.

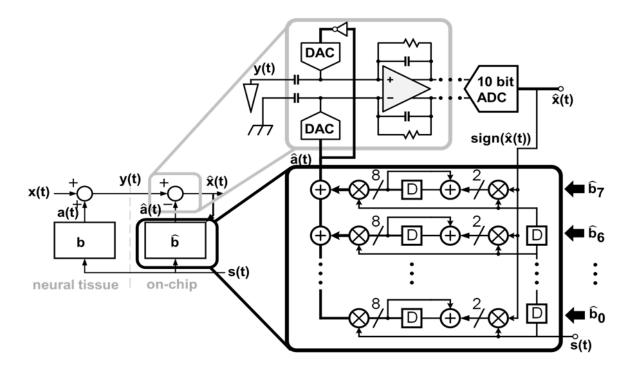

## 3.2.3 Artifact Cancellation Algorithm

Our approach to artifact cancellation circuit stems from the similarity in coupling between stimulating and recording probes of a closed-loop stimulation microsystem to the near-end crosstalk (NEXT) problem in wireline communication systems. In NEXT, a strong transmitter output couples to the input of the sensitive receiver amplifier and corrupts the received signal, increasing the system's bit-error rate [78][79]. However, by utilizing the direct correlation between the transmitted signal and the observed artifact, a number of filtering techniques have been developed to cancel the artifacts. One such technique, called *adaptive noise cancellation*, learns the filtered crosstalk noise response of the channel and subtracts it from the recorded signal [80].

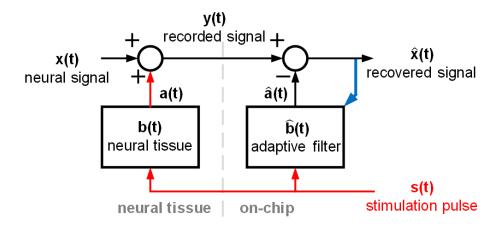

Figure 3-4. System diagram of stimulation artifact addition and cancellation through adaptive filtering. The recorded signal, y(t), is the corrupted neural signal picked up at the tissue-circuit interface, while the recovered signal,  $\hat{x}(t)$ , is the on-chip recovered neural signal.

Due to its simplicity and general applicability, we apply a similar approach to cancel neural stimulation artifacts in an implantable neural interface [81].

Analysis of the algorithm begins with the simplification of neural tissue response to a linear, time-invariant (LTI) filter. The recorded signal, y(t), can be expressed as a linear sum of the neural signal x(t) and the artifact, a(t), as shown in Figure 3-4. Furthermore, the artifact a(t) can be expressed as a stimulation signal s(t) filtered by the neural tissue response b(t):

$$y(t) = x(t) + a(t)$$

=  $x(t) + b(t) * s(t)$ . 3-1

Adaptive noise cancellation artificially recreates the response of the neural tissue in order to subtract it from the corrupted signal. To perform this task, an adaptive filter,  $\hat{b}(t)$  (in Figure 3-4), learns the impulse response of the neural tissue. When stimulation s(t) is fed through this filter, its output recreates the artifact  $\hat{a}(t)$  and this recreated artifact is subtracted from the recorded signal to cancel the real artifact as shown in following equation:

$$\hat{x}(t) = x(t) + a(t) - \hat{a}(t) = x(t) + b(t) * s(t) - \hat{b}(t) * s(t).$$

3-2

Figure 3-5. Simulation of the stimulation artifact cancellation algorithm with artificial neural data showing the system learning the response of the tissue.

By inspection of the equation above, when the fully-trained filter  $\hat{b}(t)$  approximates the neural response b(t), the stimulation term s(t) is cancelled, and the recovered output signal  $\hat{x}(t)$  approximately equals the original neural signal x(t).

A key block in adaptive noise cancellation is the learning algorithm of the adaptive filter. The Least Mean Squares (LMS) learning algorithm, first presented by Widrow, et al. and extensively used in telecommunications, is simple and reliable [82]. In LMS, the adaptive filter coefficients are updated every cycle to better approximate the desired response. The update quantity is derived by applying the steepest gradient descent approach to minimize power of the

<sup>&</sup>lt;sup>2</sup> It is important to note that while the actual non-artifact neural response is also correlated to the stimulation signal, it is much delayed and not LTI; if the filter length is kept short enough, the real neural signal is not cancelled. The neural signal will thus be omitted in further explanation.

Figure 3-6. The final impulse response of the adaptive filter after training resembles the artifact waveform.

noise error,  $\hat{x}(t)$ . As shown in [81], the online LMS algorithm predicts the coefficient update, needing only the value of the recovered output signal  $\hat{x}(t)$  from the previous cycle and the stimulation input s(t) as shown:

$$\hat{b}(t+1) = \hat{b}(t) + \mu s(t)\hat{x}^*(t).$$

3-3

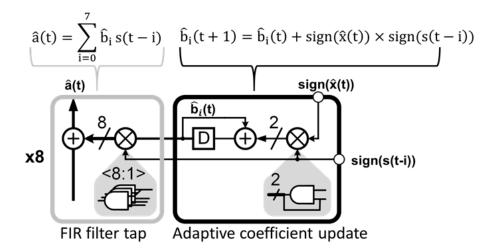

The adaptation constant μ is an adjustable knob for the user to trade adaptation speed for accuracy. A simplified version, called sign-sign LMS, eases the hardware requirements by performing computation on a sign-bit signal representation, resulting in the following update equation [83]:

$$\hat{\mathbf{b}}(t+1) = \hat{\mathbf{b}}(t) + \mu \left( \mathbf{s}(t) \times \operatorname{sign}(\hat{\mathbf{x}}(t)) \right).$$

3-4

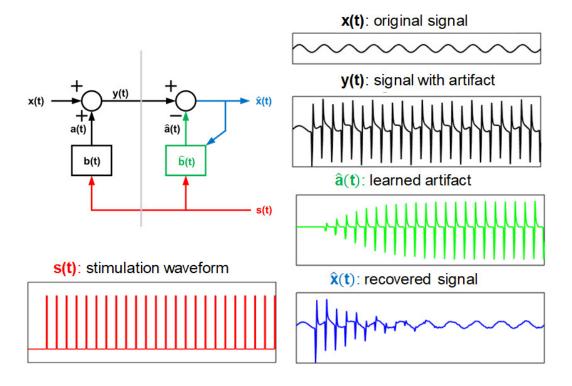

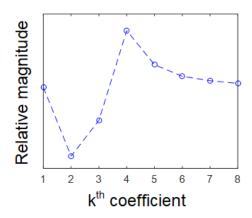

To show the effectiveness of the scheme, the algorithm is simulated with pre-recorded neural data, as shown in Figure 3-5. We artificially corrupt a known signal (here, a sinusoidal wave for clarity) with pre-recorded artifact waveforms, added at predetermined times that are correlated to the stimulation waveform. As the algorithm runs for a few stimulation cycles, the filter output begins to resemble the added artifacts. In fact, the plotted impulse response of the adaptive filter at the end of simulation in Figure 3-6 resembles a single added artifact, since the filtered artifact waveform is simply a pulse train convolved with a single 8 sample long artifact-shaped sequence. Furthermore, the recovered signal shows a decrease in correlated cross talk noise without

Figure 3-7 Top-level diagram of common average referencing (CAR) algorithm.

significant distortion of the original uncorrelated signal.

The selection of the adaptive filter length was guided by maximizing the subtraction of artifact without removing the desired evoked neural potential. An analysis of typical electrocorticograph (ECoG) and local field potential (LFP) signals showed a 2 ms period between the stimulation pulse and earliest neural response, and during this time period the artifact can be safely removed. Because the filter is sampled at the ADC frequency of 4 kHz, an 8-tap filter is sufficient to attenuate most artifacts while preserving the non-artifact neural response.

## 3.3 Common Mode Noise Rejection

As studied in [84], various environmental noise sources such as power lines and fluorescent lights capacitively couple onto the electrodes, the electrode wires, and the preamplifier inputs, potentially causing large amplitude common-mode noise. This noise can be cancelled through differential recording, where noise in two neighboring channels is rejected as common mode signal. Inconveniently, differential recording requires the user to double the number of electrodes and may also remove important signals shared between the channels. As a compromise, a large single reference electrode is often used to subtract the reference noise from multiple channels without introducing localized neural signals. Unfortunately, because of the impedance mismatch

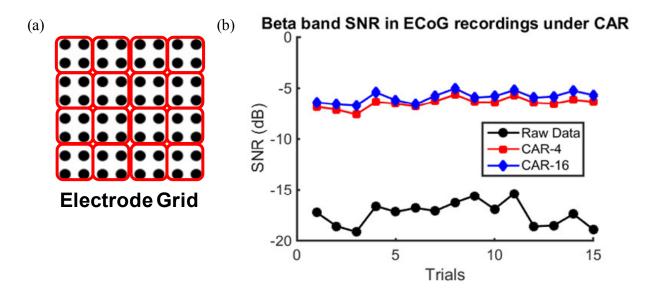

Figure 3-8. (a) CAR-4 4-channel groupings mapped onto an ECoG electrode grid, and (b) comparison in SNR of ECoG recordings between raw data, active CAR-4, and active CAR-16 algorithms.

between the recording and reference electrodes, line noise couples differently to the positive and negative inputs.

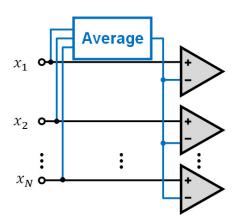

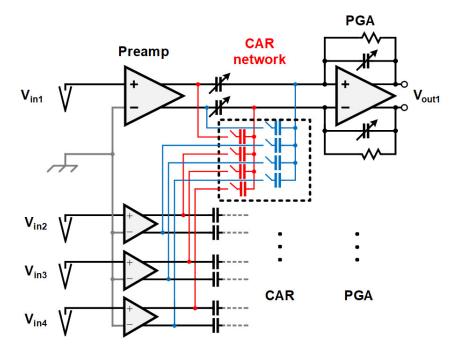

Instead of relying on a single electrode to provide an accurate reference signal, we can create a new reference signal from the existing channels. [85] creates this new reference signal in a software post-processing scheme called Common Average Referencing (CAR). CAR has become a common step in signal conditioning in neuroscientific literature [86][87]. As shown in Figure 3-6, the new reference signal is computed by averaging neighboring channels and subtracting this average from every channel. If used properly, the average holds most of the common mode noise and little of neural signal, thus providing a clean, stable reference signal.

While it has been previously implemented as a software post-processing step, we implement CAR at the recording front-end. By cancelling the noise before final amplification and digitization, the dynamic range constraints of the analog circuitry can be greatly relaxed. Challenges include unintended signal cancelation if the CM signal itself is of importance – this can be alleviated by

Figure 3-9. Top-level system architecture.

averaging enough channels so that the average contains a minimal amount of localized neural signal. Analysis of experimental neural data (Figure 3-8) shows that even a 4-channel CAR (CAR-4) can substantially improve SNR, while the use of 16-channel CAR (CAR-16) only slightly further increases SNR. This relatively small number of needed channels allows us to minimize the circuit area for CAR as described in section IV.B. The common average reference can also be contaminated by a single very strong, or perhaps broken, channel. For this reason, the user should be able to eliminate that channel from the average calculation so that the noise does not bleed into other channels.

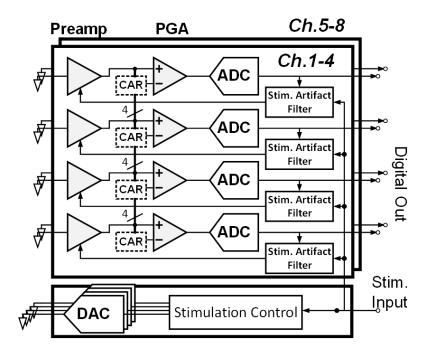

# 3.4 Circuit Implementation

The proposed system architecture, shown in Figure 3-9, consists of 8 recording channels and 4 stimulation channels. Each recording channel consists of a preamplifier with a gain of 100, a programmable gain amplifier (PGA) with gain ranging from 1 to 10, and an ADC. The bandwidth of the preamplifiers is deliberately limited to a range of 1Hz to 2kHz to pass electrocorticograph

Figure 3-10. Schematic of stimulation artifact cancellation circuit. Analog subtraction is framed in gray while the adaptive filter is framed in black.

(ECoG) and local field potiental (LFP) signals, which are most commonly used for neuromodulation control. The sampling rate of the ADC is set at 4 kS/s to properly sample the neural signals without aliasing. The resolution of the ADC is set to 10 bits to maintain the channel input-referred noise below 5  $\mu$ V<sub>rms</sub> (i.e. below the biological noise limit) while providing the ADC differential input dynamic range of 1V. The recording channels are split into two groups of 4 channels. In each group, every channel can be referenced to an average formed from any combination of these channels. The CAR circuit is placed after the preamplifier and before the PGA to remove the noise before final amplification and digitization. A stimulation artifact cancellation filter is implemented for every individual channel, as we cannot expect a similar coupled stimulation artifact for each channel. The stimulation data input is fed into the stimulation control block and also to the bank of stimulation artifact cancellation filters. Lastly, the stimulation channels themselves consist of current DACs and digital timing and control circuitry. The current

DAC resolution of 7 bits and dynamic range up to 8 mA are enough for most neuromodulation applications.

#### 3.4.1 Stimulation Artifact Cancellation Circuit

The stimulation artifact cancellation scheme is implemented with the mixed-signal circuit shown in Figure 3-10. First, the single-bit stimulation input s(t) is fed through the digital adaptive filter. The filter output, or the digitally recreated artifact  $\hat{a}(t)$ , is converted into a differential analog signal using two digital-to-analog converters (DACs). This analog artifact replica is then subtracted from the corrupted neural signal at the preamplifier input to prevent signal saturation in the channel. Finally, the sign of digitized recovered signal,  $\hat{x}(t)$ , (from the 10-bit ADC) and single-bit stimulation signal, s(t), are fed to the adaptive filter to train its coefficients.