## Charge-Domain Analog/Mixed-Signal Circuits and Applications

by

# Kyojin Choo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical & Computer Engineering) in the University of Michigan 2018

## **Doctoral Committee:**

Professor David Blaauw, Chair Associate Professor Nakhiah Goulbourne Assistant Professor Hunseok Kim Professor Dennis Sylvester

# Kyojin Choo

kjchoo@umich.edu

ORCID iD: 0000-0001-8119-094X

© Kyojin Choo 2018

# TABLE OF CONTENTS

| List of Figures                                                                            | iii |

|--------------------------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                                             | vi  |

| Chapter 1. Introduction                                                                    | 1   |

| Chapter 2. Charge-injection technique                                                      | 11  |

| Charge-injection cell·····                                                                 | 11  |

| Jitter Rejection Property                                                                  | 13  |

| Noise Characteristics from Reuse                                                           | 14  |

| Noise Sources and Analysis                                                                 | 16  |

| Mismatch and Calibration                                                                   | 25  |

| Output Impedance and Cascoded Charge-Injection Cell                                        | 28  |

| Charge-injection DAC and SAR ADC ······                                                    |     |

| Improvement in Information-Rate Density (IRD)                                              | 38  |

| Improvement in Linearity                                                                   | 43  |

| CHAPTER 3. LOW-POWER IMAGE SENSOR USING CHARGE-INJECTION SAR ADC                           | 46  |

| Capacitor-array Assisted Charge-Injection Cell-Based SAR ADC                               | 48  |

| Cascoded Charge-Injection Cell With Dummy Path · · · · · · · · · · · · · · · · · · ·       | 49  |

| ADC Row Conversion Sequence····                                                            | 53  |

| c-ciDAC Noise Contribution · · · · · · · · · · · · · · · · · · ·                           | 56  |

| Energy Efficiency Improvement Using High-Gain Capacitive Summation Path                    | 57  |

| Noise Reduction Using Multiple Sampling                                                    | 59  |

| Calibration Capacitor Bank and Calibration Operation · · · · · · · · · · · · · · · · · · · | 61  |

| Per-Column SAR Logic Circuit · · · · · · · · · · · · · · · · · · ·                         | 66  |

| Motion Detection Mode · · · · · · · · · · · · · · · · · · ·                                | 67  |

| Result                                                                                     | 71  |

| CHAPTER 4. ENERGY EFFICIENT CHARGE-DOMAIN PRE-AMPLIFIER WITH < 1 DISCRETE                  |     |

| TIME EQUIVALENT NEF                                                                        | 75  |

| CHAPTER 5 CONCLUSION AND FUTURE WORK                                                       | 85  |

# LIST OF FIGURES

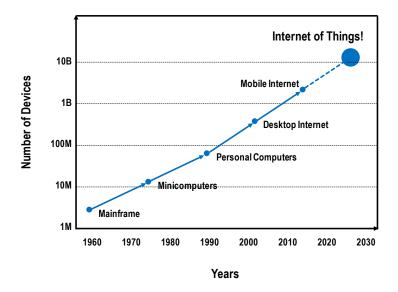

| Figure 1. Main drivers in the trend of technological evolution. IoT is projected to add tens of billions of devices during the next decade.                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

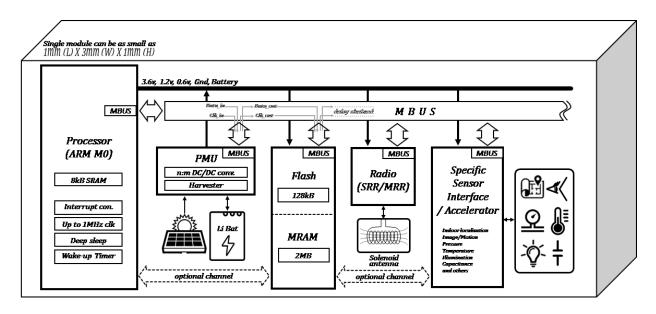

| Figure 2. Example low-power IoT sensor node. The node compacts all of sensor, readout, intelligence, power management, and communication all into a small form-factor to allow for mass dissemination                                                                                                                                |

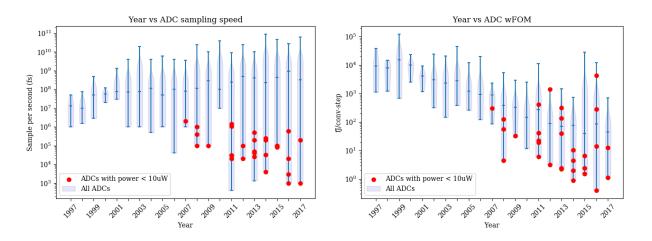

| Figure 3. Trend of low-power ADCs in sampling speed and Walden's FOM                                                                                                                                                                                                                                                                 |

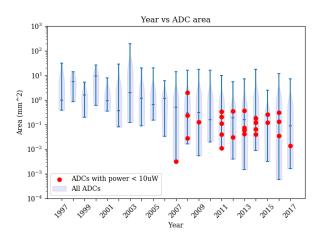

| Figure 4. Trend of low-power ADCs in area                                                                                                                                                                                                                                                                                            |

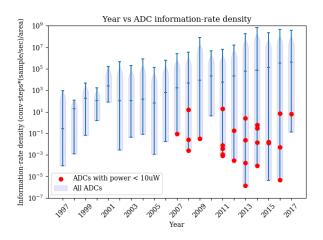

| Figure 5. Trend of low-power ADCs in information-rate density                                                                                                                                                                                                                                                                        |

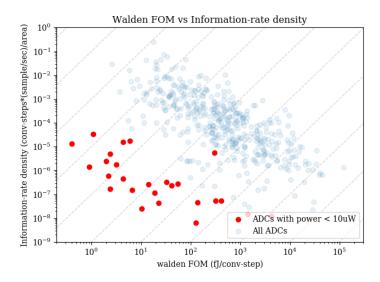

| Figure 6. ADC evaluation plane of information-rate density and Walden's FOM. Upper left is towards ideal                                                                                                                                                                                                                             |

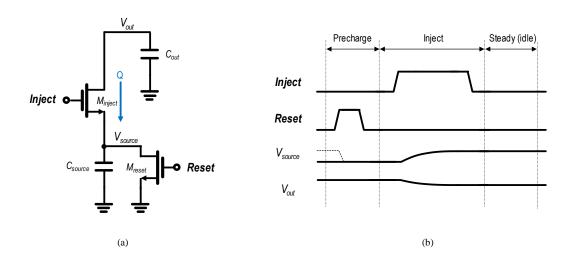

| Figure 7. (a) the most basic charge-injection cell (b) operating waveform. For simplicity of understanding, drawing only shows pull-down version of the charge-injection cell                                                                                                                                                        |

| Figure 8. Thermal noise sources in charge-injection cell                                                                                                                                                                                                                                                                             |

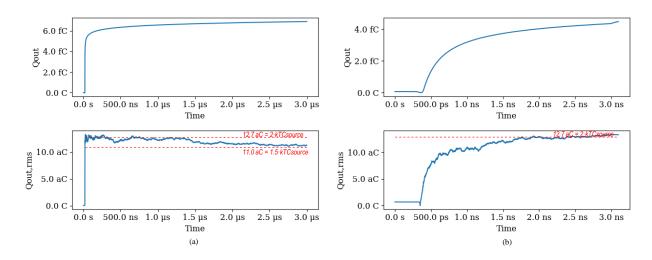

| Figure 9. Signal charge and noise charge comparison in simulation. (a)[upper] Time versus charge output [lower] Time versus standard deviation of charge output (from 100 noise seed iterations) (b) zoom in on the time scale of (a)                                                                                                |

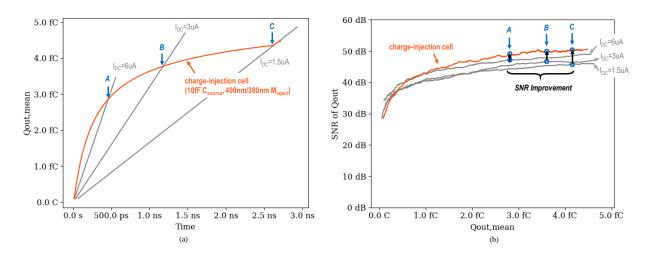

| Figure 10. (a) charge transfer characteristics ( $Q_{out}$ vs time) of charge-injection cell compared to simple current sources with different DC currents (1.5uA,3uA,6uA) (b) The SNR of charge transfer and current sources at different $Q_{out}$ value                                                                           |

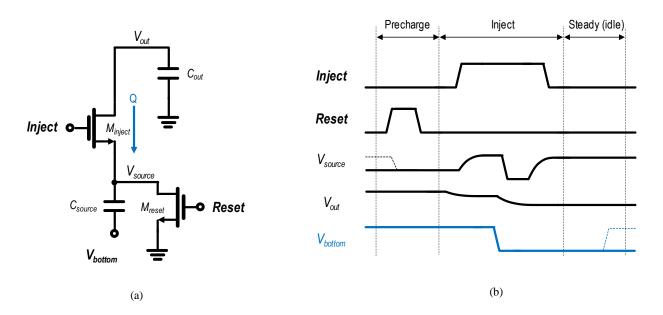

| Figure 11. (a) Modified charge-injection cell with bottom of $C_{source}$ controlled by signal, $V_{bottom}$ . (b)Operation timing of the modified cell. The $V_{delta}$ can significantly be increased                                                                                                                              |

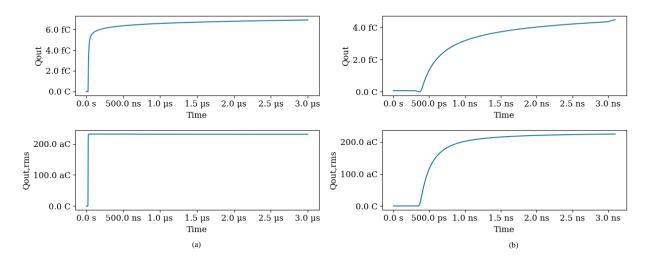

| Figure 12. Mismatch on $Q_{out}$ , simulation comparison. (a)[upper] Time versus charge output [lower] Time versus standard deviation of charge output (from 100 monte-carlo iterations) (b) zoom in on the time scale of (a)                                                                                                        |

| Figure 13. (a) calibration through modifying $V_{inject,high}$ (b) calibration through modifying $C_{out}$ 28                                                                                                                                                                                                                        |

| Figure 14. Comparison of static-current source and charge injection cell with same-sized transistor device. (a) Comparison of $Q_{out}$ by sweeping $V_{out}$ for static current source and charge-injection cell (b) charge-domain equivalent of output impedance mapped to different $V_{out}$                                     |

| Figure 15. Variation in current due to different $V_{out}$ diminishes as the device is operated for a longer time. (top) output current through $M_{inject}$ over time with different $V_{out}$ (0.5~3V) represented as different traces (bottom) standard deviation of output currents at each time point normalized to their means |

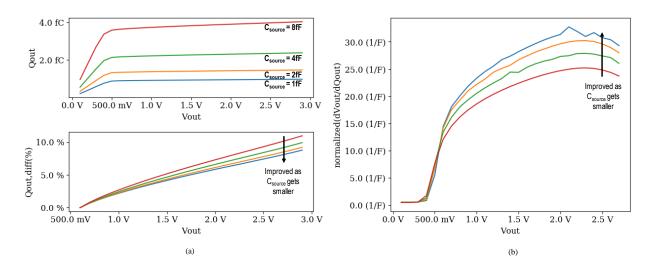

| Figure 16. $T_{inject}$ effect on the consistency of the charge-injection cell (a, upper) $Q_{out}$ vs. $V_{out}$ (a, lower) difference in $Q_{out}$ with sweeping $V_{out}$ , normalized to its own $Q_{out}$ at $V_{out}$ =500mV (b)                                                                                               |

| Calculated charge-domain equivalent of output impedance, normalized to its own $Q_{out}$ a $V_{out}$ =500mV                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 17. $C_{source}$ 's size effect on the consistency of the charge-injection cell (a, upper) $Q_{out}$ vs. $V_{out}$ (a, lower) difference in $Q_{out}$ with sweeping $V_{out}$ , normalized to its own $Q_{out}$ at $V_{out}$ =500mV (b Calculated charge-domain equivalent of output impedance, normalized to its own $Q_{out}$ at $V_{out}$ =500mV                                                                                                             |

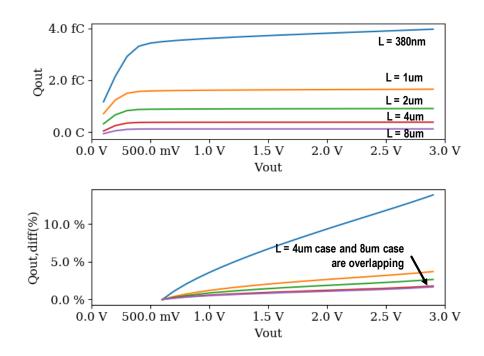

| Figure 18. Length effect on the consistency of the charge-injection cell (upper) $Q_{out}$ vs. $V_{out}$ (lower difference in $Q_{out}$ with sweeping $V_{out}$ , normalized to its own $Q_{out}$ at $V_{out}$ =500mV                                                                                                                                                                                                                                                  |

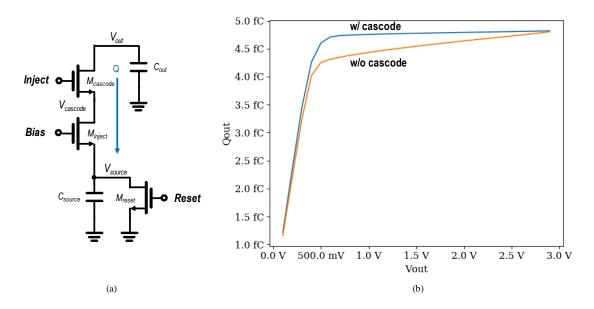

| Figure 19. (a) Charge-injection cell with cascode transistor (b) comparison of consistency with and without cascode device from $Q_{out}$ vs $V_{out}$ .                                                                                                                                                                                                                                                                                                               |

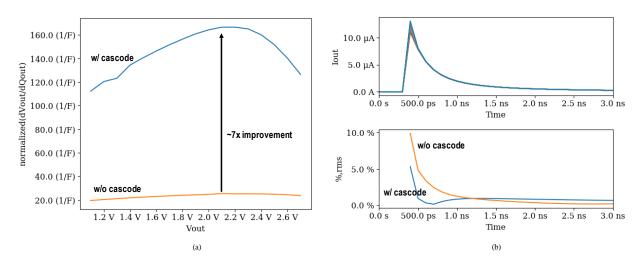

| Figure 20. Comparison of cascoding and non-cascoding charge-injection cells (a) charge-domain equivalent output impedance (b) output current profile in span of time                                                                                                                                                                                                                                                                                                   |

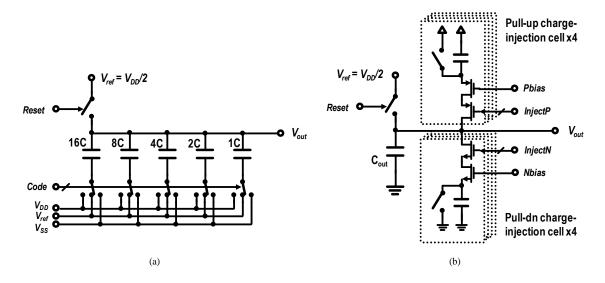

| Figure 21. Simplest 5b DAC of (a) capacitor-array structure (b) charge-injection cell structure 37                                                                                                                                                                                                                                                                                                                                                                     |

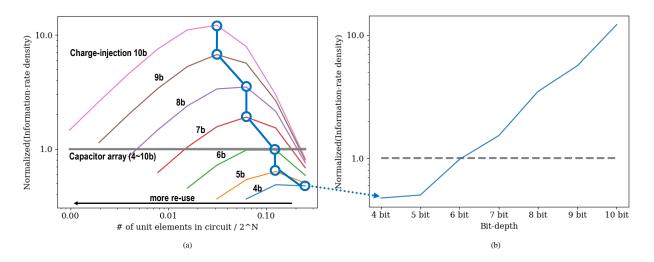

| Figure 22. (a) Information rate density (normalized to capacitor-array structure) vs. number of unicharge-injection cells incorporated in the ADC (normalized to total number of conversion step (b) (near-)optimum information rate density at different bit-depth                                                                                                                                                                                                    |

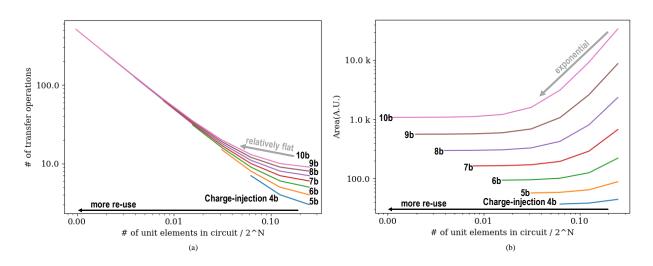

| Figure 23. N <sub>trans</sub> and area from charge-injection structure vs. degree of re-use at different bit-depths                                                                                                                                                                                                                                                                                                                                                    |

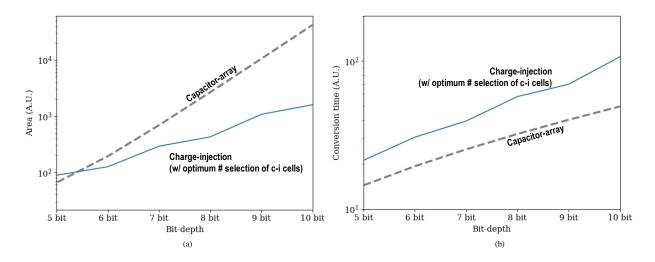

| Figure 24. Charge-injection and capacitor-array structure comparison. (a) area vs. bit-depth and (b) conversion time vs bit-depth. Area is the dominant factor that drives excellent information-rate density in charge-injection structure                                                                                                                                                                                                                            |

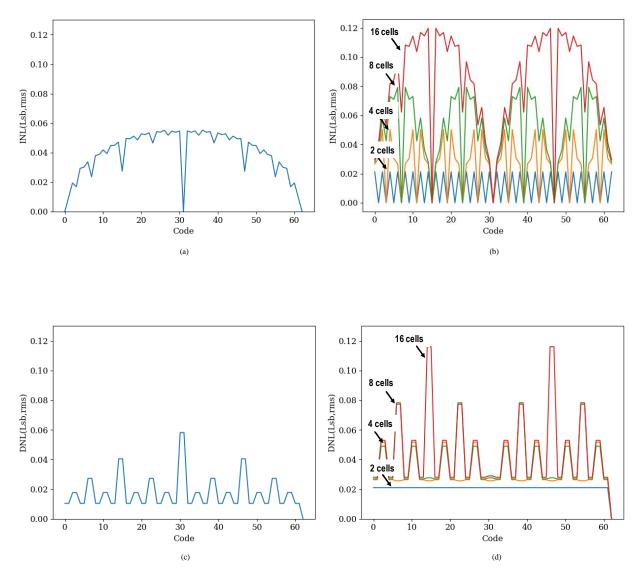

| Figure 25. (a) INL of capacitor-array structure (b) INL of charge-injection structure with different degree of re-use (c) DNL of capacitor-array structure (d) DNL of charge-injection structure with different degree of re-use For comparison, rms mismatch of unitcell in capacitor-array is assumed to be 1% of its nominal value and for charge-injection cell, 3% is assumed                                                                                     |

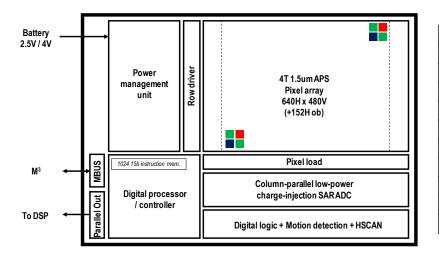

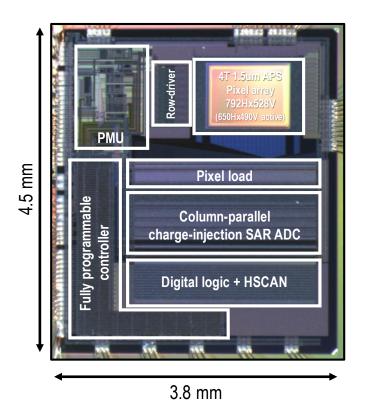

| Figure 26. Overall structure of the low-power image sensor                                                                                                                                                                                                                                                                                                                                                                                                             |

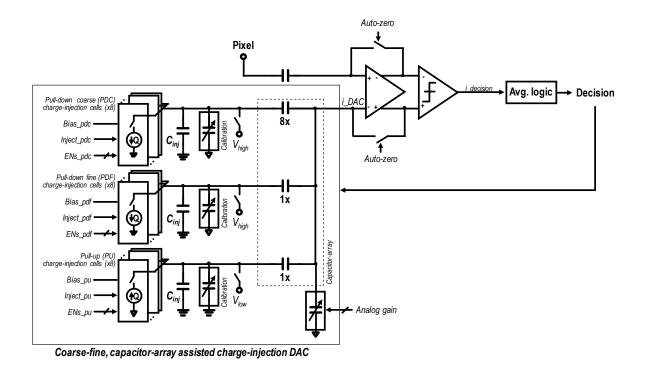

| Figure 27. Block diagram of the low-power capacitor-array assisted charge-injection SAR ADC 48                                                                                                                                                                                                                                                                                                                                                                         |

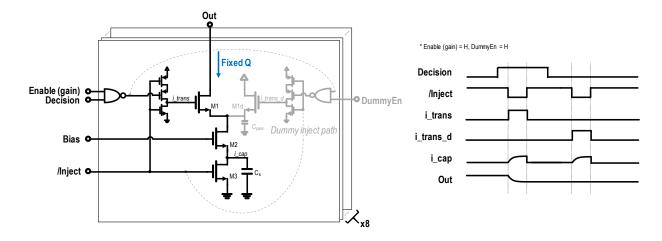

| Figure 28. Charge-injection cell used for the proposed SAR ADC                                                                                                                                                                                                                                                                                                                                                                                                         |

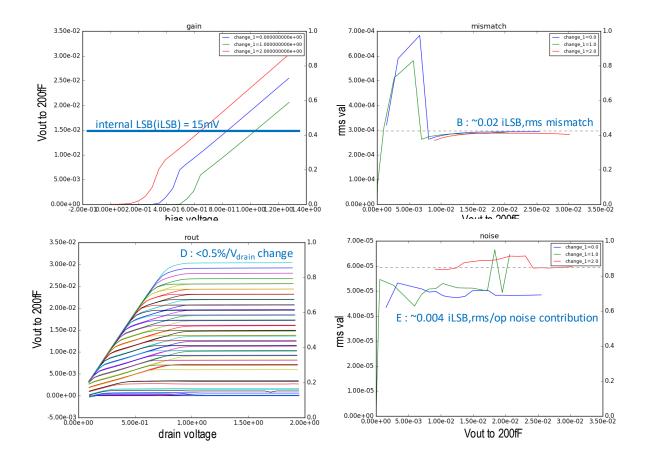

| Figure 29. Performance measure of single pull-down charge-injection cell (upper-left) Charge output (measured in voltrage) to 200fF cap per sweeping bias voltage (upper-right) monte-carle (m=100) result. X=internal LSB, $Y=\sigma_{v,mismatch}$ (lower-left) Drain voltage effect on charge output (measured in voltage). Multiple traces for different bias voltage (lower-right) Transient noise simulation (m=100) result. X=internal LSB, $Y=\sigma_{v,noise}$ |

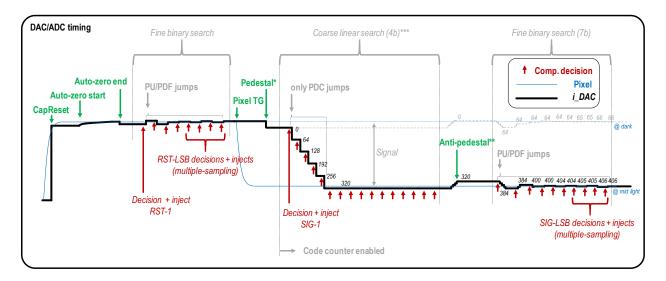

| Figure 30. Illustrative waveform of pixel signal and the DAC output over ADC operation 53                                                                                                                                                                                                                                                                                                                                                                              |

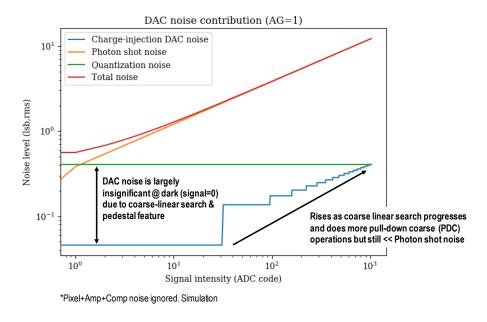

| Figure 31. Increasing noise contribution of DAC at larger codes and its relative magnitude compared to photon shot noise and quantization noise contribution                                                                                                                                                                                                                                                                                                           |

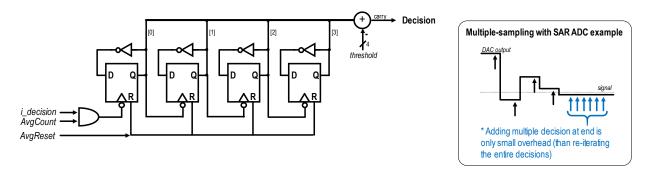

| Figure 32. Average circuit enables multiple sampling within one decision cycle                                                                                                                                                                                                                                                                                                                                                                                         |

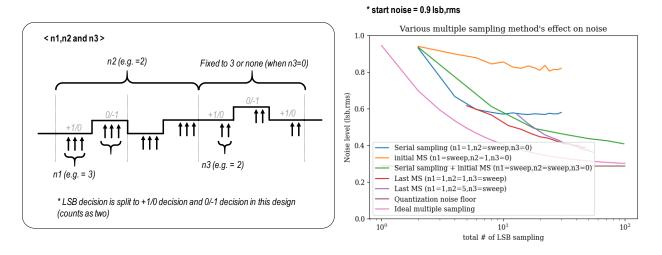

| Figure 33. Different implementation of multiple sampling and their efficacy. Simulation result (right) is based on a model that assumes uncorrelated noise at every sampling instances                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

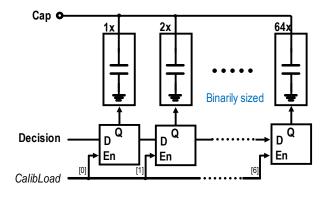

| Figure 34. Calibration capacitor bank                                                                                                                                                                                                       |

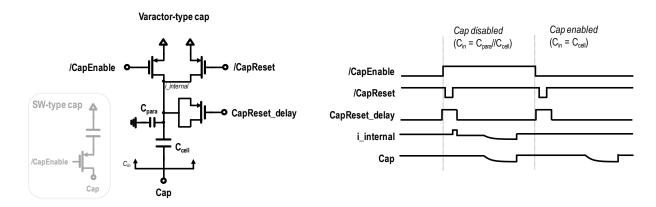

| Figure 35. PMOS varactor-type capacitor for calibration capacitor bank and AG cap used for pull-down paths.                                                                                                                                 |

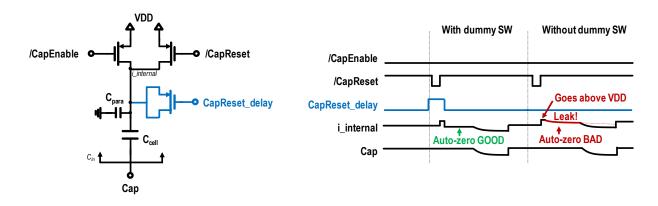

| Figure 36. Avoiding leakage due to i_internal coupling higher than VDD                                                                                                                                                                      |

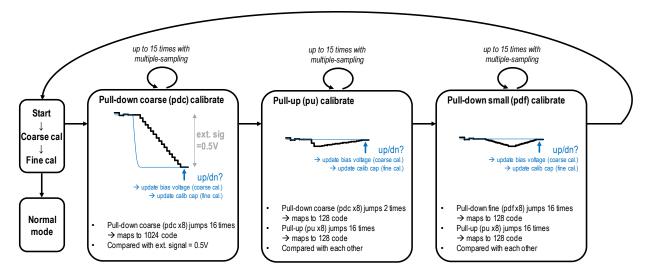

| Figure 37. Calibration sequences                                                                                                                                                                                                            |

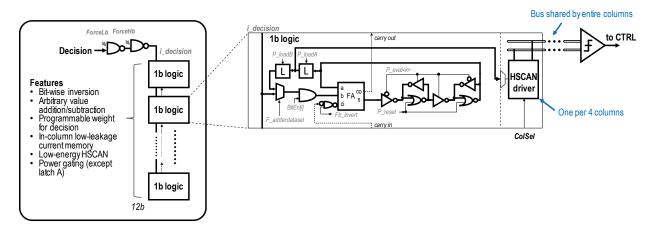

| Figure 38. SAR logic circuit of the proposed ADC                                                                                                                                                                                            |

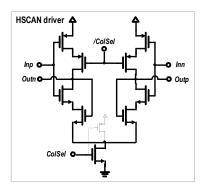

| Figure 39. Static small-swing HSCAN driver                                                                                                                                                                                                  |

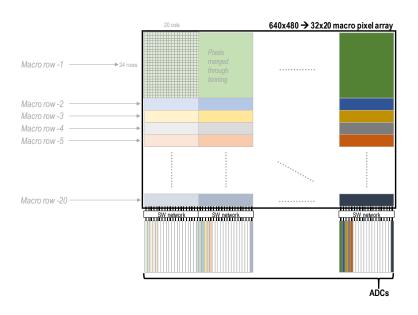

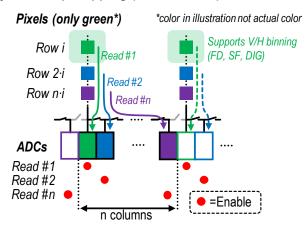

| Figure 40. Sub-sampling of the pixel array for motion-detection (MD) mode and the macro-pixel mapping to column ADCs                                                                                                                        |

| Figure 41. n-way side-step mapping for MD mode operation                                                                                                                                                                                    |

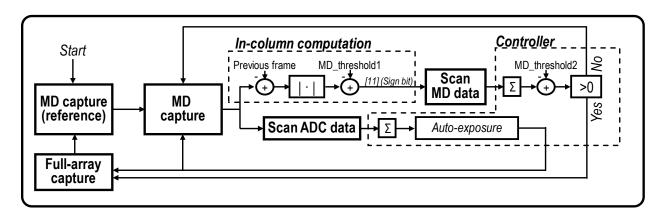

| Figure 42. Algorithm for in-column motion evaluation                                                                                                                                                                                        |

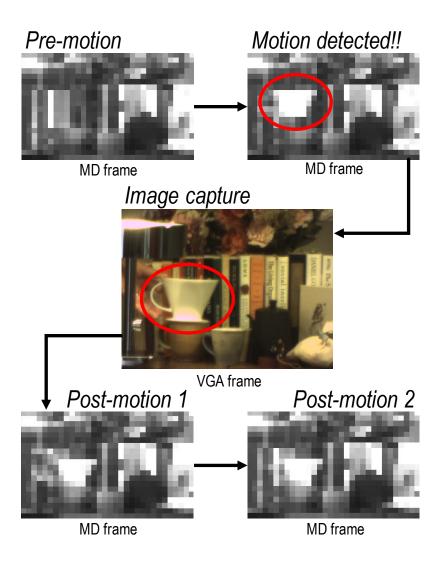

| Figure 43. MD mode triggering full image capture when motion is detected                                                                                                                                                                    |

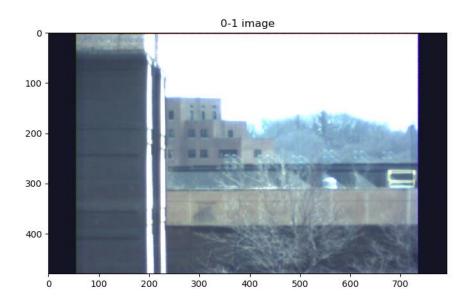

| Figure 44. Sample image from the proposed imager in full-array mode                                                                                                                                                                         |

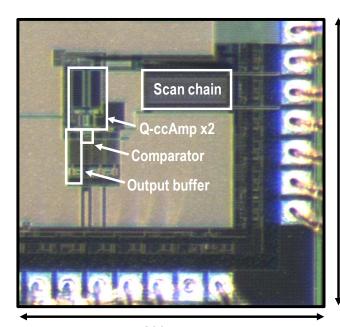

| Figure 45. Chip photo along with sensor level specifications                                                                                                                                                                                |

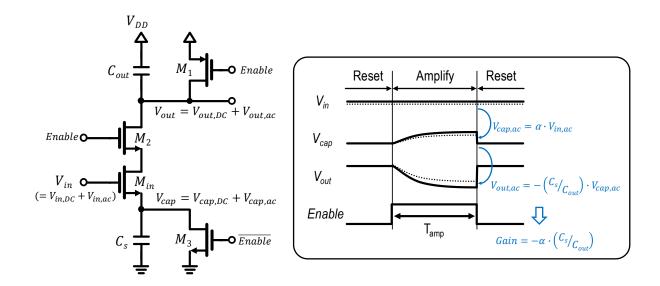

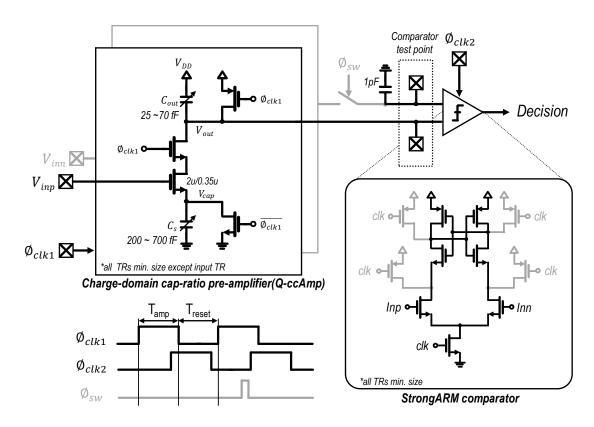

| Figure 46. Proposed charge-domain capacitor ratio based pre-amplifier (Q-ccAmp) and its operating sequence. Gain between $V_{in}$ and $V_{cap}$ ( $\equiv \alpha$ ) and the ratio between $C_s$ and $C_{out}$ determines the amplifier gain |

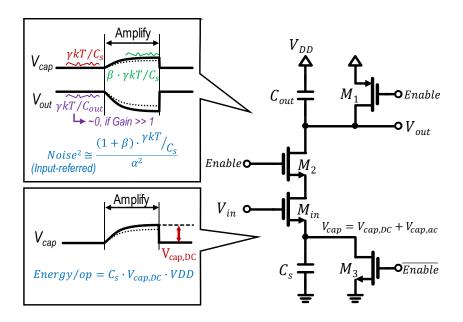

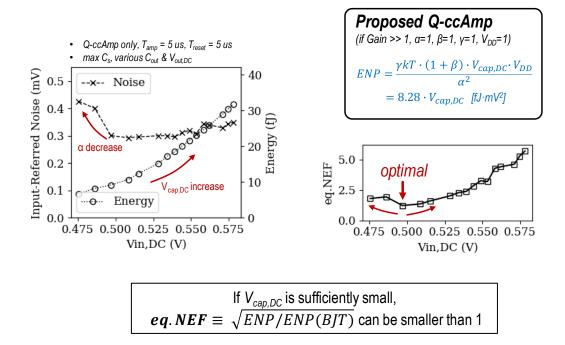

| Figure 47. Noise and energy of the proposed Q-ccAmp                                                                                                                                                                                         |

| Figure 48. By controlling $V_{cap,DC}$ , the discrete-time equivalent NEF (eq. NEF) can theoretically be made smaller than 1. Measurement confirms eq. NEF improvement and optimal point is identified                                      |

| Figure 49. Test circuit configuration of proposed Q-ccAmp. Conventional StrongARM comparator is attached after Q-ccAmp to examine input-referred noise improvement                                                                          |

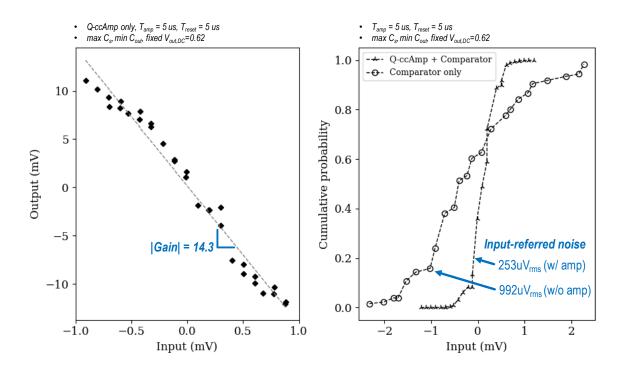

| Figure 50. Measured gain of Q-ccAmp and input referred noise comparison w/ and w/o Q-ccAmp. Input-referred noise is measured by observing the probability of finding logic-high decision at given input voltage (from >10k decisions)       |

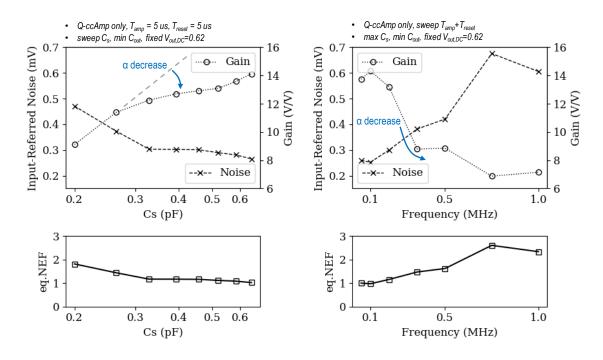

| Figure 51. Measurement of gain, input-referred noise, and resultant eq. NEF over $C_s$ and sampling frequency, $f_s$ = $(T_{amp}+T_{reset})^{-1}$                                                                                           |

| Figure 52. Chip photograph of Q-ccAmp prototype                                                                                                                                                                                             |

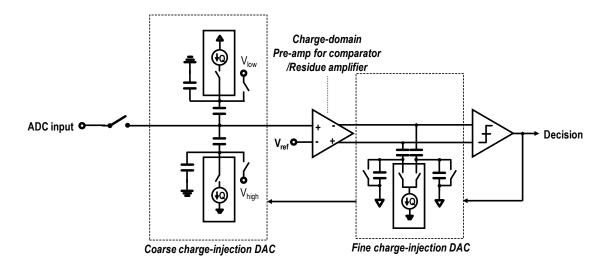

| Figure 53. A hybrid two-step SAR ADC with using charge-domain comparator as residue amplifier                                                                                                                                               |

# LIST OF TABLES

| Table 1. Selection of mark-up factors used for modeling charge-injection cell-based ADC capacitor array-based ADC | _  |

|-------------------------------------------------------------------------------------------------------------------|----|

| Table 2. Energy consumption of each parts in the ADC based on simulation                                          |    |

| Table 3. Comparison table for the proposed imager                                                                 | 74 |

| Table 4. Comparison of Q-ccAmp to other recent and well-known comparators                                         | 84 |

## CHAPTER 1.

### INTRODUCTION

The goal of technology has been and always will be to make its products available to more people. Fundamentally this is because technologies are designed to add value to people's lives and to trigger a demand. Equally importantly, there is a whole industry that depends on cultivating and then sating those demands. Incessantly, technology has striven to deliver more devices into the hands of happy customers, and this trend continues with the Internet of Things (IoT). Projected to infuse the world with tens of billions of new devices in next several years, the IoT is the latest and the largest mega-trend in the world of technology.

Figure 1. Main drivers in the trend of technological evolution. IoT is projected to add tens of billions of devices during the next decade.

The IoT offers tangible value by compacting sensors and artificial intelligence to a miniaturized form factor and coupling them with connectivity so that technology become available

in every area of our lives. Embracing this technology will enable us to continuously assimilate vital information about ourselves and our surroundings and manipulate it to a degree not previously possible. With the foundation of a strong communicational and computational infrastructure, we now possess the capacity to sustain such a mass-deployed network of simple but intelligent things. The IoT is here to prompt real change.

With the maturation of supporting technologies such as cloud computing, smart mobile handsets, hi-fi sensors, and wireless data connectivity, the time for the IoT is ripe. These technologies allow information to be gathered and processed on a mass scale. Furthermore, with more advanced key technologies for the IoT being realized (e.g., low-power connectivity/computing, neural network-based intelligence, high-density solid-state battery, and wireless sensor nodes), the IoT will soon be able to provide substantial improvements in our lives.

We, as circuit designers, stand at the forefront of delivering the promises of the IoT. The capability and success of IoT devices are highly dependent on how well we can design circuits, the core components of such intelligent devices, with respect to viability, cost-effectiveness, and resource-efficiency. This is a new challenge for circuit designers in that there has been little discussion of the resource budgets of these nearly invisible and ubiquitous devices as they represent a distinct diversion from the traditional trajectory of mainstream industry as epitomized by Moore's law.

Although Dr. Moore may not have expected his observation to be interpreted this way, traditionally the law has been used to drive the industry to make use of surplus transistors per dollar to integrate more features, performance, and functions into a circuit product. All of this was supposed to be accomplished while maintaining the price point. Often the primary goal has been to push the performance limit to beat competitors, and aided by the underlying physics of scaling,

the industry was simply set toward maximizing performance through a scaling speed race. Evidently, the word "scaling" in the semiconductor world has been synonymous with better performance in the past decades.

This approach worked well because the dominant market of semiconductors has been in computation, which involves CPUs and memories that scaled very well in terms of both cost and performance as technology improved. Also, the resources available for these computer elements have been generous so that the industry could focus on this singular drive for better performance. However, recently, scaling is finally slowing down to a level where devices are getting neither cheaper nor faster due to physical barriers. Thus, the economics of making faster or more powerful computers is becoming less and less attractive. Currently, the industry is striving to determine what to do with its honed economics of surplus transistor per dollar or diminished dollar per transistor besides just pursuing more Moore.

As we near the saturation of the 30-year drive of Moore's law in computers, the semiconductor industry is turning to the IoT and its associated non-traditional applications that have different measures of value. This new development has been coined "More Than Moore" and is focused on scaling the industry beyond the paradigm of Moore's law of computers and exploring new areas of future exponential growth. Married with the concept of the IoT, "More than Moore" promises to add value in extremely different and more diversified ways than simply making computer boxes run incrementally faster, as had been the focus in the past.

The philosophy behind the IoT that brings the industry to a new level is, in my opinion, that not all useful things require powerful performance. Oftentimes, it is preferred that IoT devices perform small load of interesting tasks in an extremely harsh environment. This type of situation usually arises when devices are interfacing with the natural world. In the natural world, events

happen in terms of seconds, minutes or hours instead of pico-seconds, a timeframe more common in the artificial world of computation. Therefore, such a task requires much less bandwidth. However, because IoT devices need to be deployed in unconventional spaces to access the large volume of untapped information, the resources to be spared per device can be extremely small.

Figure 2. Example low-power IoT sensor node. The node compacts all of sensor, readout, intelligence, power management, and communication all into a small form-factor to allow for mass dissemination

Building slow-operating, low-performance circuits for this purpose may seem like an easy chore given today's capability. However, the limitations of the resources, e.g., battery power and fabrication cost, force circuit designers to consider unconventional trade-offs. Recent circuit developments for IoT devices have focused on making the systems that consume low enough levels of power such that operation can be sustained with the small footprint battery, sacrificing area and speed. The efforts have been successful in that the first wave of commercial circuits for IoT devices has been produced. But to make further improvements in this area, I predict (and assert) that we must focus on circuit techniques that maximize energy efficiency as well as the

efficiency of silicon area usage, a concept sometimes neglected. To date, only few circuit techniques have been discussed as ways to enhance these resource efficiencies.

To fulfill the dream of tens of billions of newly added IoT devices, the economics of deploying small, less powerful but ubiquitous sensors/computers must be grounded in reality to generate sufficient revenue. To trigger an exponential adaptation of such devices, the next milestone to be met is to develop IoT products at a cost that makes mass deployment possible. To achieve this goal, I believe increasing the area efficiency in circuit design will become increasingly important.

To better illuminate the importance of resource efficiency with a focus on design, let's consider the design of an ADC, one of the most representative building blocks in sensors and communication-intense circuits. During the past ten years, there has been a rise in the number of IoT-purposed low-power ADCs in academic domains, as shown in Figure 3 (red dots). The data is from a survey [1] of published ADCs at the International Solid-State Circuit Conference and VLSI Symposium from 1997 to 2017.

Figure 3. Trend of low-power ADCs in sampling speed and Walden's FOM

This trend began around 2007, with an increasing number of reports of designs constrained to consume less than ten micro-watts and to run at very low speeds (below or around 1 MS/s) [2][3][4][5][6][7][8]. Many of these designs were energy efficient, as indicated by their excellent Walden's FOM (wFOM), and indeed these ADCs set a new record wFOM almost every year.

Figure 4. Trend of low-power ADCs in area

Although improving the energy efficiency is a significant accomplishment as far as the success of the IoT is concerned, the size of these ADCs did not decrease despite the sacrifice in speed, as shown in Figure 4. This means that less powerful low-power IoT circuits have become more energy-efficient in recent years but not cheaper, a quality that I believe is paramount to the mass marketing of such devices. Yet as a general consensus, for many analog/mixed-signal designs, the silicon area is deemed a parameter of a particular circuit, not a serious constraint or a measure of how successful the design is. This mindset is due to the fact that analog/mixed-signal designs are often considered already-small-enough peripherals alongside gigantic digital circuits that dominate the size, e.g., in CPUs and APs. It is natural to think in this situation that scaling of size is an issue for digital circuits rather than analog/mixed-signal circuits. Furthermore, there have not been many circuit techniques available to help reduce analog/mixed-signal circuit size.

For the IoT, however, as the core functionality has shifted from computation to sensor interface and communication, analog/mixed-signal circuits have become a more prominent component on the chip. Thus, the area occupied by analog/mixed-signal circuits should start to matter in this case.

Because previously the area of analog/mixed-signal circuits was of little concern, there has not been a good figure of merit by which to evaluate the area efficiency of an ADC design. Thus, I propose a new figure of merit, which I call the information-rate density (IRD) with physical meanings intended:

$$Information - rate \ density = \frac{conv - steps \cdot f_s}{Area}$$

Equation 1

As the process scaling is now truly coming to an end, the silicon area is becoming a more expensive resource. In future designs of ADCs, achieving the maximum conversion rate per a given area will become an important metric for the success of analog-intense circuit systems in terms of cost effectiveness. By using IRD, I aim to capture the future evolution in circuit design with a quantifiable metric related to area and speed that has a physical basis.

The IRD includes the sampling rate ( $f_s=1/T_{conv}$ ) and the effective conversion step (conv-steps= $2^{ENOB}$ ) in the numerator and the area as the denominator. This equation describes the rate at which an ADC is capable of putting out total valid quantization, which I dubbed the 'information-rate,' given a certain area. For example, imagine two ADCs with the same performance and power but with different sizes (e.g., one is 10x larger than the other). Nowadays, given the success of interleaved ADCs [9][10][11][12][13], extra silicon area can almost readily be converted to higher speed by pursuing parallelism such that the larger design can be said to be ten times inferior to the smaller design. This concept is captured in the IRD since the design with the larger area will have

an IRD that is only one-tenth that of the smaller design. For the same end-functionality, a larger design wastes potential speed enhancement per area, leading to increased manufacturing cost.

Figure 5. Trend of low-power ADCs in information-rate density

Indeed, as can be seen in Figure 5, the IRDs of low-power ADCs have been very poor. This observation is true because they essentially use the same circuit techniques as the other ADCs, but they apply aggressive voltage scaling to boost the energy efficiency. When voltage scaling is utilized as a method to trade off speed for energy efficiency, the linear change in voltage (and therefore energy efficiency) results in a quadratic or exponential reduction in speed. That is why their IRDs are so low. The dashed trend lines in Figure 6 illustrate that trade-off.

Figure 6. ADC evaluation plane of information-rate density and Walden's FOM.

Upper left is towards ideal

As seen in Figure 6, the low-power ADCs follow a different trend than other ADCs: their wFOMs are state-of-the-art, but their IRDs are orders of magnitude lower than those of other ADCs. Process scaling has worked in favor of the trend that brought the normal ADCs to the upper-left corner of the plot, whereas a similar trend is observed in low-power ADCs but with a severe offset to the lower-left.

My goal in circuit design was to overcome this trend toward low IRD for low-power ADCs and increase their IRD to levels comparable to that of the other ADCs [14][15] in the upper-left region of the plot. At the same time, I sought to maximize the energy efficiency, so the overall design becomes resource efficient. With these goals in mind, I investigated charge-domain circuit techniques as a possible solution to the IoT problem, benchmarking their successes in high-speed serial links [16] and in high-speed ADCs [17].

Charge-domain circuit techniques are attractive due to their inherent focus on charge as an energy-centric mode of operation, which has the potential to achieve a level of energy efficiency that is higher than that obtained by using a conventional current or voltage mode of operation.

Also, this approach provides interesting features that cannot be achieved with a conventional domain of design.

Throughout the next chapters, I introduce the charge-injection technique that was developed and analyzed in an effort to improve the energy efficiency and IRD of ADCs [14] and describe its unique properties (Chapter 2). Next, I explain its adaptation into an analog-circuit-intense low-power image sensor for IoT application with focus on improving the energy efficiency (Chapter 3) as well as a pre-amplifier for enhancing comparator performance while being energy efficient (Chapter 4). Then I conclude my dissertation (Chapter 5).

# CHAPTER 2.

## CHARGE-INJECTION TECHNIQUE

### **CHARGE-INJECTION CELL**

I first introduced the charge-injection cell technique [14], to enable a charge-domain way of designing a digital-to-analog converters (DAC) and analog-to-digital converts (ADC). It is a circuit that can create fixed amount of charge (or voltage difference) per operation and the method's aim is to exploit dynamicity of charge-based circuits in the operation of DACs. The prevalent method of operating the DAC today is based on capacitor-array based structure which is far from being dynamic in operation. Although being robust, the simple way of its operation is hindering the design to go any further from what was originally described of its potential years before. With exploring dynamicity, charge-injection cell technique births many useful features in DACs and ADCs that other methods were not capable of.

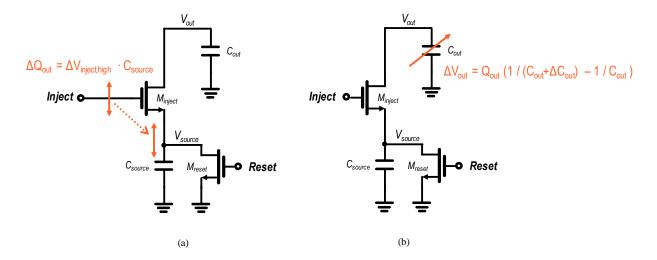

Figure 7. (a) the most basic charge-injection cell (b) operating waveform. For simplicity of understanding, drawing only shows pull-down version of the charge-injection cell.

Charge-injection cell, in its most strip-down form is shown in Figure 7. The purpose of the cell is to deliver the same amount of charge every time it runs, such that it can become a reliable charge/voltage reference generator. Toward this goal, the circuit is designed to conduct current on to the output capacitor in a controlled manner so that the amount of charge output is always kept at fixed value given that the execution is done the same way every time. The way that it works is similar to how dynamic logic circuits would work, having a discrete pre-charge state followed by an operating state to then a steady state, with a distinguishing difference being that this circuit is designed to achieve analog precision rather than to make a digital decision.

A single transfer of the charge-injection cell starts from resetting the bottom capacitor,  $C_{source}$ , to ground. During reset, transistor  $M_{inject}$  is put into turn-off state to shut-off any charge to conduct between  $V_{source}$  and  $V_{out}$ . Also,  $V_{out}$  on  $C_{out}$  is initialized to a reasonably high voltage to give headroom for transistor  $M_{inject}$ . The circuit then enters the injection phase. During injection phase, the Reset signal goes down to turn off  $M_{reset}$ , and the Inject signal transitions from zero (turn-off for  $M_{inject}$ ) to a logic-high state. The logic high voltage needs to be precisely controlled to achieve analog precision of the overall operation. Now, the  $M_{inject}$  transistor enters saturation region of operation and start to conduct charge through  $V_{source}$  and  $V_{out}$ . The current quickly puts charge on to  $C_{source}$  which makes the voltage of  $V_{source}$  to rise, consequently pushes the  $M_{inject}$  transistor deep into sub-threshold region of operation. By this time, the current through  $M_{inject}$  decays exponentially to several decades smaller value so voltages on  $V_{source}$  and  $V_{out}$  are relatively slow-changing. The inject signal is then de-asserted at a deterministic time to end the injection state and then the circuit enters idle state waiting for the next transfer cycle to begin. The voltage change from start to end of this operation on  $V_{source}$  (and  $V_{out}$ ) reflects how much charge has been

delivered to  $C_{out}$ , and is a quantity majorly decided by the interplay of logic high voltage on Inject signal, conductance of  $M_{inject}$ ,  $C_{source}$  and the time given for the injection operation.

Considering that  $M_{inject}$  and  $C_{source}$  are circuit elements that are fixed at design time, the presence of time and voltage as a controlling factor for the charge-injection cell provides ex post facto way of tuning the amount of charge injection. Furthermore, the size of  $C_{out}$  determines the conversion gain at which the transferred charge translates to voltage, so the circuit reserves yet another axis of freedom to control its behavior.

## **Jitter Rejection Property**

However, time becomes a weaker determinant as the circuit is left on for a long time which put M<sub>inject</sub> into deep sub-threshold. This makes the charge flow into C<sub>out</sub> diminish as the operation goes on. One interesting property of the charge-injection circuit is found here that the jitter on the clock that synthesizes the Inject signal will have correspondingly smaller impact over the circuit as turn-on duration extends longer. The amount of extra charge transferred due to the jitter-influenced timing of Inject signal is only proportional to the current that M<sub>inject</sub> conducts at the end of transfer. Furthermore, the relevant jitter here is the period jitter that impacts the conduction of M<sub>inject</sub> through varying the pulse width of Inject signal. Because period jitter is mostly a result of white noise sources in the clock generation circuit with no integration involved, overall magnitude of period jitter is relatively small compared to integral or absolute jitter. Overall, the circuit only puts out small extra amount noise charge.

The exponentially decaying profile of the transfer current, hence reduced sensitivity to jitter gives opportunity for the clock generation energy to scale down steeply as well. As the transfer operation is given longer time that its transfer current is diminished, the accuracy on the clock edge timing is much more relaxed, allowing the clock generation energy to scale down together. As a

general knowledge, an oscillator designed in above-threshold-voltage regime outputs jitter that is in square root relation to the period of the oscillator clock. This means that with slower clock, the circuit easily gains quadratic SNR improvement due to increasing ratio of oscillator frequency to jitter. Significant gain in overall system energy efficiency and jitter tolerance can be reaped by this mechanism. For applications absent of a clean powerful clocking source, slowing down the transfer operation is an effective and viable design choice that will lead to both improved jitter immunity and energy efficiency.

On the contrary, as the same logic projects that jitter tends to contribute more noise charge out of the charge-injection cell as it is run with a faster clock. Yet, it is still valid that an injection cell having a decaying transfer current profile would always outperform an injection cell having a flat-line profile. Also, since period jitter is usually a fraction of the integral jitter, e.g.  $1/10^{th}$ , a circuit element that is sensitive to integral jitter would most likely be the limiting factor of jitter related performance. As widely known, for systems such as ADCs that must accurately control sampling time instance, integral jitter plays bigger role in defining the performance limit than period jitter, therefore depending on the design target, the contribution of charge-injection cell noise from period jitter can be made inconsequential over other sources of noise.

### **Noise Characteristics from Reuse**

One other powerful method to fight jitter is conjoined to the charge-injection cell's inherent reset which stems the concept of reusability in charge injection cell. In fact, this reusability is the heart of the charge-injection technique. After a transfer operation, the cell is put to a reset state preparing for the next transfer cycle while resetting the internal capacitor. This means that the cell is naturally designed to be reused to transfer another instance of charge to an output capacitor to create bigger voltage change. If multiple charge-injections activations of a single cell are spread

over time rather than being concentrated to a single activation, the design can benefit from noise averaging as each instances of period jitter will be uncorrelated. In fact, this operation allows all independent high-bandwidth sources of noise, including period jitter and thermal noise, to have an impact diminished by square-root-of-N, whereas N is the number of total injections. So, the designer can incorporate this aspect of the circuit into the design to combat jitter and even other white noise sources. Also, because creating a bigger voltage swing on the output only necessitates multiple charge-injection cell activations not specific to how many cells are implemented in the design, re-use feature of the charge-injection cell can also be used towards reducing the physical size of the system.

Resetting and re-using the charge injection cell is also beneficial in reducing the impact of flicker noise. In creation of a certain reference voltage through using a continuous time circuit, the flicker noise modulates the conduction of the device and appears on the output. Flicker noise is tricky to get rid of for it changes very slowly thus cannot be low-pass filtered. However, it could be high-pass filtered. It has been well understood through studies on RTS noise behavior in cyclostationary current sources [18] and dynamic comparators that when the device is repeatedly turned on/off in their operation, the traps states in/under the gate oxide, which is the source of RTS noise, are brute-forcedly reset. The point of turning the device repeatedly on/off is to not allow the device to cumulate the trap states that they end up entirely randomly occupied/emptied over time, greatly deviating from the ideal value.

When the circuit is reset, it reduces channel carrier concentration under the oxide so that the traps also tend to empty out. When it turns back on, only the traps that are within a certain energy level are able to react quick enough to probabilistically capture a carrier before the next turn-off happens. Only those traps contribute noise which is a significant reduction from original

status without cycled reset. The trapping and de-trapping of oxide traps in CMOS is governed by a Poisson process that has mean-time to capture/emit as modeled by the following equations (NMOS case) [19].

$$\tau_c = \frac{1}{\sigma_n \cdot V_{th} \cdot n}$$

Equation 2

$$\tau_e = \frac{exp[\frac{E_F - E_T}{kT}]}{\sigma_n \cdot V_{th} \cdot n}$$

Equation 3

The equations suggest that since mean-time to emit could become very short when the device is off ( $E_F \ll E_T$ ) that it indeed is resetting the trap states in the oxide. Eliminating cumulation of trapped states with using this reset, the resultant noise does not show up as 1/f noise but rather a modulated tone in a higher frequency coupled to the periodicity of the reset. Or a flat-then-rolloff profile, effectively showing the high-pass filtration of the operation. Applying the idea to the charge-injection cell, as the cell is being reset per every transfer and each transfer only takes place during finite time duration, the contribution of flicker turns into an uncorrelated noise that is much suppressed from its original amount.

### **Noise Sources and Analysis**

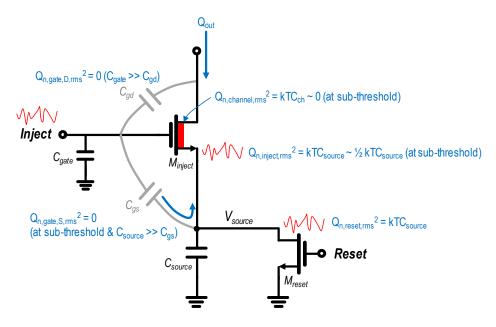

Then what about thermal noise? There are several sources of thermal noise that can affect the amount of output charge. The contribution of the noise sources can be written as follows.

$$Q_{n,out}^2 = Q_{n,reset}^2 + Q_{n,inject}^2 + Q_{n,channel}^2 + Q_{n,gate,S}^2 + Q_{n,gate,D}^2 + Q_{n,other}^2$$

Equation 4

$Q_n$  denotes the noise charge. Mostly they are the kTC charge noise from the reset operation through  $M_{reset}$  on  $C_{source}$ , the thermal noise contribution from conduction of  $M_{inject}$  that defines the

final voltage of  $V_{source}$  at the end of the transfer, the random amount of channel charge injected out of the drain of  $M_{inject}$  at the time it is turning off, and the thermal fluctuation of the signal at the gate coupled to  $V_{source}$  then therefore modulating the current output of  $M_{inject}$ . Some of these elements are a straight forward in their analysis, but some of them are non-linear and time-variant. To study the contribution of these noise sources to acquire intuition for design, some simplifications were committed.

Figure 8. Thermal noise sources in charge-injection cell

The output charge of charge-injection cell is (ideally) exactly the amount of charge  $C_{\text{source}}$  has gained. In simplistic point, what defines  $Q_{\text{out}}$  is the initial and the final voltage on  $C_{\text{source}}$  and the capacitance value as formulated in below equation.

$$Q_{out}(t) = C_{source} \cdot (V_{source}(t) - V_{source}(0^{-}))$$

Equation 5

In  $Q_{out}$ , the two terms that contribute noise are simply  $V_{source}(0^{-})$  and  $V_{source}(t)$ . The two terms are dominantly affected by the thermal noise from  $M_{reset}$  during reset and the thermal noise

of  $M_{inject}$  during injection. The thermal noise of  $M_{reset}$  can be easily analyzed that  $Q_{n,reset}^2 = kTC_{source}$  assuming no other capacitance are seen at  $V_{source}$  node. But trickily,  $V_{source}(0^-)$  and  $V_{source}(t)$  become uncorrelated during the transfer process if t is sufficiently long that the latter term does not duplicate the contents of the first term.

The process of transferring charge in the charge-injection cell is in fact very similar to the process of soft-reset commonly found in image sensor literatures. The technique is usually applied to a 3T APS structure that must control its reset noise to achieve higher performance. Relying on these prior studies [20], a mechanism of how  $V_{source}(t)$  and  $V_{source}(0^{\circ})$  loses correlation in progression of time is illuminated and also the final form of the noise contribution is found. Applying the analysis to the charge-injection cell, assuming the transfer has already taken place long-enough at  $t=0^{\circ}$  to drive  $M_{inject}$  into sub-threshold region and considering shot-noise, following can be formulated.

$$< V_{source}(t)^{2}> = \frac{mkT}{2C_{source}} \cdot \left(1 - \frac{1}{\left(1 + \frac{ql_{inject}(0)t}{mkTC_{source}}\right)^{2}}\right) + < V_{source}(0^{-})^{2}> \cdot \frac{1}{\left(1 + \frac{ql_{inject}(0)t}{mkTC_{source}}\right)^{2}}$$

Equation 6

As t approaches infinity, the form is further simplified to the following, whereas  $m=1+C_{dep}/C_{ox}$  of a MOSFET that is slightly higher than 1 and  $I_{DC}$  is the current at which  $M_{inject}$  started conducting.

$$< V_{source}(t)^2> = \frac{mkT}{2C_{source}} \cdot \left(1 - \left(\frac{mkTC_{source}}{qI_{inject}(0)t}\right)^2\right) + < V_{source}(0^-)^2> \cdot \left(\frac{mkTC_{source}}{qI_{inject}(0)t}\right)^2 \qquad \qquad Equation \ 7$$

As <V<sub>source</sub>(t)<sup>2</sup>> term includes <V<sub>source</sub>(0)<sup>2</sup>> as initial condition, the multiplied term diminishes to zero as t approaches infinity. The final form is shown below.

$$\lim_{t \to \infty} c(t) = \lim_{t \to \infty} \left( \frac{mkTC_{source}}{qI_{inject}(0)t} \right)^2 = 0$$

Equation 8

$$\langle V_{source}(\infty)^2 \rangle = \frac{mkT}{2C_{source}}$$

Equation 9

I call C(t) as a compression term which stems out because of the decay of current through  $M_{inject}$  as  $V_{source}$  rises in time. Intuitive way of understanding the compression term is to picture two charge-injection cells with slightly different start voltage of  $V_{source}$  during charge-injection. Cell that has a higher starting voltage on  $V_{source}$ , because the  $V_{GS}$  across  $M_{inject}$  would be smaller, will conduct less current. The ratio of the reduced current to the normal case is more drastic if the current conduction become a stronger function of  $V_{GS}$ , as in sub-threshold CMOS device or BJT. Under steep (exponential) decay of current through  $M_{inject}$  with reducing  $V_{GS}$  for the case of charge-injection cell, therefore, the voltages that started out higher and conduct smaller current gets caught up by the normal case. After sufficient time, the voltage difference of the two cases at  $V_{source}$  become very close and compressed. The compression term C(t), as a function of time, indicates how much this compression progressed.

Above equations outlines the behavior of noise during sub-threshold part of the operation. It suggests that whatever small-signal noise is on V<sub>source</sub> at t=0<sup>-</sup>, the eventual noise on V<sub>source</sub> after a sufficiently long time will become half of the kT/C noise on C<sub>source</sub>. It agrees with the common sense that when one strips out one degree of freedom in conduction direction to which the electrons can flow in 1-D resistor, the noise contribution is effectively halved. This phenomenon is known to be present in devices with diffusion-based conduction where a potential barrier is present that can blockade certain direction of conduction, i.e. diode or bipolar devices or sub-threshold CMOS.

The noise behavior in above-threshold is dictated by the drift behavior of channel carriers which is only weakly associated with potential barrier that it does not limit the degree of freedom in electron conduction. What this means is that during the transfer of charge in charge-injection cell in above-threshold regime,  $\langle V_{source}(t)^2 \rangle$  will exhibit the whole of kT/C noise power. And as the device enters sub-threshold region, this noise amount will become subject to compression then therefore decays to zero whereas a new half kT/C through sub-threshold operation will take over as time progresses.

Without compression, meaning if the current source is used in place of charge-injection cell, the noise charge contribution should be square-root proportional to the total transferred amount of charge which is the characteristics of shot noise. In this case, the noise can infinitely grow as one increases the amount of charge being injected out. However, the charge-injection cell operation is capable of outputting noise charge far less than current source limited by shot-noise. What compression does, in this sense, is that it is providing a strong negative feedback mechanism that factors down the shot-noise process to a thermal limit. If by chance a shot-noise was present in M<sub>inject</sub> conducting more charge, the conduction immediately feeds back to V<sub>source</sub> and raises the voltage. This in turn causes exponentially less current flow of M<sub>inject</sub> to enact compression, and hence the cell operation is regulated by constructing a strong negative feedback. As a result, the shot-noise contribution does not integrate on C<sub>out</sub> to an infinite value, but it is suppressed to a kTC<sub>source</sub> noise by the work of this feedback on V<sub>source</sub> with C<sub>source</sub>.

The phenomenon can readily be observed through simulation using transient-noise analysis with Berkeley Design Automation (now Mentor). In simulation, a test circuit comprised of arbitrarily sized M<sub>inject</sub> plus 300 fF for C<sub>out</sub> and 11 fF for C<sub>source</sub> is run for 100 iterations with ideal voltage sources for control. The result confirms with our projection of noise power that the

variance of the charge output from the charge-injection cell is at  $2 \cdot kTC_{source}$  (kTC<sub>source</sub> from reset + kTC<sub>source</sub> from M<sub>inject</sub> in above-threshold) and as time progresses, it asymptotically approaches  $1.5 \cdot kTC_{source}$  (kTC<sub>source</sub> still from reset +  $0.5 \cdot kTC_{source}$  from M<sub>inject</sub> in sub-threshold) as the conduction device is put into deeper into sub-threshold. The required time from the state to transition from  $2 \cdot kTC_{source}$  noise state to  $1.5 \cdot kTC_{source}$  noise state is related to the rate-of-decay of the compression term. This implies that if the circuit has smaller  $C_{source}$  and the initial current flowing through M<sub>inject</sub> is larger, the transition point will come earlier, leading to the conclusion that having larger M<sub>inject</sub> and smaller  $C_{source}$  is beneficial in quickly bringing the noise down to  $1.5 \cdot kTC_{source}$ . However, there are other aspects to the selection of those sizes which makes the design become subject to trade-off.

Figure 9. Signal charge and noise charge comparison in simulation. (a)[upper] Time versus charge output [lower] Time versus standard deviation of charge output (from 100 noise seed iterations) (b) zoom in on the time scale of (a)

Assuming  $C_{source}$  output fixed amount of charge mapped to a constant voltage difference from  $V_{source}(0-)$  and  $V_{source}(final)$ , denoted  $V_{delta}$ , the SNR of a fast single transfer event can be written as follows.

$$SNR_{fast\ single\ transfer} = \frac{V_{delta} \cdot C_{source}}{\sqrt{2kT}C_{source}} = V_{delta} \cdot \sqrt{\frac{C_{source}}{2kT}}$$

Equation 10

As  $V_{delta}$  (approximately  $V_{DD}$ - $V_{th}$  = ~hundreds of mV) is typically significantly larger than thermal noise (~1mV) on a small (~10fF) capacitor, the SNR of a single transfer is in the range of 50~60dB. Now comparing the result to a static current source,

Figure 10. (a) charge transfer characteristics ( $Q_{out}$  vs time) of charge-injection cell compared to simple current sources with different DC currents (1.5uA,3uA,6uA) (b) The SNR of charge transfer and current sources at different  $Q_{out}$  value

The charge-injection cell can be used multiple times (=N) to acquire higher signal output, so the SNR can be easily improved by factor of square-root of N. And to improve SNR even further, enlarging C<sub>source</sub> will make the circuit more accurate by the square root of its size increase. If the design requirement requires better noise performance yet the voltage range is flexible, one can leverage the fact that the noise is determined by C<sub>source</sub> but V<sub>delta</sub> has room to grow to improve the SNR. But if a higher voltage is not readily available, one can apply a voltage extension (boost) technique through modulating the bottom node of C<sub>source</sub> as shown in Figure 11. By using the technique, the signal output of the charge-injection can be at least doubled with the noise charge maintained at similar level. Combined, the overall achievable SNR of the inject operation can be

formulated as follows, where N is the number of transfer operation and  $k_{boost}$  is the gain factor from the boost technique.

$$SNR_{multiple\ transfer\ with\ boost} = k_{boost} \cdot V_{delta} \cdot \sqrt{\frac{N \cdot C_{source}}{2kT}}$$

Equation 11

Figure 11. (a) Modified charge-injection cell with bottom of  $C_{source}$  controlled by signal,  $V_{bottom}$ . (b)Operation timing of the modified cell. The  $V_{delta}$  can significantly be increased.

A small drawback of the boost technique is that now the system could see yet another thermal noise source at  $V_{bottom}$ , where a transistor must be present for selectively passing logic-high and logic-low level. This noise will modulate the conduction of  $M_{inject}$  resulting in noise charge, however, as the current through  $M_{inject}$  diminishes as it enters sub-threshold, the magnitude of modulation becomes extremely small to inflict only minuscule noise charge.

This filtering process is what diminishes other contributors of noise in  $Q_{n,out}$  and is worth taking a closer look. Assuming an inverter is driving the  $V_{bottom}$  node and the parasitic capacitance is in the order of fF, the bandwidth of the thermal noise given at  $V_{bottom}$  should be in the order of

GHz. Yet the network conformed by  $M_{inject}$  and  $C_{source}$ , because  $M_{inject}$  is to enter sub-threshold after sufficient time, has the bandwidth in the lower MHz range (or even lower in deep sub-threshold). This means the fast-changing noise coupling into  $V_{source}$  is rejected out by the speed of  $M_{inject}$ , hence does not result noise charge.

A similar mechanism holds for thermal noise that enters  $V_{source}$  through  $C_{gs}$  of  $M_{inject}$ . The Inject signal is also driven by an inverter, therefore is not free of thermal noise fluctuation. When that fluctuation gets coupled into  $V_{source}$ , a similar filtering as above takes place to mitigate the impact. The size of the cap,  $C_{gs}$ , can also be controlled to be a small quantity compared to  $C_{source}$  to reduce the effect. It may be important to size  $M_{inject}$  with smallest possible width to suppress this noise along with meeting other specifications, i.e. output impedance or leakage.

One other source of noise, which is the randomness of channel charge that gets injected out of  $M_{inject}$  to  $C_{out}$ . Because our assumption of the charge-injection operation is that  $V_{out}$  is maintained sufficiently high to sustain  $M_{inject}$  in saturation. What this implies is that the electrons that form the channel of  $M_{inject}$  is entirely attracted to  $V_{out}$  because of its high potential, that all electrons flow out to the drain direction. The question then is how much noise charge was originally stored at the channel by kTC, instead of by what unknown (noisy) ratio will channel electrons split into either the source and the drain. The noise charge stored at the channel is simply kTC<sub>gate</sub>, assuming the device is in strong inversion that the channel charge constitutes mostly of minority carriers at the channel and not the space charge in the depletion region.

If the charge-injection operation is halted while  $M_{inject}$  is in above-threshold and in saturation, the noise charge amount of  $kTC_{gate}$  will appear at  $C_{out}$ . However, if the operation has taken place for long time that  $M_{inject}$  is in sub-threshold region, the impact reduces greatly. In sub-threshold region, the charge stored at  $C_{gate}$  is mostly comprised of the space charge in the depletion

layer beneath the oxide layer. The space charge, during turning-off of the device, attracts majority carrier to neutralize itself from mostly the body terminal of the device and neither from the source or the drain. This means that the charge flow in turning-off a sub-threshold region operating device is nearly zero when seen from source/drain. Almost no noise charge will be output to  $C_{out}$  when  $M_{inject}$  is in sub-threshold for this reason.

Lastly, the  $C_{gd}$  of  $M_{inject}$  provides a coupling path between  $V_{out}$  and the Inject signal, passing the thermal noise on the Inject through to  $V_{out}$ . The noise transfer characteristic will be all-pass, however, the division factor of this noise can be designed to be quite high (e.g. with  $C_{gd} \sim$  few fF and  $C_{out} \sim$  few hundred fF) that its overall effect is negligible.

### **Mismatch and Calibration**

As discussed to this point, operating the charge-injection cell for long enough time for  $M_{inject}$  to reach sub-threshold region of operation helps reject unwanted involvement of several noise sources in the design. The same holds to fend off the impact of mismatch as well.

The main source of mismatch in charge-injection cell is the  $M_{inject}$  transistor. Two factors involved as sources of mismatch in  $M_{inject}$  transistor are; 1) variations that can impact the final value of the  $V_{source}$ , that is the  $V_{th}$  variation of the device, and 2) variations that impact the course of  $V_{source}$  transition, that is the mobility variation of the device. Typically, people simplify the variation model of a MOSFET as being entirely flattened to the  $V_{th}$  change, however, for our use case as in charge-injection cell, the aspect of mobility should be separated to study the operation more accurately.

As discussed in the previous section, the charge that is injected out is determined by  $V_{\text{delta}}$ . The path difference during the large-signal transition on  $V_{\text{source}}$  is compressed to a small value if the charge-injection cell is operated for sufficiently long time. What this means is that the mobility

variation of the MOSFET is compressed out of the picture whereas only the  $V_{th}$  variation remains as the most significant variation source that impacts the charge injected out of the cell.

Figure 12. Mismatch on  $Q_{out}$ , simulation comparison. (a)[upper] Time versus charge output [lower] Time versus standard deviation of charge output (from 100 monte-carlo iterations) (b) zoom in on the time scale of (a)

Although the same charge-injection cell can be reused multiple times with perfect matching between each inject operations, the absolute size of the charge injection is subject to process variation. This variation can be as high as few  $\%_{rms}$  of the typical amount of charge transferred, therefore it calls for calibration if it were to be used for high-precision systems. The ratio of the variation can greatly differ by different selection of  $V_{delta}$  and also the  $\Delta V_{th,rms}$  of  $M_{inject}$ , but a representative number for  $V_{delta}$  is  $\sim 600$  mV ( $V_{DD}$ - $V_{th}$ ) whereas  $\Delta V_{th,rms} \sim 30$ mV (for 400nm/380nm, thick oxide device) which results in 5  $\%_{rms}$  variation in injected charge amount..

Each of the determining factors of the charge-injection cell can be trimmed to yield calibrated charge output, however in terms of feasibility and efficiency, only two methods are favorable.

First method is to change the logic-high voltage of the Inject signal to a specific analog value so to control the  $V_{\text{source}}(\text{final})$ . Because  $M_{\text{inject}}$  device's threshold voltage is the most

dominant factor that alters the charge-injection amount, this method is the most straight forward and effective way to cancel out the global process and temperature variations of the threshold voltage. Also, it is relatively easy to build a replica circuit to acquire an analog voltage that tracks the process and temperature change of V<sub>th</sub>. However, the method typically necessitates a voltage buffer to apply the tracked logic-high level into the charge-injection cells, so it is less disturbed with injection operation. In many cases, the design cost of having it can outweigh the benefit. And designing it to a very fine resolution quickly grows the noise/power budget of the buffer and the replica.

The second method is to apply a tunable capacitor-array at the place of  $C_{out}$ .  $C_{out}$  is assumed to be a high-density on-chip lumped capacitor so partially converting it into a monotonic capacitor-array (also not strongly constrained by matching) only incurs slight overhead to the overall size. With using capacitance to trim the different gain of the charge-injection cell, fine resolution of calibration can be reached. For example, if original  $C_{out}$  is around ~300 fF, a multitude of small capacitance of ~300 aF (varactor scheme preferred) can be added to enable 10b-equivalent calibration capability. To cover the local variation of a single charge-injection cell, the full depth of calibration needs to cover  $\pm 3\sim 6\sigma$ , which is typically around  $\pm 10\sim 20$ % of normal charge transfer amount.

Figure 13. (a) calibration through modifying  $V_{inject,high}(b)$  calibration through modifying  $C_{out}$

## **Output Impedance and Cascoded Charge-Injection Cell**

One final characteristics of concern is the consistency against varying  $V_{out}$ . If the charge-injection cell outputs vastly different amount of charge for different  $V_{out}$ , it is not usable as a reliable reference voltage. Assuming the gate voltage of  $M_{inject}$  can be precisely controlled, one can devise a direct comparison between charge-injection cell and a simple static current source to highlight the difference between their consistency performance.

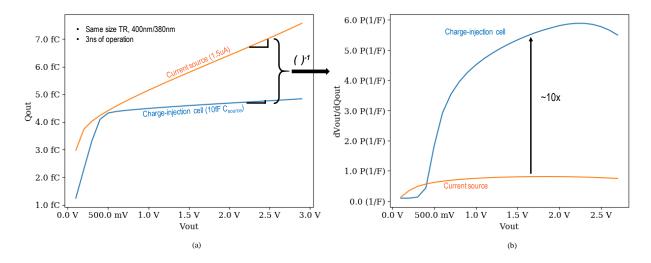

For this simulation experiment, same size transistors were given, which is 400 nm width and 380 nm of length. Each are operating as a charge-injection cell and a static current source for fixed duration of time (3 ns) to output charge to their respective V<sub>out</sub> node. With sweeping V<sub>out</sub>'s initial potential where the operation starts from, I measured how much charge has been output during the operation time. The gate voltage of the current source is fixed to an arbitrary value that yielded similar amount of charge as the charge-injection cell. The result is shown in Figure 14.

Figure 14. Comparison of static-current source and charge injection cell with same-sized transistor device. (a) Comparison of  $Q_{out}$  by sweeping  $V_{out}$  for static current source and charge-injection cell (b) charge-domain equivalent of output impedance mapped to different  $V_{out}$

From the figure, it is evident that both circuits exhibit a saturation behavior. That is, past a certain voltage in  $V_{out}$ , the amount of charge that is being output goes into a region where it stays relatively flat. However, a distinction should be made between the two circuits in respect to how well the circuits conform to saturation. By reading the numbers, the charge-injection cell outperforms a simple current source easily by 10 times with respect to equivalent output impedance.

The reason for such improvement on the charge-injection cell is again related to the negative feedback on  $V_{source}$  node that helps regulate the current output. The mechanism of "having more current through  $M_{inject}$  that leads to faster voltage rise on  $V_{source}$ , and then feeding the voltage back that produces much lesser current through  $M_{inject}$ " plays significant factor in regulating the output charge. Starting from having different current through  $M_{inject}$  at the beginning of the operation due to different  $V_{out}$ , negative feedback quickly compresses the current through  $M_{inject}$  to a significantly smaller variance. So, what really modulates the  $Q_{out}$  is the integral of the difference in current through  $M_{inject}$  over time that it took until the negative feedback compress the

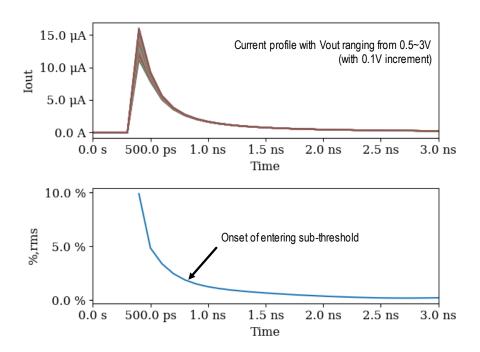

current to a negligible variance. This identifies the source of the variance that limit the output impedance of the cell as the above-threshold part of the operation. Also what needs a second mention is that once the compression has taken place, meaning the  $M_{inject}$  is in sub-threshold region of operation, the output current through  $M_{inject}$  experiences drastically improved output impedance. So, beyond this point,  $M_{inject}$  does not get influenced much with what voltage is set for  $V_{out}$  as can be interpreted from Figure 15.

In contrast, a static current source has limitation of having low output impedance at above-threshold region of operation. The trade-off for using it in sub-threshold is that the current output is strongly affected by mismatch. However, charge-injection cell traverse from above-threshold (high-speed) to sub-threshold region (high-accuracy) of operation, and benefits from both worlds to output consistent charge while being fast.

Figure 15. Variation in current due to different  $V_{out}$  diminishes as the device is operated for a longer time. (top) output current through  $M_{inject}$  over time with different  $V_{out}$  (0.5~3V) represented as different traces (bottom) standard deviation of output currents at each time point normalized to their means

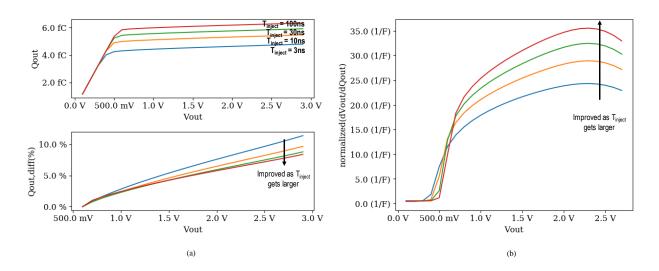

Expanding from this fact, it could be derived that the more the charge-injection cell operates in sub-threshold region, the more accurate it will become. By operating the charge-injection cell longer, an improved charge-domain equivalent output impedance could be acquired. This is backed by simulation result in Figure 16.

Figure 16.  $T_{inject}$  effect on the consistency of the charge-injection cell (a, upper)  $Q_{out}$  vs.  $V_{out}$  (a, lower) difference in  $Q_{out}$  with sweeping  $V_{out}$ , normalized to its own  $Q_{out}$  at  $V_{out}$ =500mV (b) Calculated charge-domain equivalent of output impedance, normalized to its own  $Q_{out}$  at  $V_{out}$ =500mV

As another significant factor affecting the consistency, the rate of feedback (or compression) is reliant on the size of  $C_{source}$  by which constructs the feedback gain for the behavior. With smaller  $C_{source}$ , the sensitivity on  $V_{source}$  increases with respect to current therefore the charge-injection cell achieves compressed state much faster with smaller  $C_{source}$ . For running the charge-injection cell for a fixed time, the consistency of the charge-injection cell improves with smaller smaller  $C_{source}$ . This is because the cell spends more time in compressed state where  $V_{out}$  is not in effect. The effect can be observed through simulation result captured in the following figure.

Figure 17.  $C_{source}$ 's size effect on the consistency of the charge-injection cell (a, upper)  $Q_{out}$  vs.  $V_{out}$  (a, lower) difference in  $Q_{out}$  with sweeping  $V_{out}$ , normalized to its own  $Q_{out}$  at  $V_{out}$ =500mV (b) Calculated charge-domain equivalent of output impedance, normalized to its own  $Q_{out}$  at  $V_{out}$ =500mV

The initial variation in the output current, as can be seen in Figure 15, is due to the lack of output impedance of  $M_{inject}$  in above-threshold region of operation. Since this variation is the main constriction in improving the consistency of the charge-injection cell, it is important to address it to achieve higher accuracy. To our advantage, the output impedance of  $M_{inject}$  transistor in above-threshold region, which is the cause of this variance, will respond to conventional design methods. Typically, increasing the length of the device will be the first choice in improving the output impedance, however, it comes with the disadvantage of slowing down the transfer operation that will make the time for it to enter the compressed-current state to be elongated. What this entails is that the amount of improvement could be diminished or even worsened if the operation time is constrained to be very short. In deep-submicron domain of design, increasing the length to be somewhat longer than minimum feature size may be more effective even accounting what has been lost due to slower speed, but the gain could diminish past a certain length. As seen in Figure 18, the consistency improves drastically as one increases the length of  $M_{inject}$  to be longer than the minimum length, however, the gain diminishes at the length of  $4\sim8$  um that their  $\%_{rms}$  deviation

of Q<sub>out</sub> is almost at par to each other. Also, if the energy to operate the charge-injection cell is taken into the account, the cost of increasing the length become even more prohibitive.

Figure 18. Length effect on the consistency of the charge-injection cell (upper)  $Q_{out}$  vs.  $V_{out}$  (lower) difference in  $Q_{out}$  with sweeping  $V_{out}$ , normalized to its own  $Q_{out}$  at  $V_{out}$ =500mV

A second conventional approach useful for improving the consistency of the charge-injection cell is to apply a cascode transistor to  $M_{inject}$ . Cascoding effectively shields the  $M_{inject}$  transistor from  $V_{out}$  while it is working in the above-threshold region. The outcome is that the output current of  $M_{inject}$  become much more stable with regards to varying  $V_{out}$ . However, the benefit for having a cascode, overall, is not as drastic as in static current sources. The introduction of parasitic node,  $V_{cascode}$ , results in some loss from expected improvement (by  $g_m r_o$ ) of cascoding.

Figure 19. (a) Charge-injection cell with cascode transistor (b) comparison of consistency with and without cascode device from  $Q_{out}$  vs  $V_{out}$ .

The degradation is in two-folds. First, in the compressed-current state of operation, what dictates the output charge is the  $M_{inject}$  transistor. But the drain voltage that it sees is now a more volatile  $V_{cascode}$  (capacitance should be minimized to benefit from cascoding) not the more stable  $V_{out}$  (large capacitance). Because  $M_{cascode}$  transistor, although it is also in sub-threshold, is injecting charge out to  $V_{out}$ , the voltage on  $V_{cascode}$  changes more so than  $V_{out}$ . This affects  $M_{inject}$  in that it sees larger deviation at its drain than in non-cascoding case, so it results in more variation of output current when the cell is in compressed-current state (Figure 20, lower right, tail of the graph). But since the impact of variation in the compressed-current state is already very small compared to above-threshold region operation that this effect does not overtake the benefit of cascoding entirely.

The second is that, because  $V_{cascode}$  has to start from the reset voltage and then rise to sufficiently high level to put  $M_{inject}$  into saturation, the cell has a duration of time where it makes  $M_{inject}$  operate in linear region. In linear region, the output impedance is greatly reduced that the output current become more subjective to  $V_{out}$  difference. The result is that the suppression of

current variation does not measure up to the ideal cascode gain, however, the overall suppression is still more than non-cascoding case (Figure 16, lower right, head of the graph). With these short comings, having the cascode transistor still is able to provide  $\sim$ 7x resiliency against  $V_{out}$  from the non-cascoding case.

Figure 20. Comparison of cascoding and non-cascoding charge-injection cells (a) charge-domain equivalent output impedance (b) output current profile in span of time