# Energy-Efficient Integrated Circuits and Systems to Bridge the Gap between Power and Performance in Wireless Sensor Networks

by

Avish Kosari

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2019

Doctoral Committee:

Professor David D. Wentzloff, Chair Professor Michael Flynn Professor Hun-Seok Kim Professor Jerome Lynch Avish Kosari

<u>avishk@umich.edu</u> ORCID iD: 0000-0002-5853-6823

> © Avish Kosari 2019 All Rights Reserved

To my family for always believing in me

## **ACKNOWLEDGEMENTS**

I am very fortunate to have had the opportunity to complete this dissertation with the help and support of fantastic mentors, colleagues and friends.

I would like to acknowledge and express my gratitude towards many people who contributed to my academic success, from my academic teachers and instructors to my Ph.D. advisor, to only some of whom it is possible to give particular mention here. I would like to begin by thanking my advisor Professor David Wentzloff for his unfailing generosity. Professor Wentzloff gave me an opportunity I am forever grateful for. Thank you for your guidance, support, and your endless supply of creative research ideas. I am also very thankful to Professor Hun-Seok Kim for his valuable guidance and time, and for being very generous in sharing his expertise on wireless system communications throughout my research. I also would like to extend my gratitude to Professor Michael Flynn and Professor Jerome Lynch for their precious time and invaluable advice while serving as my dissertation committee members. It has been a privilege to have you on my committee. I would like to thank my undergraduate advisor, Professor Esfandiar Mehrshahi, for teaching me the foundations of RF circuits and for his contagious passion for science and engineering.

Thanks to all the past and present members of the WICS group, and the circuits lab at the UMich for making working insightful and providing a friendly and productive research environment. I would like to take the opportunity to particularly thank Milad Moosavifard for his great help in the low power receiver project in designing the gm-C filter, Abdullah Alghaihab for

being the helping hand when needed and specially for presenting the low power receiver work on my behalf at the conference, and Jaeho Im & Xing Chen for all the helpful technical discussions. Also Thanks to Elnaz Ansari, Hyeongseak Kim and David Moore.

I would also like to express my gratitude to my dear friends in Ann Arbor, who made Ann Arbor home away from home for me. I cannot imagine how my life would have been if I did not share all the good moments and memories with them.

My deepest appreciation goes to my parents, Soheila and Zia for their endless love and support. I am extremely privileged to have been born to intelligent and loving parents who value education and culture of all kinds. They are the ones who encouraged me to reach for my goals and aim high. Thank you for believing in me. I would like to thank my sisters, Samaneh and Nikoo, who were always willing to listen to me when I was excited to share something new I learned. I can never thank you enough for your endless support. Also many thanks Faranak and Mohammad, for their love and support. Lastly, and most importantly, thank you to Armin, my best friend for the past decade, and the love of my life, for all the sacrifices he has made so I can achieve my goals. I am extremely grateful for your support and patience. Thank you for being by my side all these years.

It is for all the endless love, support and encouragement from my family that I dedicate this dissertation to them.

# **TABLE OF CONTENTS**

| Dedication.   |                                                               | ii  |

|---------------|---------------------------------------------------------------|-----|

| Acknowledg    | ements                                                        | iii |

| List of Figu  | *es                                                           | vii |

| List of Table | es                                                            | X   |

| Abstract      |                                                               | xi  |

| CHAPTER       | 1 Introduction                                                | 1   |

| 1.1           | Internet of Things Era of Computing and Communication         | 1   |

| 1.2           | Wireless Sensor Networks                                      |     |

| 1.3           | IoT Applications Enabled by WSNs                              | 4   |

| 1.4           | IoT Technologies for Long-Range Applications                  | 8   |

| 1.5           | Power in IoT Wireless Sensor Nodes                            |     |

| 1.6           | Power-Performance Tradeoff.                                   | 12  |

| 1.7           | Contributions                                                 | 15  |

| Chap          | ter 1: References                                             | 18  |

| CHAPTER       | 2 MURS Band For Long-Range IoT Communications                 | 20  |

| 2.1           | MURS Frequency Band                                           | 21  |

| 2.2           | Modulation Scheme                                             |     |

| 2.3           | MURS band Signal Propagation and Path Loss Measurements       | 23  |

| 2.4           | Link Budget and System Level Analysis                         |     |

| 2.5           | Summary                                                       |     |

| Chap          | ter 2: References                                             |     |

| CHAPTER       | <b>3 Ultra-Low Power Long-Range Injection Locked Receiver</b> | 34  |

| 3.1           | System Architecture                                           | 35  |

| 3.2           | Design Implementation                                         |     |

| 3.3           | Measurements                                                  |     |

| 3.4  | Summary                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chap | ter 3: References                                                                                                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PTER | 4 Energy-Efficient Long-Range Digital Transmitter                                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.1  |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2  | Digital Transmitter Architecture                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.3  | Design Implementation                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.4  | Measurements                                                                                                                                | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.5  | Summary                                                                                                                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chap | ter 4: References                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PTER | 5 Nano-Watt Analog Front-End For ECG Monitoring                                                                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.1  | AFE Architecture                                                                                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.2  | Low-Noise Amplifier Design                                                                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.3  | Low-Pass Filter and VGA Design                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4  | Experimental Results                                                                                                                        | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.5  | Summary                                                                                                                                     | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chap | ter 5: References                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PTER | 6 Concluding Remarks                                                                                                                        | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1  | Summary of Contributions                                                                                                                    | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.2  | Future Directions                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Chap<br><b>TER</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>Chap<br><b>TER</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Chap<br><b>TER</b><br>6.1 | Chapter 3: References. <b>PTER 4 Energy-Efficient Long-Range Digital Transmitter.</b> 4.1    Transmission Scheme      4.2    Digital Transmitter Architecture.      4.3    Design Implementation      4.4    Measurements      4.5    Summary.      Chapter 4: References    Chapter 4: References <b>PTER 5 Nano-Watt Analog Front-End For ECG Monitoring</b> 5.1    AFE Architecture      5.2    Low-Noise Amplifier Design      5.3    Low-Pass Filter and VGA Design      5.4    Experimental Results.      5.5    Summary.      Chapter 5: References    Chapter 5: References |

# LIST OF FIGURES

| 1.1 | Moore's law and integrated circuits scaling [1.4]2                                                                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Development of wireless cellular networks over the years                                                                                                           |

| 1.3 | Internet of Things vision and major applications [1.6]4                                                                                                            |

| 1.4 | Wireless communication technologies and standards for IoT [1.7]                                                                                                    |

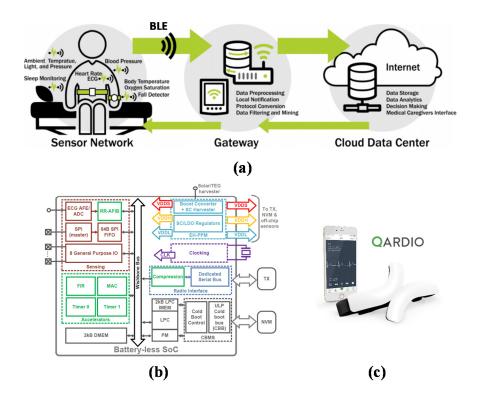

| 1.5 | (a) General IoT-based health monitoring system [1.10], (b) Block diagram of the UMich/UVA sensor node [1.8], QardioCore ECG monitoring device [1.9]                |

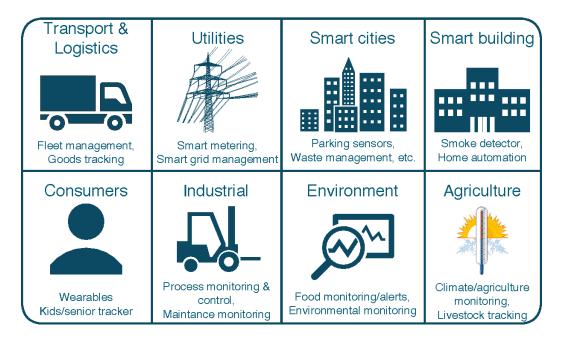

| 1.6 | IoT applications enabled by LPWANs [1.11]7                                                                                                                         |

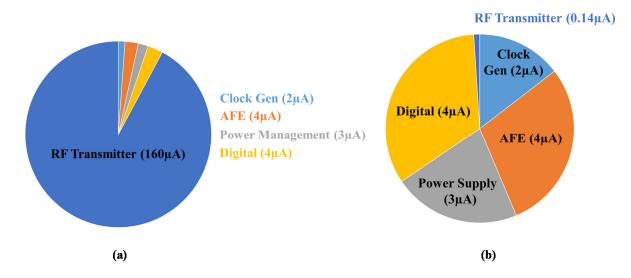

| 1.7 | Current consumption breakdown of state-of-the-art wireless sensor node with (a) continuous transmission, (b) selective, duty cycled transmission                   |

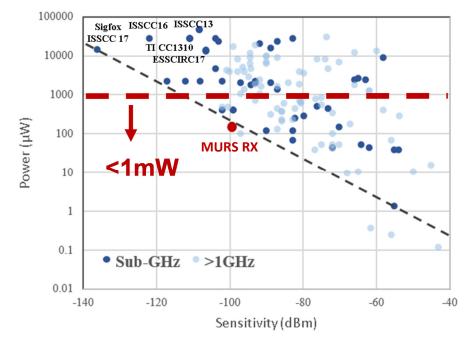

| 1.8 | Low power radio survey: Power vs. Sensitivity, from 2005 to present. The data of the radio survey is from top conferences and commercial transceiver chips, [1.19] |

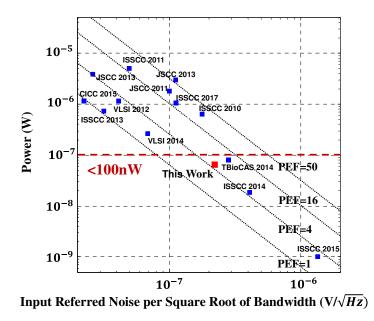

| 1.9 | Power efficiency comparison between this work and other state-of-the-art works in PEF contours. [1.20]                                                             |

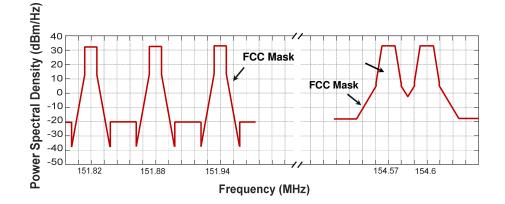

| 2.1 | FCC spectral mask for 151.82-151.94 MHz, and 154.57-154.6 MHz MURS band channels                                                                                   |

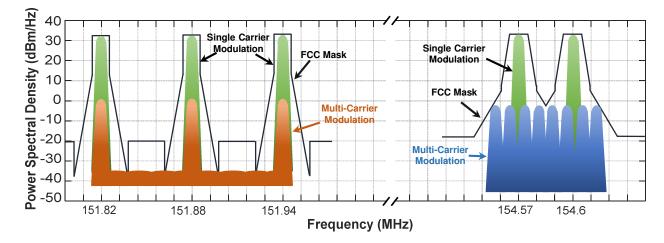

| 2.2 | Proposed single-carrier and multi-carrier modulation schemes                                                                                                       |

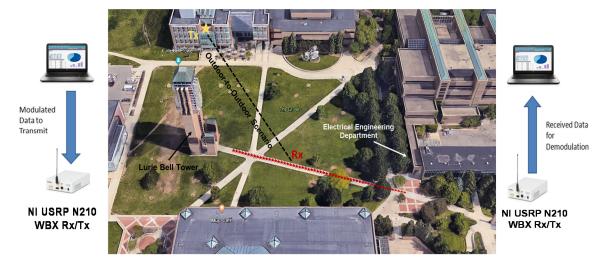

| 2.3 | Outdoor-to-Outdoor measurement scenario and measurement equipment                                                                                                  |

| 2.4 | (a) PL (b) PLE measurements for outdoor-to-outdoor measurement scenario                                                                                            |

| 2.5 | (a) Averaged PLE for selected distances for outdoor-to-outdoor scenario, (b) PLE distribution representation using box and whisker plots                           |

| 2.6 | Outdoor-to-Indoor measurement scenario                                                                                                                             |

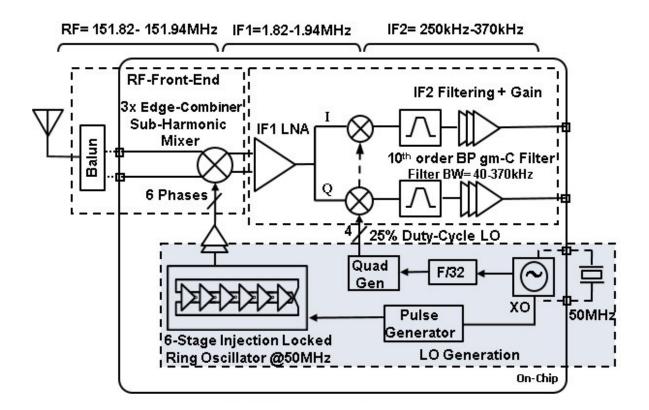

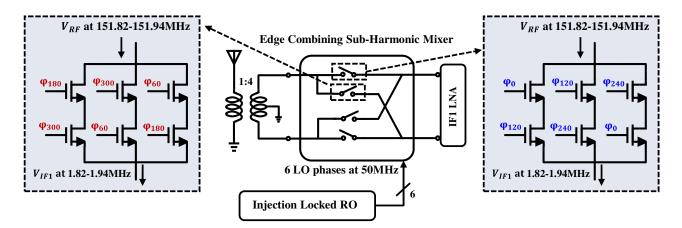

| 3.1 | Block diagram of the receiver                                                                                                                                      |

| 3.2 | RX RF front-end                                                                                                                                                    |

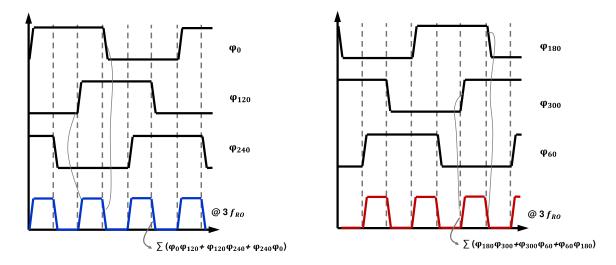

| 3.3 | Double balanced edge-combining mixer's waveforms                                                                                                                   |

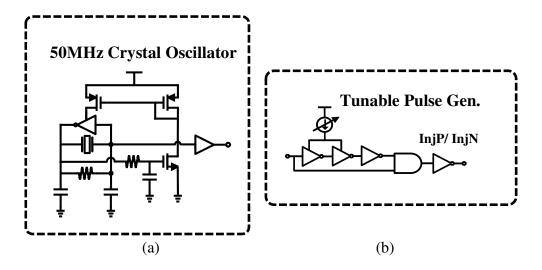

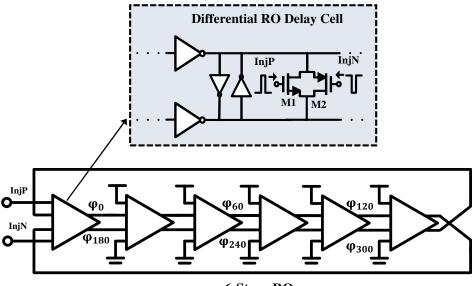

|           | ection locked LO generation blocks including the 6-stage RO and RO delay Pulse<br>erator and 50 MHz crystal oscillator                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5 (a)   | Schematic of the crystal oscillator, (b) Block diagram of the tunable pulse generator40                                                                               |

| 3.6 Dif   | ferential RO and the RO delay cell                                                                                                                                    |

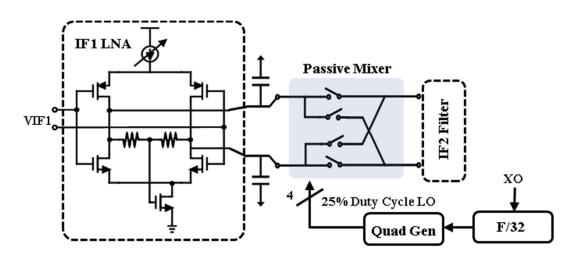

| 3.7 IF1   | stage and schematic of IF1 LNA                                                                                                                                        |

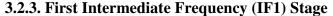

| 3.8 Blo   | ck diagram of a single stage of IF2 10th order filter43                                                                                                               |

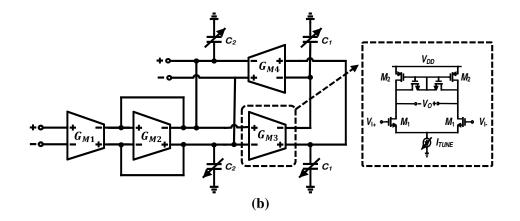

| 3.9 Die   | micrograph of the RX44                                                                                                                                                |

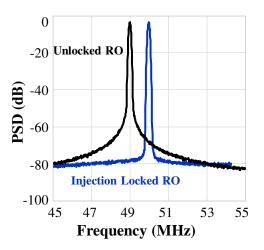

| 3.10 Unl  | locked and locked RO PSD                                                                                                                                              |

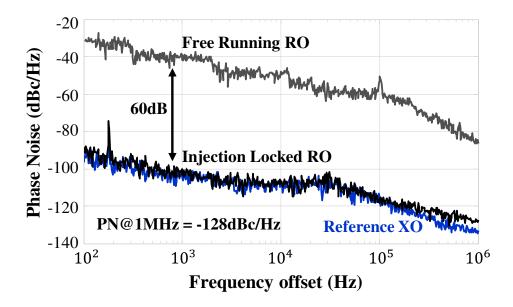

| 3.11 ILR  | O, XO and unlocked RO PN45                                                                                                                                            |

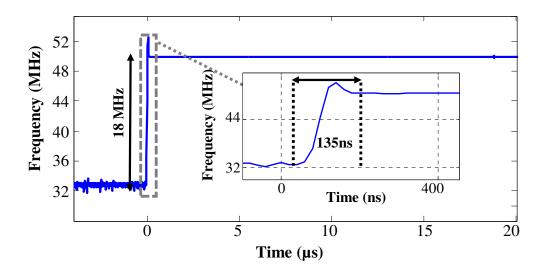

| 3.12 Free | quency transient showing the settling time for ILRO45                                                                                                                 |

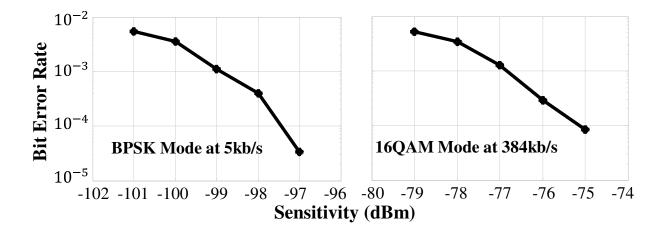

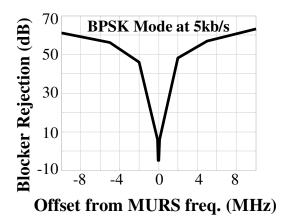

| 3.13 BEI  | R vs. sensitivity for BPSK and 16QAM OFDM modes46                                                                                                                     |

| 3.14 Blo  | cker rejection for the BPSK mode46                                                                                                                                    |

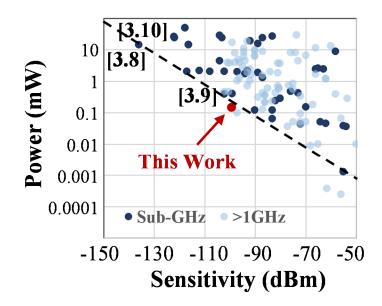

|           | w-power radio survey from 2005 to present. The data of the radio survey is from top ferences and commercial RX chips [3.11]                                           |

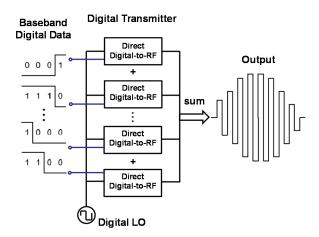

| 4.1 Blo   | ck diagram of a typical digital transmitter                                                                                                                           |

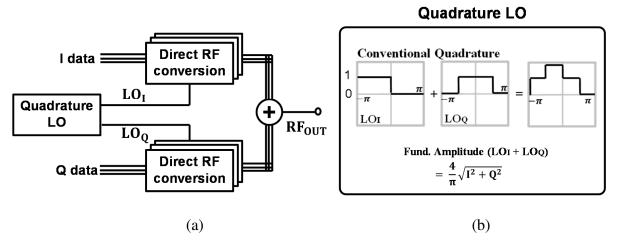

|           | Block diagram of quadrature digital transmitters (b) I and Q LO waveforms of drature transmitters                                                                     |

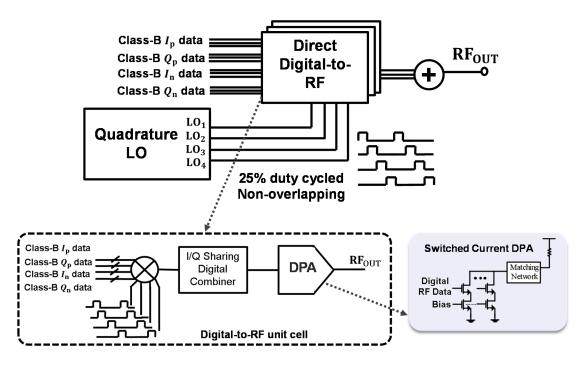

| 4.3 Blo   | ck diagram proposed digital class-B I/Q cell sharing TX55                                                                                                             |

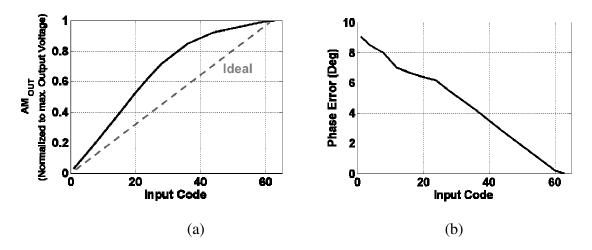

|           | Simulated Input Code- AM characteristic, (b) Simulated Input Code- PM racteristic                                                                                     |

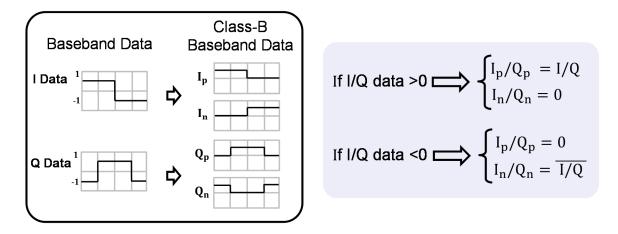

| 4.5 Bas   | beband class-B coding of I/Q data                                                                                                                                     |

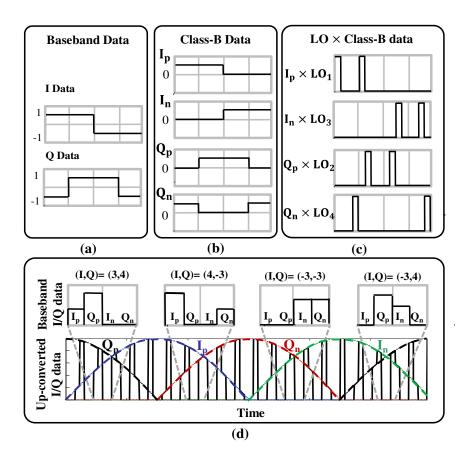

| I/Q       | beband signal processing of DTX (a) Baseband I/Q data, (b) Baseband class-B modified data (c)Up-converted I/Q data, (d) Single tone example of the I/Q combining thod |

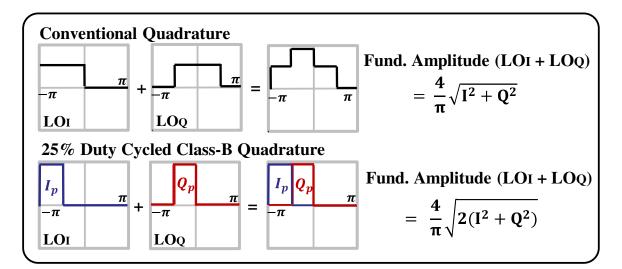

|           | I/LO <sub>Q</sub> waveforms and the IQ combined fundamental components in conventional and ss-B quadrature TX                                                         |

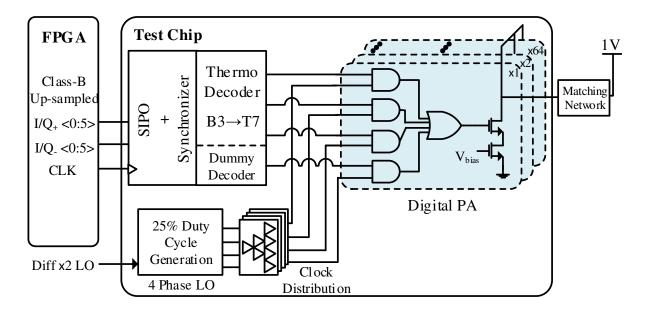

| 4.8 Blo   | ck diagram of the proposed digital transmitter59                                                                                                                      |

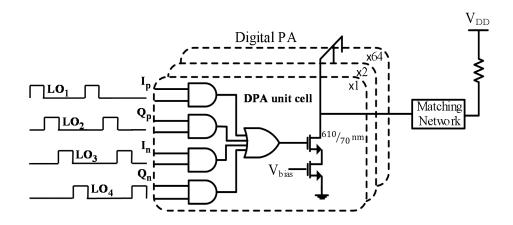

| 4.9 Clas  | ss-B IQ cell sharing DPA60                                                                                                                                            |

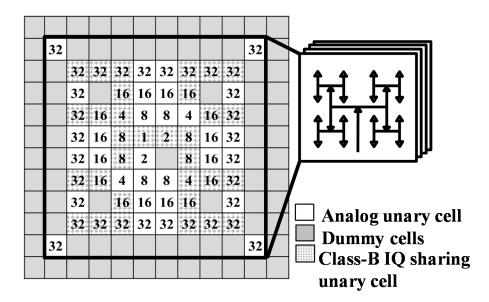

| 4.10 Flo  | or plan of the segmented DPA61                                                                                                                                        |

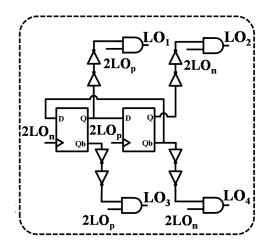

| 4.11 | 25% duty cycle LO generator block                                                                                                                                                          | .62 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

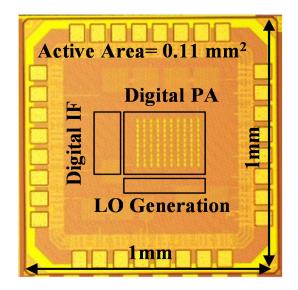

| 4.12 | Die micrograph of the transmitter                                                                                                                                                          | .62 |

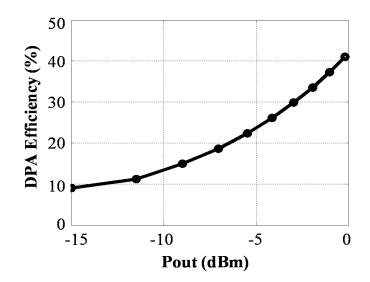

| 4.13 | DPA efficiency                                                                                                                                                                             | .63 |

| 4.14 | Measured output spectrum of single-tone BPSK at 5kb/s                                                                                                                                      | .64 |

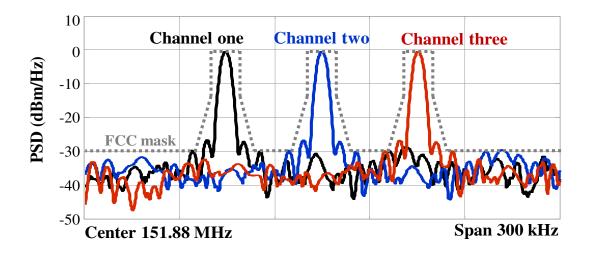

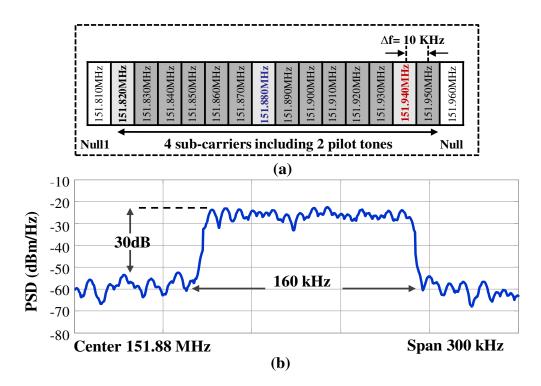

| 4.15 | (a) OFDM modulation frequency planning. (b) Measured close-in PSD of multi-to MURS transmission at 384kb/s                                                                                 |     |

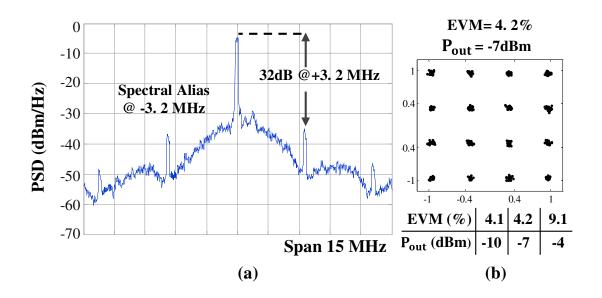

| 4.16 | Far-out PSD of multi-tone transmission (b) EVM and constellation diagram of 160k 16QAM symbols.                                                                                            |     |

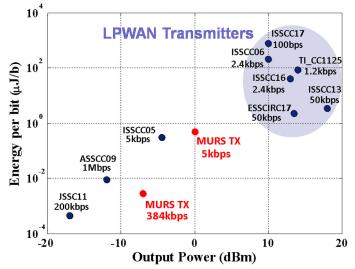

| 4.17 | Energy efficiency vs output power comparison between this work and state-of-the narrowband transmitters [4.10-4.17]                                                                        |     |

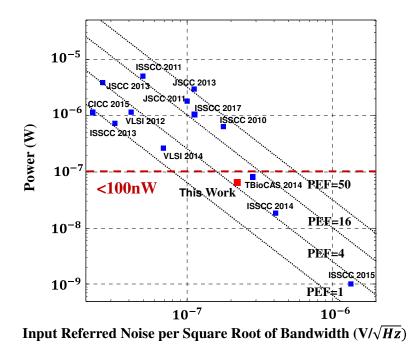

| 5.1  | Power efficiency comparison between this work and other state-of-the-art works in power efficiency factor (PEF) (NEF <sup>2</sup> xV <sub>DD</sub> ) contours. [5.6–5.18]                  |     |

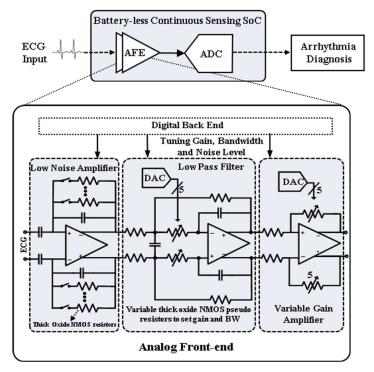

| 5.2  | Block diagram of the AFE                                                                                                                                                                   | .74 |

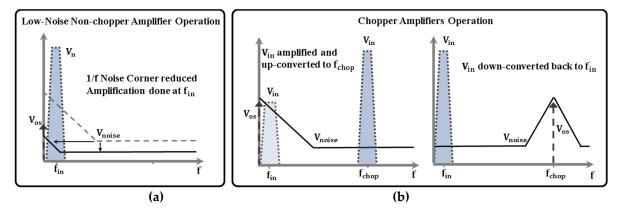

| 5.3  | Frequency domain representation of voltages (input signal $V_{in}$ , noise voltage $V_{noise}$ a offset voltage $V_{os}$ ) in (a) the proposed low-noise amplifier; (b) chopper amplifiers |     |

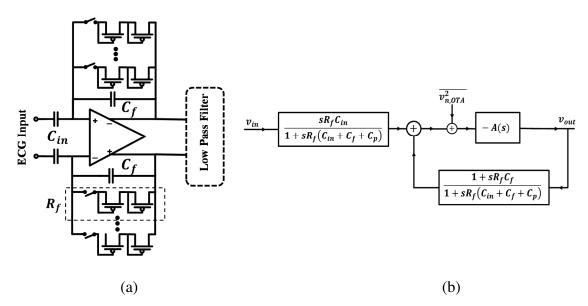

| 5.4  | (a) Circuit diagram of the low-noise instrumentation amplifier (LNA); (b) block diagr<br>representing the operation of the feedback amplifier                                              |     |

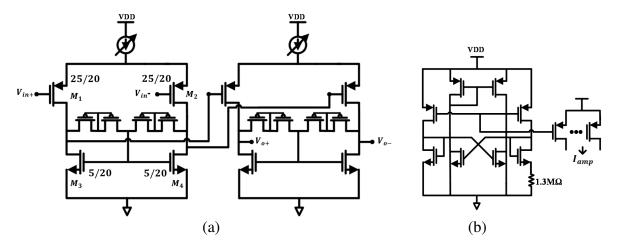

| 5.5  | (a) Circuit implementation of the operational transconductance amplifier (OTA); (b) circuit implementation of the constant g <sub>m</sub> current biasing circuit                          |     |

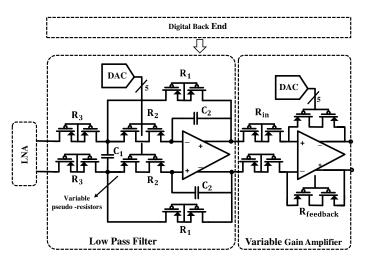

| 5.6  | Circuit implementation of the low-pass filter (LPF) and variable gain amplifier (VGA)                                                                                                      | .81 |

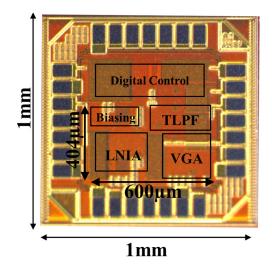

| 5.7  | Chip die micrograph                                                                                                                                                                        | .82 |

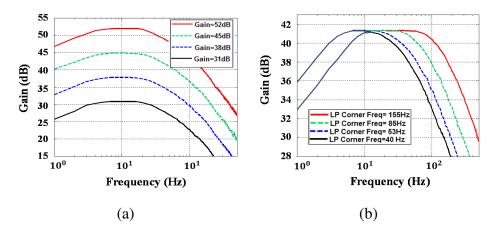

| 5.8  | Measured frequency response of the AFE. (a) gain tuning, (b) bandwidth tuning                                                                                                              | .83 |

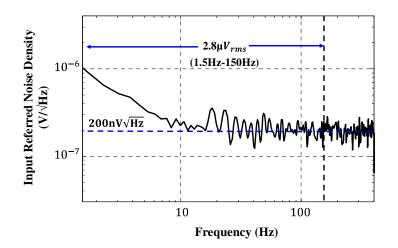

| 5.9  | Measurement input-referred noise density of the analog front-end                                                                                                                           | .84 |

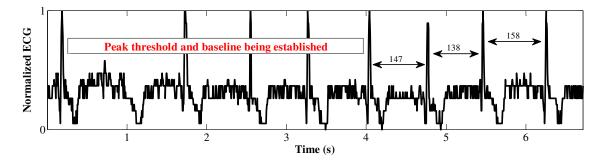

| 5.10 | Measured electrocardiogram (ECG) results for an R-R extraction algorithm. The measu results are for the acquired ECG data through the AFE integrated on the SoC                            |     |

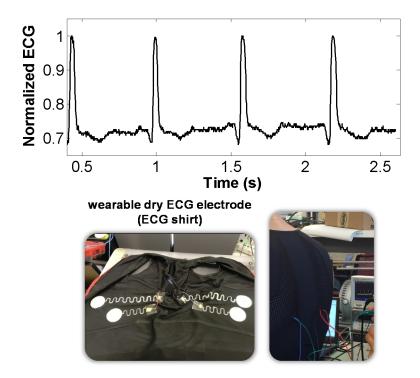

| 5.11 | Measured ECG results using dry wearable electrodes. The measured results are for acquired ECG data through the AFE integrated on the SoC                                                   |     |

## LIST OF TABLES

| 1.1 | LPWAN technologies performance summary and comparison                                                 | .9 |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.1 | Measured mean value and the standard deviation value for PL and PLE for outdoor-to<br>indoor scenario |    |

| 2.2 | Link budget for MURS LPWAN                                                                            | 0  |

| 2.3 | MURS long-range connectivity comparison with other LPWAN technologies                                 | 1  |

| 3.1 | Performance summary and comparison with the state-of-the-art narrowbar receivers4                     |    |

| 4.1 | Performance summary and comparison with state-of-the-art narrowbar transmitters                       |    |

| 5.1 | Performance summary and comparison with the state-of-the-art biopotential AFEs                        | 34 |

## ABSTRACT

The vision of the Internet of Things (IoT) is to create an intelligent and invisible worldwide network of interconnected objects that can be sensed, controlled, and programmed. As we move towards ubiquitous deployment of IoT devices and in order to enable 50 billion connected nodes as predicted by technology leaders, ultra-low power consumption of wireless sensor nodes becomes critical. This is while existing low power approaches in wireless integrated circuits design often sacrifice performance metrics, such as noise, receiver sensitivity, transmitter efficiency, etc. which is not desirable for many IoT applications. Motivated by the ultra-low power requirements of IoT applications, this research presents low power circuit and system design methodologies to bridge the gap between performance and ultra-low power consumption in wireless sensor nodes for future IoT applications.

This work introduces an array of innovative design approaches at the RF and analog circuit level, as well as system architectures for wireless networks that enable ultra-low power consumption at the IoT sensor node, while providing high sensitivity and power efficiency values. This includes circuit designs for a long-range RF transmitter and receiver, along with front-end amplifiers for sensor read-out circuits. The proposed receiver and transmitter are designed to allow data rate agile, narrowband, and long-range IoT communications for Low Power Wide Area Networks (LPWAN) applications. More specifically, the receiver that operates at the Multi-Use Radio Service (MURS) frequency band, consumes only 152µW to achieve a sensitivity of -99dBm

at 5kbps, making it capable of communication ranges on the order of tens of kilometers. Another contribution of this work is a novel transmitter architecture. The transmitter utilizes an efficient system architecture with low power design methods, both in baseband data generation and RF circuits. It delivers a peak efficiency of 41% at a peak output power of 0dBm at 5kbps BPSK modulated data transmission, and also enables 16QAM OFDM transmission with a data rate of 384kbps, making it a suitable solution for remote IoT connectivity in multipath rich environments. In addition to the circuit level implementation of the presented ultra-low power MURS band transceiver, a narrowband transmission scheme along with a system level design and link budget analysis in the MURS band is also presented. The system analysis and transmission scheme in the MURS band shows that it can serve as an ultra-low power and long-range alternative for LPWAN applications.

Finally, an ultra-low power low-noise health monitoring analog front-end (AFE) is developed and presented in this work, that demonstrates the feasibility of <100 nW AFE for continuous ECG monitoring applications. The low-noise 68nW AFE was also integrated on a self-powered physiological monitoring System on Chip (SoC) that was used to capture ECG bio-signals from human subjects.

## Chapter 1 Introduction

### 1.1. Internet of Things Era of Computing and Communication

The Internet of Things (IoT) is generally defined as a worldwide network of uniquely addressable interconnected objects (the "things"). It creates an intelligent, invisible network that can be sensed, controlled, and programmed [1.1]. The IoT is an evolution of the internet rather than a completely new concept. The internet allows for interconnecting hosts. Originally these hosts were super computers then became personal computers, laptops, and mobile phones. Today even machines or embedded devices are hosts.

The origin of internet dates back more than 4 decades to the ARPA network. In America the network grew from only a few hosts to a few dozen during its first decade in 1972 [1.2]. Today about 2.7 billion people have access to the internet in some form. That's roughly one third of the world population. In 2008 the number of things connected to the internet exceeded the number of people on earth. Projections estimate there will be 50 billion internet connected devices in the year 2020 [1.3]. This will include not just computers, smart phones, and tablets, but sensors, consumer electronics, and increasingly more connected objects from our daily lives. Connected things will be crucial enabling parts in many applications such as home automation, industrial control networks, health and sports, biomedical, transportations, agriculture, etc. Technology has come a

long way towards achieving today's remarkable visions for IoT. New disciplines such as wireless sensor networks (WSN) emerged and today can be considered a robust technology. 50 billion things connected to the internet will allow for a large range of applications. Sensors can be combined with data analytics in the cloud to build much more interactive applications which we can access on the internet using personal computers or mobile phones as interfaces. Estimations say that every person might be surrounded by 3,000 connected everyday things. Many IoT devices will be sensors and actuators. Providing this basic functionality does not often require extensive computational resources. However, for some IoT applications the processing of the sensing data should occur in the sensor node. From a performance point of view, it might make sense to do this processing in the cloud. However, the transfer of the raw sensor data to the cloud might present a bottleneck in both available communication bandwidth, and energy resources available on the possible battery driven or energy harvested device to send the data.

Fortunately, the computational power in integrated circuits has so far increased according to Moore's law, and makes more and more complex applications on the device's itself possible.

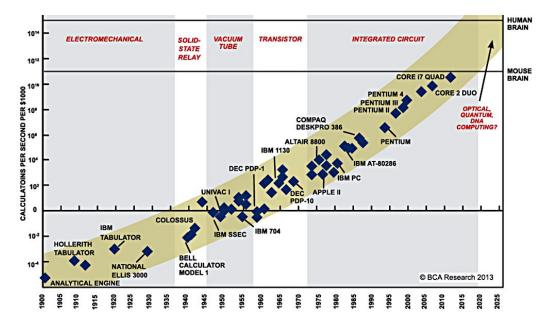

Figure 1.1. Moore's law and integrated circuits scaling [1.4]

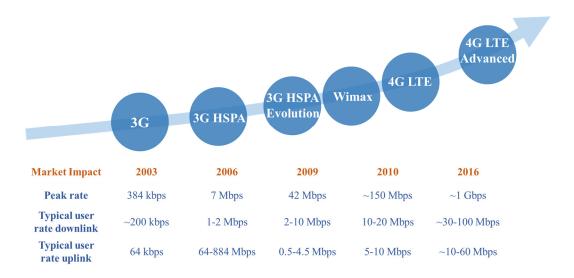

Figure 1.2. Development of wireless cellular networks over the years

According to Moor's law, as shown in Figure 1.1, the number of transistors in a dense integrated circuit doubles approximately every two years. In addition, the development of wireless communication resulted in higher data rate and lower latency. Figure 1.2 shows how cellular networks are approaching data rates comparable with wired residential internet access just a few years ago. This makes denser and more advanced IoT wireless communications possible. Therefore, the continued improvements in efficient communication and moving towards denser computation units (Moore's Law), is enabling the true potential of the IoT revolution.

## **1.2.** Wireless Sensor Networks

WSNs can be described as a network of sensor nodes and/or actuator nodes that cooperatively sense and control the environment and convey the information to gateways and clients. Recent advances in computing, communication and sensing technologies have resulted in significant changes in WSN research and brought it closer to the original vision. Research on WSNs dates back to 1980s when distributed sensor networks (DSNs) were developed [1.5]. DSNs were considered to have many spatially distributed autonomous low-cost sensor nodes, communicating with each other. However the technology was not ready and the large size of these sensor nodes significantly limited the potential applications with wireless connectivity. The new wave of research on WSNs started around 2000 [1.5]. This research focuses on networking technology and information processing suitable for dynamic and resource-constrained sensor nodes.

The state-of-the-art sensor nodes are much smaller in size (i.e. from that of a pack of cards to dust particles), and much cheaper in price. Therefore, suitable for many new applications such as vehicular sensor network, body sensor networks, and environmental monitoring.

## **1.3. IoT Applications Enabled by WSNs**

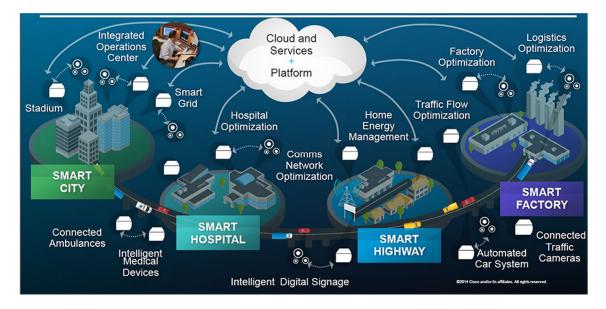

The IoT covers a broad range of applications and devices that can be divided into short range, medium range, and long range applications. These applications range from health care, vehicles and transportation, urban infrastructure, agriculture, to smart metering, and manufacturing. Figure 1.3 highlights major applications envisioned for IoT. There are a number

Figure 1.3. Internet of Things vision and major applications [1.6]

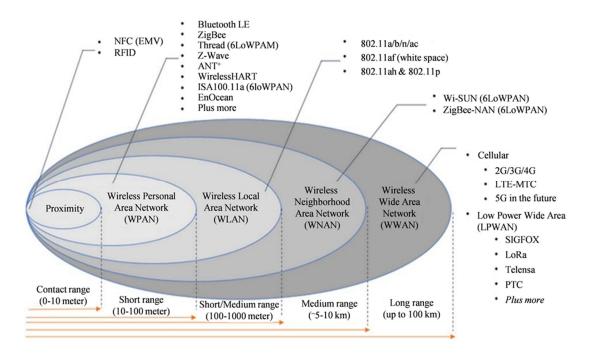

Figure 1.4. Wireless communication technologies and standards for IoT [1.7]

of wireless low-power technologies (e.g. Bluetooth low energy, Zigbee, LoRa, SIGFOX, etc.) that have been developed to address the requirements of IoT applications. These technologies are categorized based on their communication range and listed as in Figure 1.4. In the next two sections short-range and long-range applications of IoT are discussed in more details.

#### **1.3.1. Short-Range IoT Applications**

Advances in wireless technologies such as Bluetooth low energy (BLE) and IEEE 802.15.4 wireless personal area network (WPAN), have made many short-range IoT applications possible. One of the most common applications enabled by these technologies is healthcare monitoring systems. In the last decade, healthcare wearable devices have attracted much attention from the academic and industry community. Wearable devices in health monitoring are being used for motion tracking, and vital signs measurements such as ECG and EEG monitoring. With the

Figure 1.5. (a) General IoT-based health monitoring system [1.10], (b) Block diagram of the UMich/UVA sensor node [1.8], QardioCore ECG monitoring device [1.9]

development of WSNs, such devices can be autonomous and provide constant monitoring of patients without them being hospitalized. This helps improve quality of life and minimizes healthcare costs. As an example, in an IoT based ECG monitoring design, the ECG signal is detected by wearable sensors, sent through a short range communication technology such as BLE to the IoT wearable device where it is processed and analyzed. The analyzed data is finally sent to a remote gateway device for further analysis and storage via wide area connections such as Wi-Fi. A generalized IoT-based health monitoring system is shown in figure 1.5 (a).

An example of an academic sensor node, capable of autonomous ECG monitoring is presented in [1.8]. This work that has been done as a joint collaboration between the University of Michigan and the University of Virginia, measures ECG signals, but does so from harvested thermos-electric energy instead of external batteries. Figure 1.5 (b) shows a block diagram of the sensor node. The battery-less system-on-chip (SoC) is designed as part of a system-in-package (SiP) with a 1 Mbps FSK transmitter (TX) at 2.4 GHz and a non-volatile memory, capable of sensing, processing, and transmission of the data. One commercial example of a smart wearable ECG monitor is QardioCore [1.9], shown in Figure 1.5 (b). This wearable device adopts wireless Bluetooth for data transmission and uses a lithium-ion polymer battery which enables a continual working time up to a day.

#### **1.3.2.** Long-Range IoT Applications

While short-range technologies are appropriate for many IoT applications, they are not well suited for all applications. Some applications such as water/gas metering in the utilities industry, lighting and waste management in smart cities, etc. require low power consumption levels and cost, but long IoT communication ranges. Therefore, Low Power Wide Area Networks (LPWAN) are considered as the evolution of WSNs for long range IoT applications. LPWAN technologies

Figure 1.6. IoT applications enabled by LPWANs [1.11].

operate in both licensed and unlicensed spectrum, and has emerged to fill the gap to enable much wider range of IoT applications. LPWAN technologies have been used in different scenarios in manufacturing, power utilities, agriculture, and transportation. Examples of these applications scenarios are shown in Figure 1.6, and discussed below.

As one of the early adopters of LPWAN, power utilities use smart meters to read household energy usage as well as to send and retrieve billing information remotely in real-time using smartphones. Similarly, LPWAN technologies are making it possible for farmers to track the condition and health of soil and livestock by using LPWAN sensors. These sensors can send data on soil conditions, temperature, and humidity for fertilizer, or detect out-of-ordinary animal movement. Farming requires periodic transmission of data, a few times per hour, and due to remote and rural locations of farms, unlicensed LPWAN technologies are a good candidate for these applications. Additionally, LPWAN technologies can be used in transportation. Cellular networks can now monitor locations of vehicles, trains and boats. However, lower value assets such as parcels, luggage, and packages remain unconnected. This provides a great opportunity for LPWAN technologies, for periodic transmission of location data for these applications.

## **1.4. IoT Technologies for Long-Range Applications**

As mentioned earlier, LPWAN technologies are attracting a lot of attention for long-range connectivity of IoT devices. This Section gives an overview of recent advances in these technologies. LPWANs are considered as the evolution of WSNs for IoT long-range low-data applications. These networks focus on low cost, scalability, extended range, and energy efficiency for end user devices as opposed to traditional broadband networks, which focus on high data rates and low latency. Some of the major applications foreseen for LPWAN are smart metering,

precision agriculture, smart homes, and intelligent transportation systems. Enabling these applications requires the following four key performance metrics for LPWAN technologies [1.12]:

- Long range: LPWAN sensor nodes are expected to communicate with base stations at distances ranging from a few to tens of kilometres.

- Ultra-low-power performance: the device should allow a battery life of greater than 10 years, or the ability to be powered by energy harvesting sensors.

- Low cost: the use of license-free bands and fully integrated transceivers with minimal off-chip components significantly reduces cost in LPWAN.

- Scalability: a single LPWAN base station is expected to connect tens of thousands of sensor nodes over several kilometers.

Several solutions have been proposed for long range connectivity to IoT devices for low data rate and low power applications. Amongst those, two of the common LPWAN technologies being deployed in higher frequency ranges of unlicensed sub-GHz ISM bands are Sigfox and Long range (LoRa) alliance. Sigfox is an ultra-narrowband technology that uses 100 Hz channels with differential binary phase-shift keying modulation [1.13]. LoRa is based on spread spectrum

|                        | y sigfox               | LoRa i                | Simply genit |                       | Weightless"  |

|------------------------|------------------------|-----------------------|--------------|-----------------------|--------------|

| Technology             | SIGFOX                 | LoRa                  | RPMA         | NB-IoT                | Weightless-P |

| Freq. (MHz)            | 868/ 902               | Sub-GHz ISM           | 2400         | 850/900               | Sub-GHz ISM  |

| Licensed               | No                     | No                    | No           | Yes                   | Yes/No       |

| Modulation             | DBPSK/GFSK             | CSS                   | RPMA         | GMSK/<br>QPSK (OFDMA) | GMSK/PSK     |

| Data rate(kb/s)        | 0.1                    | 0.3-37.5              | 0.01-8       | 20-250                | 0.2-100      |

| Coverage range<br>(km) | Rural: 50<br>Urban: 10 | Rural: 15<br>Urban: 5 | 15           | 40                    | Urban: 2     |

Table 1.1. LPWAN technologies performance summary and comparison.

techniques and Gaussian frequency shift keying [1.14]. Another solution for IoT connectivity is NB-IoT cellular IoT technology that utilizes licensed LTE bands with 200 kHz bandwidths [1.15]. Table 1.1 summarizes the key performance metrics for the most common LPWAN technologies [1.13-1.17]. The existing LPWAN technologies often use a high uplink transmit power (>13dBm) and high receiver sensitivity values of around -140 dBm in downlink. These performance metrics result in a high power consumption in the RF front-end of sensor nodes. In addition, most of the existing LPWAN solutions utilize the sub-GHz band to target reliable long range communications with low power budgets. However, these solutions still have excessive power consumption that limits their on-time and adoption for ultra-low-power radios for massive IoT connectivity. More detailed discussions about power constraints in wireless sensor nodes are presented in the following sections.

### **1.5.** Power in IoT Wireless Sensor Nodes

Ultra-low power operation is a key requirement to tap into the huge business opportunity by battery-powered IoT devices. In some applications such as those of LPWAN, a battery lifetime of 10 years or more with AA or coin cell batteries is desirable to achieve lower maintenance costs. Additionally, in some energy-constrained applications a self-powered and battery-less operation of sensor nodes is of crucial importance, and significantly reduces the costs associated with replacing batteries.

As mentioned earlier, the basic functionality of a typical IoT sensor node is: sensing the environment, processing some of the data on node, and wirelessly communicating with the outside world. In these devices often receivers and transmitters that are responsible for the wireless communication of the data, dominate the power budget. There are many reasons why transceivers consume higher power compared to other components in a sensor node. This is often tied into the

Figure 1.7. Current consumption breakdown of state-of-the-art wireless sensor node with (a) continuous transmission, (b) selective, duty cycled transmission

deliverables and specifications of radios. The main performance requirements of transceivers which leads to their high power consumption are: the high operating frequency, low noise performance and sensitivity requirements of receivers, high output power and efficiency of transmitters, and high interference tolerance which creates the need for high precision and power hungry clock generation. As a reference point, the power breakdown of the academic wireless sensor node presented in [1.18] is shown in Figure 1.7 (a). The current consumption breakdown confirms that in a state-of-the-art wireless sensor node the receiver and transmitter are the energy bottleneck.

In some IoT applications where there is no need for a continuous data transmission in the wireless sensor node, duty cycling is employed in the radios to save power. Therefore, the captured data is only transmitted if required or at specific time intervals. Although this method significantly reduces the power overhead of radios, in many scenarios analog front-ends (AFEs), which are the primary input blocks in a sensor node and responsible for amplification of the sensed data, need to stay on at all times to perform a continuous monitoring of the data. Therefore, the power

consumption for AFEs becomes comparable to the overall power consumption of sensor nodes. This is specifically important in scenarios where multiple sensing channels exists or the sensor node has to operate from a harvested energy. Figure 1.7 (b) shows this comparison and confirms the importance of ultra-low power AFEs in wireless sensor nodes.

## **1.6.** Power-Performance Tradeoff

#### **1.6.1. Radio Design Tradeoffs**

IoT applications demand different wireless technologies and radio specifications. Some applications such as connected cars require high data rates for short-range communications, while others like LPWAN call for very long-range low data rate communications. Pushing for any of the performance metrics in a receiver or a transmitter often results in a higher power consumption. From a system-level perspective, long-range communication translates into a high link budget for a transceiver, which accounts for all the gains and losses in the transmitter to receiver path. In

Figure 1.8. Low power radio survey: Power vs. Sensitivity, from 2005 to present. The data of the radio survey is from top conferences and commercial transceiver chips, [1.19]

order for a transmitter to enable a long-range transmission with a low power consumption, it needs to provide high output powers with high efficiency values. In addition, for receivers to enable longrange communications, they require high sensitivity values. A highly sensitive receiver would require a very good noise performance which results in a high power consumption in the receiver.

The radio survey presented in Figure 1.8 spans major conferences and journals from 2005 to 2018, and includes commercial transceiver chips, demonstrating this power-sensitivity tradeoff for low power receivers. With sensitivity, in dBm, on the x-axis and power, in  $\mu$ W, on the y-axis, a linear trend-line is shown on the figure that suggests a correlation between sensitivity and power. As highlighted on the top left corner of the plot, long-range LPWAN radios often target high sensitivities and interference tolerance, but have a high power consumption. In addition, some of these LPWAN technologies such as SigFox, highly sacrifice wireless communication data rate in order to achieve long range communications. It should be noted that while the survey separates radios of different frequencies, it includes receivers of different data rates, architectures, and interference characteristics; none of which is separated in the plot.

With the rapid growth in the number of IoT devices, there is a need for long-range ultralow power, with less than a milliwatt power consumption, radios that can bridge this gap, and enable wide area ubiquities communication. In the radios presented in this work, we have performed highly efficient circuit and system design techniques to realize a balanced powersensitivity design and to bridge the gap between long-range LPWAN and ultra-low power radios. As it is highlighted in Figure 1.8, a receiver with a power-sensitivity of around 150µW at -100dBm is presented, that can achieve similar coverage ranges to other LPWAN technologies at a much lower power consumption.

13

#### **1.6.2. AFE Design Tradeoffs**

As mentioned earlier in the discussion about power in wireless sensor nodes, to ensure a long lifetime for IoT devices without battery replacement, having an ultra-low power analog frontend amplifier in a sensor read-out circuit is of crucial importance. The accuracy of decisions based on the sensed data, directly depends on the performance of the front-end amplifier. One of these main performance metrics for a sensor read-out circuit is the overall noise performance which is typically dominated by the AFE. For a given amplifier topology, there exists a fundamental tradeoff between power and noise. Therefore, to achieve a better noise performance, amplifiers often consume a sufficiently large amount of power. In addition, the amplifier power does not decrease with technology scaling, as it is noise limited rather than technology limited.

Recent advancements in state-of-the-art self-powered systems, such as [1.9], have demonstrated sub- $\mu$ W operation for these systems. This highlights the requirement for <100 nW AFEs. However, targeting low absolute power often results in poor noise performance. Figure 1.9

Figure 1.9. Power efficiency comparison between this work and other state-of-the-art works in PEF contours. [1.20].

presents a comparison of power consumption versus root mean square (RMS) input-referred noise per square root of bandwidth for the recent state-of-the-art signal acquisition systems, and shows the power-noise tradeoff for these front-ends. As shown in the plot, the majority of signalacquisition systems, sacrifice power to achieve a better noise performance or vice versa. Note that constant power efficiency factor [1.21] (PEF) contours are shown on the plot.

In order to enable large utilization of IoT sensors, there is a need for ultra-low power AFEs with less than 100 nW power consumption with low noise performance. As shown in Figure 1.9, an AFE is developed in this work which sits between ultra-low power and high performance AFEs in order to bridge this gap.

#### **1.7. Contributions**

As we move towards ubiquitous deployment of IoT devices and in order to enable 50 billion connected nodes as predicted by technology leaders, ultra-low power consumption of wireless sensor nodes becomes critical. However, low power approaches in wireless integrated circuit design often result in sacrificing the performance, such as noise, receiver sensitivity, transmitter efficiency, etc. which is not desirable for many IoT applications. To mitigate these challenges, this thesis presents innovative low power system and circuit design techniques that bridges the gap in performance in wireless sensor nodes to ultra-low power consumptions for future IoT applications.

#### 1.7.1. Multi-Use Radio Service Band for Long-Range Communications

As discussed earlier, with the rapid growth of IoT applications requiring long-range data transmission, LPWAN technologies are attracting a lot of attention. However, enabling communication ranges on the order of tens of kilometers by using ultra-low power wireless nodes

is very challenging. In order to address the ultra-low-power requirement and conflicting challenges of LPWAN, we introduce a narrowband transmission scheme along with a system level design and link budget analysis in the MURS band as a long range and low-power alternative system wireless link demonstration for the LPWAN IoT applications. Experimental channel and link characterization for the proposed MURS band system architecture for LPWAN long-range scenarios has also been performed.

#### 1.7.2. Ultra-Low Power Long-Range Receiver

As seen from the low power radio survey in Figure 1.8, most receiver's that are intended for long-range applications are high power with power consumption values greater than 1mW. Therefore, for energy-constrained applications there is a need for ultra-low power radios that enable long distant communications. To this end, we have developed a receiver system architecture and low power RF circuit design techniques to allow ultra-low power consumption for kilometer range applications. In Chapter 2, a 152  $\mu$ W Multi-Use Radio Service (MURS) band receiver is presented that addresses the low active power, high sensitivity, and interference rejection challenges and requirements of LPWAN radios. The RX achieves a sensitivity of -99 dBm at 5kbps, capable of over 10 km communication.

#### 1.7.3. Ultra-Low Power Long-Range Transmitter

Similar to receivers, power is often scarified in transmitters to achieve a better efficiency or a higher data rate. As a solution for IoT long-range connectivity, an efficient design for an ultralow power digital transmitter is introduced and implemented. As mentioned earlier, long-range IoT technologies use low data rate transmission schemes to mitigate the power constraints. We have developed systematic low power design methods both in baseband data generation and RF circuits to enable a lower power consumption while achieving a high efficiency value for the transmitter. In Chapter 4 we present an ultra-low power digital transmitter that uses our method of class-B I/Q cell sharing in order to deliver a peak efficiency of 41% at a peak output power of 0 dBm at 5 kbps in the MURS frequency channels. It also enables 16QAM OFDM transmission with a data rate of 384 kbps, making it a very suitable solution for remote IoT connectivity in multipath rich environments.

#### **1.7.4. Ultra-Low Power ECG Monitoring Analog Front-End**

As it was shown in the power breakdown of Figure 1.7, the ultra-low power consumption of AFEs is essential for organic growth of WSNs. However, low absolute power often results in poor noise performance in AFEs, as shown in the plot in Figure 1.9. In Chapter 5 we present an ultralow power low-noise AFE that meets the requirements of ultra-low power energy-harvesting physiological sensors. The AFE uses low-noise and low-power circuit design methodologies and aggressive voltage scaling to satisfy both the low power consumption and low input-referred noise requirements of ECG signal acquisition systems. We show the feasibility of <100 nW AFE for continuous ECG monitoring applications. The low-noise 68nW AFE was also integrated on a selfpowered physiological monitoring System on Chip (SoC) that was used to capture ECG bio-signals from human subjects from wet and dry wearable electrodes.

### **Chapter 1: References**

- [1.1] A. Al-Fuqaha, M. Guizani, M. Mohammadi, M. Aledhari and M. Ayyash, "Internet of Things: A Survey on Enabling Technologies, Protocols, and Applications," in *IEEE Communications Surveys & Tutorials*, vol. 17, no. 4, pp. 2347-2376, Fourthquarter 2015.

- [1.2] V.G. Cerf, D.D. Clark, R.E. Kahn, L. Kleinrock, "A brief history of the Internet", in: ACM SIGCOMM Computer Communications Review, vol. 39, no. 5, October 2009 (reprint from Internet Society, December 2003).

- [1.3] Evans, D. (2011). "The Internet of Things: How the Next Evolution of the Internet is Changing Everything". Cisco Internet Business Solutions Group (IBSG).

- [1.4] Kurzweil, Ray, "The Singularity Is Near: When Humans Transcend Biology" P67, The Viking Press, 2006.

- [1.5] Q. Wang, I. Balasingham, "Wireless Sensor Networks An Introduction", *Wireless Sensor Networks: Application Centric Design*, 2010, ISBN 978-953-307-321-7.

- [1.6] Major Applications and Issues in Internet of Things, Accessed on August 23, 2018. [Online]. Available: http://www.aiehive.com/applications-issues-internet-things//.

- [1.7] Building IoT gateways to the cloud, Accessed on August 23, 2018. [Online]. Available: https://www.microcontrollertips.com/building-iot-gateways-to-the-cloud/

- [1.8] Yahya, F.; Lukas, C.J.; Breiholz, J.; Roy, A.; Patel, H.N.; Liu, N.; Chen, X.; Kosari, A.; Li, S.; Akella, D.; et al, "A Battery-less 507nW SoC with Integrated Platform Power Manager and SiP Interfaces", *In Proceedings of the 2017 Symposium on VLSI Circuits*, Kyoto, Japan, 5–8 June 2017.

- [1.9] QARDIO. Accessed on Aug. 22, 2018. [Online]. Available: https://www.getqardio.com.

- [1.10] Rahmani et al, "Exploiting Smart E-Health Gateways at the Edge of Healthcare Internet-of-Things: A Fog Computing Approach", *Future Generation Computer Systems* 78 (2018).

- [1.11] Boulogeorgos, A.A., Diamantoulakis, P.D., & Karagiannidis, G.K. (2016). Low Power Wide Area Networks (LPWANs) for Internet of Things (IoT) Applications: Research Challenges and Future Trends. *CoRR*, *abs/1611.07449*.

- [1.12] GU. Raza et al., "Low Power Wide Area Networks: An Overview," *in IEEE Commun. Surveys* & *Tutorials*, vol. 19, no. 2, pp. 855-873, Second quarter 2017

- [1.13] Sigfox. Accessed on July 30, 2018. [Online]. Available: http://www.sigfox.com/.

- [1.14] "LoRa modulation basics," Semtech Corp., Camarillo, CA, USA, Rep. AN1200.22, May 2015. [Online]. Available: http:// www.semtech.com/images/datasheet/ an1200.22.pdf

- [1.15] Y. P. E. Wang et al., "A Primer on 3GPP Narrowband Internet of Things," *in IEEE Commun. Mag.*, vol. 55, no. 3, pp. 117-123, March 2017.D

- [1.16] Weightless. Accessed on July 30, 2018. [Online]. Available: http://www.weightless.org/

- [1.17] Ingenu. Accessed on July 30, 2018. [Online]. Available: https://www.ingenu.com/ technology/rpma/

- [1.18] Zhang, Y.; Zhang, F.; Shakhsheer, Y.; Silver, J.D.; Klinefelter, A.; Nagaraju, M.; Boley, J.; Pandey, J.; Shrivastava, A.; Carlson, E.J.; et al. A Batteryless 19µW MICS/ISM-Band Energy Harvesting Body Sensor Node SoC for ExG Applications. *IEEE J. Solid-State Circuits* 2013, 48, 199–213.

- [1.19] David D. Wentzloff, "Low Power Radio Survey," [Online]. www.eecs.umich.edu/wics/ low\_power\_radio\_survey.html

- [1.20] Kosari, A.; Breiholz, J.; Liu, N.; Calhoun, B.H.; Wentzloff, D.D. A 0.5 V 68 nW ECG Monitoring Analog Front-End for Arrhythmia Diagnosis. J. Low Power Electron. Appl. 2018, 8, 27.

- [1.21] Muller, R.; Gambini, S.; Rabaey, J.M. A 0.013mm2 5μW DC-coupled neural signal acquisition IC with 0.5V supply. IEEE J. Solid-State Circuits 2012, 47, 232–243.

## Chapter 2 Murs Band For Long-Range IoT Communications

As stated in Chapter 1, the four key performance metrics for IoT LPWAN applications are extended range, scalability, low cost, and ultra-low power. This chapter discusses the advantages of MURS frequency band for LPWAN applications and introduces a transmission scheme along with a system level and link budget analysis for the operation on this band as the first demonstration of MURS band potential for LPWAN applications in the literature. Many LPWAN applications such as smart parking, smart agriculture, and smart metering are expected to exchange limited data with low data-rates, and can therefore benefit from operation in the VHF band. VHF band possesses a much better propagation characteristic compared to the higher frequency bands allocated to LPWAN technologies. As an example, according to Hata model [2.1], the path loss (PL) value decreases by about 21 dB when the frequency is lowered from 915 MHz to 151 MHz.

In this chapter the FCC regulations and requirements for operation in the MURS band are discussed. An experimental measurement campaign is carried out in order to analyse the channel characteristics and measure the PL and path loss exponent (PLE) values for different transmission scenarios. We introduce a narrowband transmission scheme in the MURS band as an alternative solution for LPWAN technologies. Finally, a system level and link budget analysis is performed and the proposed long-range transmission scenario in the MURS band is compared with the other LPWAN technologies.

By leveraging ultra-low-power circuit design techniques and low-loss propagation characteristics at the low VHF frequencies, along with the system architecture presented in this chapter, it is shown in the following chapters that we can achieve a significant (90-fold) reduction in the power consumption in our MURS transceiver compared to the existing state-of-the-art commercial solutions, while maintaining similar coverage ranges.

### 2.1. MURS Frequency Band

Unlike other IoT standards that operate in the already crowded ISM bands, MURS operates in five narrowband channels in the VHF band. The FCC authorizes a maximum bandwidth of

Figure 2.1. FCC spectral mask for 151.82-151.94 MHz, and 154.57-154.6 MHz MURS band channels.

11.25 kHz at 151.820, 151.880 and 151.940 MHz channels, and a maximum bandwidth of 20 kHz at 154.570 and 154.500 MHz MURS channels [2.2]. The FCC allows both data and voice communication in MURS band with a maximum transmit power of 2 watts. The high allowable output power and the ability to use high gain antennas, is an advantage over other long-range IoT technologies. Additionally, there is no legislative requirements for duty cycling the data in this band. The FCC authorized transmission mask for the MURS band is depicted in Figure 2.1.

### 2.2. Modulation Scheme

For the MURS band long range communication, we propose an adjustable modulation scheme, enabling adaptive modulations [2.3]. It uses single carrier as well as multi-carrier modulations to compensate for multipath events. The single-carrier communication is based on binary phase-shift keying (BPSK) modulation that uses narrowband 10 kHz sub-carriers at any of the MURS channels. By choosing 10 kHz channel bandwidths, we are able to use a total of five channels to transmit a maximum allowable power of 33 dBm at a data rate of 5 kbps per channel. Figure 2.2 shows the channel allocation of the proposed single carrier modulation scheme for long-range low data rate applications.

In order to support bandwidth hungry use cases in dense IoT applications, we have also implemented an orthogonal frequency division multiplexing (OFDM) multi-carrier modulation in the MURS band. The multi-carrier modulation approach is based on compromising the maximum transmitted power with the goal of achieving higher continuous bandwidths for higher data rate applications and be FCC compliant. By utilizing different numbers of contiguous subcarriers in the MURS band, the multi-carrier modulation allows adaptive modulations based on QPSK, 8-

Figure 2.2. Proposed single-carrier and multi-carrier modulation schemes.

PSK, or 16QAM constellations. An example of such multi-carrier modulation over the higher frequency 154.570 – 154.600 MHz MURS band is shown in Figure 2.2, where by lowering the maximum transmit power to -5 dBm, an 8-PSK constellation points can be mapped to 8 subcarriers with a 10 kHz subcarrier spacing. Additionally, the multi-carrier transmission can be realized at higher transmit power values, by using null subcarriers for the intermediate spaces. This is shown as an example multi-carrier transmission over the three over MURS frequencies in Figure 2.2.

By using this selective modulation technique in MURS band, we are able to achieve longdistance communications at agile data rates of 5-384 kbps (assuming a guard time ratio of <sup>1</sup>/<sub>4</sub>). The feasible coverage range using the mentioned modulation techniques is described in the section 2.3.

### **2.3. MURS band Signal Propagation and Path Loss Measurements**

In order to study the feasibility of MURS band communication for LPWAN applications, PL characterization of MURS band propagation at various common scenarios, such as smart parking, agriculture, and smart metering, is performed. PL represents the signal attenuation between the transmitted signal power and the received signal power. The well-known Friis freespace equation describes this relation as presented in (2.1):

$$P_r = P_t + G_r + G_t - 20 \log_{10}\left(\frac{4\pi}{\lambda}\right) - 10PLE \log_{10}(d)$$

(2.1)

Where  $G_r$  and  $G_t$  are the antenna gains at the receiver and the transmitter respectively,  $\lambda$  is the wavelength (1.98 m at 151 MHz), d is the distance between the transmitter and the receiver, and *PLE* is the path loss exponent. The value of *PLE* is equal to 2 in free-space and for urban scenarios it typically ranges from 2.5 to 4, due to various phenomena like reflection, diffraction, multi-path induced fading, shadowing, etc. To measure the PLE for the aforementioned applications, the power level of the narrowband continuous wave (CW) received signal at 151MHz is measured and the PLE value is extracted from (2-1). Due to multi-path fading, the narrowband received power fluctuates over a small area. In order to mitigate the effect of multi-path fading, the received signal power needs to be averaged along several wavelengths on a linear track for a reliable estimate of the local average power [2.5-2.6]. In the measurement campaign in this work, PL from outdoor base stations to external receivers placed at various locations around the campus is measured for two different indoor and outdoor scenarios. The following sections describe the methodology for measuring PL and PLE as well as descriptions of measurement procedures, sites, and hardware.

#### 2.3.1. Measurement Equipment and Setup

The measurement setup consists of a receiver and a transmitter implemented using universal software radio peripherals (USRP) N210, with WBX USRP daughterboards to generate and receive MURS band signals in the 151 MHz frequency band, as shown in Figure 2.3. The USRPs are connected to omnidirectional, loaded, quarter wavelength antennas (EXR150) with a gain of about -2 dBi and the antennas are tuned to achieve better than 15 dB of measured return loss at the 151 MHz MURS channel. The transmitter power has been adjusted to deliver 21 dBm to the antenna and a laptop computer was used to record the power samples received at the receiver.

Before initiating measurements at each of the measurement sites, calibrations were performed, where the transmitter and the receiver were connected back to back using a calibrated cable bypassing the antennas in order to calculate the overall system gain and installation losses.

Figure 2.3. Outdoor-to-Outdoor measurement scenario and measurement equipment.

#### **2.3.2. Measurement Procedure**

In order to characterize the PL properties for the stated applications in the MURS band, the measurements are performed in two different scenarios, namely, (a) outdoor-to-outdoor propagation, and (b) outdoor-to-indoor propagation scenario.

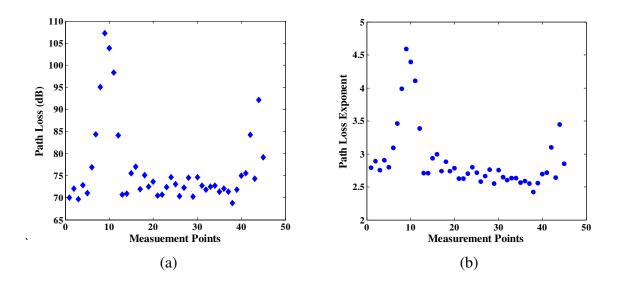

The outdoor-to-outdoor scenario represents typical smart parking or smart agriculture applications where the base station is positioned on a tower and the ground-level sensors are placed within the coverage area of the tower. In this measurement the transmitter is placed at a fixed location 11 m above ground, illuminating the north campus area at the University of Michigan. The CW received power was collected as the receiver (at 1 m above ground) was moved along the 50 $\lambda$  long track for 45 measurement points (Figure 2.3), and at every location the received power is averaged over 500 cycle of the signal. Figure 2.4 shows the measured PL and PLE associated with the CW received power at the 45 measurement points. As shown, for the measurement points nearby large obstacles, such as those near the Lurie Bell Tower and the Electrical Engineering Department, there are higher fluctuations in the measured received power and therefore PL. These

points correspond to the two ends of the measurement track, and are caused mainly due to the fading from these obstacles.

Figure 2.4. (a) PL (b) PLE measurements for outdoor-to-outdoor measurement scenario

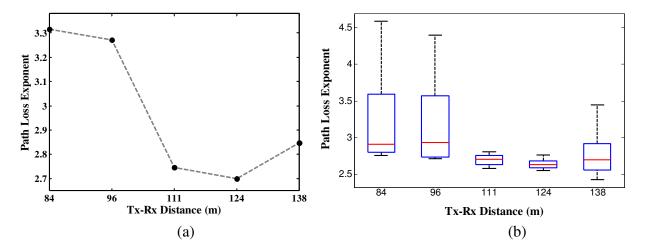

As mentioned before, in order to eliminate the effect of multi-path fading, the received power collected along the linear path has been averaged over every  $10\lambda$  distanced measurements. Figure 2.5 presents the average path loss exponents measured over the aforementioned test scenario. Based on these measurements, the MURS band propagation exhibits an average PLE of

Figure 2.5. (a) Averaged PLE for selected distances for outdoor-to-outdoor scenario, (b) PLE distribution representation using box and whisker plots

2.9 with a standard deviation of 0.3 for outdoor-to-outdoor communication scenarios in environments similar to university campuses.

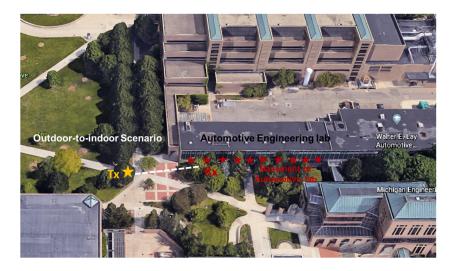

The second measurement scenario is the outdoor-to-indoor scenario representing typical smart metering applications. In these applications the meters are often placed underground or inside buildings and the base stations are usually located outdoors on street-level mountings such as building rooftops or street lamps. Since the wireless sensors are placed indoors or underground for these applications, the system experiences more attenuation due to building penetration and installation losses.

In our measurements we have positioned the transmitter outside of the Electrical Engineering Department (1 m above ground), as shown in Figure 2.6, and the receiver is placed in the basement of the Automotive Engineering Lab. Similar to the outdoor-to-outdoor scenario, the

Figure 2.6. Outdoor-to-Indoor measurement scenario

|         | Mean | Standard Deviation |

|---------|------|--------------------|

| PL (dB) | 77.8 | 1.7                |

| PLE     | 4.7  | 0.12               |

Table 2.1. Measured mean value and the standard deviation value for PL and PLE foroutdoor-to-indoor scenario.

received power is measured at several adjacent locations in the basement with  $1\lambda$  displacement, and the received power values have been averaged accordingly in order to mitigate the fast-fading effects. Table 2.1 summarizes the measured PL and PLE for this scenario, where a PLE of 4.7 is reported.

## 2.4 Link Budget and System Level Analysis