# Design of Detectors and Decoders for MIMO Wireless Systems

by

Wei Tang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2019

Doctoral Committee:

Associate Professor Zhengya Zhang, Chair Professor Michael P. Flynn Associate Professor Justin C. Kasper Assistant Professor Hun-Seok Kim Wei Tang

weitang@umich.edu

ORCID iD: 0000-0001-5204-9728

© Wei Tang 2019

To my family and friends for their love and support

## ACKNOWLEDGEMENTS

I would like to thanks to my advisor, Professor Zhengya Zhang for his valuable support and guidance. He has been give me great advice, encouragement and inspiration over the years of my PhD life; And I would like to thanks to Professor Michael Flynn, Justin Kasper and Hun-Seok Kim for serving on my dissertation committee and providing valuable feedback;

I am lucky to meet and work with my fellow colleagues in my research group. Thanks to Thomas, Chester, Sung-Gun, Teyuh, Jie-Fang and Shiming, Phil, Chia-Hsiang, Youn Sung for providing a fun and healthy environment in the office; we have had many inspirational discussions about research problems and nice chat about daily life. Also, I would like to thanks to the collaborators at Lund University, Professor Viktor wall, Professor Liang Liu, Hammenth, Rakesh, and Farrokh for being so kind and helpful when I visiting there.

Last but not least, I want to express my deepest appreciation to my family in Taiwan for their unconditional love and support.

# TABLE OF CONTENTS

| DEDICATIO   | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ii                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| ACKNOWLE    | DGEMENTS i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ii                                         |

| LIST OF FIG | URES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ii                                         |

| LIST OF TAI | BLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | х                                          |

| LIST OF AB  | BREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ci                                         |

| ABSTRACT    | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                          |

| CHAPTER     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

| I. Intro    | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                          |

| 1.1<br>1.2  | 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{2}{4}$                              |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6<br>6                                     |

| 1.3         | 1 ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                          |

| II. MMS     | E-NBLDPC Iterative Detector and Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                          |

| 2.1         | 2.1.1 MMSE-PIC Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 1 \\ 2 \\ 3 \end{array}$ |

| 2.2         | Detector-Decoder Interface and Optimization       1         2.2.1       Converting Soft Symbols to LLRV       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5<br>5<br>9                                |

| 2.3         | SISO MMSE-PIC Detector    2      2.3.1    Tandem Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2<br>3<br>4                                |

| 2.4         | 2.3.3 Interleaving Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{4}{6}$                              |

|             | server and the server | •                                          |

|        |        | 2.4.1 High-throughput Fully Parallel Architecture                                                | 28 |

|--------|--------|--------------------------------------------------------------------------------------------------|----|

|        |        | 2.4.2 Skimmed Check Node with Data Forwarding                                                    | 29 |

|        |        | 2.4.3 Variable Node with Data Reallocation and Forwarding                                        | 31 |

|        | 2.5    | Low Power Techniques–Clock Gating Exploiting Regular Mem-                                        |    |

|        |        | ory Access                                                                                       | 33 |

|        | 2.6    | Chip Measurement Results                                                                         | 34 |

|        | 2.7    | Summary                                                                                          | 38 |

| III. I | Low-c  | complexity Message-Passing Massive MIMO Detector .                                               | 39 |

|        | 3.1    | Message-Passing Detection Algorithm                                                              | 40 |

|        |        | 3.1.1 Interference-Plus-Noise Approximation and Cancel-                                          |    |

|        |        | lation $\ldots$ | 42 |

|        |        | 3.1.2 Constellation Matching                                                                     | 43 |

|        | 3.2    | Complexity Reduction and Convergence Speedup                                                     | 44 |

|        |        | 3.2.1 Low-Complexity Symbol Hardening                                                            | 45 |

|        |        | 3.2.2 Flooding and Layered Schedules                                                             | 48 |

|        | 3.3    | Architectural Optimization                                                                       | 49 |

|        |        | 3.3.1 Fully Parallel Architecture                                                                | 50 |

|        |        | 3.3.2 4-Layer Architecture                                                                       | 50 |

|        |        | 3.3.3 4-Layer Architecture with 2-way Interleaving                                               | 51 |

|        | 3.4    | Low-Power Techniques                                                                             | 53 |

|        |        | 3.4.1 Adaptive Dynamic Precision Control                                                         | 53 |

|        |        | 3.4.2 Clock Gating Exploiting Regular Memory Access                                              | 54 |

|        |        | 3.4.3 Early Termination                                                                          | 55 |

|        | 3.5    | Chip Measurement Results and Discussion                                                          | 55 |

|        |        | 3.5.1 Voltage Scaling                                                                            | 56 |

|        |        | 3.5.2 Results of Architectural Optimizations                                                     | 57 |

|        |        | $3.5.3$ Comparison $\ldots$                                                                      | 57 |

|        | 3.6    | Summary                                                                                          | 58 |

| IV. 1  | Link-a | adaptive Expectation-Passing Massive MIMO Detector                                               | 60 |

|        | 4.1    | Channel Conditions and Link Adaptive Detection in Practical                                      |    |

|        |        | Massive MIMO Systems                                                                             | 60 |

|        | 4.2    | Expectation Propagation Detection (EPD)                                                          | 63 |

|        |        | 4.2.1 Posterior Calculation with MMSE Estimation                                                 | 65 |

|        |        | 4.2.2 Gaussian Prior Refinement with Moment-Matching                                             | 66 |

|        | 4.3    | Link Adaption in EPD for Energy Efficiency                                                       | 68 |

|        | -      | 4.3.1 Dynamic Dimension Reduction                                                                | 69 |

|        |        | 4.3.2 Early Termination                                                                          | 70 |

|        |        | 4.3.3 Evaluation                                                                                 | 70 |

|        | 4.4    | EPD Architecture                                                                                 | 71 |

|        |        | 4.4.1 Matrix Inversion Architecture                                                              | 72 |

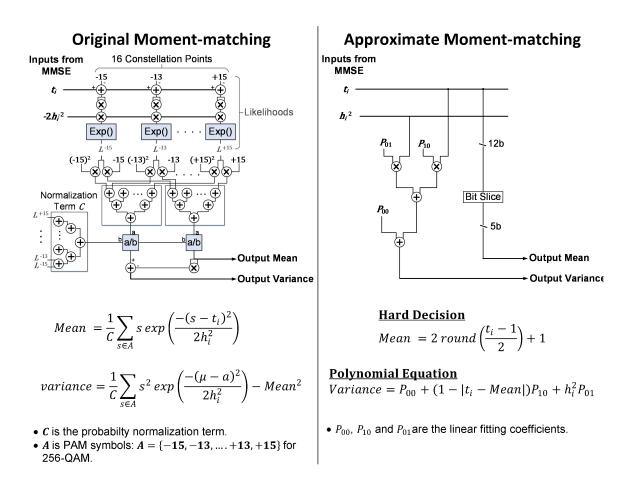

|        |        | 4.4.2 Approximate Moment-Matching (AMM)                                                          | 75 |

|        |        |                                                                                                  |    |

| 4.5 Chip Measurement Results and Discussion                                                 | 78 |

|---------------------------------------------------------------------------------------------|----|

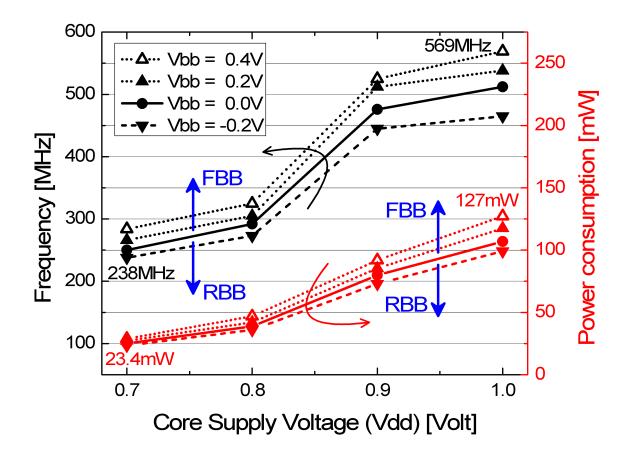

| 4.5.1 Voltage Scaling and Body-biasing                                                      | 78 |

| $4.5.2  \text{Comparison}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 79 |

| 4.6 Summary                                                                                 | 80 |

| V. Conclusion and Outlook                                                                   | 82 |

| BIBLIOGRAPHY                                                                                | 84 |

# LIST OF FIGURES

# Figure

| 1.1  | Global mobile data traffic and connected devices growth trend                  | 1  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Illustration of four configurations of multiple antenna systems: SISO,         |    |

|      | SIMO, MISO and MIMO.                                                           | 2  |

| 1.3  | The data rate of wireless communication standards                              | 3  |

| 1.4  | Illustration of an $N_t \times N_r$ multi-user MIMO system                     | 5  |

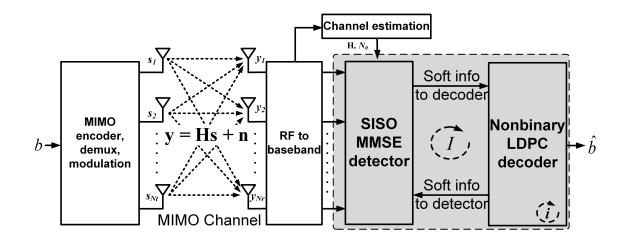

| 2.1  | Illustration of an $N_r \times N_t$ IDD MIMO system with a soft-input-soft-    |    |

|      | output (SISO) MMSE detector and an onbinary LDPC decoder                       | 11 |

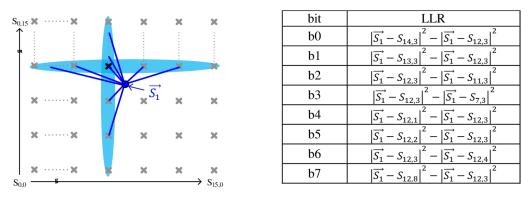

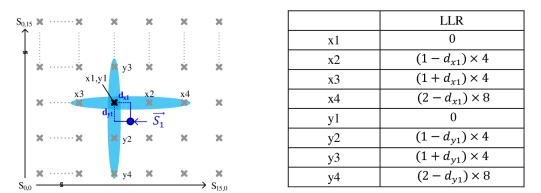

| 2.2  | SISO Detector input soft symbols and variances in (a) binary scheme,           |    |

|      | and (b) proposed nonbinary scheme                                              | 17 |

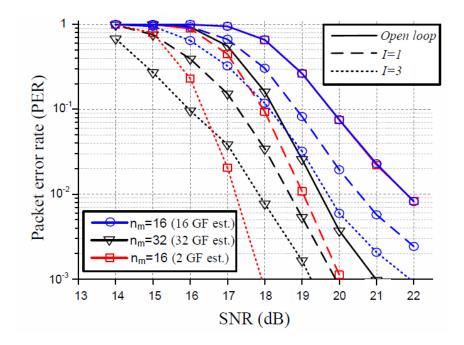

| 2.3  | PER comparison among three setups: (1) 16 GF elements for de-                  |    |

|      | coding and 16 GF elements for soft symbol estimation, $(2)$ 32 GF              |    |

|      | elements for decoding and 32 GF elements soft symbol estimation,               |    |

|      | and $(3)$ 16 GF elements for decoding and only top 2 GF elements for           |    |

|      | soft symbol estimation                                                         | 20 |

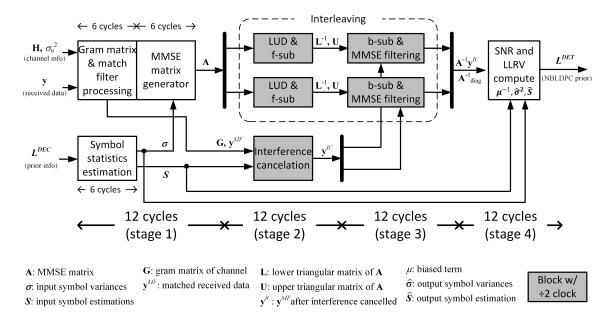

| 2.4  | Design of the MMSE detector in 4 task-based coarse pipeline stages.            |    |

|      | Stage 2 and 3 operate at a $2 \times$ slower clock frequency, and the re-      |    |

|      | maining stages operate at the base clock frequency. $\ldots$ $\ldots$ $\ldots$ | 22 |

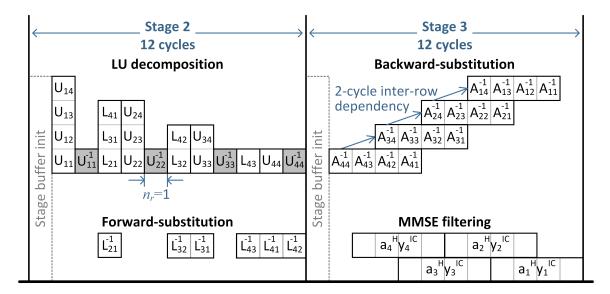

| 2.5  | Tandem scheduling of matrix Inversion and MMSE filtering                       | 24 |

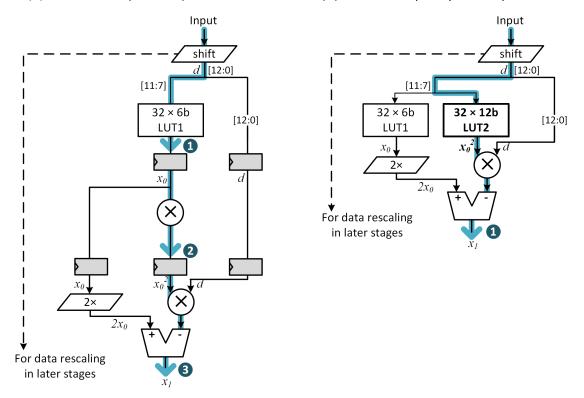

| 2.6  | Reciprocal unit design: (a) baseline 3-cycle design from $[1]$ and (b)         |    |

|      | dual-lookup single-cycle design.                                               | 25 |

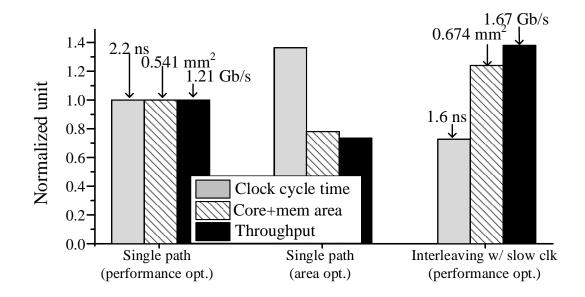

| 2.7  | Comparison between single-path area optimization (middle) and dual-            |    |

|      | path interleaving with slow clock (right)                                      | 27 |

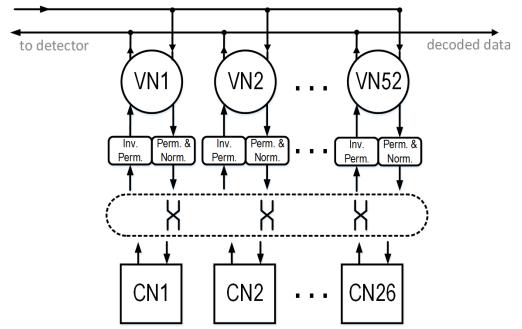

| 2.8  | Fully parallel architecture of Nonbinary LDPC instantiating 52 vari-           |    |

|      | able nodes and 26 check nodes.                                                 | 29 |

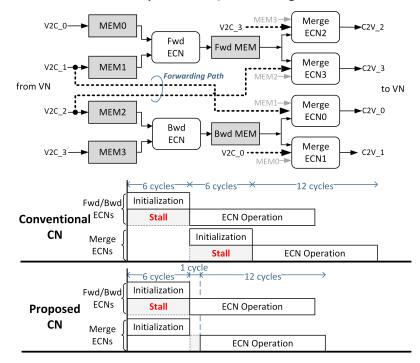

| 2.9  | Proposed CN design with V2C forwarding; the pipeline schedules of              |    |

|      | conventional and proposed CN design.                                           | 30 |

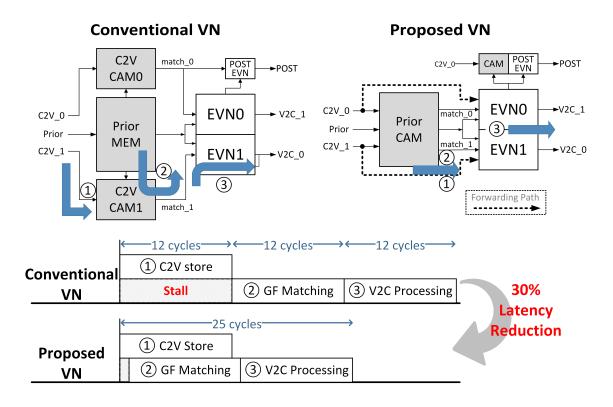

| 2.10 | Data flow and operation latency of the conventional and proposed               |    |

|      | VN designs.                                                                    | 32 |

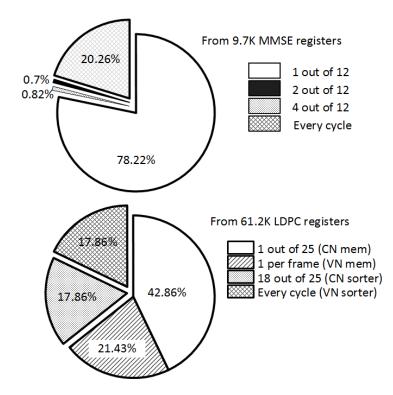

| 2.11 | Power breakdown and the activities of registers.                               | 34 |

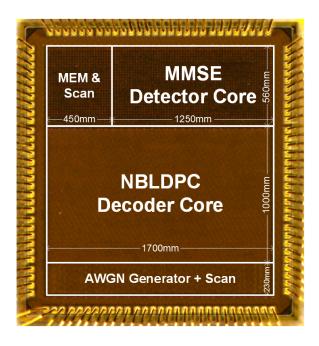

| 2.12 | Chip die photo.                                                                | 35 |

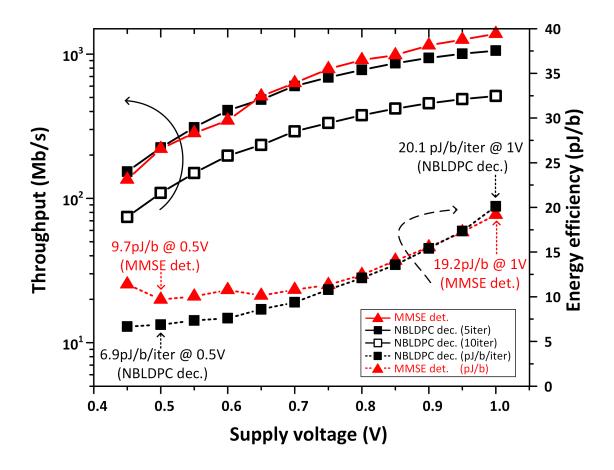

| 2.13 | Measured throughput and energy efficiency with voltage scaling                 | 37 |

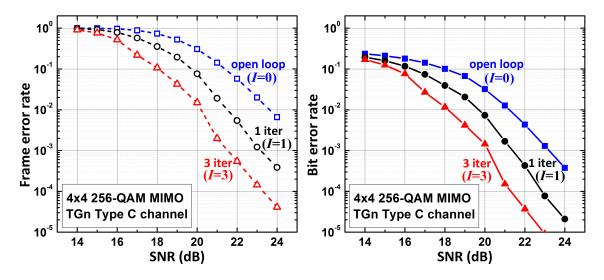

| 2.14 | The bit error rate and frame error rate versus SNR of the proposed MMSE-NBLDPC IDD system                                                                                                                                                                          | 37 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

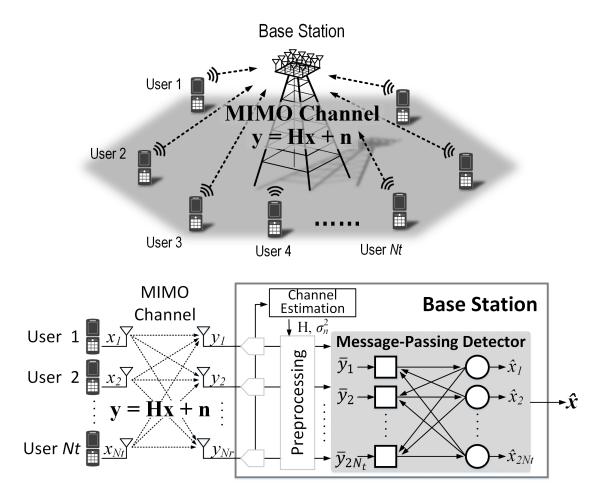

| 3.1  | Illustration of an uplink large-scale MIMO system of $N_t$ single-antenna<br>users and $N_r$ antennas at base station; and a top-level block diagram<br>of a MPD detector.                                                                                         | 41 |

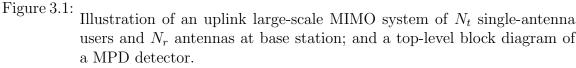

| 3.2  | (a) Full constellation matching $(N_m = \sqrt{M})$ and (b) constellation matching using 2 nearest neighbors $(N_m = 2)$ .                                                                                                                                          | 45 |

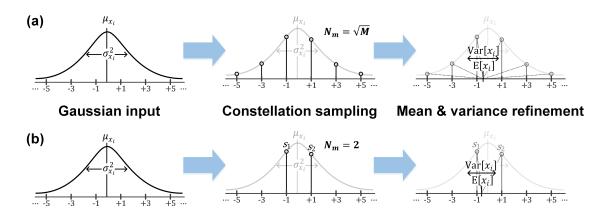

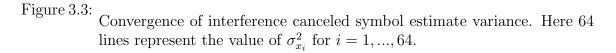

| 3.3  | Convergence of interference canceled symbol estimate variance. Here 64 lines represent the value of $\sigma_{x_i}^2$ for $i = 1,, 64$ .                                                                                                                            | 46 |

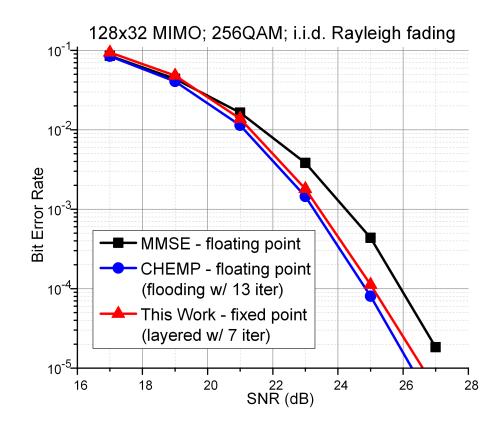

| 3.4  | Bit error rate (BER) performance of $128 \times 32$ uplink MMSE, CHEMP<br>and proposed detections.                                                                                                                                                                 | 48 |

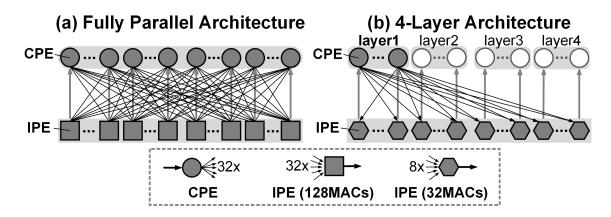

| 3.5  | Architectural optimization from (a) fully parallel architecture using<br>a flooding schedule to (b) block parallel architecture using a layered<br>schedule.                                                                                                       | 50 |

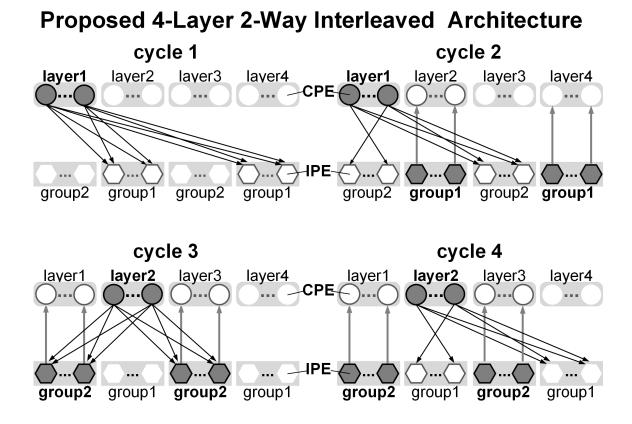

| 3.6  | The proposed 4-layer 2-way interleaved architecture and the data flow of first 4 cycles.                                                                                                                                                                           | 51 |

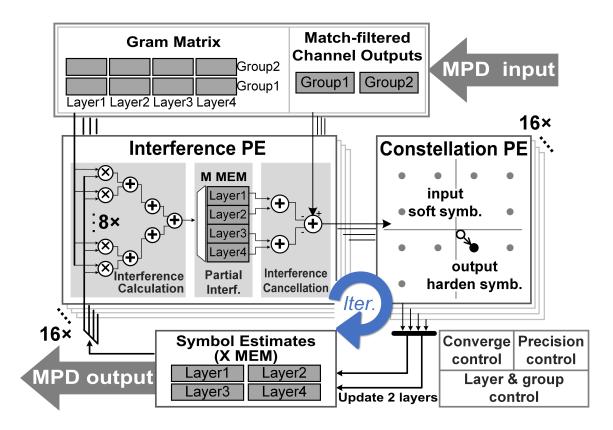

| 3.7  | Detailed block diagram of the proposed message-passing detector us-<br>ing 16 Interference PEs and 16 constellation PEs.                                                                                                                                           | 52 |

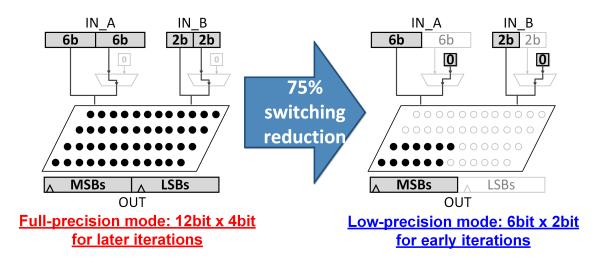

| 3.8  | Multiplier with full precision mode (left) and low precision mode (right).                                                                                                                                                                                         |    |

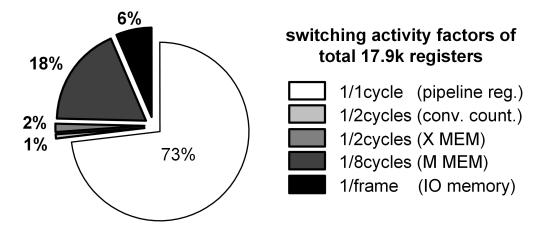

| 3.9  | Power breakdown and the activities of registers                                                                                                                                                                                                                    | 54 |

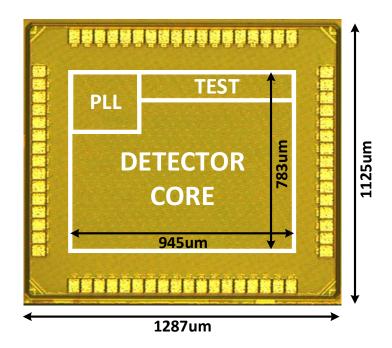

| 3.10 | The proposed MPD Chip photo containing a PLL, testing block and                                                                                                                                                                                                    | 01 |

| 0.10 | detector core.                                                                                                                                                                                                                                                     | 55 |

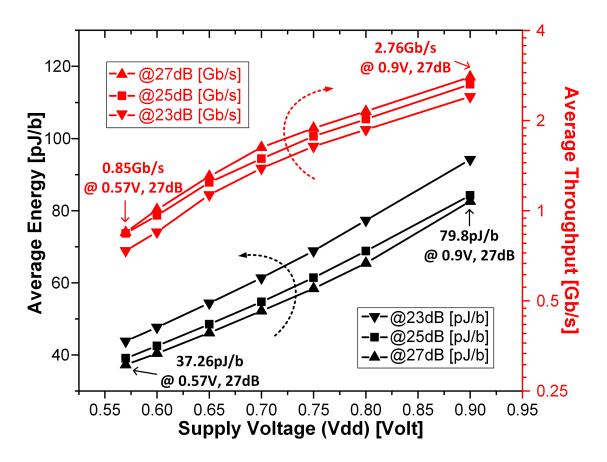

| 3.11 | Measured average throughput (red) and energy efficiency (black) with voltage scaling at different SNRs.                                                                                                                                                            | 56 |

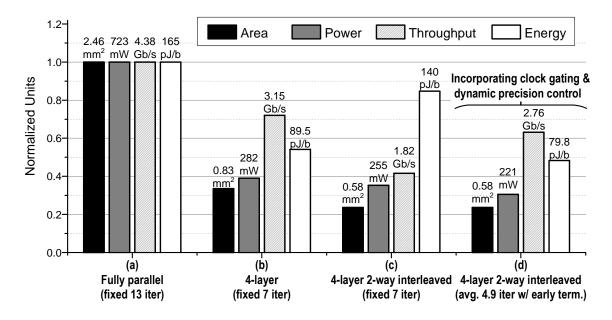

| 3.12 | Measured throughput, power, and energy consumption improvement<br>by proposed dynamic precision control, clock gating and early termi-                                                                                                                             |    |

|      | nation.                                                                                                                                                                                                                                                            | 57 |

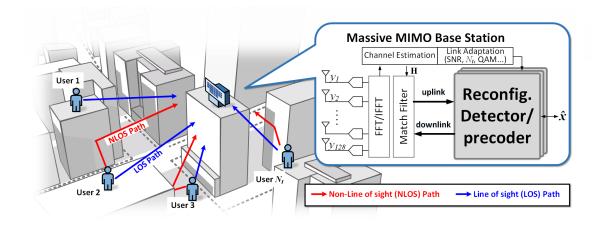

| 4.1  | Illustration of a multi-user massive MIMO system                                                                                                                                                                                                                   | 61 |

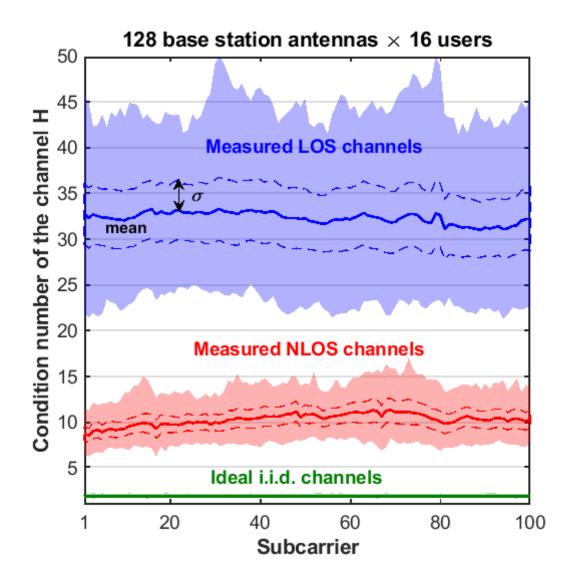

| 4.2  | The condition numbers of measured LOS (blue), NLOS (red) and<br>ideal iid channels with 100 subcarriers. The shade of each channel<br>represent the range, the dashed line is the standard deviations, and<br>the solid line is the means of the condition numbers | 62 |

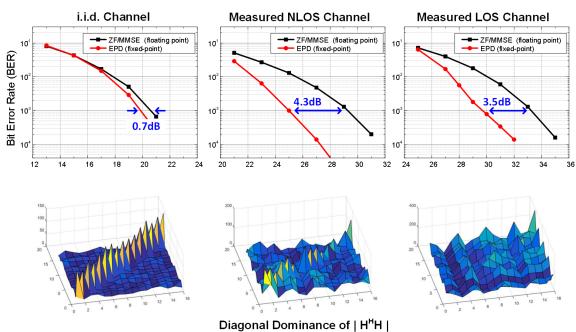

| 4.3  | Top: BER of MMSE detector (black line) and EPD (read line) under different channels. Bottom: the absolute values of Gram matrices                                                                                                                                  | 02 |

|      | $ \mathbf{H}^{H}\mathbf{H} $                                                                                                                                                                                                                                       | 63 |

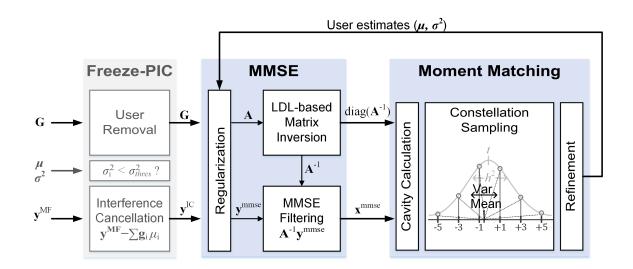

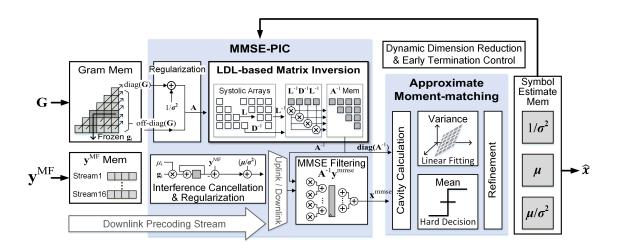

| 4.4  | Block diagram of EPD. The blocks in gray shade perform dynamic dimension reduction and parallel interference cancellation (detailed                                                                                                                                |    |

|      | in 4.3). $\ldots$                                                                                                                                                                                                                                                  | 64 |

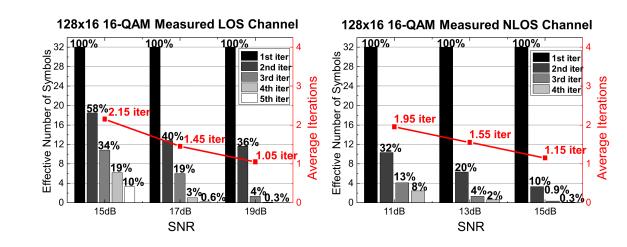

| 4.5  | The effective number of symbols and iterations reduced by dimension<br>reduction and early termination under different SNRs in LOS channel                                                                                                                         |    |

|      | (left) and NLOS channel (right)                                                                                                                                                                                                                                    | 70 |

| 4.6  | Link-adaptive EPD architecture                                                                                                                                                                                                                                     | 71 |

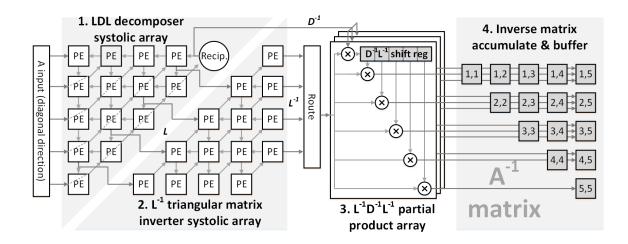

| 4.7  | Example of a $5 \times 5$ matrix inversion micro architecture based on                                                                                                                                                                                             |    |

|      | systolic arrays                                                                                                                                                                                                                                                    | 73 |

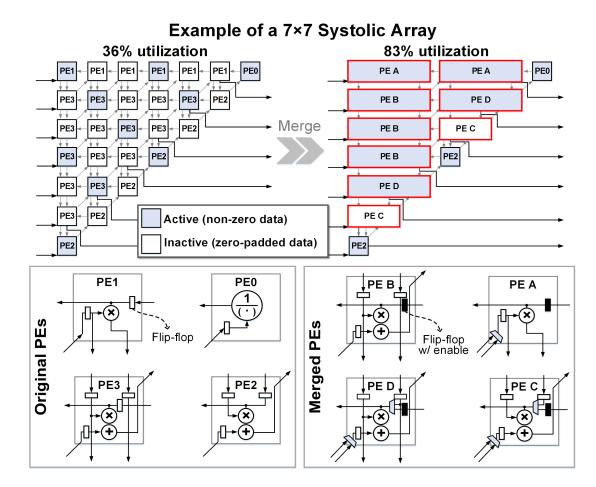

| 4.8  | Condensed LDL systolic array with enhanced utilization and merged  |    |

|------|--------------------------------------------------------------------|----|

|      | PE designs.                                                        | 74 |

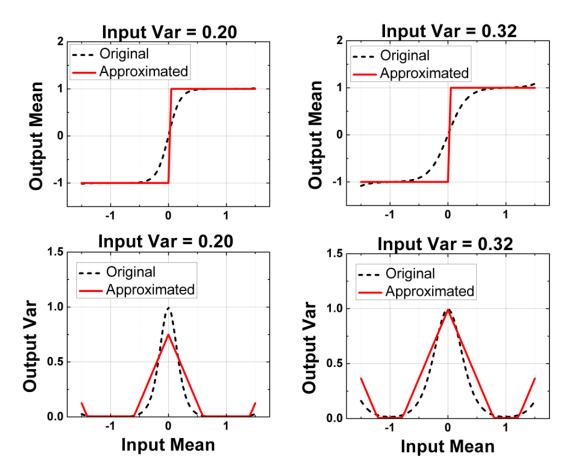

| 4.9  | The approximations of mean and variance under input variance of    |    |

|      | 0.2 and $0.32$ for example                                         | 76 |

| 4.10 | Circuitry implementations and complexities of the original and ap- |    |

|      | proximated moment-matching                                         | 78 |

| 4.11 | Chip features and microphotograph.                                 | 79 |

| 4.12 | Measured frequency and power with different core voltages and body |    |

|      | biases in a 128x16 256-QAM LOS channel                             | 80 |

# LIST OF TABLES

## <u>Table</u>

| 2.1 | Comparsion of Bit-by-Bit Conversion and Direct Conversion from                                                                                |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Soft Symbol to LLRV                                                                                                                           | 17 |

| 2.2 | Comparsion of Bit-by-Bit Conversion and Approximate Direct Con-                                                                               |    |

|     | version from LLRV to Soft Symbol                                                                                                              | 21 |

| 2.3 | Comparison Table of State-of-the-Art MIMO Detectors and LDPC                                                                                  |    |

|     | Decoders                                                                                                                                      | 36 |

| 3.1 | Computational Complexity Comparison of Original, Two-Neighbor                                                                                 |    |

|     | Approximation and Symbol-hardening MPD                                                                                                        | 47 |

| 3.2 | Comparison Table of State-of-the-Art MIMO Detector Designs                                                                                    | 58 |

| 4.1 | Coefficient Values of the Proposed Approximate Moment Matching                                                                                |    |

|     | $(4.24) \ldots \ldots$ | 77 |

| 4.2 | Comparison Table of State-of-the-Art MIMO Detector Designs                                                                                    | 81 |

| 5.1 | Conclusion of the Three MIMO Detector Designs in This Dissertation                                                                            | 82 |

|     |                                                                                                                                               |    |

## LIST OF ABBREVIATIONS

| <b>Gall</b> The old Conclation Farmership Flope | <b>3GPP</b> | The 3rd | Generation | Partnership | Projec |

|-------------------------------------------------|-------------|---------|------------|-------------|--------|

|-------------------------------------------------|-------------|---------|------------|-------------|--------|

AMM Approximated Moment-Matching

**ASIC** Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

**BER** Bit Error Rate

${\bf BS}\,$  Base Station

**b-sub** Backward-Substitution

${\bf CAGR}\,$  Compounded Annual Growth-Rate

**CAM** Content Addressable Memory

**CHEMP** Channel Hardening-Exploiting Message Passing

**CN** Check Node

**CPE** Constellation Processing Element

${\bf CSI}\,$  Channel State Information

**DSP** Digital Signal Processor

**DVFS** Dynamic Voltage Frequency Scaling

**EMS** Extended Min-Sum

**EPD** Expectation Propagation Detection

**EVN** Elementary Variable Node

**FBB** Forward Body Biasing

FD-SOI Fully-Depleted Silicon-on-Insulator

FEC Forward Error Correction

${\bf FER}\,$  Frame Error Rate

FIFO First-In First-Out

**FLOP** Floating Point Operations

**FSM** Finite State Machine

$\mathbf{f}\text{-}\mathbf{sub} \ \ \mathbf{Forward}\text{-}\mathbf{Substitution}$

${\bf GF}\,$  Galois Field

**GSM** Global System for Mobile communications

HSPA+ Evoluted High Speed Packet Access

IAI Inter-Antenna Interference

i.i.d. Independent and Identically Distributed

**IC** Integrated Circuit

**IO** Input Output

**IPE** Interference Processing Element

**ISI** Inter-Symbol Interference

LDPC Low-Density Parity Check

LLR Log-Likelihood Ratio

LLRV Log-Likelihood Ratio Vector

LOS Line-of-Sight

**LTE** Long Term Evolution

LTE-A LTE-Advanced

LUT Look-Up Table

MAC Multiply-Accumulate

$\mathbf{MF}$  Matched Filter

MIMO Multiple-Input Multiple-Output

MISO Multiple-Input Single-Output

ML Maximum Likelihood

- **MMSE** Minimum Mean Square Error

- MPD Message-passing Detection

- **MSE** Mean Square Error

- **NBLDPC** Non-Binary Low-Density Parity Check

- NLOS Non-Line-of-Sight

- ${\bf NS}\,$  Neumann Series

- **OFDM** Orthogonal Frequency-Division Multiplexing

- **PAM** Pulse-Amplitude Modulation

- **PAR** Peak-to-Average Ratio

- **PE** Processing Element

- ${\bf PER}\,$  Packet Error Rate

- **PIC** Parallel Interference Cancellation

- **PLL** Phase Locked Loop

- **QAM** Quadrature Amplitude Modulation

- **RBB** Reverse Body Biasing

- **RF** Radio-Frequency

- **RNG** Random Number Generator

- **RTL** Register-Transfer Level

- ${\bf R}{\bf X}$  Receive

- **SD** Sphere Decoder

- **SER** Symbol Error Rate

- **SIC** Successive Interference Cancellation

- **SIMO** Single-Input Multiple-Output

- SINR Signal-to-Interference and Noise Ratio

- SISO Single-Input Single-Output

- **SNDR** Signal-to-Noise and Distortion Ratio

- **SNR** Signal-to-Noise Ratio

${\bf SQNR}$ Signal-to-Quantization-Noise Ratio

$\mathbf{T}\mathbf{X}$  Transmit

**UMTS** Universal Mobile Telecommunications Service

**UTBB** Ultra Thin Body BOX

${\bf VN}\,$ Variable Node

$\mathbf{WLAN}$  Wireless Local Area Network

**ZF** Zero-Forcing

## ABSTRACT

Multiple-Input-Multiple-Output (MIMO) technology makes use of multiple transmit and receive antennas to improve the spectral efficiency and reliability by spatial diversity and multiplexing. However, MIMO systems require complicated baseband detector designs to cancel the Inter-Antenna Interference (IAI). This work develops high-performance and energy efficient MIMO detectors using state-of-the-art iterative detection and decoding, message-passing detection and expectation-propagation detection approaches.

Iterative Detection and Decoding, or IDD, is an iterative receiver design that improves the error rate performance and relaxes both the detector and decoder designs by iterating the soft decisions between the detector and the decoder. Through iterative interference cancellation and error correction, the Signal-to-Interference-and-Noise Ratio (SINR) can be substantially improved. In this dissertation, a  $2.4 \text{ mm}^2$  $4 \times 4 \text{ MIMO IDD ASIC}$  incorporating Minimum Mean Squared Error (MMSE) detector and Non-Binary Low-Density Parity Check (NBLDPC) decoder is demonstrated. The IDD chip exploits an efficient nonbinary interface between the detector and the decoder to achieve a 1.02 Gb/s throughput, 20 pJ/b energy efficiency and superior detector performance compared to previous detector designs.

The upcoming 5G wireless communication relies on scaling up the numbers of antennas at the base station, using a new technology known as massive MIMO. Massive MIMO often refers to a multiple-user wireless communication system, where the base station is equipped with hundreds of antennas and serves tens of single-antenna user terminals. The large number of antennas entails a high complexity in baseband digital signal processing. To lower the complexity, previously demonstrated massive MIMO systems deployed linear detectors. Despite its simplicity, a linear detector requires expensive matrix inversion operations, the cost of which can become excessive in a massive MIMO system.

In a rich scattering environment, a massive MIMO channel can be modeled as an independently and identically distributed (i.i.d.) Rayleigh fading channel. This favorable property allows us to explore approximate detection algorithms to greatly reduce the computational complexity while still maintaining close-to-optimal BER-SNR performance. This idea is realized and demonstrated in a 0.58 mm<sup>2</sup> 128 × 32 low complexity Message-Passing Detector (MPD) for a massive MIMO base station. With a symbol hardening technique, the complexity of the MPD is reduced by more than 60%. The detector is implemented in a pipelined block-parallel architecture using a layered-grouped schedule to accelerate convergence, enabling an average throughput of 2.76 Gb/s at 221 mW. The chip incorporates adaptive precision control and clock gating to improve energy efficiency to 80 pJ/b.

Practical massive MIMO channels for mobile applications are fast varying. From the channel measurement in practical environments conducted by Lund University, it is discovered that the massive MIMO channel could vary and degrade. A highly correlated channel is observed when mobile users are closely deployed in an environment where the line-of-sight (LOS) signal propagation paths dominate. In such a condition, a conventional linear MMSE detector is unable to satisfy the BER-SNR requirement. To address this challenge, a  $2.0 \text{ mm}^2$  iterative expectation-propagation detector (EPD) is presented for a  $128 \times 16$  massive MIMO system supporting up to 256-QAM modulation. Tested with measured channel data, the detector achieves 4.3 dB processing gain over state-of-the-art massive MIMO detectors, enabling 2.7 times reduction in transmit power for battery-powered mobile terminals. The EPD chip uses link-adaptive processing to meet a variety of practical channel conditions with scalable energy consumption. The design is realized in a condensed systolic array architecture and an approximate moment-matching circuitry to reach 1.8 Gb/s at 70.6 pJ/b. The performance and energy efficiency can be tuned over a wide range by the UTBB-FDSOI body bias.

This dissertation studies the NBLDPC decoder and MIMO detector designs for both small-scale and large-scale MIMO system. The cross-domain optimizations from system and algorithm to architecture and circuits led to a highly efficient and adaptive detector and decoder designs to meet the demanding performance requirements of future mobile communication systems.

# CHAPTER I

# Introduction

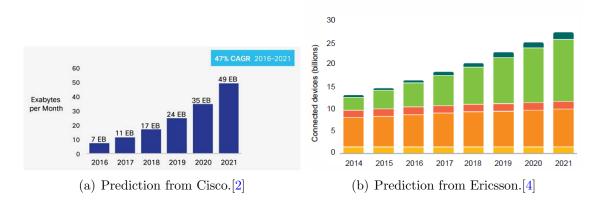

The global data traffic is predicted to have a Compounded Annual Growth-Rate (CAGR) of 47% with 25 billion IoE connected devices by 2021 [2, 3, 4] as shown in Fig. 1.1. It is envisioned that the upcoming 5G wireless communication will meet the traffic demand at a 100 times higher energy efficiency, 10 times higher spectral efficiency and reliability compared to the current 4G standard. Small-scale MIMO and massive MIMO, exploiting the use of multiple numbers of antennas, is a key enabling technology.

Figure 1.1: Global mobile data traffic and connected devices growth trend.

### 1.1 MIMO Technology

Since throughput = spectral efficiency (bits/s/Hz)  $\times$  bandwidth (Hz), one way of increasing data throughput is to increase the number of elements along the spatial dimension by placing multiple antennas at both the transmitting and receiving side of the communication link. This MIMO technology has many advantages: it increases the data throughput [5] and the link reliability by exploiting the link diversity [6] in rich scattering environments.

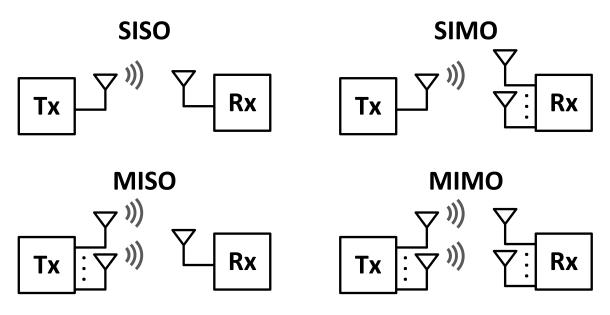

Based on the configurations of the number of transmit (TX) antennas and the number of receive (RX) antennas, MIMO systems can be classified as single-input single-output (SISO), single-input multiple-output (SIMO), multiple-input single-output (MISO), and multiple-input multiple-output (MIMO) systems, as shown in Fig. 1.2.

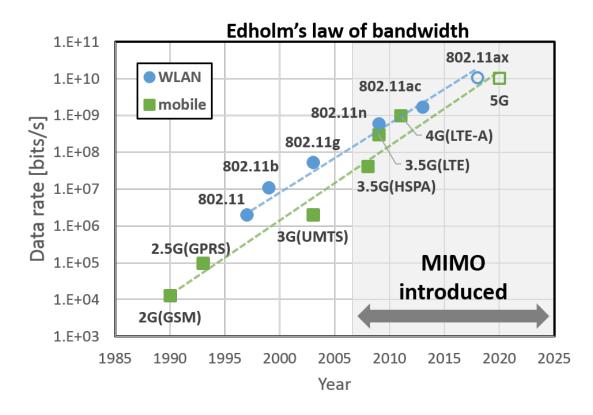

The data rates of wireless communication standards from the second generation (2G) to the fifth generation (5G) are shown in Fig.1.3. MIMO technology has been introduced starting from 3G to satisfy the ever increasing data rate requirement. Recent

Figure 1.2: Illustration of four configurations of multiple antenna systems: SISO, SIMO, MISO and MIMO.

Figure 1.3: The data rate of wireless communication standards.

wireless communication standards such as IEEE 802.11n, 802.11ac, Evoluted High Speed Packet Access (HSPA+) [7], 3GPP Long-Term Evolution (LTE) Advanced Release 10/11 [8], mobile communication, and WiMAX all adopt MIMO communication to increase spectral efficiency and data rate. For example, IEEE 802.11n allows for up to a  $4 \times 4$  antenna configuration (4 transmit and 4 receive antennas); IEEE 802.11ac calls for up to a  $8 \times 4$  antenna configuration and 3GPP LTE Advanced release 10 [8] specifies up to an  $8 \times 8$  antenna configuration. The enhancement in spectral efficiency and higher data rate comes with a significant computational cost: workload profiling indicates that MIMO detection at the receiver can consume a large number of computing cycles in the physical layer baseband processing [9].

The increasing data rates motivate further exploitation of a large number of antennas. As pointed out in [10], the effects of the additive receive noise, the small-scale fading, as well as the inter-user interference could be averaged out by increasing the number of antennas at the base station. Scaling up MIMO provides higher degrees of freedom in the spatial domain to increase the overall spectral efficiency and reliability. A massive MIMO is a system equipped with a larger number of antennas (in hundreds) at the base station. Such a massive MIMO system typically serves multiple user terminals (in tens) using the same time-frequency resources.

Another important distinction of a massive MIMO system is that it exploits the multi-path components are exploited in massive MIMO to improve the signal strength at the receiver. This is possible due to the high spatial resolution and array gains in massive MIMO with a large number of antennas at the base station. Moreover, massive MIMO allows processing efforts to be concentrated at the base station side, while battery-operated mobile terminals can have low hardware cost and power consumption.

### **1.2 MIMO Signal Detection**

One of the most complex and energy consuming blocks in a MIMO system is the signal detection at the receiver. This is because transmitting multiple streams simultaneously through a wireless channel would result in the crosstalk of the signals at the receiver. Therefore, signal processing needs to be performed to separate the data streams, which is generally termed MIMO detection.

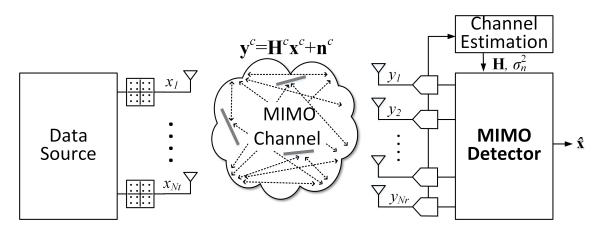

Consider a MIMO system as shown in Fig. 1.4 where  $N_t$  transmit antennas communicate to a receiver with  $N_r$  antennas and each antenna transmits an M-Quadrature Amplitude Modulation (QAM) symbol at each channel use. The system model is given in (1.1), where  $\mathbf{x}^c = [x_1^c, x_2^c, ..., x_{N_t}^c]^{\mathsf{T}}$  is the transmitted vector of QAM symbols,  $x_i^c \in \tilde{\mathcal{A}}$  is represented by a complex value, and  $|\tilde{\mathcal{A}}| = M$ .  $\mathbf{H}^c$  is a  $N_r \times N_t$ complex matrix representing a memoryless flat-fading complex MIMO channel. For an i.i.d. Rayleigh channel, each coefficient of  $\mathbf{H}^c$  is drawn according to a complex zero-mean unit-variance Gaussian distribution. Assume the perfect channel state in-

Figure 1.4: Illustration of an  $N_t \times N_r$  multi-user MIMO system.

formation (CSI) at the receiver and  $\mathbf{H}^c$  is known at the receiver. The channel output is  $\mathbf{y}^c \in \mathbb{C}^{N_r}$ , where

$$\mathbf{y}^c = \mathbf{H}^c \mathbf{x}^c + \mathbf{n}^c \tag{1.1}$$

and  $\mathbf{n}^c \in \mathbb{C}^{N_r}$  is an additive white circular-symmetric complex Gaussian noise vector with independent zero-mean components and the  $N_0$ -variance. According to this model, the Signal-to-Noise Ratio (SNR) is defined as:

$$SNR(dB) = 10 \log_{10}(N_t E_s / N_0)$$

(1.2)

where  $E_s$  is the constellation average energy in Joules.

The complex values in (1.1) can be written in the real domain as:

$$\begin{bmatrix} \Re(\mathbf{y}^c) \\ \Im(\mathbf{y}^c) \end{bmatrix} = \begin{bmatrix} \Re(\mathbf{H}^c) & -\Im(\mathbf{H}^c) \\ \Im(\mathbf{H}^c) & \Re(\mathbf{H}^c) \end{bmatrix} \begin{bmatrix} \Re(\mathbf{x}^c) \\ \Im(\mathbf{x}^c) \end{bmatrix} + \begin{bmatrix} \Re(\mathbf{n}^c) \\ \Im(\mathbf{n}^c) \end{bmatrix}$$

$$\Rightarrow \mathbf{y} = \mathbf{H}\mathbf{x} + \mathbf{n}, \tag{1.3}$$

where  $\Re(\cdot)$  and  $\Im(\cdot)$  denote the real and imaginary parts, respectively. And note that the real and imaginary part of a QAM symbol are represented by the two underlying Pulse Amplitude Modulation (PAM) symbols from alphabet  $\mathcal{A}$ , i.e.  $\mathbf{x} \in \mathcal{A}^{2N_t}$ , where  $|\mathcal{A}| = \sqrt{M}.$

#### 1.2.1 Maximum Likelihood Detection

Upon observing  $\mathbf{y}$ , the Maximum Likelihood (ML) detection enumerates all possible combinations of the transmitted constellation symbols and find the best (mostlikely) combination as the estimate. The posterior of the estimation is:

$$P(\mathbf{x} \mid \mathbf{y}, \mathbf{H}) \propto P(\mathbf{y} \mid \mathbf{x}, \mathbf{H}) P(\mathbf{x}).$$

(1.4)

Here each of the prior is uniformly and discretely distributed over the QAM constellation, thus the overall prior  $P(\mathbf{x})$  spans a space of  $\mathcal{A}^{2N_t}$ . The maximum likelihood estimates can be formulated as follows:

$$\mathbf{x}^{ML} = \underset{\mathbf{x} \in \mathcal{A}^{2N_t}}{\arg \max} P(\mathbf{y} \mid \mathbf{x}, \mathbf{H}).$$

(1.5)

Maximum likelihood detection can achieve the optimal error rate performance, however, the complexity of such an enumeration procedure increases exponentially with the number of transmit antennas  $(N_t)$  and the QAM order (M). Many researchers have worked on efficient and reduced search space for MIMO detection, such as sphere decoding [11, 12, 13, 14] and Tabu search [15, 16], to manage the implementation cost in hardware. However, these search-based detections still scale poorly, especially in a large-scale MIMO system using more than 8 antennas.

#### 1.2.2 Minimum Mean Equared Error (MMSE) Detection

A low-complexity linear detection, such as Minimum Mean Squared Error (MMSE) or Zero-Forcing (ZF), has sub-optimal performance in terms of error rate. To avoid exhaustive enumeration, an MMSE detection approximates the prior in (1.4) by a continuous Gaussian distribution with zero-mean and a variance equal to the symbol energy  $E_s$ :

$$P(\mathbf{x} \mid \mathbf{y}, \mathbf{H}) = \mathcal{N}(\mathbf{y}; \mathbf{H}\mathbf{x}, N_0 \mathbf{I}) \prod \mathcal{N}(x_i; 0, E_s).$$

(1.6)

With the continuous Gaussian approximation of the prior, the estimates having the minimum mean squared error can now be calculated as:

$$\mathbf{x}^{MMSE} = (\mathbf{H}^{H}\mathbf{H} + N_0/E_s\mathbf{I})^{-1}(\mathbf{H}^{H}\mathbf{y})$$

=  $\mathbf{A}^{-1}\mathbf{y}^{MF}$ , (1.7)

where we define the MMSE filtering matrix  $\mathbf{A}^{-1}$  and matched-filtered received signals  $\mathbf{y}^{MF}$ . The result of MMSE detection are "soft" symbols, i.e. the *i*-th estimate is a Gaussian distribution with a mean of  $x_i^{MMSE}$  and a variance of  $A_{ii}^{-1}$ .

There is an inherent trade-off between accuracy and complexity when implementing a MIMO detector. Our design goal is to achieve an acceptable accuracy with as low complexity as possible. Different methods will be explored in this dissertation: in Chapter II, an iterative detection and decoder (IDD) technique is investigated to improve detection and decoding accuracy while simplifying both detector and decoder designs; in Chapter III, a message-passing detection (MPD) is designed to take advantage of an i.i.d. Rayleigh massive MIMO channel to reduce complexity; and in Chapter IV, a versatile expectation-propagation detection (EPD) is adopted to ensure detection accuracy in highly correlated massive MIMO channels with adaptive power consumption.

### **1.3** Dissertation Outline

The MIMO signal detector is one of the most energy- and latency-critical parts in the MIMO baseband digital processing. The complexity of the detector grows with the scale of a MIMO system. This dissertation focuses on efficient MIMO detector designs for both small-scale and large-scale MIMO systems. In Chapter II, an MMSE-NBLDPC IDD design for a  $4 \times 4$  MIMO system is presented. The IDD technology enables competitive BER-SNR performance with a lowcomplexity MMSE detector and a nonbinary LDPC decoder.

In Chapter III, a low-complexity message-passing detector (MPD) design for a  $128 \times 32$  massive MIMO system is presented. With the i.i.d. Rayleigh channel assumption in a massive MIMIO system, the proposed high-throughput MPD design can be substantially simplified to achieve high energy efficiency and the optimal detection performance.

In Chapter IV, a link-adaptive close-to-optimal iterative expectation-propagation detector (EPD) for practical massive MIMO systems is presented. The design is able to adapt to different practical channel scenarios from the worst-case highly correlated channel to the best-case i.i.d. channel.

In Chapter V, we conclude this dissertation and provide outlooks for future research in massive MIMO processor design.

## CHAPTER II

# **MMSE-NBLDPC** Iterative Detector and Decoder

The latest MIMO wireless systems have adopted iterative detection and decoding (IDD) to reduce the signal-to-noise ratio (SNR) required for a reliable transmission. An IDD system consists of a soft-in soft-out (SISO) detector to cancel interference, and a SISO forward error correction (FEC) decoder to remove errors. The two blocks exchange soft information to improve the frame error rate (FER) iteratively.

State-of-the-art IDDs based on sphere decoding (SD) and binary low-density parity-check (LDPC) FEC have been demonstrated in [17], [18] for up to 4x4 64-QAM MIMO system, achieving up to 396Mb/s in detection throughput [17] and 586Mb/s in decoding throughput [18]. As antenna configuration continue to scale beyond  $4\times4$  and modulation order increases above 64-QAM, the complexity of a SISO SD detector is expected to grow exponentially, making it impractical. A SISO minimum mean square error (MMSE) detector [1] features a lower complexity and a higher throughput than a SISO SD detector. An MMSE detector can be more easily scaled to support a large antenna configuration and a high order modulation. The drawback of an MMSE detector is its lower detection performance (measured in error rate). However, an IDD system potentially overcomes this weakness by iteration.

Recent IDD designs have used binary low-density parity-check (LDPC) codes for FEC [17, 18, 19]. However, binary LDPC codes are not matched to high-order modulation and a loss is expected. Compared to binary LDPC codes, nonbinary LDPC (NBLDPC) codes defined over Galois field (GF) outperform binary LDPC codes of comparable block length in coding gain [20]. Even at a moderate block length, an NBLDPC code offers a superior coding gain, and the coding gain improves with a larger GF size.