## Securing Safety Critical Automotive Systems

$\mathbf{b}\mathbf{y}$

### Ahmad MK. Nasser

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Information Science) in the University of Michigan-Dearborn 2019

#### **Doctoral Committee:**

Associate Professor Di Ma, Chair Associate Professor Jinhua Guo Assistant Professor Bochen Jia Professor Brahim Medjahed Ahmad MK. Nasser ahmadnas@umich.edu

ORCID iD 0000-0001-8318-7082

© Ahmad MK. Nasser 2019

### **DEDICATION**

This dissertation is dedicated first to my mom and dad: Amal Awada and Mohamad-Kheir Nasser. You have taught me from a young age not only to have big dreams, but also to have the tenacity to pursue them. I also like to dedicate this to my wife, Batoul Abdallah. Your love and support gave me the necessary strength to persevere through the arduous journey of combining a full time career with challenging academic research. Last but not least, I like to dedicate this to my children: Yahya and Dalia. Although, you gave me many reasons to be distracted, I want this achievement to motivate you in your future endeavors to always challenge yourself and aim to leave a mark in whatever you choose to do.

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Dr. Di Ma, for her guidance, insights and valuable feedback when reviewing my work. It was her lectures on network security that initially sparked in me the desire to learn more about the intersection of security and safety. Thanks to her advice, I was later able to refine my research skills when looking at problems, not only as an engineer seeking solutions, but also as a researcher looking for answers. Our collaboration made it possible for this work to be impactful. I also would like to express my gratitude to my committee members, Dr. Brahim Medjahed, Dr. Jinhua Guo, and Dr. Bochen Jia, for the time they spent in reviewing my work and the valuable feedback they provided. In addition, this work would not have been possible without the support of numerous colleagues and collaborators who have given me their advice and technical opinions. Special thanks to the Renesas HSM firmware team (Raymon Abdelmassih, Shem Rajiah, Li Li, Cristian Man, and Plamen Stoyanov) for their support. I am also grateful to Renesas for providing me the hardware and software to carry out my experiments as well as the support in pursuing this work, with special thanks to Paul Kanan, Yasuhisa Shimazaki, and Takeo Tomokane. To Eric Winder, Wonder Gumise, and Dr. Matthias Krauledat, I am grateful for our technical debates and discussions which allowed me to refine my ideas for the larger academic audience. Last but not least, I like to thank Dheeraj Sharma, Chris Thibeault, and Kyle Taylor from Elektrobit for their support with the AUTOSAR software stack.

# TABLE OF CONTENTS

| DEDICATIO                       | N                                       | ii                                     |

|---------------------------------|-----------------------------------------|----------------------------------------|

| ACKNOWLE                        | DGEMENTS                                | iii                                    |

| LIST OF TAI                     | BLES                                    | vii                                    |

| LIST OF FIG                     | URES                                    | viii                                   |

| ABSTRACT                        |                                         | Х                                      |

| CHAPTER                         |                                         |                                        |

| I. Introd                       | luction                                 | 1                                      |

| 1.1<br>1.2                      | Contributions                           | 2                                      |

| II. Backg                       | round and Related Work                  | 5                                      |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | AUTOSAR                                 | 5<br>6<br>8<br>9<br>13                 |

| III. Safety                     | Driven Security Analysis: A System View | 15                                     |

| 3.1<br>3.2<br>3.3<br>3.4        | Introduction                            | 15<br>16<br>17<br>18<br>21<br>24<br>25 |

|           | 3.4.3 Security Requirements                        |

|-----------|----------------------------------------------------|

|           | 3.4.4 Impact on Safety Architecture                |

| 3.5       | Comparison to UPTANE                               |

| 3.6       | Conclusion                                         |

|           |                                                    |

| . AUT     | OSAR Safety and Security: Synergies and Conflicts  |

| 4.1       | Introduction                                       |

| 4.2       | Attack Model                                       |

| 4.3       | Survey of AUTOSAR Safety Features                  |

|           | 4.3.1 End to End Library                           |

|           | 4.3.2 AUTOSAR OS Protections                       |

|           | 4.3.2.1 Memory Protections                         |

|           | 4.3.2.2 Timing Protections                         |

|           | 4.3.2.3 Hardware Protection                        |

|           | 4.3.3 Watchdog Manager                             |

|           | 4.3.4 Core Test                                    |

|           | 4.3.5 RAM Test                                     |

|           | 4.3.6 Flash Test                                   |

| 4.4       | Summary of Security Gaps                           |

| 4.5       | Exploiting Security Gaps                           |

|           | 4.5.1 Message Loss Attack                          |

|           | 4.5.1.1 Security Countermeasures                   |

|           | 4.5.2 Task Execution Budget Attack                 |

|           | 4.5.2.1 Security Countermeasures                   |

|           | 4.5.3 Demonstrative Attacks                        |

| 4.6       | Extending Safety Mechanisms for Security           |

|           | 4.6.1 Stack Usage Monitoring                       |

|           | 4.6.2 RAM Execution Prevention                     |

|           | 4.6.3 Flow Integrity Protection                    |

|           | 4.6.4 OsTiming Protections                         |

|           | 4.6.5 Hardware Resource Protection                 |

|           | 4.6.6 Demonstrative Protections                    |

|           | 4.6.6.1 Stack Overflow Protection                  |

|           | 4.6.7 Recommendations for AUTOSAR Protections      |

| 4.7       | Conclusion                                         |

|           |                                                    |

| . SecM    | IonQ: Security Monitoring of AUTOSAR Based Systems |

| 5.1       | Introduction                                       |

| 5.1 $5.2$ | Attack Goal and Threat Model                       |

| 5.3       | Background and Related Work                        |

| ა.ა       |                                                    |

|           | 0 1                                                |

| E 1       | 5.3.2 Hardware Based Security Monitors             |

| 5.4       | Our Framework                                      |

|                                      | 5.4.1 Secure Execution Environment                                          | 72                                                                        |

|--------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                      | 5.4.2 Secure Checkpoint Buffer                                              | 72                                                                        |

|                                      | 5.4.3 Secure Interruption                                                   | 73                                                                        |

|                                      | 5.4.4 Trusted Safety Function                                               | 74                                                                        |

| 5.5                                  | Design of SecMonQ                                                           | 75                                                                        |

|                                      | 5.5.1 Time Checker                                                          | 76                                                                        |

|                                      | 5.5.2 Flow Checker                                                          | 77                                                                        |

|                                      | 5.5.2.1 Path Definition and Checkpoint Selection                            | n 77                                                                      |

|                                      | 5.5.2.2 Flow Violation Detection                                            | 79                                                                        |

|                                      | 5.5.3 Firmware Integrity Checker                                            | 80                                                                        |

|                                      | 5.5.4 CAN Integrity Checker                                                 |                                                                           |

|                                      | 5.5.5 Policy Handler                                                        | 86                                                                        |

|                                      | 5.5.6 Safety Considerations                                                 | 87                                                                        |

| 5.6                                  | Case Study: Defeating the CAN Masquerading Attack                           | 88                                                                        |

|                                      | 5.6.1 Experimental Setup: Time and Flow Monitors                            | 90                                                                        |

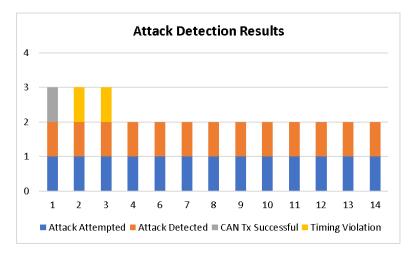

|                                      | 5.6.1.1 Results                                                             | 92                                                                        |

|                                      | 5.6.2 Experimental Setup: CAN Integrity Monitor                             | 97                                                                        |

|                                      | 5.6.2.1 Results                                                             | 97                                                                        |

| 5.7                                  | Discussion                                                                  | 99                                                                        |

| 5.8                                  | Conclusion                                                                  | 101                                                                       |

| 6.1                                  | lability: Adding Trust without Sacrificing Performance  Introduction        | 103                                                                       |

| 6.2                                  | Related Work                                                                | 100                                                                       |

| _                                    |                                                                             | 105                                                                       |

| 6.3                                  |                                                                             | 105<br>108                                                                |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme                    | 108                                                                       |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108                                                                |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108                                                         |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108<br>109                                                  |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108<br>109<br>112                                           |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108<br>109<br>112<br>116                                    |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108<br>109<br>112<br>116<br>117                             |

| 6.3                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>108<br>109<br>112<br>116<br>117                             |

|                                      | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>109<br>112<br>116<br>117<br>118<br>119                      |

| 6.4                                  | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>109<br>112<br>116<br>117<br>118<br>119                      |

| 6.4<br>6.5                           | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>109<br>112<br>116<br>117<br>118<br>119<br>120               |

| 6.4<br>6.5<br>6.6                    | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>109<br>112<br>116<br>117<br>118<br>119<br>120<br>126<br>128 |

| 6.4<br>6.5<br>6.6<br><b>II. Conc</b> | PBASS: Probabilistic Boot Authentication Sampling Scheme 6.3.1 Threat Model | 108<br>108<br>109<br>112<br>116<br>117<br>118<br>119<br>120<br>126<br>128 |

# LIST OF TABLES

| <u>Table</u> |                                                            |     |

|--------------|------------------------------------------------------------|-----|

| 3.1          | Simplified Hazard Analysis for OTA                         | 23  |

| 3.2          | Safety Driven Attacker Model                               | 25  |

| 3.3          | Attacks with safety goal violations                        | 26  |

| 3.4          | Attacks with safety goal violations                        | 28  |

| 4.1          | Survey of AUTOSAR safety mechanisms                        | 33  |

| 4.2          | Applying SDAS to E2E Library                               | 34  |

| 4.3          | SDAS results against AUTOSAR Safety Goals                  | 45  |

| 4.4          | CAN FD frame time in $\mu s$ based on 64 byte DLC          | 54  |

| 5.1          | Frame transmission times for various data lengths          | 84  |

| 5.2          | Actions that SecMonQ can take upon policy violation        | 87  |

| 5.3          | Checkpoint reporting overhead at host CPU clock of 120Mhz  | 96  |

| 5.4          | Attack results at different attack rates and Frame DLC     | 99  |

| 6.1          | Impact of file size on evasion, $s=15\%$ and $m=512$ bytes | 112 |

# LIST OF FIGURES

| <u>Figure</u> |                                                                       |

|---------------|-----------------------------------------------------------------------|

| 2.1           | Network architecture of a modern vehicle                              |

| 2.2           | Security in-depth concept for advanced vehicle architectures          |

| 2.3           | Evita Medium HSM architecture                                         |

| 3.1           | Architecture of OTA system considered for the security analysis 1     |

| 3.2           | Safety Driven Security Approach process steps                         |

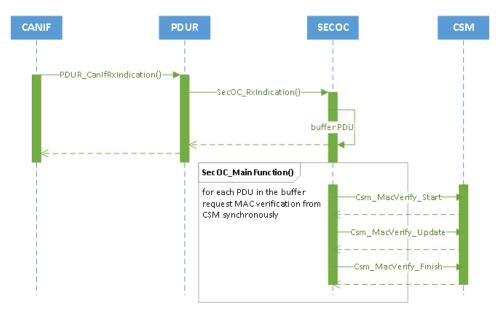

| 4.1           | Data flow from CANIF to the CSM layer for frame authentication . 4    |

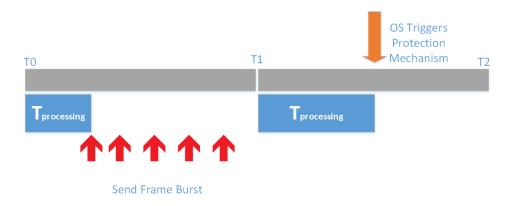

| 4.2           | Triggering the OS protection mechanism                                |

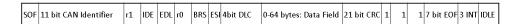

| 4.3           | CAN FD Frame layout, for 64 byte frames CRC is 21 bits long 5         |

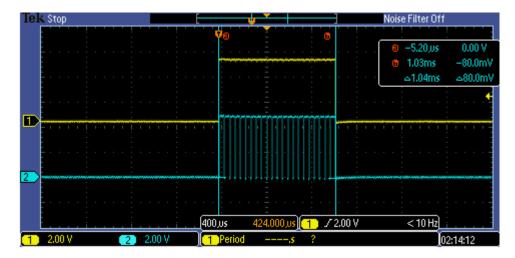

| 4.4           | 1.04ms of total run-time for processing 22 CAN FD messages 5          |

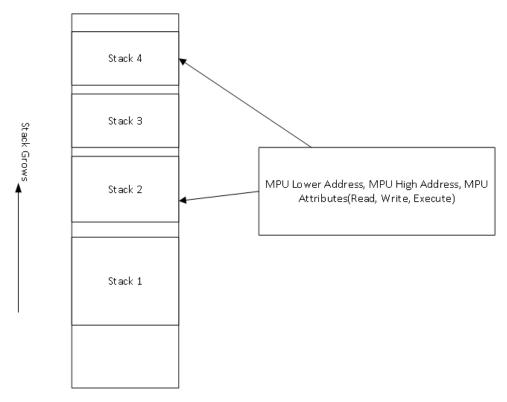

| 4.5           | MPU based stack protection                                            |

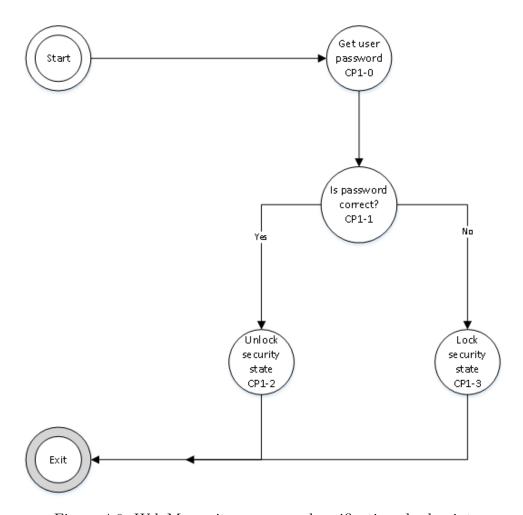

| 4.6           | WdgM monitors password verification checkpoint                        |

| 4.7           | Stack content before attack: return address = $0x4e80 \dots 6$        |

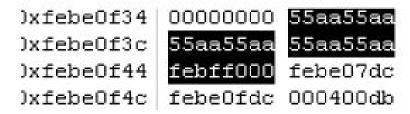

| 4.8           | Stack content after the attack: return address = $0xfebff000 \dots 6$ |

| 4.9           | Malicious routine is successfully entered after the stack overflow 6  |

| 4.10          | MPU exception triggered due to violation of execution rights 6        |

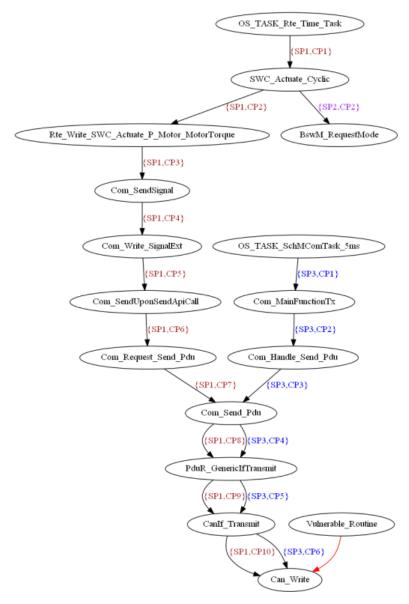

| 5.1           | AUTOSAR Software Architecture 6                                       |

| 5.2           | System Level Block Diagram                                            |

| 5.3           | Configuring a trusted function within EB tresos                       |

| 5.4           | Attack flow against a function in the safety-critical path            |

| 5.5           | Control flow graph for the Can_Write critical function                |

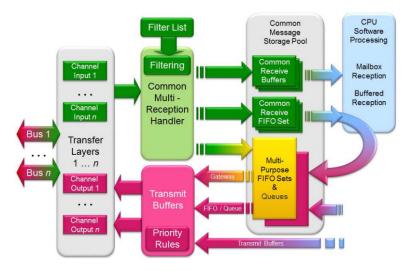

| 5.6           | RSCANFD CAN controller architecture, [19] 8                           |

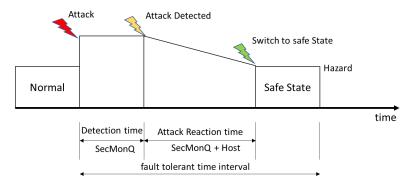

| 5.7           | Impact of SecMonQ detection time on FTTI constraint 8                 |

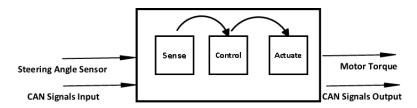

| 5.8           | ECU Model of Sensor Actuator Application                              |

| 5.9           | RH850 Development Environment and Debug Setup 9                       |

| 5.10          | Attack results on the Can_Write function                              |

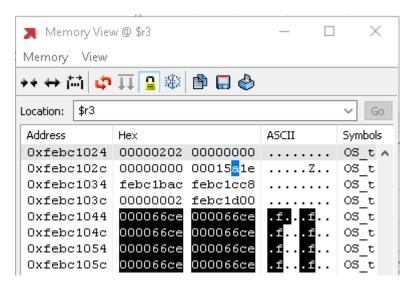

| 5.11          | Contents of stack frame after corruption                              |

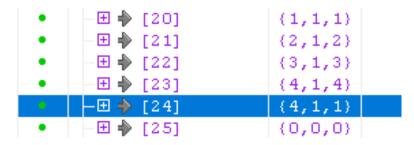

| 5.12          | Checkpoint cache: reception of CP_4 when CP_1 was expected 9          |

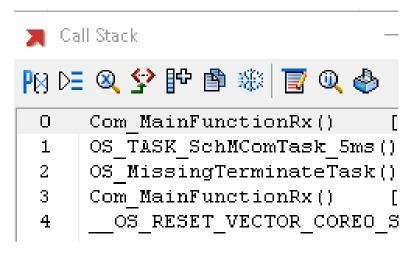

| 5.13          | Call trace after the attack, OS still scheduling tasks                |

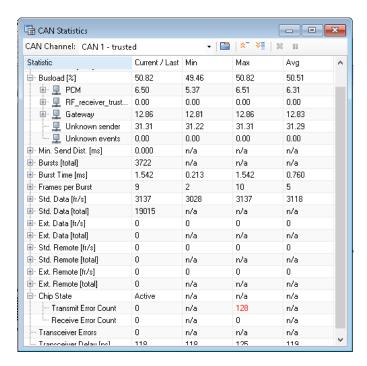

| 5.14          | CAN Bus load to mimic real vehicle bus conditions                     |

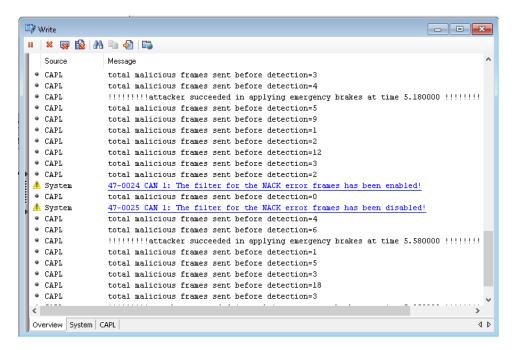

| 5.15          | Attack results when attack rate is 10ms                               |

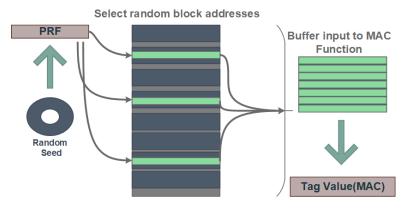

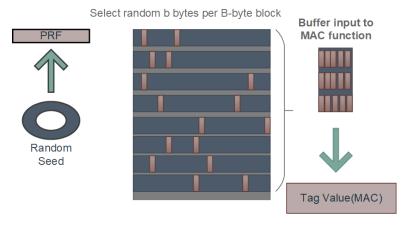

| 6.1           | Tag generation process using randomly selected blocks                 |

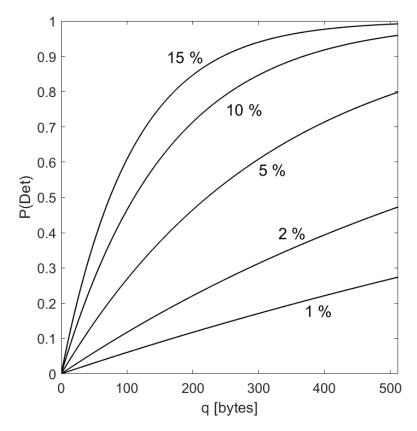

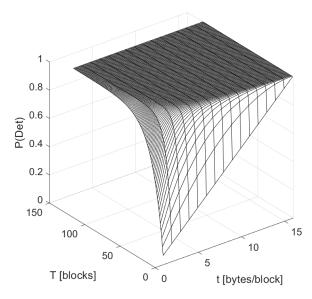

| 6.2  | Theoretical probability of detection vs. number of <i>contiguously</i> mod- |     |

|------|-----------------------------------------------------------------------------|-----|

|      | ified bytes given various sample sizes using rBS                            | 111 |

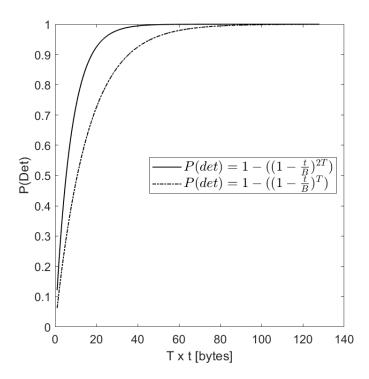

| 6.3  | Per Block Sampling method                                                   | 114 |

| 6.4  | Theoretical probability of detection vs. number of modified bytes for       |     |

|      | per Block Sampling (pBS), with B=16 bytes, t=1 byte and b either            |     |

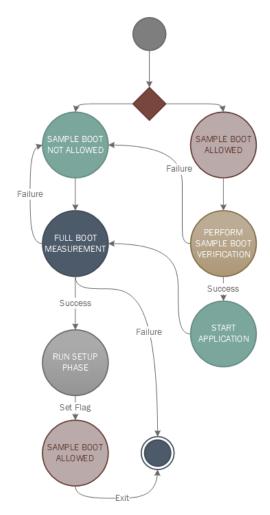

|      | 1 or 2 bytes per block                                                      | 115 |

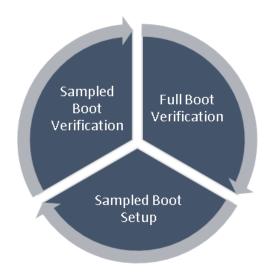

| 6.5  | State flow diagram for the dual phase boot approach                         | 119 |

| 6.6  | Coupling of the sampled boot phase with the full boot phase to reduce       |     |

|      | risk of undetected data tampering                                           | 120 |

| 6.7  | Python Simulation showing probability of detection vs. number of            |     |

|      | contiguously modified bytes given various sample sizes for Random           |     |

|      | Block Sampling (rBS)                                                        | 121 |

| 6.8  | Python Simulation showing probability of detection vs. number of            |     |

|      | non-contiguously modified bytes given various sample sizes for Ran-         |     |

|      | dom Block Sampling (rBS)                                                    | 122 |

| 6.9  | Python Simulation:probability of detection vs. modified bytes for           |     |

|      | different b values using pBS                                                | 123 |

| 6.10 | Probability of detection vs. number of modified bytes per block(t),         |     |

|      | vs. number of tampered blocks(T) for per Block Sampling (pBS)               |     |

|      | with b=1                                                                    | 124 |

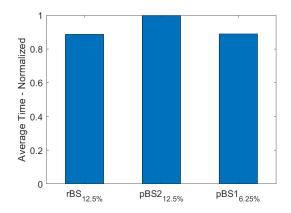

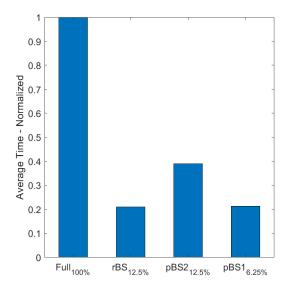

| 6.11 | Setup time comparison between the different variants with different         |     |

|      | sample sizes                                                                | 125 |

| 6.12 | Verification time comparison relative to full boot                          | 126 |

#### ABSTRACT

In recent years, several attacks were successfully demonstrated against automotive safety systems. The advancement towards driver assistance, autonomous driving, and rich connectivity make it impossible for automakers to ignore security. However, automotive systems face several unique challenges that make security adoption a rather slow and painful process. Challenges with safety and security co-engineering, the inertia of legacy software, real-time processing, and memory constraints, along with resistance to costly security countermeasures, are all factors that must be considered when proposing security solutions for automotive systems. In this work, we aim to address those challenges by answering the next questions. What is the right safety security co-engineering approach that would be suitable for automotive safety systems? Does AUTOSAR, the most popular automotive software platform, contain security gaps and how can they be addressed? Can an embedded HSM be leveraged as a security monitor to stop common attacks and maintain system safety? When an attack is detected, what is the proper response that harmonizes the security reaction with the safety constraints? And finally, can trust be established in a safety-critical system without violating its strict startup timing requirements? We start with a qualitative analysis of the safety and security co-engineering problem to derive the safety-driven approach to security. We then apply the approach to the AUTOSAR classic platform to uncover security gaps. Using a real automotive hardware environment, we construct security attacks against AUTOSAR and evaluate countermeasures. We then propose an HSM based security monitoring system and apply it against the popular CAN masquerading attack. Finally, we turn to the trust establishment problem in constrained devices and offer an accelerated secure boot method to improve the availability time by several factors. Overall, the security techniques and countermeasures presented in this work improve the security resilience of safety-critical automotive systems to enable future technologies that require strong security foundations. Our methods and proposed solutions can be adopted by other types of Cyber-Physical Systems that are concerned with securing safety.

### CHAPTER I

### Introduction

As defined in [60], automotive security is the field of assessing cyber threats against automotive systems and developing security countermeasures for the detection and prevention of the corresponding attacks. Due to the increased connectivity of automotive systems to the internet and smart devices, the threat of cyber attacks is ever more present. Since automotive systems contain an element of control, safety becomes a concern when exposed to security threats, therefore securing these systems is a high priority. Furthermore, securing safety-critical systems in the vehicle requires a holistic approach that takes into account all vehicle access points, external interfaces, and internal networks. Failure to properly secure vehicles will result in a chaotic world where drivers are at the mercy of malicious attackers, who are determined to create safety hazards through cyber attacks. While functional safety in automotive systems is a mature and stable domain, the interplay between safety and security remains a hot topic that requires solving. What makes it a difficult problem to solve is the automotive industry's resistance to radical changes due to massive market forces of cost sensitivity, legacy tools and software, as well as existing infrastructure that cannot be easily adapted. Therefore, security solutions must work within the existing constraints of the automotive industry otherwise face rejection. The primary question we want to answer in this dissertation is how to maintain vehicle safety in the presence of a malicious attacker who is determined to circumvent typical security countermeasures while working within the aforementioned constraints. To answer this question, we take a two-tiered approach: first, by looking at the system view to formulate a safety aware security engineering method, and second, by zooming in onto the electronic control unit to uncover security gaps and formulate security countermeasures that ensure safe operation even while under attack. To study the safety and security interplay the following road map is followed:

- Formulate a system level approach to engineering secure safety systems

- Evaluate the current state of the art of ECUs in terms of safety and security to find existing gaps

- Close the security gaps with a solution that is compatible with the safety requirements of the target systems

- Build practical security defenses that meet the constraints of real-time systems to satisfy availability and integrity requirements

#### 1.1 Contributions

The contributions of this work are multi-fold. First, we start by studying the Overthe-Air Update process from a safety point of view. We formulate a safety driven security approach that aims to uncover security requirements that protect the safety aspects of the update process in the ECU. We compare the approach against the state of the art OTA industry approach and show comparable findings. The safetydriven approach is further used in our work when defining a secure architecture for protecting safety in deeply embedded ECUs. The second contribution is in the area of AUTOSAR security analysis. We are the first to perform a comprehensive security analysis of AUTOSAR as it relates to safety to identify security gaps. We find that

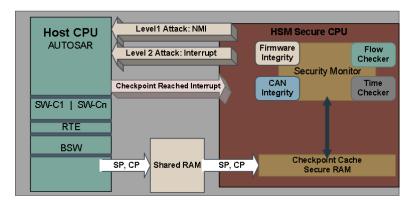

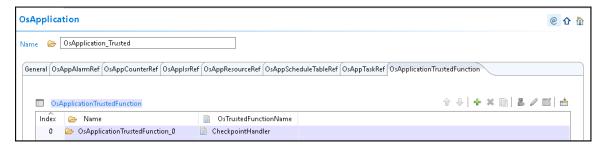

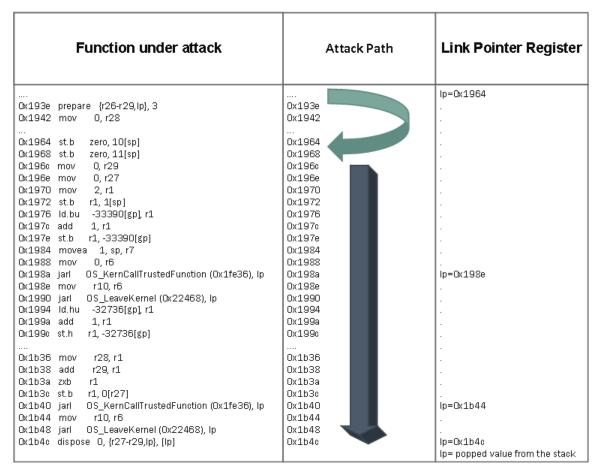

AUTOSAR classic took a primarily safety-focused approach which led to some design decisions being in conflict with security. We demonstrate a network-based attack that can result in an ECU shutdown. We also show ways in which AUTOSAR safety mechanisms can be leveraged to improve security hardening. The third contribution is in defining a secure ECU architecture that leverages the embedded HSM to provide security monitoring of four critical aspects of the ECU. A context-based control flow integrity monitor safeguards safety-critical program points by monitoring the relevant execution paths. A timing monitor ensures an attacker does not reroute control away to his own malicious code consequently starving safety-critical tasks from execution budget. A firmware integrity monitor ensures flash tampering is detected in real time to prevent persistent code modification. And a CAN peripheral integrity monitor ensures that the message transmit list is not modified after startup to launch a CAN masquerading attack. We show that the approach has minimal impact on legacy code and host CPU run-time. The fourth contribution is in the area of secure boot acceleration. Due to the strict startup requirements of safety systems and the increased demands for memory, authenticating the full software at startup can take prohibitively excessive time leading to compromises in what gets authenticated and when. Our probabilistic approach achieves high confidence in the integrity of the software within a fraction of the traditional secure boot time.

## 1.2 Organization

The dissertation is organized as follows: Chapter II introduces background topics and related work. In Chapter III, the OTA process is analyzed from a safety point of view to derive the safety-driven approach to security analysis. In Chapter IV, the approach is applied to the AUTOSAR classic software platform to identify security gaps and propose security hardening countermeasures. In Chapter V, the HSM based security monitoring system is introduced to address the security gaps uncovered in

Chapter IV. In Chapter VI, a probabilistic approach to secure boot is presented to enable the accelerated availability of automotive embedded devices. Finally, Chapter VII provides a conclusion and future work.

### **CHAPTER II**

# Background and Related Work

#### 2.1 AUTOSAR

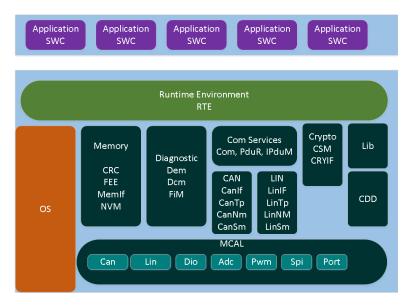

AUTOSAR stands for AUTomotive Open System ARchitecture. The AUTOSAR classic version has seen wide success in the automotive ECU market since its initial introduction in 2003 and is expected to expand its dominance as more users continue to adopt it across the automotive industry [1]. One of the greatest strengths of AUTOSAR is its standardized architecture, shown in Figure 5.1, where hardware features are abstracted away from the rest of the system to ease software portability and interoperability. For safety support, AUTOSAR follows an approach of safety element out of context and provides several safety mechanisms to support typical automotive use cases. In terms of security, AUTOSAR provides a cryptography stack which enables ECUs to provision keys as well as execute various security and cryptography services. There is also a secure onboard communication module that provides authentication services to in-vehicle network data. As of version 4.4, additional security modules have been added to support key management, security audit logging, and dynamic rights management for diagnostic access. Beyond that, it is expected that ECU designers build additional security layers to secure their systems, for e.g. locking JTAG ports, implementing secure flash bootloaders, enforcing secure boot on startup, and following security best practices such as the principle of least privilege. AUTOSAR makes a general assumption that the host CPU running the AUTOSAR stack is trusted and therefore makes no requirement on how security sensitive software is accessed and by whom. In fact, AUTOSAR uses the term "Trusted Applications" to refer to any application partition which is considered safety qualified. As a result, such applications run at the same privilege level as the operating system [11], and can, therefore, change the MPU configuration to disable security protections of memory. It is, therefore, up to the implementer to add the necessary protections to prevent unauthorized access to the security-relevant services of AUTOSAR and to act when an attack is detected. In this work, we study the gaps that currently exist in AUTOSAR and create supplementary countermeasures to increase the security resilience of AUTOSAR based systems.

### 2.2 Automotive Embedded Systems

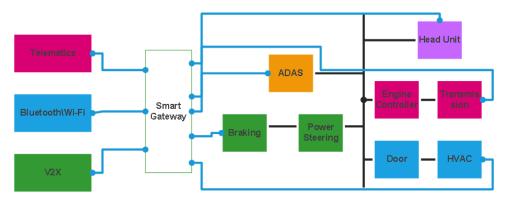

Modern vehicles contain upwards of 80 ECUs that control various vehicle functions in a distributed fashion [35]. The right vehicle data architecture is essential to the security posture of these ECUs. For e.g., if the braking control ECU is connected directly to the infotainment head unit, the attacker only has to compromise the infotainment head unit to gain access of the braking controller which can have catastrophic results. In a state of the art vehicle architecture, shown in Figure 2.1, vehicle buses are separated based on the domain function with a central gateway that controls cross-domain message transfer. This provides a level of isolation to prevent a malicious ECU from being able to compromise the entire vehicle. Normally, modules with external connectivity are located behind the gateway ECU. Examples of those are the telematics unit with a cellular connection, the bluetooth and wi-fi radios and V2X module for the car to car communication. On the opposite end of the gateway, various domain networks are separated by vehicle function. The body bus contains ECUs that control comfort such as door control and heating and cooling. The power-

Figure 2.1: Network architecture of a modern vehicle

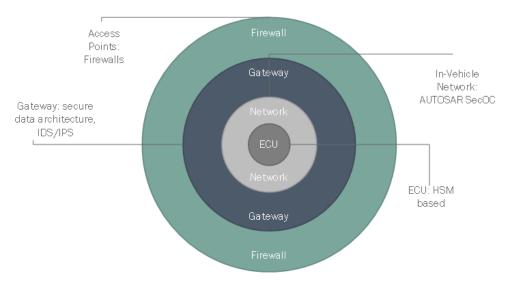

train bus contains the engine and transmission controllers. The chassis bus contains steering and braking controllers. The ADAS bus contains the advanced driving assistance modules which can leverage cameras and radar. And finally, the media bus contains the head unit which serves various media content to the passengers. The domain networks most popular communication protocol is CAN due to its robustness and low implementation cost. Other bus systems such as LIN, Flexray, MOST and Ethernet are commonly used based on the vehicle manufacturer preference. Data flowing over these buses are mainly used for control, status, diagnostics, and media. It is well understood that a defense-in-depth approach is needed to secure the various data layers of the vehicle architecture as shown in Figure 2.2. First, external interfaces are protected through traditional firewall technology. Next, an intrusion detection or prevention system in the smart gateway ensures anomalous network data is detected or stopped. In addition to that, the gateway enforces separation rules that prevent nodes of one bus from directly sending messages to other networks. Beyond the gateway, individual vehicle bus domains are protected through the AUTOSAR secure onboard communication layer [10], which provides data authentication and freshness protections. Finally, the ECU level security leverages hardware security modules(HSM) in order to establish trust and protect its security assets. Note, most vehicles today only implement a subset of the aforementioned security layers due to the cost and/or impact on legacy systems.

Figure 2.2: Security in-depth concept for advanced vehicle architectures

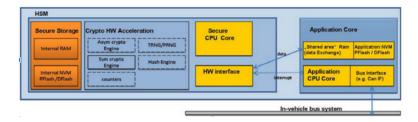

## 2.3 Hardware Security Modules

Certain attacks against automotive embedded systems cannot be thwarted through software-only security mechanisms. An embedded HSM plays a vital role in bridging that gap by providing support for security primitives, such as secure boot, secure communication, access control, key management, and cryptographic acceleration. The HSM defined by EVITA [100] and later extended by Bosch [36], was designed to meet the various security use cases deemed relevant for automotive systems. As shown in Figure 2.3, HSMs are embedded in the microcontroller with a dedicated CPU and cryptographic hardware accelerators. Additionally, they support a random number generator along with optional features such as I/O ports. Communication between the host and the HSM is done through an interrupt mechanism and shared RAM buffers. Due to the flexibility of the firmware executed within the HSM environment [29], it is possible to add security extensions such as host CPU monitoring to detect malicious behavior. Depending on the chip, an HSM may be able to monitor several host subsystems such as CAN as well as control the reset of the host CPU.

Figure 2.3: Evita Medium HSM architecture

### 2.4 Combining Safety and Security in Automotive Systems

The problem of combining safety and security engineering processes has been studied in various industries in which cybersecurity threats intersect with the physical control of a process. A survey by Kriaa et al. [65], showed the various standards and approaches proposed across a wide range of cyber-physical systems. Although the automotive domain is relatively a latecomer to this problem, many parallels can be drawn between challenges facing the automotive industry and other industries. Briefly, the problem of security interdependency is one in which the two domains can be in any one of the following states [85], [53]:

- Synergistic: here the safety and security requirements compliment one another. A typical example is the usage of a MAC to protect both authenticity and data integrity which also fulfills the role of a safety CRC. We shall see in Chapter IV, how we leverage this relationship type in AUTOSAR based systems to improve security resilience.

- Conflicting: here a safety and security requirement contradict or compete with one another. We shall see in Chapter IV how this relationship results in safety mechanisms making the system vulnerable to specific attacks.

- Conditional: here safety and security are prerequisites for one another. We shall see in Chapter V how we build security systems that guarantee this relationship type is upheld when building security countermeasures that respect safety

constraints.

For automotive systems, Glas et al. [53], presented various cases in which these relationships can be observed. In terms of conflicting requirements, they gave the example of a safety-related cyclic RAM test that requires stalling the HSM core to prevent interference. As a result, the safety requirement violates a security principle that a security module (e.g. HSM) is disabled during normal operation. Such scenarios are important to detect early on in the design of the vehicle to avoid introducing bugs, or security vulnerabilities. The work in [101] took a practical approach to assessing the resilience of safe automotive micro-controllers in handling power glitching attacks. They showed that the dual lock core step safety mechanism which is meant to detect faults within the CPU, could be leveraged to detect maliciously induced CPU output mismatches. However, the safety mechanism on its own was not always able to detect all the power glitches which lead to skipping critical security code sections that unlocked the JTAG interface. The work highlighted the potential for synergistic relations between safety and security mechanisms albeit with some effort to account for malicious fault sources. In the area of AUTOSAR based safety and security overlap, the work of [34], showed how the EB tresos [2] AUTOSAR OS can be used to harden the ECU against attacks. Using mechanisms such as stack overflow protection, and MPU based read/write and execution prevention, the security posture of such systems can be significantly improved. The work in [56] raised the issue of conditional safety and security when introducing TPMs in a safety-related Cyber-Physical System. The study showed various aspects of potential conflicts if the safety element is dependent on the TPM. As a result, a set of requirements was proposed to ensure TPM technology can be used safely. The study of TPM usage in a safety context is useful to explain the practical results of introducing security elements which can interfere with the safety concept of the system and thus require adequate analysis and handling.

In terms of the interplay between safety and security engineering processes in Cyber-Physical Systems, there are generally two schools of thought. The unification approaches aim to produce a single engineering process that considers both safety hazards and security threats simultaneously as in [95] and [31]. While this reduces the number of engineering resources, it is challenging to find experts who can tackle both areas with the same required rigour. The integration approaches on the other hand, propose separating the two processes while cross-referencing the resulting requirements to identify and resolve conflicts as in [59]. The automotive industry has also attempted to address the engineering processes interdependence through various standardization efforts. The automotive functional safety standard, ISO 26262 [17], requires that hazards to functional safety be adequately addressed to reduce their risk to acceptable levels. In terms of security, the standard leaves the handling of threats that cause safety hazards open for future standards to handle. This is where SAE stepped in through SAE J3061 [43], to define a cybersecurity framework that is analogous in process steps to the safety standard. In terms of the combination of safety and security, the standard proposes three ways of approaching that:

- Apply the process as a standalone activity with communication points to the safety standard

- Apply process steps in conjunction with the safety standard

- Apply the process as a hybrid, which leads to some activities being done in conjunction and others done separately

Due to the vast difference of expertise between the domains of safety and security, there is a near consensus in the automotive industry that the ideal approach pursues a parallel path between the two processes with connection points that ensure consistency between the derived safety and security requirements. SAE J3061 extends the Hazard Analysis and Risk Management (HARA) from functional safety, into security

Threat Analysis and Risk Assessment (TARA), to identify and prioritize cybersecurity risks. Over the years, several TARA methods have been proposed for automotive systems such as HEAVENS [3], SAHARA [71], and EVITA [87]. They follow a general scheme of applying a threat model against system components or functional use cases to derive relevant threats. Then they decompose each threat based on a specific risk model to allow prioritization and subsequent mitigation. Threats that result in severe impact to safety while requiring low resources, and know-how are prioritized for mitigation. Such threats can result in changes to the safety architecture to mitigate the corresponding security risks. HEAVENS, which stands for Healing Vulnerabilities to Enhance Software Security and Safety, uses the STRIDE threat model [91], against functional use cases to derive threats. Then decomposes threat levels in terms of required expertise, knowledge about the target, window of opportunity to carry out the attack, the type of equipment needed to launch the attack, and the impact severity. SAHARA follows a similar approach but for threat assessment, it considers three factors: required resource to materialize the threat, required know how, and threat criticality. EVITA [87], emphasizes the use of attack trees to derive attacks and performs the risk analysis based on an ASIL extended risk model. The work in [38], presented an approach to extend the ISO 26262 safety standard [17], to consider security threats and their potential hazardous classification. They apply their approach to the use case of the adaptive cruise control function. This resulted in deriving a set of functional and technical security requirements which aim to reduce the risk of security threats to an acceptable level. The approach highlighted again the many parallels between safety and security engineering processes. Alternatively, the authors in [26] proposed an iterative approach to safety and security in which one process provides feedback to the next. Their approach requires a safety pattern engineering step to be performed first to arrive at the close to complete architecture. Next comes the security pattern engineering which can result in impacts on the safety architecture. This is followed by a safety and security co-engineering loop to resolve conflicts between the two. The iterative nature of that approach is closely related to our safety-driven approach to security(SDAS) which we introduce in Chapter III. The gap in the available approaches listed above is that no clear direction is given on how to link the safety and security processes practically. While the need for harmonizing the security and safety requirements is well-understood, how one would go about doing so is left open. In Chapter III, we shall see how our proposed SDAS approach tackles this problem by providing a practical method for linking the safety engineering analysis to the security analysis in a way that produces harmonized requirements between the two domains. Note, at the time of writing this thesis, the ISO/SAE 21434 Road Vehicles Cybersecurity engineering standard was not yet published but is expected to provide answers that relate to this topic.

### 2.5 Attacks on Safety

Since one of the primary goals of our work is to improve the security resilience of safety-critical ECUs, it is useful to survey the types of attacks that such systems are subjected to. The past years have seen a sharp increase in academic publications about successful attacks on automotive systems with the intent to create a safety hazard. Checkoway and Koscher [39] performed a comprehensive analysis of automotive attack surfaces in a groundbreaking study that demonstrated the reality behind cyber attacks on vehicle systems. They showed different ways by which an attacker can get access to the vehicle CAN bus where the critical control commands exist, in order to take control of the vehicle. The approach of their analysis was based on extracting the ECU firmware and then reverse engineering the code and data using disassembly, and debug tools. By disassembling the code using a tool like IDA Pro they could map the control flow and identify vulnerabilities. This approach led to uncovering several vulnerabilities, such as a buffer overflow in the media player which allowed a mali-

cious WMA audio file to run malicious code. The latter could then interfere with the vehicle based on the vehicle architecture and what other ECUs are connected to the media player. This and other vulnerabilities demonstrated how security attacks could be launched to impact vehicle safety. Then came Miller and Valasek [73], [74] who demonstrated a remote attack on a Jeep vehicle that led to the loss of brake function at low speed. This later resulted in a recall of Jeep vehicles and became the most publicized successful attack on a vehicle. They used a software update vulnerability in the head unit in order to modify the firmware of the vehicle processor interface. The latter could then interfere with the CAN bus via the park assist module by sending a diagnostic command to bleed the brakes causing the vehicle to lose braking ability. The study presented many insights into tools and methods by which vehicle security can be analyzed for the purpose of launching a successful remote attack. Following that, several research teams demonstrated successful attacks such as the ones against the Nissan Leaf [63], GM Corvette [54] and Tesla [66], [98]. The Tencent Labs attacks followed a similar pattern of finding a vulnerability in the autopilot electronic unit in order to launch CAN spoofing attack on critical safety components like steering. In response to such attacks, several security best practices have been published [25] and individual OEM's have taken concrete steps to harden the security of their vehicles. Still, the road to fully securing vehicles seems long and arduous. In the following chapters, we demonstrate how security resilience of automotive safety systems can be improved to handle those types of attacks while keeping in line with the unique constraints and challenges of automotive systems.

#### CHAPTER III

# Safety Driven Security Analysis: A System View

#### 3.1 Introduction

The first phase of our research consisted of surveying the available safety-security engineering approaches. As discussed in section 2.4, it was apparent that engineering secure safety-critical automotive systems still faced several questions that required answering. Since the primary goal of our target systems is to ensure safety, the approach applied had to be heavily biased towards that aim. To do so, the following questions shall be answered:

- How can the safety analysis be linked to the security analysis in a way that guarantees that security measures are addressing maliciously triggered hazards?

- In case attack prevention is possible, how to ensure that the resulting security countermeasures are still compatible with the safety architecture?

- When only attack detection is possible, what is the proper reaction that the system shall take to ensure safe operation while under attack?

To answer these questions and formulate a safety and security co-analysis approach, we chose to study the use case of over-the-air updates (OTA). By studying the OTA safety and security interplay, we can formulate then validate our approach through comparison to the state of the art in OTA security. The outcome of our analysis shall generate security requirements that ensure the process of updating software in the vehicle does not result in an unsafe vehicle state at the ECU level [79]. Following that step, the approach can then be applied to other aspects of our research into ECU level security as will be shown in the following chapters.

### 3.2 Background

Securing Cyber-Physical Systems (CPS) depends largely on keeping such systems up to date with the latest security patches. A connected vehicle which contains a number of independent and interconnected modules is an example CPS where securely updating the software in any module is a concern for the overall integrity and availability of safety functions. A connected software update process is defined as a process in which the software update is delivered to the vehicle wirelessly or through a connected device to be later flashed into a target ECU over the vehicle network. Reduction of recall costs, the migration towards ADAS and autonomous driving, the desire to download security patches, as well as the possibility of upgrading vehicle features wirelessly, all make the connected software update a mandatory building block to support the future of vehicle development. Until recently, flashing an automotive ECU after it left the manufacturing plant was only possible through the use of a diagnostic tester tool which physically connected through the OBD II port [57], or insertion of physical media into the vehicle's media-related components. Security vulnerabilities with such tools are well-documented in [39]. They showed various attack scenarios such as infecting the diagnostic tool to perform unauthorized diagnostic services or installing malware on an audio CD infect the head unit and gain access to the internal vehicle bus system. Adding connectivity to a vehicle makes the attack surfaces for the software update process much larger. Malware may be delivered to the vehicle when a vulnerability exists in the OTA update/remote diagnosis process, flaws in embedded web browsers, malicious aftermarket equipment, or through removable media ports and others [103]. With a compromised software update process an attacker can reprogram ECUs with malicious code that can compromise vehicle safety. The famous Jeep UConnect attack by Miller and Valasek [74], relied on a software update vulnerability in the head unit in order to craft a series of attack steps that lead to the modification of the vehicle processor interface firmware. The latter could then interfere with the vehicle CAN bus by sending a diagnostic command to bleed the brakes causing the vehicle to lose braking ability at low speeds. This and other similar proven attacks demonstrate the need for the download process especially at the ECU level where malicious downloads can be catastrophic.

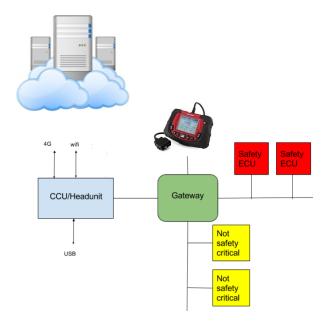

#### 3.2.1 OTA Architecture

The connected software update allows the remote delivery of software updates to an ECU in a vehicle. Whether the update is delivered over the air, for example through a telematics unit or through a Bluetooth enabled smart device, direct authentication with the originating source is needed to ensure the integrity and authenticity of the software update. In this chapter when we discuss over the air update, we are referencing the process by which software updates are delivered to a vehicle wirelessly first by downloading to a primary ECU like the vehicle gateway, and second by flashing the target ECU. The architecture, shown in Figure 3.1, is a simplified diagram of the vehicle data architecture with the following associated attack surfaces and threat sources:

#### **OBD-II Port:**

- Download tool connected to the OBD-II connector

- Aftermarket equipment connected to OBD-II port (Insurance Dongle)

#### Telematics/Headunit:

Figure 3.1: Architecture of OTA system considered for the security analysis

- Cellular Modem Connection

- Wifi Hotspot (and related software)

- Bluetooth connection to mobile device

- Media Ports (USB, SD Card, CD/DVD)

#### Internal Vehicle network:

- CAN bus network

- Compromised ECU, either gateway or ECU on safety bus.

In the following sections, we will see how this architecture results in a set of threats that have safety impacts and how they can be mitigated by applying the safety-driven security approach.

### 3.3 Related Work

In Section 2.4, we surveyed the various techniques for combining safety and security analysis. Here, we shall look at existing approaches for securing software update

processes to provide a reference for our comparison. Several papers have already presented concepts for a secure software update process as well as the possible threats that such systems face. The EVITA project [87], presented ten attack trees based on eighteen security use cases. One of the security use cases is the attack on the flashing capability of the vehicle. Based on the derived attack tree, security requirements were developed to protect vehicle assets against flash programming threats. The project derived the following security requirements for firmware updates relative to the OEM, the Download Tool (DT), the Communication Control Unit (CCU) and the ECU:

- Firmware confidentiality (CSR.1): Firmware must be kept confidential when transferred from OEM to DT and from DT to the target ECU

- Key confidentiality (CSR.2): Exchanges transferring or using non-public keys must preserve key secrecy along the whole flashing process

- Internal Authenticity (ASR.1): Whenever an exchange between CCU and ECU happens, the correspondence between claimed and real authors must be authenticated

- External Authenticity (ASR.2): Whenever data is exchanged between DT utility and OEM server or between DT and in-car components, the correspondence between claimed and real authors must be authenticated.

Note, the above requirements do not make a distinction between safety-relevant security requirements and those which are purely security relevant. Nilsson et al. [82], studied the different security threats that face software updates and presented a list of threats based on the different elements involved in the flash update process, which are: the portal, the communication link between the portal and the vehicle, and the vehicle itself. In the portal, they pointed to masquerading attacks in which an attacker takes-over or creates a fake portal to distribute malicious software packages. In

the communication link, they pointed to the risk of the wireless link being vulnerable to traffic manipulation through packet injection and replay attacks. As for the vehicle level threats, they pointed to the case where an attacker can impersonate a vehicle and connect to the portal to uncover security vulnerabilities or attack vectors. These vectors can then result in further intrusion attacks. The authors derived security requirements to address those risks in a methodical fashion:

- Preventing impersonation of the portal by using certificate based identity verification of the portal and preloading the portals public key in the vehicle

- Usage of an Intrusion Detection System in the portal to detect an intrusion and take the proper action

- Secure end-to-end communication over the wireless link by encrypting all the data with a freshness counter to prevent packet injection or playback

- Preventing impersonation of a vehicle by establishing the vehicle identity through a certificate

- Usage of a firewall and an IDS in the vehicle to alert against an intrusion and log the intrusion to prevent future breaches

In the above requirements, safety is again assumed as a by-product of securing the overall system. Note, in our work, while we are interested in the overall security, the focus of our work is on securing safety at the ECU level. UPTANE [61], is an open source project that proposes a full OTA solution specifically designed for automotive systems. The project enlisted security experts from academia as well as experts from the automotive industry to come up with a state of the art open source solution to OTA. The project presents the following design goals to deal with security attacks:

• Leverage additional storage to recover from endless data attacks. This allows the new software image to be flashed without overwriting the original image which can serve as a backup.

- Broadcast metadata to prevent mixed-bundles attacks where a compromised primary ECU can send incompatible software images to secondary ECUs

- Utilize a vehicle version manifest to detect partial bundle installation attacks which can leave ECUs partially programmed

- Use a time server to limit freeze attacks to prevent an ECU from completing its download or preventing it from receiving any updates

The above design goals guide the full implementation of UPTANE which defines in greater detail the roles of primaries, secondaries, and the content of metadata. Due to the maturity and completeness of UPTANE, we shall use it in this chapter as a reference for validating the output of our security analysis using the safety-driven approach to security.

## 3.4 A Safety Driven Approach to Security

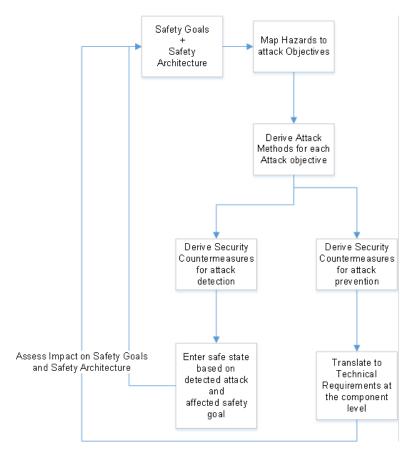

The safety-driven approach to security(SDAS), assumes that the safety analysis is performed initially to define a safe system architecture along with the risk of safety hazards that shall be mitigated. Therefore, SDAS starts from the point where the safety analysis was finished and then re-iterates until both the safety and security requirements are in no further conflict as shown in Figure 3.2. In each iteration, changes applied to the architecture are evaluated from both the safety and security points of view. The approach builds upon the premise that hazards outside the physics of the system cannot be added through cyber attacks. Instead, the latter is only able to manifest hazardous events from the set of possible hazards that a specific ECU can experience. Consider for e.g. an electronic power steering ECU which is required to mitigate the hazard of an over-steering event that can result from a failure in the

Figure 3.2: Safety Driven Security Approach process steps

steering angle sensor. An attacker can induce the hazard of over-steering by spoofing the sensor data, but he cannot create a totally new hazard in the target ECU outside its own physical limits. Incidentally, he can create hazards for other ECUs through a masquerading attack, but that is handled separately within the hazard analysis of the respective ECUs. Furthermore, by focusing on the safety goals as a starting point we limit the search space of security threats to ones that are guaranteed to result in a safety impact. Since our aim is to secure safety-critical systems, we argue that biasing the security analysis in this manner is acceptable.

Based on the target application use case, we map hazards to attack objectives using the attacker model. Given the attack objectives, there are several techniques to produce attack methods, such as attack trees, as is done in the EVITA project [87], or by looking at documented attack methods as in [92]. Alternatively, applying a

| Hazard                                                                                                                                                                                       | Functional Unit        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Software is corrupted during the down-<br>load process without detection by the<br>ECU. ECU then executes corrupted<br>code which can result in undefined and<br>potentially unsafe behavior | CCU,Gateway,Target ECU |

| Download of incompatible binary files for e.g. a calibration file with unsafe parameter settings                                                                                             | Gateway, Target ECU    |

| A communication failure prevents the download from completing leaving a safety critical ECU un-programmed                                                                                    | Gateway, Target ECU    |

| A power failure during programming leaves a safety critical ECU partially programmed or un-programmed                                                                                        | Gateway, Target ECU    |

| A permanent communication failure in<br>the system prevents any updates from<br>reaching the vehicle including safety<br>critical patches, e.g. recall related up-<br>dates                  | CCU                    |

Table 3.1: Simplified Hazard Analysis for OTA

threat model such as STRIDE[91], can also be useful in enumerating threats that can lead to a safety hazard. Although we are focusing here on threats that lead to hazards, this does not mean that non-safety related threats are to be ignored. For such threats, traditional security engineering approaches can be applied in parallel to protect properties such as driver privacy. Once, we have a set of attacks that can directly violate our safety goals, we can now evaluate whether each attack is preventable, or only detectable. For preventable attacks, the next step is to define the technical security requirement at the component level to realize the security countermeasure. If only detection is possible, we need to define the detection method as well as how the system shall react when the attack is detected. Since each attack is mapped to a specific safety goal, we can reuse the fail safe-states defined in the safety case [17], to determine what the proper reaction shall be in the face of such an attack. At this point a re-evaluation of the safety architecture and relevant safety goals is performed

to ensure that the resulting system with the added functional security requirements does not introduce conflicts with the safety assumptions of the system. The process is repeated with several iterations to allow for refinements to the functional safety and security requirements until all conflicts are resolved. One example of such a conflict would be a functional security requirement that aims to immediately reset the system when an attack is detected. This in turn violates a safety goal for a graceful shutdown to prevent sudden loss of system function. Since our analysis is biased towards safety, we always give priority to safety requirements when a conflict is detected. In the remaining sections, SDAS is applied to the connected software update use case to demonstrate its effectiveness.

#### 3.4.1 Safety Goals

As stated above, a prerequisite to analyzing the security threats which have safety implications on the software update process is to define the safety goals first. Typically these are produced during the safety assessment. Since we do not have a real system to analyze, we came up with safety goals based on a simplified hazard and risk analysis of the OTA system described in Figure 3.1. The identified hazards are shown in Table 3.1. Note, we did not assess risk levels of safety goals in this theoretical use case because it requires a complete system to be defined first. The list of hazards we identified lead us to the following consolidated safety goals for the OTA system:

- Data corruption in software downloaded to the ECU shall not go undetected

- Incompatible software images shall not be downloaded to an ECU without detection

- Safety critical ECUs shall not be permanently left in an un-programmed or partially programmed state as a result of an OTA event.

| Attacker        | Objective                     | Impact                        |

|-----------------|-------------------------------|-------------------------------|

| Organized       | Download Malware to con-      | Injury or Loss of Life to In- |

| Crime           | trol an individual vehicle of | dividual Car                  |

|                 | victim                        |                               |

| Terrorist       | Download Malware to con-      | Injury or Loss of Life to     |

|                 | trol fleets of vehicles to    | civilian or government vehi-  |

|                 | cause mass chaos              | cles                          |

| Cyber Activists | Disrupt OTA process to        | Loss of customer confidence   |

|                 | prevent safety critical       | in OTA, potential for injury  |

|                 | patches or vulnerability      | or loss of life if manual up- |

|                 | fixes from being installed    | date not performed            |

| Cyber Criminals | Re-program ECUs remotely      | Loss of consumer confidence   |

|                 | with unsigned software,       | in ADAS systems, and in-      |

|                 | to force the ECU to stay      | creased risk of injuries or   |

|                 | in bootloader mode(un-        | loss of life                  |

|                 | programmed state) con-        |                               |

|                 | sequently, without safety     |                               |

|                 | critical functionality        |                               |

Table 3.2: Safety Driven Attacker Model

• It shall always be possible to download an update to fix unsafe software or roll back to a safe version

#### 3.4.2 Attacker Model

In our safety driven security approach, the attacker objectives are to trigger hazardous events that violate the defined safety goals. This is presented in Table 3.2. Given our attacker objectives, we can derive three safety driven attack objectives associated with the connected software update as shown in Table 3.3.

## 3.4.3 Security Requirements

Depending on the security architecture, certain attacks may not be prevented but at least they can be detected and action is taken. A security analysis shall evaluate each attack in terms of feasibility of both, prevention and detection in order to assign the proper recovery action. Based on the attacks presented in Table 3.3, we propose

| Attack Description                                 | Safety Goal |

|----------------------------------------------------|-------------|

| Download malware to take control of an ECU         | 1           |

| without detection                                  |             |

| Download a validly signed binary images with in-   | 2           |

| compatible software                                |             |

| Disrupt the update process indefinitely to prevent | 3           |

| an update from reaching completion. Here the at-   |             |

| tacker may not be able to forge an authentic soft- |             |

| ware image, yet he is still able to interfere with |             |

| the software update process in a way to prevent    |             |

| critical software updates from being delivered or  |             |

| flashed to the target ECU.                         |             |

| Manipulate the update process to result in an un-  | 4           |

| programmed ECU. In the case where the attacker     |             |

| cannot forge the signature of the software, he may |             |

| try to disrupt the download so as to result in an  |             |

| un-programmed ECU.                                 |             |

Table 3.3: Attacks with safety goal violations

the following functional security requirements:

- The software download shall only be possible with authenticated data and from an authorized source

- The authenticity of the binaries shall include the compatibility information among binaries to prevent flashing incompatible software binaries

- The OTA architecture shall permit multiple download channels to prevent safety critical updates from being blocked indefinitely through a single compromised channel

- Failure to update safety critical ECUs shall not result in an un-programmed ECU, i.e. the system shall retain a backup copy of the software to be able to restore such ECUs to their previous functioning state

# 3.4.4 Impact on Safety Architecture

Following the generation of attack prevention and detection countermeasures, SDAS requires evaluating the impact on the original safety architecture to resolve potential conflicts. The derived requirements in the previous section focused completely on prevention. To support these requirements, the ECU requires the ability to perform data authentication and access control functions. This results in the addition of security algorithms as well as hardware support, such as a TPM, to store keys securely. Hoeller et al. [56], showed that TPMs used in safety-critical systems require special handling. The areas of concern are the impact on real-time performance and the potential for faults in the TPM hardware which can result in safety violations. This highlights the need for further refinement of the safety and security architecture to ensure the impact on both is understood and action is taken. In terms of attack detection, when a software image is maliciously erased and the updated image is detected as invalidly signed, the safe state is to revert back to the backup software through the redundant storage. This ensures that our safety goal of not leaving a safety critical ECU in a permanently un-programmed state is upheld.

# 3.5 Comparison to UPTANE

The derived security requirements at the ECU level map very well to the security requirements stated in UPTANE [61], as shown in Table 3.4. In the following chapters, we shall apply SDAS to a wider use case to validate its effectiveness experimentally.

# 3.6 Conclusion

In this chapter, we presented a safety-driven approach to security analysis to bridge the gap between the two interdependent domains of functional safety and cybersecurity. We applied the approach to a popular OTA update process use case

| UPTANE                             | SDAS                                |

|------------------------------------|-------------------------------------|

| Prevent endless data attacks       | Failure to update safety critical   |

| through backup storage             | ECUs shall not result in an un-     |

|                                    | programmed ECU, i.e. the sys-       |

|                                    | tem shall retain a backup copy of   |

|                                    | the software to be able to restore  |

|                                    | such ECUs to their previous func-   |

|                                    | tioning state                       |

| Prevent mixed bundle attacks       | The authenticity of the binaries    |

| through the broadcast of meta      | shall include the compatibility in- |

| data                               | formation among binaries to pre-    |

|                                    | vent flashing incompatible soft-    |

|                                    | ware binaries                       |

| Detect partial bundle installation | Failure to update safety critical   |

| attacks by using a vehicle version | ECUs shall not result in an un-     |

| manifest                           | programmed ECU, i.e. the sys-       |

|                                    | tem shall retain a backup copy of   |

|                                    | the software to be able to restore  |

|                                    | such ECUs to their previous func-   |

|                                    | tioning state                       |

| Limit freeze attacks by using a    | The OTA architecture shall per-     |

| timeserver                         | mit multiple download channels      |

|                                    | to prevent safety critical updates  |

|                                    | from being blocked indefinitely     |

|                                    | through a single compromised        |

|                                    | channel                             |

Table 3.4: Attacks with safety goal violations

to fine-tune and validate the approach. As a result, we produced a list of security requirements that were shown to be aligned with the state of the art in OTA systems security. By focusing on the safety goals first, we were able to leverage the safety analysis in deriving safety hazards that can be induced maliciously. This led to defining security requirements that are necessary to counteract such threats. Also, by differentiating preventable from strictly detectable attacks, we were able to reference back the safe states of the system to ensure recovery action is compatible with the corresponding safety goals. In the next chapter, we apply SDAS to the AUTOSAR software architecture to uncover safety-relevant security vulnerabilities and

recommend ways to improve the AUTOSAR security resilience.

## CHAPTER IV

# AUTOSAR Safety and Security: Synergies and Conflicts

# 4.1 Introduction

In the previous chapter, we explored how taking an iterative approach to safety and security by linking safety goals to security threats can lead us to derive safety-relevant security countermeasures in a harmonized fashion. We saw that a safety-driven approach to security(SDAS), can indeed generate security requirements that safeguard safety as a system property. The approach also takes care of exploring areas of incompatibilities between the safety and security countermeasures which required iterative refinement to arrive at a system that satisfies both objectives. In this chapter, we apply the approach to AUTOSAR as the ECU level software architecture with the hope to uncover security vulnerabilities and then propose security countermeasures that improve the security posture of AUTOSAR based systems. The latter being the most popular software architecture platform for automotive systems [1], is a natural pick when studying the state of the art of automotive systems and ways in which safety and security may be in conflict or for that matter in harmony. Just as in chapter III, we start with the safety analysis since the systems primary function is to meet safety goals. Although, we did not have access to the AUTOSAR safety

analysis documentation, by examining the AUTOSAR defined safety mechanisms we could synthesize the assumed safety architecture behind AUTOSAR safety systems and evaluate how it would fair under the threat of attack. In parallel, as we analyze the security requirements of AUTOSAR, we go back to the safety architecture to determine incompatibilities and synergies. As will be shown in this chapter, there were instances in which safety mechanisms became attack vectors, and in others, they were useful as security countermeasures. When it came to attack mitigation, harmonizing the security response with the safety requirements became a must to ensure a fail-safe attack response. Next, we enumerated safety mechanisms that are synergistic with security and provide some constraints on how they can be used for ECU hardening. We then shift from analytical to experimental validation by demonstrating two attacks against a safety rated micro-controller. Finally, we demonstrate how specific safety mechanisms that are synergistic with safety can be used for attack mitigation, using the same hardware target.

# 4.2 Attack Model

Deeply embedded systems are assumed to be located behind several defense lines: firewall, security gateway, and a secure communication bus. Assuming the vehicle has implemented a properly layered secure architecture, launching successful attacks on such systems requires compromising several security layers upstream. Previous works by [73], [98], have shown that at some point these defenses can be broken and an attacker may be able to launch a successful attack against the vehicle control system. Let us consider the three classes of attacks that are relevant to both deeply embedded ECUs and traditional computer systems [48]:

• Malware and exploitable software vulnerabilities which aim to take control of the system

- Physical access type attacks

- Network based attacks