# Interface Engineering and Practical Applications of Amorphous Silicon Based Opto-electronic Devices for Large-Area Electronics

by

Qingyu Cui

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2019

**Doctoral Committee:**

Professor L. Jay Guo, Chair Associate Professor Xiaogan Liang Professor Jamie Phillips Associate Professor Zhaohui Zhong Qingyu Cui

qycui@umich.edu

ORCID iD: 0000-0003-3603-8994

© Qingyu Cui 2019

## Dedication

To my whole family, my friends

#### Acknowledgements

First and foremost, I would like to sincerely express the highest gratitude to my advisor Prof. L. Jay Guo, for all of his support during my PhD journey in the University of Michigan, Ann Arbor. He left a very big room for me to explore my own ideas, and was very patient, especially when I was stuck and failed in the experiments. His guidance is always insightful and encouraging for me to think deeply for the big background picture as well as the details of the experiments. Meanwhile, he tried to get me involved in the practical applications of some research works, and strengthened my understanding for the different needs and specifications of the research aims between the industries and academia. Moreover, he gave me very precious suggestions and opportunities for my personality development, for the future career environment. The PhD studies in the Guo group is an unforgettable experience in my life, which not only enables me to build inner strength and perseverance, but also shapes the outer doing and thinking behaviors.

Secondly, I would like to truthfully thank my committee members, Prof. Jamie Phillips, Prof. Zhaohui Zhong, and Prof. Xiaogan Liang. During the thesis proposal meeting, they gave me very good comments to verify and clarify the descriptions of my works. I appreciate very much the questions from Prof. Jamie Phillips about the charge doping and interfacial properties related to a-Si active layers. Thanks to the comments from Prof. Zhaohui Zhong about the surface dipole and the electrical behavior of the resistive switching devices. I also remember the course of solid-state physics he instructed. In that semester I had the opportunities to understand the semiconductors from a deeper perspective related to the interactions between electrons or atoms. I am very grateful that Prof. Xiaogan Liang spent around 2 hours discussing my PhD works face-to-face in his office, and he gave many insightful comments and valuable guidance for the further verification and better interpretation of the obtained experiments results.

I also greatly appreciate the help from the members of Guo group and other groups. Although I had a very short overlapping with Dr. Jeayong after I joined Guo group, his works related to a-Si devices gave me a big direction and I can extensively do the further explorations. Dr. Cheng Zhang is my LNF mentor, and he taught me many usage experiences of the LNF equipment. Moreover, he gave me the opportunities for the collaborations on the flexible OLEDs, resistive switching devices as well as the transparent OFETs. Dr. Chengang Ji is an expertise in optics, and I thank him for the optical simulations of my devices. Moreover, thanks to the discussion about device physics with Dr. Chad Huard, also about the equipment and laboratory maintenance with Suneel. Many visiting students, including Qingyu Huang, Zhengmei Yang and Danyan Wang offer their help for the experiments and simulations. Besides, I also appreciate the help provided by Dr. Xiaojian Zhu, Da Li and Eunseong Moon from other groups for the photolithography processes and surface characterizations. I am expecting that I could spend more time with so many supportive colleagues.

I also would like to thank my advisors and colleagues before joining this group. If I did not get chances to learn the fabrication techniques and do the research on the thin film devices, I would not be able to get familiar with the experiment facilities and device design so fast, which helped me avoid many possible mistakes during my PhD studies.

The extensive friendships from EECS as well as other departments, such as ME, Information, Math, Business, Law, LSA and so on, made the Ann Arbor a paradise to acquire many different opinions and interact with many different personalities, which opens more colorful aspects of my daily life.

Finally and importantly, I would like to dedicate my PhD works to my parents and all of my family members. They are consistently providing economic and mental supports for my whole education journey, and also make my life full of happiness all the time. Without their support from the very beginning, I am not able to complete my PhD program, the highest academic degree.

### **Table of Contents**

| Dedication   | ii                                                                  |

|--------------|---------------------------------------------------------------------|

| Acknowled    | gementsiii                                                          |

| List of Figu | res x                                                               |

| List of Tabl | es xvi                                                              |

| List of App  | endices xvii                                                        |

| Abstract     | xviii                                                               |

| Chapter 1    | Introduction and Background Review1                                 |

| 1.1          | Basic Properties of Amorphous Silicon1                              |

| 1.2          | PECVD Deposition of Amorphous Silicon7                              |

| 1.3          | Working Principles of the Solar Cells and Photodiodes9              |

| 1.4          | Compact Model for Solar Cells or Photodiodes11                      |

| 1.5          | Extensive Devices Based on a-Si Active Layers                       |

| 1.6          | Auger Electron Spectroscopy (AES) 19                                |

| 1.7          | Overview of the Transparent Electronics                             |

| 1.8          | Dissertation Organization                                           |

| Chapter 2    | The Influence of Interfacial Materials on the Dipole Induced in     |

|              | Polyethylenimine Layer of Cathode Contacts                          |

| Ab           | stract                                                              |

| 2.1          | Introduction                                                        |

| 2.2          | Device Structure and Fabrication                                    |

| 2.3          | Characterizations for Surface Morphology and IV Behaviors           |

| 2.4          | Further Analysis for the Dipole Induced in PEI Interlayers          |

| 2.5          | Surface Analysis by AES and IV Curves for Other Cathodes 41 $_{vi}$ |

|         | 2.6 | Conclusion 42                                                          | 2  |

|---------|-----|------------------------------------------------------------------------|----|

| Chapter | 3   | Interfacial Modulation of Metal Oxide Enabling Centimeter Scale non    | i- |

|         |     | Electrode Area for Solar Cell Devices                                  | 4  |

|         | Abs | tract                                                                  | 4  |

|         | 3.1 | Introduction                                                           | 4  |

|         | 3.2 | Device Structure and Fabrication                                       | 7  |

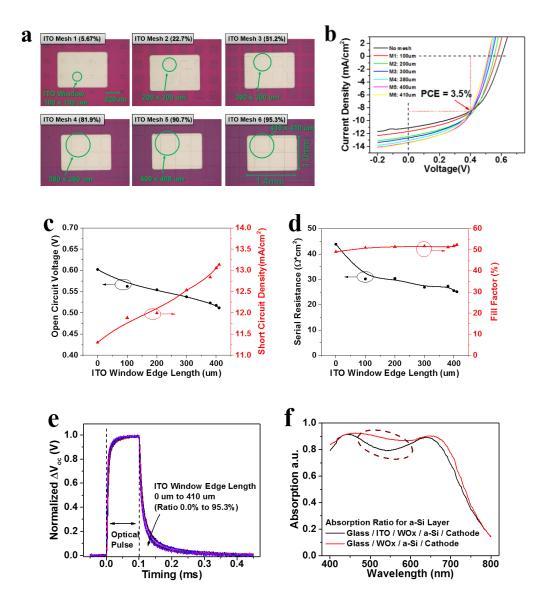

|         | 3.3 | The a-Si Solar Cell Devices with Different ITO Window Ratios           | 8  |

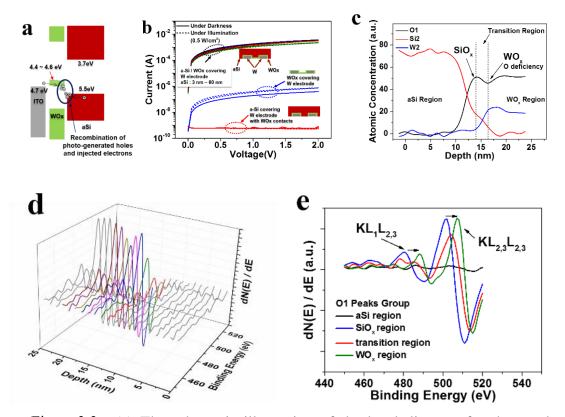

|         | 3.4 | Investigation on the Interfacial Properties of WO <sub>x</sub> /a-Si   | 0  |

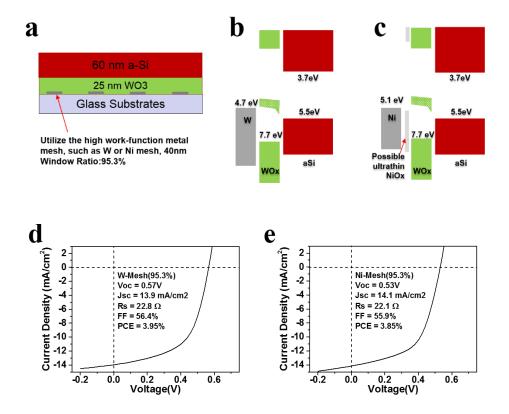

|         | 3.5 | The a-Si Solar Cell Devices Based on Ultra-sparse Metal Meshes 54      | 4  |

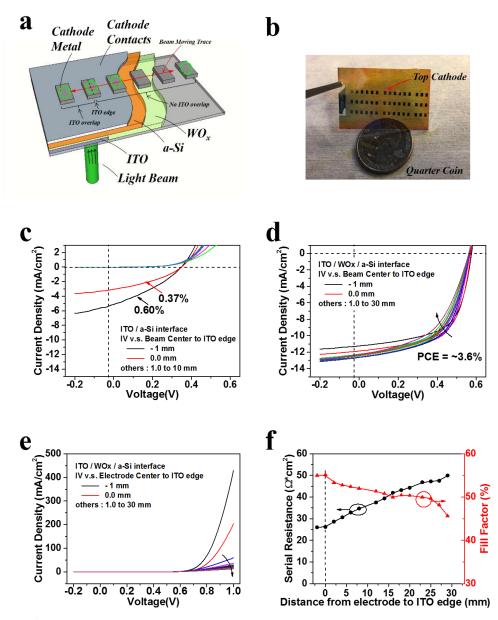

|         | 3.6 | Dimension Limitation for the Non-Electrode Area                        | 5  |

|         | 3.7 | Conclusion                                                             | 7  |

| Chapter | 4   | Top Cathode Contacts for a-Si Photodetectors towards Fingerprin        | ıt |

|         |     | Sensing Array                                                          | 8  |

|         | Abs | stract                                                                 | 8  |

|         | 4.1 | Introduction                                                           | 8  |

|         | 4.2 | Device Design and Fabrication                                          | 9  |

|         | 4.3 | Opto-electrical Characterizations for the Large Area a-Si PD 60        | 0  |

|         | 4.4 | Fabrication and Characterizations of a-Si PD Short Linear Array 6      | 6  |

|         | 4.5 | Conclusion 7                                                           | 1  |

| Chapter | 5   | Inverted Device Design of a-Si Photodetectors for the Integration with | h  |

|         |     | TFT Array Backplanes                                                   | 3  |

|         | Abs | tract                                                                  | 3  |

|         | 5.1 | Introduction                                                           | 3  |

|         | 5.2 | Device Structure and Fabrication7                                      | 5  |

|         | 5.3 | IV Characterizations for Large Area Devices                            | 6  |

|         | 5.4 | Fabrication and Characterizations for Pixel Devices            | 79   |

|---------|-----|----------------------------------------------------------------|------|

|         | 5.5 | Conclusion                                                     | . 87 |

| Chapter | 6   | Photo Excited Artificial Synapses Based on Amorphous Silicon   | and  |

|         |     | Polyethylenimine Interfaces                                    | 88   |

|         | Abs | stract                                                         | 88   |

|         | 6.1 | Introduction                                                   | . 88 |

|         | 6.2 | Device Structure and Fabrication                               | . 90 |

|         | 6.3 | IV Sweep Hysteresis and Mechanisms                             | . 91 |

|         | 6.4 | Current Response under Pulse Stimuli                           | . 96 |

|         | 6.5 | Response Decay and Timing Dependent Plasticity                 | 98   |

|         | 6.6 | Conclusion                                                     | 101  |

| Chapter | 7   | Highly Transparent Resistive Switching Devices Based on Optic  | ally |

|         |     | Optimized Dielectric / Metal / Dielectric Structure            | 102  |

|         | Abs | stract                                                         | 102  |

|         | 7.1 | Introduction                                                   | 102  |

|         | 7.2 | Device Structure and Fabrication                               | 103  |

|         | 7.3 | IV Sweeps for the Devices Based on Ultrathin Doped Metal Films | 105  |

|         | 7.4 | Verification for the Origin of the Hysteresis                  | 107  |

|         | 7.5 | Conduction Mechanisms and Continuous Resistive Switching       | .110 |

|         | 7.6 | Conclusion                                                     | .113 |

| Chapter | 8   | Air-Stable Ultrathin Copper Based Composite Metal Electrodes   | for  |

|         |     | Transparent Organic Thin Film Transistors                      | .114 |

|         | Abs | stract                                                         | .114 |

|         | 8.1 | Introduction                                                   | .114 |

|         | 8.2 | Device Structure and Fabrication                               | .115 |

|           | 8.3  | Transmission and Surface Morphologies                        | 117 |

|-----------|------|--------------------------------------------------------------|-----|

|           | 8.4  | IV Characterizations and Contact Resistance                  | 120 |

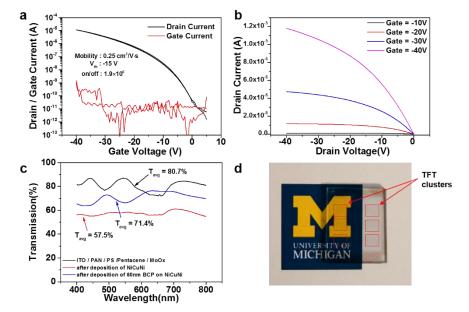

|           | 8.5  | Demonstration of Transparent Pentacene TFTs                  | 122 |

|           | 8.6  | Conclusion                                                   | 123 |

| Chapter   | 9    | Summary and Future Plan                                      | 124 |

|           | 9.1  | Summary                                                      | 124 |

|           | 9.2  | All-inorganic Transparent a-Si Optoelectronic Devices        | 128 |

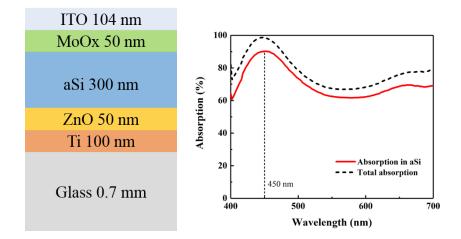

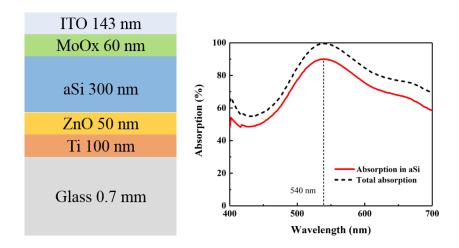

|           | 9.3  | Thickness Modulation of Transparent Top Anode and HTL        | 129 |

|           | 9.4  | Dielectric / Metal / Dielectric for the Top Anode of a-Si PD | 130 |

| Appendi   | ces  |                                                              | 133 |

|           | A.   | Labview Program of the Data Acquiring for Solar Cells        | 133 |

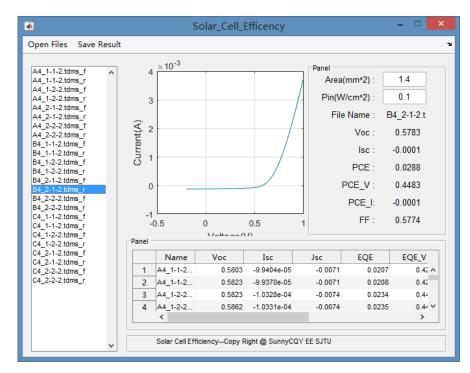

|           | B.   | Matlab User Interface for the Solar Cell Data Analysis       | 135 |

| Bibliogra | aphy | у                                                            | 138 |

# List of Figures

| Figure 1.1  | Silicon ingot after preliminary purifications                              |

|-------------|----------------------------------------------------------------------------|

| Figure 1.2  | The atom lattice for the monocrystalline and amorphous materials 2         |

| Figure 1.3  | Solar cells based on the a-Si fabricated on rigid or flexible substrates 3 |

| Figure 1.4  | Customer electronic products equipped with a-Si solar cells                |

| Figure 1.5  | Schematic structures of crystalline silicon, amorphous silicon, the        |

| dangli      | ng bonds in the amorphous lattice                                          |

| Figure 1.6  | Schematic density of states distribution for an amorphous silicon showing  |

| the bar     | nds, the band tails, and the defect states in the band gap                 |

| Figure 1.7  | Schametic illustration of the conduction mechanisms                        |

| Figure 1.8  | PECVD chamber structure                                                    |

| Figure 1.9  | PECVD Plasmtherm 790 for a-Si deposition                                   |

| Figure 1.10 | The schematic illustration of the solar cells or photodiodes               |

| Figure 1.11 | Schematic of investigated front sides of simple planar solar cells11       |

| Figure 1.12 | Equivalent circuits of a solar cell and photodiode12                       |

| Figure 1.13 | Schematic cross section of a multispectral photodiode on polyimide         |

| substra     | ate and Energy band diagram15                                              |

| Figure 1.14 | Operation concept of molybdenum disulfide amorphous silicon                |

| hetero      | junction photodetector16                                                   |

| Figure 1.15 | Design and performance of the perovskite/silicon tandem cell. IV           |

| charac      | terizations and the efficiency at the maximum power point16                |

| Figure 1.16 | The structures of polymer / a-Si tandem cells17                            |

| Figure 1.17 | Schematic illustration of the integrated PV-EC device under operation      |

| with th     | ne a-Si / a-Si photocathode and a RuO2 anode19                             |

| Figure 1.18 MS signal and SFE values for a wireless Co-OEC   3jn-a-Si   NiMoZn cell                  |

|------------------------------------------------------------------------------------------------------|

| under AM 1.5 illumination in KNO <sub>3</sub> (blue trace)19                                         |

| Figure 1.19 Two views of the Auger process                                                           |

| Figure 1.20 Non-smoothed Si AES peaks for silicon oxide and elemental Si22                           |

| Figure 1.21 Device structure and optical property                                                    |

| Figure 1.22 IV characterizations for the semitransparent solar cell devices with                     |

| different Ag electrode thicknesses24                                                                 |

| Figure 1.23 Principles of the commercialized visible transparent solar cell panels25                 |

| Figure 1.24 Schematic illustration of the device structure and energy-band diagram of                |

| the Transparent QLED25                                                                               |

| Figure 1.25 Structure of the proposed transparent DPh-BTBT TFTs                                      |

| Figure 1.26 Fabrication process of the ITO/Al <sub>2</sub> O <sub>3</sub> /G device and SEM image of |

| graphene square dots27                                                                               |

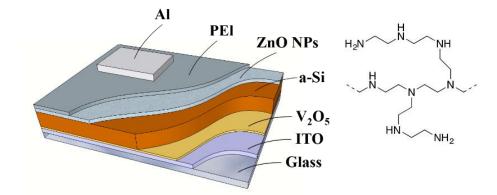

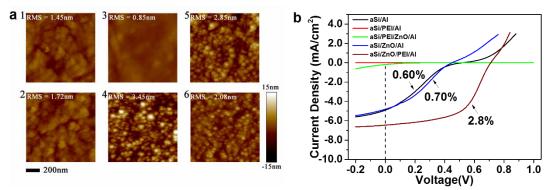

Figure 2.1 The schematic of the devices fabricated based on ZnO NPs and PEI....34

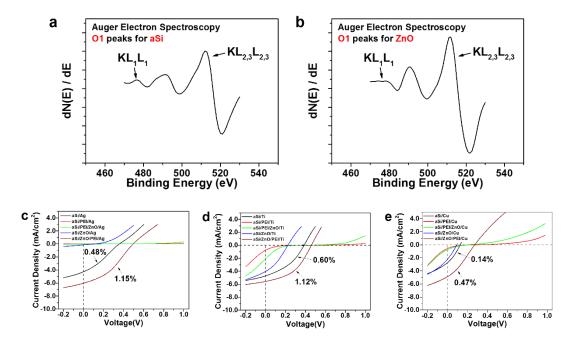

- Figure 2.4 Auger Electron Spectroscopy (AES) characterizations for a-Si (a) and ZnO NPs (b). The IV characterizations for devices with Ag, Ti and Cu (c-e)....41

| Figure 3.3 | (a) The schematic illustration of the band diagram for the anode contacts.              |

|------------|-----------------------------------------------------------------------------------------|

| (b) The    | e lateral conductivity measurement for the WO <sub>x</sub> /a-Si interfaces. (c) Atomic |

| concer     | ntration depth profile                                                                  |

| Figure 3.4 | Device design, IV characteristics and the band diagram illustration for the             |

| a-Si so    | olar cell devices based on ultra-sparse W or Ni metal meshes54                          |

Figure 3.5 Investigation of the dimension limitation for the non-electrode area.....56

| Figure 4.1  | The schematic illustration of the device design60                        |

|-------------|--------------------------------------------------------------------------|

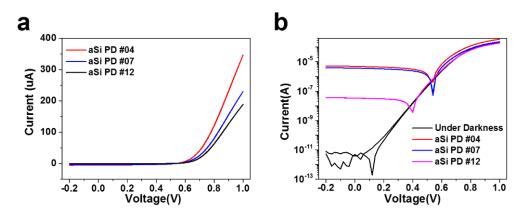

| Figure 4.2  | IV characterizations for the devices with top cathodes                   |

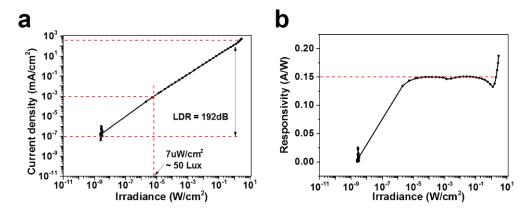

| Figure 4.3  | The characterizations for the linear dynamic range, responsivity and     |

| externa     | al quantum efficiency, under white illumination63                        |

| Figure 4.4  | The characterizations for the linear dynamic range, responsivity and     |

| externa     | al quantum efficiency, under green illumination64                        |

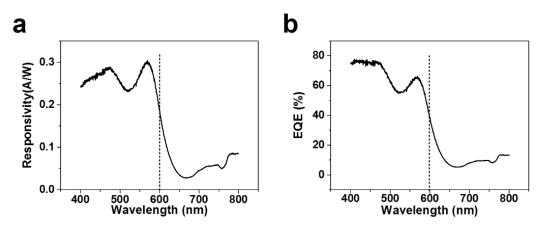

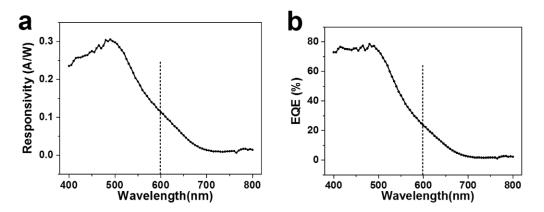

| Figure 4.5  | The responsivity and EQE under the x-axis of wavelength65                |

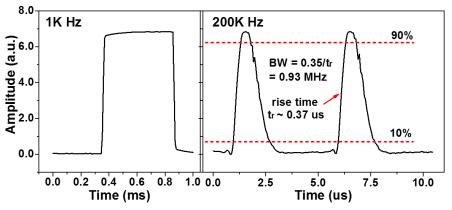

| Figure 4.6  | The transient response and the bandwidth under rectangular waveform      |

| stimul      | us of the light source                                                   |

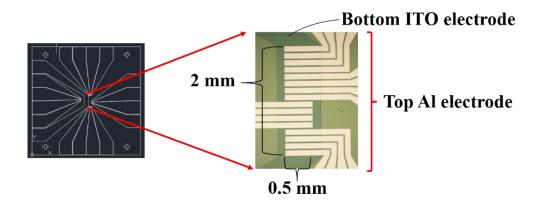

| Figure 4.7  | The layout and image for the short linear array of 16 pixels67           |

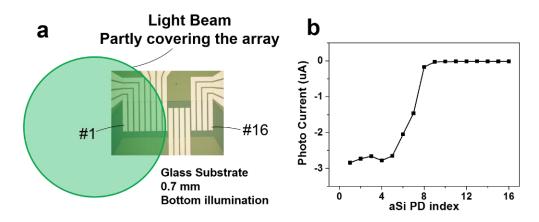

| Figure 4.8  | Schematic illustration of the test configuration for a-Si PD array, and  |

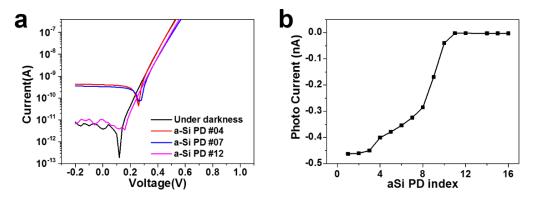

| compa       | rison of photocurrent obtained from the 16 pixels                        |

| Figure 4.9  | Selected IV curves for the a-Si PD arrays                                |

| Figure 4.10 | The characterizations for the linear dynamic range and responsivity69    |

| Figure 4.11 | Selected IV curves for the a-Si PD arrays                                |

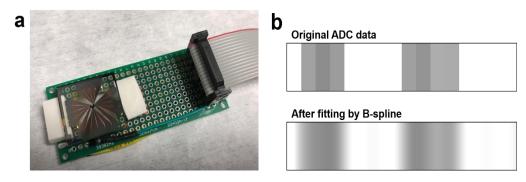

| Figure 4.12 | Peripheral socket for the mounting of the short linear array sample, and |

| the ori     | ginal ADC data collected by the Arduino Microcontroller70                |

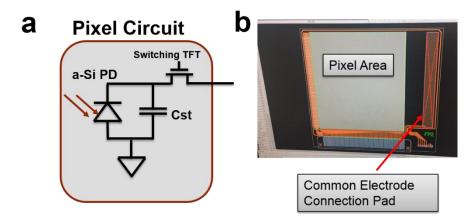

| Figure 5.1  | The pixel circuit for the a-Si PD matrix and the layout design for the dem | 0 |

|-------------|----------------------------------------------------------------------------|---|

| of the      | fingerprint sensing7                                                       | 5 |

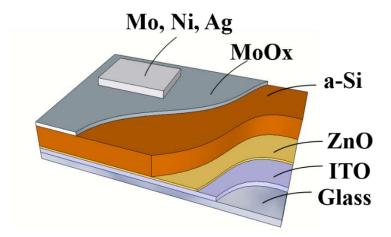

| Figure 5.2  | Device design with inverted architecture                                   | 6 |

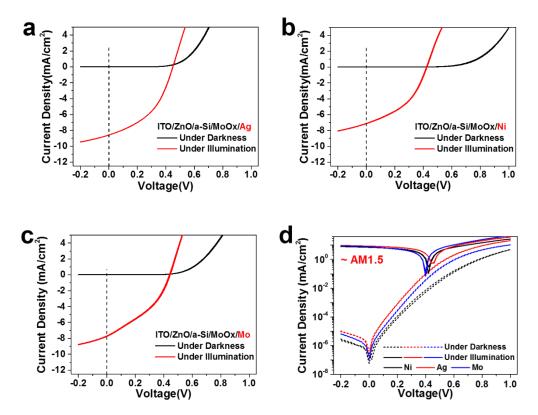

| Figure 5.3  | IV characterizations for the devices with Ag, Ni and Mo7                   | 7 |

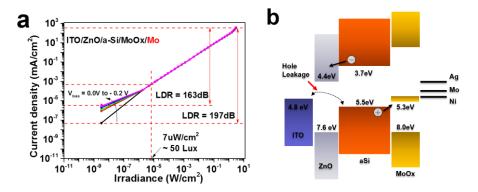

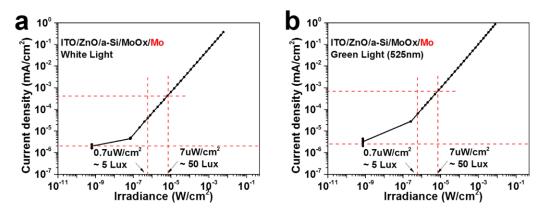

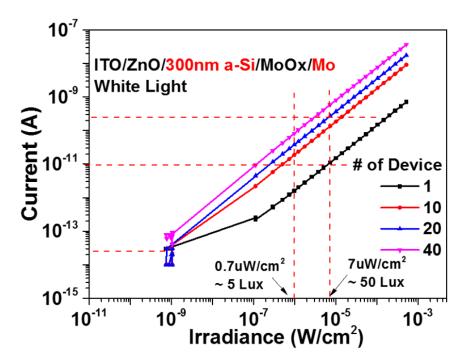

| Figure 5.4  | LDR characterizations for a-Si PDs with top Mo anode7                      | 8 |

| Figure 5.5  | The responsivity and EQE of the inverted a-Si PDs7                         | 9 |

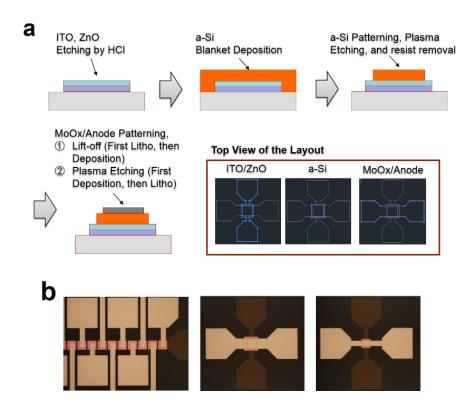

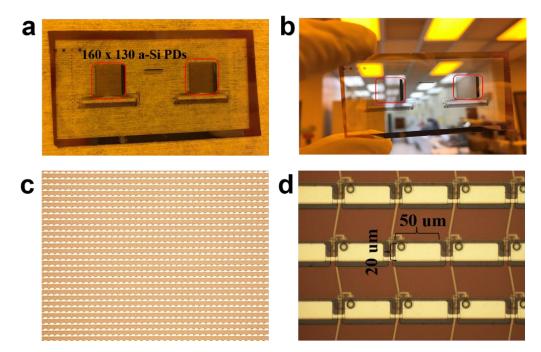

| Figure 5.6  | Fabrication procedure and layout design for the small area a-Si PDs8       | 0 |

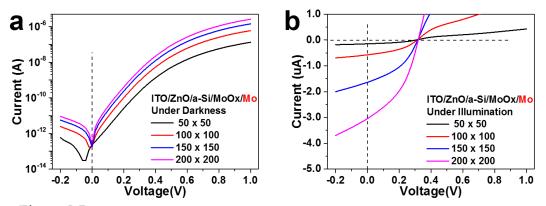

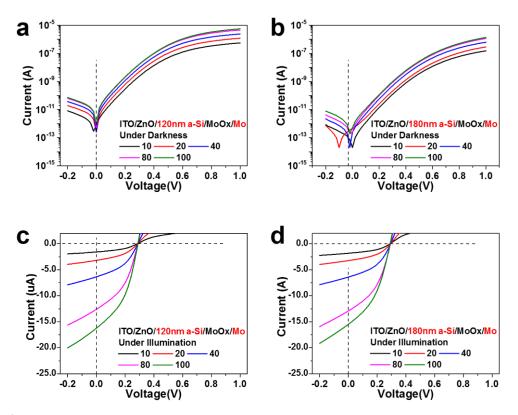

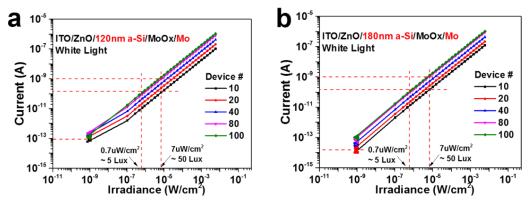

| Figure 5.7  | IV characterizations for the small area a-Si PDs8                          | 1 |

| Figure 5.8  | LDR characterizations for the small area a-Si PDs                          | 1 |

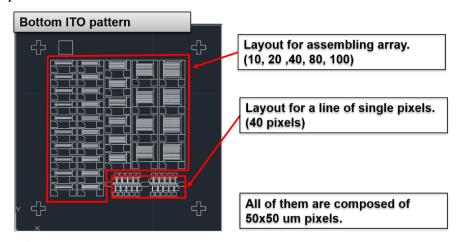

| Figure 5.9  | Photo mask layout design for the assembling arrays                         | 2 |

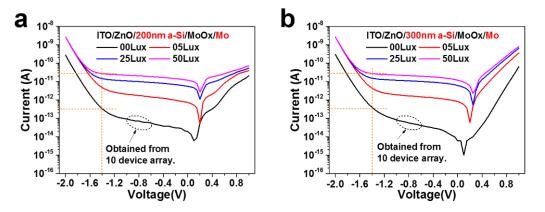

| Figure 5.10 | IV characterizations for the a-Si PD arrays                                | 3 |

| Figure 5.11 | LDR characterizations for the a-Si PD arrays                               | 4 |

| Figure 5.12 | The leakage current under reversed biases                                  | 4 |

| Figure 5.13 | LDR characterizations for the a-Si PD arrays                               | 5 |

| Figure 5.14 | Integration of the a-Si PD matrix with the TFT backplane                   | 6 |

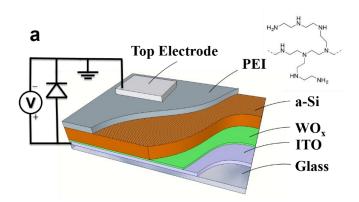

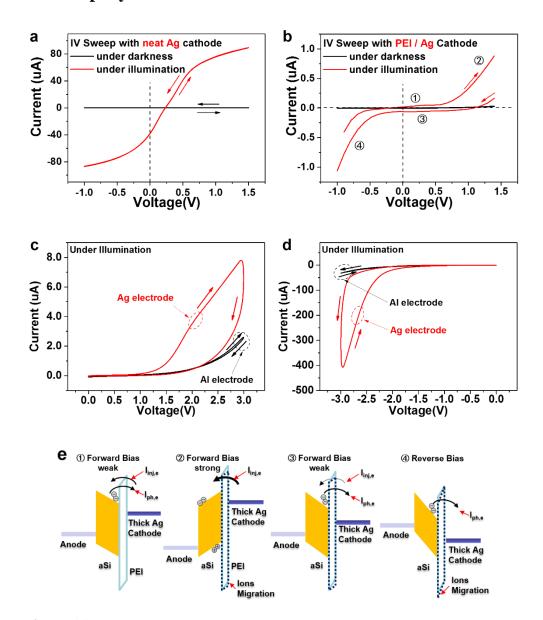

| Figure 6.1 | Schematic illustration of the PEAS device design, equivalent circuit and |

|------------|--------------------------------------------------------------------------|

| the ch     | emical structure of the polymer PEI (inset)9                             |

| Figure 6.2 | IV characteristics and corresponding hysteresis, and the schemati        |

| illustr    | ation for the proposed mechanism9                                        |

| Figure 6.3 | The conduction mechanism analysis for initial sweeps94                   |

| Figure 6.4 | Current response after 100 ms pulse stimuli, and the comparison for the  |

| PEAS       | devices with different PEI thicknesses                                   |

| Figure 6.5 | The current response for the increasing light intensity                  |

| Figure 6.6 | Timing dependent plasticity for  | the pre- / post-spikes | without overlapping, |

|------------|----------------------------------|------------------------|----------------------|

| under      | larkness (black) or illumination | (blue)                 |                      |

| Figure 7.1 | The schematic of the resistive switching devices, transmission spectrum,  |

|------------|---------------------------------------------------------------------------|

| and th     | e SEM characterization104                                                 |

| Figure 7.2 | The consecutive IV sweep characterization under positive voltages or      |

| under      | negative voltages                                                         |

| Figure 7.3 | The consecutive IV sweeps for control samples, and the the oxidation      |

| states     | for WO <sub>x</sub> films108                                              |

| Eiguro 7 4 | The continuous IV sweeps for both polarities, the normalized conductivity |

Figure 9.1 Transparent a-Si photodetector devices with top ITO anodes......128

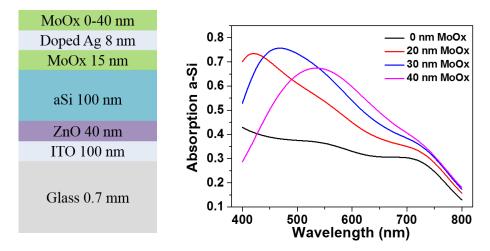

| Figure 9.3                                             | Top illumination a-Si device design and the corresponding absorption |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------|--|--|

| spectr                                                 | um with a peak located at 450 nm130                                  |  |  |

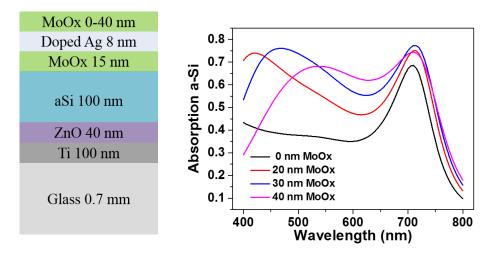

| Figure 9.4                                             | Top illumination a-Si device design and the corresponding absorption |  |  |

| spectr                                                 | um with a peak located at 540 nm130                                  |  |  |

| Figure 9.5                                             | Transparent a-Si device designs based on bottom ITO cathode and the  |  |  |

| transp                                                 | arent top DMD configuration131                                       |  |  |

| Figure 9.6                                             | Top illumination a-Si device designs based on reflective bottom Ti   |  |  |

| electrode and the transparent top DMD configuration131 |                                                                      |  |  |

|                                                        |                                                                      |  |  |

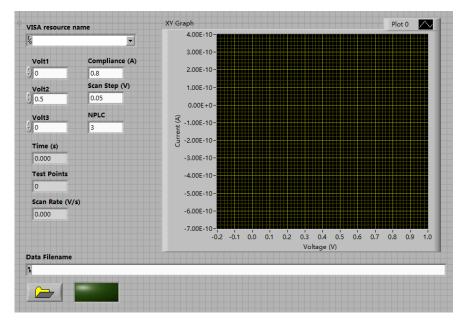

| Figure A1. | Image of the Labview User Interface of the data acquiring for the IV     |

|------------|--------------------------------------------------------------------------|

| charac     | cterizations of solar cell devices                                       |

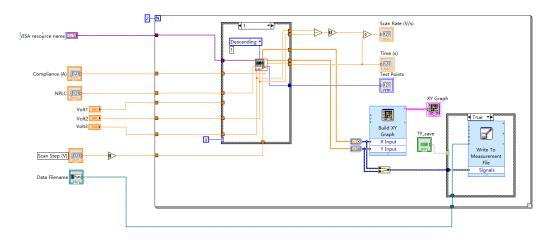

| Figure A2. | The block diagram configuration of the Labview User Interfaces for the   |

| Solar      | Cell characterizations                                                   |

| Figure B1. | Matlab User Interface for the post data analysis                         |

| Figure B2. | Code samples for the modules of loading data files and saving results to |

| the ex     | cel files                                                                |

## List of Tables

| Table 2.1 | The extracted parameters for the different devices | 36  |

|-----------|----------------------------------------------------|-----|

| Table 8.1 | The thermal and air-stability characterization     | 117 |

# List of Appendices

| A. | Labview Program of the Data Acquiring for Solar Cells  | 133 |

|----|--------------------------------------------------------|-----|

| B. | Matlab User Interface for the Solar Cell Data Analysis | 135 |

#### Abstract

In this dissertation, we extensively studied intrinsic amorphous silicon (a-Si) hybrid structure with inorganic / organic materials and explored the potential practical applications. Meanwhile, we still stepped into the various transparent electronic devices, including the transparent organic TFTs and memristors based on the developed transparent ultrathin metal film electrodes.

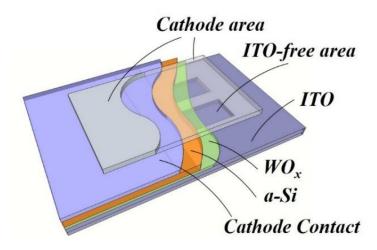

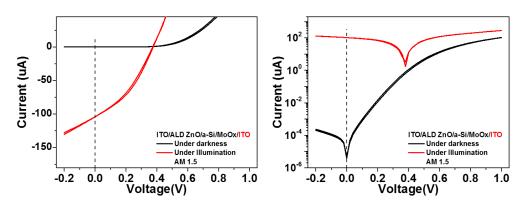

Top cathode contacts based on the conjugated organic materials were developed in our group, we further developed the air-stable cathode contacts based on the Polyethylenimine (PEI) and ZnO interlayers. We found the dipole induced in the PEI layers is highly related to the surface properties of the adjacent interlayers. The dipole between ZnO / PEI interlayers is supposed to be overcome by another one induced between PEI and cathode metal. Then we move to the investigation on the bottom anode contacts. We analyzed the band diagram and the carrier lateral transportation of the WOx / a-Si interfaces. We found the WOx / a-Si interface is able to to support centimeter-scale non-electrode area, without the additional conductive layers. From the developed anode and cathode contacts, we further characterized the electrical performance of the a-Si devices as photodetectors (PD), and re-designed device structure towards the applications of in-screen fingerprint scanners. The a-Si PDs with top cathode contacts based on ZnO NPs and PEI interlayers can achieve the LDR up to 190 dB, and at least 4 orders for the illuminations < 50 Lux. The current sequence in the short linear arrays exhibited good ratio up to 2 orders. The inverted a-Si PD with bottom cathode contacts were developed and characterized to fulfill the requirements of the architecture design for the sensing arrays. The ZnO and MoOx are employed as the ETL and HTL. The current leakage and LDR are analyzed for different a-Si thicknesses and device areas. Finally, the optimized a-Si PD arrays are fabricated on the LTPS TFT backplanes. In order to meet the development opportunities for the neuromorphic computation, innovative artificial synapses were demonstrated based on the interactions between the a-Si and PEI interlayers. The hysteresis and timing dependent plasticity of the artificial synapses can be excited by light illumination, coupled with electrical pulse stimuli. The device design is promising to serve as fundamental elements for neuromorphic functionalities towards the simultaneous visual information process in large-area electronics or IoT.

Transparent electronics is the hot research area to promote the information interactions. We also fabricated transparent devices based on the ultrathin transparent metal films and the corresponding optical management. Transparent resistive switching devices were demonstrated based on ultrathin doped Ag films and optically optimized dielectric / metal / dielectric structure. The overall transparency is higher than 80%, and the device conductance modulation is found to be analog and continuous. Transparent organic TFTs were achieved based on ultrathin Cu-based composite electrodes with Ni seeding and capping layers. The transparency is up to 71.4 % for the source/drain regions and even higher for the overall transparency.

Finally, based on the developed a-Si photodetectors, we proposed the potential development optimizations. The first one is the transparent a-Si optoelectronic devices based on all-inorganic interlayers. Then the optical design can be further conducted to modulate the absorption spectrum of a-Si active layers as well as the exterior apparent colors.

#### Chapter 1 Introduction and Background Review

#### **1.1 Basic Properties of Amorphous Silicon**

Silicon (Si) is a chemical element with the atomic number of 14, which defines the properties as tetravalent metalloids and semiconductors. It is a hard and brittle crystalline solid with a blue-grey metallic lustre, as shown in Figure 1.1. Silicon is the eighth most common element in the universe by mass, but very rarely occurs as the pure element in the Earth's crust, most widely distributed in dusts, sands, planetoids, and planets as various forms of silicon dioxide (silica) or silicates. More than 90% of the Earth's crust is composed of silicate minerals, making silicon the second most abundant element in the Earth's crust (about 28% by mass) after oxygen. [1]

Figure 1.1 Silicon ingot after preliminary purifications. (Reproduced from [1]).

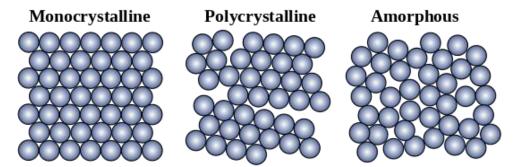

Si is a fourfold coordinated atom that is normally tetrahedrally bonded to four neighboring silicon atoms. According to the organization of the atom lattice, we can classify it as crystalline silicone, poly-crystalline silicon, and amorphous silicon, as shown in Figure 1.2. In the crystalline silicon, the tetrahedral structure continues over a large range, thus forming a well-ordered crystal lattice. In the poly-crystalline silicon, the ordered tetrahedral structure only continues over a short range, just like the tight stacking of small grains. However, it forms a random orientation in a long range. In the amorphous silicon, the long range order is not present. Rather, the atoms form a continuous random network. [2]

Figure 1.2 The atom lattice for the monocrystalline, polycrystalline and amorphous materials, which are long range ordered, short range ordered and disordered, respectively. (Reproduced from [2]).

Silicon is the important and fundamental semiconductor materials in the integrated circuit industries. The silicon can be doped by phosphorus (P) atoms (5 valence electrons) or boron (B) atoms (3 valence electrons). The P atom can contribute a free electron to the Si lattice to form a closed and paired outer shell with neighboring Si atoms, creating the excess n-type carriers, and demoted as N-doping. On the contrary, the B atom will take an electron away from the Si lattice to form a closed and paired outer shell with neighboring Si atoms, creating the excess p-type carriers and demoted as P-doping.[3] Utilizing different doping types and profiles, we can create N-channel or P-channel FETs on Si wafers, and thus build the complete hierarchy of the integrated circuits from the fundamental devices.[4] As promoted by the stringent requirement for a lower cost and the continuous evolving of the photo-lithography technology, the channel length is gradually shrinking to only 1s nanometers, as predicted or guided by the Moore's law.[5] Besides being used as semiconductor material in the FETs for the

purpose of logic calculation, the crystalline Si is also a fundamental semiconductor materials for the opto-electronic devices or chips, such as the Si photodiodes or CMOS image sensors embedded in the DSLR cameras.[6-8]

Polycrystalline Si is becoming an important semiconductor candidate for the transistors used in the active matrix driving the high resolution and large area Flat Panel Display screens, because of its high mobility and easy fabrication process from the amorphous Si. Moreover, polycrystalline Si has been widely used in the solar cell industries, as a basic semiconductor material for the standard 6 inch square solar cell panels. The panels can be assembled to make the large-scale solar cell plants and provide power for houses, offices, or even factories.[9]

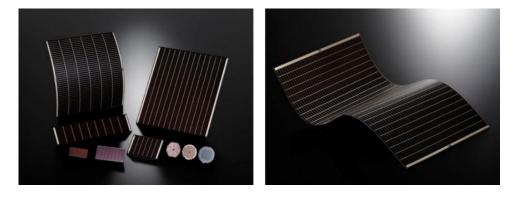

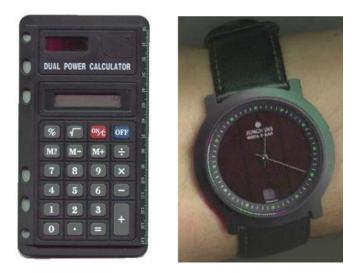

Amorphous Si (a-Si) was the dominant semiconductor material for the commercialized thin-film transistors (TFTs) fabricated for the active matrix backplanes in TFT-LCDs, owing to its low cost and easy deposition.[10] Meanwhile, a-Si is also extensively used in the solar cells. Because of the low deposition temperature, it can be deposited on a variety of rigid or flexible substrates, such as glass, metal or even PI films, as shown in Figure 1.3.[2] However, it is suffering a low efficiency because of the high trap density, determining its main target market is the customer electronics with low power consumptions, such as calculators or digital watches, as shown in Figure 1.4.

Figure 1.3 Solar cells based on a-Si, fabricated on the rigid or flexible substrates. (CopyRight @ Amorton)

Figure 1.4 Customer electronic products (calculators and watches) equipped with a-Si solar cells. (Reproduced from [2])

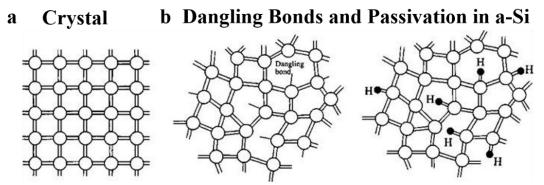

Although the silicon atoms have 4 valence electrons ready to be paired with the neighbor atoms, not all the atoms within a-Si are fourfold coordinated in a-Si. Part of the Si atoms have unpaired valence electrons and the corresponding dangling bonds due to the disordered nature of the material, as shown in Figure 1.5. The dangling bonds mean the defects in the random network of the atom lattice, which limits the electrical performance of a-Si used for transistors, solar cells or photodiodes. Fortunately, the dangling bonds can be passivated by hydrogen (H) atoms, since H atoms have one valence electron, which can be paired with the unpaired valence electron in the dangling bonds. Just because of the H passivation, a-Si can be named as Hydrogenated amorphous silicon (a-Si:H), which has a sufficiently low amount of defects, particularly in the protocrystalline growth regime. People usually use the short name "a-Si" instead of "a-Si:H", without special notifications, since the hydrogenated a-Si is a standard deposition process for a-Si. However, hydrogenation is highly related to light-induced degradation of the material, described as Staebler-Wronski effect (SWE). The most favoured explanation is the H bond switching model, where the weak Si-Si bonds can be broken by the non-radiative energy released from the recombination of the photoexcited electrons and holes, and a back-bonded H atom prevents the restoration of the broken bond by a bond switching event. [2, 11-13]

Figure 1.5 Schematic structures of crystalline silicon, amorphous silicon, the dangling bonds in the amorphous lattice and the corresponding hydrogenation passivation for the dangling bonds. (Reproduced from [2]).

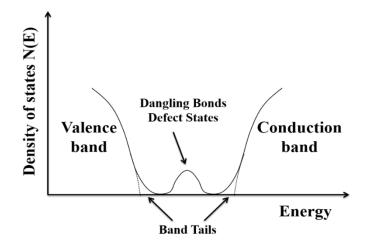

As we know, the a-Si is just named from its long-range structure disorder, which means the wave functions for the random atom lattice can not be sufficiently and uniformly overlapped, resulting in no sharp edges for the conduction bands and valence bands. Referring to the band diagram shown in Figure 1.6, there are band tails near the band bottom or top, which behaves as shallow traps and plays an important role for the carrier transportation. Meanwhile, the dangling bonds create defect states in the midgap, thus create a secondary conductive pathway and introduce additional leakage for the a-Si devices.[14]

Figure 1.6 Schematic density of states distribution for amorphous silicon, showing the bands, the band tails, and the defect states in the band gap. The dashed curves are the equivalent density of states in a crystalline silicon. (Reproduced from [14])

Figure 1.7 Schematic illustration of the conduction mechanisms related to the amorphous silicon. (Reproduced from [14])

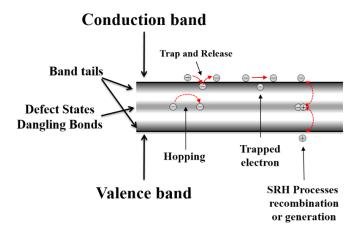

There are several electronic processes related to the conduction / valence bands, band tails as well as the defect states induced by dangling bonds, as shown in Figure 1.7. We use electron transportation as an example to clarify the electronic processes. Usually, the electron transportation occurs near the bottom edge of the conduction band, which defines the mobility of the electrons. Because of the shallow traps in the band tails, the electrons can get trapped, then released through the thermal excitation, which is mainly considered as ohmic conduction. When the electrons approaching a trap filled by a trapped electron, they will go over the traps without being trapped, indicating a higher mobility or conductance, which occurs during the strong injection or generation of carriers in a-Si. Moreover, the defects induced by the dangling bonds are very deep from the band edges. If electrons dropped to those states, it is possible for them to hop between the adjacent states through the tunneling processes, which can be promoted at elevated temperatures, and will produce unexpected leakage between the interlayers or contacts sandwishing the a-Si layers. The traps or defects distributed between the conduction band and valence band can serve as the centers to assist Shockley-Read-Hall (SRH) processes, including the recombination or generations, which will adversely affect on the opto-electronic conversion efficiency and increase the current leakage.[15]

#### **1.2 PECVD Deposition of Amorphous Silicon**

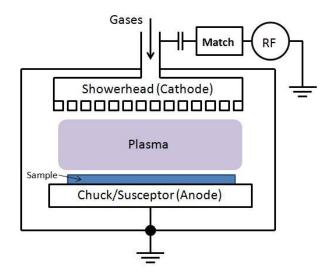

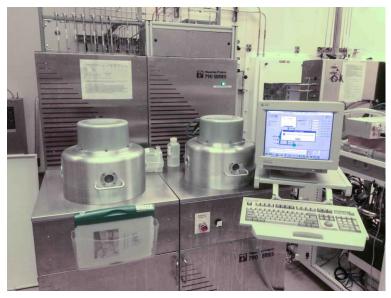

Chemical Vapor Deposition (CVD) is the standard method for the deposition of a-Si, including the Low Pressure CVD (LPCVD) and Plasma Enhancement CVD (PECVD). PECVD is utilizing the plasma atmosphere to provide additional energy for the reactive gas, thus requiring a lower process temperature, compared with the LPCVD. The chuck temperature in PECVD chamber is usually in 200 - 400 °C, while the LPCVD is around 425 – 900 °C. The energy supplied by plasma provides the key advantage of reduced process temperatures for PECVD, compared to LPCVD where all of the energy for reaction is supplied thermally. Therefore, the PECVD allows the deposition on a large variety of substrates, including on glass, metal, or even plastic films. As shown in Figure 1.8, the reactant gases flow to the process chamber through a shower head which is a large perforated metal plate located above the sample, and produce a uniform distribution of the gas flow over the sample surface. The 13.56 MHz RF power is used to generate the plasma, and the electrons with high energy in the plasma ionize or dissociate the reactant gases to generate more chemical reactive radicals. These radicals react to form the thin films of deposition on top of the sample. The following equations are the typical reactions for the Si-based materials, including silicon nitride, silicon oxide, silicon oxynitride, as well as a-Si. The Plasmatherm 790 is the equipment model for the a-Si films we are using, which includes PECVD and RIE chambers at the same time, as shown in Figure 1.9. [16]

$$SiN_{x} : SiH_{x} + NH_{x} \longrightarrow SiN_{x} (+H_{2})$$

$$SiO_{x} : SiH_{x} + N_{2}O \longrightarrow SiO_{x} (+H_{2} + N_{2})$$

$$SiON_{x} : SiH_{x} + N_{2}O + NH_{3} \longrightarrow SiON_{x} (+H_{2} + N_{2})$$

$$aSi : H_{x} : SiH_{x} \longrightarrow Si (+H_{2})$$

Figure 1.8 PECVD chamber structure, including the chuck, sample, shower head and the gas supplying. (Reproduced from [16])

The quality of a-Si active layers is highly related to the deposition conditions. The pressure is determined by the collisions of the gas molecules, which greatly influence the location of the reactions, in the gas flow or on the sample surface. A proper gas flow rate can maintain the supplying of the reactive radicals, and get rid of the depletion. RF power is used to control the dissociation rate, then determines the deposition rate. Meanwhile, the substrate temperature also influences the reaction speed on the sample surface. The deposition rate is supposed to be optimized to guarantee the quality of the a-Si films.

Figure 1.9 PECVD Plasmtherm 790 for a-Si deposition, which is used for the a-Si active layers in the devices we worked on.

#### **1.3 Working Principles of the Solar Cells and Photodiodes**

Both of Solar Cells and Photodiodes are used to convert the light illuminations to the electricity, and share the same fundamental working principles to maximize the collection efficiency of the photo-generated carriers. However, solar cells are used to provide power to the external load, while the Photodiode is used to detect the light intensity from the external illumination, which determines the different characterization specifications or optimization aims.

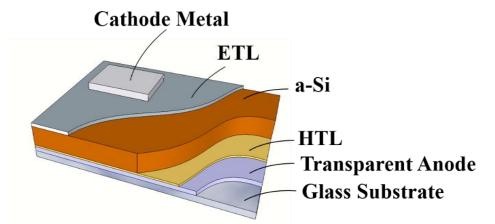

As shown in Figure 1.10, the basic devices of a-Si Solar Cells or Photodiodes are composed of transparent substrate and anode, hole transportation layer (HTL), a-Si active layer, electron transportation layer (ETL) and the top cathode metal. Usually, p-doping and n-doping a-Si interlayers are used for the HTL and ETL, respectively, to form the p-i-n structure. The generation and separation of the photo-generated electron-hole pairs mainly occur in the a-Si layer since the highest electric field drops in the a-Si layer, and the HTL or ETL are used to form good contacts with anode or cathode maximizing the carrier collection efficiency. Anode is usually placed at the incident illumination side allowing the holes to traverse a shorter average distance to the anode because of its lower mobility than the electrons. [17, 18]

Figure 1.10 The schematic illustration of the devices, for the solar cells or photodiodes, which includes the substrates, transparent anode, HTL, active layer, ETL and the top cathode metal.

Conventionally, the p-doped and n-doped a-Si layers are used as HTL and ETL, respectively. The dopants are introduced during the PECVD deposition of a-Si layers

with the gas phase molecular containing P or B atoms, such as PH<sub>3</sub> or BH<sub>3</sub>.[19] The P atom can contribute one excess electron, while the B atom can contribute one excess hole. Correspondingly, the Fermi levels will be modulated to approach to the CB in ndoped layer, and to the VB in p-doped layer. The biggest advantage of the doped a-Si layers is the homo-junctions to the sandwished intrinsic a-Si active layers, which means compatible deposition processes, and good affinity or contacts by doping dose profile modulations. However, some drawbacks still exist. Firstly, the doped a-Si layers need a certain thickness to contain sufficient dopants and realize the roles in the electronic structure as contacts, typically weak 10s nm. The light illumination for the intrinsic a-Si layer will be reduced because of the similar band gap and absorption coefficients of the doped or intrinsic layers, thus resulting in the unnecessary efficiency reduction. Moreover, the electron-hole pairs are still generated in the doped layer, and they will be recombined quickly, because of the high excess carriers, the recombination centers induced by the ionized dopants, as well as the low electric field. Therefore, the photons absorbed in the doped layers do not actually contribute to the photo-electric conversion.[14]

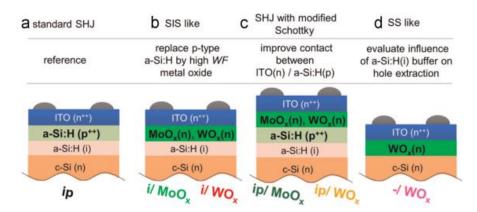

People started to consider apply various metal oxides as HTL for the a-Si devices, which can reduce the light absorption of HTL layers and promote more new electronic properties of the a-Si devices. As shown in Figure 1.11, the authors investigated the interface properties between Moly Oxide or Tungsten Oxide and a-Si layers, and the corresponding thermal stability.[20, 21] Although the metal oxides expand the device design and optimization space, it also means introducing the challenges at the same time for the device design, lifetime or reliability, even for the process compatibility during the commercialization. Most works of this dissertation are based on the heterojunctions of a-Si layers, and we investigate the interactions between metal oxide and a-Si for the devices towards various application scenarios.

Figure 1.11 Schematic of investigated front sides which form the hole selective contact of simple planar solar cells. Above the sketches is the motivation for the respective structure. Below the sketches the acronyms used throughout this work to distinguish between the different structures are shown. (Reproduced from [20])

#### **1.4 Compact Model for Solar Cells or Photodiodes**

The opto-electrical behaviors of the devices are indeed based on the fundamental device physics, and the device modeling can simplify the physical processes and promote the simulations for the fast device design and mechanism explanations. On the other hand, the external systems are more interested in the electrical properties related to the terminals, such as anode/cathode for diode-based devices, or source/drain/gate for the transistor-based devices, not in the detailed electronic processes inside of the devices. Therefore, the compact models are created to provide a conceptual view for the opto-electrical behaviors related to the terminals for the external circuits.

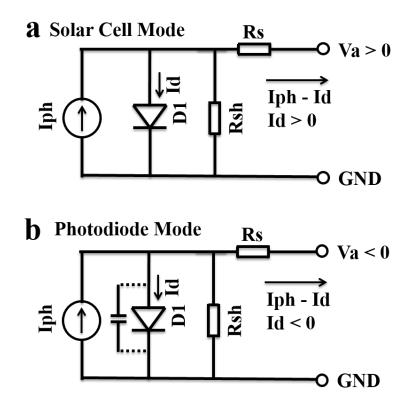

As shown in Figure 1.12, the compact model for the solar cells and photodiode are almost identical, where the basic components include a diode (D1) with a forward current I<sub>d</sub> representing the device configuration for the active layer sandwished by the HTL/anode and ETL/cathode, and a current source representing the photocurrent (I<sub>ph</sub>), without considering the parasitic series resistance (R<sub>s</sub>) and shunt resistance (R<sub>sh</sub>). The biggest difference is the polarity of the applied voltage. The cathode of the diode in the model need to be grounded, and the other terminal was applied by the voltage (V<sub>a</sub>). In the solar cell mode, V<sub>a</sub> > 0, D1 is forward biased with a current I<sub>d</sub> and the I<sub>ph</sub> is counteracted by the I<sub>d</sub>. If the net current (I<sub>ph</sub>-I<sub>d</sub>) > 0, it will follow out to the V<sub>a</sub>, which means the model is providing power to the external loads. In the photodiode mode,  $V_a < 0$ , the D1 is reversed biased with a negative  $I_d$  ( $I_d < 0$ ) and the net current ( $I_{ph}$ - $I_d$ ) > 0. The net current still flows out to the  $V_a$  terminal, which means the model is receiving power supply from external sources. Therefore, they are sharing quite similar device structures, but the solar cells work in the fourth quadrant, and photodiodes work in the third quadrant.

Figure 1.12 Equivalent circuits of solar cells (a) and photodiodes (b). They are sharing almost identical equivalent circuits, including a current source, a diode, shunt resistance and series resistance. On the other hand, the equivalent circuit of photodiode also includes a capacitor for the transient response characterizations. (Reproduced from [22, 23])

Let us further discuss the details for the model. The photodiode (D1) is the key component, representing the recombination through SRH processes or band-to-band transitions. Sometimes, people use two diodes in the model to accurately simulate the opto-electrical behaviors, since different recombination modes occur for the different biases or illuminations. For example, the SRH recombination is limited by the minority carriers under low injection, while it is limited by both types of the carriers under high injection. Moreover, if other recombination or conduction mechanisms are taken into account, such as Auger recombination or tunneling conductions through the barriers, it becomes more challenging for the modeling.[24, 25] Anyway, the one-diode model will give a fast simulation or evaluation for the electrical analysis.

Both of solar cells and photodiodes are producing photocurrent ( $I_{ph}$ ), which stems from the generation and separation of the photo-generated electron-hole pairs, mainly occurring in the photoactive layers, such as in the intrinsic a-Si layers of a-Si devices. Then the electron-hole pairs separate, diffuse through HTL and ETL, then get collected to the anode or cathodes to form the  $I_{ph}$  for the external circuits. Sometimes, the contacts for electrons or holes are not equally perfect, which means one type carriers can not be efficiently collected, resulting in the S-shaped IV curves and a reduced conversion efficiency.[26, 27] The  $I_{ph}$  is usually well proportional to the light illumination intensity, however, it will be limited by the diode leakage current or the measurement precision under ultra-low illumination, and deviates from the linearity under ultra-high illumination because of the voltage-drop on the series resistance.

Back to the  $R_s$  and  $R_{sh}$ , they are key parameters to maximize the photo-conversion efficiency.  $R_s$  is the resistance connected in series to the anode or cathode, which is usually determined by the contact properties, including the energy band matching, surface traps, surface dipoles induced in the interlayers, and so on.  $R_{sh}$  is the resistance connected in parallel to the diode, which is determined by the film quality of the active layers, or the band diagram of the whole device structure. The film with bad quality may contain pin-holes, resulting in the unexpected leakage under voltage biases. If the overall band diagram of the device was not well matched, it will create the electron leakage current to the anode or vice versa. For solar cells,  $R_s$  consumes the power generated by the  $I_{ph}$ , and  $R_{sh}$  equivalently increases the recombination rate for the photogenerated carriers, reducing the  $I_{ph}$  and fill factor, therefore small  $R_s$  and high  $R_{sh}$  are demanded to achieve a high photo-conversion efficiency. On the other hand, in photodidoes, the net current ( $I_{ph} - I_d$ ) is constant for a certain illumination since the reversed current ( $I_d < 0$ ) for D1 is constant. At this point,  $R_s$  is impeding the net current to flow to the  $V_a$  terminal, and  $R_{sh}$  is the additional conductive pathway for the leakage from GND to  $V_a$ , in addition to the net current ( $I_{ph} - I_d$ ), which increases the dependence on the external applied voltage  $V_a$ . A stable net photo current is required for the photodiodes under reversed bias, to maximize the linearity and create a reliable range for the external circuit design.

Besides the static performance, dynamic or transient performance is also important for photodiodes. Therefore, a capacitor needs to be added in the modeling in parallel to the D1, a shown in Figure 1.12b. The capacitor is mainly from the junction capacitance, also from the parasitic capacitors related to the device electrodes in the measurement setup. Increasing the thickness of the photoactive layer is a straightforward method to reduce the capacitor, which will also facilitate the restriction of the leakage current, equivalently increasing  $R_{sh}$ .

#### **1.5 Extensive Devices Based on a-Si Active Layers**

Although a-Si deposition technologies have been developed for decades and were the previous dominant TFT technologies in the active matrixes of TFT-LCDs, right now it is still enabling the integration with various material systems, such as 2D materials, perovskites or conjugated polymers, to further extend the adversity of a-Si devices. In this thesis, we also describe various investigations and applications for a-Si based devices, such as the conductance modulation based on the metal oxide/a-Si interface, and the photo excited artificial synapses based on the a-Si / PEI interface. In the following, we are going to describe some works from the reported literatures to show the big picture of the versatile a-Si based devices.

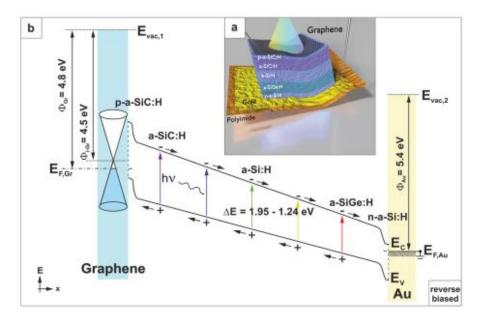

Prof. Lemme group developed the multispectral photodetector based on the hybrid graphene / a-Si device architecture, and they even achieved flexible devices on the Au coated polyimide films, because of the low deposition temperature of a-Si. As shown in Figure 1.13, the single- and bi-layer graphene transparent conductive anodes are deposited by CVD. Various a-Si based semiconductors are deposited sequentially to

achieve the continuously modulated band gap to expand the light absorption band and maximize the responsivity, incorporating the broadband transmission of the graphene. The device allows single pixel detection of UV to visible light, and the maximum of photo-responsivity is up to 0.239 A/W.[28]

Figure 1.13 Schematic cross-section of a multispectral photodiode on polyimide substrate and energy band diagram of a gradually doped a-Si / graphene multispectral photodetector in reverse bias conditions. (Reproduced from [28])

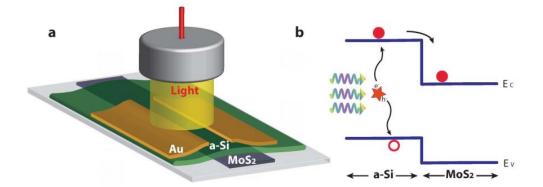

People achieved high speed Molybdenum Disulfide (MoS<sub>2</sub>) a-Si heterojunction photodetectors, as shown in Figure 1.14.[29] This device is basically a photo-transistor, and the channel materials are 60 nm mechanically exfoliated MoS<sub>2</sub> covered by 100 nm a-Si. The electron-hole pairs are generated by the absorption of photons in a-Si layers. The photogenerated electrons diffuse to the a-Si/MoS<sub>2</sub> interface and subsequently get swept into the MoS<sub>2</sub> layer. Due to the higher mobility of electrons in MoS<sub>2</sub>, 2 or 3X higher than that of a-Si, the photoresponse for the a-Si / MoS<sub>2</sub> photodetectors are much faster, compared to the ones based on a-Si only. If the photodetector were used in the flat-panel X-ray imagers, the fast response allows shorter x-ray exposure to patients which helps to reduce the health hazards.

Figure 1.14 Operation concept of molybdenum disulfide a-Si heterojunction photodetector. (a) schematic and (b) energy band diagram of a-Si /  $MoS_2$  heterojunction MSM photodetector. The light is incident from a-Si side, optical absorption occurs in a-Si, and photogenerated electrons diffuse to the underlying  $MoS_2$  layer and are transferred across the  $MoS_2$  layer toward a metal contact. (Reproduced from [29])

Figure 1.15 Design and performance of the perovskite/silicon tandem cell. IV characterizations and the efficiency at the maximum power point (inset) of the perovskite solar cell with illumination through the SnO<sub>2</sub> side. Total absorbance (1-R, where R is the reflectance; dashed grey line), EQE (solid blue line), and transmittance (solid red line) of the perovskite solar cell. (Reproduced from [30])

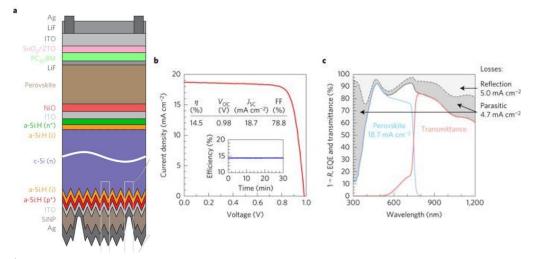

Moreover, the a-Si solar cells can also serve as a platform to be integrated with other solar cell technologies and achieve the tandem device designs for high power conversion efficiency. As shown in Figure 1.15, the transparent perovskite solar cells are integrated with the Si-based solar cells with a-Si passivation layers.[30] The rapid rise of perovskite solar cells with record single junction efficiencies of over 22% can be ascribed to the combinations of unique properties, and they are becoming increasingly attractive for the use in tandem solar cells due to their wide, tunable bandgap and solution processability. In this work, the authors improved the efficiency of monolithic, two-terminal perovskite/silicon tandems to 23.6% by integrating an infrared-tuned silicon heterojunction bottom cell with the recently developed caesium formamidinium lead halide perovskite.

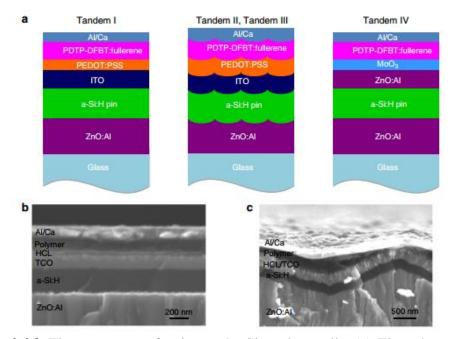

Figure 1.16 The structures of polymer / a-Si tandem cells. (a) The schematic of tandem architectures constructed. Tandem I and IV have flat surface morphology, whereas Tandem II and III have textured morphology. Tandem I, II and II used ITO/PEDOT:PSS to connect the two sub-cells, while Tandem IV employed ZnO:Al/MoO<sub>3</sub>. (b) Typical cross-sectional scanning electron microscopic (SEM) images of a tandem cell made on a flat surface such as Tandem I and IV. (c) Typical cross-sectional SEM images of a tandem cell made on a textured surface such as Tandem II and III. (Reproduced from [31])

Conjugated polymers has been considered as excellent candidate materials for fabricating low-cost, light weight and flexible solar cell devices. People have demonstrated the integration of single junction a-Si and organic solar cells, to achieve a high power conversion efficiency of 10.5%, which is much higher than either of the two single junction solar cells, as shown in Figure 1.16.[31] Such high-efficiency thin-

film tandem cells are optimized by optical management and interface engineering of fully characterized front and back cells without sacrificing photovoltaic performance in both cells. They used AZO or ITO as interfacial conducting layers between a-Si and polymer cells, to promote electrical conduction, working as a cathode for the front subcell and as an anode for the back one. ITO was paired with PEDOT:PSS, while AZO was with MoO<sub>3</sub>, as the strong acidic PEDOT:PSS etches ZnO:Al during a deposition process.

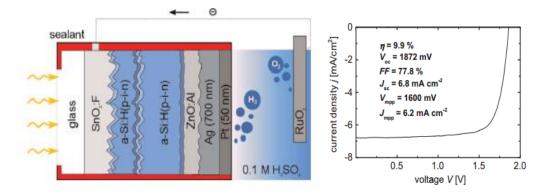

The a-Si solar cell device structure can also be applied as photocathode for the direct solar-to-hydrogen conversion via water splitting.[32] The solar cell was adapted to provide sufficient photovoltage to drive both the hydrogen and oxygen evolution reactions. In the standalone solar water-splitting systems, silicon based thin film technology stands out due to its chemical resistance, earth abundance and low cost production, presenting a promising pathway to the sustainable solar hydrogen production. Under operation of the device, the electrons are injected from the rear side (Pt layer) of the photocathode into the electrolyte for the hydrogen evolution reaction and thus the holes are transferred from the TCO front contact (SnO<sub>2</sub>:F) of the photocathode to the anode (RuO<sub>2</sub>) for the oxygen evolution reaction, as shown in Figure 1.17. However, this is a wired architecture since the photocanode is wired with the photocathode.

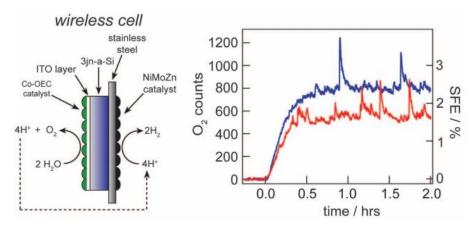

Based on the same working principle, people also demonstrated the wireless configuration to make the system more compact, as shown in Figure 1.18.[33] The authors use a triple junction, a-Si solar cells to interface the hydrogen- and oxygen-evolving catalyst made from an alloy of earth-abundant metals and a cobaltlborate catalyst, respectively. The wireless cell was constructed by deposition of the hydrogen-evolving catalyst, NiMoZn, onto the steel-backing substrate of the a-Si cell, and the oxygen-evolving catalyst on the top side. The cell architecture dictated that O<sub>2</sub> bubbles evolved from the illuminated anode at the front face and bubbles of H<sub>2</sub> evolved from the cathode at the back of the wireless cell.

Figure 1.17 Schematic illustration of the integrated PV–EC device under operation with the a-Si / a-Si photocathode and a  $RuO_2$  anode. Hydrogen evolution occurs at the rear side of the a-Si photocathode. Photocurrent–voltage measurement of the investigated a-Si tandem junction solar cell with a ZnO:Al/Ag back reflector. (Reproduced from [32])

Figure 1.18 MS signal and SFE values for a wireless Co-OEC | 3jn-a-Si | NiMoZn cell under AM 1.5 illumination in 1 M KBi (red trace) and in 0.5 M KBi and 1.5 M KNO<sub>3</sub> (blue trace). The cell was illuminated over the 2 hours of the experiment; MS signal corresponds to the concentration of O<sub>2</sub> in the carrier gas of the cell. The spikes in the data originate from sudden release of gas bubbles that were adhered to the cells, resulting in a temporary increase of the O<sub>2</sub> concentration in the headspace. SFE values were calculated as described in the SOM. (Reproduced from [33])

#### **1.6 Auger Electron Spectroscopy (AES)**

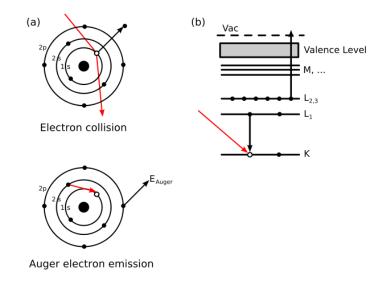

The Auger effect is a physical phenomenon in which the filling of an inner-shell vacancy of an atom is accompanied by the emission of an electron from the same atoms. When a core electron is removed, leaving a vacancy, an electron from a higher energy level may fall into the vacancy, resulting in a release of energy. Although most often this energy is released in the form of an emitted photon, the energy can also be transferred to another electron, which is ejected from the atom; this second ejected electron is called an Auger electron. Upon ejection, the kinetic energy of the Auger electron corresponds to the difference between the energy of the initial electronic transition into the vacancy and the ionization energy for the electron shell from which the Auger electron was ejected. These energy levels depend on the type of atom and the chemical environment in which the atom was located, as shown in Figure 1.19. Auger electron spectroscopy involves the emission of Auger electrons by bombarding a sample with either X-rays or energetic electrons and measures the intensity of Auger electrons that result as a function of the Auger electron energy. The resulting spectra can be used to determine the identity of the emitting atoms and some information about their environment.[34]

The AES is a surface characterization technique with an analysis depth of around 5 nm and a high lateral resolution down to 8 nm. Meanwhile, it can be equipped with an ion bombardment sputtering tool to achieve a depth profile to track the information of several atoms in the sample. The electrons in atoms are localized in different shells, such as K, L, M, N, and up to valence band (V), with different energy. Taking O atoms as an example, its atomic number is 8, and 8 electrons are localized in the K and L shells, where 2 in K, 2 in L1, 2 in L2 and 2 in L3. If the Auger transition involves the electrons in K, L1, L3, then the kinetic energy (KE) of the Auger electron is  $KE = E_K - E_{L1} - E_{L3}$ , where KE is independent of the mechanism of initial core hole formation. The Auger transition also involve the electrons come from other shells, denoted as LMM, MMV or NNV and so on.

Figure 1.19 Two views of the Auger process. (a) illustrates sequentially the steps involved in Auger deexcitation. An incident electron (or photon) creates a core hole in the 1s level. An electron from the 2s level fills in the 1s hole and the transition energy is imparted to a 2p electron which is emitted. The final atomic state thus has two holes, one in the 2s orbital and the other in the 2p orbital. (b) illustrates the same process using X-ray notation,  $KL_1L_{2,3}$ . (Reproduced from [34])

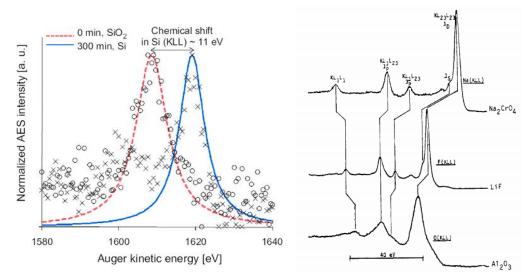

The energy of the electrons in different shells will be influenced by the internal or external chemical environment. As shown in Figure 1.20, the KLL peak group for the Si atoms in SiO2 is left shifted compared to those in the elemental Si sample, which is because the electrons of the external shells are paired with O atoms, and the energy of the electrons the inner shells is increased due to the stronger attraction from the positive atom core. Similar principles also apply to the analysis for the different ionized atoms with same shells, such as the Na, F and O as shown in Figure 1.20. The AES peaks of the atoms with higher atomic number are right shifted because the energy of the electrons in all the shells are increased due to the higher positive charge in the atom core. Meanwhile, each transition mode will generate a peak group because each shell will be divided as several subshells, and the peak ratio is also highly related to the chemical state of the atoms. In this thesis, we extensively use AES to characterize the atomic ratio and chemical states for the O atoms in various metal oxides, which facilitates the verifications of the interfacial property analysis. [35-37]

Figure 1.20 Non-smoothed Si AES peaks for silicon oxide (circles) and for elemental Si (crosses) with fitted main components using pseudo-Voigt functions. The comparison of sodium, fluorine, and oxygen KLL Auger Lines. (Reproduced from [35, 36])

## **1.7 Overview of the Transparent Electronics**

As the Internet of Things is rapidly developing and gradually promoting the evolution of everyone's lifestyle, people are interacting with the surrounding and manipulating the information in real time, which enables the potential opportunities of the transparent electronics and the systems on glasses, beyond the conventional Sibased electronics. The transparent electronics require the electronic devices to be seethrough, or convert the conventional opaque electronic systems to be translucent, such as transparent displays, transparent solar cell panels, and smart windows.[38-42] In this thesis, we are dabbling into the transparent electronic devices, including the transparent organic transistors and transparent memristors, based on the ultrathin metal-film electrodes and the corresponding optical optimizations. In the following, a few works from the reported literatures are described to show the state-of-the-art technologies for transparent electronics.

The transparent solar cell devices with angle insensitive transmissive colors were developed in our group, as shown in Figure 1.21. The cathode and anode contacts are employing various metal oxide and organic hybrid interlayer stacks, with the optimized optical management. The intrinsic a-Si were used here as the active layer for the photo carriers generation, meanwhile the great angle tolerance of the transmitted color is due to the negligible optical phase associated with light propagation in a-Si layers. All of the blue, green or red solar cell panels, the a-Si layer is much thinner than the typical charge diffusion length, so most photogenerated carriers are extracted to the electrodes. This work provides the solutions to realize energy harvesting colored solar cell panels for the exterior decorations.[43]

Figure 1.21 Device structure and optical property. (a) A schematic diagram of proposed structure. The cathode is composed of dielectric-metal-dielectric (DMD) and organic layers, and only DMD structure for the anode. The ultra-thin a-Si layer thickness is 6, 11, and 31 nm for blue, green, and red, respectively. (b) Calculated and measured transmission spectra of individual colors (blue, green, and red) at normal incidence. (c) Photographs of distinct blue, green, and red colors by the fabricated devices. (Reproduced from [43])

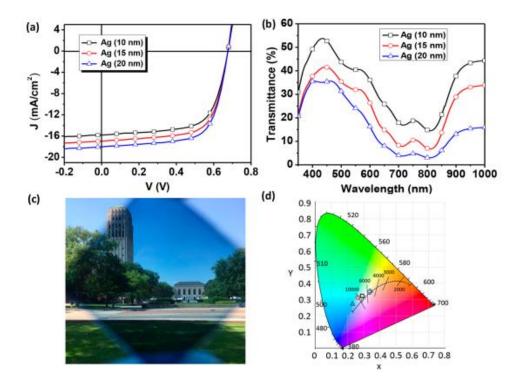

Organic Solar Cells are important emerging solar cell technologies for the customer electronic products due to the light and potential flexible profile, and it can also be modified for the transparent profile. As shown in Figure 1.22, Prof. Forrest group achieved the semitransparent solar cells based on the non-fullerene acceptor. The key step for the overall transparency lies in the top electrode, since the bottom electrode and other interlayers are basically transparent. Here, they used ultra-thin Ag films as the top anode. It has a higher transmission at the shorter wavelength band, giving it a slightly bluish tint.[44]

Figure 1.22 a) IV characterizations for the semitransparent solar cell devices with different Ag electrode thicknesses. b), Transmission spectra of the corresponding devices. c), out door image through the semitransparent device with 10 nm Ag. d), the CIE coordinates of the transmission spectra of the devices with different Ag thicknesses, under AM 1.5G illumination. (Reproduced from [44])

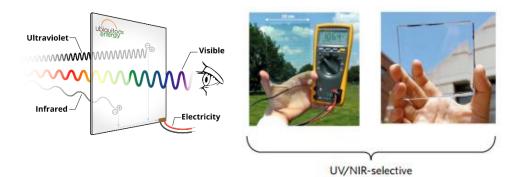

Besides the colored solar cell panels, people explored more on the colorless transparent solar cell panels, as shown in Figure 1.23. The authors developed fully invisible solar cells by selectively absorbing ultraviolet and near infrared light, which allows the surfaces in our daily life surroundings to be tuned into solar harvesting arrays without the sacrifice of the functions or aesthetics. The light in ultraviolet and infrared takes over two thirds of the light available for energy harvesting, and the demonstrated transparent solar cell panel achieved the practical efficiencies over 10% with a visible transparency up to 90%. The luminescent solar concentrators are employed for the power conversions in ultraviolet or infrared bands, where the phosphorescent luminophores consisting of hexanuclear metal halide nanoclusters are used for ultraviolet light, and the organic salt derivatives are used for near infrared light.[45, 46]

Figure 1.23 Working principle of the commercialized visible transparent solar cell panels. Diagram of a wavelength-selective TPV and a large-area, wavelength-selective TPV module. Diagram of a wavelength-selective LSC and a wavelength-selective LSC module. (Reproduced from [46])

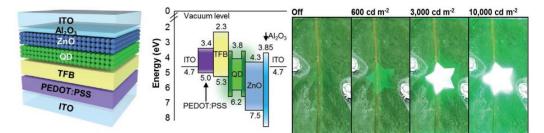

Transparent solar cells panels are used for the energy harvesting at any surface in the daily life surroundings. On the other hand, the transparent display panels embedded with the ambient environments will give rise to further information interactions between human and surroundings, such as augmented reality, smart surgical glasses or smart windows, which enables transparent light emitting devices to be the hot topic in the transparent displays.[47] As shown in Figure 1.24, Prof. Dae-Hyeong Kim group utilized the Quantom Dot light emitting devices to realize the transparent display devices. Both of the bottom and top electrodes are ITO, and the PEDOT:PSS/TFB and ZnO are used as the HTL and ETL, respectively. The ultrathin nature of Tr-QLEDs allows the conformal integration, and the high resolution patterning of red, green, and blue (513 pixels in.–1) shows the potential of the full-color transparent display.[48]

Figure 1.24 Schematic illustration of the device structure and energy-band diagram of the Transparent QLED. The band edges are estimated by ultraviolet photoelectron spectroscopy. Effect of brightness on vividness of the display under ambient light. (Reproduced from [48])

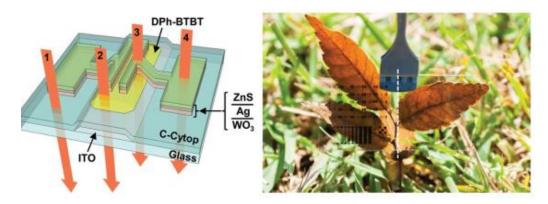

The active matrix is the critical component to drive the light emitting pixels in the flat panel displays, which is actually built up by the thin-film transistors (TFT). Therefore, the Transparent TFTs have attracted great attention to further fulfill the transparent display panels, moreover the unique properties of which are expected to greatly extend the portfolio of modern electronic applications. As shown in Figure 1.25, Prof. Seunghyup Yoo achieved excellent organic transparent TFT device based on the DPh-BTBT and the optical optimization for the source/drain electrodes. In the electrodes, an ultrathin Ag layer (a 15 nm Ag layer in this study) enables efficient lateral conduction, an outer dielectric layer (ZnS) covering the Ag layer enhances the transparency using a destructive interference effect, and an inner dielectric layer (WO<sub>3</sub>) provides efficient hole injection into the channel from the Ag electrode.[49]

Figure 1.25 Structure of the proposed transparent DPh-BTBT TFTs. The numbers 1-4 indicate four optically distinct positions under consideration. The photograph on the right side shows both conventional and transparent samples (1 in.  $\times$  1 in.) containing the full TFT array structure. (Reproduced from [49])

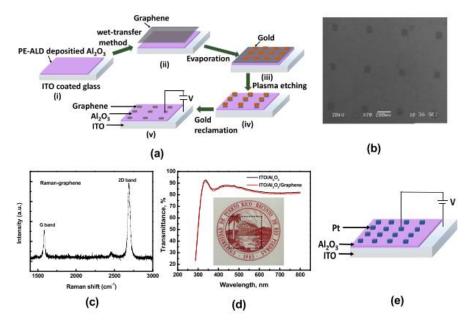

The transparent electronics created more opportunities for the extensive information interactions, but it still requires information storage or processing, which gives rise to the development space for the transparent memristors. As shown in Figure 1.26, Prof. Ram S. Katiyar group developed transparent memristors based on the top graphene electrodes. The main active layer is 15 nm Al<sub>2</sub>O<sub>3</sub>, deposited by ALD, and the top graphene electrodes are transferred from the Cu/graphene by PMMA coating to the ITO/Al<sub>2</sub>O<sub>3</sub>, then get etched with the Au hard masks. In the on-state, the IV relationship follows the ohmic conduction, while in the off-state, the nonlinear behavior is

dominated by the interface-limited Schottky charge transportation. The switching mechanisms are due to the O ions or vacancies interaction between oxide and graphene layer. [50]

Figure 1.26 (a) Fabrication process of the ITO/Al<sub>2</sub>O<sub>3</sub>/G device (b) SEM image of graphene square dots on the Al<sub>2</sub>O<sub>3</sub> layer. (c) Raman spectra of graphene on Al<sub>2</sub>O<sub>3</sub> showing G- and 2D-bands. (d) Optical transmission spectra of ITO/Al<sub>2</sub>O<sub>3</sub> and ITO/Al<sub>2</sub>O<sub>3</sub>/G samples and the inset shows the ITO/Al<sub>2</sub>O<sub>3</sub>/G sample placed on the university logo. (e) Schematic of ITO/Al<sub>2</sub>O<sub>3</sub>/Pt capacitor. (Reproduced from [50])

#### **1.8 Dissertation Organization**

We further the investigations on the device design and applications of the a-Si devices previously developed in our group. Moreover, we still stepped into the various transparent electronic devices, including the transparent memristors and organic TFTs based on the developed transparent ultrathin metal film electrodes and the corresponding optical management. The organization of the dissertation is described as follows.

In Chapter 2, we reported the surface properties for the Polyethylenimine (PEI) and the adjacent layers. Dipoles will be induced along the ZnO/PEI interface, pointing from ZnO to PEI, which will facilitate the work-function lowering of bottom cathodes. However, for the top cathode contacts in the normal-type devices, we found that the dipole induced across the PEI layers is highly related to the surface properties of the layers adjacent to it. The obtained results revealed the ZnO/PEI interlayers also work well as top cathode contacts. The reported dipole between ZnO/PEI which is supposed to increase the barrier, is actually overcome by another dipole induced along the interface between the PEI and cathode metals. The fabrication of ZnO/PEI interface is based on solution and low-temperature processes, which gives rise to other promising cathode contact alternatives as top cathode contacts of devices, especially for those with semi-transparency, even flexibility.

In Chapter 3, the interface conductivity and oxygen deficiency for WO<sub>x</sub>/a-Si contacts are reported. The ITO transparent electrode extensively used in large-area electronics is becoming more and more expensive, and the metal mesh is a popular backup alternative for the replacement of ITO. However, the local conductivity for the non-conductive area in the metal meshes has to be compensated. In this work, we systematically analyzed the interfacial properties of the WO<sub>x</sub>/a-Si interfaces, including the band diagram and the carrier lateral transportation. We found the WO<sub>x</sub>/a-Si interface is able to support centimeter-scale non-electrode area, without the additional conductive layers compensating the low local conductivity. The hypothesis and characterizations reported here can be used to determine more details for the exact definition of the device areas and secure better device designs. More significantly, it gives rise to the further possibilities of devices with semi-transparency, ultra-sparse metal mesh electrodes, and so on.

In Chapter 4 and 5, we characterized the photodetectors based on the developed interlayers for a-Si devices, especially the detection under low illumination towards the in-screen fingerprint scanners. In this work, we employed top ZnO NPs and PEI interlayers. High LDR are achieved up to 190 dB, and at least 4 orders for the illuminations < 50 Lux. In order to show the clear current ratio between the adjacent a-Si PD pixels, short linear arrays are fabricated, and the current sequence in the arrays exhibited good ratio up to 2 orders. Finally, peripheral circuits are built up based on the Arduino microcontrollers to fast acquire the current detected by the short linear arrays,

which can clearly show the patterns mimicking the groves and valleys of the fingerprints. The inverted a-Si PD with bottom cathode contact interlayers are developed and characterized to fulfill the requirements of the architecture design for the sensing arrays. The ZnO and MoO<sub>x</sub> are employed as the ETL and HTL for the inverted a-Si PDs. The current leakage and LDR get analyzed with different a-Si thicknesses and device areas. The a-Si PD arrays with pixel areas are fabricated based on the photo-lithography processes in order to extract accurate current leakage and LDR. Finally, the optimized a-Si PD arrays are fabricated on the LTPS TFT backplanes.

In Chapter 6, innovative artificial synapses were demonstrated based on the interactions between the a-Si and PEI interlayers. The hysteresis and timing dependent plasticity of the artificial synapses can be excited by light illumination, coupled with electrical pulse stimuli. The device design is promising to serve as fundamental elements for neuromorphic functionalities towards the simultaneous visual information process in large-area electronics or IoT.

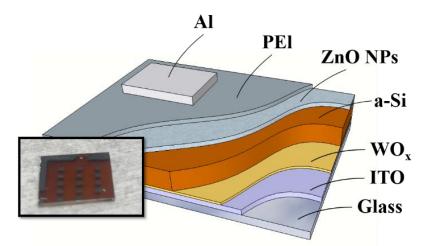

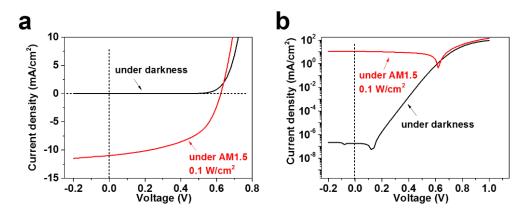

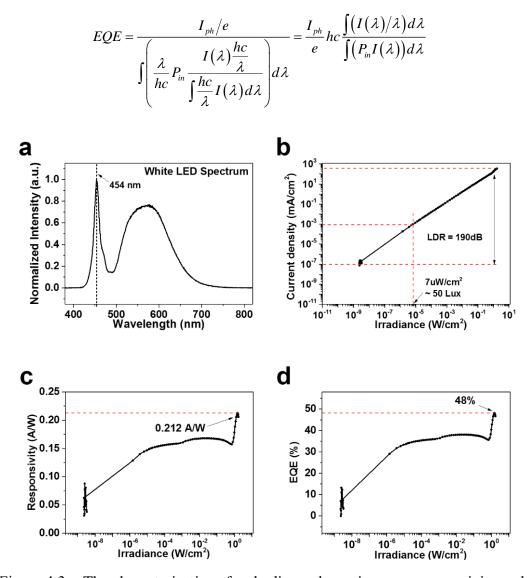

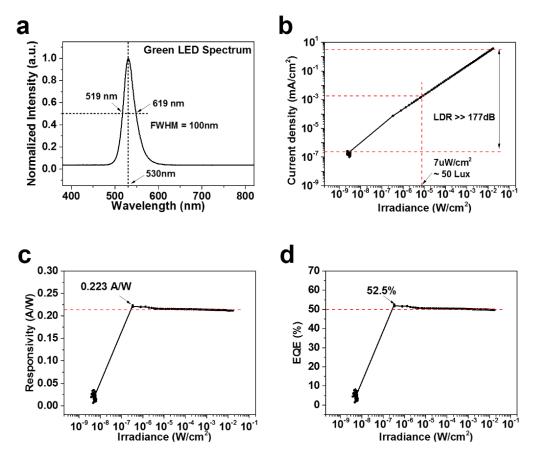

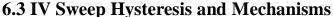

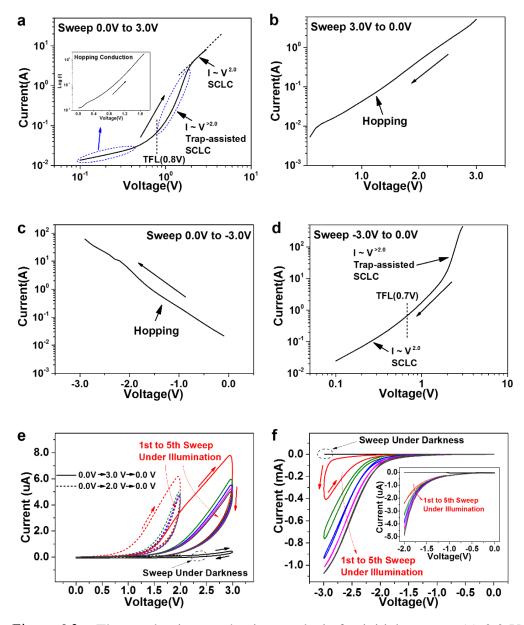

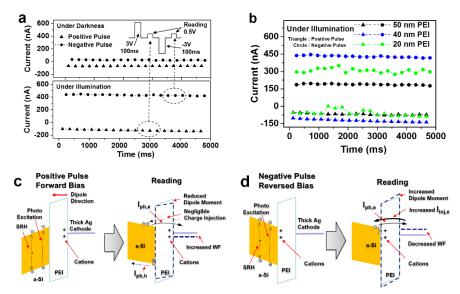

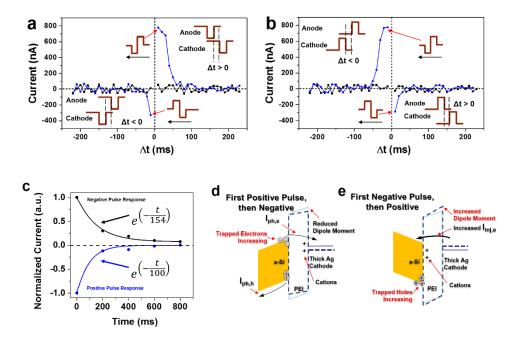

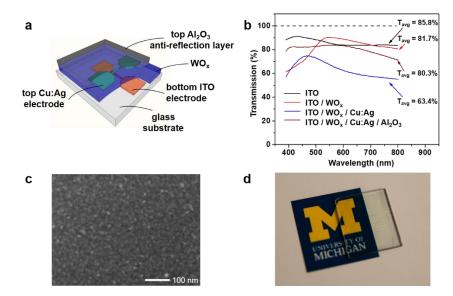

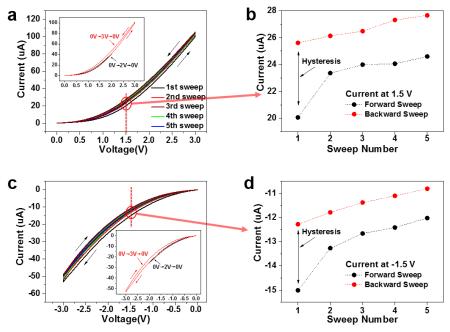

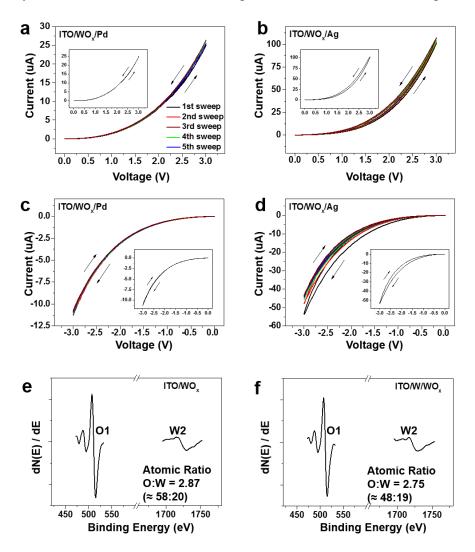

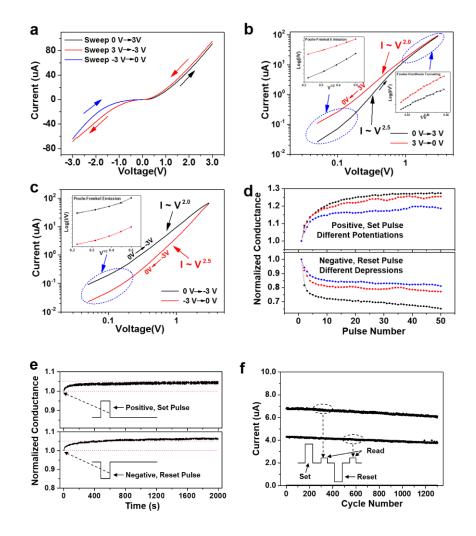

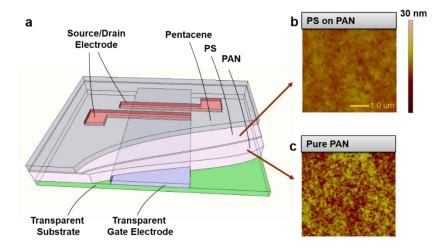

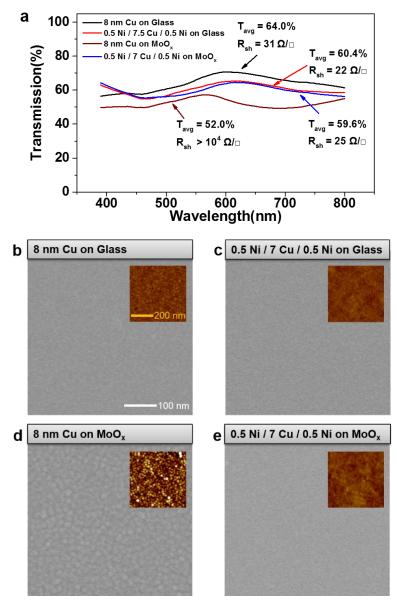

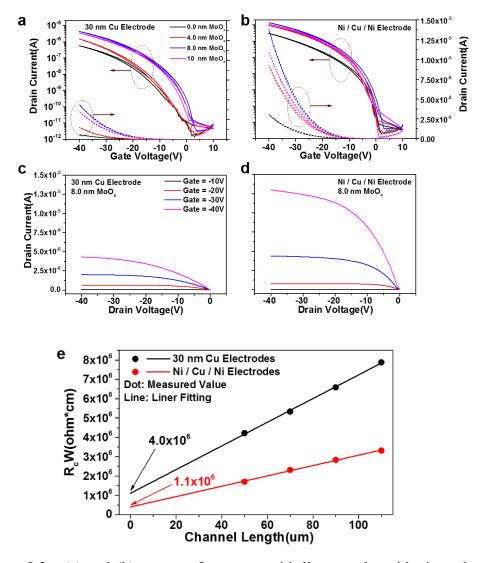

In Chapter 7, we achieved transparent resistive switching devices to promote neuromorphic computing for the transparent electronic systems. The devices are based on ultrathin doped Ag films and optically optimized dielectric/metal/dielectric structure. The overall transparency is higher than 80%, and the device conductance modulation is found to be analog and continuous. Under consecutive pulse stimulus with different durations, the device finally stabilized at different conductance levels, acting as different potentiation or depression levels in terms of neuromorphic functionalities.