# **Runtime Systems for Persistent Memories**

by

Vaibhav Gogte

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2020

### **Doctoral Committee:**

Professor Thomas F. Wenisch, Chair Professor Peter M. Chen Associate Professor Satish Narayanasamy Associate Professor Zhengya Zhang

# Vaibhav Gogte

vgogte@umich.edu

ORCID iD: 0000-0002-7382-636X

© Vaibhav Gogte 2020

To my parents, Vinod Gogte and Sangita Gogte

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank Prof. Tom Wenisch, my PhD advisor and mentor, who has been incredibly supportive during my PhD. Tom is a great educator and a devoted advisor. He is always eager to help; his open-door office policy and regular lab visits were incredibly helpful in getting things moving quickly. I can now admire his patience, having thoroughly exploited his open-door policy to my benefit for all these years. I have always been in awe of his technical expertise; he is unbelievably quick in identifying the problems and giving pointed feedback. He has always adapted to my working style, giving me sufficient space to independently work on my ideas when I desired, and closely working with me and helping me out with the problems when I was stuck. I am grateful to Tom for taking me in his lab and helping me evolve, both personally and professionally. I also worked closely with Prof. Peter Chen and Prof. Satish Narayanasamy on all the memory persistency projects. Pete and Satish taught me how to critically examine my work. Pete's systems outlook and Satish's PL perspective helped me evolve my ideas on architecture, systems and programmability fronts. I can now admit that the weekly meetings with them were overwhelming at first, but the discussions quickly became the highlight of my week. I would also like to thank Prof. Zhengya Zhang for serving on my thesis committee and for his valuable comments that have helped me improve this dissertation. I am also grateful to have worked with the amazing collaborators, Prof. Aasheesh Kolli, William Wang, Stephan Diestelhorst, Prof. Michael Cafarella, and Prof. Loris D'Antoni.

Its been my pleasure to have worked with some of the brightest and hard-working PhD researchers. I would like to thank the members of Wenisch lab – Aasheesh Kolli, Akshitha

Sriraman, Amir Mirhosseini, Amlan Nayak, Brendan West, Harini Muthukrishnan, Hossein Golestani, Kevin Loughin, Neha Agarwal, Ofir Weisse, and Steve Zekeny – not just for all the technical help, but also for organizing numerous unicorn-themed pranks on Tom. They made working in Wenisch lab lively and fun. I would specially like to thank Akshitha Sriraman for entertaining the long discussions on my half-baked ideas and helping me out with the low-level technical details in my projects. She is incredibly hardworking and devoted towards her goals, and she has always inspired me to be persistent and focused in difficult times. I would also like to acknowledge the CSE staff members, Ashley Andrea, Denise Duprie, Jamie Goldsmith, Karen Liska and Stephen Reger, for providing the logistical support in a timely manner.

My PhD experience over the last five years was full of ups and downs. When ideas failed to work after the umpteenth iteration, hopes were crushed after failure to meet paper deadlines, and reviewer B glorifyingly rejected the premise of my papers, I cannot imagine to have endured it all without the kind support of my friends. A big shout-out to the Juwaris group — Kumar Aanjaneya, Harshad Dharmatti, Kunal Garg, Animesh Jain, Sneha Joshi, Aditi Kulkarni, Saurabh Mahajan, Bharadwaj Mantha, Niket Prakash, Shriya Sethuraman, Poorwa Shekhar, Ripudaman Singh, Akshitha Sriraman, and Keval Ramani — for making Ann Arbor a home away from home. The board game nights, boisterous Avalon sessions, and impromptu road-trips with this jovial gang kept me sane these five years. I am grateful to Kumar Aanjaneya for being such an amazing roommate, for pushing me to go to work on dull winter mornings, and for the enlightening discussions over chai. I would specially like to thank Shriya Sethuraman, my closest ally and best friend. She always had my back, and showed me the fun side of life and put a smile on my face when times got tough.

Lastly, I am incredibly grateful to my parents, Sangita Gogte and Vinod Gogte, and my sister Aishwarya Gogte, for their unwavering love and support. I cannot thank them enough for the sacrifices they have made to give me all the independence I needed to follow my dreams. Their constant guidance and encouragement has made me what I am today.

# TABLE OF CONTENTS

| DEDICATION   |                                              |

|--------------|----------------------------------------------|

| ACKNOWLED    | GEMENTS                                      |

| LIST OF FIGU | RES viii                                     |

| LIST OF TABL | ES xii                                       |

| ABSTRACT     |                                              |

| CHAPTER      |                                              |

| I. Introd    | uction                                       |

| 1.1          | Software Wear Management                     |

| 1.2          | Persistency for Synchronization-Free Regions |

| 1.3          | Relaxed Hardware Persistency Model           |

| 1.4          | Summary                                      |

| II. Backg    | round and Motivation                         |

| 2.1          | Persistent Memories (PMs)                    |

| 2.2          | Endurance of Persistent Memories             |

|              | 2.2.1 Wear Management for PMs                |

|              | 2.2.2 Wear-aware Virtual Memory System       |

| 2.3          | Memory Persistency Models                    |

|              | 2.3.1 Failure Atomicity                      |

|              | 2.3.2 Logging Mechanisms                     |

| 2.4          | Persistency Semantics for Languages          |

|              | 2.4.1 C++ Memory Model                       |

| 2.5          | ISA-Level Persistency Mechanisms             |

| III. Softwa  | are Wear Management for Persistent Memories  |

| 3.1         | Introduct    | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 21  |

|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.2         | Kevlar .     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 24  |

|             | 3.2.1        | Wear Leveling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 24  |

|             | 3.2.2        | Wear Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|             | 3.2.3        | Wear Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 31  |

| 3.3         | Impleme      | ntation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 34  |

| 3.4         |              | logy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|             | 3.4.1        | Emulating Persistent Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 36  |

|             | 3.4.2        | System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|             | 3.4.3        | Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 3.5         | Evaluatio    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

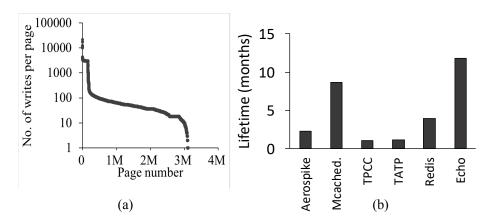

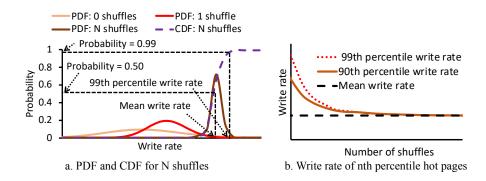

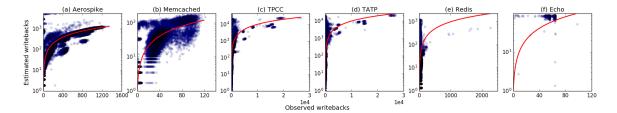

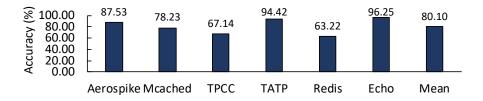

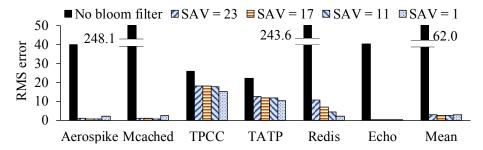

|             | 3.5.1        | Modeling Wear Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

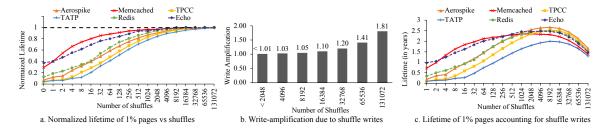

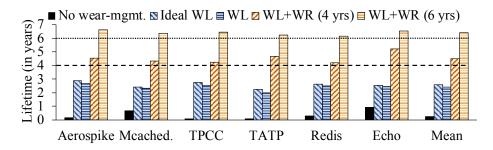

|             | 3.5.2        | PM Lifetime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

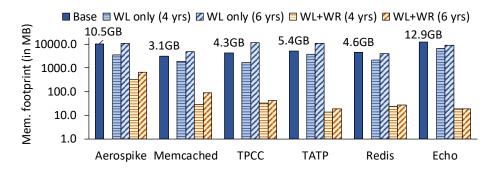

|             | 3.5.3        | Memory Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

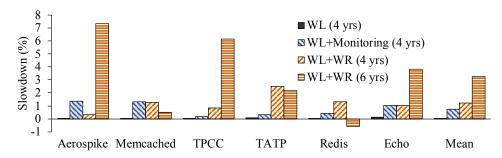

|             | 3.5.4        | Performance Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|             | 0.07.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •     |

| IV. Persist | tency for S  | synchronization-Free Regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 47  |

| 4.1         | Introduct    | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 47  |

| 4.2         | Design O     | verview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

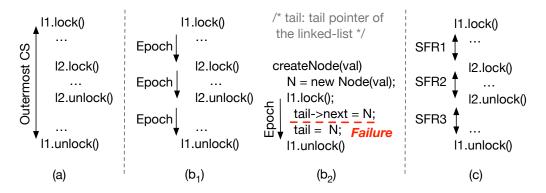

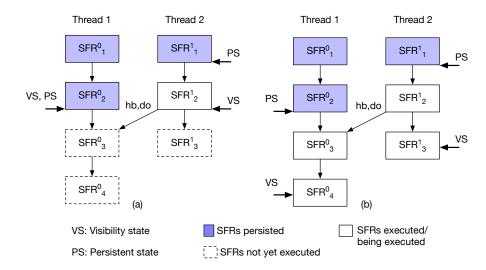

| 4.3         | SFR Fail     | ure Atomicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 52  |

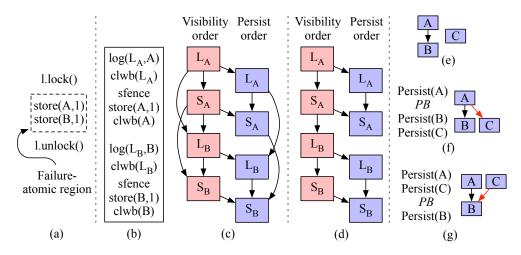

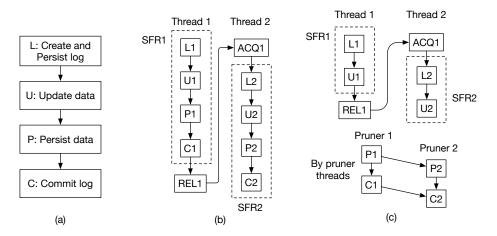

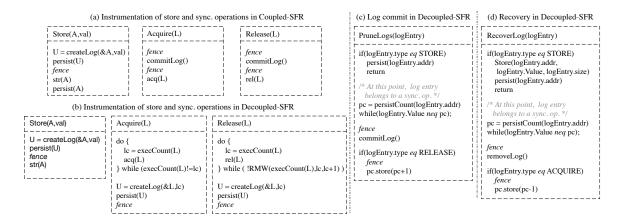

|             | 4.3.1        | Logging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 52  |

|             | 4.3.2        | SFR-atomicity with Coupled Visibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 54  |

|             | 4.3.3        | SFR-atomicity with Decoupled Visibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| 4.4         | Durabilit    | y Invariants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|             | 4.4.1        | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|             | 4.4.2        | SFR Durability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|             | 4.4.3        | Coupled-SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|             | 4.4.4        | Decoupled-SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

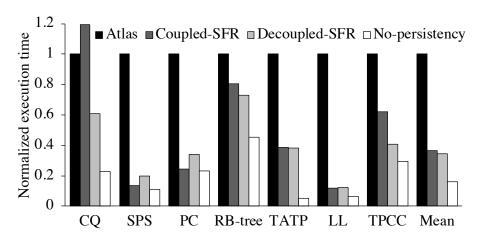

| 4.5         | Evaluatio    | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|             | 4.5.1        | Performance Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

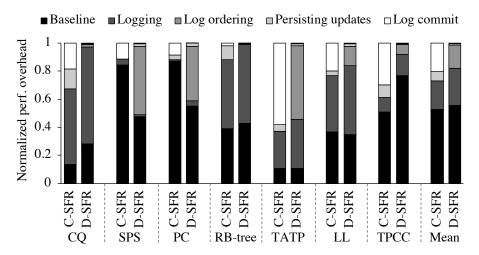

|             | 4.5.2        | Logging Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

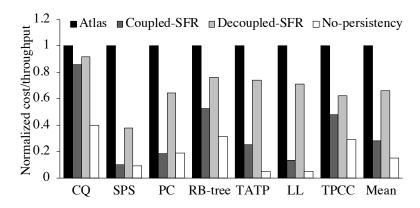

|             | 4.5.3        | CPU Cost per Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

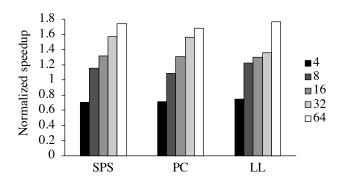

|             | 4.5.4        | Sensitivity Study of Operations/SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|             |              | sensitivity study of operations, sixtin in the contract of the | • , 1 |

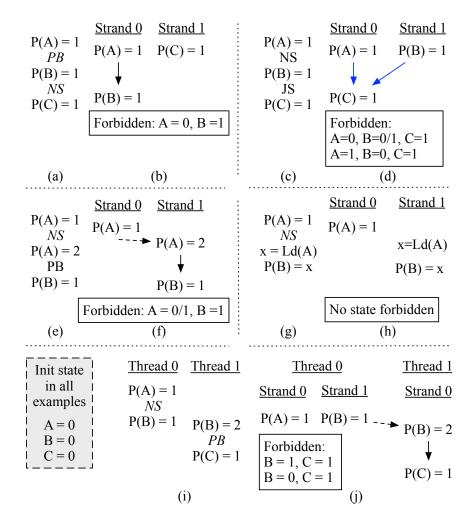

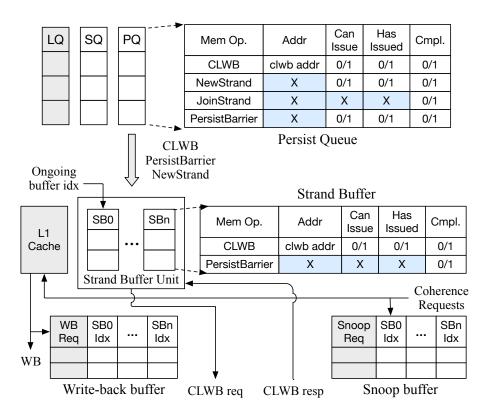

| V. Relaxe   | ed Persist ( | Ordering Using Strand Persistency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 72  |