# Distributed, Intelligent Audio Sensing Enabled by Low-Power Integrated Technologies

by

Minchang Cho

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2020

Doctoral Committee:

Assistant Professor Hun Seok Kim, Co-Chair Professor Dennis M. Sylvester, Co-Chair Professor David T. Blaauw Assistant Professor Reetuparna Das Minchang Cho mincho@umich.edu ORCID iD: 0000-0002-4044-0276

© Minchang Cho 2020 All Rights Reserved To God and my family with love and gratitude

# TABLE OF CONTENTS

| DEDICATION                                                                                                                                                | ii                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LIST OF FIGURES                                                                                                                                           | v                                      |

| LIST OF TABLES                                                                                                                                            | viii                                   |

| ABSTRACT                                                                                                                                                  | ix                                     |

| CHAPTER                                                                                                                                                   |                                        |

| I. Introduction                                                                                                                                           | 1                                      |

| <ol> <li>Prior Art: Wireless Audio Sensor Motes</li> <li>Challenges of Achieving Millimeter-Scale Audio Sensing</li> <li>Dissertation Overview</li> </ol> | 3<br>6<br>9                            |

| II. A Microwatt Power Audio Processing IC and 8Mb Streaming<br>Flash Memory                                                                               | 11                                     |

| <ul> <li>2.1 Introduction</li></ul>                                                                                                                       | 11<br>12<br>14<br>18<br>22<br>25<br>27 |

| III. A Picowatt Standby Power Neural Network Processor With<br>Custom ISA and 7T SRAM for Sensor Applications                                             | 33                                     |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                       | 33<br>36<br>36<br>42                   |

|           | 3.2.3 Ultra-Low Leakage 7T SRAM Memory              | 44 |

|-----------|-----------------------------------------------------|----|

| 3.3       | Acoustic Object Detection Sensor System             | 45 |

| 3.4       | Measurement Results                                 | 47 |

| IV. An A  | coustic Signal Processing Chip With Nanowatt Power  |    |

| Voice     | Activity Detection                                  | 53 |

| 4.1       | Introduction                                        | 53 |

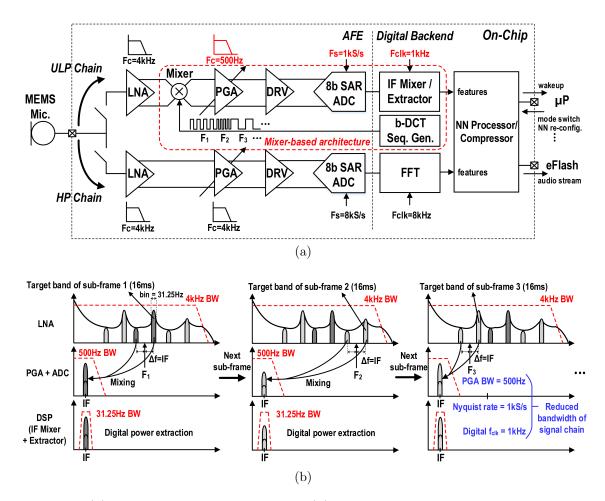

| 4.2       | VAD System Overview                                 | 56 |

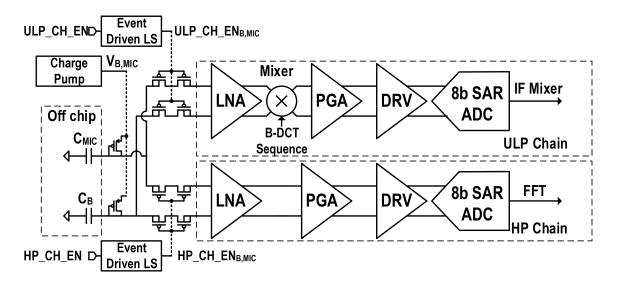

| 4.3       | Analog Front-End Implementation                     | 58 |

|           | 4.3.1 Overall Architecture                          | 58 |

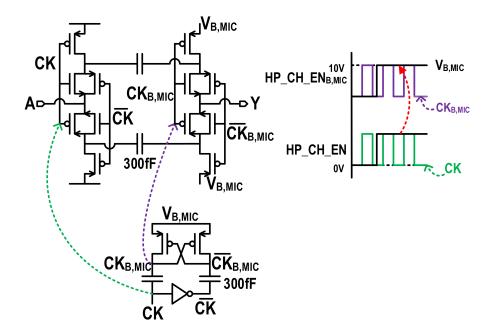

|           | 4.3.2 Charge Pump and 10-V Level Shifter            | 59 |

|           | 4.3.3 Low-Noise Amplifier and Programmable-Gain Am- |    |

|           | plifier                                             | 60 |

| 4.4       | Digital Back-End Implementation                     | 64 |

|           | 4.4.1 Overall Architecture                          | 64 |

|           | 4.4.2 Binary DCT Mixer Sequence Generator           | 65 |

|           | 4.4.3 IF Mixer and Extractor                        | 67 |

|           | 4.4.4 Neural Network Processor                      | 68 |

| 4.5       | Acoustic Signature Wakeup Detection                 | 70 |

| 4.6       | Measurement Results                                 | 71 |

| 4.7       | Summary                                             | 78 |

| V. Millir | neter-Scale Wireless Audio Sensor Node              | 81 |

| 5.1       | The First Generation                                | 81 |

| 5.2       | The Second Generation                               | 85 |

| VI. Conc  | lusion                                              | 93 |

| IBLIOGRA  | PHY                                                 | 97 |

## LIST OF FIGURES

## Figure

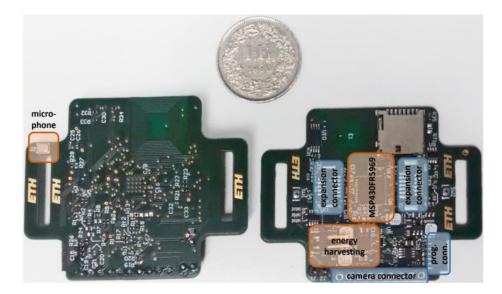

| 1.1  | The $\mu$ AMPS sensor node (2000)                                    | 3  |

|------|----------------------------------------------------------------------|----|

| 1.2  | (a) Audio sensor mote for acoustic scenes monitoring (2009) (b)      |    |

|      | TinyEARS (2013)                                                      | 4  |

| 1.3  | InfiniTime $(2016)$ .                                                | 5  |

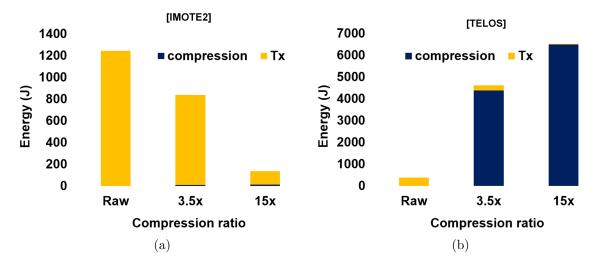

| 1.4  | Energy consumption vs. compression ratio on (a) IMOTE2 platform      |    |

|      | and (b) TELOS platform.                                              | 7  |

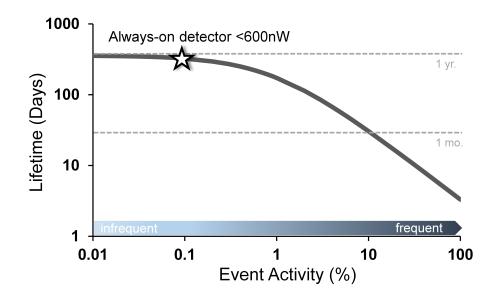

| 1.5  | Sensor system lifetime vs. event activity: When the event of inter-  |    |

|      | est occurs infrequently, the always-on detector would determine the  |    |

|      | lifetime.                                                            | 8  |

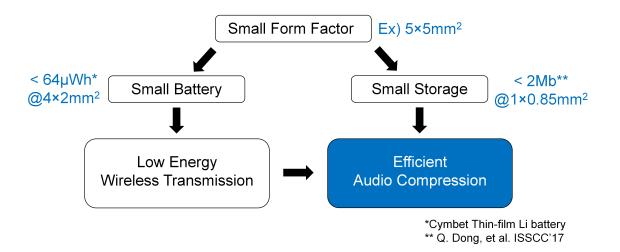

| 2.1  | Miniaturized audio sensor challenges.                                | 12 |

| 2.2  | Overall architecture of audio processing IC                          | 13 |

| 2.3  | Analog front-end (AFE) and ADC circuits.                             | 14 |

| 2.4  | Measured input referred noise spectrum of AFE                        | 15 |

| 2.5  | Synchronous SAR ADC clock controller circuits and its operational    |    |

|      | timing diagram.                                                      | 16 |

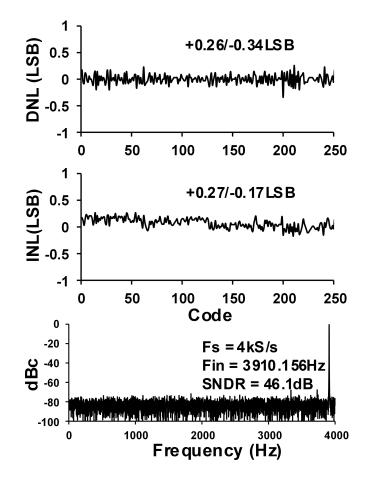

| 2.6  | Measured DNL, INL, and frequency spectrum of ADC                     | 17 |

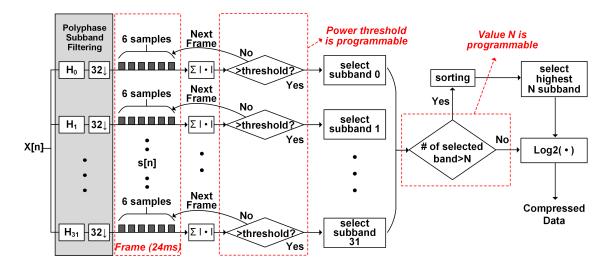

| 2.7  | Proposed compression algorithm.                                      | 18 |

| 2.8  | Polyphase Quadrature Filtering (PQF) process.                        | 19 |

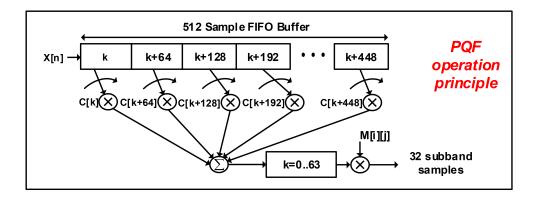

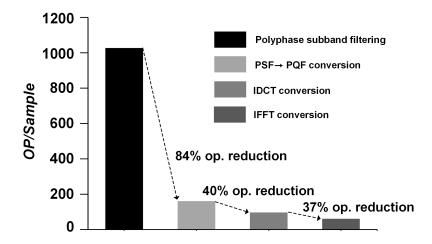

| 2.9  | Compelxity reduction from the algorithm optimization                 | 21 |

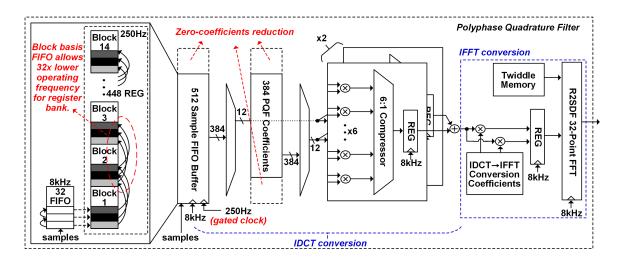

| 2.10 | Polyphase quadrature filter architecture.                            | 23 |

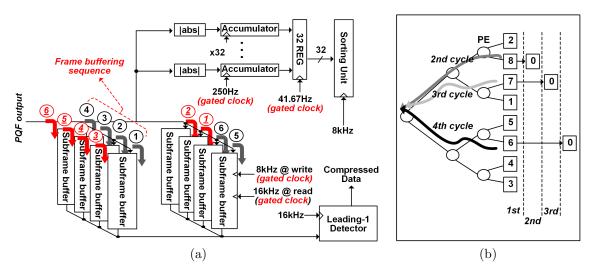

| 2.11 | Compression engine architecture.                                     | 24 |

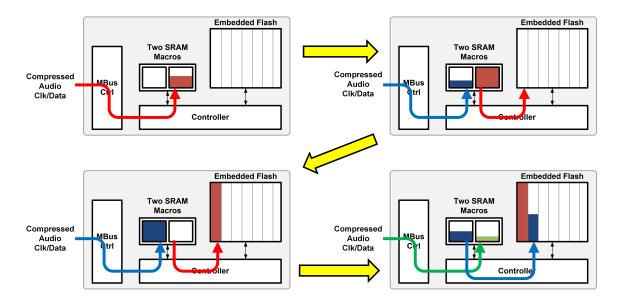

| 2.12 | Operation principle of ping-pong streaming Flash                     | 25 |

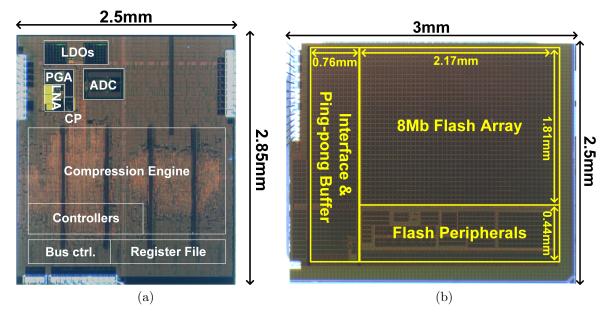

| 2.13 | Chip die photo of (a) audio processing chip and (b) 8Mb NOR Flash    |    |

|      | chip                                                                 | 27 |

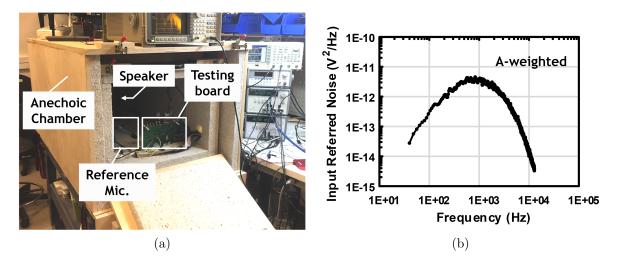

| 2.14 | (a) Acoustic measurement setup (b) power spectral density (PSD) of   |    |

|      | AFE                                                                  | 28 |

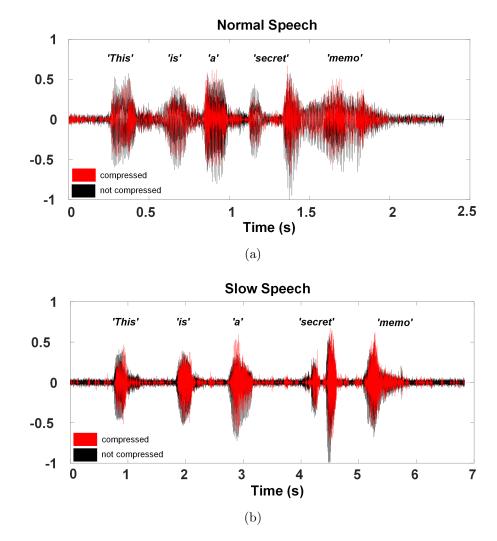

| 2.15 | Time domain signals for compressed and origial audio clip at (a)     |    |

|      | normal speed speech and (b) slow speed speech                        | 29 |

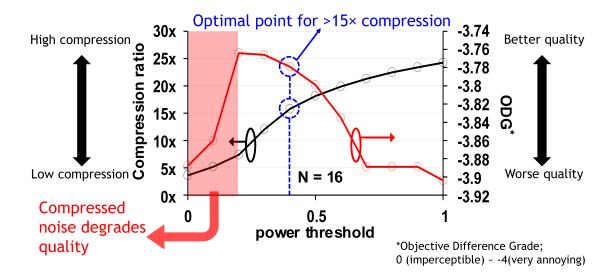

| 2.16 | Measured compression ratio vs. sound quality trade-off               | 30 |

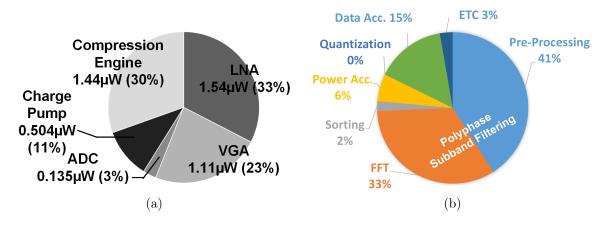

| 2.17 | Measured power breakdown of (a) audio IC and (b) compression engine. | 31 |

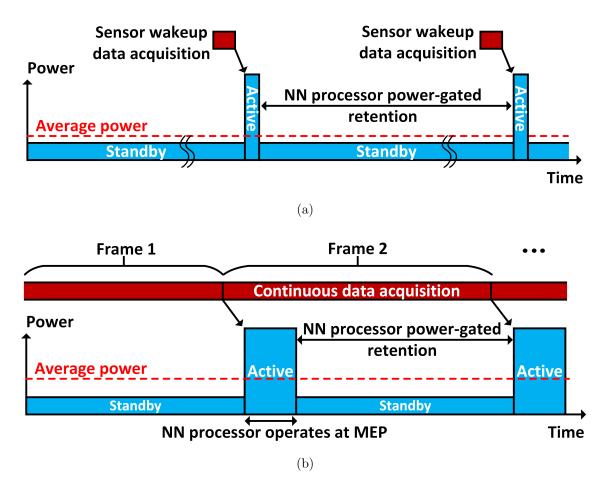

| 3.1  | The power profile and average power consumption of NN processor      |    |

|      | in (a) duty-cycled operation and (b) always-on operation             | 35 |

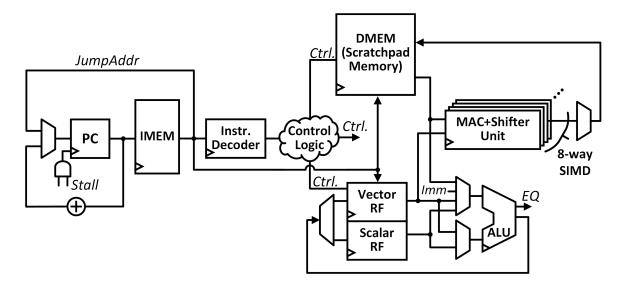

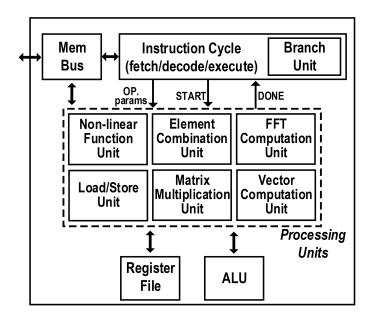

| 3.2  | The microarchitecture of on-sensor NN processor.                                                                                    | 42 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

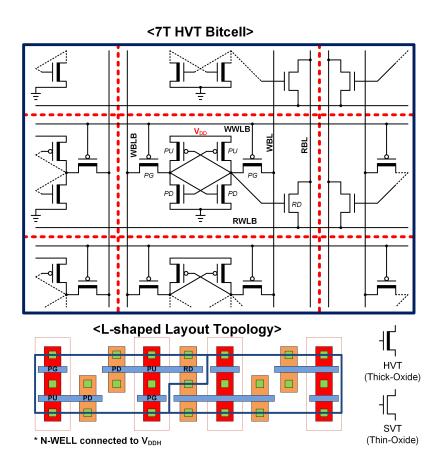

| 3.3  | 7T HVT SRAM bitcell and layout.                                                                                                     | 44 |

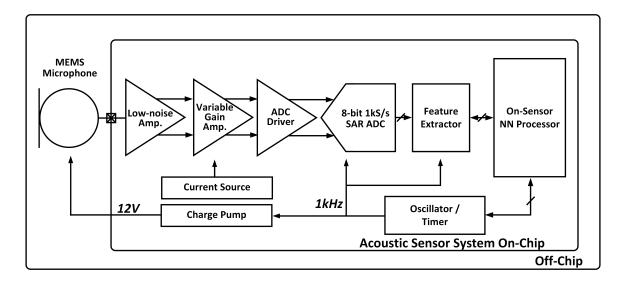

| 3.4  | Overall block diagram of acoustic sensor system for object detection.                                                               | 46 |

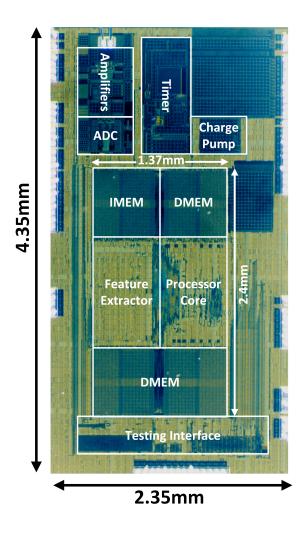

| 3.5  | Die photograph of acoustic sensor system with on-sensor NN processor.                                                               | 47 |

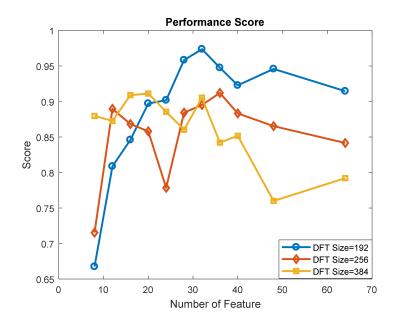

| 3.6  | Algorithm parameter sensitivity analysis                                                                                            | 49 |

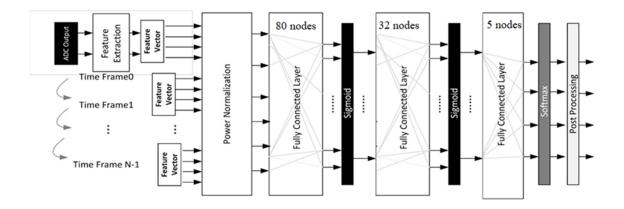

| 3.7  | Neural network topology for acoustic object detection                                                                               | 51 |

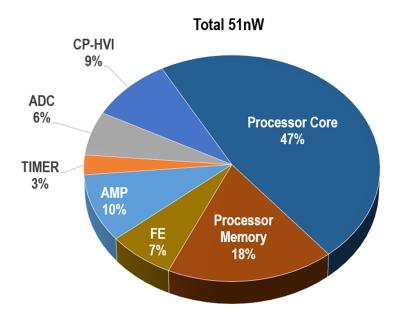

| 3.8  | Power breakdown of the proposed acoustic sensor system                                                                              | 52 |

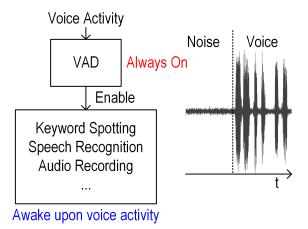

| 4.1  | Always-on voice activity detection as a wakeup mechanism. Ad-<br>vanced processing is enabled upon voice activity detection to save |    |

|      | the overall power. $\ldots$                        | 54 |

| 4.2  | (a) VAD system architecture. (b) Operating principle of mixer-based                                                                 |    |

|      | sequential frequency scanning                                                                                                       | 57 |

| 4.3  | AFE block diagram with ULP and HP chains                                                                                            | 59 |

| 4.4  | 10-V level shifter shifts up nominal VDD level to 10 V with periodic                                                                |    |

|      | refresh. Its waveforms are shown at right                                                                                           | 60 |

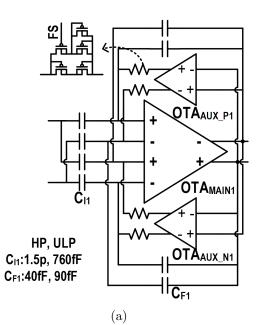

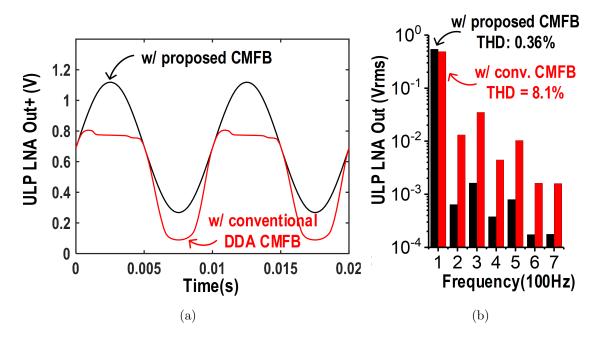

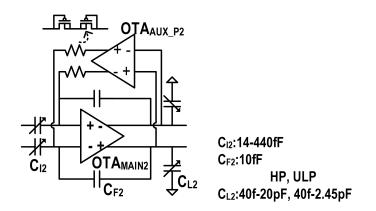

| 4.5  | (a) LNA circuit diagram. (b) $OTA_{MAIN1}$ . (c) $OTA_{AUX_N1}$ and their                                                           |    |

|      | bias implementation. $OTA_{AUX_P1}$ are implemented similarly with the                                                              |    |

|      | opposite type of transistors.                                                                                                       | 62 |

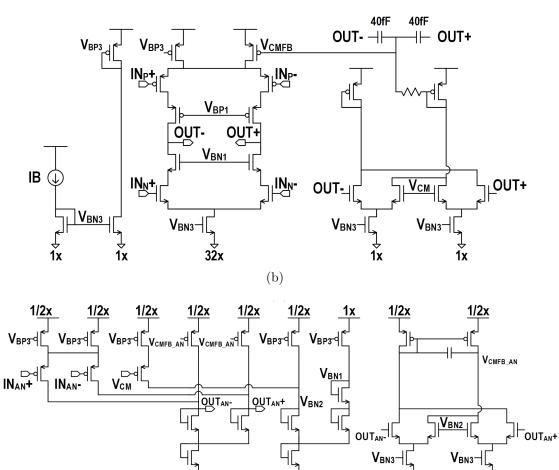

| 4.6  | (a) ULP LNA output waveform with conventional DDA CMFB (red)                                                                        |    |

|      | versus with proposed CMFB consisting of coupling capacitors and                                                                     |    |

|      | DDA (black). (b) Its spectrum (simulated)                                                                                           | 63 |

| 4.7  | PGA circuit diagram.                                                                                                                | 63 |

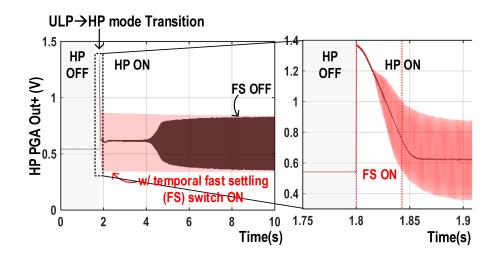

| 4.8  | Measured HP PGA output showing ULP-HP mode transition time.                                                                         |    |

|      | By turning on fast settling switches for 30 ms, the settling time re-                                                               |    |

|      | duces from 6 s (black) to 100 ms (red). $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                         | 64 |

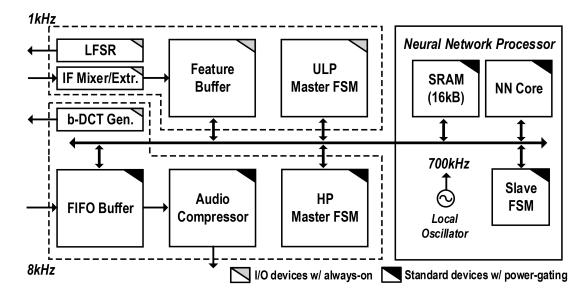

| 4.9  | Digital backend architecture.                                                                                                       | 65 |

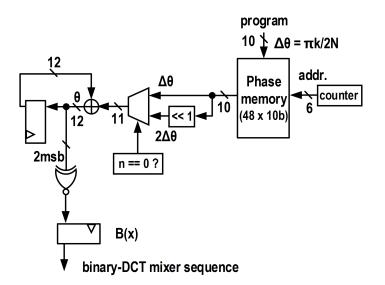

| 4.10 | Binary DCT mixer sequence generator circuits                                                                                        | 66 |

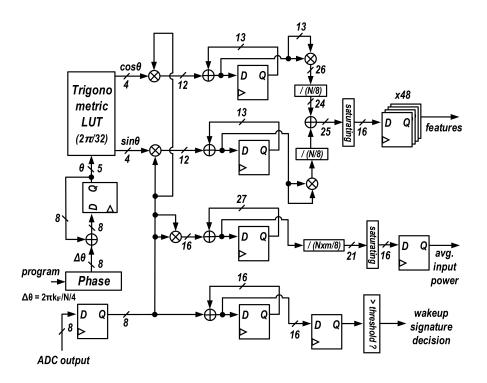

| 4.11 | IF mixer and extractor circuits.                                                                                                    | 67 |

| 4.12 | NN processor core architecture.                                                                                                     | 68 |

| 4.13 | Measured power reduction from computational sprinting                                                                               | 69 |

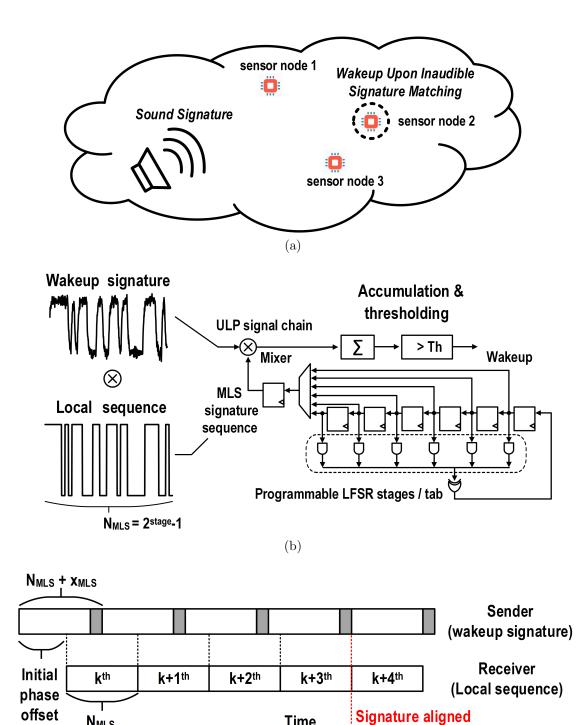

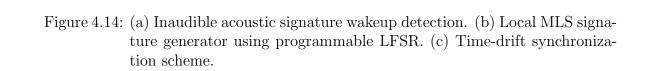

| 4.14 | (a) Inaudible acoustic signature wakeup detection. (b) Local MLS                                                                    |    |

|      | signature generator using programmable LFSR. (c) Time-drift syn-                                                                    |    |

|      | chronization scheme.                                                                                                                | 72 |

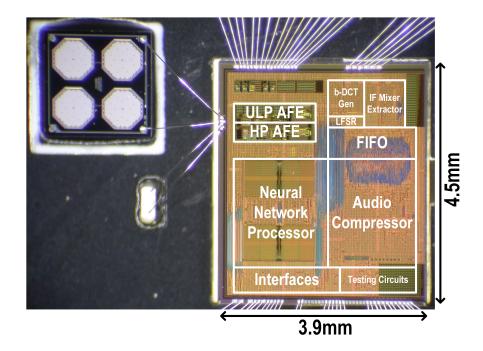

| 4.15 | Die micrograph and system integration with MEMS microphone                                                                          | 73 |

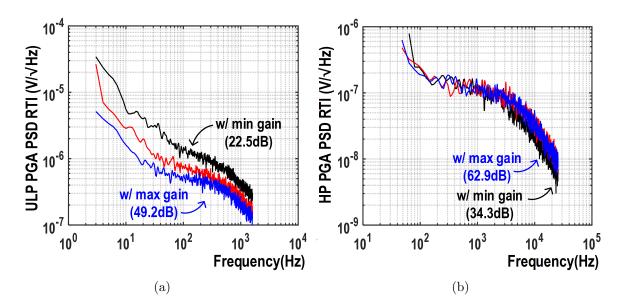

| 4.16 | (a) ULP PGA. (b) HP PGA input referred noise spectrum density                                                                       |    |

|      | with different PGA gain settings (min, mid, and max gain)                                                                           | 73 |

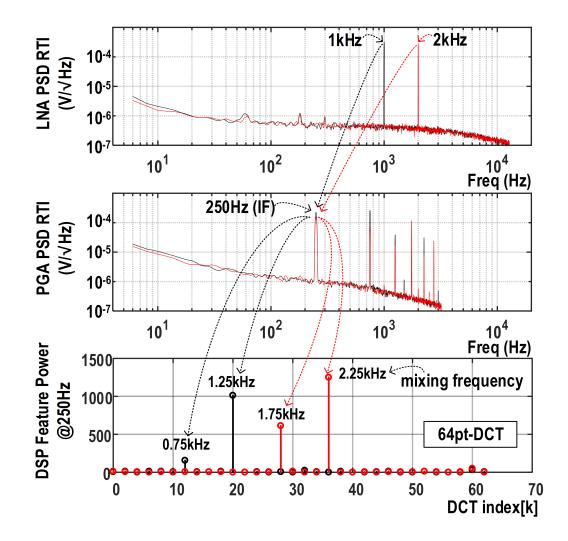

| 4.17 | Power spectral density referred to input (PSD RTI) for LNA, PGA,                                                                    |    |

|      | and DSP. Two different applied tones (1 and 2 kHz) are mixed down                                                                   |    |

|      | to 250 Hz in IF and extracted by DSP at two mixing frequencies each                                                                 |    |

|      | (0.75  and  1.25  kHz for  1  kHz and  1.75  and  2.25  kHz for  2-kHz tone).                                                       | 74 |

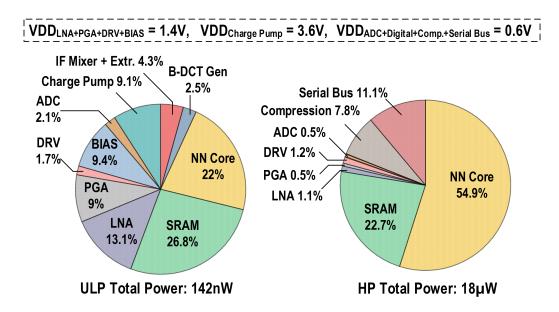

| 4.18 | Measured power distribution of ULP mode (left) and HP mode (right).                                                                 | 75 |

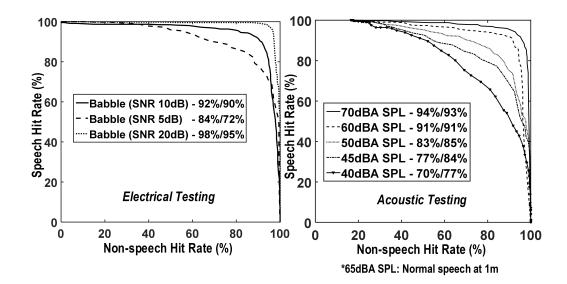

| 4.19 | ROC curves for ULP VAD mode with varying SNRs in the electrical                                                                     |    |

|      | test (electrical connection to LNA, left) and SPLs in the acoustic test                                                             |    |

|      | (using speaker/integrated microphone in the sound chamber, right).                                                                  | 76 |

|      |                                                                                                                                     |    |

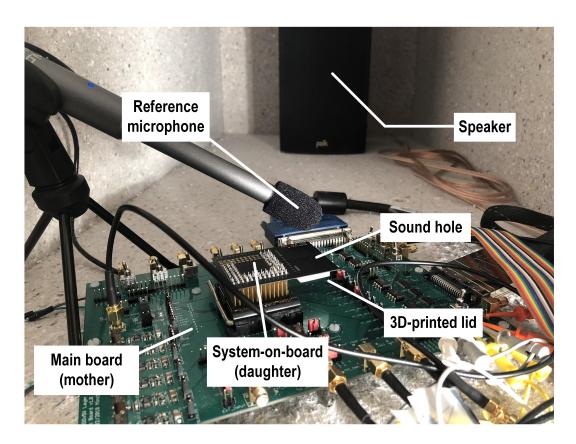

| 4.20 | Acoustic testing setup. Proposed chip was integrated into the system-     |    |

|------|---------------------------------------------------------------------------|----|

|      | on-board with a MEMS microphone and 3-D-printed lid and tested            |    |

|      | in a sound chamber                                                        | 76 |

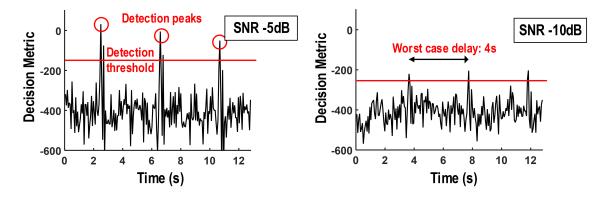

| 4.21 | Measurement results of acoustic signature wakeup detection with           |    |

|      | MLS sequence of six stages, $N_{MLS} = 63$ , and $x_{MLS} = 1$ at various |    |

|      | SNRs, showing detection down to -10-dB SNR                                | 77 |

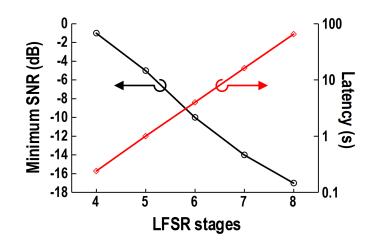

| 4.22 | Measurement results of acoustic signature wakeup detection with var-      |    |

|      | ious LFSR stages, showing the tradeoff between the minimum re-            |    |

|      | quired SNR versus worst case detection latency.                           | 78 |

| 4.23 | Measured waveform of the acoustic system that switches between            |    |

|      | ULP and HP modes.                                                         | 79 |

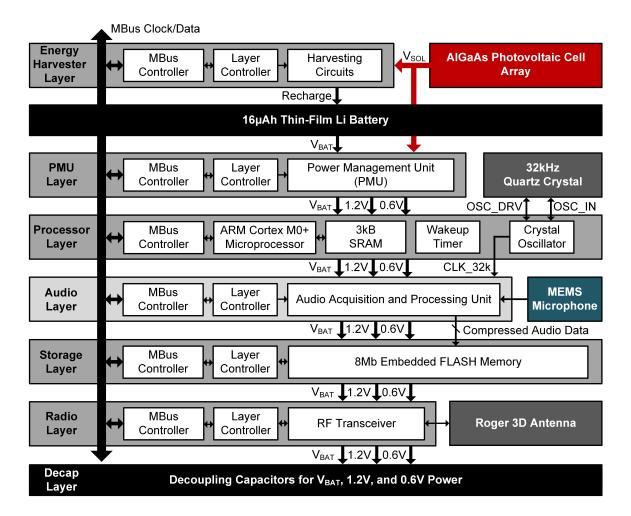

| 5.1  | Overall block diagram of the first generation audio sensor node           | 82 |

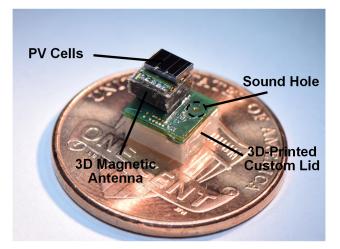

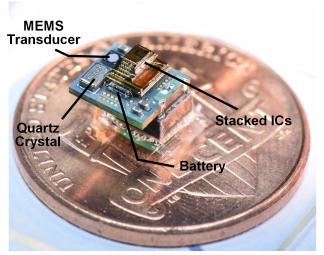

| 5.2  | The complete $6 \times 5 \times 4 \text{ mm}^3$ audio sensor node         | 84 |

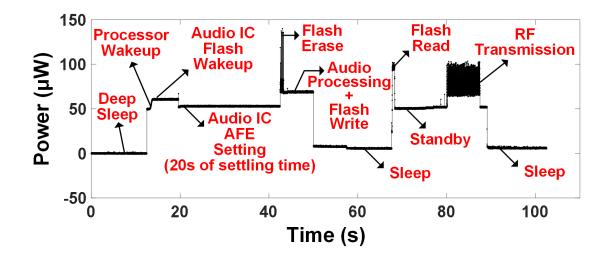

| 5.3  | Measured power profile of audio sensor node                               | 85 |

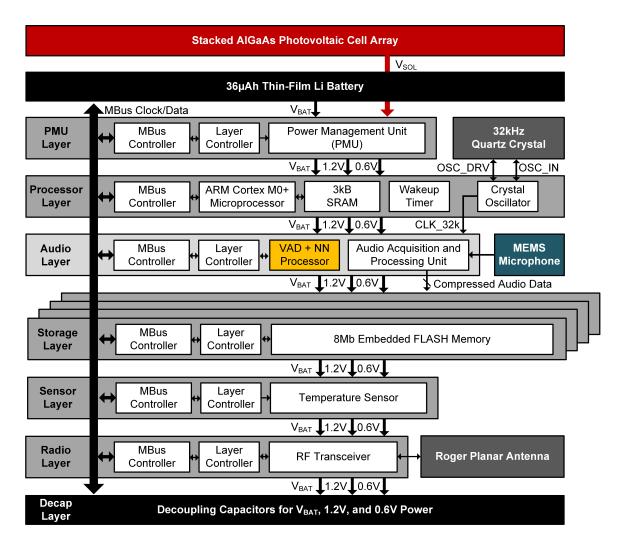

| 5.4  | Overall block diagram of the second generation audio sensor node          | 86 |

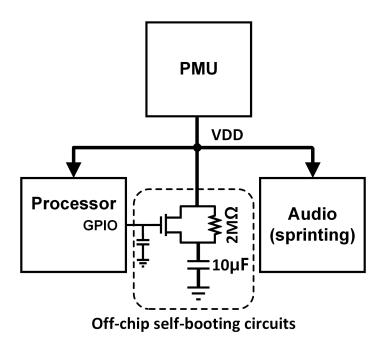

| 5.5  | Self booting circuits using COTS components                               | 87 |

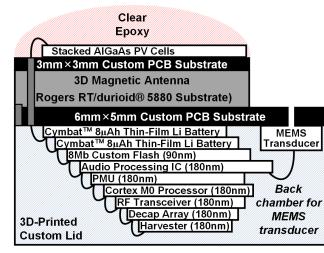

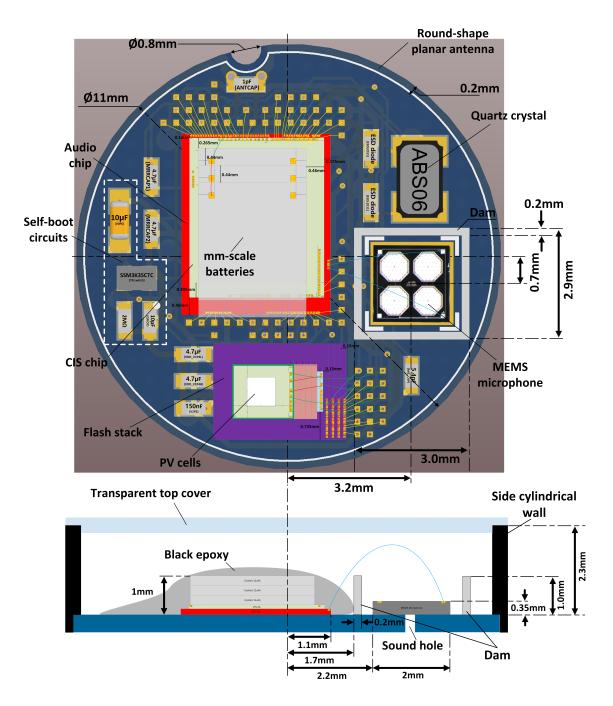

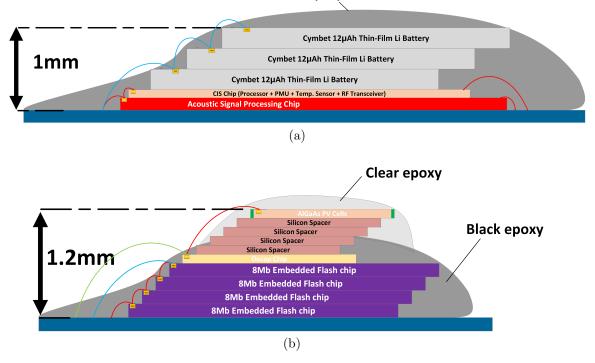

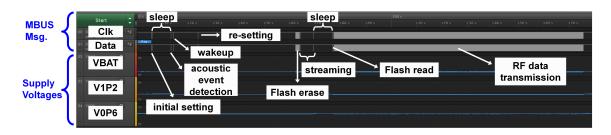

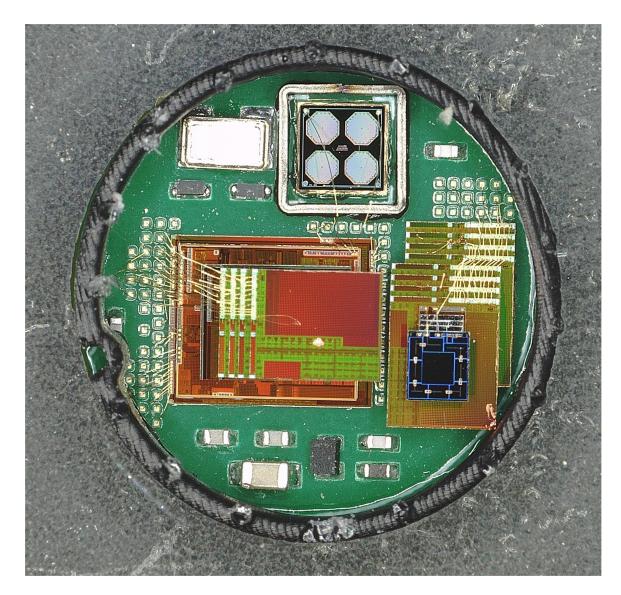

| 5.6  | Planar and side view diagram of system integration                        | 89 |

| 5.7  | Vertical view of (a) main processing stack and (b) storage stack          | 90 |

| 5.8  | Audio sensor system operation cycle.                                      | 91 |

| 5.9  | The complete $\phi 11$ mm × 3mm audio sensor node                         | 92 |

# LIST OF TABLES

## <u>Table</u>

| 2.1 | Measurement Summary of Analog Front-End     | 13 |

|-----|---------------------------------------------|----|

| 2.2 | Measurement Summary of ADC                  | 17 |

| 2.3 | Compression Algorithm Comparison            | 22 |

| 2.4 | Measurement Results of Compression Ratio    | 28 |

| 2.5 | Summary of Audio Processing IC              | 31 |

| 2.6 | Comparison of Embedded Flash ICs            | 32 |

| 3.1 | Instruction Set of On-Sensor NN Processor   | 37 |

| 3.2 | Comparison of Neural Network Processor      | 48 |

| 3.3 | Measured Acoustic Object Detection Accuracy | 50 |

| 4.1 | Comparison of Feature Extractor             | 80 |

| 4.2 | Comparison of Voice Activity Detector (VAD) | 80 |

| 5.1 | Comparison of Developed Audio Sensor Node   | 91 |

### ABSTRACT

Distributed audio sensing is promising to bring full bloom of a variety of applications to improve human life. However, despite of the continued efforts, the state-ofthe-art audio sensor node systems still remain at centimeter-scales in size, preventing true ubiquitous and unobtrusive deployment of them. Meanwhile, the silicon technology has been remarkably advanced, dictated by Moore's Law, and this enables a new opportunity to realize millimeter-scale of computing. In this dissertation, we explore a way to develop a millimeter-scale wireless audio sensor node system, by combining the integrated silicon technology, machine learning, and low-power circuit techniques.

This dissertation first presents an audio processing IC that performs audio acquisition and compression, consuming  $4.7\mu$ W. A new low-power compression algorithm and its accelerator consume only  $1.5\mu$ W to provide  $4-32\times$  real-time audio compression. Newly designed custom 8Mb embedded NOR Flash enables seamless audio streaming by a ping-pong buffering scheme.

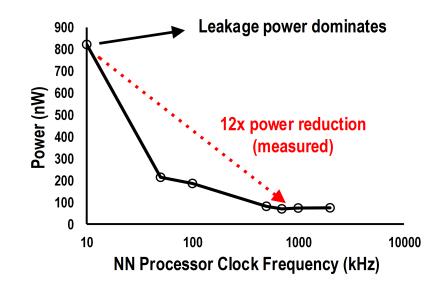

Second, a picowatt-level standby power neural network processor is introduced for sensor applications. By combining custom instruction set architecture, compact SIMD microarchitecture, and ultra-low leakage SRAM memory, the processor consumes only 440pW of power at standby mode while achieves 400-GOPS/W of energy efficiency at active mode, which is suitable for modest neural network workloads on miniaturized sensor platforms. The proposed neural network processor is integrated in an acoustic object detection sensor system, and successfully demonstrates >90% of positive detection and <3% of false alarm for 5 acoustic targets detection. Next part of this dissertation is a voice and acoustic activity detector that uses a mixer-based architecture and ultra-low power neural network based classifier. By sequentially scanning 4 kHz of frequency bands and down-converting to below 500 Hz, feature extraction power consumption is reduced by  $4\times$ . The neural network processor employs computational sprinting, enabling  $12\times$  power reduction. The system also features inaudible acoustic signature detection for intentional remote silent wakeup of the system while re-using a subset of the same system components. The measurement results achieve 91.5%/90% speech/non-speech hit rates at 10 dB SNR with babble noise and 142 nW power consumption. Acoustic signature detection consumes 66 nW, successfully detecting a signature 10 dB below the noise level.

Finally, two generations of complete, fully functional energy-autonomous audio sensor nodes with millimeter-scale form factor are demonstrated. The systems use the proposed audio processing ICs and neural network processor integrated with a MEMS microphone, general-purpose microprocessor, 8Mb Flashes, RF transceiver with custom antenna, PV cells for energy harvesting and optical communication, and millimeter size batteries. The complete stand-alone systems achieve 1 hour (1st gen.) and 3.2 hours (2nd gen.) of continuous speech recording and energy-autonomous operation in room light.

The research in this dissertation is believed to pave a way towards distributed, intelligent audio sensing and computing.

## CHAPTER I

## Introduction

Recent advance of distributed sensing systems has made devices feasible that can sense their environment and perform actions based on the collected data. This new technology has attracted a lot of attention from both industry and research community, and has also opened up a myriad of civilian and military applications. Especially, the distributed systems that are wirelessly interconnected compose the wireless sensor network (WSN), which enables remote retrieving of video and audio streams, images, and scalar sensor data such as temperature, pressure or humidity. Moreover, the long-term collection of big data based on these networked sensors has gaining huge popularity for Internet of Things (IoT) applications, in accordance with the recent success of machine learning (ML) and artificial intelligence (AI). In this paradigm, every objects surrounding our daily lives will be wirelessly connected, gather information, and will identify, classify, infer, correlate, and fuse the information from heterogeneous sources, which is expected to bring benefits for the improved quality of our daily life.

To be benefited by massively distributed sensor networks, the size reduction of each sensor device is paramount. Minuscule size makes the sensors as easy-to-deploy and unobtrusive as possible, minimizing the disturbance to human activity. In addition, small form factor enables the placement of sensor devices in completely new locations where computing was absent before. In that vein, the 'smart dust' concept was proposed in [1, 2], envisioning the applications and usage scenario of a sensor node with the size of grain of salt, with primary focus on wireless communication and networking architecture. Since then, miniaturized wireless sensor nodes have been a popular topic of research in the cyber-physical systems community. More recently, M<sup>3</sup> (Michigan Micro-Mote) sensing platform was introduced in [3], with more focus on hardware design perspective. The platform features millimeter-scale modular architecture and various system-level techniques. With staircase stacking method of four bare-die ICs and one battery, the overall system only consumes 1.0 mm<sup>3</sup> of volume.

However, prior achievements of size shrinking have been only limited to sensor nodes with low dimensional sensing modalities, such as temperature [4], pressure [5,6], pH [7], and simple still cut images [8]. On the other hand, acoustic sensing is gaining more attention as it offers several advantages over other sensing modalities. The information carried by sound is comparable to that of video, yet requires much lower computational cost to be processed for the realization of highly resource constrained platforms. Sound is captured omni-directionally and intrinsically tolerant to light or obstacles, thus enables simultaneous multi-targets and/or events detection without careful positioning or adjustment. In addition, human voice is one of the most natural way to communicate with machines, avoiding the use of one's hands. Due to a variety of these merits, audio sensing and processing are widely adopted in extensive applications such as smart grid and home automation [9], ambient assisted living (e.q. patients support) [10], structural monitoring [11], biodiversity assessment [12], environmental monitoring for urban [13] and nature [14], surveillance [15, 16], localization [17], and voice user interfaces [18, 19]. Realizing audio sensing capability on miniaturized wireless sensor node will further provide enriched opportunities to broaden its applications, as the massively distributed audio sensor network will facilitate innovative information acquisition and processing to reshape interactions between

Figure 1.1: The  $\mu$ AMPS sensor node (2000).

people, environment, and devices.

#### 1.1 Prior Art: Wireless Audio Sensor Motes

The journey for the development of miniaturized wireless audio sensor node began in the late 1990's. In 1999, Rockwell Science Center and UCLA were engaged in a joint research program for DARPA/TTO, and developed a prototype microsensor node called AWAIRS 1 (Adaptive, Wireless Arrays for Interactive RSTA in SUO) [20]. This device consists of modular architecture, in that the modular boards can be freely stacked up on top of the existing system to support additional sensor interfaces. The system features Intel SA1100 microprocessor based on 32-bit ARM RISC architecture, 128KB of SRAM and 1MB of Flash storage, >100m of wireless connectivity at 100Kbps, and 2kHz bandwidth of audio interface. Two 40-pin mini-connectors are used as a system bus, connecting all module boards. The system consumes 1W and the size of a node is  $7 \times 6.7 \times 8.0$  cm<sup>3</sup>. In 2000,  $\mu$ AMPS mote was developed by MIT [21] for the acoustic sensing applications, as shown in Figure 1.1. The work improves the power consumption through the power-aware operation methodology

Figure 1.2: (a) Audio sensor mote for acoustic scenes monitoring (2009) (b) TinyEARS (2013).

such as dynamic voltage scaling, energy-quality trade-off, and fine-grained control over power states of radio module depending on the transmission range.

Afterward, lots of miniaturized wireless sensor platform have been surged for both academic and commercial purposes, such as BTnode (2001) [22], Medusa MK2 (2002) [23], IMOTE (2003) [24], MICA/MICA2/MICA2 (2004) [25], Telos/TelosB (2005) [26], Waspmote (2008) [27], LOTUS (2011) [28], and .NOW eMote (2012) [29]. Although these motes have been improved in terms of their size, performance and power consumption as the Moore's Law continued, their architectural solution remain same as AWAIRS 1, using pluggable modules to create an acoustic sensing interface. None of these works have exploited the opportunity of benefits from built-in integration and optimization for the audio sensing and processing tasks. Instead, they provide suitable ports to allow a variety of sensors to be attached for more versatility.

There yet exists several works to devise miniaturized wireless sensor node dedicated to audio applications. In [30, 31], the authors proposed a sensor mote based on the commercial MICAz [32] platform. The mote shown in Figure 1.2a was developed for voice activity detection (VAD), gender classification, and acoustic feature extraction for further processing in base-station. To process audio signal more ef-

Figure 1.3: InfiniTime (2016).

ficiently, they attached digital signal processing (DSP) module, which includes TI TMS320C6713 DSP chip operating at 225MHz, to the mote. Although it provides profound capability to process various audio tasks in real-time, it draws >500mA of current, and its size is 21 cm  $\times$  11.5 cm, limiting its practical usage. A custom sensor node with self-designed analog front end (AFE) interfacing microphone to fine-grained control over parameters and power consumption was proposed in [33] for acoustic event detection. This system consumes 200mA at active mode, but the  $1.5\mu$ A of sleep mode current and highly duty-cycled operation enable the power supply from a super capacitor and solar harvesting, achieving unattended operation of a sensor node. However, since this node system aimed for infrequent event detection whose sampling rate is similar to that of scalar sensors, its operation under the harvesting is not scalable to general-purpose real-time audio streaming applications, considering its active power level. Moreover, the system size of a few hundreds of  $cm^2$  reduces its efficacy of broad deployment. The authors of [34] developed a wireless audio sensor mote based on IMOTE2 [35] as shown in Figure 1.2b for household appliances power monitoring network based on acoustic signature. The IMOTE2 has a built-in DSP coprocessor with wireless MMX instruction set enabling low power signal processing acceleration. By the benefit from it, the system efficiently implements audio signal processing pipeline such as FFT, MFCC, and feature extraction at 30mA of active current consumption within  $3.6 \times 4.8 \times 1.5$  cm<sup>3</sup> of volume, realizing a centimeter-scale audio sensing. The power consumption of an audio sensor node is further improved in [36] by the holistically customized system design, avoiding the use of any existing platforms. This flexibility of system design allows extreme power management to keep the quiescent and operative energy consumption low. The realtime audio acquisition consumes only 1.2mA, and the system size is approximately 4  $\times$  6 cm<sup>2</sup> as shown in Figure 1.3.

Although a lot of efforts have pursued to reduce the form factor of audio sensor node, they still remain at centimeter-scales. In addition, mA-level of power consumption prevents to further shrink the size of system due to the constraint from battery size. Thus, this dissertation focuses on the realizing of millimeter-scale audio sensor node to enable pervasive audio computing.

### 1.2 Challenges of Achieving Millimeter-Scale Audio Sensing

For many applications of wireless audio sensor network, frequent battery recharging or replacement is unlikely feasible, especially in large scale deployments with thousands of densely distributed nodes, or for nodes placed in where hard to access. Thus, long enough life time under the battery and/or autonomous operation by energy scavengers are indispensable. Meanwhile, the advance in battery technology is lagging [37], as the amount of energy stored in the micro battery is decreased proportionally to its size. This battery size limitation imposes critical constraint on the miniaturization of audio sensor node. Therefore, the energy efficiency and low power operation of every components in the system are critical to guarantee the unattended operation of a sensor node for a long time, and as a corollary, to achieve ultra-small form factor.

Figure 1.4: Energy consumption vs. compression ratio on (a) IMOTE2 platform and (b) TELOS platform.

Typically, wireless transmission of sensed data over the network dissipates the most of power in a sensor system [38]. Consequently, in addition to the low power wireless protocols and transceivers, the data compression also plays as a key enabler for miniaturized audio sensor node, by reduction of the required network bandwidth. Furthermore, the compression saves more space of system storage, allowing longer audio logging and more complex on-edge post processing. For example, in [35], the authors implemented audio compression algorithm based on linear prediction to prove the benefit of on-sensor compression over the raw data transmission. Depending on the compression ratio, the compression reduced overall energy consumption by  $9 \times$  at the most when  $15 \times$  compression is applied as shown in Figure 1.4a. For this purpose, many researchers have attempted to implement built-in compression on the audio sensor node, such as  $4 \times$  compression by G.726 at 26mA [39],  $16 \times$  compression by Speex at 260mA [40], and  $1.6 \times$  compression by linear prediction at  $\sim 3$ mA [38]. However, all these prior works used off-the-shelf algorithms based on software implementation, and thus the compression itself easily consumes > mA of current even with the very simple algorithm, which provides minimal compression ratio. As shown in Figure 1.4b, even the same compression algorithm and implementation on different hardware platform

Figure 1.5: Sensor system lifetime vs. event activity: When the event of interest occurs infrequently, the always-on detector would determine the lifetime.

give worse results due to the hardware inefficiency. Therefore, both more efficient compression algorithm and its hardware acceleration should be devised to make the energy and power consumption below the budget of millimeter-scale batteries and harvesters.

Another important challenge is to minimize standby power of overall system since a sensor node stays at standby or sleep mode a vast majority of time. Such low energy resource systems rely heavily on the duty-cycled operation to ensure long lifetime especially for audio sensing applications where the event of interest occurs infrequently. As the standby power dominates over time, the leakage current of each system component should be minimized. In addition, deliberated system wakeup method should be considered to use limited resources more efficiently. Conventionally, the audio sensor motes include low power wakeup timer to wake system up with a predefined period [33, 34]. However, this periodic wakeup may miss the events or waste resources at out-of-events. Instead of predetermined wakeup, the host can send a query to a node by network, and then the low power wireless wakeup receiver could trig the system up to start the tasks [38]. Although this method delivers high flexibility to the host or user when to wake the system up, it charges a burden of careful managing strategy of whole network to the host, resulting in high system complexity and costs. Moreover, this method also fails to avoid the event hit and miss problem without prior knowledge about the event rate and instances. Therefore, the development of more efficient yet low power wakeup method for audio applications is highly required. The wakeup method should intelligently detects the event of interest so that the sensor system knows by itself the event rate and instances. However, at the same time, the wakeup method should also consume minimal power since the always-on wakeup detector would dominate overall average system power when the event of interest occurs infrequently as shown in Figure 1.5.

Finally, since the wireless audio sensor node consists of many COTS components such as microphone, quartz crystal, antenna, and solar-cells for autonomous operation, achieving millimeter-scale form factor is extremely challenging. Thus, the physical integration process of a system must be carefully devised to reduce the size dramatically.

#### **1.3** Dissertation Overview

This dissertation seeks to develop a millimeter-scale wireless audio sensor node enabled by various low-power integrated circuit architectures and designs, addressing the aforementioned challenges.

In Chapter II, the design of low-power audio processing chip is studied. Along with analog front-end circuits to interface with a MEMS microphone, a novel audio compression algorithm is proposed and the hardware architecture for the acceleration of it is discussed, resulting in  $4-32\times$  real-time audio compression while consuming  $1.5\mu$ W.

Chapter III introduces an ultra-low standby power neural (NN) network processor. As the ML and AI show rapid progress, there is a surging need for built-in processing capability of ML workloads on sensor node. The proposed on-sensor NN processor meets the need while consumes only 440pW of standby power, enabling long lifetime of duty-cycled, miniaturized sensor systems. The proposed processor is integrated in acoustic sensor system and demonstrates >90% of detection accuracy for multiple acoustic objects in real-time.

Chapter VI discusses acoustic wakeup methods for the audio sensor nodes. A lowpower voice activity detection (VAD) technique is proposed to make a human speech activity as a target wakeup event. The design of VAD chip is detailed and validated in 180nm CMOS technology. Moreover, a wakeup method based on acoustic signature is also studied in this Chapter. The proposed VAD consumes 140nW of power with >80% of accuracy at 50 dBA SPL of sound, and the acoustic signature detection consumes only 66nW.

Finally, two generations of millimeter-scale wireless audio sensor nodes are demonstrated in Chapter V, with the system design and integration strategy.

### CHAPTER II

# A Microwatt Power Audio Processing IC and 8Mb Streaming Flash Memory

#### 2.1 Introduction

Realizing a millimeter-scale audio processing platform enables a number of new IoT applications such as distributed audio recording, event logging, and security monitoring. While several efforts [39, 40] have sought to miniaturize audio sensors, their centimeter-scale volume and >20mW power severely limit use as an unobtrusive, selfpowered sensing node. The key challenge to reduce the form factor of audio sensor node is low power operation due to the small battery size as shown in Figure 2.1. For example, the audio mote consuming 330mW [39] can only last 0.7s with millimeterscale thin-film Li battery ( $16\mu$ Ah, 4V). In addition, small physical size severely limits the capacity of data storage. As shown in Figure 2.1, a 1×0.85 mm<sup>2</sup> NOR Flash has less than 2Mb density [41]. Consequently, power efficient data compression is a key enabler in that it not only mitigates the size requirement of on-site storage, but also reduces wireless transmission energy. However, 22mA of current consumption in [40] implies that compression itself requires high computation burden. One another enabler for small form factor of audio sensor node is a power efficient compact non-volatile storage to save audio footage. Since a sensor node is typically highly

Figure 2.1: Miniaturized audio sensor challenges.

duty cylced, it spends only a fraction of their time in active mode. Therefore, embedded Flash memory is a good candidate to store measured audio data, allowing the other system components to be power-gated in standby mode. This chapter demonstrates an audio processing IC that consumes only  $4.7\mu$ W for signal acquisition and compression. The proposed compression engine operates in real-time at  $1.44\mu$ W. In addition, this chapter also introduces an 8Mb custom NOR Flash for continuous audio streaming and retention.

#### 2.2 Audio Processing IC

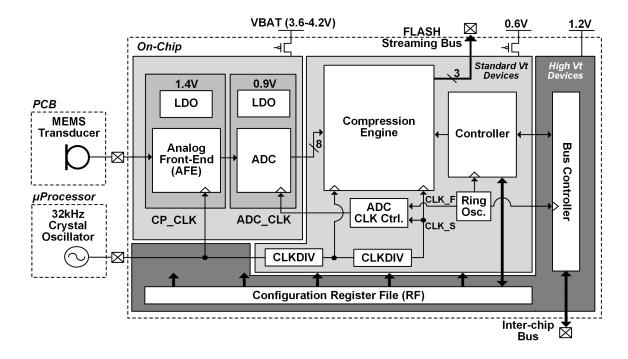

Figure 2.2 shows the architecture of the proposed audio processing IC that integrates AFE, ADC and compression engine. First, we use capacitive MEMS microphone, and it requires 10V bias voltage for the optimal sensitivity [42]. The charge pump generates bias voltage directly from battery voltage, VBAT (3.6 - 4.2V). The AFE and ADC operate at 1.4V and 0.9V respectively, regulated by on-chip LDOs from the battery to decouple them from the noisy digital supply. To optimize the power consumption, we employ multi-voltage, multi-threshold design strategy for the digital circuits. The compression engine operates at 0.6V with standard threshold transistors

Figure 2.2: Overall architecture of audio processing IC.

to meet the real-time throughput constraint. These logic blocks are power-gated in sleep mode. The 1.2V bus controller and configuration register file are always-on and thus use thick oxide I/O devices to reduce leakage current.

| Table 2.1: Measurement Sum | nmary of A        | nalog Front-End     |

|----------------------------|-------------------|---------------------|

| This Work                  |                   |                     |

| Supply                     | $1.4\mathrm{V}$   |                     |

| Gain                       | 20-48dB           |                     |

| Bandwidth                  | 4kHz              |                     |

| Input referred noise (IRN) | $13.2\mu V_{rms}$ | $_{s}$ (A-weighted) |

|                            | LNA               | $1.1 \mu A$         |

| Current                    | VGA               | $0.8 \mu A$         |

|                            | Total             | $1.9 \mu A$         |

| NEF                        |                   | 11.1                |

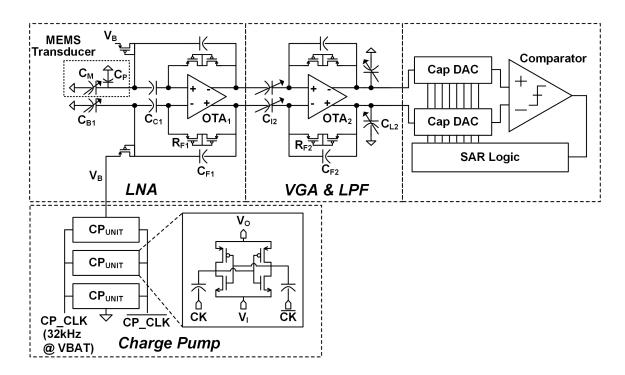

Figure 2.3: Analog front-end (AFE) and ADC circuits.

#### 2.2.1 Analog Front-End Design

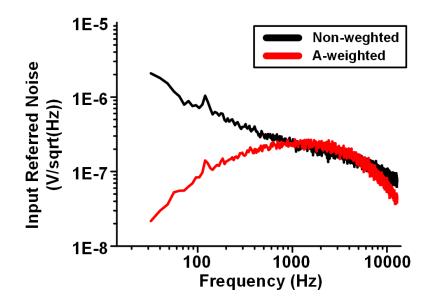

The analog front-end (AFE) shown in Figure 2.3 consists of low noise amplifier (LNA), variable gain amplifier (VGA) and charge pump. The charge pump biases the MEMS transducer at 10V. It is based on 3-stage voltage doubler circuits and generates bias voltage with 32kHz of clock. Note that to realize differential structure, dummy capacitors and resistors (pseudo) are added on the other side of microphone, matching the input impedance. The LNA gain (29dB) is set by the MEMS capacitance over the feedback capacitance ( $C_M/C_{F1}$ ), and the gain and bandwidth of VGA are tuned by capacitor arrays  $C_{I2}$  and  $C_{L2}$ , respectively.  $R_{F1,2}$  sets input common-mode voltage and removes offset. To maximize noise efficiency, OTA<sub>1</sub> and OTA<sub>2</sub> use inverter-based cascode amplifier and their input-pair transistors operate in subthreshold region. The bandwidth of this analog gain stages was set to 4kHz. Figure 2.4 shows measured input referred noise (IRN) spectrum of the AFE. The LNA and VGA consume 1.54 $\mu$ W and 1.11 $\mu$ W, respectively, to achieve 20.1 $\mu$ V<sub>rms</sub> (non-weighted) and 13.2 $\mu$ V<sub>rms</sub> (A-

Figure 2.4: Measured input referred noise spectrum of AFE.

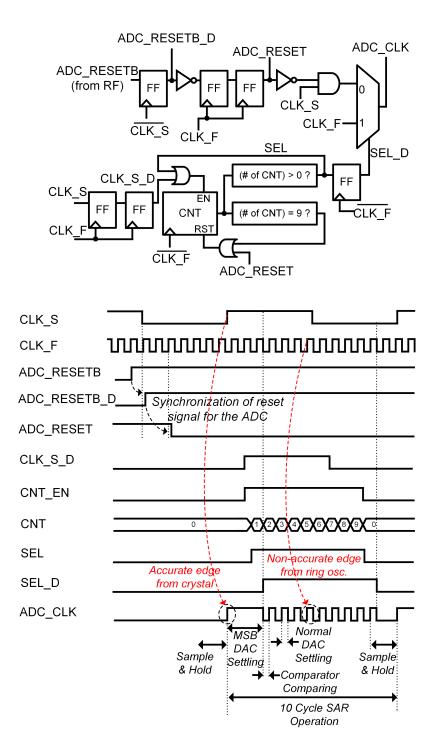

weighted) IRN with 4kHz of bandwidth. The measurement results of the AFE is summarized in Table 2.1. After gain stages, the 8-bit synchronous SAR ADC (Figure 2.3) digitizes the incoming amplified and filtered audio signal. The ADC operates on two separate clocks: an 8kHz clock (CLK\_S) for sample and hold, and a 150kHz clock (CLK\_F) for the internal SAR control logic. Since the audio signal is processed in the frequency domain at compression engine, the frequency stability and phase noise of CLK\_S can directly affect the audio compression quality while CLK\_F has significantly relaxed constraints. The 32kHz external crystal clock is divided to 8kHz (CLK\_S) and merged with internal 150kHz clock (CLK\_F) obtained from a powerefficient ring oscillator at 0.6V by the ADC clock controller as shown in Figure 2.5. With this controller scheme, the need of high frequency crystal oscillator for the synchronous SAR ADC clocking can be vanished. The measured SNDR of ADC is 46.1dB which corresponds to 7.4-bit ENOB, and the FoM is 100fJ/Conv as shown in Figure 2.6. The ADC consumes only 135nW of power. Table 2.2 summarizes the measurement results of ADC.

Figure 2.5: Synchronous SAR ADC clock controller circuits and its operational timing diagram.

|               | This Work              |  |  |  |  |

|---------------|------------------------|--|--|--|--|

| Supply        | $0.9\mathrm{V}$        |  |  |  |  |

| $\mathbf{Fs}$ | 8kHz                   |  |  |  |  |

| INL           | +0.26/-0.34 LSB        |  |  |  |  |

| DNL           | +0.27/-0.17 LSB        |  |  |  |  |

| SNDR          | 46.1dB                 |  |  |  |  |

| ENOB          | 7.4bits                |  |  |  |  |

| Power         | $135 \mathrm{nW}$      |  |  |  |  |

| FoM           | $100 \mathrm{fJ/Conv}$ |  |  |  |  |

Table 2.2: Measurement Summary of ADC

Figure 2.6: Measured DNL, INL, and frequency spectrum of ADC.

Figure 2.7: Proposed compression algorithm.

#### 2.2.2 Compression Algorithm

Compression of the audio stream is critical to minimize storage size, access energy, and wireless transmission energy. However, real-time audio compression is a computationally intensive task. Thus compression power itself should be minimized for the proposed ultra-small audio sensor node.

The proposed power efficient compression algorithm is shown in Figure 2.7. The incoming samples are first converted to the frequency domain using polyphase subband filtering (PSF). This filtering technique critically samples the incoming signal by modulating and decimation, meeting Nyquist criteria for each center frequency of band-pass filter in filter bank. By nature, this filter technique reduces the amount of data by eliminating overly sampled portions. However, due to the non-ideal band-pass filter characteristic, signal aliasing always occurs, and therefore it results in a lossy compression. In contrast to the block transform such as FFT, this filter bank overlaps in time domain and avoids block edge artifacts. Once the signal is filtered by equally spaced 32 filter bank, the power of each subband is accumulated during 1 frame which consists of 6 samples. And then, each accumulated power is compared with a programmable power threshold. The subbands having lower power than a thresh-

Figure 2.8: Polyphase Quadrature Filtering (PQF) process.

old are eliminated, and we only select subbands whose power exceed the threshold. Then, the number of selected subbands is compared with a pre-determined (but, programmable) number N. If the number of remaining subbands exceeds the number N, the highest power of N subbands are selected by sorting. This processes guarantees a constant worst-case compression rate but, in general, the final compressed bit rate can vary depending on the frequency domain sparsity of the signal. Finally, logarithmic-compressed quantization is applied to further reduce data rate.

In this algorithm, the complexity of the PSF dominates others. To have linear phase shift to prevent any phase distortion for audio quality, 512-tap FIR filter is used to realize band-pass filters. The filtered signal can be represented as follows:

$$s_t[i] = \sum_{n=0}^{511} x[t-n] \times H_i[n]$$

(2.1)

where  $H_i$  is an impulse response of the *i*-th band-pass filter, x[t] is an audio sample at time *t*, and  $s_t[i]$  is the filter output sample for subband *i* at time *t*, where *t* is an integer multiple of 32 audio sample intervals. In the PSF, the band-pass filter can be regarded as a modulated version of a prototype low-pass filter as follows:

$$H_i[n] = h[n] \times \cos[\frac{(2i+1)(n-16)\pi}{64}]$$

(2.2)

where h[n] is a prototype low-pass filter. This plain implementation of PSF requires 1023 OP/sample of complexity. To reduce power, we apply a mathematicallyequivalent but more computationally efficient polyphase quadrature filtering (PQF) [43]. Since the sinusoid in Equation 2.2 contains an odd number of half cycles in 64 coefficients, blocks of 64 products of the multiplications are accumulated with the sign of alternate blocks negated. These 64 points are then multiplied by 32 sinusoids to generate 32 output samples. This process is depicted in Figure 2.8. From the explained PQF process, we can derive the following equation for the filter bank outputs:

$$s_t[i] = \sum_{k=0}^{63} \sum_{j=0}^7 M[i][k] \times (C[k+64j] \times x[k+64j])$$

(2.3)

where

$$C[n] = \begin{cases} -h[n] & n/64 = odd \\ h[n] & \text{otherwise} \end{cases}$$

(2.4)

$$M[i][k] = \cos\left[\frac{(2i+1)(k-16)\pi}{64}\right]$$

(2.5)

This implementation requires 157 OP/sample, which is 84% reduction in the complexity. Then, this filtering is further optimized by inverse discrete cosine transform (IDCT) conversion [44]. Equation 2.3 can be re-written as follows:

$$s_t[i] = \sum_{k=0}^{63} y[k] \times \cos\left[\frac{(2i+1)(k-16)\pi}{64}\right]$$

(2.6)

Figure 2.9: Compelxity reduction from the algorithm optimization.

By re-arranging the y[k] sequence, the above equation is re-formulated as follows:

$$s_t[i] = \sum_{k=0}^{63} y'[k] \times \cos\left[\frac{(2i+1)k\pi}{64}\right]$$

(2.7)

where

$$y'[k] = \begin{cases} y[16] & k = 0\\ y[k+16] + y[16-k] & k = 1, 2, ..., 16\\ y[k+16] - y[80-k] & k = 17, 18, ..., 31 \end{cases}$$

(2.8)

Equation 2.7 is well-known IDCT fomula. This optimization reduces the complexity to 93 OP/sample. Finally, IDCT computation is performed using a mathematically equivalent inverse FFT (IFFT) operation as follows:

let

$$X[k] = y'[k] \times e^{jk\pi/2N}$$

$k = 0, 1, 2, ..., 31$  (2.9)

$$x[m] = Re[FFT^{-1}(X[k])] \quad m = 0, 1, 2, ..., 31$$

(2.10)

| Table 2.3: Compression Algorithm Comparison |                 |                     |                       |                      |

|---------------------------------------------|-----------------|---------------------|-----------------------|----------------------|

|                                             | MPEG Layer III  | CELP                | $ADPCM^1$             | This Work            |

| Raw Data $Rate^2$                           |                 | 64kbps              |                       |                      |

| Compressed Data Rate                        | 32kbps          | $9.6 \mathrm{kbps}$ | $16 \mathrm{kbps}$    | $4.07 \mathrm{kbps}$ |

| Compression $\operatorname{Ratio}^3$        | 2               | 6.7                 | 4                     | 15.7                 |

| Latency<br>Variable Bit Rate                | >100ms<br>Yes   | 30ms<br>Yes         | $\stackrel{<2ms}{No}$ | 32ms Yes(2-16kbps)   |

| Complexity                                  | 3000  op/sample | 45000  op/sample    | 4  op/sample          | 61  op/sample        |

| $ODG^4$                                     | 0.2             | -3.873              | -3.885                | -3.879               |

Table 2.3: Compression Algorithm Comparison

<sup>1</sup>Linear ADPCM with 1'st order prediction

<sup>2</sup>Male voice in English

<sup>3</sup>Raw data rate/compressed data rat

<sup>4</sup>Objective Difference Grade; -4(very annoying) - 0(imperceptible)

then

$$s_t[i] = \begin{cases} s_t[2i] = x[i] & i = 0, 1, 2, ..., 15 \\ s_t[2i+1] = x[31-i] & i = 0, 2, ..., 15 \end{cases}$$

(2.11)

By the efficiency of FFT computation, the complexity is reduced to 57 OP/sample. Overall, the complexity is reduced by 94% in total from aforementioned algorithm optimizations as shown in Figure 2.9. A comparison between the proposed and other off-the-shelf algorithms is shown in Table 2.3. Maintaining similar sound quality, the proposed algorithm has  $1000 \times$  lower complexity than CELP and  $3.9 \times$  better compression than ADPCM.

#### 2.2.3 Compression Engine Architecture

The fixed-point pipelined architecture is proposed to implement the algorithm efficiently as shown in Figure 2.10 and Figure 2.11. Multiple word widths with different fixed-point positions are applied to balance between the power consumption and truncation error.

The proposed polyphase quadrature filter implementation is shown in Figure 2.10. To realize polyphase quadrature filter, previous 512 samples must be latched to be processed while new samples are continuously streamed in at sampling rate, which

Figure 2.10: Polyphase quadrature filter architecture.

requires 512-entry FIFO shifted at 8kHz consuming 62% of total compression power. To address this predominance, new samples are streamed into 32-entry FIFO instead, and shift operation of whole samples is performed block-by-block only when 32-entry FIFO becomes full. Consequently, 512-entry FIFO is clock gated until the next block shift, resulting in  $32 \times$  power reduction. In addition, we observe that 25% of filter coefficients are zero, allowing us to inactivate unused samples and to eliminate corresponding registers and datapath. The 512 samples are re-arranged and R2SDF based 32-point FFT is performed to realize the optimized subband filtering.

Filtered data are then stored in a sub-frame buffer as shown in Figure 2.11a. Since compression is performed in a frame (i.e., 6 sub-frames) basis, the two additional buffers are added (i.e., total 8 sub-frame buffers) as ping-pong buffers to store next frame data while processing the current frame. The sub-frame buffers and power accumulators are clock gated with frame based operation, and this clock gating shows 34% of total engine power reduction (simulated). Moreover, along with clock gating, the data gating is used to avoid unnecessary data switching on shared data bus of sub-frame buffers. This data gating further reduces the power consumption by 25% (simulated).

For frequency-rich signals, sorting operation is necessary. The proposed sorting

Figure 2.11: Compression engine architecture.

unit uses a tree structure as shown in Figure 2.11b), where all processing elements (PEs) compare and forward their inputs in the 1st cycle to obtain the top result. Hence, every PEs are active in the 1st cycle. Then, in each subsequent cycle the winning PE zeros its value and only its related path is updated to produce the next highest values. So for the remaining cycles until finding the top N out of 32, only a fraction of PEs are in active. Compared with a conventional parallel sorter, such as bitonic sorting, this implementation shows 42% less dynamic energy for sorting top 16 out of 32. The complexity of the proposed sorting when finding the top N/2 out of N is described as follows:

$$(N-1) + \frac{N}{2} \times \log_2 N \tag{2.12}$$

After pruning, selected subband samples are log-domain quantized with leading-one detector, implemented with round approximation.

Figure 2.12: Operation principle of ping-pong streaming Flash.

#### 2.3 8Mb Embedded Streaming NOR Flash

One key requirement to realize a miniature audio sensor node is embedded nonvolatile memory for compact and retentive storage of sensed audio data. Non-volatile storage retains the data even during power source outage. Also, it allows near-zero retentive power during the standby mode, and thus lengthens the lifetime of a sensor node. In general, however, typical NOR Flash memory consumes mW-level of power for program and erase, preventing its usage as an embedded storage for sensor applications. To address this issue, [41] proposed ultra-low power 1Mb NOR Flash design. They increased the efficiency of high voltage generation, which is often a power bottleneck during program, by using a combined Dickson and Cockcroft-Walton charge pump with MIM capacitors. In addition, they employed separate power gating for each bank so that the peripheral circuits of the banks that are not used can be powergated. With other low power circuit techniques, their Flash design consumes  $\mu$ W-level power consumption for program, read, and erase operations.

In this work, we design a custom 8Mb NOR Flash chip following all the strategies in [41]. As the capacity and size of Flash macro increase, one distinctive feature is proposed and designed in this work, since the instantaneous power for program exceeds the allowed budget of sensor system. Although the compressed audio data rate in Section 2.2 is <7kbps in average (measured results are shown in Section 2.4), the streaming format requires 32kbps burst data rate since the compression algorithm operates over multiple sub-frames. To meet this program speed, the 8Mb Flash chip should consume more than twice of power compared with 1Mb macro in [41]. To solve this issue, we design a streaming Flash with ping-pong SRAM buffers as shown in Figure 2.12. Since the SRAM write power is much less than the Flash, we buffer the incoming stream into the SRAM first with higher write speed. Two SRAM macros act as ping-pong buffers: one macro filled with audio streaming; the other being transferred to Flash. In this way, we can keep the Flash program cycle time longer than requirement to reduce instantaneous power consumption. The Flash controller automatically handles seamless ping-pong streaming.

Figure 2.13: Chip die photo of (a) audio processing chip and (b) 8Mb NOR Flash chip.

## 2.4 Measurement Results

The proposed audio processing chip is fabricated in 180nm CMOS with an active area of 7.125mm<sup>2</sup>, and the die photo of it is shown in 2.13a. Measured A-weighted input referred noise of amplifiers is  $13.2\mu V_{rms}$  (Figure 2.4), translates to 61dBA of SNR at 94dBSPL (1kHz) input sound. We also performed acoustic testing as shown in Figure 2.14a. The audio chip is integrated with a MEMS microphone on the chipon-board (COB) setting, and placed inside anechoic chamber to measure acoustic performance accurately without ambient sound noise. Playing a tone sound using a speaker and measure its sound pressure level (SPL) by a reference microphone. In this acoustic testing, the analog front-end consists of MEMS microphone, charge pump, LNA and PGA. The overall analog chain achieves  $32\mu V_{rms}$  A-weighted input referred noise while consuming  $3.15\mu$ W of power. The SNR and sensitivity are 54.6dBA and  $-14\sim13.6$ dBV, respectively, with 94dBA SPL input sound at 1kHz. Figure 2.14b shows the power spectral density (PSD) of this analog front-end.

Measured compression rate depends on the signal sparsity. Figure 2.15 shows the

Figure 2.14: (a) Acoustic measurement setup (b) power spectral density (PSD) of AFE.

| Table 2.4: Measurement Results of Compression Ratio |                      |               |  |  |  |  |  |

|-----------------------------------------------------|----------------------|---------------|--|--|--|--|--|

| Compressed Data Rate Compression Rat                |                      |               |  |  |  |  |  |

| Tone                                                | $2.69 \mathrm{kbps}$ | $23.8 \times$ |  |  |  |  |  |

| Slow speech                                         | $3.56 \mathrm{kbps}$ | $17.9 \times$ |  |  |  |  |  |

| Normal speech                                       | $4.37 \mathrm{kbps}$ | $14.6 \times$ |  |  |  |  |  |

| Music                                               | $6.71 \mathrm{kbps}$ | 9.5 	imes     |  |  |  |  |  |

time domain plots of compressed and original audio clips. Figure 2.15a represents normal speed of speech case, and Figure 2.15b shows slow speech case for same sentence. We can observe that the compressed signal samples are highly suppressed in quiet region since they are below the power threshold. For a normal speech, measured average compression ratio is  $14.6\times$ . On the other hand the compression ratio is  $18\times$  for a slow speech, as expected. Table 2.4 summarizes the compression ratio for various sound types, and it varies automatically depending on the signal sparsity. For the normal human speech, the audio processing chip provides  $\sim 15\times$  compression, enabling >30 mins of recording with 8Mb custom Flash.

Compression rate and quality trade-off can be tuned by the number N and the power threshold. In Figure 2.16, the x-axis is the power threshold, the value below which subbands are pruned for compression. A higher threshold means more aggres-

Figure 2.15: Time domain signals for compressed and origial audio clip at (a) normal speed speech and (b) slow speed speech.

Figure 2.16: Measured compression ratio vs. sound quality trade-off.

sive compression. The y-axis on the left is the compression ratio, and the y-axis on the right is sound quality: A higher value indicates the better quality. The number N is the maximum number of remaining subbands after pruning, and we are using N=16 case for this measurement. As the power threshold is decreased, audio quality improves, but compression rate also decreases as expected. However, when the power threshold goes too low, noise gets to be included in compression, and degrades the audio quality.

The audio processing IC consumes  $4.73\mu$ W of power, dictated by continuous run for ~14 hours under  $64\mu$ Wh millimeter-scale battery. Figure 2.17a shows the power breakdown of the audio processing IC. The compression engine dissipates  $1.44\mu$ W of power, and its power breakdown is shown in Figure 2.17b. As shown in the Figure, polyphase subband filtering (pre-processing + FFT) consumes 74% of total compression engine power even after all of optimizations from both algorithm and architecture due to the high amount of data to process and the required throughput. Table 2.5 summarizes the proposed audio processing IC.

The proposed custom 8Mb embedded Flash is fabricated in 90nm ESF3 NOR Flash technology. Due to its increased capacity, program power becomes double

Figure 2.17: Measured power breakdown of (a) audio IC and (b) compression engine.

| Table 2.5: Summary of Audio Processing IC |                                 |  |  |  |  |

|-------------------------------------------|---------------------------------|--|--|--|--|

|                                           | This Work                       |  |  |  |  |

| Technology                                | 180nm                           |  |  |  |  |

| Die area                                  | $2.5 \times 2.85 \mathrm{mm}^2$ |  |  |  |  |

| Supply voltage                            | 0.6/1.2/3.6V                    |  |  |  |  |

| Amplifiers gain                           | 20-48dB                         |  |  |  |  |

| AFE bandwidth                             | 4kHz                            |  |  |  |  |

| AFE input referred noise                  | $32\mu V_{rms}$ (A-weighted)    |  |  |  |  |

| AFE SNR                                   | 54.6 dBA @ 1Pa                  |  |  |  |  |

| Clock frequency                           | $8/16/150 \mathrm{kHz}$         |  |  |  |  |

| Compression ratio                         | $4-32 \times$ (auto-variable)   |  |  |  |  |

| Power                                     | $4.73 \mu W$                    |  |  |  |  |

| Table 2.6: Comparison of Embedded Flash ICs |                                             |                     |                       |                        |                              |  |  |

|---------------------------------------------|---------------------------------------------|---------------------|-----------------------|------------------------|------------------------------|--|--|

|                                             | This Work                                   |                     | [41]                  | [45]                   | [46]                         |  |  |

| Technology                                  | 90nm ESF3                                   |                     | 90nm ESF3             | 90nm MONOS             | $130 \mathrm{nm}$ SONOS      |  |  |

| Capacity                                    | 8Mb                                         |                     | 1Mb                   | 1Mb                    | $1024 \times 260 \mathrm{b}$ |  |  |

| Area $(mm^2)$                               | 7.5                                         |                     | 0.73                  | 2.26                   | 0.85                         |  |  |

| Prog. throughput                            | $730 \mathrm{kbps}$                         | $7.2 \mathrm{kbps}$ | $800 \mathrm{kbps}$   | $341 \mathrm{kbps}$    | $1 \mathrm{Mbps}$            |  |  |

| Prog. power                                 | $80\mu W$                                   | $38 \mu W$          | $39 \mu W$            | $323\mu W$             | $125 \mu W$                  |  |  |

| Prog. energy                                | $110 \mathrm{pJ/bit}$ $656 \mathrm{pJ/bit}$ |                     | $49 \mathrm{pJ/bit}$  | $946 \mathrm{pJ/bit}$  | $122 \mathrm{pJ/bit}$        |  |  |

| Read power                                  | $28 \mu W$                                  |                     | $25 \mu W$            | N/A                    | $176 \mu W$                  |  |  |

| Read energy                                 | 3.5p.                                       | J/bit               | $3.1 \mathrm{pJ/bit}$ | N/A                    | $1.2 \mathrm{pJ/bit}$        |  |  |

| Erase power                                 | $13 \mu W$                                  |                     | $15 \mu W$            | N/A                    | N/A                          |  |  |

| Erase energy                                | $3.3 \mathrm{pJ/bit}$                       |                     | $9.4 \mathrm{pJ/bit}$ | $1.07 \mathrm{nJ/bit}$ | $29 \mathrm{pJ/bit}$         |  |  |

| Standby power                               | 7.8                                         | $\mu \mathrm{W}$    | $5.4 \mu W$           | N/A                    | N/A                          |  |  |

than [41] when it uses similar program throughput. However, thanks to the pingpong streaming technique, we can tune down the program speed to 7.2kbps, reducing the program power by 2.1×. We achieve  $38\mu$ W of program power which is the lowest, compared with prior works for custom embedded Flash as shown in Table 2.6. Moreover, 8Mb of large capacity enables >30 mins of continuous audio streaming when combined with the proposed compression engine. Read and erase consumes  $28\mu$ W and  $13\mu$ W of power, respectively, also meeting the peak power budget of millimeter-scale energy sources.

Table 2.6: Comparison of Embedded Flash ICs

## CHAPTER III

# A Picowatt Standby Power Neural Network Processor With Custom ISA and 7T SRAM for Sensor Applications

## 3.1 Introduction

Wireless sensor node enables remote retrieving of video and audio streams, images, and scalar sensor data such as temperature, pressure or humidity. To be benefit from massively distributed sensor nodes, the size reduction of each sensor device is paramount. Minuscule size makes the sensors as easy-to-deploy and unobtrusive as possible, minimizing the disturbance to human activity. Continued advance of integrated circuits and technologies have enabled millimeter-scale sensing nodes [1,3, 7,47], paving the way to ubiquitous wireless sensor applications.

As machine learning (ML) techniques such as neural network (NN) have been rapidly proliferated, having built-in NN processing capability on sensor becomes a highly desirable feature to implement efficient large-scale sensor network, alleviating bandwidth, latency, security and communication energy limitations [48, 49]. While the NN workloads require intensive computation and large memory footprint, the sensor node design is heavily constrained by its small form factor, energy, and storage. The software implementation of NN processing on the general-purpose microprocessor typically equipped with sensor nodes lacks energy and memory efficiency, failing to meet the stringent constraints of millimeter-scale node. As a complement, many of prior works have sought to realize dedicated NN accelerators for embedded platforms [50–53]. However, they mainly aimed at convolutional neural networks (CNNs) or large, deep-layered neural networks (DNNs) that can be regard as too excessive capacity for sensing applications [54], and thus their designs rather cause inefficiencies such as low utilization of resources and leakage dominance in the cases where moderately-sized network model is sufficient. Moreover, since prior accelerator designs trade flexibility for efficiency, they can not support not only arbitrary NN topology, but also arbitrary algorithms (e.q., moving average, normalization, sorting, etc.).

In this Chapter, we explore a compact and programmable NN processor to support small-to-medium size models under highly resource-constrained sensor platform. Several prior works optimized for modest NN workloads have been reported in [55–57, 61, 73]. Unlike these works, we consider standby power as the primary design metric since this is of particular importance in a typical wireless sensor node that stays at standby mode a vast majority of time as the event of interest occurs infrequently. As shown in the Figure 3.1a, when the sensor node spends an extended period of time at standby mode, the average power consumption of a sensor node is governed by the processor's standby power. Once the processor is initially programmed using on-chip memory, it is necessary to retain the instructions and data (i.e. NN parameters) during the standby mode to avoid off-chip memory access at every wakeup. The low standby power is also beneficial in always-on sensor, which is the case in Figure 3.1b. Since a typical sensor collects data stream for a long interval to make an input vector to NN (i.e. a frame), the processor computes NN workloads at minimum energy point (MEP) quickly, and then returns to standby mode waiting for next input vector. If the frame length is long enough and the required NN

Figure 3.1: The power profile and average power consumption of NN processor in (a) duty-cycled operation and (b) always-on operation.

workload is low-to-moderate, then again the standby mode might contribute more energy [58].

We have developed a programmable NN processor with 440pW of standby power to support small-to-medium NN workloads in the sensor nodes. To reduce the standby power consumption, we exploit a custom instruction set architecture (ISA) for high code density and sufficient flexibility, a lightweight SIMD microarchitecture, and an ultra-low leakage SRAM bitcell. Finally, we have embedded the processor into a single chip integrated sensor system for acoustic object detection to validate the efficacy of the on-sensor NN processor.

The remainder of this Chapter is organized as follows. Section 3.2 introduces the on-sensor NN processor with custom ISA, microarchitecture, and memory cell. Section 3.3 describes the integrated sensor system on chip for acoustic object detection. Section 3.4 discusses the measurement results.

## 3.2 On-Sensor Neural Network Processor

#### 3.2.1 Custom Instruction Set Architecture

The design of a NN processor ISA must consider a few characteristics particularly for modest workloads in highly resource-constrained sensor environment. Since the data retention of on-chip storage dominates overall power consumption at standby mode, the program code size should be compact enough to enable minimal sized memory, and thus minimum data retention power in the processor. At the same time, the ISA must also maintain sufficient flexibility to realize a variety of network model structures/sizes, and additional general-purpose programs as needed. The CISCtype ISA generally provides high code density, resulting in succinct programs to be stored. However, it requires more complex hardware implementations and prevents fine-grained management of hardware resources by programmer, often failing to meet

| Instruction            | Assembly Format                           | Description                                 |

|------------------------|-------------------------------------------|---------------------------------------------|

| Load                   | LD regID,\$dst,len,\$src                  | load data from memory to register           |

| Store                  | ST regID,\$src,len,\$dst                  | store data from register to memory          |

| Vector Add             | VADD srcID,len,\$src or #imm              | (vector) + (vector/scalar/immediate)        |

| Vector Subtract        | VSUB srcID,len,\$src or #imm              | (vector) - (vector/scalar/immediate)        |

| Vector Multiply        | VMLT srcID,len,\$src or #imm              | $(vector) \times (vector/scalar/immediate)$ |

| Scalar Add             | SADD srcID,\$src or #imm                  | (scalar) + (scalar/immediate)               |

| Scalar Subtract        | SSUB srcID,\$src or #imm                  | (scalar) - (scalar/immediate)               |

| Scalar Multiply        | SMLT srcID,\$src or #imm                  | $(scalar) \times (scalar/immediate)$        |

| Matrix-Vector Multiply | MMLT iLen,oLen,shb,shl or shr,\$src,\$dst | $(matrix) \times (vector)$ with shifting    |

| PWL Approximate        | PL regID,\$src1,len,\$src2,plshb          | non-linear functions on register            |

| Element-wise Compute   | EC funcID,len,\$dst                       | element-wise functions on vector register   |

| Conditional Branch     | CBR \$src,#imm,jumpAddr                   | jump when (reg[\$src]==#imm)                |

| Direct Jump            | JMP jumpAddr                              | direct PC jump to jumpAddr                  |

| No Operation           | NOP cycles                                | pipeline stall for cycles of clock cycles   |

Table 3.1: Instruction Set of On-Sensor NN Processor

stringent power budget. On the other hand, while the RISC-style ISA allows simpler microarchitectures, it consumes more on-chip storage for the same program than CISC approach. Moreover, atomic primitive instructions put more burden on fetch, decode, and rename stages than the computation itself, causing energy inefficiency [59], and this is exacerbated in the case where small footprint of network models are deployed. Therefore, the ISA design should try to keep a balance between both approaches by enabling small number of code lines and low power hardware implementations, simultaneously. Finally, some degree of SIMD data-level parallelism should also be exploited to make the NN computation more efficient.

Taking account of aforementioned characteristics, we define a set of instructions for a programmable NN processor for various sensor applications, and provide the list and assembly format along with their description in Table 3.1. The symbol \$ denotes register and memory addressing, and the symbol # denotes the immediate constant. The instructions consist of fixed 32-bit width: 6 bits for opcode (redundant bits are reserved for instruction extension) and the remaining 26 bits for different fields per instruction. The ISA supports separate scalar and vector register files (RF) which can be shared as either general-purpose registers or NN buffers within the same program, saving the total number of registers. The ISA design also includes on-chip scratchpad memory to store all the data used by NN models. Since NN techniques often require variable-length, contiguous vector or matrix data, the exposure of scratchpad memory to the programmer allows high flexibility for efficient data management. Although the idea of scratchpad memory is similar to [60], their ISA design doesn't support vector RF at the same time and thus, cannot exploit any data reuse opportunities. The vector RF combined with scratchpad memory provides stationary input vector reuse and flexible-width of matrix data access, simultaneously. The ISA is based on a load-store architecture in which the on-chip scratchpad memory access occurs with load (LD) and store (ST) instructions. Since the ISA supports both scalar and vector registers, regID specifies the type of register. The variable-length of data access for vector or matrix can be controlled by len field.

The arithmetic instructions can be used for program control flow, simple algorithm realization, and vector-wise processing. The scalar instructions (SADD, SSUB, SMLT) operate on scalar registers or immediate value in the instructions. The first operand and destination are implicitly fixed to a same register (sreg[\$0]) to reduce hardware complexity and to shorten the length of instructions. Whether to use a value in scalar register or immediate constant as the second operand is determined by the srcID field. The vector arithmetic instructions (VADD, VSUB, VMLT) perform vector addition, vector subtraction, and element-wise vector product when the memory is specified as an source operand. The instructions take the first vector operand always from the vector RF, and take the second vector operand from the memory. When the second operand is specified as scalar register or immediate, then the instructions perform vector-scalar arithmetic.

Many of ML and NN techniques are composed mainly of matrix-vector multiplication. However, as more complex and computationally demanding algorithms have been emerged, most prior works implemented high dimensional operation primitives such as matrix-matrix multiplication, convolutional kernels, etc. Involving such complex primitives yet gives poor utilization efficiency especially when un-

| Program 1. RNN                 |                             |  |  |  |  |

|--------------------------------|-----------------------------|--|--|--|--|

| LD vreg,\$0,16,\$in            | %load input                 |  |  |  |  |

| MMLT 16,16,2,shl,\$w1.ff,\$out | %feed-forward path          |  |  |  |  |

| LD vreg,\$0,16,\$prev.hidden   | %load previous hidden layer |  |  |  |  |

| VMLT mem,16,\$w1.fb            | %feed-back path             |  |  |  |  |

| VADD mem,16,\$out              | %sum ff and fb              |  |  |  |  |

| VADD mem,16,\$b1               | %add bias                   |  |  |  |  |

| PL vreg,\$0,16,\$tanh,11       | %tanh activation            |  |  |  |  |

| ST vreg,\$0,16,\$prev.hidden   | %save current hidden layer  |  |  |  |  |

| MMLT 16,16,2,shl,\$w2.ff,\$out | %output path                |  |  |  |  |

| LD vreg,\$0,16,\$out           | %load output                |  |  |  |  |

| VADD mem,16,\$b2               | %add bias                   |  |  |  |  |

| PL vreg,\$0,16,\$tanh,11       | %tanh activation            |  |  |  |  |

| ST vreg, \$0, 16, \$out        | %save current output        |  |  |  |  |