# **Enabling Hyperscale Web Services**

### by

### Akshitha Sriraman

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2021

#### **Doctoral Committee:**

Professor Thomas F. Wenisch, Chair Professor David Brooks, Harvard University Assistant Professor Jean-Baptiste Jeannin Assistant Professor Baris Kasikci Professor Margo I. Seltzer, University of British Columbia

## Akshitha Sriraman

akshitha@umich.edu

ORCID iD: 0000-0003-4780-9483

© Akshitha Sriraman 2021

| To the ones who raised me to believe that anything is possible, Sriraman and Rajalakshmi. |

|-------------------------------------------------------------------------------------------|

| To the one who made many things possible, Akshay.                                         |

| A 1, 1 1 1 1 1 11 A 1,                                                                    |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

| And to the one who makes everything possible, Amrit.                                      |

#### ACKNOWLEDGEMENTS

My Ph.D. experience was a roller coaster: ups and downs, twists and turns. But boy, was it a ride! For all the marvelous times when I built large systems that somehow just worked, had papers accepted, and won fellowships, there were just as many, if not more, challenging times when I built large systems that somehow just *didn't* work, floundered with no clue about what I was doing, and struggled with imposter syndrome. I express my deepest gratitude to the village of phenomenal people who made the challenging times conquerable and the marvelous memorable, *enabling a Ph.D.* that I didn't think would happen.

**AMMA & APPA.** Starting with the people who have *always* been there, I thank my parents, my Amma and Appa, **Rajalakshmi Sriraman** and **P.R. Sriraman**. Rather, I will *attempt* to thank them, because I know that words will always fall short in this case.

My father aspired to be an electrical engineer, but his chance of realizing his dreams perished when he lost his father at a young age. I thank you, Appa, for teaching me the gratification of sincere efforts—you never gave up, endured a job that kept you far from home, and pursued an advanced degree well into adulthood. Learning to persevere like you

has helped me come a long way. Appa, I thank you for the seemingly small things that made the biggest difference—for setting alarms to wake up at odd hours to then wake *me* up with a coffee in hand before my deadlines, for staying up on Skype for hours on end to "keep me company" when I was working and was feeling homesick, for always reading every word I write, and for texting me *every single day* to tell me you love me. Thank you for your value of education and for always encouraging me to push boundaries. Because of you, I have become the person I always dreamed of being. I hope that makes you proud. I thank you for being my inspiration—wanting to make you proud is the fire that fuels me to revive the dreams you once dreamed, by living them. *Appa, this Ph.D. is for you*.

As my first teacher, I thank you, Amma, for instilling in me from an early age the idea that anything is possible, any dream attainable. Today, several of my dreams have come true. And I want you to know that it is because of you. I thank you for believing in me even at times when I did not believe in myself. I will forever be indebted to you for all that I am today. You told me that you do not understand the meaning behind several technical details in my dissertation. While that may be true, I want you to know that this dissertation is meaningless without you. And for this reason, Amma, I dedicate this dissertation to you.

**AKSHAY SRIRAMAN.** I thank the best brother I could ask for, Akshay Sriraman. In the past, when I had trouble figuring out who I wanted to be, I simply followed Akshay without question. I followed him when I decided to pursue engineering and I followed him again when I decided to study electronics. I knew that if I did what he did, I would do great.

I thank Akshay for putting me before himself *so* many times. He sacrificed his goals of getting a Master's degree because he knew that I wanted to pursue one. So, instead, he took up a job to monetarily back my (extremely expensive) Master's education at UPenn<sup>1</sup>. These sacrifices, like a skyscraper's foundation, are the kinds of things that seemingly go unseen, but actually form the very cornerstone of a person's achievements. I don't think I

<sup>&</sup>lt;sup>1</sup>As the picture suggests, Akshay did eventually get a Master's degree, also from the University of Pennsylvania. So, perhaps, *he* followed *me* this time around?

would be writing this dissertation if not for him. How else could I have traveled to the US? Pursued further education? Received my first exposure to research and decided on a Ph.D.? Recognized that my dream is to become a professor? And later go on to achieve that dream? I start at Carnegie Mellon University in January 2022, and I am forever indebted to Akshay for enabling the cascading set of events that brought me to this point.

UPenn, who started it all. Joe took me on when *nobody* would have given me a second glance, and also despite me not doing great in his course<sup>2</sup>. I thank him for believing that I could do research; his belief made a world of difference. I recall telling him he was making a mistake—although I wanted to try doing research, I didn't think I could. He said that I was hard working, motivated, and passionate, and those are the only things I would need. Thank you, Joe, for showing me what *truly* matters—every time I felt overwhelmed due to my lack of prior CS education, your words kept me going. Your faith in me made me push myself harder every day—I didn't want you to be wrong and I just didn't want to let you down.

When I struggled with visualizing software, Joe pointed out how I could use my strength of networking with people to learn from others about how *they* might build the software I was working on. Joe, Chapter III of this dissertation, my biggest software effort, is for you. Thank you for identifying my strengths; knowing, and using them to my advantage has made me come a long way. But most importantly, I thank you for giving meaning to my entire life and career. You are the reason I dreamed of becoming a professor—if I can pass on what you did for me to at least one other student, I shall declare my life *wildly* successful.

**THOMAS WENISCH.** When I moved from Penn to Michigan, I didn't initially work with my Ph.D. advisor, Tom. I thank Tom for taking me on from another lab (resulting in me naming our research group "The Sanctuary Lab"). That single decision changed the entire course of my Ph.D., making it into a more fabulous experience that I ever dreamed possible.

Tom is famous for (amongst other things, e.g., a Maurice Wilkes award) saying the

<sup>&</sup>lt;sup>2</sup>This happened to be a graduate course on *computer architecture*. Ironic, isn't it? Goes to show that grades don't really define the career you can go on to have.

words: "I already have a PhD. I don't have a need to get another PhD via you". Although these words might seem like a joke at first blush, I realize that they summarize how Tom shaped me as a researcher. Tom did everything to make me an independent researcher, so that I could define my Ph.D. in a way that was uniquely me. From guiding me every step of the way when he knew I was utterly lost, to taking a back seat when he knew I was ready, I thank Tom for doing it all in the most beautiful way imaginable.

Tom knows me as a researcher even better than I know myself. He encouraged me to independently see a project through and write a paper about it (see Chapter VI); "We are taking the training wheels off," he said. Although I felt unprepared initially, I emerged much more confident in my abilities and much closer towards winning my battle against imposter syndrome. I will always maintain that "Tom knows everything about everything." Tom, I know that if I become at least half as great an advisor as you, I will be *ridiculously* happy.

**DOCTORAL COMMITTEE MEMBERS. Margo Seltzer**, for taking me under her wing and being such a fabulous role model to me. Having Margo as my mentor exemplifies the notion that sometimes the most incredible things in life happen by accident. She leads by example and has always gone above and beyond whenever I needed help, be it technical, professional, or personal. I thank Margo for reading every single word of this dissertation and I thank her for always accepting nothing less than my absolute best. I am incredibly lucky to have Margo as my mentor. *Everyone needs a Margo in their life*.

Baris Kasikci, for being such a constant pillar of support. The past couple of years

of working with Baris and EFES Lab members have truly helped me grow and thrive as a researcher. I am so grateful to Baris for everything he does: from letting me know whether an email draft looks okay, to helping me with the job search process, Baris has been there for it all. I thank him for being the perfect mix of a mentor who is also a friend.

**David Brooks**, for giving an opportunity to mentor Ph.D. students when I was a Ph.D. student myself. And **Jean-Baptiste Jeannin**, for the valuable feedback on my work.

MENTORS and COLLABORATORS. I thank Sarita Adve for being my biggest role model. I thank her for leading by example in teaching me how to be a tough cookie at times when I encounter bias. I am grateful to **Peter Chen** for always insisting that I think about a research problem from first principles and **Christos Kozyrakis** for teaching me how to write grant proposals. I thank all three of them for helping me land my dream job.

I thank **Reetu Das** for reaching out to me at a time when I was thinking about quitting the Ph.D. program, for her kindness, and for our "lunch dates" every semester. I thank **Kim Hazelwood** for recruiting me for a Facebook internship that opened a world of research possibilities, and for helping me land my dream job. When I was concerned about how my research approach didn't always fit the mould (e.g., introducing humour, or rather my version of humour, in my talks), Kim told me something that I will always remember: "*You are a unicorn. Don't let people chop off your horn and convert you into yet another sheep.*"

I am grateful to **Abhishek Dhanotia**, my Facebook internship mentor, for his research advice during multiple Facebook internships. I thank him for showing me how much fun research can be when one is not constantly worrying about the next paper deadline. My time at Facebook was always intellectually enriching because of stimulating conversations with so many people who were merely a ping away. I especially thank **Vijay Balakrishnan**, **Carlos Torres**, **Pallab Bhattacharya**, **Hsien-Hsin Lee**, **Carole-Jean Wu**, **Xiaodong Wang**, **Jonathan Haslam**, **Denis Sheahan**, **Jay Kamat**, and **Shobhit Kanaujia** for helping me understand production systems. I thank Facebook for granting me access to real-world data centers, significantly enhancing my dissertation's contributions. I also thank Facebook for

the free food during my internships (especially for the best boba and ramen I've ever had)!

I thank **Ed Nightingale** and **Galen Hunt**, my MSR internship mentors, for teaching me to never take no for an answer because there will always be a workaround if I looked hard enough. I am grateful to many MSR researchers who helped me create a concrete research vision at a time when I was floundering. I especially thank **Ricardo Bianchini** for helping me realize  $\mu$ Tune; "The moment you have an inflection point, you have a story," he said.

**Gilles Pokam** and **Rajeev Alur**, for helping me get into one of the best Ph.D. programs. **Rajagopalan Nadathur**, without whom I couldn't have moved to the US and started at Penn. **James Mickens**, **Abhishek Bhattacherjee**, **Brandon Reagen**, and my **WICArch** friends for all their advice. In loving memory of my English teacher, **Ms. Stephens**, without whom I couldn't have authored my papers. I wish I could share them with her.

SANCTUARY LAB. A huge shout-out to Aasheesh Kolli and Neha Agarwal for always encouraging me. I thank Amlan Nayak, Brendan West, Hossein Golestani, Harini Muthukrishnan, Steve Zekeny, Ofir Weisse, and Amir Mirhosseini for all the technical discussions, but more importantly, for being my partners in crime when pulling unicorn-themed pranks on Tom. (Remember the time we TP'd Tom's office with prancing unicorn-themed toilet paper?) All of you made graduate school memorable and fun.

But, this Ph.D. wouldn't have happened without **Vaibhav Gogte**. From teaching me how to write code (yes, that indeed happened since I entered a Ph.D. program in *CS* without prior programming education—smh), to spending long hours entertaining my (half-baked) ideas, Vaibhav has been my greatest source of inspiration. I thank him for being my go-to (inside joke: more like "gogo") person for *everything*. Vaibhav exemplified an ideal Ph.D. student by living his own quote: "*Your Ph.D. is just another job. It is not a higher calling*." His words stuck with me and made graduate school so much more than just about publishing papers. I thank him for making graduate school the most valuable experience of my life.

EFES LAB. A huge shout-out to Tanvir Khan, Kevin Loughlin, Andrew Quinn, Marina Minkin, Sara Shahri, Ian Neal, Jiacheng Ma, and Gefei Zuo—for tirelessly attend-

ing my many (bad) practice talks. I thank them for making me one of their own and for being my new research home. I thank Tanvir for making me look forward to being a professor.

MICHIGAN CSE. I thank Manos Kapritsos for caring so deeply about every student. Mahdi Cheraghchi, Mark Guzdial, John Laird, and Emily Provost, for helping me at key phases. And Karen Liska, Ashley Andrea, Stephen Reger, Jamie Goldsmith, Laura Fink, Sylvia Galaty, Cindy Estell, and Erika Hauff, for being CSE's true heroes.

**GRANTS.** My work was supported by (1) the Center for Applications Driving Architectures (ADA), one of six centers of JUMP, a Semiconductor Research Corporation program co-sponsored by DARPA and (2) NSF Grant IIS1539011 and gifts from Intel. I also thank Facebook for a fellowship that allowed me to freely explore new research directions.

**FRIENDS.** I thank my best friend, **Amritha Varshini**, for being the sister I never had.

Thank you for always having my back. Thank you for being the loving, encouraging, and nonjudgemental person that you are, all wrapped into one small, amazing package. When I started at Penn, I had no idea that I would come away with the greatest gift of my life.

A big shout-out to the Juwaris group—Kumar Aanjaneya, Aditi Kulkarni, Sneha Joshi, Shriya Sethuraman, Poorwa Shekhar, Ripudaman Singh, Niket Prakash, Harshad Dharmatti, Kunal Garg, Saurabh Mahajan, Bharadwaj Mantha, and Keval Ramani—for the boisterous board game nights that helped me stay sane during the dark times. Meeting Zahra Tarkhani at MSR made me realize that soulmates are real—our similarities are too strong to be a coincidence; but, perhaps, building a bare-metal hypervisor from scratch, together, does that to you? Thank you, Zahra, for the laughs and the crazy, impromptu drives. I thank Nilmini Abeyratne, Sai Gouravajhala, Amir Rahmati, and Earlence Fernandes for helping me move to Sanctuary Lab. Animesh Jain, for the walk

along the Sammamish river, where  $\mu$ Tune took a concrete form for the first time. **Vidushi Goyal**, for all our "discussions" over chai. **Caroline Trippel**, for being such a trailblazer and passing on advice on how to become one. **Tumpa Chakraborty**, for all her support.

**RELATIVES.** In loving memory of my grandpa, **Thathappa**, who was the first person to tell me that I should do a Ph.D., introducing the word to me. I miss you, Thathappa, and I wish I could share this dissertation with you. I thank my grandma, **Momma**, for being the sweetest person I've ever met. In loving memory of my grandma, **Radha paatti**. I hope she would be proud. I never got to meet my grandpa, but I hope he would be proud too. I thank my extended parents, **Anandhi** and **Gopal**, for all their love and for always being there; they are my life's most beautiful gifts. I thank **Shruthi** and **Abhinaya** for their love.

When I first moved to the US, I was terribly homesick and wanted to move back to India in a grand total of three days. I thank **Ranga uncle**, **Anu aunty**, **Sumun**, **Pranav**, and **Leo** for everything they did to make Philly my home away from home. I am also very grateful to **Krishnan uncle** and **Shankar uncle** for helping me navigate the US academic system.

**PO GOPAL.** I thank Po, my oh-so-adorable puppy. Po is my lucky charm: my dissertation work took off only after he entered my life. Po sat with me (more like slept near me) through every deadline and was my rubber duck (dog, rather) for debugging. Thank you, Po, for being fluffy, for being silly, and for your (literally) warm presence that kept me company.

**AMRIT GOPAL.** Saving the best for last, to my husband, Amrit, a few private words

addressed to you in public. Thank you for your love, patience, and unwavering support

towards my growth—you have always been my rock. From spending numerous hours critiquing my work, to squandering your vacation days traveling to conferences so that you could sit in the front row and record my talk (like some kind of a proud parent), you have done it all. Amrit, you are a true partner, and I feel truly blessed that I get to have you by my side. During the past six years, I felt a lot like I did just the front-end UI development work, when you were the back-end data center holding the fort together.

Amrit, this Ph.D. is as much yours as it is mine.

And finally, Amrit, Amma, and Appa, you know the past few years were not easy:

When I felt so lost, like I'd lost my way,

When I didn't know what to do or say,

When I didn't know if my research was sound,

When I was floundering all around,

When my research vision was rare to see,

When I didn't know what I'd grow to be,

When paper acceptances were rare,

When Reviewer C just didn't care,

When I had no clue and felt very blue,

I knew I could always turn to you.

I knew you'd always be there.

I knew you'd always care.

All I'd do was close my eyes and think of you

And I knew I'd come through.

"The city of Pittsburgh gleaming suddenly before her . . . so startling in its vastness and its beauty that she had gasped and slowed, afraid of losing control of the car."

Kim Edwards

# TABLE OF CONTENTS

| DEDICATION      |                    |                                                                                                | i   |

|-----------------|--------------------|------------------------------------------------------------------------------------------------|-----|

| ACKNOWLED       | GEMENT             | rs                                                                                             | ii  |

| LIST OF FIGURES |                    |                                                                                                |     |

| LIST OF TABL    | ES                 |                                                                                                | XX  |

| ABSTRACT        |                    |                                                                                                | xxi |

| CHAPTER         |                    |                                                                                                |     |

| I. Introd       | luction .          |                                                                                                | 1   |

| 1.1             | Motivatio          | on                                                                                             | 1   |

|                 | 1.1.1              | Web Services Powered by Data Centers are Here, There,                                          |     |

|                 |                    | and Everywhere                                                                                 |     |

|                 | 1.1.2              | Radical Shift in Hyperscale Computing                                                          | 3   |

|                 | 1.1.3              | Decline in Technology Trends that Drive Processor Per-                                         |     |

|                 |                    | formance Scaling                                                                               | 4   |

|                 | 1.1.4              | Consequences on the Software and Hardware Research                                             | _   |

| 1.2             | Dagagala           | Landscape                                                                                      |     |

| 1.2             | 1.2.1              | Challenges and Goals                                                                           | 14  |

|                 | 1.2.1              | Enabling the Study of Modern Web Services Redesigning Software Based on Underlying Data Center | 14  |

|                 | 1.2.2              | Hardware Constraints                                                                           | 16  |

|                 | 1.2.3              | Architecting Commodity Hardware for New Web Ser-                                               | 1(  |

|                 | 1.2.3              | vice Software Paradigms                                                                        | 18  |

|                 | 1.2.4              | Architecting Custom Hardware for New Web Service                                               | 10  |

|                 | 1.2.4              | Software Paradigms                                                                             | 22  |

| 1.3             | Dissertat          | ion Contributions                                                                              |     |

| 1.4             |                    | ion Outline                                                                                    |     |

| 1.7             | <b>D</b> 10001 tat | aon comme                                                                                      |     |

| II A Ren        | chmark S           | uite for Microservices                                                                         | 31  |

|      | 2.1    | Prior Work                                                                                                     | 34 |

|------|--------|----------------------------------------------------------------------------------------------------------------|----|

|      | 2.2    |                                                                                                                | 35 |

|      |        | •                                                                                                              | 36 |

|      |        |                                                                                                                | 40 |

|      |        |                                                                                                                | 43 |

|      |        | <del>_</del>                                                                                                   | 45 |

|      | 2.3    |                                                                                                                | 49 |

|      | 2.4    |                                                                                                                | 51 |

|      | 2.5    | <i>C</i> ;                                                                                                     | 52 |

|      |        |                                                                                                                | 52 |

|      |        | C 1                                                                                                            | 53 |

|      |        | 1 ,                                                                                                            | 54 |

|      | 2.6    |                                                                                                                | 59 |

|      | 2.7    |                                                                                                                | 61 |

|      |        |                                                                                                                | -  |

| III. | Auto-T | uned Software Threading for Microservices                                                                      | 63 |

|      |        |                                                                                                                |    |

|      | 3.1    | Motivation                                                                                                     | 66 |

|      |        |                                                                                                                | 66 |

|      |        | e ·                                                                                                            | 67 |

|      |        |                                                                                                                | 68 |

|      | 3.2    |                                                                                                                | 68 |

|      |        |                                                                                                                | 69 |

|      |        | , and the second se | 71 |

|      |        | , and the second se | 73 |

|      | 3.3    |                                                                                                                | 75 |

|      |        | •                                                                                                              | 76 |

|      |        |                                                                                                                | 76 |

|      | 3.4    | 1                                                                                                              | 78 |

|      | 3.5    | •                                                                                                              | 79 |

|      | 3.6    | Evaluation                                                                                                     | 80 |

|      |        |                                                                                                                | 81 |

|      |        |                                                                                                                | 89 |

|      | 3.7    | <u>.</u>                                                                                                       | 96 |

|      | 3.8    |                                                                                                                | 97 |

|      | 3.9    |                                                                                                                | 98 |

|      | 3.10   | Follow-On Research                                                                                             | 01 |

|      |        | Chapter Summary                                                                                                |    |

|      |        |                                                                                                                |    |

| IV.  | Optimi | zing Commodity Server Architectures for Microservice Diver-                                                    |    |

|      | _      | Hyperscale                                                                                                     | 05 |

|      | •      |                                                                                                                |    |

|      | 4.1    | Understanding Microservice Performance                                                                         | 08 |

|      |        | 4.1.1 The Production Microservices 1                                                                           |    |

|            | 4.1.2                                  | Characterization Approach                            | 110 |

|------------|----------------------------------------|------------------------------------------------------|-----|

|            | 4.1.3                                  | System-Level Characterization                        |     |

|            | 4.1.4                                  | -                                                    |     |

| 4.2        | "Soft" SI                              | KU                                                   | 124 |

| 4.3        | μSKU: S                                | System Design                                        | 126 |

| 4.4        |                                        | logy                                                 |     |

| 4.5        |                                        | on                                                   |     |

|            | 4.5.1                                  | Knob Characterization                                | 131 |

|            | 4.5.2                                  |                                                      |     |

| 4.6        | Discussion                             | on                                                   | 137 |

| 4.7        |                                        | Work                                                 |     |

| 4.8        |                                        | rm Impact Potential                                  |     |

| 4.9        | _                                      | On Research                                          |     |

| 4.10       |                                        | Summary                                              |     |

|            | 1                                      | •                                                    |     |

| V. Redesig | gning Co                               | mmodity Server Architectures for Efficient Event No- |     |

| tificatio  | on at Hyp                              | erscale                                              | 148 |

|            |                                        |                                                      |     |

| 5.1        | •                                      | Widely-Used Notification Paradigms Fall Short?       |     |

|            | 5.1.1                                  | Microservice Requirements                            |     |

|            | 5.1.2                                  | Interrupts                                           |     |

|            | 5.1.3                                  | Spin-polling                                         | 155 |

|            | 5.1.4                                  | MWAIT                                                | 158 |

| 5.2        | The $\mu$ No                           | otify Paradigm                                       | 159 |

|            | 5.2.1                                  | Design Goals                                         | 159 |

|            | 5.2.2                                  | System Model                                         | 160 |

|            | 5.2.3                                  | $\mu$ Notify Overview                                | 161 |

|            | 5.2.4                                  | $\mu$ Notify's Back-end Microarchitecture            | 163 |

|            | 5.2.5                                  | $\mu$ Notify's Front-end Programming Model           | 165 |

| 5.3        | Evaluation                             | on                                                   | 168 |

|            | 5.3.1                                  | Experimental Setup                                   | 168 |

|            | 5.3.2                                  | Microservices                                        | 169 |

|            | 5.3.3                                  | Peak Throughput                                      |     |

|            | 5.3.4                                  | Queue Scalability                                    | 172 |

|            | 5.3.5                                  | Median and Tail Latency                              |     |

|            | 5.3.6                                  | Overheads                                            | 174 |

| 5.4        | Discussion                             | on                                                   | 174 |

| 5.5        | Related V                              | Work                                                 | 175 |

| 5.6        | Chapter S                              | Summary                                              | 176 |

| /I. Unders | standing l                             | Hardware Customization Opportunities at Hyperscale   | 179 |

| I. Chacis  | ······································ | 2 pportunities at hyperscale                         | 11) |

| 6.1        | Understa                               | nding Microservice Overheads                         | 183 |

|            | 6.1.1                                  | The Production Microservices                         |     |

|            |                                        | Characterization Approach                            |     |

|             | 6.1.3     | Leaf Function Characterization                           |

|-------------|-----------|----------------------------------------------------------|

|             | 6.1.4     | Service Functionality Characterization 193               |

| 6.2         | The Acc   | elerometer Model                                         |

|             | 6.2.1     | Acceleration Strategies                                  |

|             | 6.2.2     | System Abstraction                                       |

|             | 6.2.3     | Parameter Definition                                     |

|             | 6.2.4     | Modeling Diverse Threading Designs 199                   |

|             | 6.2.5     | Accelerometer Use Cases                                  |

| 6.3         | Validatin | g the Accelerometer Model                                |

|             | 6.3.1     | Validation Methodology                                   |

|             | 6.3.2     | Experimental Setup                                       |

|             | 6.3.3     | Case Study 1: AES-NI for Cache1 206                      |

|             | 6.3.4     | Case Study 2: Encryption for Cache3 208                  |

|             | 6.3.5     | Case Study 3: Inference for Ads1 209                     |

| 6.4         | Applying  | g the Accelerometer Model                                |

|             | 6.4.1     | Compression                                              |

|             | 6.4.2     | Memory Copy                                              |

|             | 6.4.3     | Memory Allocation                                        |

| 6.5         | Related ' | Work                                                     |

| 6.6         | Long-Te   | rm Impact Potential                                      |

| 6.7         | Chapter   | Summary                                                  |

| VII. Future | e Work an | d Conclusions                                            |

| 7.1         | Future D  | rirections                                               |

|             | 7.1.1     | Enabling Cross-Stack Designs for Emerging Web Ser-       |

|             |           | vice Paradigms and Application Domains                   |

|             | 7.1.2     | Rethinking Hardware-Software Co-Design for System        |

|             |           | Overheads that Arise at Hyperscale                       |

|             | 7.1.3     | Mitigating the Killer Microsecond Problem in Modern      |

|             |           | Web Services                                             |

|             | 7.1.4     | Redesigning Software Stacks for Emerging Hardware        |

|             |           | Accelerators                                             |

|             | 7.1.5     | Designing Systems to Support Emerging Device Tech-       |

|             |           | nologies                                                 |

|             | 7.1.6     | Using Machine Learning to Self-Navigate the Hyper-       |

|             |           | scale Design Space                                       |

|             | 7.1.7     | Designing Energy-Efficient Data Centers                  |

|             | 7.1.8     | Making Intersectionality, Equity, and Fairness as First- |

|             |           | Order System Design Metrics                              |

| 7.2         | Dissertat | tion Conclusions                                         |

| RIRLIOGRAPI | ΗV        |                                                          |

| ~ OIWII I   |           |                                                          |

# LIST OF FIGURES

# Figure

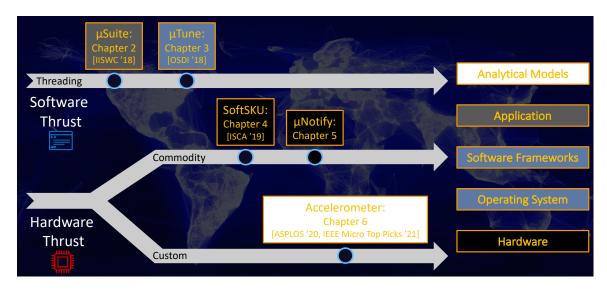

| 1.1  | A timeline of the work presented in this dissertation, organized horizon-<br>tally according to the years when portions of the individual dissertation<br>chapters were published. The timeline is divided into this dissertation's<br>software and hardware thrusts to show a bird's eye view of the software<br>and hardware design space studied in this dissertation. Each work of<br>research is annotated with the dissertation chapter in which it is covered<br>and the publication venue where portions of that chapter were published.<br>The background color of the box representing each work of research is<br>color coordinated with the levels of the systems stack (shown on the right) |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | that the technologies presented in that chapter cover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25 |

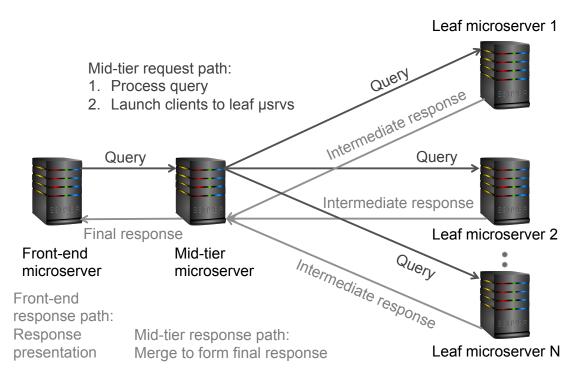

| 2.1  | A typical web application fan-out: Modern web services are composed of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | a complex web of microservices that interact via RPCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

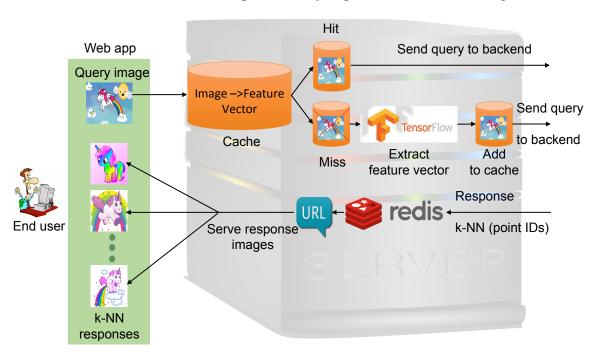

| 2.2  | HDSearch: Front-end presentation microservice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

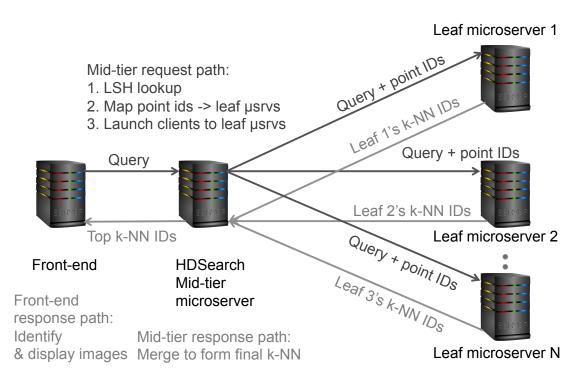

| 2.3  | HDSearch: Back-end request and response pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

| 2.4  | An example of HDSearch's request (left) and 1-NN response (right):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | Response's highlighted circular segment illustrates why the images match.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

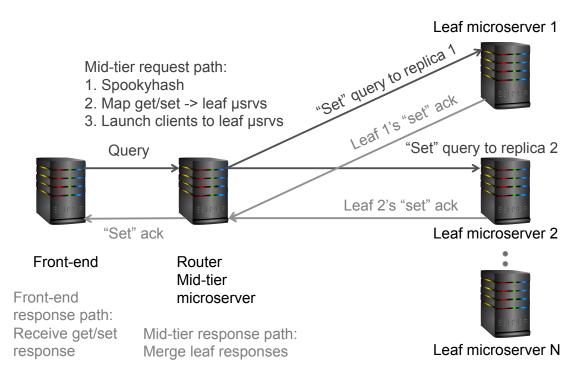

| 2.5  | Router: Back-end request and response pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

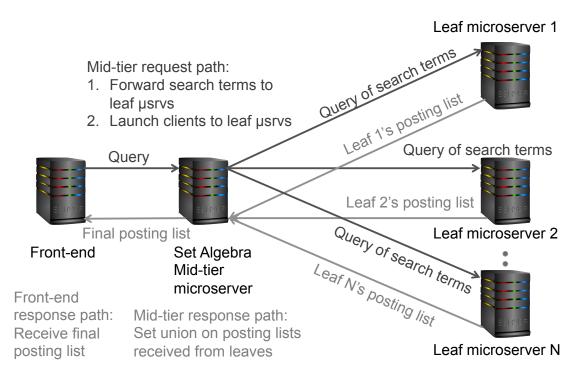

| 2.6  | Set Algebra: Back-end request and response pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

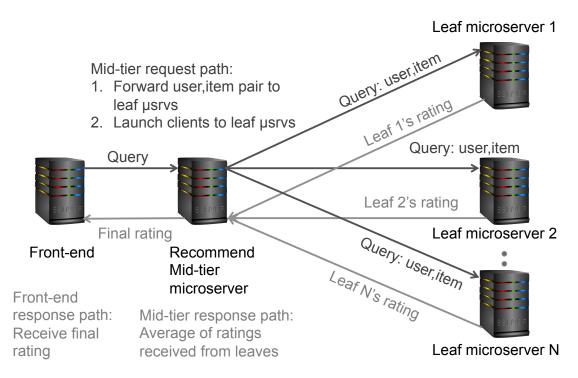

| 2.7  | Recommend: Back-end request and response pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48 |

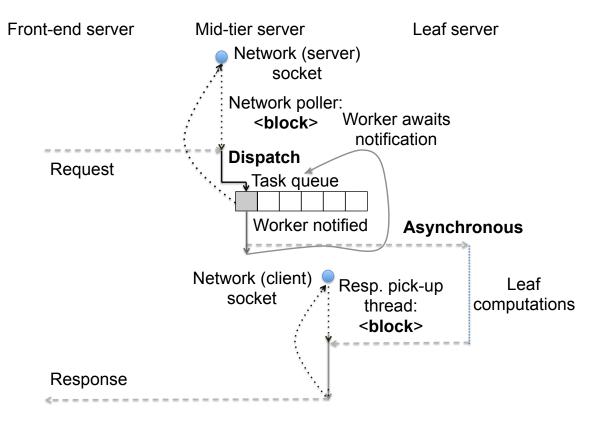

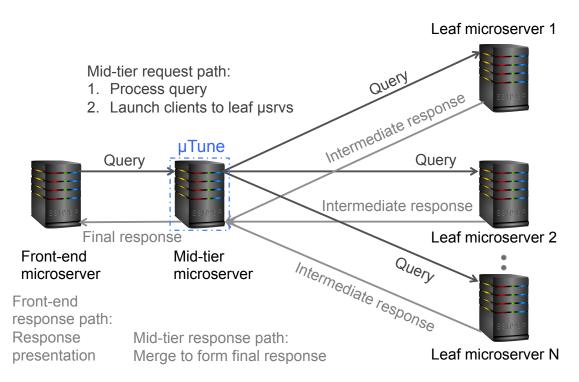

| 2.8  | $\mu$ Suite's mid-tier microservice design: $\mu$ Suite's mid-tier microservices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | block on the front-end network socket, dispatch processing of front-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | requests, and asynchronously communicate with leaf microservices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49 |

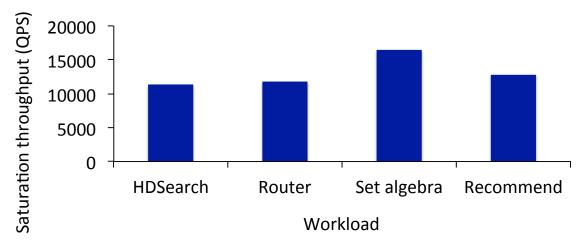

| 2.9  | Saturation throughput (QPS): $\mu$ Suite is similar to real-world web services.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

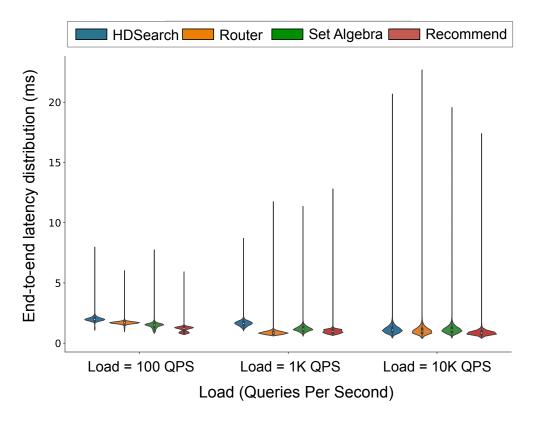

| 2.10 | End-to-end response latency across different loads for each benchmark:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | Median latency is higher at low load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

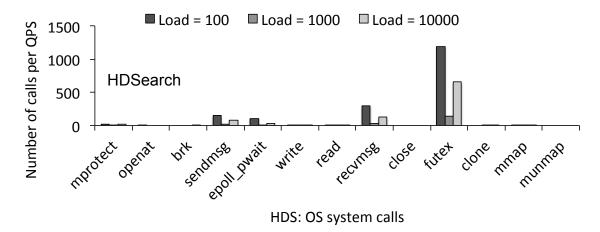

| 2.11 | HDSearch's counts of OS system call invocations per QPS: The futex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | system call is predominantly invoked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |

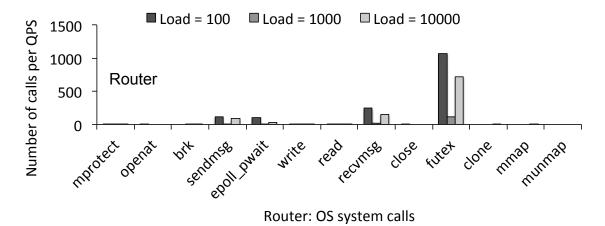

| 2.12 | Router's counts of OS system call invocations per QPS: The futex system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | call is predominantly invoked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55 |

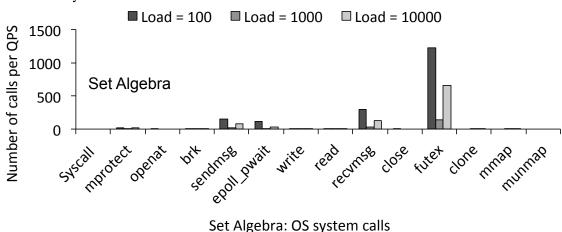

| 2.13 | Set Algebra's counts of OS system call invocations per QPS: The futex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | system call is predominantly invoked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55 |

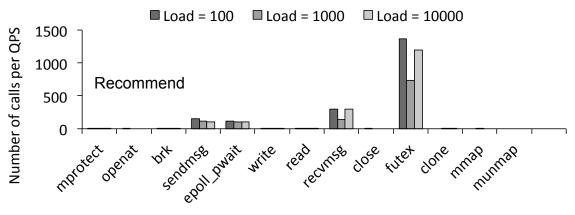

| 2.14 | Recommend's counts of OS system call invocations per QPS: The <i>futex</i>         |     |

|------|------------------------------------------------------------------------------------|-----|

|      | system call is predominantly invoked                                               | 55  |

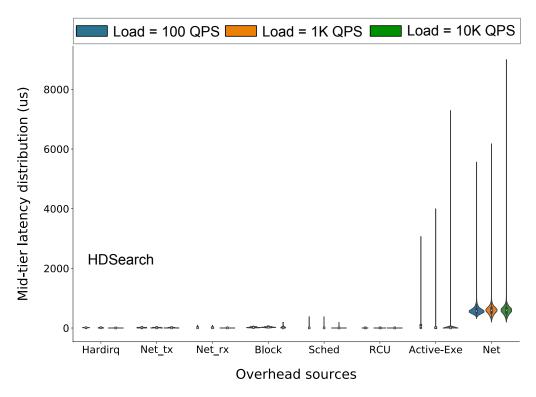

| 2.15 | HDSearch's breakdown of OS overheads: Time to switch a thread from                 |     |

|      | the <i>active</i> to the <i>running</i> state is high                              | 56  |

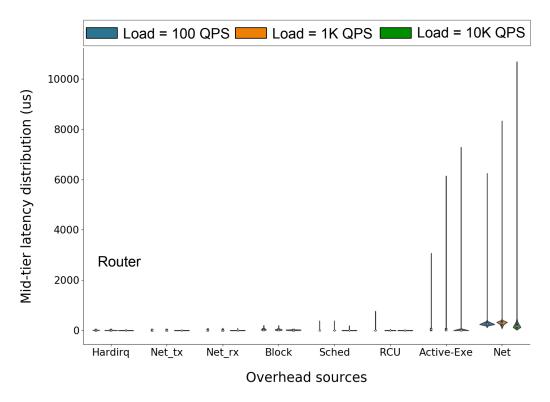

| 2.16 | Router's breakdown of OS overheads: Time to switch a thread from the               |     |

|      | active to the running state is high                                                | 57  |

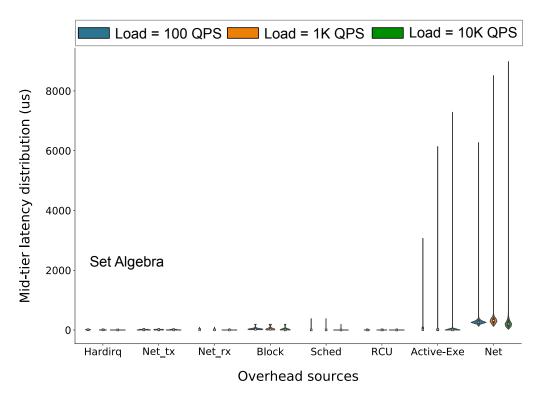

| 2.17 | Set Algebra's breakdown of OS overheads: Time to switch a thread from              |     |

|      | the <i>active</i> to the <i>running</i> state is high                              | 58  |

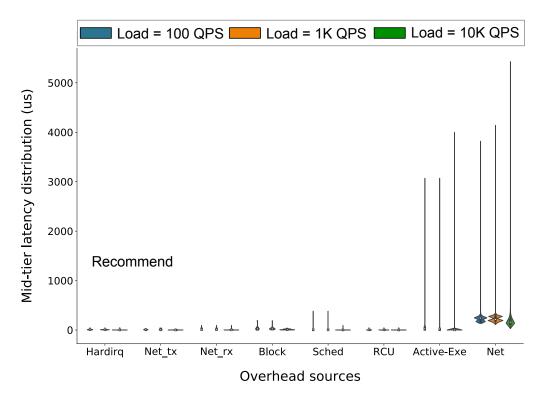

| 2.18 | Recommend's breakdown of OS overheads: Time to switch a thread from                |     |

|      | the <i>active</i> to the <i>running</i> state is high                              | 59  |

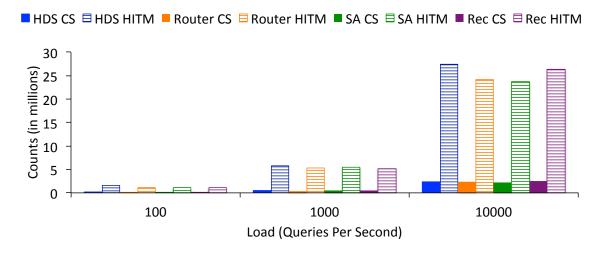

| 2.19 | Context switches (CS) and thread contention (HITM) incurred (in millions)          |     |

|      | for each benchmark across diverse loads: Thread contention is a significant        |     |

|      | overhead                                                                           | 59  |

| 3.1  | A typical web application fan-out                                                  | 64  |

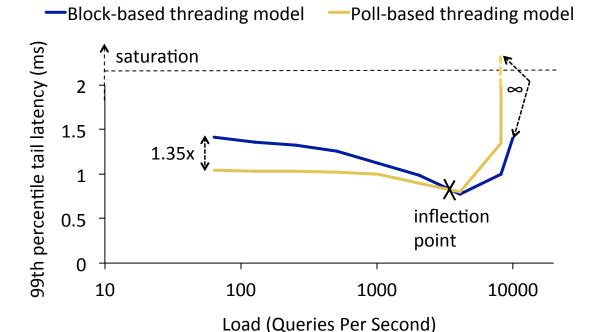

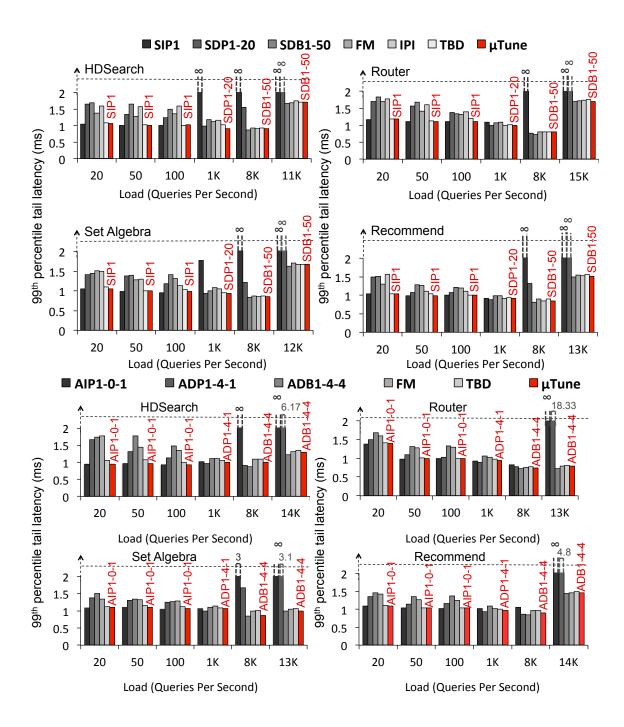

| 3.2  | 99 <sup>th</sup> % tail latency for an RPC handled by a block-based and poll-based |     |

|      | model: Poll-based model reduces latency by 1.35x at low load, and satu-            |     |

|      | rates at high load                                                                 | 67  |

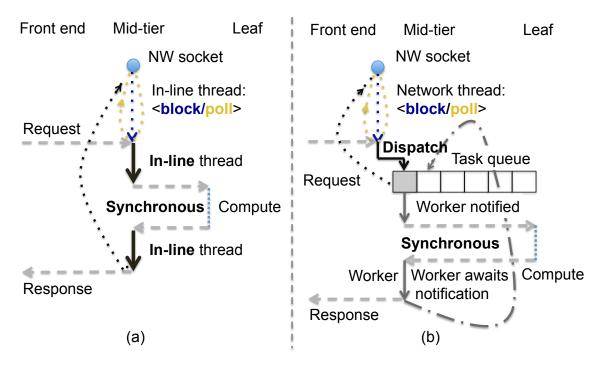

| 3.3  | Execution of an RPC by (a) SIB/SIP (b) SDB/SDP                                     | 72  |

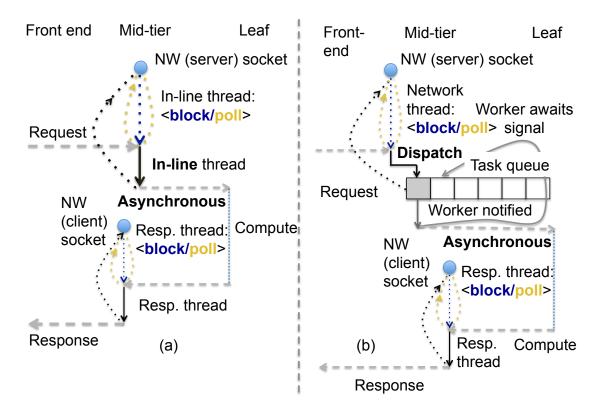

| 3.4  | Execution of an RPC by (a) AIB/AIP (b) ADB/ADP                                     | 74  |

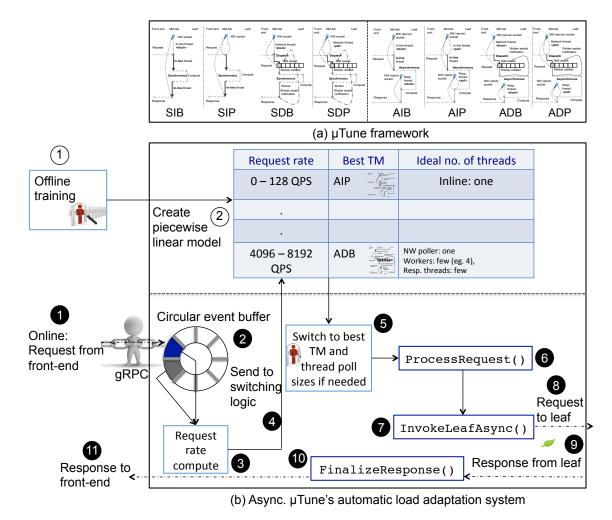

| 3.5  | $\mu$ Tune: System design                                                          | 75  |

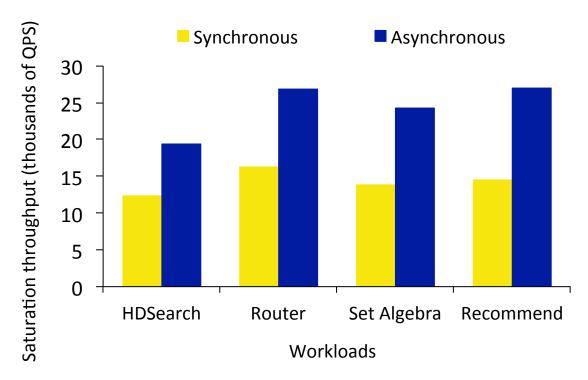

| 3.6  | Synchronous vs. asynchronous model's saturation throughput: The asyn-              |     |

|      | chronous model performs better by 42% on average                                   | 81  |

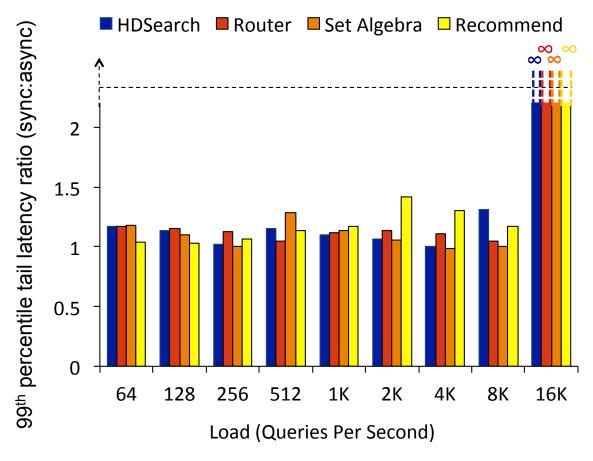

| 3.7  | Ratio of the best synchronous model's latency to the best asynchronous             |     |

|      | model's latency: The best asynchronous model is faster by a mean 12% at            |     |

|      | the loads that are achievable by the best synchronous model, and infinitely        |     |

|      | faster at higher loads                                                             | 82  |

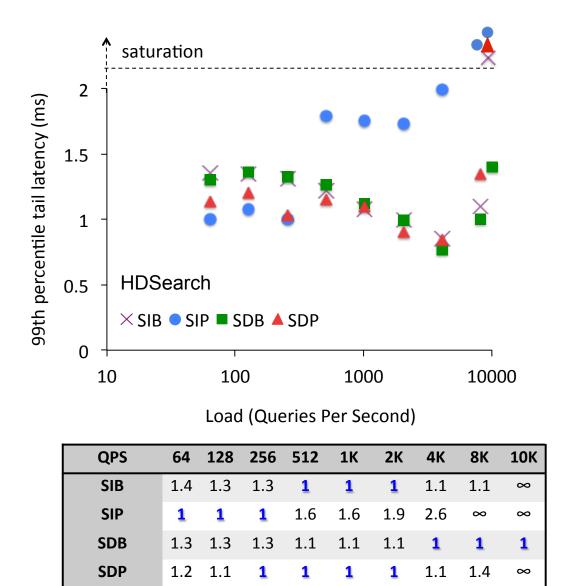

| 3.8  | Graph: Latency vs. load trade-off for HDSearch's synchronous models.               |     |

|      | Table: Latencies at each load normalized to the best latency for that load:        |     |

|      | No threading model is always the best                                              | 83  |

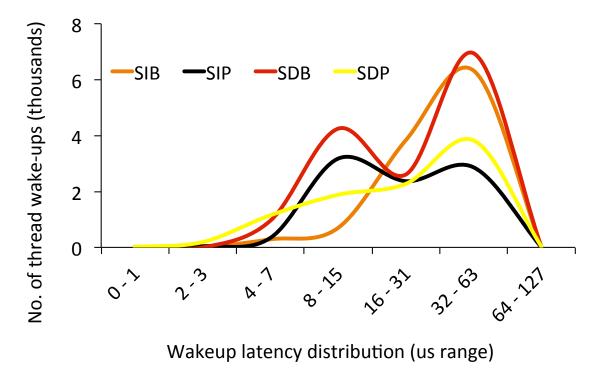

| 3.9  | HDSearch synchronous thread wakeups at 64 QPS: Block incurs more                   |     |

|      | wakeups                                                                            | 85  |

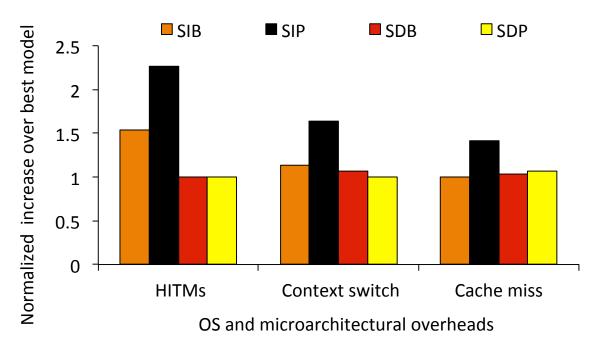

| 3.10 | Relative frequency of synchronous contention, context switches, and cache          |     |

|      | misses at 10K QPS: SIP performs the worst                                          | 86  |

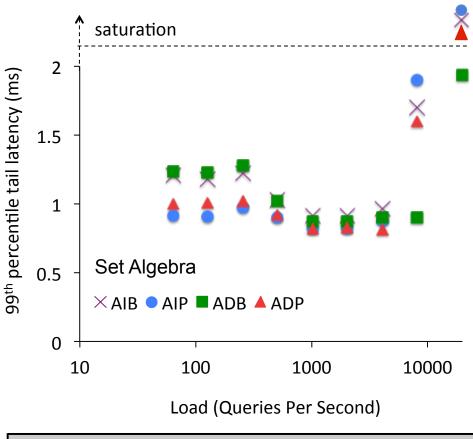

| 3.11 | Graph: Latency vs. load for Set Algebra's asynchronous models. Table:              |     |

|      | The latency at each load level normalized to the best latency for that load:       |     |

|      | No threading model is always the best                                              | 87  |

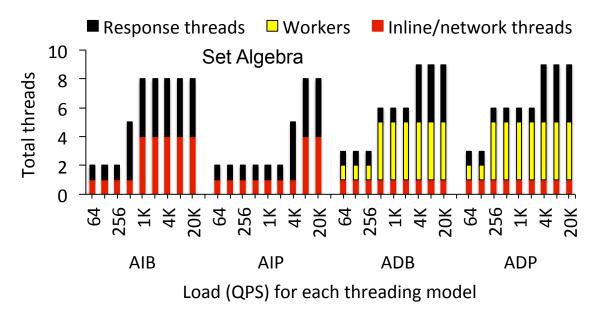

| 3.12 | Asynchronous thread pools for best tail latency: Big thread pools content.         | 88  |

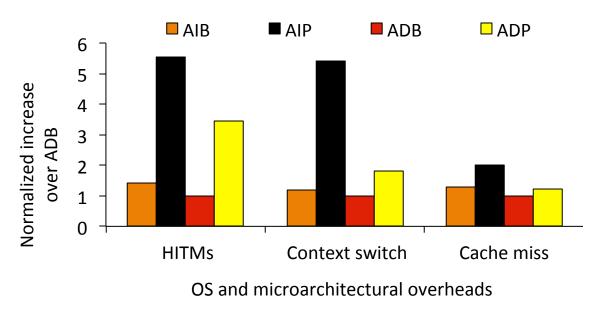

| 3.13 | Asynchronous Set Algebra's relative frequency of contention, context               |     |

|      | switches, and cache misses over the best asynchronous model at peak load:          |     |

|      | AIP performs worst                                                                 | 88  |

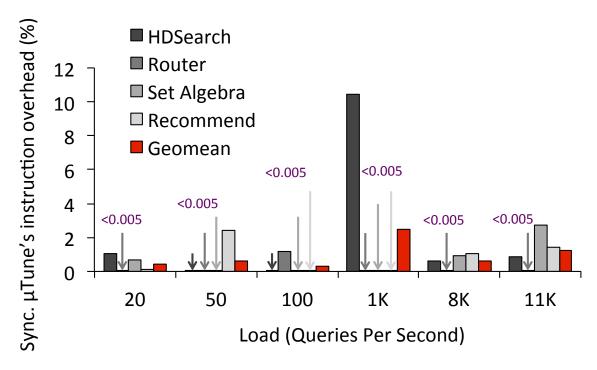

| 3.14 | Synchronous (top) and asynchronous (bottom) steady-state adaptation                | 92  |

| 3.15 | Synchronous $\mu Tune$ 's instruction overhead for steady-state loads: Less        |     |

|      | than 5% mean overhead incurred                                                     | 93  |

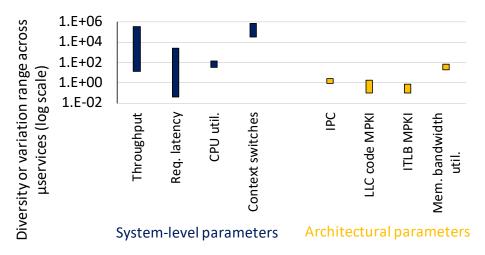

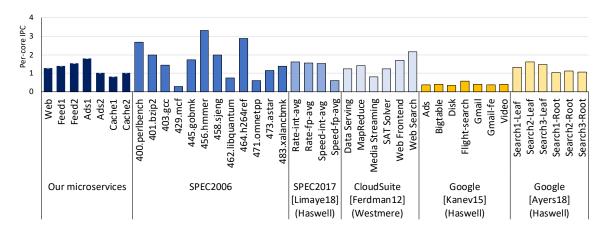

| 4.1  | Variation in system-level & architectural traits across microservices: Face-       |     |

|      | book's microservices face extremely diverse bottlenecks                            | 106 |

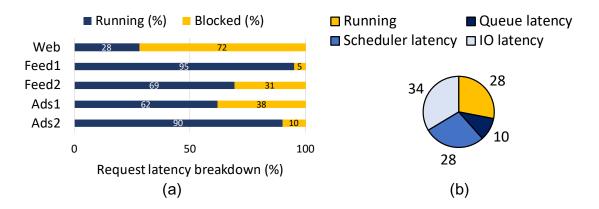

| 4.2  | (a) A single request's latency breakdown for each $\mu$ service: Few $\mu$ services |        |

|------|-------------------------------------------------------------------------------------|--------|

|      | block for a long time, (b) Web's request latency breakdown: Thread over-            |        |

|      | subscription causes scheduling delays                                               |        |

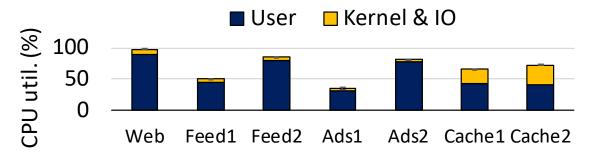

| 4.3  | Max. achievable CPU utilization in user- and kernel-mode across $\mu$ services:     |        |

|      | Utilization can be low to avoid QoS violations                                      | . 114  |

| 4.4  | Fraction of a second spent context switching (range): Cache1 & Cache2               |        |

|      | can benefit from context switch optimizations                                       | . 115  |

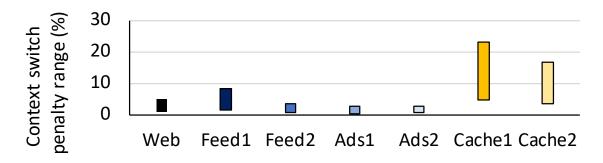

| 4.5  | Instruction type breakdown across microservices: Instruction mix ratios             |        |

|      | vary substantially across microservices                                             | 116    |

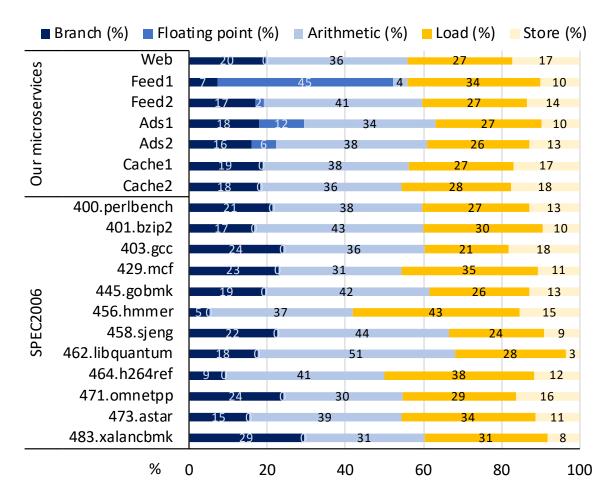

| 4.6  | Per-core IPC across Facebook's microservices and prior work (IPC mea-               |        |

|      | sured on other platforms): Facebook's microservices have a high IPC                 |        |

|      | diversity                                                                           | . 117  |

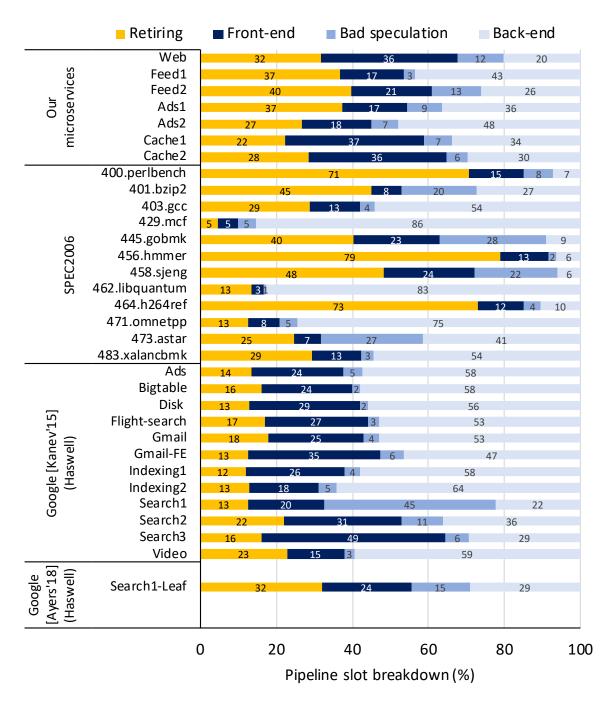

| 4.7  | Top-down bottleneck breakdown: Several of Facebook's microservices                  |        |

|      | face high front-end stalls                                                          | 118    |

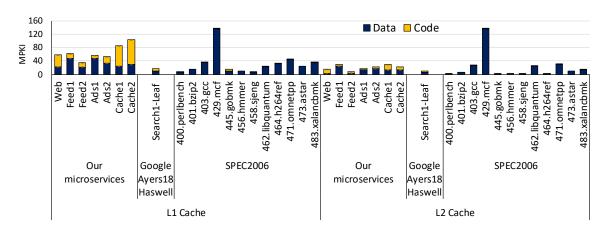

| 4.8  | L1 & L2 code & data MPKI: Facebook's microservices typically have                   |        |

|      | higher L1 MPKI than comparison applications                                         | 120    |

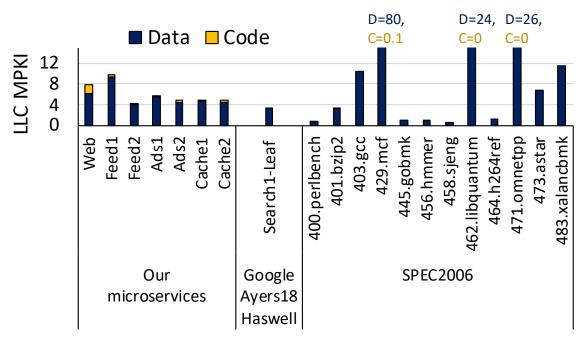

| 4.9  | LLC code & data MPKI: LLC data MPKI is high across microservices                    |        |

|      | and Web incurs a high code LLC MPKI                                                 | 121    |

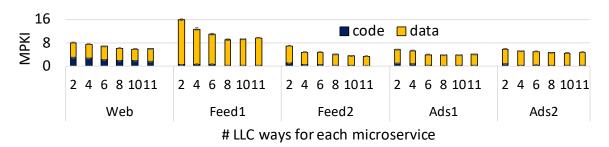

| 4.10 | LLC code and data MPKI vs. LLC size: Some microservices may benefit                 |        |

|      | from trading LLC capacity for more cores                                            | 121    |

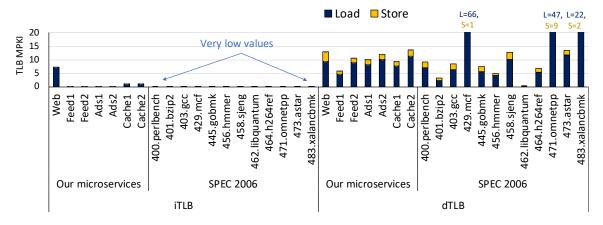

| 4.11 | I-TLB & D-TLB (load & store) MPKI breakdown: Some microservices                     |        |

|      | can benefit from huge page support.                                                 | 122    |

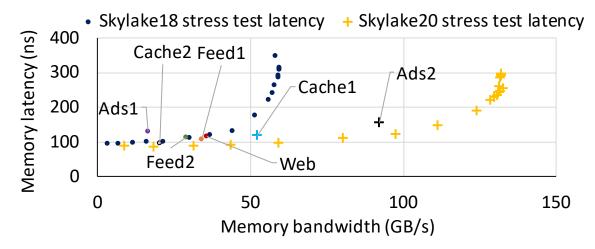

| 4.12 | Memory bandwidth vs. latency: Microservices under-utilize memory                    |        |

|      | bandwidth to avoid latency penalties                                                | 123    |

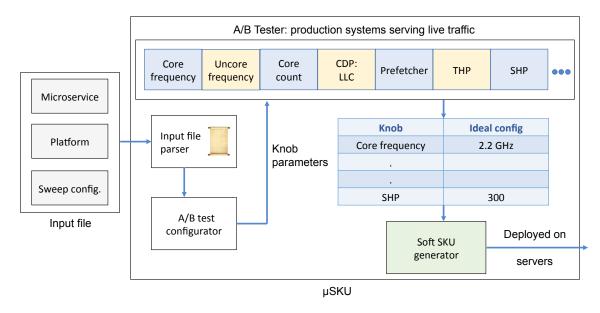

| 4.13 | $\mu$ SKU: System design                                                            |        |

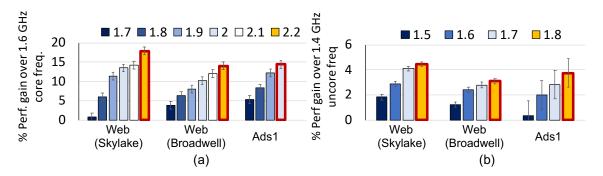

| 4.14 | Performance trend with (a) core frequency scaling, (b) uncore frequency             |        |

|      | scaling: The maximum frequency offers the best performance                          | 131    |

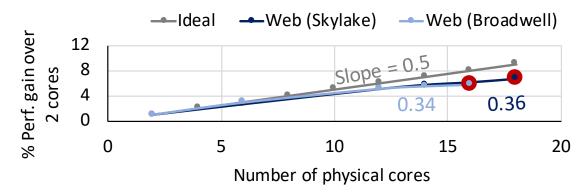

| 4.15 | Performance trend with core count scaling: Web is core-bound                        |        |

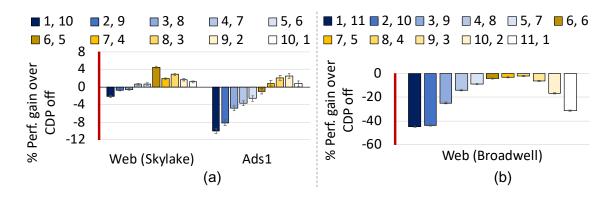

| 4.16 | Performance trend with CDP scaling: (a) Web (Skylake) & Ads1 benefit                | 100    |

| 0    | due to lower code MPKI (b) Web (Broadwell) has no gains                             | 133    |

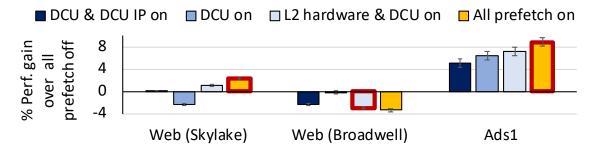

| 4.17 | Performance trends with varied prefetcher configurations: Turning off               | 100    |

| 1.17 | prefetchers can improve bandwidth utilization in Web (Broadwell)                    | 134    |

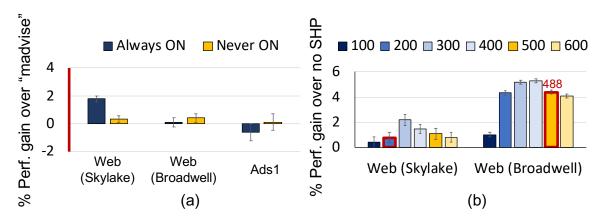

| 4.18 | Performance trends with varied (a) THP: Web (Skylake) benefits from                 | . 15 1 |

| 1.10 | THP ON, (b) SHP: There is a sweet spot in optimal SHP count                         | 135    |

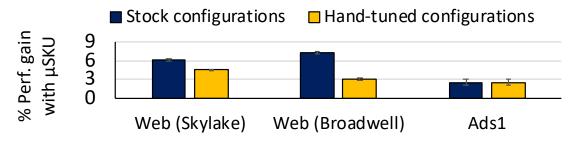

| 4.19 | Performance gain with $\mu SKU$ over stock and hand-tuned servers: $\mu SKU$        | 155    |

| т,17 | outperforms even hand-tuned production servers                                      | 136    |

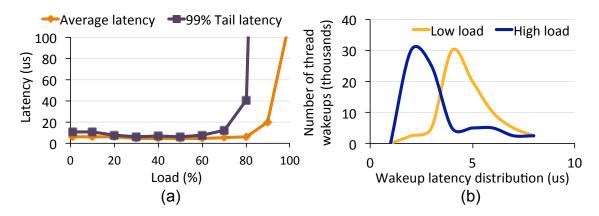

| 5.1  | (a) Epoll latency with increasing load: Interrupts face $\mu$ s-scale context       | 150    |

| 3.1  | switches & thread wakeups. (b) Thread wakeups at low & high load:                   |        |

|      | Low-load wakeups are costlier.                                                      | 154    |

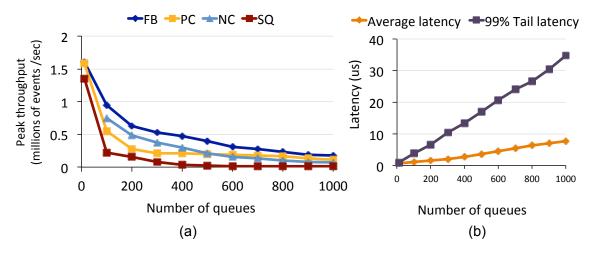

| 5.2  | (a) Peak throughput when spin-polling many queues: Throughput reduces               | 154    |

| 3.2  | due to empty queue checks. (b) Latency when polling many queues: Long               |        |

|      |                                                                                     | 157    |

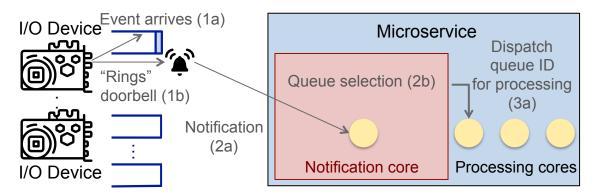

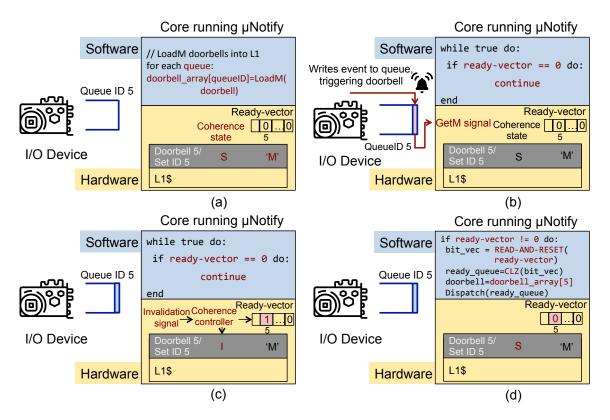

| 5.3  | loop traversals dominate                                                            |        |

|      | High-level system model                                                             |        |

| 5.4  | High-level diagram of $\mu Notify$ 's operations                                    |        |

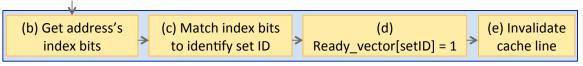

| 5.5  | High-level cache coherence controller with $\mu Notify$                             | . 104  |

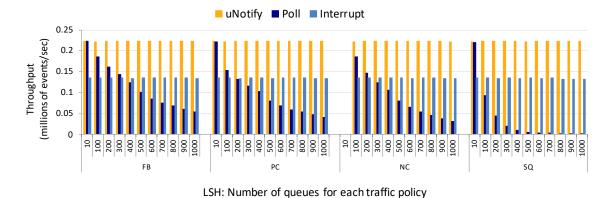

| 5.6  | Peak throughput achieved by $\mu Notify$ compared to spin-polling and interrupts across different queue counts and traffic shapes for LSH: $\mu Notify$ consistently achieves a higher throughput compared to state-of-the-art                     |       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      |                                                                                                                                                                                                                                                    | . 170 |

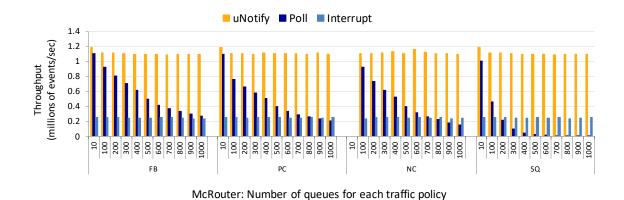

| 5.7  | Peak throughput achieved by $\mu Notify$ compared to spin-polling and interrupts across different queue counts and traffic shapes for McRouter: $\mu Notify$ consistently achieves a higher throughput compared to state-of-                       | . 170 |

|      | the-art paradigms                                                                                                                                                                                                                                  | . 170 |

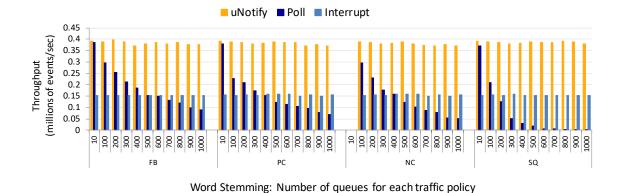

| 5.8  | Peak throughput achieved by $\mu Notify$ compared to spin-polling and interrupts across different queue counts and traffic shapes for Word Stemming: $\mu Notify$ consistently achieves a higher throughput compared to state-of-the-art paradigms | 171   |

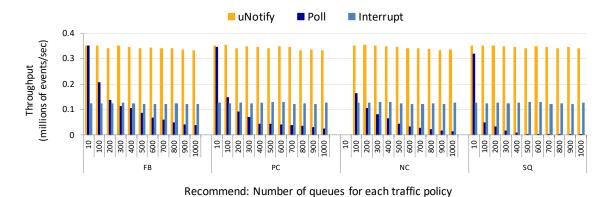

| 5.9  | Peak throughput achieved by $\mu Notify$ compared to spin-polling and interrupts across different queue counts and traffic shapes for Recommend: $\mu Notify$ consistently achieves a higher throughput compared to state-of-                      | . 171 |

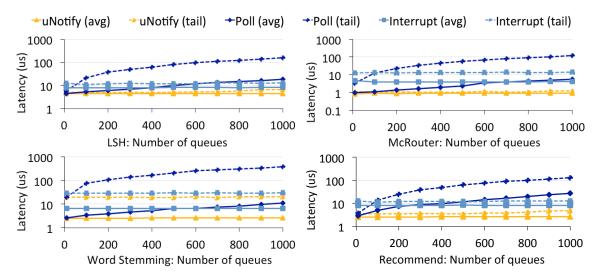

| 5.10 | $\mu Notify$ 's latency under light traffic with increasing queues (Y-axis is log-scale): $\mu Notify$ achieves lower latency.                                                                                                                     |       |

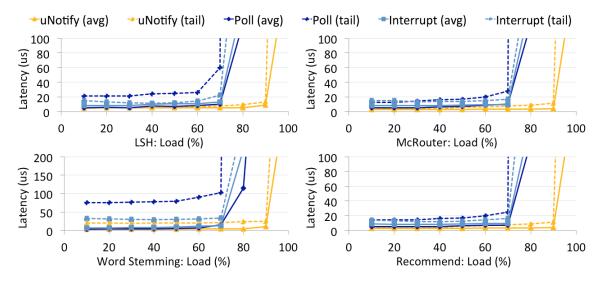

| 5.11 | $\mu Notify$ 's latency with increasing load compared to state-of-the-art: $\mu Notify$ sustains higher load with low latency.                                                                                                                     |       |

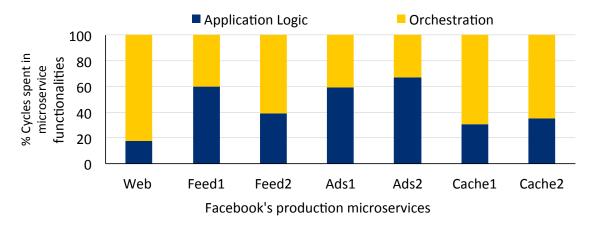

| 6.1  | Breakdown of cycles spent in core application logic vs. orchestration work: Orchestration overheads can significantly dominate.                                                                                                                    |       |

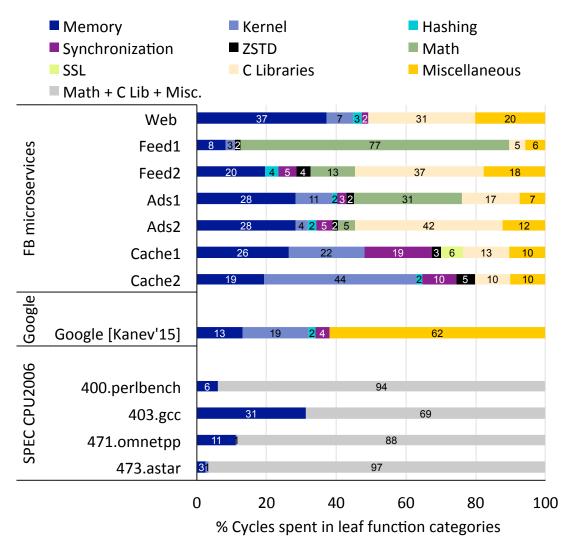

| 6.2  | Breakdown of cycles spent in leaf functions: Memory functions consume a significant portion of total cycles                                                                                                                                        |       |

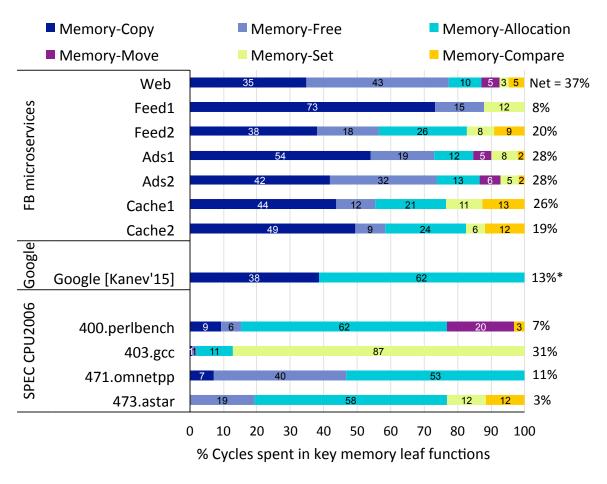

| 6.3  | Breakdown of cycles spent in memory leaf functions as a fraction of total cycles: Memory copy, allocation, & free consume significant cycles                                                                                                       |       |

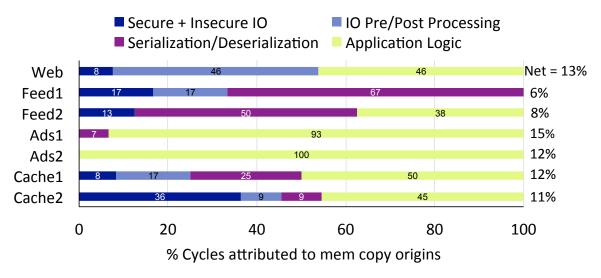

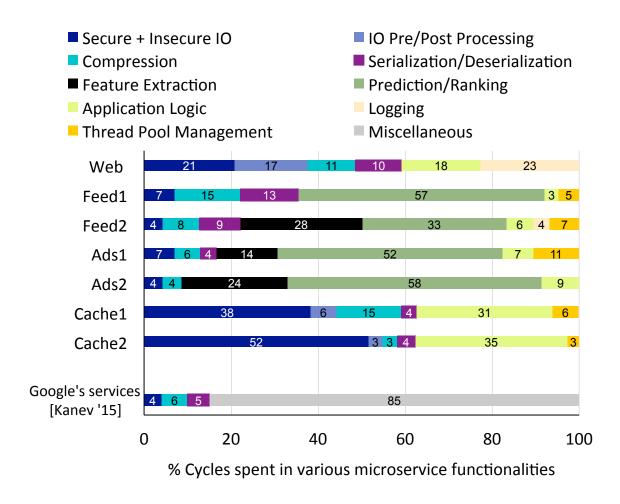

| 6.4  | Breakdown of service functionalities that invoke memory copies: There is significant diversity in dominant functionalities that perform copies                                                                                                     |       |

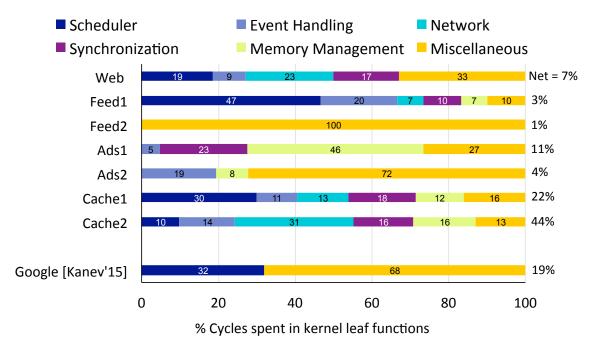

| 6.5  | Breakdown of cycles spent in various kernel leaf functions: Kernel scheduler, event handling, and network overheads can be high.                                                                                                                   |       |

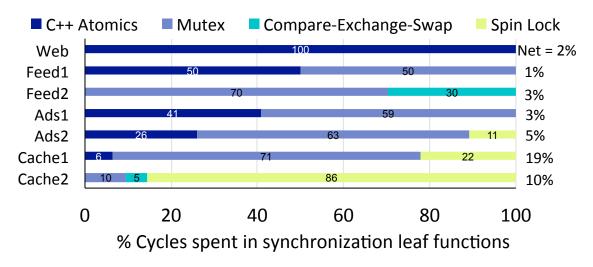

| 6.6  | Breakdown of CPU cycles spent in synchronization functions: Cache frequently uses spin locks to avoid thread wakeup delays                                                                                                                         |       |

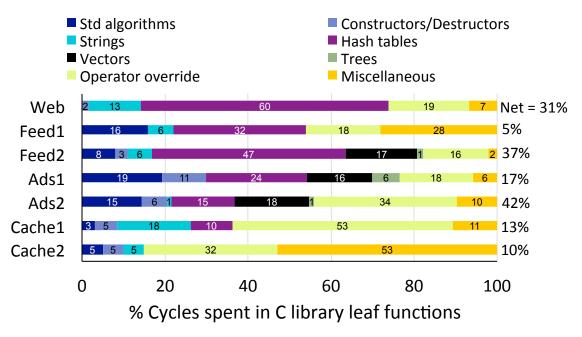

| 6.7  | Breakdown of CPU cycles spent in C libraries: ML services perform several vector operations while dealing with large feature vectors                                                                                                               |       |

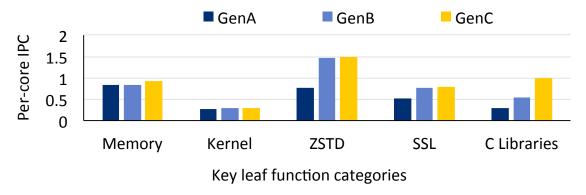

| 6.8  | Cache1's IPC scaling across three CPU generations for key leaf functions:                                                                                                                                                                          |       |

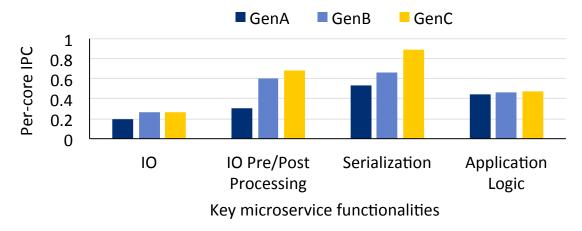

| 6.9  | Kernel IPC is typically low & scales poorly                                                                                                                                                                                                        |       |

| 6.10 | Cache1's IPC scaling across three CPU generations for key functionality categories: A low I/O IPC is primarily due to a low kernel IPC                                                                                                             |       |

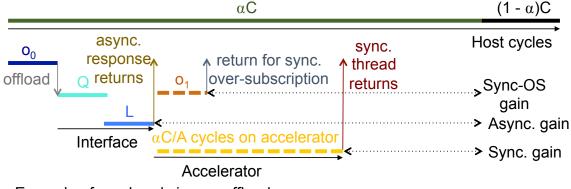

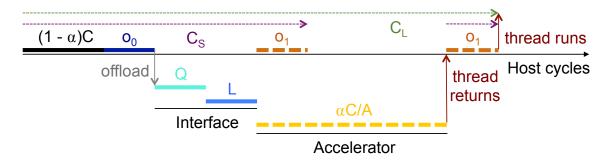

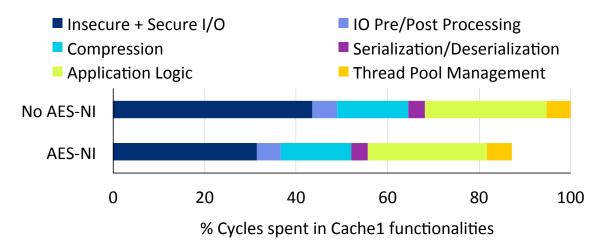

| 6.11 | Example timeline of host & accelerator                                                                                                                                                                                                             |       |

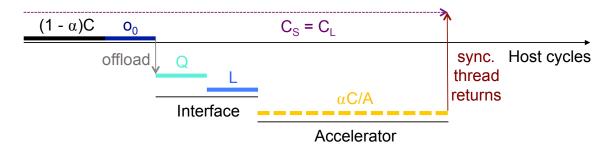

| 6.12 | Modeling Sync $C_S$ and $C_L$ for one offload                                                                                                                                                                                                      |       |

| 6.13 | Modeling Sync-OS $C_S$ and $C_L$ for one offload                                                                                                                                                                                                   |       |

| 6.14 | Modeling Async $C_S$ and $C_L$ for one offload                                                                                                                                                                                                     |       |

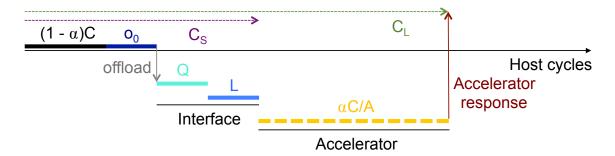

| 6.15 | CDF of bytes encrypted in Cache1: <512B are frequently encrypted.                                                                                                                                                                                  |       |

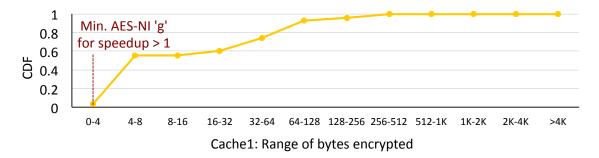

| 6.16 | Breakdown of cycles spent in Cachel's functionalities for both the no-     |

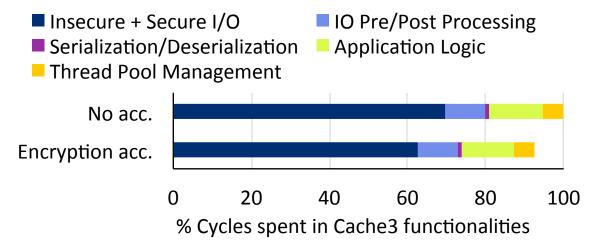

|------|----------------------------------------------------------------------------|

|      | AES-NI (unaccelerated) & with-AES-NI (accelerated) cases: 12.8% of         |

|      | cycles are freed up with AES-NI                                            |

| 6.17 | Breakdown of cycles spent in Cache3's functionalities when encryption is   |

|      | accelerated vs. not: Secure IO calls are optimized with acceleration 208   |

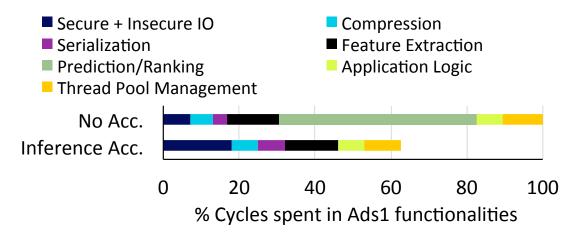

| 6.18 | Breakdown of cycles spent in Ads1's functionalities for both the inference |

|      | unaccelerated & accelerated cases: All inference cycles are freed up 209   |

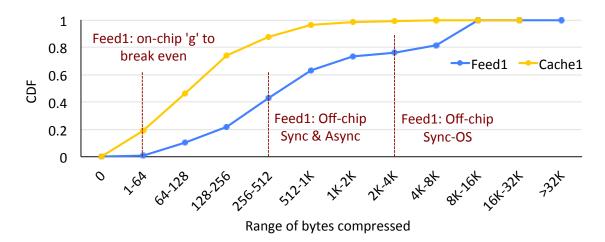

| 6.19 | CDF of bytes compressed in Feed1 and Cache1: Feed1 often compresses        |

|      | large granularities                                                        |

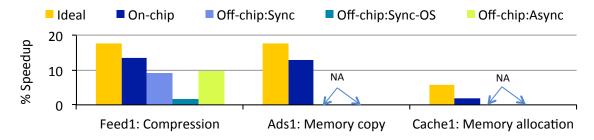

| 6.20 | Accelerometer-estimated speedup for key overheads we identified: Perfor-   |

|      | mance bounds from accelerator offload limit achievable speedup 212         |

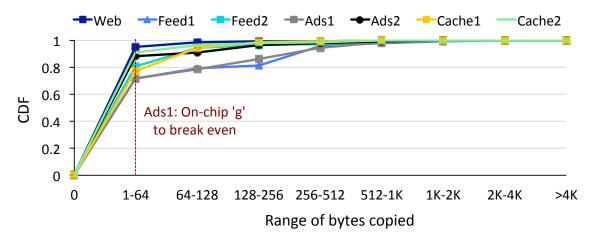

| 6.21 | CDF of memory copies across microservices: Most microservices fre-         |

|      | quently copy small granularities                                           |

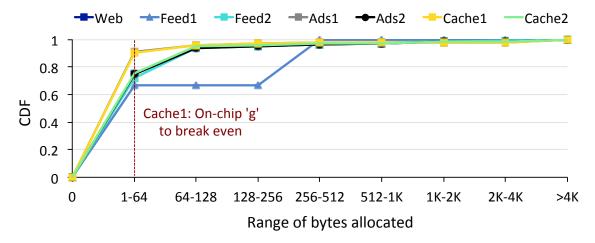

| 6.22 | CDF of memory allocations across microservices: Most microservices         |

|      | frequently allocate small granularities                                    |

# LIST OF TABLES

## **Table**

| 1.1 | Timeline of the application layer's evolution in response to the unprecedented growth in hyperscale web service trends and today's hardware reality: There has been a shift from monolithic web application architectures to more granular architectures such as microservices |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Timeline of the evolution of software abstraction layers in response to the unprecedented growth in hyperscale web service trends and today's hardware reality: There has been a shift from heavy-weight abstractions                                                          |

|     | (e.g., virtualization) to light-weight abstraction layers (e.g., containers).                                                                                                                                                                                                  |

| 1.3 | Timeline of the hardware layer's evolution in response to the unprecedented growth in hyperscale web service trends and today's hardware                                                                                                                                       |

|     | reality: There has been a shift towards building specialized hardware for                                                                                                                                                                                                      |

|     | various "killer" web applications                                                                                                                                                                                                                                              |

| 2.1 | Summary of a comparison of $\mu$ Suite with prior works: Unlike prior works,                                                                                                                                                                                                   |

|     | $\mu$ Suite is open-source, has web services composed of microservices, and                                                                                                                                                                                                    |

|     | enables the study of mid-tier microservices                                                                                                                                                                                                                                    |

| 2.2 | Mid-tier microservice processor specification                                                                                                                                                                                                                                  |

| 3.1 | Mid-tier microservice processor specification                                                                                                                                                                                                                                  |

| 3.2 | $99^{th}\%$ tail latency (ms) for load transients                                                                                                                                                                                                                              |

| 4.1 | Skylake18, Skylake20, Broadwell16's key attributes                                                                                                                                                                                                                             |

| 4.2 | Average request throughput, request latency, & path length across mi-                                                                                                                                                                                                          |

|     | croservices: We observe great diversity across services                                                                                                                                                                                                                        |

| 4.3 | Summary of findings and suggestions for future optimizations 124                                                                                                                                                                                                               |

| 6.1 | GenA, GenB, and GenC CPU platforms' attributes                                                                                                                                                                                                                                 |

| 6.2 | Categorization of leaf functions                                                                                                                                                                                                                                               |