# **Compiler Auto-Tuning for Code Optimization**

by

Sunghyun Park

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2021

Doctoral Committee:

Professor Scott Mahlke, Chair Associate Professor Ronald Dreslinski Jr Professor Mingyan Liu Associate Professor Yongjun Park, Hanyang University Associate Professor Lingjia Tang © Sunghyun Park sunggg@umich.edu ORCID iD: 0000-0003-4793-9069

2021

To my family

# ACKNOWLEDGEMENTS

Overall, it was such a journey. However, this journey would have not been possible without the support of many people.

First of all, I would like to thank Professor Scott Mahlke for giving me this wonderful opportunity to grow and advising me how to become an independent researcher. By using his insights and critical thinking, I could learn important questions that have to be asked and shape my own way of attacking the problem. Also, I truly appreciate how he helped me making important decisions in/outside the research.

It was fortunate to have the privilege of working with amazing people. Professor Yongjun Park has provided invaluable advice and support for my studies. The mentorship from Dr. Youfeng Wu had a great influence on my direction of thesis by assisting me to explore my research interests during my internship at Intel. The collaboration work with folks at Carnegie Mellon University under the guidance of Professor Tianqi Chen and Professor Zhihao Jia has been inspiring and their insights have been helpful to move forward to the right direction. I also enjoyed working as a teaching assistant for Professor Lingjia Tang by having certain degree of freedom in leading every Friday's discussion session. The support and advice from Professor Jae W. Lee was very helpful during the graduate school admission process. Also, Professor Mingyan Liu and Ronald Dreslinski Jr gave me great feedback to improve my dissertation.

I am grateful to have great comrades as a part of the CCCP research group. Ankit Sethia, Mehrzad Samadi, Anoushe Jamshidi, Andrew Lukefahr, Shruti Padmanabha, Hyoun Kyu Cho, John Kloosterman, Jason Jong Kyu Park, and Janghaeng Lee have been always approachable and willing to help me whenever I need. Also, it has been fun to suffer together and grow together with Babak Zamirai, Jiecao Yu, Shikai Li, Jonathan Bailey, Salar Latifi, Ze Zhang, Hossein Golestani, Pedram Zamirai, Armand Behroozi, Brandon Nguyen, Yunjie Pan and Sanjay Sri Vallabh.

When life gets rough on me, I could use my friends to laugh and get recharged. Hyochan Ahn, Sungwoon Jang, Sangmin Yoo, Heewoo Kim, Gwen Ahn, Sangtaek Oh, Walter Shin, Chihyo Ahn, Kyumin Kwon, Byungjoon Lee, Taeju Park, Junki Cho, Seungjong Lee, Changyoung Jeong, Jonghoon Shin, Hun Kim, Hyorim Han and many others made Ann Arbor feel like home. Jongjin Lee, Chungha Sung and Sungbo Park are the ones who have been going through the graduate school together at different locations in North America. Although he is half a globe away, my old friend, Daseul Shin, has been giving me great encouragement by having our own silly conversations over the phone. Also, whenever I visit Korea once a year, Inhyuk Seo, Yonghan Kim, Junoh Park, Heesung Lee, Hyunkwon Shin, Ji-Su Lee, Seejun Choi, Sookyung Park, Jae-Yun Kim, Sedong Yeo, Minseo Kim, Jaewook Mirco Jung, Dojeon Lee, Junsu Kim, Jaehwan Seol, Sungmin Kim, and Jimo Gu always welcome me and make me feel like old times. During my last semester, I had a unique opportunity to collaborate with my old friend, Byungsoo Jeon. I have been enjoying this special experience very much. Also, I am happy to have my close friend, Yoon Jung, nearby for my new start in Seattle.

I would like to give my special thanks to my dear friend, Youngdae Kim, who always has been funny and inspiring to me. Without him, this journey would not have started. I miss him so much lately.

Last but not least, my utmost gratitude goes to my beloved family. Their infinite love and support made me possible to come this far. Unconditional love from my grandmother always makes me feel warm inside, steadfast belief from my parents gives me confidence to challenge myself to the next step, and my little bother always provides me with an immense amount of gratitude for everything he does for our family. I cannot wait to celebrate the end of this chapter in my life with them.

# TABLE OF CONTENTS

| DEDICA    | ΓΙΟΝ                                                                | ii  |

|-----------|---------------------------------------------------------------------|-----|

| ACKNOV    | VLEDGEMENTS                                                         | iii |

| LIST OF   | FIGURES                                                             | ix  |

| LIST OF   | TABLES                                                              | iii |

| ABSTRA    | СТ х                                                                | iv  |

| СНАРТЕ    | R                                                                   |     |

| 1 Introdu | iction                                                              | 1   |

| 1.1       | Introduction                                                        | 1   |

| 1.2       | Challenges and Contributions                                        | 3   |

|           | 1.2.1 Feasibility Study of Learning-Based Auto-Tuning Methods       | 3   |

|           | 1.2.2 Customization for a Group of Compiler Optimizations           | 3   |

|           | 1.2.3 Search for the Best Use of Diverse Backends                   | 4   |

|           | 1.2.4 Provision of Low-Cost Fault Protection                        | 4   |

| 1.3       | Background                                                          | 5   |

|           | 1.3.1 Compilers From Diverse Domains and Their Optimizations        | 5   |

|           | 1.3.2 Compiler Auto-Tuning                                          | 6   |

| 2 Multi-o | bjective Exploration for Practical Optimization Decisions in Binary |     |

| Transla   | ntion                                                               | 10  |

| 2.1       | Introduction                                                        | 10  |

| 2.2       |                                                                     | 12  |

|           | e                                                                   | 12  |

|           | •                                                                   | 14  |

| 2.3       | Motivation                                                          | 16  |

| 2.4       | Challenges and Opportunities                                        | 17  |

| 2.5       |                                                                     | 18  |

|           | 2.5.1 Feature Extraction                                            | 19  |

|           |                                                                     | 20  |

| 2.6       |                                                                     | 20  |

|           | 1 1                                                                 | 20  |

|           | 2.6.2 Prediction Accuracy                                           | 22  |

|           | 2.6.3 Performance Improvement In Translated Code                   | 24 |

|-----------|--------------------------------------------------------------------|----|

|           | 2.6.4 Prediction Overhead Analysis                                 | 25 |

|           | 2.6.5 Choice of Classification Algorithm                           | 26 |

| 2.7       | Redundant Feature Pruning                                          | 28 |

| 2.8       | Related Works                                                      | 30 |

| 2.9       | Conclusion                                                         | 31 |

|           | er: Effective Compiler Optimization Customization By Exposing Syn- |    |

| ergistic  | Relations                                                          | 33 |

| 3.1       | Introduction                                                       | 33 |

| 3.2       | Related Works                                                      | 35 |

| 3.3       | Design Motivation                                                  | 37 |

|           | 3.3.1 Multistage Structure                                         | 38 |

|           | 3.3.2 Optimization Impact Estimation                               | 40 |

|           | 3.3.3 Handling Local Optima                                        | 42 |

| 3.4       | SRTuner                                                            | 43 |

|           | 3.4.1 Reward Policy                                                | 46 |

|           | 3.4.2 Stage-Optimization Mapping                                   | 47 |

|           | 3.4.3 Extract Important Synergistic Relations                      | 48 |

| 3.5       | Performance Evaluation                                             | 48 |

|           | 3.5.1 Experimental Setup                                           | 48 |

|           | 3.5.2 GCC                                                          | 49 |

|           | 3.5.3 TVM                                                          | 51 |

|           | 3.5.4 OpenCL Compilers                                             | 52 |

| 3.6       | Discussion                                                         | 52 |

|           | 3.6.1 Identification Of Important Misuses                          | 52 |

|           | 3.6.2 Generalization Of Tuning Experiences                         | 55 |

| 3.7       | Conclusion                                                         | 57 |

| 4 Collage | e: Auto-tuning Deep Learning Execution Plans With Diverse Backends | 58 |

| 4.1       | Introduction                                                       | 58 |

| 4.2       | Related Work                                                       | 62 |

| 4.3       | Overview                                                           | 63 |

| 4.4       | Backend Pattern Abstraction                                        | 64 |

| 4.5       | Auto-tuning Execution Plan                                         | 66 |

|           | 4.5.1 Backend Placement Problem                                    | 66 |

|           | 4.5.2 Op-level Auto-tuning                                         | 66 |

|           | 4.5.3 Graph-level Auto-tuning                                      | 69 |

| 4.6       | Evaluation                                                         | 70 |

|           | 4.6.1 Experimental Setup                                           | 70 |

|           | 4.6.2 End-to-end Evaluation                                        | 71 |

|           | 4.6.3 Analysis of Backend Operator Placement                       | 73 |

|           | 4.6.4 Tuning Time                                                  | 73 |

| 4.7       | -                                                                  | 74 |

| 5 Low-Co  | ost Prediction-Based Fault Protection Strategy                     | 76 |

vii

| 5.1      | Introduction                              | 76  |

|----------|-------------------------------------------|-----|

| 5.2      | Motivation and Idea                       | 78  |

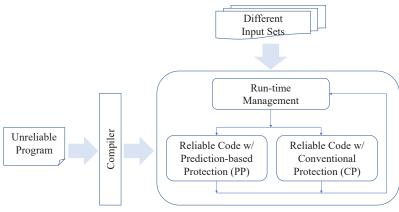

| 5.3      | System Overview                           | 82  |

| 5.4      | Prediction Techniques                     | 83  |

|          | 5.4.1 Dynamic Interpolation               | 84  |

|          | 5.4.2 Approximate Memoization             | 85  |

| 5.5      | Run-time Management                       | 86  |

| 5.6      | Training                                  | 88  |

| 5.7      | Evaluation                                | 88  |

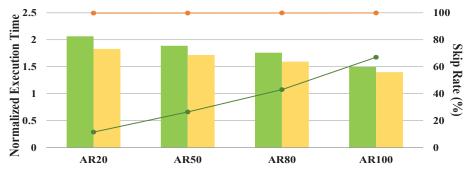

|          | 5.7.1 Performance Overhead                | 89  |

|          | 5.7.2 Reliability                         | 93  |

|          | 5.7.3 The Rationality of Acceptable Range | 94  |

| 5.8      | Related Works                             | 95  |

| 5.9      | Conclusion                                | 96  |

| 6 Conclu | sion and Future Works                     | 97  |

| 6.1      | Conclusion                                | 97  |

|          |                                           | 99  |

| BIBLIOG  | <b>GRAPHY</b>                             | .01 |

# LIST OF FIGURES

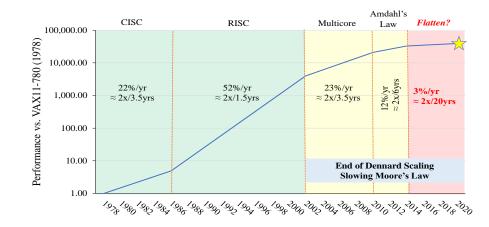

| 1.1 | Growth of computer performance using SPECintCPU benchmark suite [78]. The end of Dennard Scaling and Moore's Law slows down the performance improvement with hardware innovations. Annotation (star) indicates where we stand today in 2020.                 | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

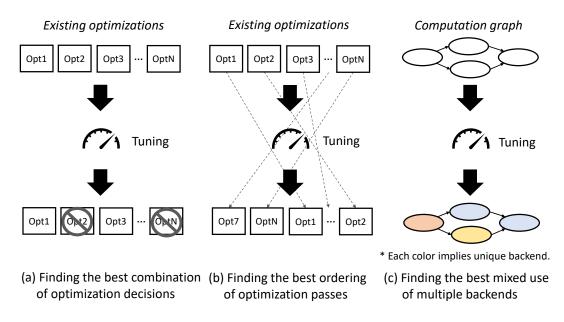

| 1.2 | Representative tuning problems                                                                                                                                                                                                                               | 7  |

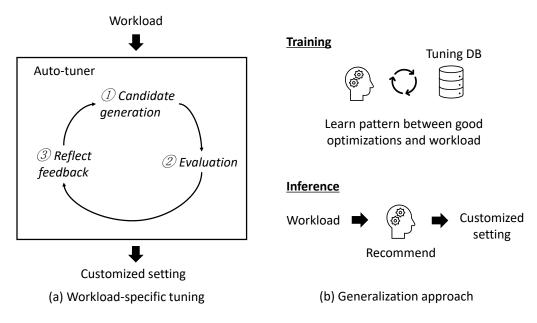

| 1.3 | Representative tuning approaches                                                                                                                                                                                                                             | 8  |

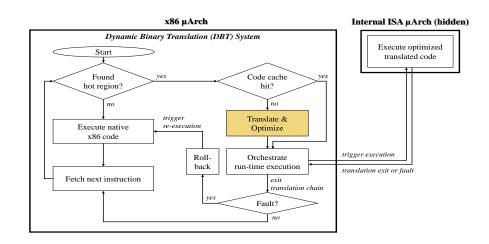

| 2.1 | Big picture of our HW/SW co-designed CPU with a DBT system. It con-<br>stains two different microarchitectures that each supports its own ISA. The<br>highlighted box illustrates the translation process by a binary translator and a<br>dynamic optimizer. | 13 |

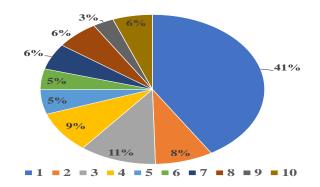

| 2.2 | Distribution of optimal unroll factors.                                                                                                                                                                                                                      | 16 |

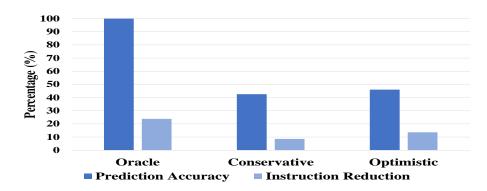

| 2.3 | Evaluation of current heuristic design. Prediction accuracy for optimal loop<br>unrolling decision and its impact on the dynamic instruction count in the re-                                                                                                |    |

|     | sulting optimized code are measured                                                                                                                                                                                                                          | 17 |

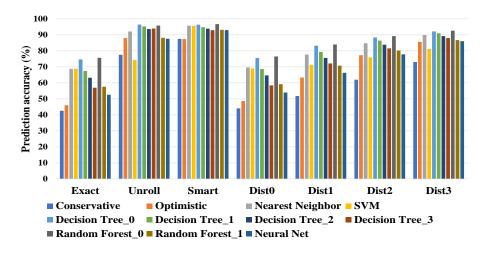

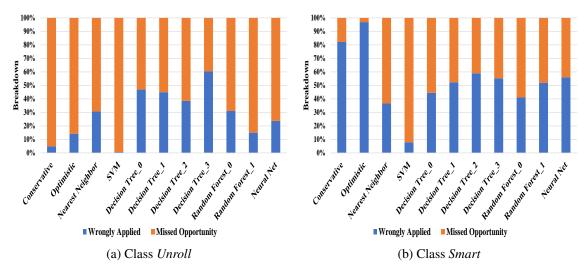

| 2.4 | Prediction accuracy with various classes                                                                                                                                                                                                                     | 23 |

| 2.5 | The breakdown of wrong predictions.                                                                                                                                                                                                                          | 23 |

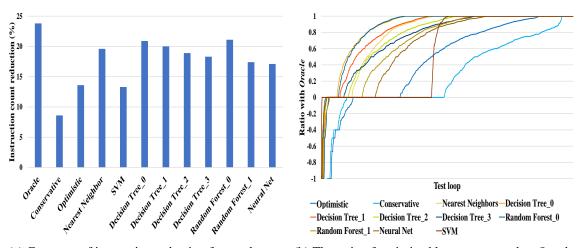

| 2.6 | Averaged instruction count reduction and the ratio of optimized loops com-<br>pared to <i>Oracle</i> for each decision model.                                                                                                                                | 25 |

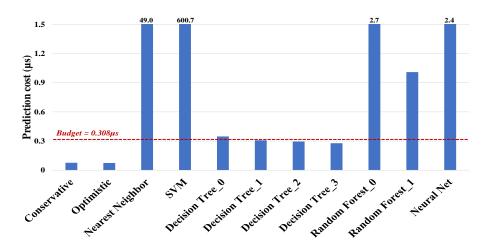

| 2.7 | Inference time for each model with given budget.                                                                                                                                                                                                             | 26 |

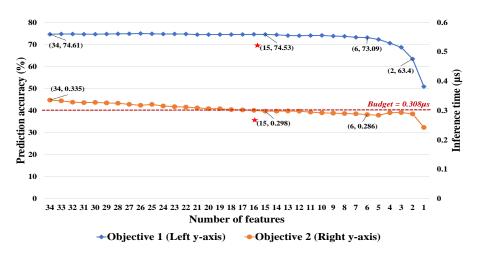

| 2.8 | The change in prediction accuracy and inference time during greedy feature selection process. With Top 15 features (marked with stars), the decision tree model can show an almost identical level of prediction accuracy to the model                       | 20 |

|     | with all 34 features while satisfying the time constraint                                                                                                                                                                                                    | 28 |

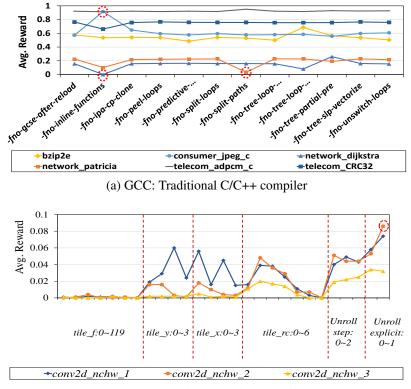

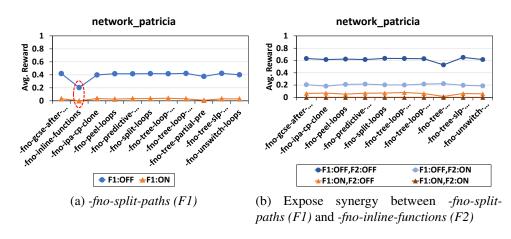

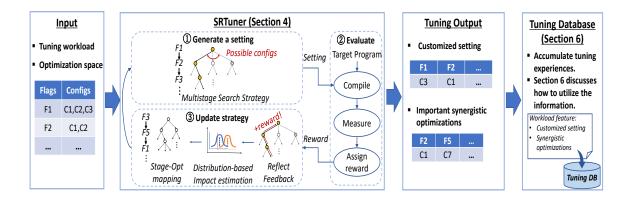

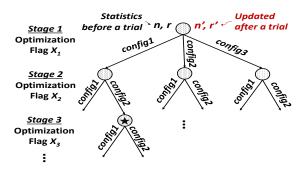

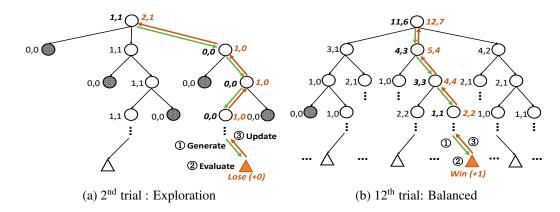

| 3.1<br>3.2   | Motivational experiment with two representative compilers. A reward (+1) is assigned whenever a combination outperforms the baseline setting. By sampling 2,000 settings, averaged reward for configuring each flag is examined Averaged reward given extra condition: (a)-(c) for GCC, (d) for TVM. Starting from Figure 3.1, the high-impact flag is configured for each benchmark. (a) shows the average reward after a single stage. When more than one flags are given, the relation between optimizations can be unveiled. (b) and (c) present the positive/negative interaction between two given optimizations, respectively. (d) demonstrates the same approach can be applied to TVM as | 38       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

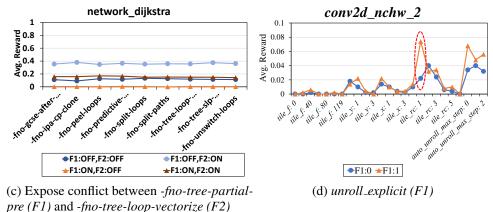

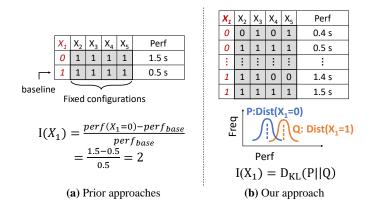

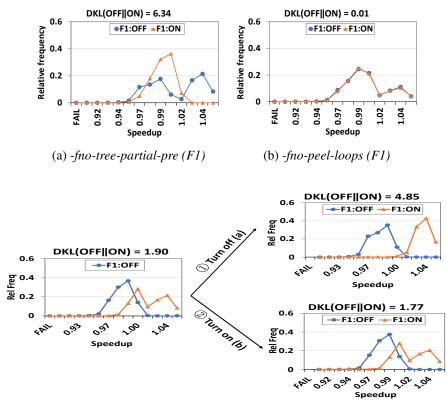

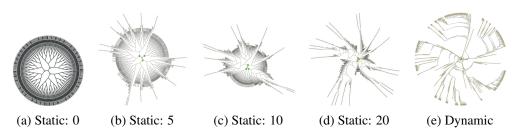

| 3.3          | well                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39       |

| 3.4          | configurations of others                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41       |

| 3.5          | are configured, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42<br>43 |

| 3.6          | SRTuner overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43       |

| 3.7          | visits, $n$ , and accumulates rewards, $r$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45<br>45 |

| 3.8          | Visualization of different reward policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46       |

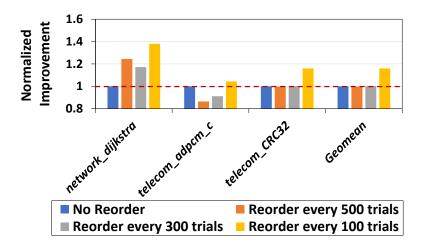

| 3.9          | Analysis of reordering frequencies. Each performance is normalized by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|              | one without remapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47       |

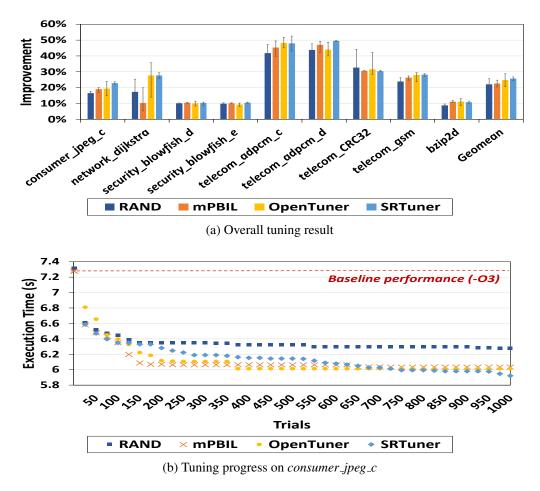

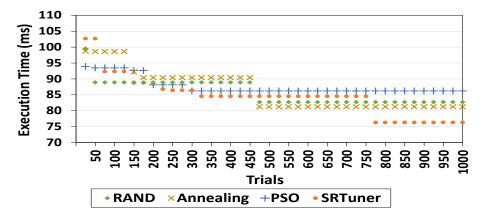

| 3.10         | Tuning C/C++ applications with GCC on Intel Xeon E5-2430.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

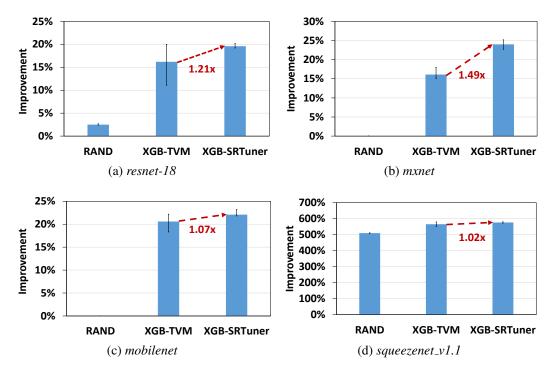

| 3.11         | Tuning deep learning workloads with TVM on NVIDIA RTX 2080Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51       |

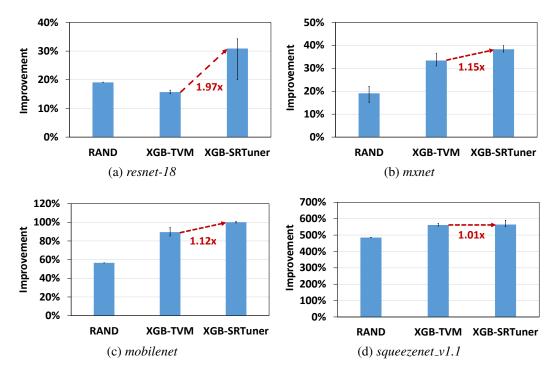

| 3.12<br>3.13 | Tuning deep learning workloads with TVM on NVIDIA Quadro K620 Tuning <i>comm</i> with OpenCL on Intel i7 9700K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| 3.13<br>3.14 | Tuning gemm with OpenCL on Intel i7-9700K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53       |

| 5.17         | running genun with Opened on review Kirk 200011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55       |

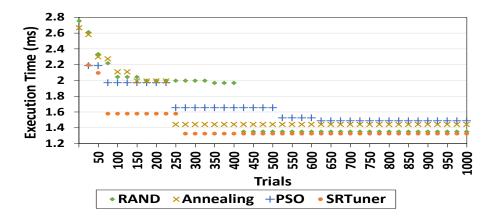

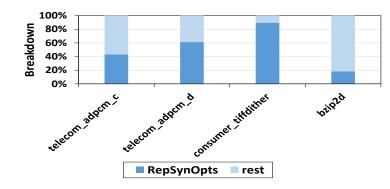

|      | Examine representative subset of synergistic optimizations revealed by                                                                                 | 54 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

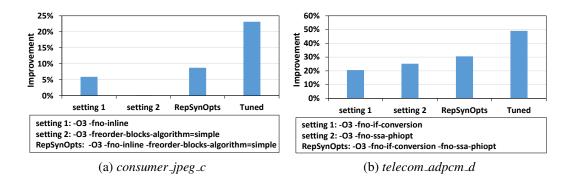

| 3.10 | Hot code region in <i>telecom_adpcm_d</i> where if-conversion and phi-node opti-<br>mizations are seriously misapplied by GCC.                         | 54 |

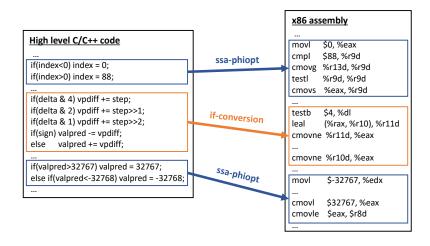

| 3.17 | Diverse applications with <i>-fno-if-conversion</i> and <i>-fno-ssa-phiopt</i> in their syn-                                                           | 54 |

| 5.17 | ergistic optimizations. Breakdown shows their importance in each customized                                                                            |    |

|      | setting.                                                                                                                                               | 55 |

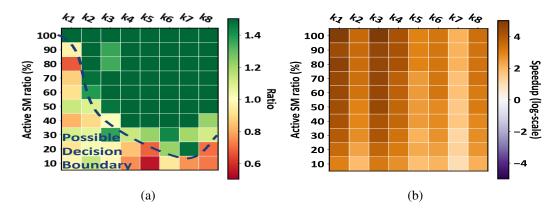

| 3.18 | Experiment with eight different kernels $(k1-8)$ and diverse SM activation ra-                                                                         | 55 |

| 5.10 | tios. (a) Performance ratio between high-end and low-end settings. Green and                                                                           |    |

|      | red cells imply cases where high-end and low-end settings should be applied                                                                            |    |

|      | respectively. Blue line represents a possible decision boundary. (b) Speed-                                                                            |    |

|      | up when choosing one of high-end and low-end settings in the right places.                                                                             |    |

|      | Speed-up is computed against the performance of default setting with 100%                                                                              |    |

|      | SMs                                                                                                                                                    | 56 |

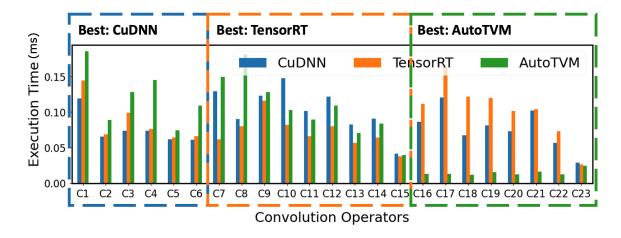

| 4.1  | Performance of various convolution operators in ResNext-50 on NVIDIA RTX                                                                               |    |

| 4.1  | 2070; Note that there is no single backend that always delivers the fastest                                                                            |    |

|      | implementation.                                                                                                                                        | 59 |

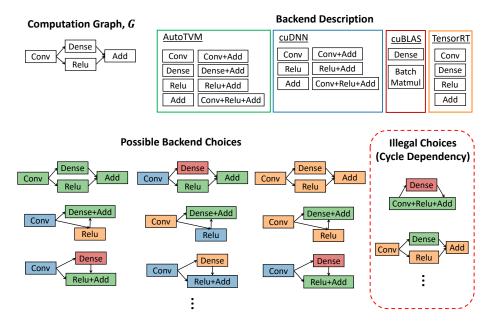

| 4.2  | An example of possible execution strategies for a simple workload with four                                                                            | 07 |

|      | different backends. This illustrates the explosive size of the search space and                                                                        |    |

|      | the difficulty in the efficient exploration. To assign backend, both graph topol-                                                                      |    |

|      | ogy and the supported backend pattern should be matched. In case of lowering                                                                           |    |

|      | to fused operators or offloading partial graph to inference engines, matched                                                                           |    |

|      | operators should not have any cyclic data dependency to avoid deadlock                                                                                 | 60 |

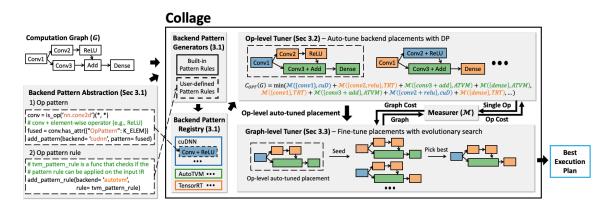

| 4.3  | System overview of <i>Collage</i>                                                                                                                      | 63 |

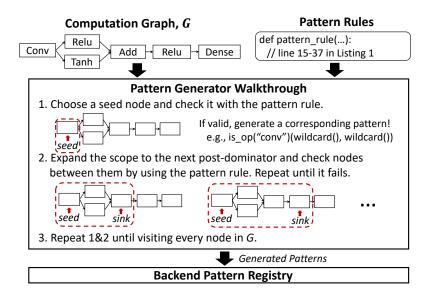

| 4.4  | Example illustrating how the backend pattern generator would automatically                                                                             |    |

|      | generate valid patterns with the pattern rule assumed in the listing 1                                                                                 | 65 |

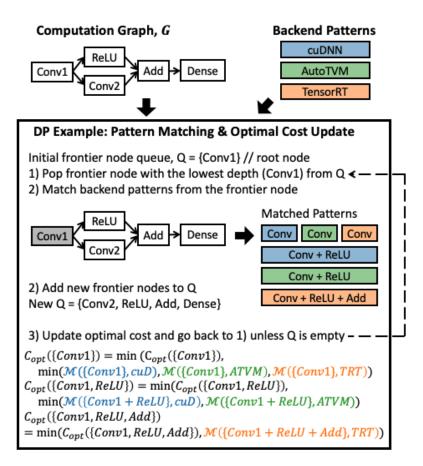

| 4.5  | Example of Dynamic Programming (DP) procedures for pattern matching and                                                                                |    |

|      | optimal cost update                                                                                                                                    | 67 |

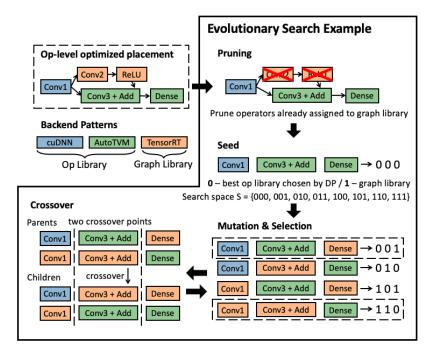

| 4.6  | Example of Evolutionary Search (ES) procedure                                                                                                          | 69 |

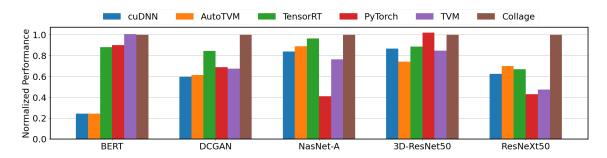

| 4.7  | End-to-end performance of diverse strategies in five different workloads on                                                                            |    |

|      | NVIDIA RTX 2070. Each performance is normalized by the performance of <i>Collage</i> . Note that following state-of-the-arts backends are employed for |    |

|      | each framework according to their capabilities: PyTorch (cuDNN, cuBLAS),                                                                               |    |

|      | TVM (cuDNN, cuBLAS, AutoTVM) and (cuDNN, cuBLAS, AutoTVM, and                                                                                          |    |

|      | Tensor $RT$ ).                                                                                                                                         | 71 |

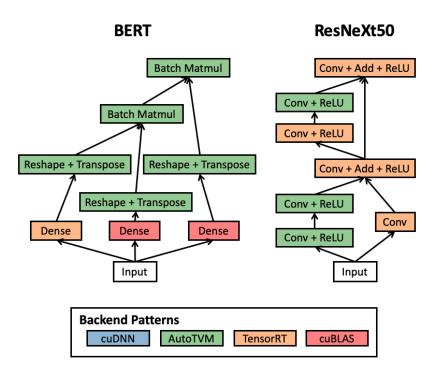

| 4.8  | Backend placement discovered by <i>Collage</i> on ResNeXt50 and BERT.                                                                                  | 72 |

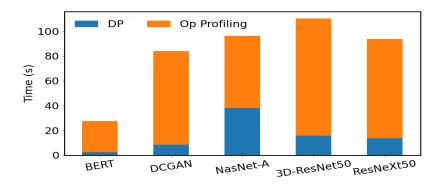

| 4.9  | Op-level tuning (DP) time breakdown for five different workloads. On aver-                                                                             |    |

|      | age, profiling overhead for operator cost measurements takes up 82% of the                                                                             |    |

|      | entire tuning time. Note that profiling is only necessary for new operators.                                                                           |    |

|      | Once the cost of a new operator is measured, its information will be saved in                                                                          |    |

|      | the logging database in <i>Collage</i> to avoid the repetitive profiling                                                                               | 74 |

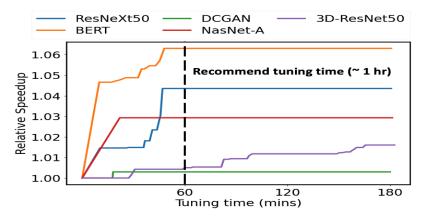

| 4.10 |                                                                                                                                                        |    |

|      | workloads. The y-axis presents the speedup relative to op-level tuning (DP).                                                                           |    |

|      | We observe that one hour of graph-level tuning empirically provides good                                                                               |    |

|      | trade-off between tuning time and speedup for most workloads                                                                                           | 74 |

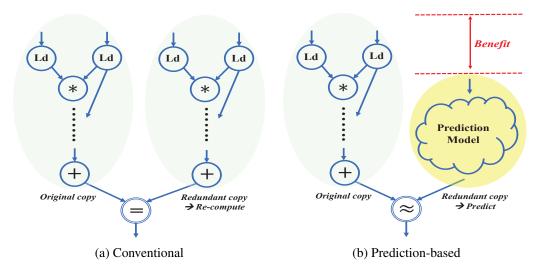

| 5.1 | Idea of each protection strategy. (a) Re-compute and validate. (b) Estimate    |    |

|-----|--------------------------------------------------------------------------------|----|

|     | and fuzzy-validate                                                             | 79 |

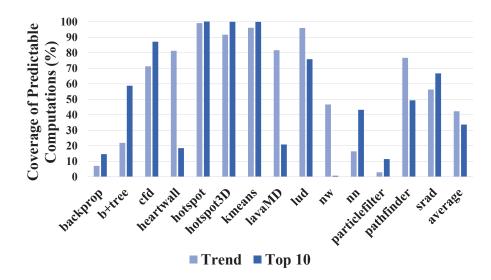

| 5.2 | Proportion of dynamic instructions whose computation outputs can be esti-      |    |

|     | mated. Measured in Rodinia [54] benchmark suite                                | 80 |

| 5.3 | System Overview                                                                | 82 |

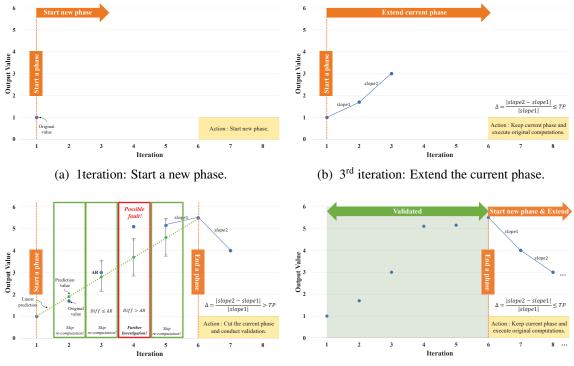

| 5.4 | Sketch of dynamic interpolation. Whenever slope change is above tuning pa-     |    |

|     | rameter (TP), a phase is defined. During the validation process at (c), a data |    |

|     | element is considered as a possible fault if the difference between original   |    |

|     | value and prediction value is greater than acceptable range (AR)               | 83 |

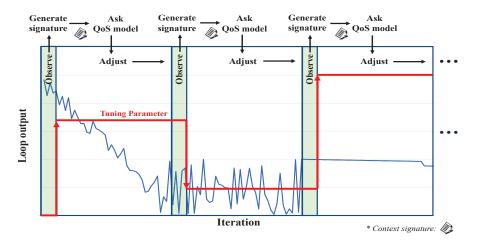

| 5.5 | An example of run-time management for dynamic interpolation. Run-time          |    |

|     | management periodically generates context signatures by summarizing the        |    |

|     | current run-time context to adjust TP based on the QoS model                   | 87 |

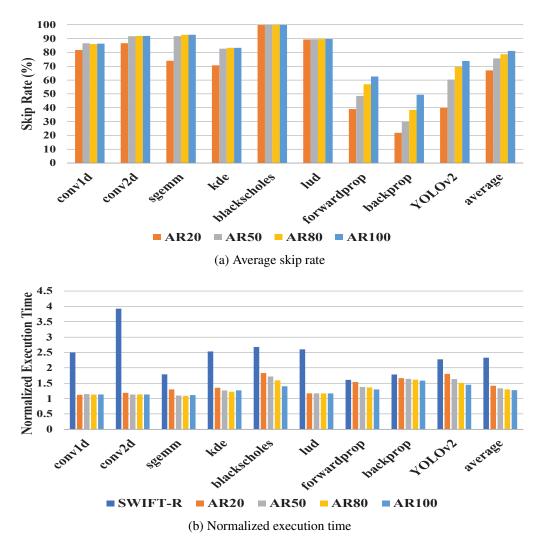

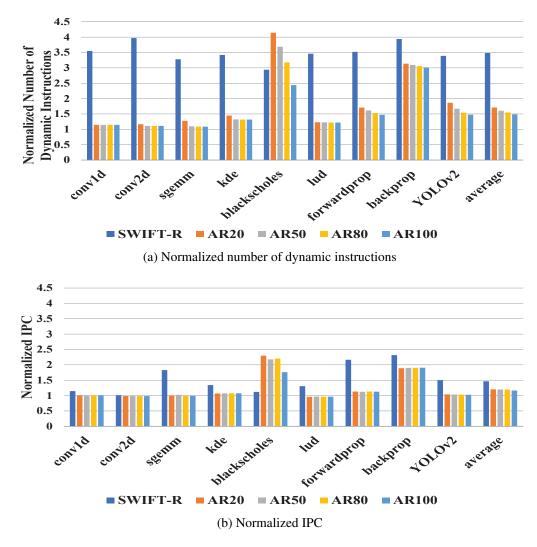

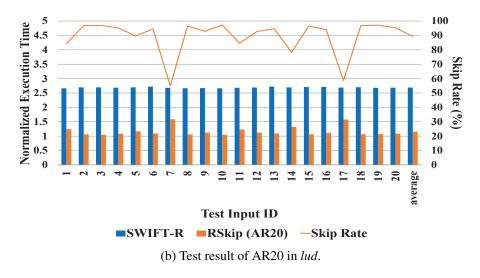

| 5.6 | Test result with test inputs of each benchmarks (AR : Acceptable Range)        | 89 |

| 5.7 | Test result with test inputs of each benchmarks (AR : Acceptable Range)        | 90 |

| 5.8 | The detailed analysis for two selected benchmarks                              | 91 |

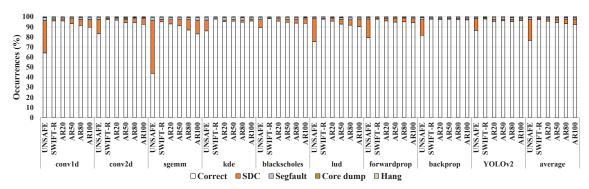

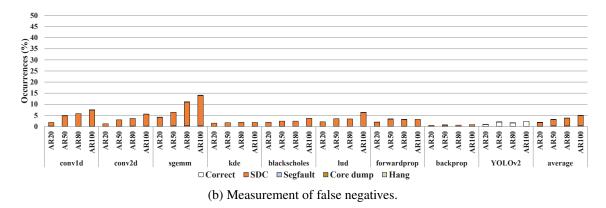

| 5.9 | The result of the fault injection experiment. Each protection scheme is tagged |    |

|     | under every application.                                                       | 92 |

# LIST OF TABLES

| 2.1 | A subset of features for loop unroll decision under different categories. The<br>ratio of each static operation is computed by dividing the number of each op-<br>eration by the number of static instructions. Note, unavailable features (e.g., |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | live range size) in our infrastructure are crossed out. The total of 34 features are extracted and used for the experiment.                                                                                                                       | 19 |

| 2.2 | Configurations for the classifiers. Annotated (*) configurations are generated without any restriction on both the maximum depth and the maximum number                                                                                           |    |

| 2.3 | of leaf nodes                                                                                                                                                                                                                                     | 22 |

|     | random forest configurations are represented by their largest configurations                                                                                                                                                                      | 27 |

| 2.4 | Top 15 features for decision tree. Check marks ( $\checkmark$ ) indicate that the corresponding features are considered in the current heuristic design: 8 out of the top 15 features are employed by current heuristics.                         | 29 |

| 3.1 | Experiment setup                                                                                                                                                                                                                                  | 49 |

| 3.2 | GPU specification. We consider RTX 2080 Ti and Quadro K620 as high-end and low-end devices respectively.                                                                                                                                          | 55 |

| 5.1 | Selected benchmarks. The impact of skipping re-computation can be imagined<br>by provided computation type and location. Both training input and test input<br>are randomly generated or selected without any intersection                        | 86 |

# ABSTRACT

To deliver the best performance to users, modern compilers apply hundreds of optimizations that transform a program into a more efficient form. Since a program execution is a complicated process of the delicate interplay between software and hardware, each compiler optimization should be carefully determined with consideration for its trade-offs to benefit from the corresponding code transformation. Today, most of the important optimization decisions are made by hand-crafted heuristics which often largely depend on the developers' expertise. However, as the complexity of both software and hardware continues to increase, performance analysis often overly simplifies the interactions between diverse system components and cannot capture system characteristics accurately. As a result, current human-made heuristics generally fail to achieve maximum performance. In the era of limited processor performance gains, this loss is becoming more significant. Furthermore, a huge amount of time and cost need to be repeatedly invested for this manual tuning process whenever one of the system components is updated.

To attack these challenges, this thesis proposes a suite of automatic methods that can successfully improve optimization decisions inside state-of-art compilers by effectively exploiting the knowledge acquired during previous executions. Various representative compilers from diverse domains are investigated with different backends.

First, the decision for a single optimization is investigated. By focusing on *loop unrolling*, which is one of the most representative compiler optimizations, the first part of this thesis suggests a methodology that automatically constructs the best affordable decision model for the dynamic binary translator in mobile system. By effectively learning the patterns between optimal decisions and workload features from the training dataset, this method significantly outperforms the best heuristics handwritten by industry experts by saving  $1.5 \times$  dynamic instructions.

Next, a group of optimizations is considered. To identify the best use of existing optimizations, the second work of this thesis proposes an intelligent pure search method, called *SRTuner*, which customizes effective optimization settings for each workload by exposing important inter-optimization relations. Results show that SRTuner accelerates target executions upto  $34.4 \times$  compared to the highest level of optimization provided by each compiler while outperforming prior state-of-the-art tuning methods. As a byproduct of its unique tuning strategy, SRTuner offers synergistic optimizations which can benefit future tuning strategies.

The third work of this thesis proposes *Collage* which is an auto-tuning system that attacks the practical problem of identifying the best mixed use of diverse backends to efficiently run deep learning workloads on their target devices. The experimental results demonstrate that this system efficiently customizes fast execution strategy that outperforms the hand-written strategies in the existing deep learning frameworks by  $1.3 \times$  by investing a short amount of tuning time.

Finally, the last work investigates the field of reliability and suggests *RSkip* which provides a cost-efficient protection scheme for a transient fault. By leveraging the trade-off between its overhead and protection rate, RSkip optimizes the protection scheme by creating an approximate copy of the program that will be used to detect a potential fault. With a control for the loss in the protection rate, RSkip could reduce protection cost by  $1.83 \times$ .

The contributions in this thesis improve future optimization decisions in state-of-thearts compilers by searching for the right use of existing optimizations for each workload and hardware devices and identifying the pattern between good optimization settings and workload characteristics. By delivering better optimizations settings, users can enjoy better performance by better utilizing their underlying hardware.

# **CHAPTER 1**

# Introduction

# 1.1 Introduction

The main mission of a compiler is to transform a program into its best form for the target system by applying hundreds of various optimizations. Since a compiled program will be running on the top of multiple system layers, various interactions between components should be considered to make optimal optimization decisions. For example, *loop unrolling* is a representative compiler optimization that can increase both instruction-level parallelism and optimization window at the cost of certain degree of code bloat. As its actual impact is the combined effect of both advantage and disadvantage from the optimization, loop unrolling may harm performance when it is too aggressively used in the system with restricted memory like embedded system. However, when the increased optimization window can significantly benefit later optimizations or underlying hardware supports high level of instruction parallelism, even embedded system can achieve significant improvement with aggressive use of loop unrolling. Therefore, optimization should be carefully configured depending on the situation for its right use.

Today, such optimization decisions in modern compilers mostly rely on heuristic decision models hand-crafted by system developers [149, 70]. To construct an effective model, developers often conduct performance analysis to capture system characteristics and estimate the impact of an optimization. Although such the manual approach may be feasible, it inevitably requires an expert level of understanding towards the overall target system and a huge amount of person-hours. Given that these non-trivial manual efforts need to be repeatedly invested to reflect any update among the system components, heuristic-based approach can be highly resource-intensive and time-consuming. This may become a serious problem for the fast evolving domain like deep learning. Furthermore, due to the increasing complexity and diversity of the both hardware and software, it gets much harder to model system characteristics accurately. An optimization may have different impact depending on

Figure 1.1: Growth of computer performance using SPECintCPU benchmark suite [78]. The end of Dennard Scaling and Moore's Law slows down the performance improvement with hardware innovations. Annotation (star) indicates where we stand today in 2020.

the target hardware, application, or input. On the top of that, various interactions with other optimizations add severe difficulty in performance analysis. As a result, even system experts often overly simplify system characteristics, which leads to the sub-optimal optimization decisions. Stephenson and Amarasinghe reported that a heuristic decision model in Open Research Compiler (ORC) makes optimal decisions only 16% of the time [149]. Also, even the most naive tuner easily outperforms the highest optimization setting in GCC by 11% [70]. These performance losses can be critical since squeezing the last drop of performance actually matters. At the data center scale, 1% of performance improvement can save significant amount of operation cost and there are explosive demands for faster deep learning execution from various domains. Besides, as Figure 1.1 illustrates, two digits of yearly performance gain became almost impossible to expect from hardware improvements due to the end of Dennard Scaling and Moore's Law. Therefore, delivery of better optimization decision is becoming more crucial.

To attack this lack of efficiency, we consider an alternative. To take humans out-of-theloop and maximize performance, researchers have suggested diverse compiler auto-tuning methods [149, 70, 32, 89]. By exploiting information acquired from previous executions, these auto-tuning approaches improve the future execution. *Iterative compilation* is one of such tuning approaches [42, 90, 124]. Within the limited trials, iterative compilation techniques try to identify the best possible configurations of a set of optimizations for the target program. For example, GCC provides classic one-size-fits-all approaches with standard optimization levels (e.g., -O3) that essentially applies fixed configurations of a set of optimizations for every situation. Prior works have demonstrated that iterative compilation methods can customize better configurations that outperform the most aggressive performance-oriented standard optimization for each situation. To generate promising candidates during a tuning process, these techniques equip diverse strategies of utilizing feedback, such as random search [70], genetic algorithm [68, 83], statistical methods [124, 119]. As machine learning techniques are demonstrated to be very powerful at recognizing the pattern and drawing decision boundaries in multi-dimensional space, various learning-based approaches have been also examined for the the effective use of the prior executions. For instance, Stephenson and Amarasinghe showed that machine learning classifiers can be adopted as a decision model for a single optimization by defining an optimization decision as a classification problem [149].

Inspired by prior approaches, this thesis endeavors to expand the applicability of autotuning technologies by examining complicated optimization decision problems in various representative compilers from diverse domains with different back-ends. Depending on the problem, the feasibility of diverse machine learning concepts and techniques is also investigated.

# **1.2** Challenges and Contributions

This thesis suggests a suite of auto-tuning methods that can effectively improve various optimization decisions inside modern compilers. To demonstrate their effectiveness, state-of-the-arts compilers from different domains are examined with diverse target hardware architectures.

#### 1.2.1 Feasibility Study of Learning-Based Auto-Tuning Methods

To assess feasibility of learning-based auto-tuning, we examine the dynamic binary translator for mobile processor that has hard constraints to satisfy [121]. As memory resources are quite limited in mobile processor, there exist couple of budgets allowed for each optimization in dynamic binary translator. Also, since optimization will be dynamically applied during translation at run-time, each optimization should be completed within certain time limit. Therefore, an optimization decision model for the target system has to be fast and lightweight. Chapter 2 describes how the best affordable decision model can be automatically constructed by supervised learning for a single optimization in this system with tough restrictions. Its performance is evaluated with the hand-crafted heuristics designed by industry experts.

#### 1.2.2 Customization for a Group of Compiler Optimizations

To deliver the optimization setting, state-of-the-arts compilers offer several standard optimization levels, which are a few fixed set of optimization settings under the hood. As the complexity of both hardware and software systems continuously increases, these one-for-all approach cannot deliver the maximum performance anymore. Despite the obvious opportunity, finding the best use of existing optimizations is known to be highly difficult due to the vast search space and the presence of inter-optimization relations. To tackle down this challenge, Chapter 3 suggests *SRTuner* which customizes the competitive optimization setting by efficiently revealing the interaction between optimizations and using them for the effective tuning process. Due to its unique approach, this method can provide important synergistic optimizations for the given workload at no extra cost. This chapter also discusses how this information can benefit future compiler optimization design and auto-tuning studies.

#### **1.2.3** Search for the Best Use of Diverse Backends

Strong needs for the powerful platform for the efficient Deep Learning (DL) execution has driven rapid evolution in various software backends. These backends include optimized library (e.g., cuDNN, cuBLAS), which provides efficient operator kernels, and inference engines (e.g., TensorRT), which offers a run-time to execute the deep learning models and apply various graph-level cross-kernel optimizations. To extract the best performance, it is key to use the right backend for each case given the strength and weakness of each backend. However, it is difficult to capture the full capabilities of diverse backends with different characteristics. Complex fusion patterns from advanced fusion engines add the complexity. Furthermore, tuning process is not easy since both topology of DL workload and the coverage of each backend should be considered together to find the legitimate candidate of execution plan with multiple backends. As a breakthrough, Chapter 4 proposes *Collage*, which is the auto-tuning system that efficiently customizes the optimal execution strategy with diverse backends. To fully leverage the capability of each unique backends, this system provides the seamless user interface that supports flexible description of pattern rules that each backend follows. For the effective search, this system adopts two-level tuning approach. By ignoring the cross-kernel optimizations in the inference engines, the first level tuner could introduce dynamic programming with efficient cost model that can customize the near-optimal execution plan for the real-life deep learning models within a few seconds. Then, based on the plan created by the first tuner, the second tuner provides the fine-tuning opportunity that makes up for the potential loss from the relaxation regarding the graph-wide optimizations.

#### **1.2.4** Provision of Low-Cost Fault Protection

Increasing failures from transient faults necessitates the cost-efficient protection mechanism that will be always activated. To provide a low-cost software-level protection, Chapter 5 propose a novel prediction-based transient fault protection strategy. Instead of re-executing expensive computations for validation, an output prediction is used to cheaply determine an

approximate value for a sequence of computation. When actual computation and prediction agree within a predefined acceptable range, the computation is assumed fault-free, and expensive re-computation can be skipped. With this approach, a significant reduction in dynamic instruction counts is possible. As missed faults may occur, it is crucial to explicitly keep their occurrences to a small amount by adjusting an acceptable range and aggressiveness of approximation techniques properly. Therefore, with the suggested prediction-based scheme, this work also discusses how to control them accordingly.

#### **1.3 Background**

#### **1.3.1** Compilers From Diverse Domains and Their Optimizations

To deliver the most efficient form of binary executable for the given workload and underlying hardware, various compiler stacks have been developed. GCC [21] is one of the most popular state-of-the-arts compilers that provides hundreds of code transformation and analysis passes to optimize C/C++ programs for CPUs. As CPUs aim for the effective general purpose computing, this compiler offers a wide collection of optimizations, such as redundant code eliminations, control flow/data flow optimizations, vectorizations, parallelizations, loop optimizations, and etc [19]. LLVM [22] is another popular compiler technology that is broadly adopted in both industry and academia. By providing the seamless modular design, compiler engineers can easily customize their own compiler and optimizations with LLVM. Likewise, this compiler also equips diverse code transformation and analysis passes [24]. Beyond the powerful CPU support, LLVM recently has started the GPU support [23, 25].

To seek for the optimization opportunity by leveraging the run-time information, the concept of Just-In-Time (JIT) compilation is proposed [94, 84]. Once the hot path is identified during the program execution, a JIT compiler may invest certain compilation overhead to dynamically re-compile this important code region with the run-time observations and extract the further performance gain. These dynamic information may help compilers to make more accurate optimization decisions by providing the run-time context. While using interpreter to offer the fast response time, most Virtual Machines (VMs) adopt the JIT compilation to complement its relatively less efficient quality of generated code [26, 27]. Binary translator [43] also employs the dynamic optimization to improve the translation quality at runtime.

Unlike CPU programs, which require careful handling of the complicated control dependencies, GPU mainly targets data-intensive programs with simple control flow. To promptly process the large volume of data in parallel, modern GPU architectures have thousands of computing units in a number of Stream Multiprocessors (SMs) and the efficient utilization of their resources is key to extract the peak performance. To do so, the amount of computation should be well distributed to SMs in the target GPU with the careful consideration for its memory architecture. To attack this problem, advanced GPU compilers offer several optimizations, such as loop tiling, loop unrolling, and data layout transformation [128, 55, 117, 116].

OpenCL compilers have endeavored for the effective heterogeneous computing and the performance portability across a wide range of hardware devices with different design philosophy. By mainly targeting important computations, such as BLAS kernels, they apply various optimizations for data-intensive workloads, including loop tiling and loop unrolling [116, 117].

To provide the powerful platform for Deep Learning (DL) workloads, various DL frameworks have been actively developed. TensorFlow [10], PyTorch [9] and TVM [55] are the representative examples. By targeting a wide range of hardware devices, including custom accelerators [2, 1], these framework apply graph-level optimizations on the top of the conventional compiler optimizations. For instance, computation graph of the DL workload may be rewritten in the more efficient form as long as the correctness of program is guaranteed. Operator fusion [6, 115, 55] is also a powerful optimization technique that merges multiple kernels to improve memory usage and scheduling overhead. To automatically generate an effective operator kernel, TVM provides a template implementation of each operator with various optimizations, such as loop unrolling, loop tiling, and etc. When targeting accelerators, users may also consider tensorization to fully utilize their custom hardware.

#### **1.3.2** Compiler Auto-Tuning

As modern compilers generally provide manifold optimization/analysis passes, it is known to be highly challenging to identify the best use of existing optimizations. Both the impact of a single optimization and the interaction between optimizations would be different depending across workloads and hardware devices, which adds the complexity of the problem. Thus, to extract the maximum performance for the workload, compilers often need to find out the best combination of optimization decisions [32, 56, 42, 89], the optimal ordering between optimization passes [93, 96, 95, 60], and the best use of various backends, such as optimized libraries (Figure 1.2). To attack these problems, one of the most popular methods adopted in the current state-of-the-arts compilers is to provide standard optimization levels, which is essentially a few set of fixed optimization settings hand-tuned by system experts. However, due to the increasing complexity of both hardware and software system, this approach cannot deliver the best performance to users anymore by making sub-optimal decisions for many occasions [121, 108, 70].

As a breakthrough, various auto-tuning techniques have been proposed [32, 56, 101,

Figure 1.2: Representative tuning problems

108, 70, 121]. Largely, these technologies can be classified into two groups (Figure 1.3): (1) workload-specific tuning: This approach explores the large and complex optimization space by investing separate tuning time to customize the best possible optimization decisions for the given workload. Pure search methods [32, 90, 68, 119] is one of the representative examples that navigates the search space by only using the feedback acquired during the tuning process without any prior information, such as the cost model and prior tuning experiences. (2) generalization: This approach tries to recommend the good optimization settings for the unseen workload without the expensive investment of tuning time. By learning the relationship between the workload features and its customized optimization settings in the training dataset, these techniques can provide more flexible optimization settings efficiently [70, 34, 121, 75]. A high quality of training data is necessary for the effective training and thus, generalization methods often adopt the pure search methods to prepare their data.

In general, workload-specific tuning is not cheap and most of its tuning overhead is from the repetitive run-time evaluations that include compilation and run-time measurement. To alleviate the cost, researchers often introduce the hardware cost model which can approximate the performance of an optimization setting without the actual measurement on the hardware. However, due to the high complexity of the computing system, it is not easy to construct the effective cost model by hand. To resolve this issue, the idea of learning-based approach has been proposed [56, 28]. By utilizing the run-time samples acquired during the tuning process, this approach automatically constructs the effective hardware cost model.

Figure 1.3: Representative tuning approaches

To maximize the efficiency, these methods often support transfer of the cost model across different tuning jobs.

To respond to high demands for the faster platform for DL workloads, there has been various active studies to fine-tune their executions. To automatically create the competitive implementation of DL operators, TVM offers two different auto-tuning technologies. If users want to customize the optimization settings within their manually defined search space, AutoTVM [56] can be used. Otherwise, Ansor [167] may be considered to traverse broader space with a hierarchical representation of the program. TVM also provides a graph tuner that optimizes layout transformation for CPU workloads [55]. By leveraging a set of re-writing rules, graph re-writing methods, such as TASO [85], explore the promising variants of the computation graph of the given workload to identify the best form for the underlying environment (e.g., hardware, compiler). For the efficient evaluation of each candidate, these methods often adopt the simple heuristic of cost model.

To construct the effective generalization model [121, 70, 34] by reusing the past tuning experience, it is key to have a high quality of training data that consists of workload features and their effective customized optimization settings as the ground-truth. As previously discussed, optimization settings can be automatically identified by various pure search approaches. For the effective learning, feature selection is crucial for the accurate workload characterization to provide important information that is necessary for the optimization decisions. Thus, to identify the key information for optimizations, it is often useful to understand which applications are similar from an optimization perspective. Although there

have been manual approaches that rely on the expert's insight [70, 34], this is generally known to be extremely challenging. To avoid difficulty of manual feature selection, compiler researchers have proposed automatic feature generation techniques [97, 98]. By navigating the given search space, these methods examine the impact of each feature and choose the ones with high importance.

The comprehensive survey for auto-tuning domain is well presented by Ashouri et al. [33].

# **CHAPTER 2**

# Multi-objective Exploration for Practical Optimization Decisions in Binary Translation

# 2.1 Introduction

Today, many important optimization decisions are made by heuristics, which often depends on the developers' expertise. With an expert level of understanding of the system and a huge amount of effort, programmers can create effective models that capture architectural characteristics [163]. However, due to the increasing complexity of architectural design, it becomes much harder to build effective human-made models. Additionally, the subtle interactions between software optimization phases add to the exploration space. As a result, heuristics often fail to make good decisions. Stephenson and Amarasinghe showed that the loop unrolling heuristics in Open Research Compiler (ORC) only achieve 16% prediction accuracy for optimal unroll factor [149].

To make effective optimization decisions, researchers build decision models by applying machine learning techniques [149, 110, 51, 150]. Particularly, given its system-wide impact, researchers have studied how to improve the optimization decision for loop unrolling. By relaxing loop-carried dependencies, properly applied loop unrolling can increase Instruction Level Parallelism (ILP) and bring more opportunities for subsequent optimization phases, resulting in significant performance improvement. However, it may cause code bloat or large numbers of register spills when it is applied too aggressively. For the best use of loop unrolling, Stephenson and Amarasinghe suggested defining loop unroll factor prediction as a classification problem [149]. By employing supervised classification techniques, they successfully improve prediction accuracy as well as loop performance over a baseline heuristic. These previous works are built by using statically known information and inserted into a static compiler. Since they target a static compiler, the overhead (computation and memory) of the built model is not considered.

On the other hand, hardware/software (HW/SW) co-design has been extensively studied

for mobile and embedded systems to achieve better performance or reduce design cost [37, 160, 12, 159]. A DBT system is a key component in such a co-design process. Since the DBT system conducts optimization during translation [43], the optimization decision has a direct impact on the quality of the translation. Thus, smart optimization decisions are necessary to provide high translation quality. To make better decisions, we examine an approach to tailor machine learning optimization decision models for a code optimizer in DBT. Particularly, we target a mobile processor that supports high-performance applications but still operates in a constrained environment (e.g., a mobile processor for an autonomous vehicle). Unlike previous works [149, 110, 97] in a static compiler, the prediction overhead (e.g., memory usage, performance overhead, and energy consumption) of a decision model may restrict the usage of a complex or large decision model in the mobile system.

As the first step, we choose *loop unrolling* as a representative optimization and investigate five different multi-class classification techniques and their diverse configurations to build its effective decision model. Note, this work focuses on the single optimization decision while leaving the decision for a group of optimizations for Chapter 3. This is also a multi-objective exploration observing the relationship between prediction overhead and accuracy. We build our approach with the industrial strength DBT infrastructure. Our code optimizer has an optional optimization for loop unrolling, called *smart unrolling*, that can remove redundant branches [107]. Since smart unrolling can have performance side effects, the built model must make an additional decision on whether to apply smart unrolling. Furthermore, unlike previous works [149, 110, 97] in a static compiler, some useful but expensive analyses like dataflow analysis (DFA) may not be available due to their high overhead in binary translation. Instead, new opportunities to utilize dynamic information (e.g., loop trip count, taken probability of side exits) collected during runtime are studied. These turned out to be important features for unroll factor classifiers.

For experiments, we collected 17,116 unrollable loops from 200 real-life programs and benchmarks in various domains. By employing all available features that might be crucial for loop unrolling decision, we suggest the best classification algorithm for our infrastructure given both prediction accuracy and cost. Then, we identify its significant features to prune the feature set and evaluate the model built by using selected important features. As a result, the best affordable classifier that is within the memory/time budgets for the decision process shows a 74.5% of prediction accuracy for optimal unroll factor and realizes an average 20.9% reduction in dynamic instruction count during the steady-state translated code execution when the ideal upper bound for instruction reduction is 23.8%. For comparison, the best current heuristic shows a 46.0% prediction accuracy with an average of 13.6% instruction count reduction.

The major contributions of this work are as follow:

- We show how machine learning techniques can improve loop unrolling decisions for dynamic binary translation on the mobile processor, which is a more challenging environment than static compilers used in previous works [149, 110, 97]. The demanding environment requires a more careful model selection with multiple objectives considered which is not necessary for a static compiler. New opportunities to employ dynamic information is also examined. This approach is instruction set independent and can be extended to other optimization decisions.

- We investigate the relationship between prediction overhead (i.e., time, memory) and accuracy for diverse classification algorithms and their different configurations. As a result, the best classification algorithm is discovered. Then, by applying feature space pruning technique, we provide its major features and suggest the best affordable decision model for our infrastructure given the specific budgets allocated for the decision process.

- We compare the current heuristics in the industrial strength infrastructure and the proposed machine learning based approach. Given that the infrastructure is already highly optimized, the heuristics are well crafted and provide a challenging baseline for comparison.

# 2.2 Background

## 2.2.1 Our Infrastructure with Binary Translation

Figure 2.1 sketches our HW/SW co-designed CPU. Although this CPU only accepts the binary code written in x86, it incorporates a hidden microarchitecture that supports additional Instruction Set Architecture (ISA) internally. By having a DBT system that translates legacy code into internal ISA and orchestrates execution between two different architectures, the internal ISA and its architectural design can stay invisible from the outside and be innovated without worrying about backward compatibility. To manage program execution, our infrastructure employs the region-level atomic execution similar to [154]. The dynamic binary translation system profiles the execution and constructs optimization regions to translate x86 instructions in the hot traces into internal ISA instructions that will be executed on its optimized microarchitecture. To maximize the performance benefit, it is crucial to produce a high quality of translated code. Therefore, during translation, the dynamic optimizer applies various code optimizations [154], including loop unrolling, to improve the translation quality.

Figure 2.1: Big picture of our HW/SW co-designed CPU with a DBT system. It constains two different microarchitectures that each supports its own ISA. The highlighted box illustrates the translation process by a binary translator and a dynamic optimizer.

# 2.2.1.1 Target Loops

- Reducible (Single entry) loop.

- Innermost loop. The outer loop is only considered when the innermost loop is fully unrolled.

- Both *counting* and *non-counting* loops with a loop invariant trip count [59].

# 2.2.1.2 Smart Unrolling

Our dynamic optimizer has an aggressive version of loop unrolling which is an optional optimization when loop unrolling is enabled. By targeting counting loops, the technique tries to transform the loop structure and exit condition to minimize the number of branches [107]. For example, the optimization can eliminate loop exit branches in copies of a loop body. Also, the optimization phase inserts a run-time check outside of the loop to prevent exceptions (e.g. overflow).

Smart unrolling can have side effects. When the run-time check fails, deoptimization will be triggered to revert the code and degrade the performance. Also, applying smart unrolling to a loop with a low trip count may result in performance degradation due to the overhead of the transformed structure. Thus, smart unrolling should be applied carefully to realize performance improvement.

# 2.2.1.3 Current Heuristics

There are two unrolling heuristics in our dynamic optimizer: *Optimistic* and *Conservative*. By default, *Optimistic* is used to optimize identified hot traces. When speculation with

*Optimistic* fails repeatedly [61], *Conservative* is used to generate optimized code with less aggressive optimization. Both heuristics make a decision based on identical information such as trip count, the expected number of post-unroll instructions, etc. The only difference between the two is two parameters: the maximum number of post-unroll instructions and the maximum unroll factor. *Conservative* has lower values than *Optimistic*. Each heuristic predicts an unroll factor that is lower than its upper limits. The maximum unroll factor is set to 8 for *Optimistic* and 4 for *Conservative*, respectively. Also, although smart unrolling may have side effects, current heuristics always apply it on counting loops with the optimistic expectation.

## 2.2.2 Supervised Multi-class Classification

Supervised classification is a process identifying which set of classes (or labels) a new observation belongs to, based on the learning from training data. This section describes five representative classification techniques as background to deliver their main concepts with the pros and cons.

#### 2.2.2.1 k-Nearest Neighbors (kNN)

kNN classifies a new observation based on the majority voting from k number of closest neighbors in training data. The idea is straightforward: find the most similar case from the training database and assign the same label to the new observation. Thus, in our case, kNN will search the most similar loops from the training data and assign the dominant label among them. Without having any form of generalization process on training dataset, training data will be saved and populated directly during the inference. Since kNN scans data points in the training set to find the closest neighbors, its prediction cost is proportional to the size of the training data set. Also, its learned model is unable to be interpreted and give any intuition to the system designers.

## 2.2.2.2 Support Vector Machines (SVM)

SVM makes a classification based on the decision boundaries. During training, the technique constructs decision boundaries that separate the training data points. Rather than focusing on minimizing prediction errors on the training set, it tries to minimize the expected generalization loss based on the probabilistic assumption for unseen data. Naturally, SVM is resistant to overfitting [138]. To divide data points under different classes while minimizing the generalization loss, SVM chooses each decision boundary that is farthest away from the observed training data among all possible boundaries. Thus, each selected decision boundary is also called the *maximum margin separator* and the points closest to the separator is called *support vector*. However, it takes a long time to train this model and the learned

model is not comprehensible. Fundamentally, *SVM* manages multiple two-class decision boundaries to conduct multi-class classification. Therefore, the prediction cost may become expensive as the number of boundaries increases.

## 2.2.2.3 Decision Tree

A decision tree is a function that makes a decision by conducting a sequence of tests [138]. Each node in a tree checks the value of one of the input features and guides to the next node until the final decision at the leaf node. During training, a decision tree learns what will be tested at each node. If a feature is numerical, the threshold will also be determined for each node. Fundamentally, the decision tree consists of nested conditional statements. Therefore, unlike other machine learning techniques, the learned model is able to be interpreted and easy to visualize. This is a noteworthy property in the sense that the learned model can give system designers insights that they may have been missing. In addition, the worst case for the prediction cost is proportional to the maximum height of the tree. Note, the computation at each node is quite cheap since it is usually just a simple comparison. Thus, if it is able to build an effective tree with the control of the maximum height, the model can be highly practical. However, the technique may suffer from overfitting.

## 2.2.2.4 Random Forest

Random forest manages a multitude of decision trees and makes a prediction by aggregating the predictions from trees in the forest (e.g., majority voting). Since the random forest is essentially a group of decision trees, the learned model is also easy to visualize and is able to give information about the relation between the feature set and the prediction. In general, the technique is able to convey high accuracy and efficiently handle a large dataset with high dimensionality of feature space. Also, the estimate of generalization loss will be computed during training, which can be used to enhance overfitting. However, when the forest grows a multitude of large trees in parallel, it may require a lot of memory [100]. This may cause an overhead to the memory system and increase the inference time affecting the translation time in our case.

## 2.2.2.5 Artificial Neural Network (ANN)

ANN is a learning method that mimics the brain activity mathematically. The model consists of multiple layers: an input layer, hidden layers, and an output layer. Each layer contains a large number of neurons and each neuron is connected to other neurons in the other layer. In this work, a fully-connected network, whose each neuron is connected to all neurons in the next layer, is assumed. In general, the neural network is known for its outstanding classification accuracy compared to the traditional learning techniques. However, it may

Figure 2.2: Distribution of optimal unroll factors.

need a large network and a large training dataset to achieve satisfactory accuracy [165]. The inference can be very compute-intensive, particularly with a large network. In addition, the decision-making process is like a "black box" so that the internal mechanism would hardly give any intuition to the system designers.

# 2.3 Motivation

Our current DBT system employs heuristic-based decision models designed by industry experts. Given the difficulty of creating effective models that describe subtle interaction between optimization phases while satisfying hard environmental constraints, we notice the pitfall that may exist: hand-made heuristic models might be biased by the designer's experience or insight. Therefore, we recognize the need to not only evaluate their effective-ness, but also develop the automatic and systematic approach to building decision models to lessen the burden required for their design process (e.g., analysis, tuning). Without an automatic method, system designers may need to repeatedly invest a huge amount of efforts to tune their optimization decision whenever other system component(s) are updated.