### Upgrades of the ATLAS Muon Spectrometer Front-end Electronics for the High-Luminosity LHC

by

Xiong Xiao

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Physics) in the University of Michigan 2022

**Doctoral Committee:**

Professor Junjie Zhu, Chair Professor Myron Campbell Associate Professor Thomas Schwarz Professor Zhengya Zhang Professor Bing Zhou Xiong Xiao xiongx@umich.edu ORCID iD: 0000-0002-1344-8723

© Xiong Xiao 2022

### ACKNOWLEDGMENTS

First of all, I would like to express my sincere thanks and greatest gratitude to my advisor Professor Junjie Zhu for guiding me through my Ph.D. study. He has always made himself available if I need help. Without his knowledgeable advice and encouragement, I could not have made it to this step. I would also like to express my deepest gratitude to Professor Bing Zhou for providing many supports on my research.

Working in the University of Michigan ATLAS group has been an honor. I would like to thank Professors Thomas Schwarz, Dante Amidei, John Chapman, and Jianming Qian for the discussion, comments, and suggestions during group meetings.

I want to give my thanks to Jinhong Wang who brought me to the world of ASIC. I want to thank Yu Liang for letting me know how powerful I am. I thank Xueye Hu who is always willing to offer helps to me. I also want to thank Yuxiang for working together on the TDC project.

I want to thank Liang Guan for sharing his expertise on detectors and his selfless help. I also want to thank Siyuan Sun for teaching me how to fight for myself. I want to thank Man Yuan for the days and nights we were waiting for cosmic muons. I would like to thank Artur Coimbra for offering supports for the cosmic ray test station. I am grateful to Tiesheng Dai for helping me set up my computing desktop. I would also like to thank the other group members in the sTGC I&C team and they are Xu, Rongkun, Prachi, Andy, Bobby, Billy, Jinglu, Nicholas, Xinmeng.

Last, I want to thank my parents for their unselfish support.

# **TABLE OF CONTENTS**

| A  | CKNO                                          | LEDGMENTS                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Ll | ST OI                                         | FIGURES                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| LI | LIST OF TABLES                                |                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| LI | ST OI                                         | ABBREVIATIONS                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| A  | BSTRA                                         | CT                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| C  | HAPT                                          | R                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 1  | Intro                                         | uction                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 2  | Larg                                          | Hadron Collider and the ATLAS Detector                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|    | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | The Large Hadron Collider4The ATLAS detector52.2.1 The ATLAS coordinate system72.2.2 The ATLAS trigger and data acquisition system8The Muon spectrometer82.3.1 Monitored Drift Tube chamber112.3.2 Cathode Strip Chamber122.3.3 Resistive Plate Chamber132.3.4 Thin Gap Chambers14 |  |  |  |  |  |  |

| 3  | Upgr                                          | des of the ATLAS Muon Spectrometer                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|    | 3.1<br>3.2<br>3.3                             | ntroduction15The Phase-I upgrade163.2.1Motivation of the New Small Wheel detector163.2.2Structure of the New Small Wheel detector183.2.3Electronics of the New Small Wheel detector21The Phase-II upgrade25                                                                        |  |  |  |  |  |  |

|    |                                               | 3.3.1First-Level Muon Trigger with MDT chambers263.3.2The Phase-II MDT Electronics28                                                                                                                                                                                               |  |  |  |  |  |  |

| 4  | The l                                         | nase-I Upgrade: sTGC Front-end Electronics                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|    |                                               | VMM                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|   | 4.3<br>4.4                                    | 4.3.1       Pad TDS                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>34<br>35                               |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 5 |                                               | Phase-I Upgrade: sTGC Mini-DAQ System                                                                                                                                                                                                                                                                                                                       | 39                                                 |

|   |                                               | Mini-DAQ FPGA Firmware                                                                                                                                                                                                                                                                                                                                      | 39<br>40<br>48<br>49<br>51<br>54                   |

| 6 | The                                           | Phase-I Upgrade: sTGC Trigger Chain Front-end Electronics Commissioning                                                                                                                                                                                                                                                                                     | 55                                                 |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | sTGC Front-end Electronics Integration and Commissioning procedureOn-bench FEB Trigger Chain Reception Test6.2.1 On-bench pFEB Trigger Chain Automatic Test Flow6.2.2 Clock phasesOn-wedge Trigger Chain Connectivity Test6.3.1 pFEB to Pad trigger board6.3.2 sFEB to Router board6.3.3 Pad Trigger Board to sFEB6.3.4 Cosmic ray hit map with the CO2 gas | 56<br>57<br>57<br>58<br>68<br>69<br>70<br>71<br>72 |

|   | 6.4                                           | Result Summary                                                                                                                                                                                                                                                                                                                                              | 72                                                 |

| 7 | The 2                                         | Phase-I Upgrade: sTGC Cosmic Ray Study                                                                                                                                                                                                                                                                                                                      | 76                                                 |

|   | 7.1                                           | Setup                                                                                                                                                                                                                                                                                                                                                       |                                                    |

|   | 7.3                                           | sTGC Pad in the Trigger Chain7.3.1 Mapping Verification7.3.2 S-curve7.3.3 Efficiency7.3.4 Timing Performance                                                                                                                                                                                                                                                | 91<br>91<br>92<br>92<br>94                         |

|   | 7.4                                           | Logical pad and sTGC strip in the Trigger Chain                                                                                                                                                                                                                                                                                                             | 100<br>104<br>105                                  |

| 8  | The l                                                                       | Phase-II                                                         | Upgrade: MDT Front-end Electronics      | • •                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | • |                                       |                                       | • •                                   | 113                                           |

|----|-----------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------------|

|    | 8.1<br>8.2                                                                  |                                                                  | MDT Electronics                         |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | • |                                       |                                       |                                       | 114                                           |

|    |                                                                             | 8.2.2                                                            | The Mezzanine card                      |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | • |                                       |                                       |                                       | 117                                           |

| 9  | The                                                                         | Phase-II                                                         | Upgrade: Development of the MDT TDC ASI | С                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |   |                                       |                                       |                                       | 122                                           |

|    | <ul> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> </ul> | The Art<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>Fabrica<br>Design | ations for the MDT TDC ASIC             | · · · · · · · · · · · · · · · · · · · | <ul> <li>.</li> <li>.&lt;</li></ul> | · · · · · · · · · · · · · · · · · · · |   | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | 124<br>124<br>126<br>133<br>134<br>136<br>137 |

| 10 | Conc                                                                        | lusion                                                           |                                         |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | • |                                       |                                       |                                       | 143                                           |

| AP | PENI                                                                        | DIX                                                              |                                         |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | • |                                       |                                       |                                       | 145                                           |

| BI | BIBLIOGRAPHY                                                                |                                                                  |                                         |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |   |                                       |                                       |                                       |                                               |

# **LIST OF FIGURES**

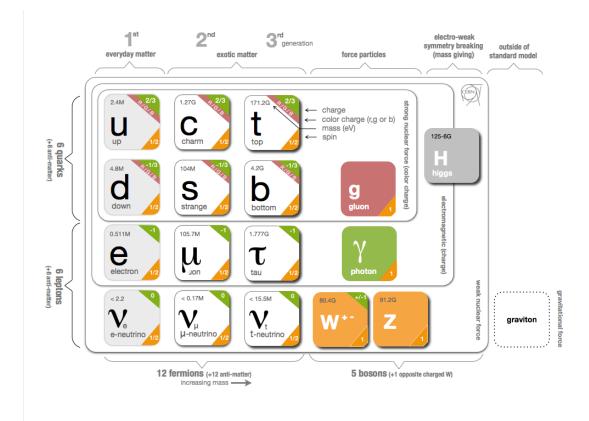

| 1.1  | Summary of all elementary particles [2]                                                                  | 2  |

|------|----------------------------------------------------------------------------------------------------------|----|

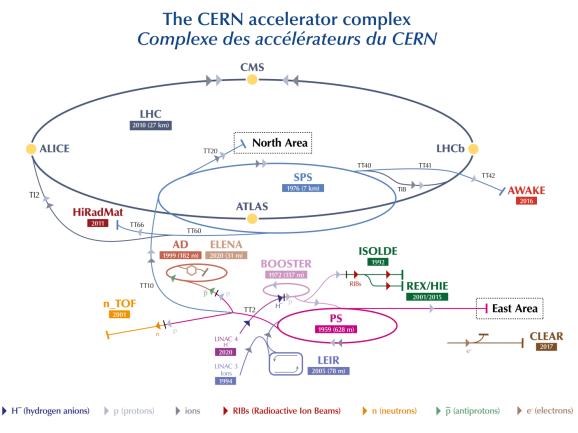

| 2.1  | The CERN accelerator complex [19].                                                                       | 5  |

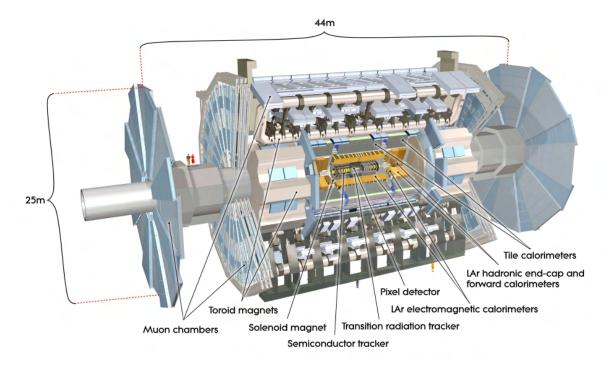

| 2.2  | A view of the ATLAS detector [15].                                                                       | 6  |

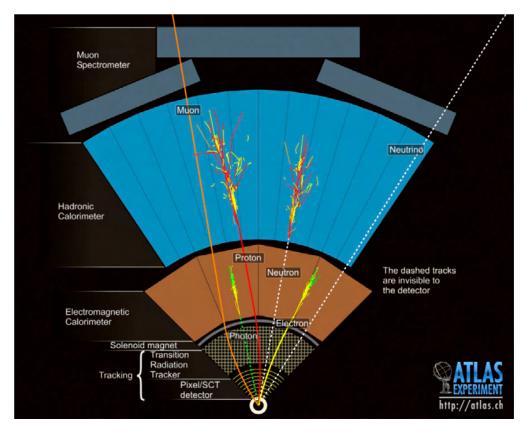

| 2.3  | Simulated detector responses for different types of particles in the ATLAS detector [44].                | 7  |

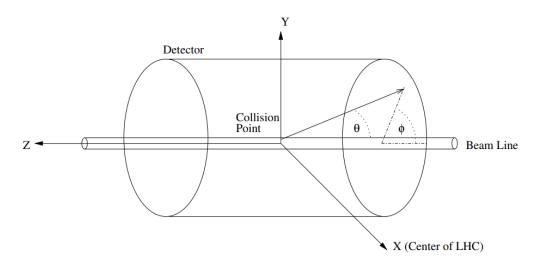

| 2.4  | The right-handed coordinate system used by the ATLAS collaboration [45].                                 | 8  |

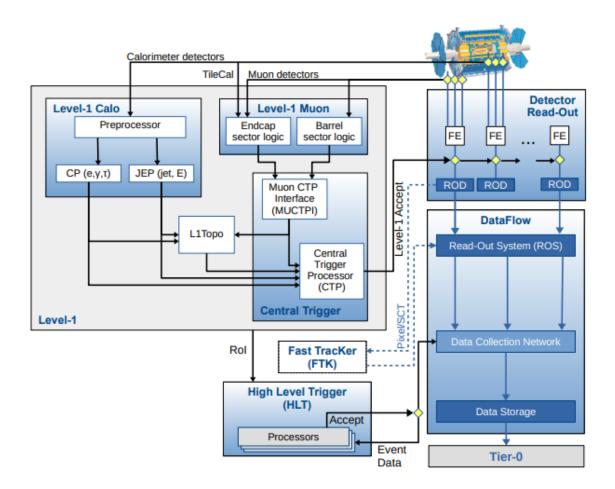

| 2.5  | The ATLAS Trigger and Data Acquisition (TDAQ) system used during the Run II. [47].                       | 9  |

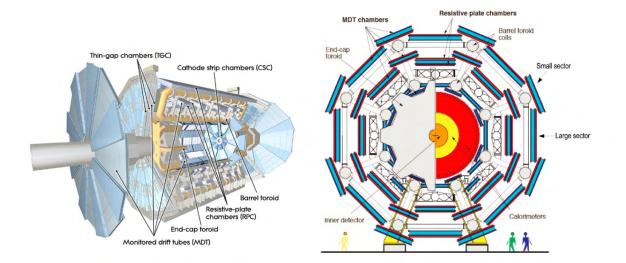

| 2.6  | ATLAS Muon spectrometer cutaway diagram [15] and the view perpendicular to the                           |    |

|      | beam line [50].                                                                                          | 10 |

| 2.7  | ATLAS Muon Spectrometer quadrant in the $r-z$ direction. The top figure is the layout                    |    |

|      | for larger sectors and the bottom figure is the layout for small sectors [50].                           | 10 |

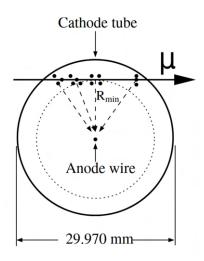

| 2.8  | Diagram of a MDT tube with ionisation along a muon track [53].                                           | 11 |

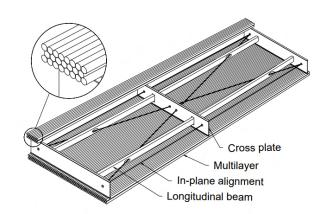

| 2.9  | Structure of a MDT chamber [41]                                                                          | 11 |

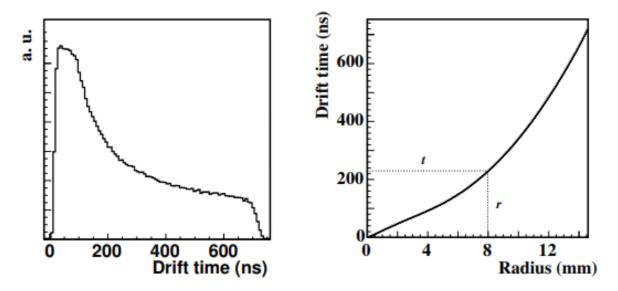

| 2.10 | Typical MDT electron drift time spectrum and $r - t$ relation [15]                                       | 12 |

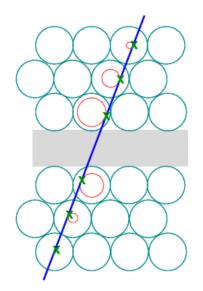

| 2.11 | MDT track reconstruction with a MDT chamber [54]                                                         | 13 |

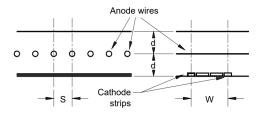

| 2.12 | Structure of the Cathode Strip Chamber [55]                                                              | 13 |

| 2.13 | Charge distribution on CSC strips [15]                                                                   | 13 |

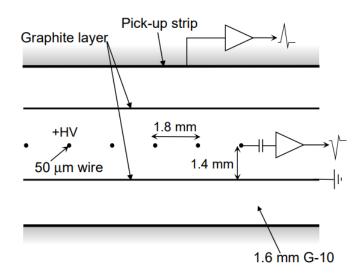

| 2.14 | Structure of the Resistive Plate Chamber [56].                                                           | 14 |

| 2.15 | Structure of the Thin Gap Chamber [15].                                                                  | 14 |

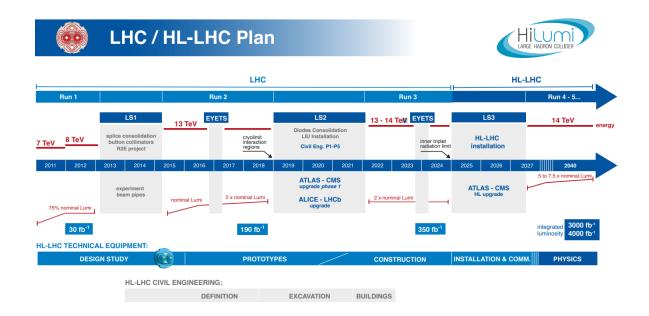

| 3.1  | The overall LHC/HL-LHC schedule [57].                                                                    | 15 |

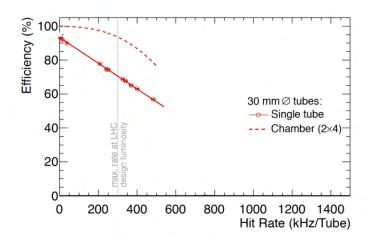

| 3.2  | The MDT efficiency as a function of the tube hit rate. The solid line is the efficiency                  |    |

|      | for a single tube and the dashed line is the efficiency for a 8-layer MDT chamber [59].                  | 17 |

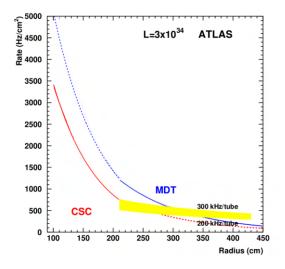

| 3.3  | Expected hit rate as a function of the radius for the inner end-cap station at an instan-                |    |

|      | taneous luminosity of $3.0 \times 10^{34}$ cm <sup>-2</sup> s <sup>-1</sup> and $\sqrt{s} = 14$ TeV [59] | 18 |

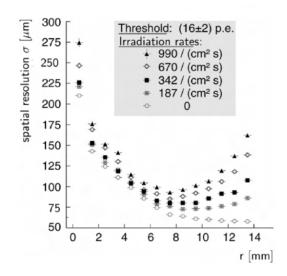

| 3.4  | MDT spatial resolution as a function of the radius under different background rates [68].                | 18 |

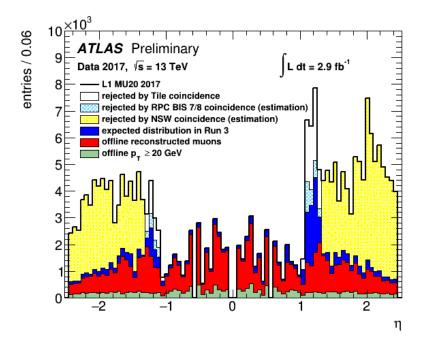

| 3.5  | The $\eta$ distribution of the L1_MU20 with different matching conditions considered [69].               | 19 |

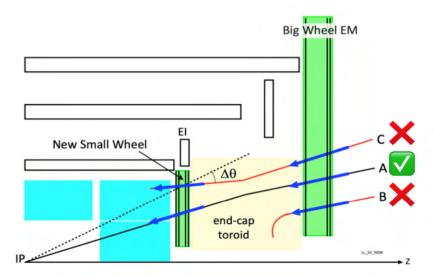

| 3.6  | Trigger selection with the NSW detector. Track B only hits the BW while track C                          |    |

|      | does not point back to the IP. Only track A should be triggered. [59]                                    | 19 |

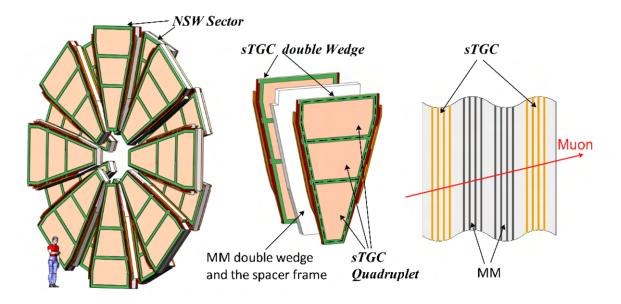

| 3.7  | The mechanical structure of the NSW detector [76]. There are eight large sectors and                     |    |

|      | eight small sectors. Each sector has two sTGC wedges and two MM wedges. Each                             |    |

|      | sTGC wedge is composed of three sTGC quadruplets. In total there are 16 detector                         |    |

|      | layers for each sector.                                                                                  | 20 |

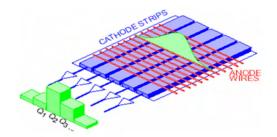

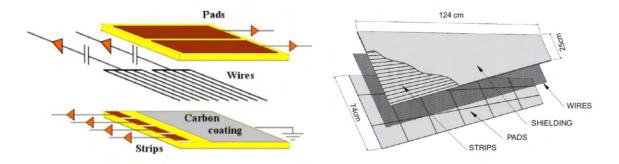

| 3.8  | The internal structure of the sTGC detector [59].                                                        | 21 |

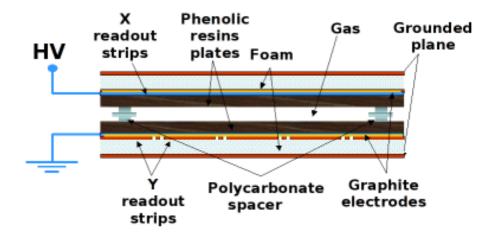

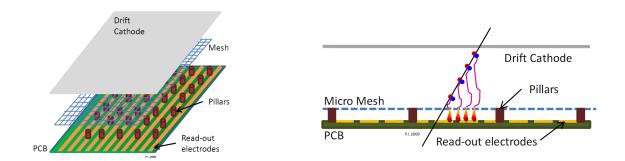

| 3.9  | Structure of the MM detector and its operation principle [59]                                            | 21 |

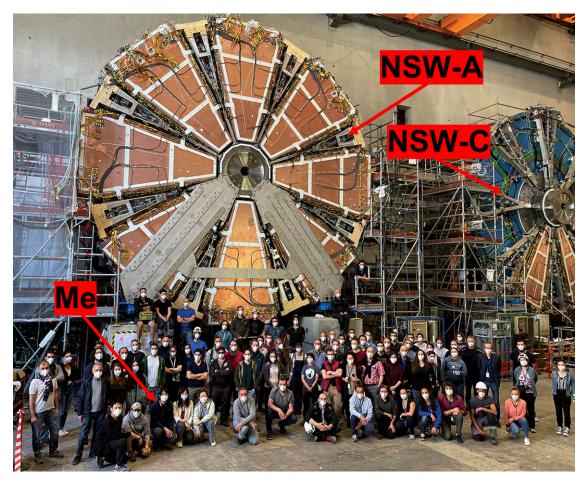

| 3.10         | The picture of the NSW-A (left) and NSW-C (right) when NSW-A was ready for the transport and installation to the ATLAS collision hall in July 2021[77]. | 22       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

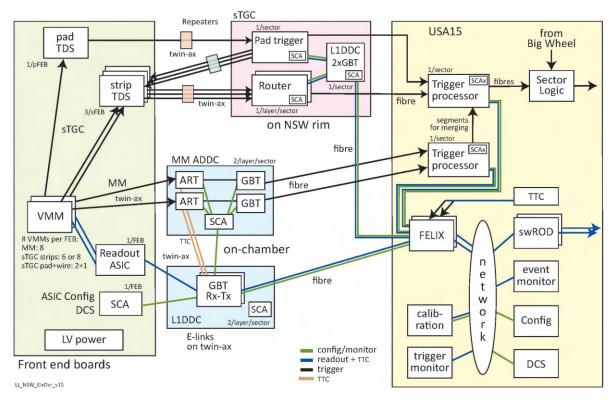

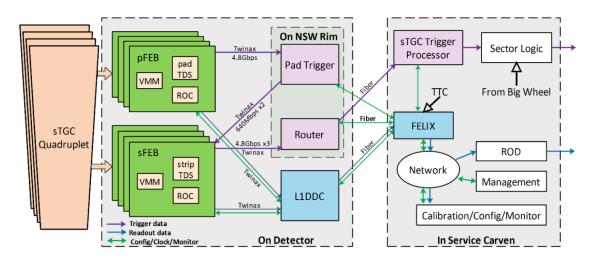

| 3.11         | Overview of the NSW trigger and readout electronics [83]                                                                                                | 23       |

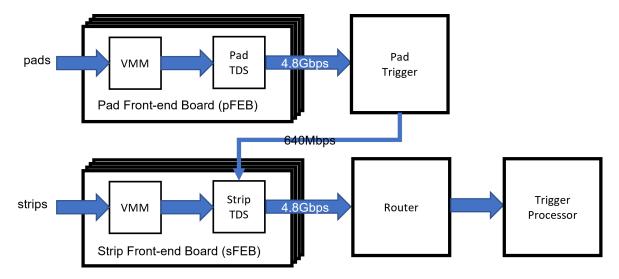

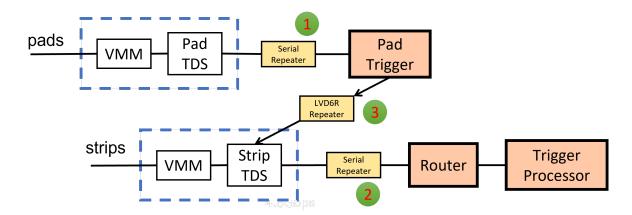

| 3.12         | The sTGC trigger chain data flow.                                                                                                                       | 24       |

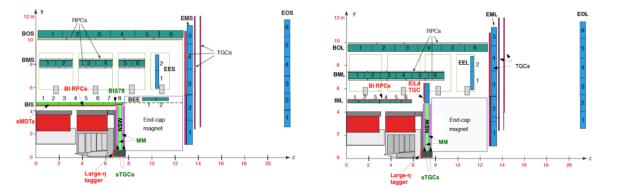

| 3.13         | The new MS layout in the $r - z$ direction (the left plot is for the small sector and the                                                               |          |

|              | right plot is for the large sector). Detectors marked by green text were installed during                                                               |          |

|              | the Phase-I upgrade, those marked with red text are the detectors that will be installed                                                                |          |

|              | during the Phase-II upgrade [58].                                                                                                                       | 26       |

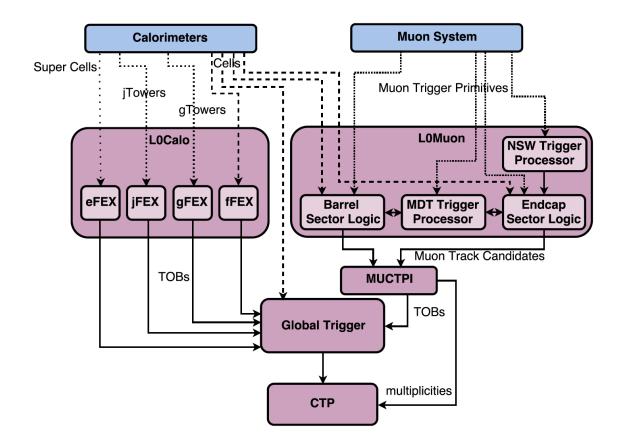

| 3.14         | Diagram of the Level-0 trigger of ATLAS detector after Phase-II upgrade. The muon                                                                       |          |

|              | trigger primitives from the RPC (barrel region) and TGC (end-cap region) are used in                                                                    |          |

|              | coincidence with the information from the outermost layer of the tile calorimeter. The                                                                  |          |

|              | NSW and MDT prove hit information to their corresponding trigger processors. The                                                                        |          |

|              | Barrel Sector Logic and Endcap Sector Logic determines muon candidates with the                                                                         |          |

|              | refinements of momentum measurement from MDT Trigger Procesor [58]                                                                                      | 27       |

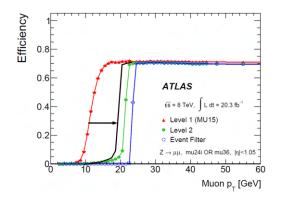

| 3.15         | Trigger efficiency in terms of $p_T$ at L1, L2, and EF stages. The black line is the                                                                    |          |

|              | expected L0 trigger performance with the MDT detector used [98]                                                                                         | 28       |

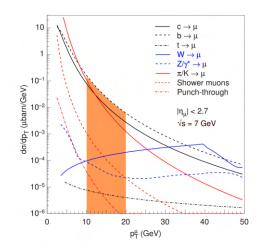

| 3.16         | The production cross-section of single muons as a function of the muon $p_T$ . The                                                                      |          |

|              | momentum range marked by the orange area is vital to be assisted by the MDT in the                                                                      |          |

|              | muon triggering [98].                                                                                                                                   | 28       |

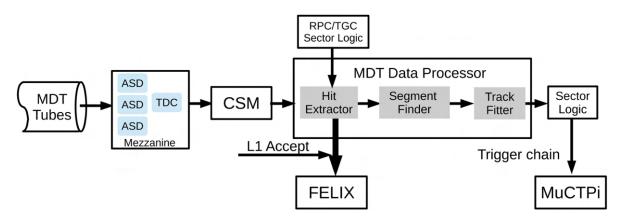

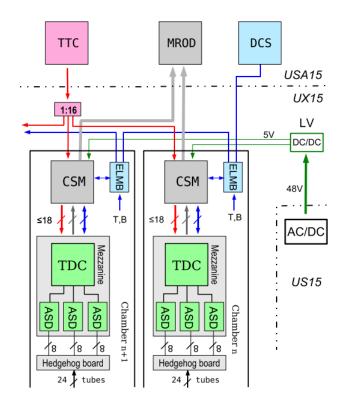

| 3.17         | The new architecture of the MDT electronic system in the Phase-II upgrades                                                                              | 29       |

| 4.1          | Simplified diagram of the sTGC trigger and readout system [76]                                                                                          | 30       |

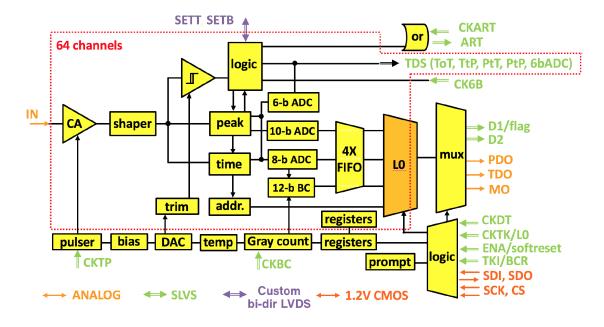

| 4.2          | Architecture of the VMM ASIC [101].                                                                                                                     | 31       |

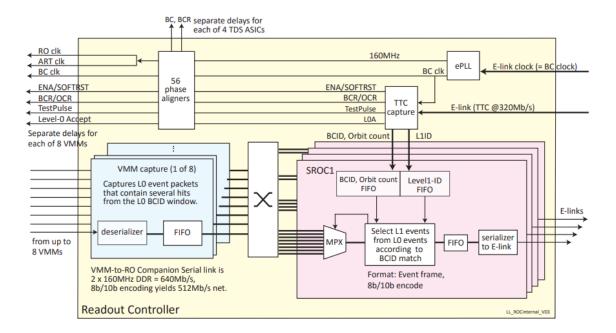

| 4.3          | Structure diagram of the ROC ASIC [102].                                                                                                                | 33       |

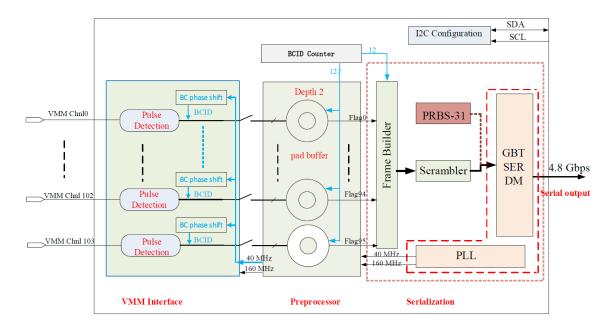

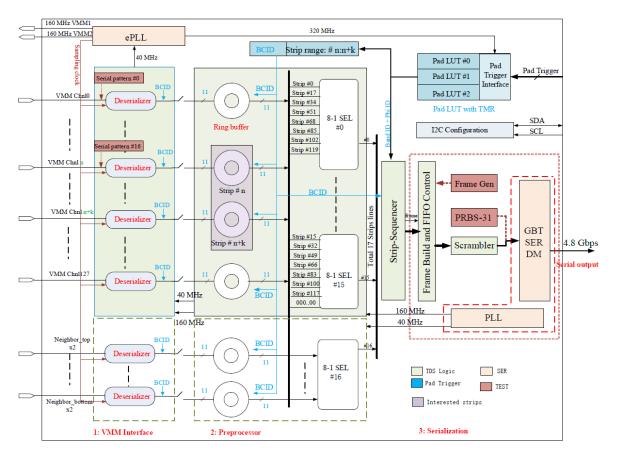

| 4.4          | Architecture of the pad TDS ASIC [103]                                                                                                                  | 34       |

| 4.5          | Architecture of the strip TDS ASIC [103]                                                                                                                | 35       |

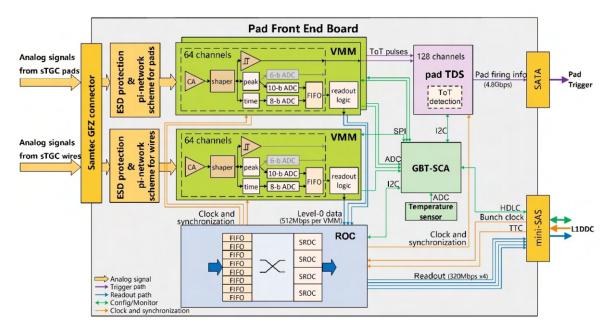

| 4.6          | Block diagram of the pFEB [76]                                                                                                                          | 36       |

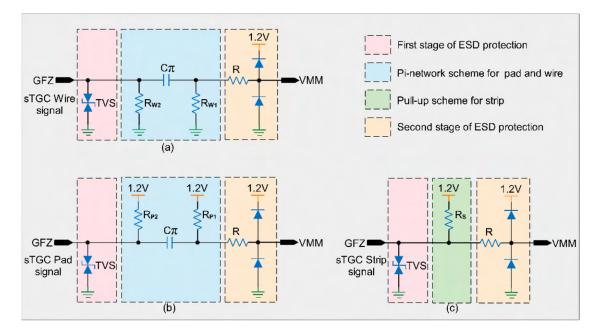

| 4.7          | The sTGC FEB analog input protection circuit [76].                                                                                                      | 36       |

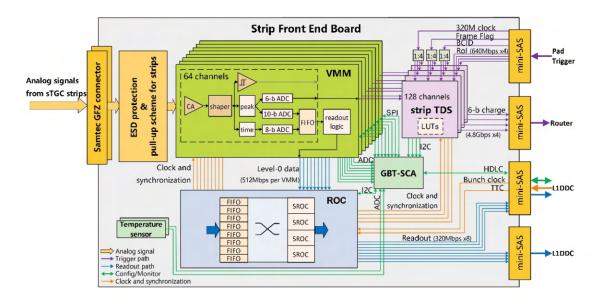

| 4.8          | Block diagram of the sFEB [76]                                                                                                                          | 37       |

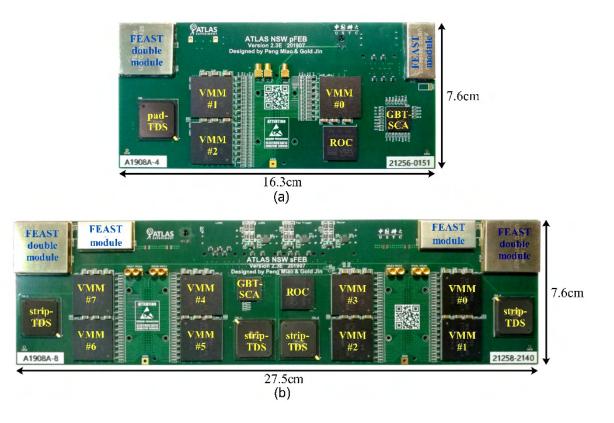

| 4.9          | Assembled sTGC pFEB (a) and sFEB8 (b) boards [76]                                                                                                       | 38       |

| 5.1          | The custom-designed mini-DAQ motherboard with a XCKU035 FPGA. A mini-SAS                                                                                |          |

|              | to FMC adapter board is mounted on it.                                                                                                                  | 40       |

| 5.2          | The Xilinx KC705 evaluation board                                                                                                                       | 40       |

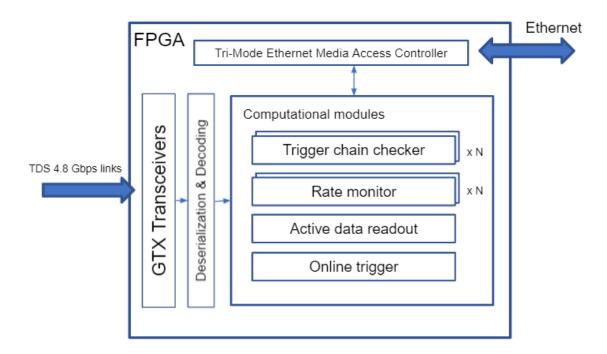

| 5.3          | Architecture of the mini-DAQ firmware.                                                                                                                  | 41       |

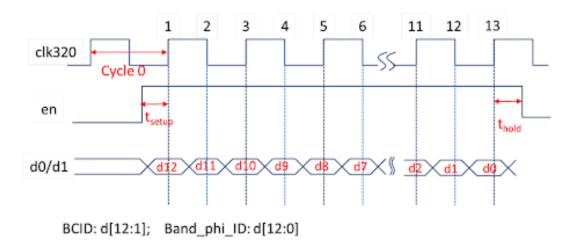

| 5.4          | The trigger signals sent by the Pad Trigger board to the strip TDS [103].                                                                               | 44       |

| 5.5          | The Band-ID to the strip channel grouping.                                                                                                              | 46       |

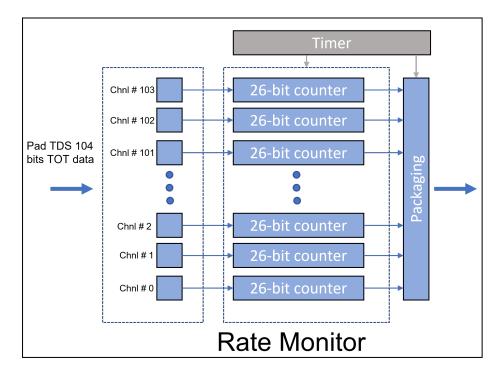

| 5.6          | Architecture of the Rate Monitor module.                                                                                                                | 48       |

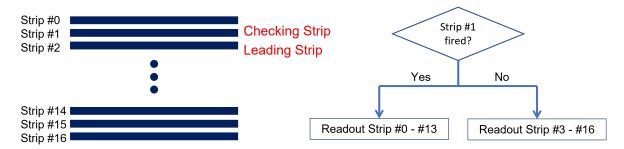

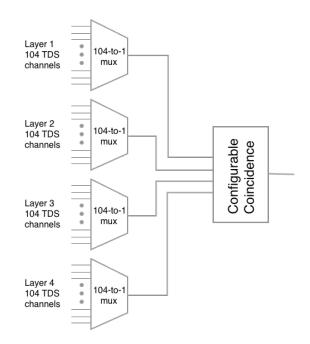

| 5.7          | The online trigger scheme.                                                                                                                              | 49<br>50 |

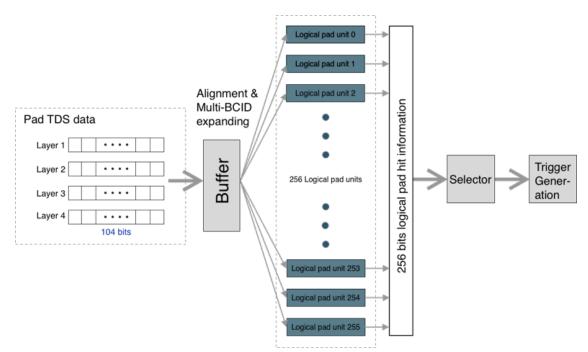

| 5.8          | Architecture of the logical pad unit.                                                                                                                   | 50       |

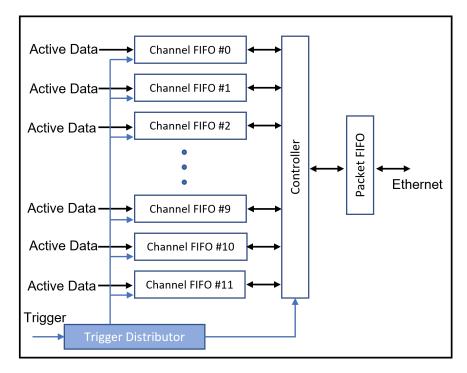

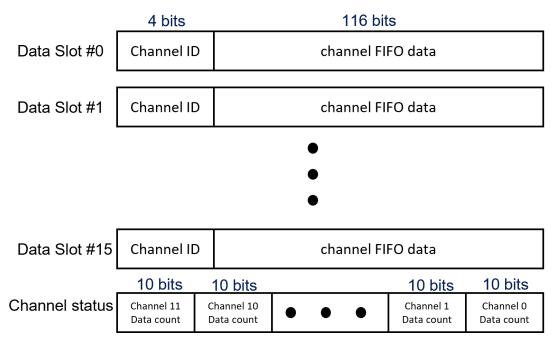

| 5.9<br>5.10  | Architecture of the Active Data Readout module.                                                                                                         | 52<br>53 |

| 5.10<br>5.11 | Data format of the active data readout packet.                                                                                                          | 53<br>54 |

| 5.11         |                                                                                                                                                         | 54       |

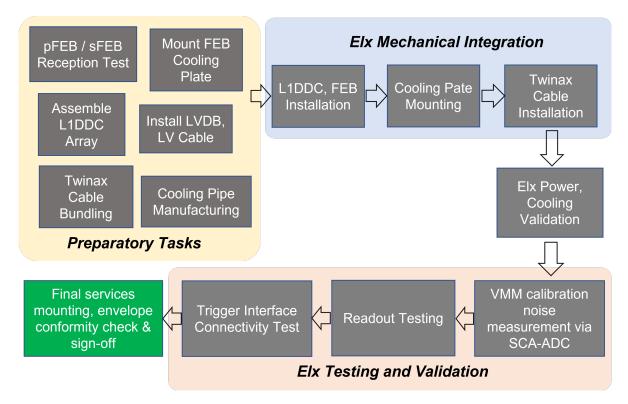

| 6.1          | Procedure of the sTGC front-end electronics integration and commissioning                                                                               | 55       |

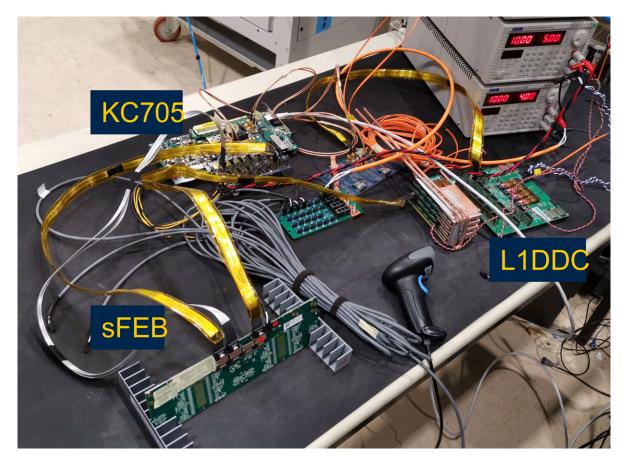

| 6.2  | The on-bench trigger chain test station with the KC705 board and one sFEB                       | 58 |

|------|-------------------------------------------------------------------------------------------------|----|

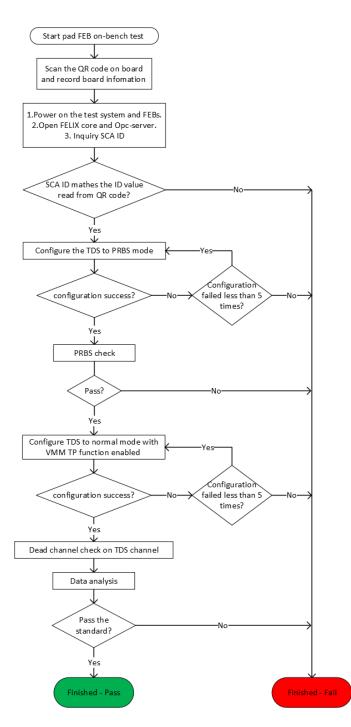

| 6.3  | The pFEB on-bench automatic test flow.                                                          | 59 |

| 6.4  | sFEB trigger chain data and clock connection.                                                   | 60 |

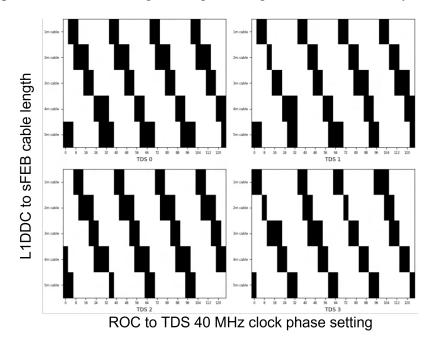

| 6.5  | Working ROC-TDS clock phase (white areas) for different L1DDC-to-sFEB cable                     |    |

|      | lengths. The four sub-figures are the results of four TDS chips on the same sFEB                | 61 |

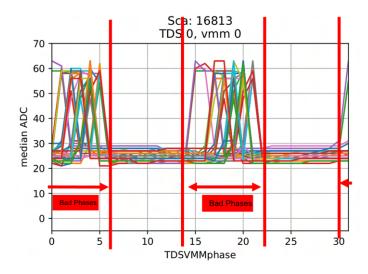

| 6.6  | sFEB 6-bit ADC scan with different TDS-VMM clock phases. Each line presents one                 |    |

|      | channel. The amplitude of the VMM TP is fixed during the scan.                                  | 62 |

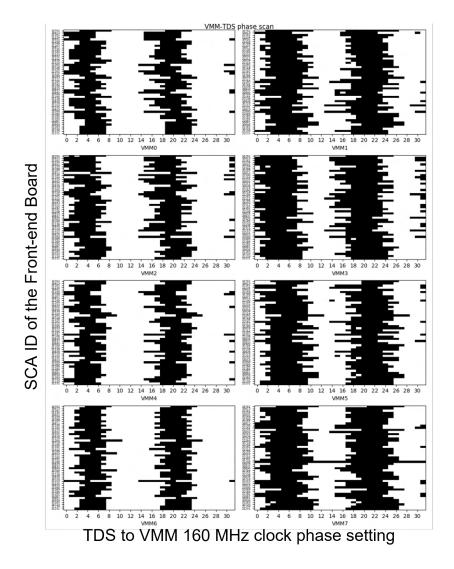

| 6.7  | Working TDS-VMM clock phases (presented by the white areas) for the first batch of              |    |

|      | 48 sFEBs. The eight sub-figures are the results of 8 VMMs from the same sFEB. The               |    |

|      | <i>x</i> -axis is the TDS-VMM 160 MHz clock phase, and the <i>y</i> -axis is the SCA ID of each |    |

|      | FEB                                                                                             | 63 |

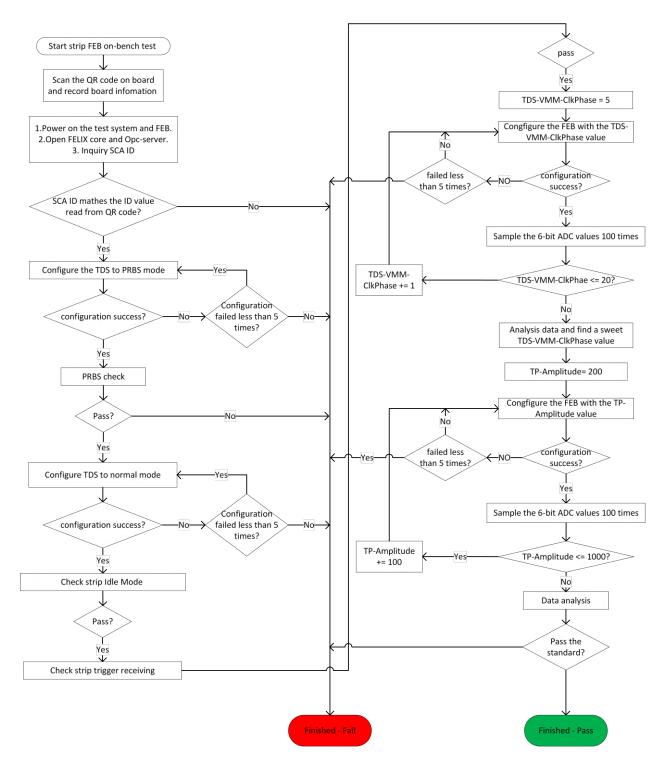

| 6.8  | sFEB on-bench automatic test flow.                                                              | 65 |

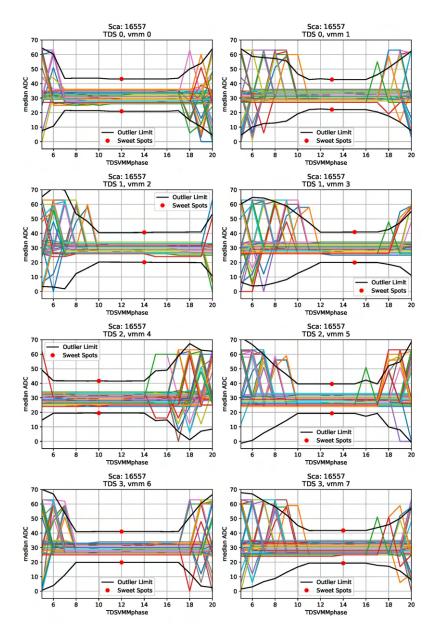

| 6.9  | TDS-VMM clock phase scan results. The eight sub-figures are the results for 8 VMMs              |    |

|      | on the sFEB. Each color line presents one VMM channel (64 channels per VMM). The                |    |

|      | red dots are the sweet points                                                                   | 66 |

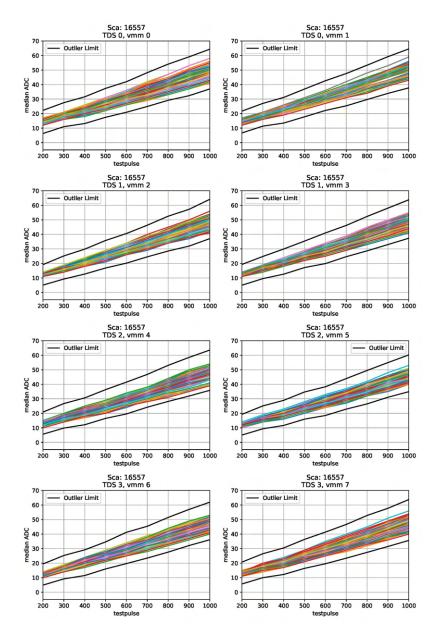

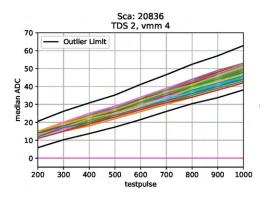

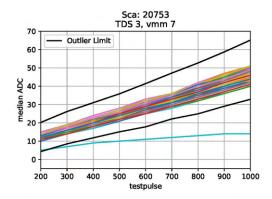

| 6.10 | sFEB 6-bit ADC linearity scan. The eight sub-figures are the results for 8 VMMs on              |    |

|      | the sFEB. Each color line presents one VMM channel(64 channels per VMM)                         | 67 |

| 6.11 | Dead channel example in the 6-bit ADC linearity scan. Each color line presents one              |    |

|      | VMM channel. The pink line shows the dead channel.                                              | 68 |

| 6.12 | Outlier channel example in the 6-bit ADC linearity scan. Each color line presents one           |    |

|      | VMM channel. The blue line shows the outlier channel.                                           | 68 |

| 6.13 | On-wedge trigger chain front-end electronics connections                                        | 69 |

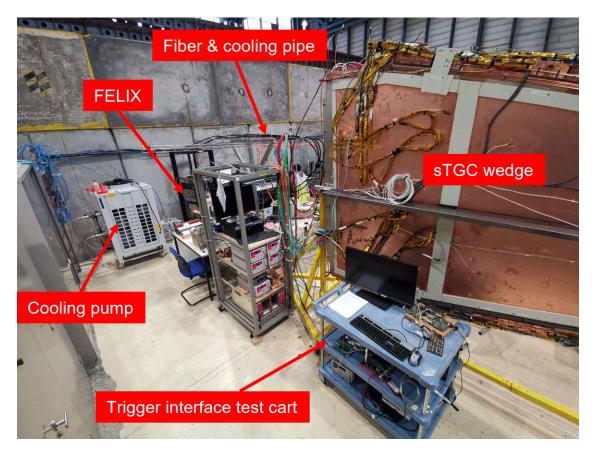

| 6.14 | The on-wedge trigger chain connectivity test setup                                              | 69 |

| 6.15 | On-wedge connection for pFEB to Pad Trigger board.                                              | 70 |

| 6.16 | On-wedge pFEB PRBS error rate results.Link 0 to link 11 are 12 pFEB links and it                |    |

| <    | shows zero error during the time of test. The BERs are also recorded                            | 70 |

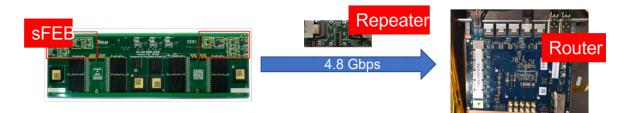

| 6.17 | On-wedge connection for sFEB to Router board                                                    | 71 |

| 6.18 | On-wedge sFEB PRBS error test results. There are one sFEB8 and two sFEB6 from                   |    |

| 6.10 | the same layer of the sTGC quadruplet.                                                          | 71 |

| 6.19 | On-wedge connection for sFEB trigger receiving test.                                            | 72 |

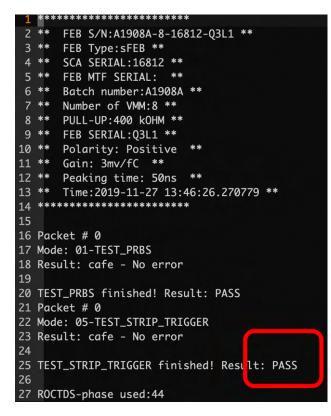

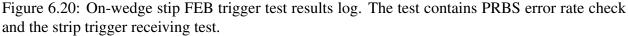

| 6.20 | On-wedge stip FEB trigger test results log. The test contains PRBS error rate check             | 70 |

| ( 01 | and the strip trigger receiving test.                                                           | 73 |

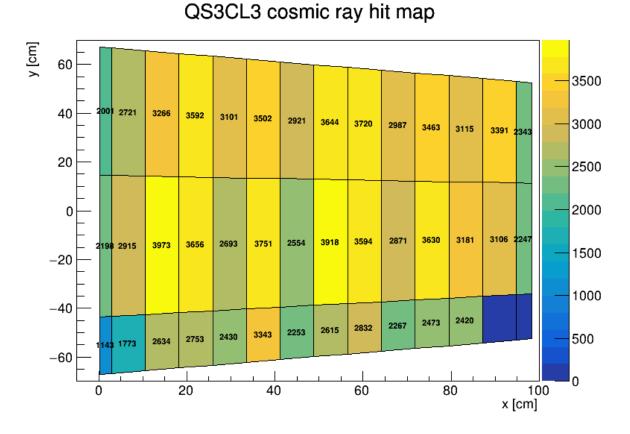

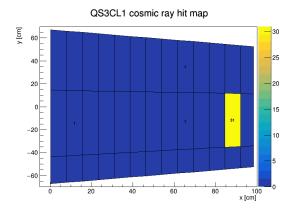

| 6.21 | Cosmic ray hit map of Layer 3 of the Q3C measured for 30 minutes with a 50 mV                   | 74 |

| ( 22 | threshold setting and 2800 V HV. The two channels at the right bottom corner are dead.          | 74 |

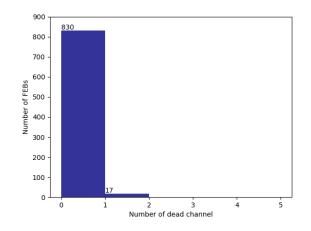

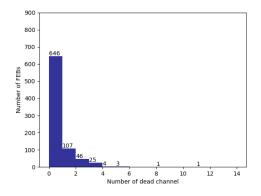

| 6.22 | Dead channel summary of all 847 functional pFEBs. 830 of them have zero dead                    | 75 |

| (2)  | channels and 17 of them have one dead channel                                                   | 75 |

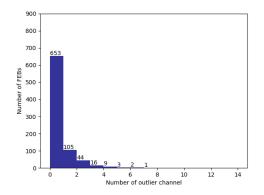

| 6.23 | Outlier channel summary of all 833 functional sFEBs. 653 of them have zero outlier              | 75 |

| 6.24 | channels                                                                                        | 75 |

| 6.24 | Dead channel summary of all 833 functional sFEBs. 646 of them have zero dead                    | 75 |

|      | channels                                                                                        | 75 |

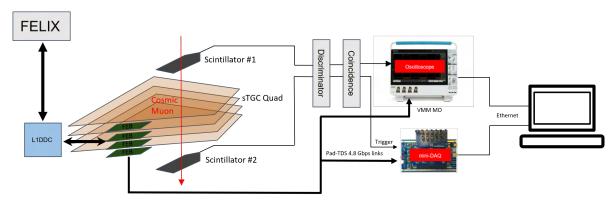

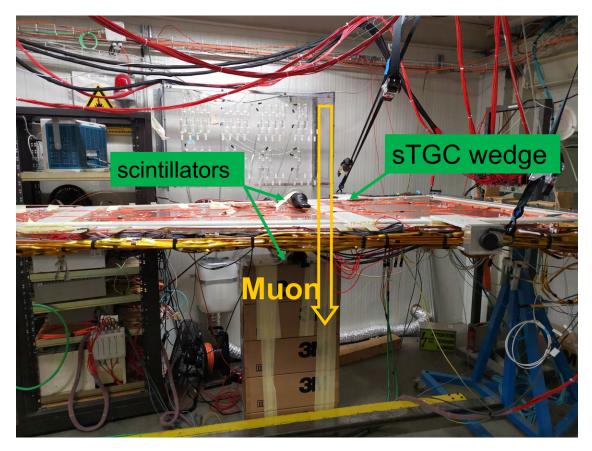

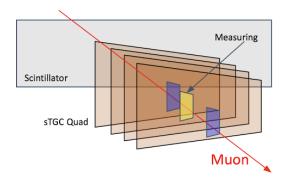

| 7.1  | Block diagram of the test setup for the sTGC cosmic ray study                                   | 77 |

| 7.2  | A photograph of the test setup in the CERN Building 180 gas room.                               | 78 |

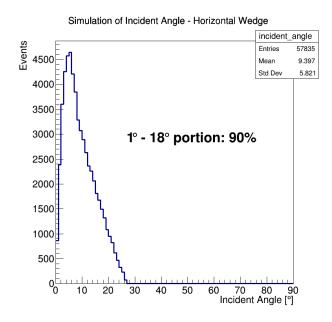

| 7.3  | Simulated muon angular distribution in the horizontal trigger scheme. 90% of muons              |    |

|      | triggered have an incident angle from $1^{\circ}$ to $18^{\circ}$ , and the mean value is 9.4 ° | 79 |

| 7.4   | Simplified diagram for the vertical trigger scheme. The trigger is the coincidence of the scintillator and two sTGC pads from the other two layers. | 80  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

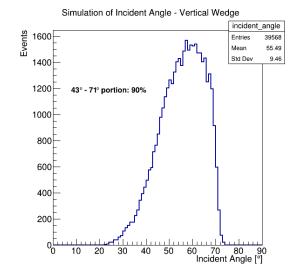

| 7.5   | Simulated muon angular distribution in the vertical trigger scheme. 90% of the muons                                                                | 00  |

| ,     | have an incident angle from 43° to 71°, and the mean value is 55.5 °                                                                                | 80  |

| 7.6   | An event saved by the oscilloscope. The trigger signal is the coincidence of signals                                                                |     |

|       | from the two scintillators. The yellow line and the green line are the analog outputs                                                               |     |

|       | from the VMM MO.                                                                                                                                    | 81  |

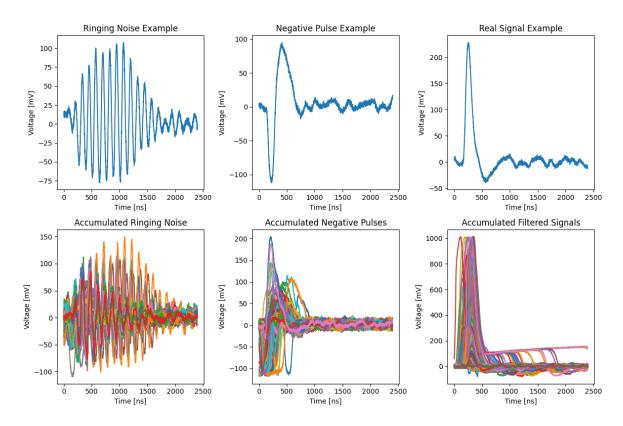

| 7.7   | sTGC pad analog signal waveforms from the collected events. Three columns repre-                                                                    |     |

|       | sent ringing noise, negative pulse, and candidate muon signal. The top row shows an                                                                 |     |

|       | example of each category, and the bottom row presents the accumulated waveforms                                                                     | 81  |

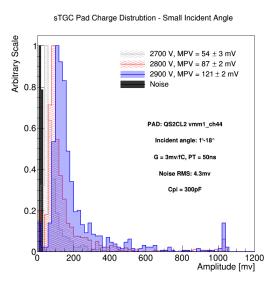

| 7.8   | sTGC pad charge distribution in the horizontal trigger scheme. The maximum value                                                                    |     |

|       | of each distribution is normalized to one                                                                                                           | 82  |

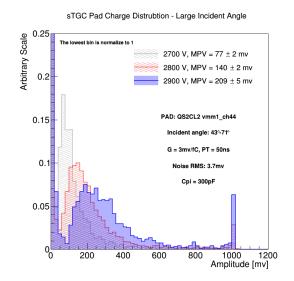

| 7.9   | sTGC pad charge distribution in the vertical trigger scheme. Noise is normalized to                                                                 |     |

|       | one                                                                                                                                                 | 82  |

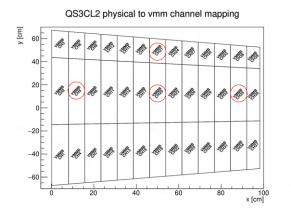

| 7.10  | Selected sTGC pads for MPV measurements. Marked by the red circles in the map-                                                                      |     |

|       | ping figure. The three pads in the middle row are chosen as nominal size pads, while a                                                              |     |

|       | tiny pad in the top row is chosen to present the extreme case                                                                                       | 83  |

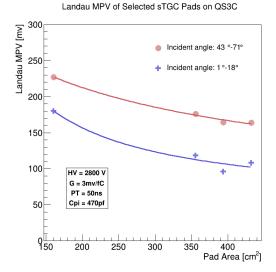

| 7.11  | MPV of selected sTGC pads with a high voltage of 2,800 V. The red dots are the                                                                      |     |

|       | results from the vertical trigger scheme, and the blue dots are the results from the                                                                | ~ ~ |

| 7 10  | horizontal trigger scheme.                                                                                                                          | 83  |

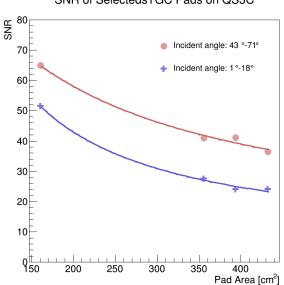

| 7.12  | SNR of selected sTGC pads. The red dots are the results from the vertical trigger                                                                   | 0.4 |

| 7 1 2 | scheme, and the blue dots are the results from the horizontal trigger scheme                                                                        | 84  |

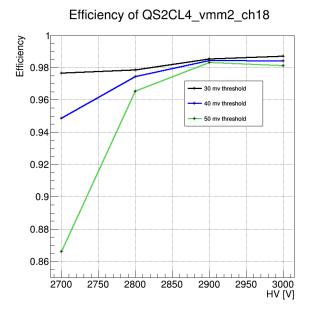

| 7.13  | The sTGC pad efficiency for a selected pad on the QS2C quadruplet with 30 mV, 40 mV and 50 mV. Thusehold actings                                    | 05  |

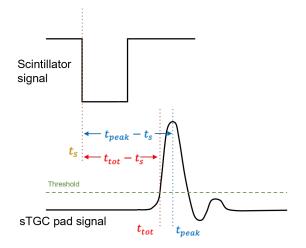

| 7.14  | mV and 50 mV Threshold settings. $\dots$ Diagram of the timing concepts in the measurement. $t_s$ is the falling edge of the scin-                  | 85  |

| /.14  | tillator signal. $t_{tot}$ is defined as the time when the sTGC signal crosses the threshold.                                                       |     |

|       | $t_{peak}$ is defined as the time when the signal reaches its peak                                                                                  | 86  |

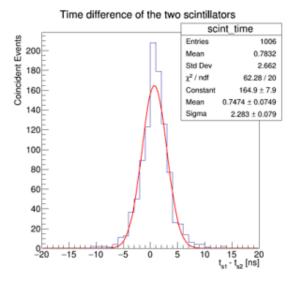

| 7.15  | Distribution of the timing difference of the two scintillators $(t_{s1} - t_{s2})$ . The Gaussian                                                   | 00  |

| 7.15  | fit sigma is 2.28 ns. $\ldots$                                     | 86  |

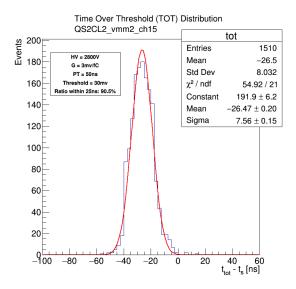

| 7.16  | Distribution of the $t_{tot} - t_s$ for a selected pad on the QS2C quadruplet. The Gaussian                                                         | 00  |

| /.10  | fit sigma is $7.56 \text{ ns.}$                                                                                                                     | 87  |

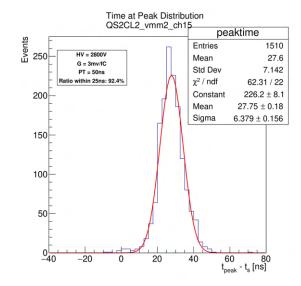

| 7.17  | Distribution of the $t_{\text{peak}} - t_s$ of a selected pad on the QS2C quadruplet. The Gaussian                                                  | 07  |

|       | fit sigma is $6.38 \text{ ns.}$                                                                                                                     | 87  |

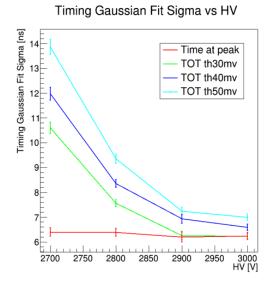

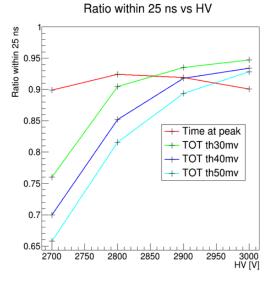

| 7.18  | Gaussian fit sigma of the timing distribution as a function of the high voltage applied.                                                            | 87  |

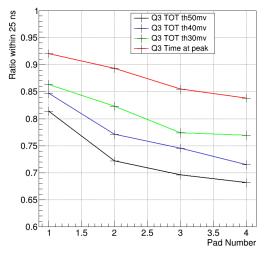

| 7.19  | The fraction of events contained within 25 ns                                                                                                       | 87  |

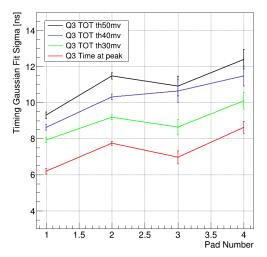

| 7.20  | Timing Gaussian fit sigma of the selected pads with 2,800 V. The x-axis is the pad                                                                  |     |

|       | number. Each line represents the performance of the four pads under a particular case.                                                              | 88  |

| 7.21  | The ratio (events contained within 25 ns) of the selected pads with 2,800 V. The x-                                                                 |     |

|       | axis is the pad number. Each line represents the performance of the four pads under a                                                               |     |

|       | particular case.                                                                                                                                    | 88  |

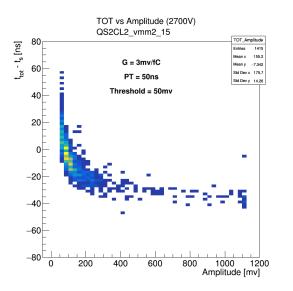

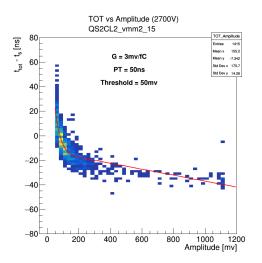

| 7.22  | $t_{\text{tot}} - t_s$ vs the signal amplitude at 2,700 V                                                                                           | 89  |

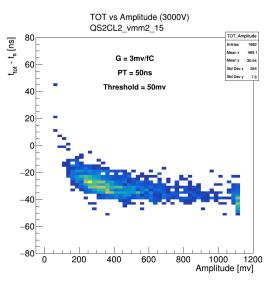

| 7.23  | $t_{\text{tot}} - t_s$ vs the signal amplitude at 3,000 V                                                                                           | 89  |

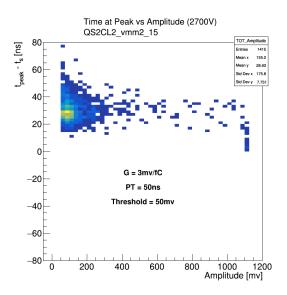

| 7.24  | $t_{\text{peak}} - t_s$ vs the signal amplitude at 2,700 V                                                                                          | 89  |

| 7.25  | $t_{\text{tot}} - t_s$ vs the signal amplitude at 2,700 V. The red line fits the trend                                                              | 90  |

| 7.26  | Distribution of the $t_{tot} - t_s$ at 2,700 V. The Gaussian fit sigma is 13.9 ns                                                                   | 90  |

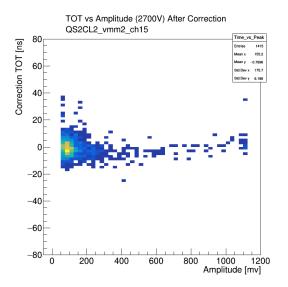

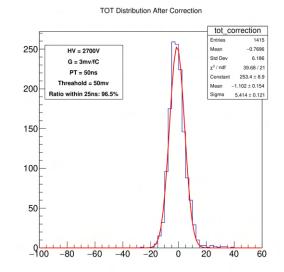

| 7.27  | $t_{\text{tot}} - t_s$ vs the signal amplitude at 2,700 V after the time walk corrections applied Distribution of the t $t_s$ at 2,700 V after the time walk corrections applied. The | . 91  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.28  | Distribution of the $t_{tot} - t_s$ at 2,700 V after the time walk corrections applied. The Gaussian fit sigma is 5.4 ns.                                                             | . 91  |

| 7.29  | An example hit map for the mapping verification. The location of the fired pad                                                                                                        | . 91  |

| 1.29  | · · · · ·                                                                                                                                                                             | 02    |

| 7 20  | matches the location where the scintillators were placed                                                                                                                              | . 92  |

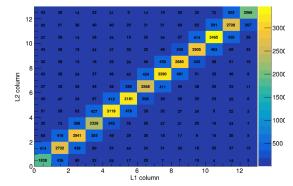

| 7.30  | The column hit correlation plot between layer 1 and layer 2 on QS3C. A clear diagonal                                                                                                 | 02    |

| 7 0 1 | line confirms the mapping.                                                                                                                                                            | . 92  |

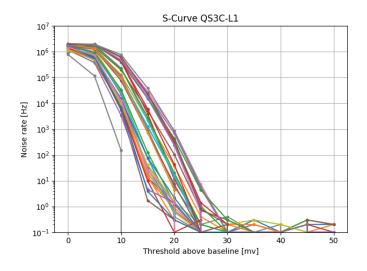

| 7.31  | The S-curve for pads on layer 1 of the QS3C quadruplet. Each line presents one sTGC                                                                                                   | 02    |

| 7 22  | pad channel.                                                                                                                                                                          |       |

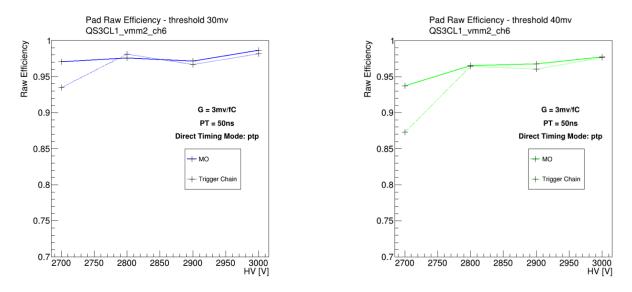

| 7.32  | The sTGC pad efficiency with a threshold of $30 \text{ mV}$ .                                                                                                                         |       |

| 7.33  | The sTGC pad efficiency with a threshold of $40 \text{ mV}$ .                                                                                                                         |       |

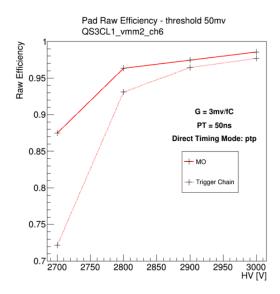

| 7.34  | The sTGC pad efficiency with a threshold of 50 mV.                                                                                                                                    | . 94  |

| 7.35  | Demonstration of the binning effect. In the green line example, the ideal arrival time                                                                                                |       |

|       | of the ToT pulse is close to the edge of the TDS 40 MHz clock. The TDS will have                                                                                                      |       |

|       | a 50% chance to sample the BCID as $n$ and another 50% chance for BCID to be                                                                                                          | 05    |

| 7 26  | identified as $n + 1$ .                                                                                                                                                               |       |

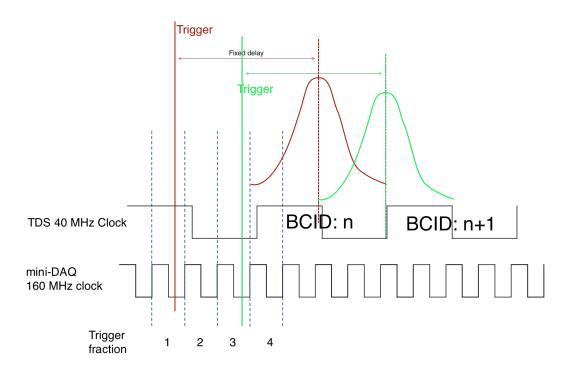

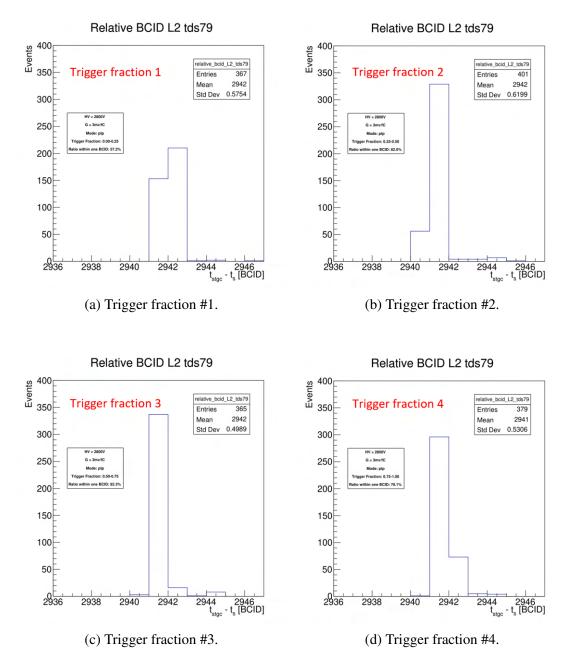

| 7.36  | The distribution of the BCID difference with the four trigger fractions                                                                                                               | . 90  |

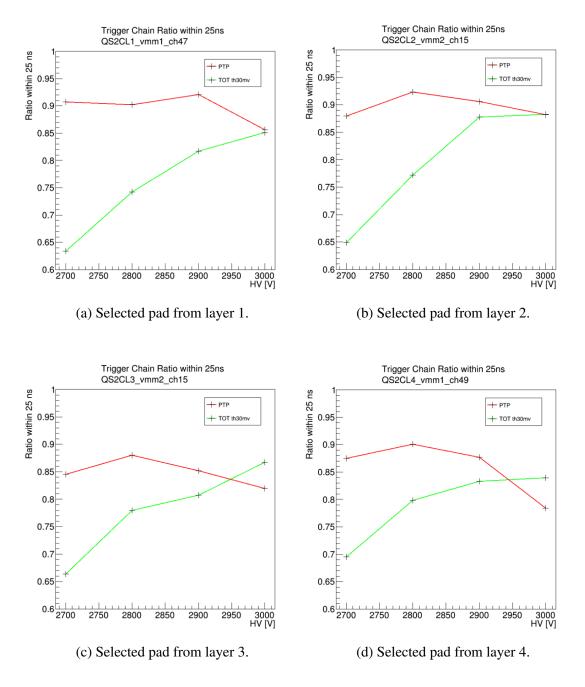

| 7.37  | The percentage of the events contained within 25 ns on the four sTGC pads selected                                                                                                    |       |

|       | from a logical pad. The red lines are the results using VMM PtP mode, and the green                                                                                                   | 07    |

| 7 20  | lines are the results from VMM ToT mode with a 30 mV threshold setting                                                                                                                | . 97  |

| 7.38  | Timing performance vs. trigger fraction before tuning. All four pads have a pad dealy                                                                                                 | 00    |

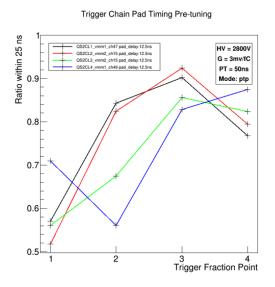

| 7 20  | setting of 12.5 ns                                                                                                                                                                    | . 98  |

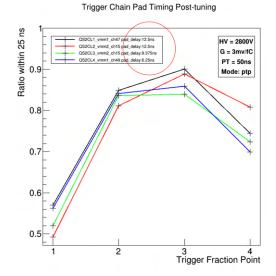

| 7.39  | Timing performance vs. trigger fraction after tuning. Layer 1 pad delay: 12.5 ns;                                                                                                     | 00    |

| 7 40  | layer 2 pad delay: 12.5 ns; Layer 3 pad delay: 9.375 ns; layer 4 pad delay: 6.25 ns.                                                                                                  | . 98  |

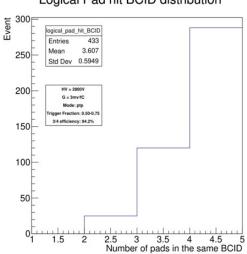

| 7.40  | Logical pad BCID distribution. For 3-out-of-4 coincidence using one BCID trigger                                                                                                      | 00    |

| 7 4 1 | window, the trigger efficiency is found to be 94.2%                                                                                                                                   |       |

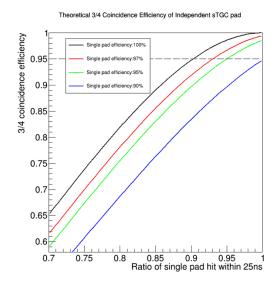

| 7.41  | The simulation result of 3-out-of-4 coincidence efficiency.                                                                                                                           |       |

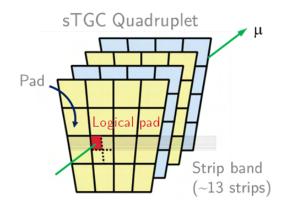

| 7.42  | Demonstration of the logical pad [59].                                                                                                                                                |       |

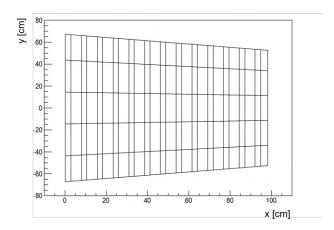

| 7.43  | sTGC pad divisions on the QS3C quadruplet.                                                                                                                                            | . 101 |

| 7.44  | Projection of the pad divisions from the four layers on the QS3C quadruplet. The new division splits the detector plane into 130 pieces with 60 large pieces and 70 small             |       |

|       | pieces                                                                                                                                                                                | 101   |

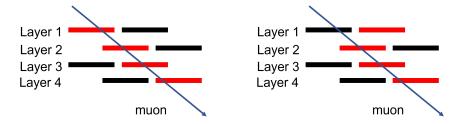

| 7.45  | Demonstration of multiple logical pads firing under the 3-out-of-4 coincidence                                                                                                        |       |

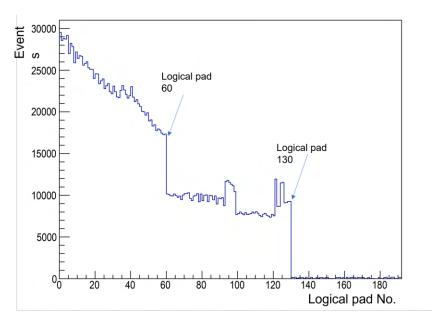

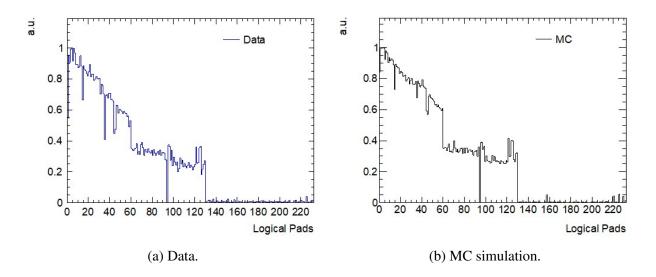

| 7.45  | Logical pad event distribution.                                                                                                                                                       |       |

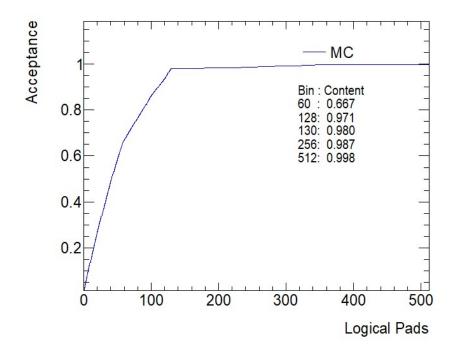

| 7.47  | Logical pad geometric acceptance.                                                                                                                                                     |       |

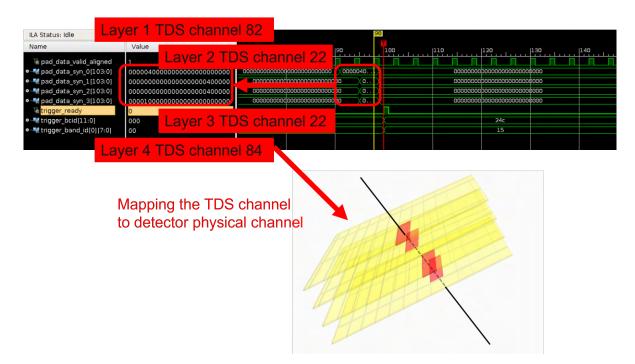

| 7.48  | An online trigger captured by the ILA core. Each layer has one pad fired, and the                                                                                                     | . 105 |

| 7.40  | bottom 3D model shows all fired pads                                                                                                                                                  | 104   |

| 7.49  | Hit distribution of the logical pads on the QS3C quadruplet.                                                                                                                          |       |

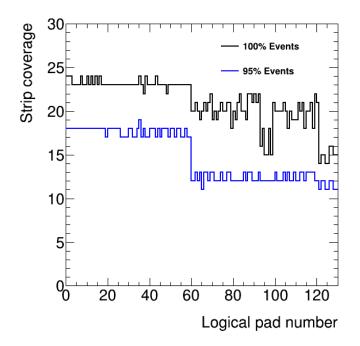

| 7.50  | Number of strips that each logical pad covers in the MC simulation without charge                                                                                                     | . 105 |

| 7.50  | sharing.                                                                                                                                                                              | 107   |

| 7.51  | Online trigger generating and strip TDS data receiving in ILA.                                                                                                                        |       |

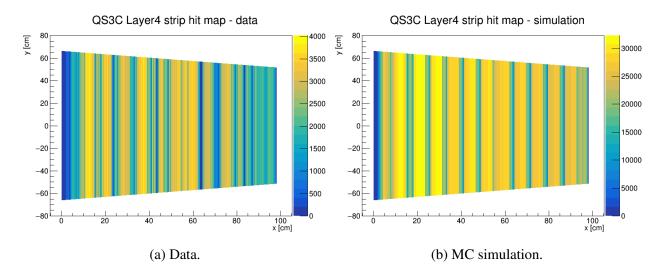

| 7.52  | The sTGC strip hit map on layer 4                                                                                                                                                     |       |

| 7.52  | Strip TDS data captured by ILA with the multiple Band-IDs triggering.                                                                                                                 |       |

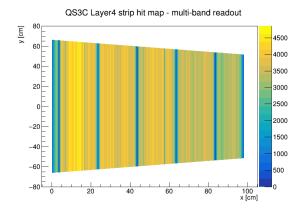

| 7.54  | Strip hit map with the multiple Band-ID trigger scheme.                                                                                                                               |       |

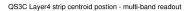

| 7.55  | Strip charge-centroid hit map with the multiple Band-ID trigger scheme.                                                                                                               |       |

| 1.55  | Surp charge-centrole int map with the multiple band-iD trigger scheme                                                                                                                 | . 110 |

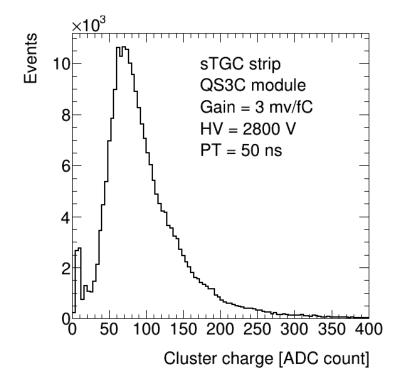

| 7.56         | Distribution of the strip cluster charge                                                    |

|--------------|---------------------------------------------------------------------------------------------|

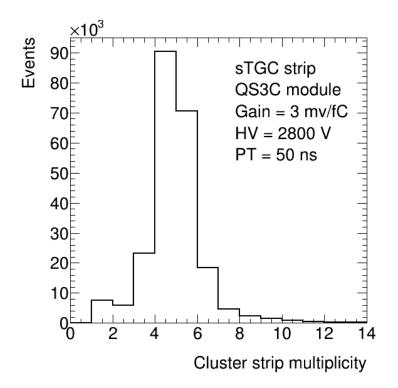

| 7.57         | Distribution of the cluster strip multiplicity                                              |

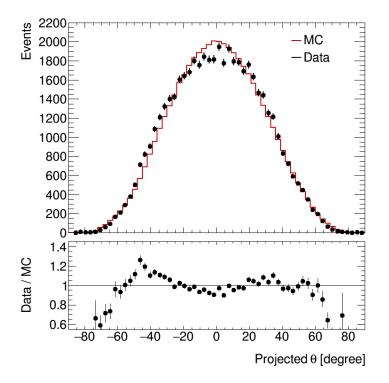

| 7.58         | The 1D projected angular distribution of cosmic muons measured by sTGC strips in            |

|              | the trigger chain                                                                           |

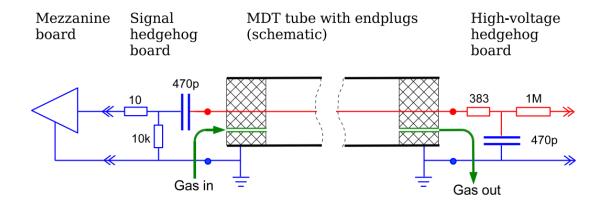

| 8.1          | Illustration of the electrical services of the MDT tube [53]                                |

| 8.2          | The current MDT readout electronics [53]                                                    |

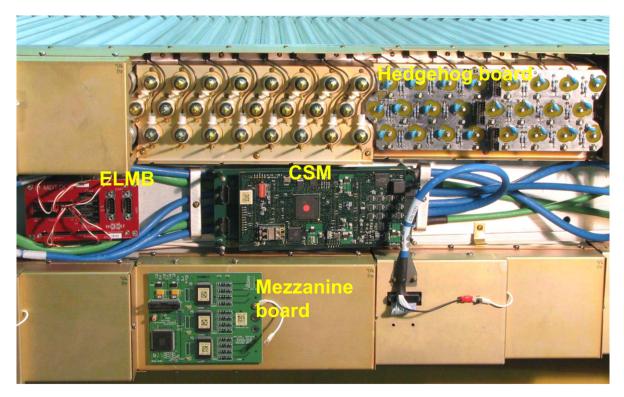

| 8.3          | Picture of the current MDT front-end electronics mounted on an MDT chamber [53]. 115        |

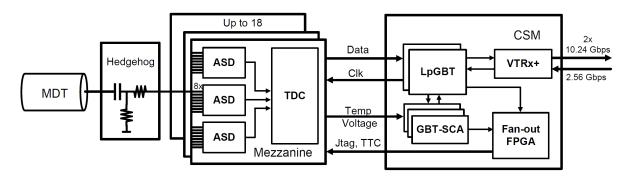

| 8.4          | MDT front-end electronics for the Phase-II upgrade [107]                                    |

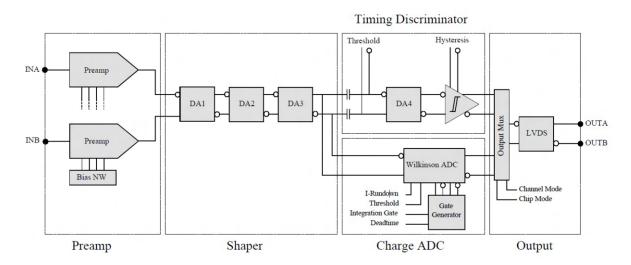

| 8.5          | Block diagram of the ASD/ASD2 ASIC [99]                                                     |

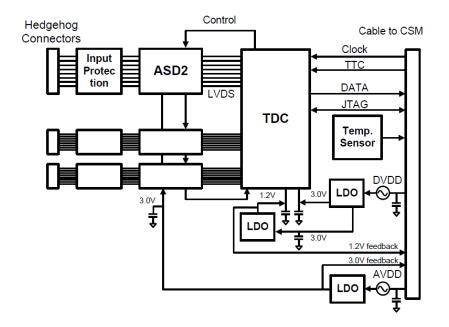

| 8.6          | Structure of the Mezzanine card for the Phase-II upgrade [107]                              |

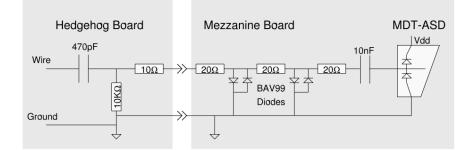

| 8.7          | The protection network on the hedgehog board and the Mezzanine card that limits the         |

|              | pulse current into the ASD amplifier [53]                                                   |

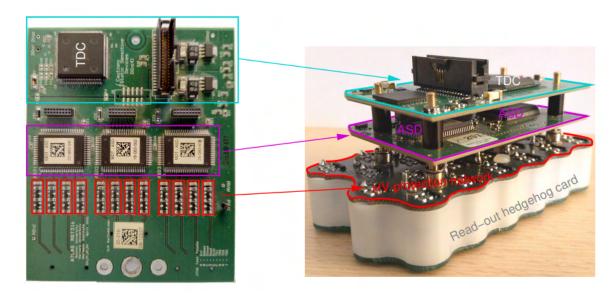

| 8.8          | Photographs of the legacy MDT316 Mezzanine card (left) and the Stack Mezzanine              |

|              | card (right) for sMDT[109]                                                                  |

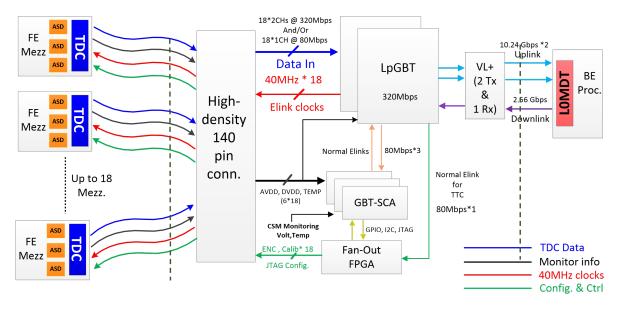

| 8.9          | The architecture of the prototype CSM [110]                                                 |

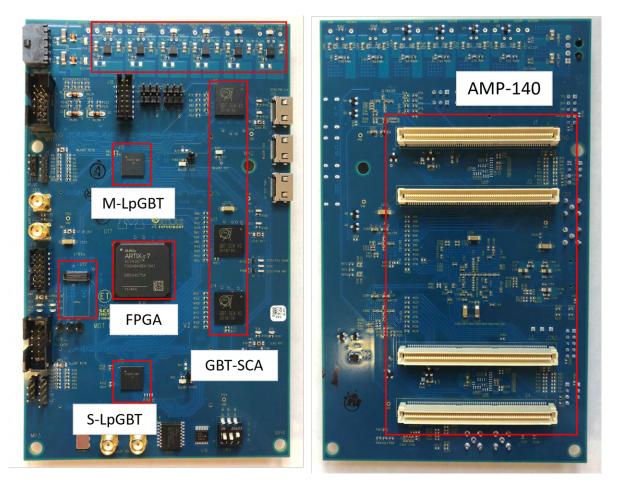

| 8.10         | Picture of the top side (left) and bottom side (right) of the LpGBT-CSM prototype [110].121 |

|              |                                                                                             |

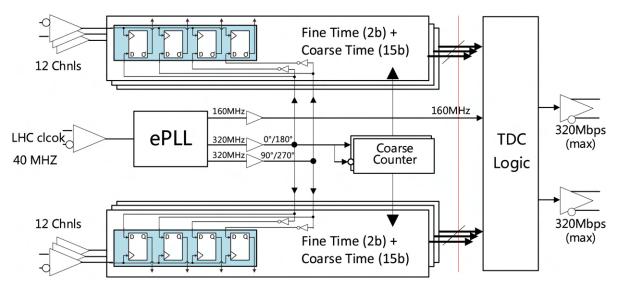

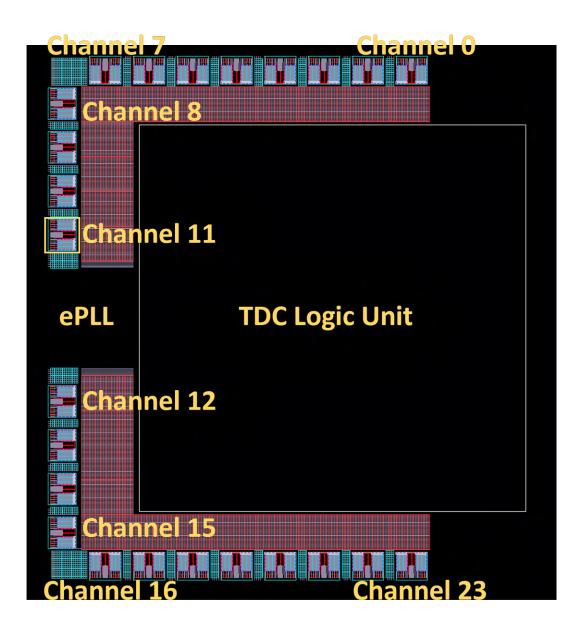

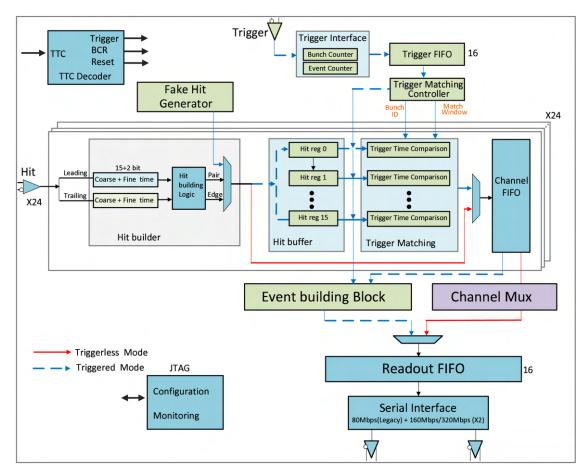

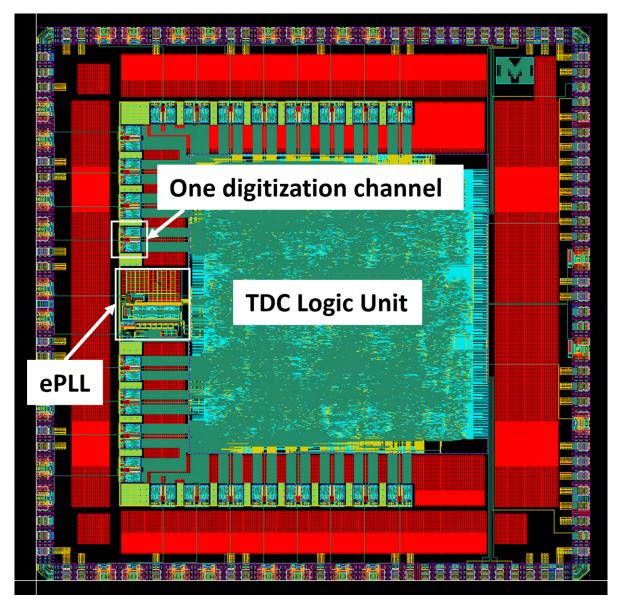

| 9.1          | Architecture of the MDT-TDC ASIC [111]                                                      |

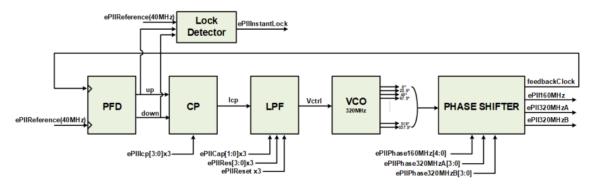

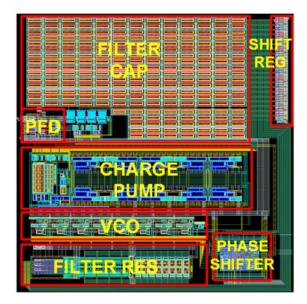

| 9.2          | The structure of the ePLL [113]                                                             |

| 9.3          | Layout of the ePLL [113]                                                                    |

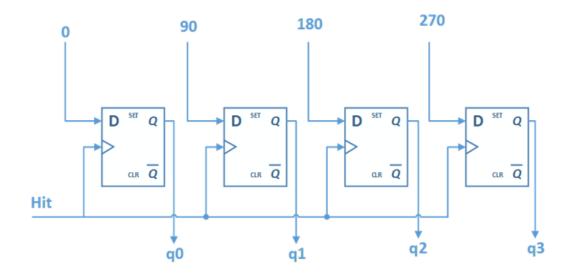

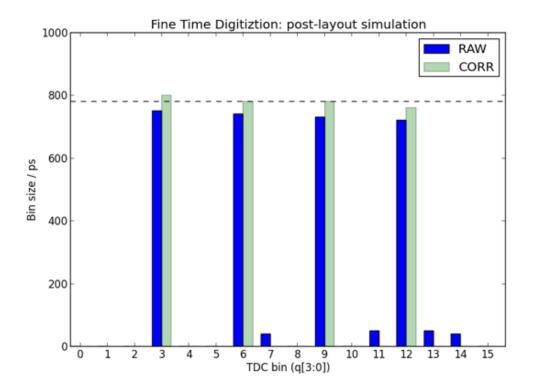

| 9.4          | Structure of the fine-time sampling circuit                                                 |

| 9.5          | The timing diagram presents the fine-time raw coding. Left sub-figure is the ideal case     |

| 0.6          | and the right sub-figure is a practical case with unaligned clocks                          |

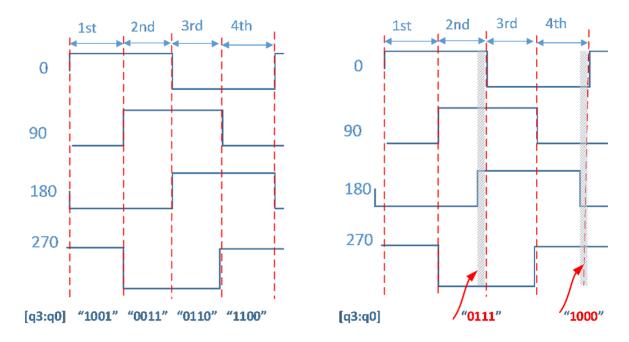

| 9.6          | Schematic diagram of the sampling register: (a) the True single Clocked Latches             |

|              | (TSPC) used for the demonstrator prototype and (b) the Pulse-Triggered Register             |

| 0.7          | (PTR) used for the MDT TDC [111]                                                            |

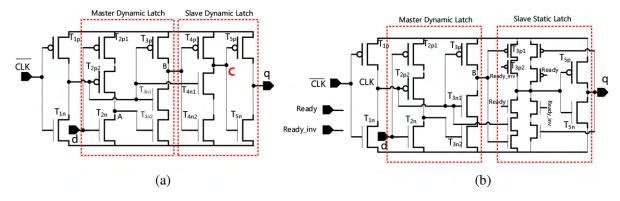

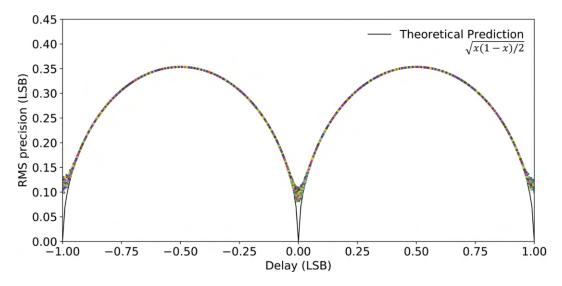

| 9.7          | Simulation of the fine-time sampling circuit with corrections applied. Correction is        |

| 0.0          | applied to the raw codings                                                                  |

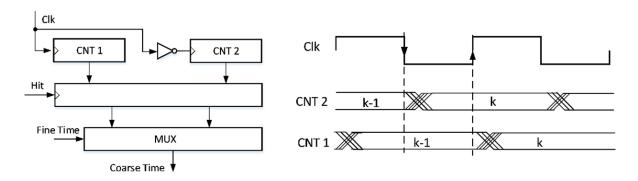

| 9.8          | Coarse-time Sampling Circuit. The CNT 1 is driven by the rising edge of the clock           |

| 0.0          | and the CNT 2 is driven by the falling edge of the clock                                    |

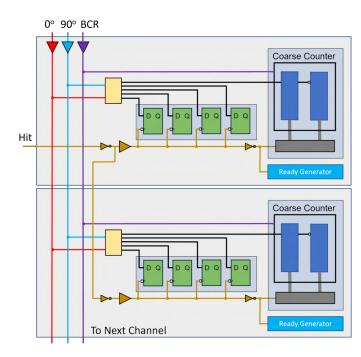

| 9.9          | Block diagram of the time digitization circuit of a single channel. Two identical sub-      |

| 0.10         | channels sample the rising and falling edges of the hit signal, respectively                |

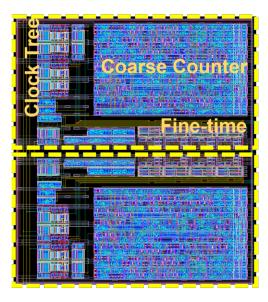

| 9.10         | The layout of a single channel                                                              |

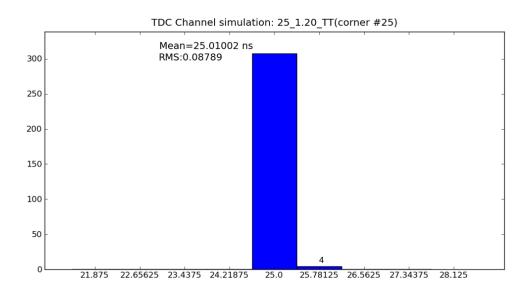

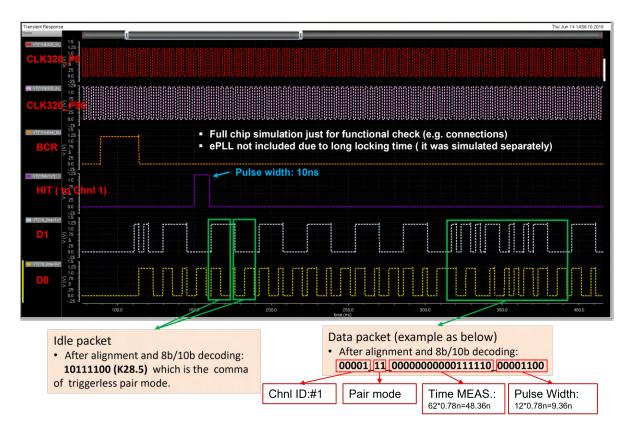

| 9.11         | Simulation of the timing digitization of a single channel. The input is a clock with        |

| 0.12         | period of 25.01 ns. The measured mean value is 25.01002 ns                                  |

| 9.12         | Layout of 24 digitization channels                                                          |

| 9.13         | Block diagram of the TDC logic unit                                                         |

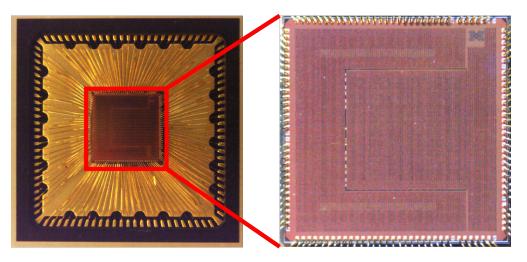

| 9.14         | Layout of the MDT TDC ASIC (the silicon area is $3.7 \text{ mm} \times 3.7 \text{ mm}$ )    |

| 9.15         | Full chip function simulation (time digitization units and logic unit)                      |

| 9.16         | MDT TDC die with the QFN100 package [114]                                                   |

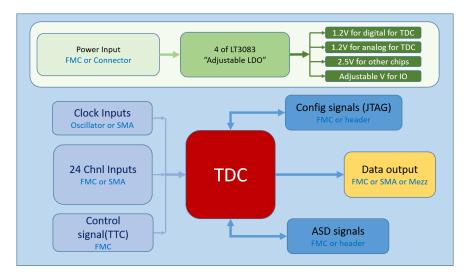

| 9.17         | Block diagram of the MDT TDC test board [114]                                               |

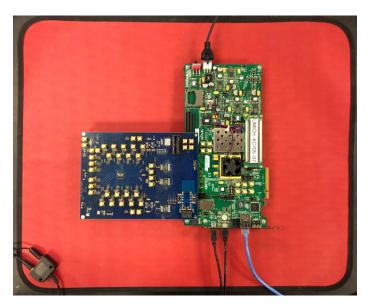

| 9.18<br>9.19 | A photograph of the MDT TDC test board [114]                                                |

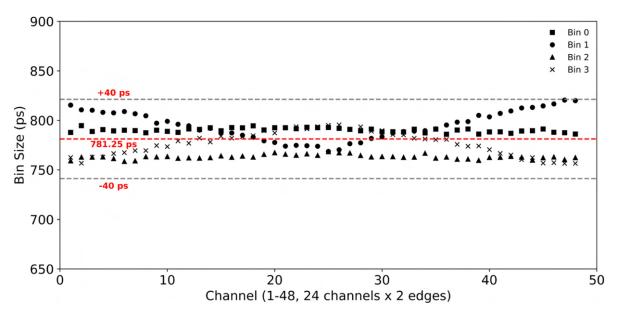

| 9.19         | Fine-time bin size of the 48 sub-channels.                                                  |

| 2.20         |                                                                                             |

| 9.21 | The RMS timing precision of the 48 sub-channels.                                                                                                                                                                                                        | 141 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

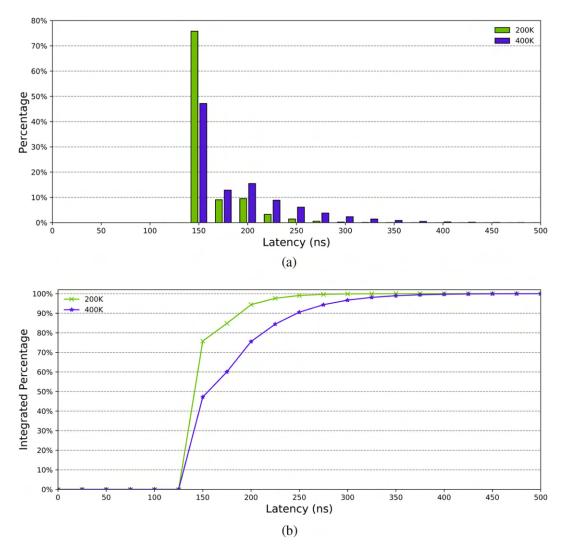

| 9.22 | (a) Latency distribution with a hit rate of 200/400 kHz per channel. (b) Integrated latency distribution. At 350 ns, 99 % of the data can be transmitted with a hit rate of                                                                             |     |

|      | 400 kHz per channel                                                                                                                                                                                                                                     | 142 |

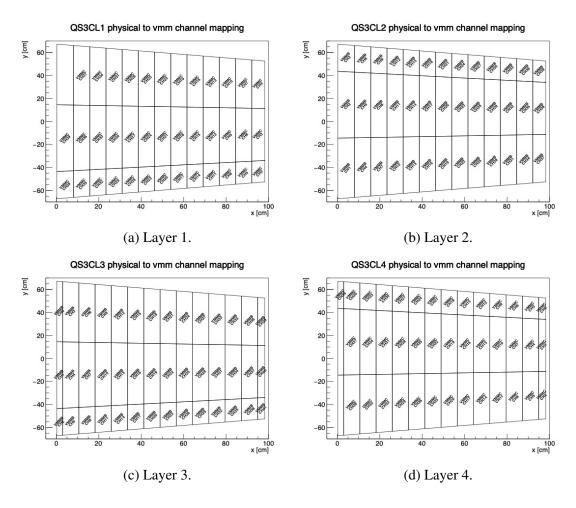

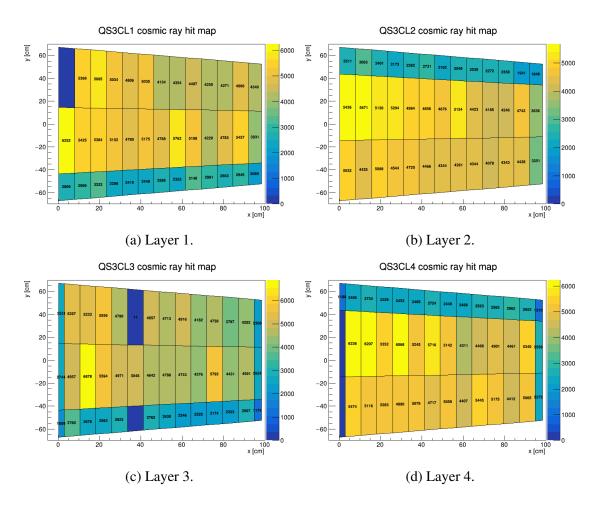

| A.1  | Hit map of the four layers of the QS3C quadruplet used for cosmic ray study under 2800 V HV and 50 mV threshold. The number on each pad is the hit count during the test period. The pads with zero or close to zero hit numbers are the unconnected or |     |

|      | dead channels.                                                                                                                                                                                                                                          | 146 |

# LIST OF TABLES

| 3.1 | ATLAS operation comparisons between nominal LHC and HL-LHC [58]                          | 16  |

|-----|------------------------------------------------------------------------------------------|-----|

| 5.1 | Trigger chain checker functions.                                                         | 41  |

| 5.2 | Pad TDS data format.                                                                     |     |

| 5.3 | The strip TDS 30-bit raw data format.                                                    | 43  |

| 5.4 | The strip TDS output data format.                                                        | 45  |

| 5.5 | LUTs used for the strip TDS                                                              | 47  |

| 5.6 | The 3-out-of-4 coincidence configuration table.                                          | 51  |

| 6.1 | The Test functions available for the sFEB in the mini-DAQ software                       | 64  |

| 7.1 | Noise RMS and the area for the four sTGC pads studied                                    | 84  |

| 7.2 | The strip TDS Band-ID LUT for the three TDSs on layer 1                                  | 106 |

| 9.1 | Specifications of the MDT TDC ASIC.                                                      | 123 |

| 9.2 | Default fine-time correction table.                                                      | 128 |

| 9.3 | Simulation of the clock duty cycles for 12 channels located on the top half of the chip. | 133 |

# LIST OF ABBREVIATIONS

| ASD Amplifier Shaper Discriminator    | HL-LHC High-Luminosity LHC                                            |

|---------------------------------------|-----------------------------------------------------------------------|

| BCR Bunch Counter Reset               | <b>IBERT</b> Integrated Bit Error Ratio Tester                        |

| BC Bunch Crossing                     | INL Integral Non-Linearity                                            |

| <b>BER</b> Bit Error Rate             | L0A L0 Accept                                                         |

| BGA Ball Grid Array                   | L1A L1 Accept                                                         |

| BSM Beyond Standard Model             | L1DDC Level-1 Data Driver Card                                        |

| <b>BW</b> Big Wheel                   | L1 Level-1                                                            |

| CSC Cathode Strip Chamber             | LDO Low-DropOut                                                       |

| CSM Chamber Service Module            | LHC Large Hadron Collider                                             |

| <b>DNL</b> Differential Non-Linearity | LUT Lookup Table                                                      |

| FELIX Front-End Link Exchange         | <b>LVCMOS</b> Low-Voltage Complementary Metal<br>Oxide Semiconductors |

| FPGA Field Programmable Gate Array    | LVDS Low-Voltage Differential Signaling                               |

| GUI Graphical User Interface          | LV Low voltage                                                        |

| MC Monte Carlo                            | <b>RPC</b> Resistive Plate Chamber       |  |  |

|-------------------------------------------|------------------------------------------|--|--|

| MDT Monitored Drift Tube                  | sFEB strip Front-End Board               |  |  |

| <b>mini-DAQ</b> mini data acquisition     | SLVS Scalable Low-Voltage Signaling      |  |  |

| MIP Minimum Ionizing Particle             | SM Standard Model                        |  |  |

| MM MicroMegas                             | SNR Signal-to-Noise Ratio                |  |  |

| MO Monitored Output                       | sTGC small-strip Thin Gap Chamber        |  |  |

| MPV Most Probable Value                   | <b>TDAQ</b> trigger and data acquisition |  |  |

| MS Muon Spectrometer                      | TDC Time-to-Digital Converter            |  |  |

| <b>NIM</b> Nuclear Instrumentation Module | <b>TDS</b> Trigger Data Serializer       |  |  |

| NSW New Small Wheel                       | TCC This Cos Chamber                     |  |  |

| I/O Input and Output                      | <b>TGC</b> Thin Gap Chamber              |  |  |

| <b>pFEB</b> pad Front-End Board           | TMR Triple Module Redundancy             |  |  |

| PLL Phase Locked Loop                     | ToT Time-over-Threshold                  |  |  |

| <b>PRBS</b> Psuedo-Random Binary Sequence | TP Test Pulse                            |  |  |

| RMS Root-Mean-Square                      | TTC Time, Trigger, and Control           |  |  |

| <b>ROC</b> Readout Controller             | DAC Digital-to-Analog Converter          |  |  |

| ROI Region of Interest                    | ADC Analog-to-Digital Converter          |  |  |

### ABSTRACT