# Design Techniques for Energy-Efficient and Scalable Machine Learning Accelerators

by

Teyuh Chou

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in The University of Michigan 2022

Doctoral Committee:

Professor Zhengya Zhang, Chair Professor Michael Flynn Professor Wei Lu Professor Trevor Mudge Teyuh Chou teyuh@umich.edu © ORCID iD 0000-0001-7033-336X

> © Teyuh Chou 2022 All Rights Reserved

To my family, friends, and coworkers

# TABLE OF CONTENTS

| DEDICATIO   | Ν                                                     | ii   |

|-------------|-------------------------------------------------------|------|

| LIST OF FIG | URES                                                  | v    |

| LIST OF TAI | BLES                                                  | viii |

| ABSTRACT    |                                                       | ix   |

| CHAPTER     |                                                       |      |

| I. Introd   | luction                                               | 1    |

| 1.1         | Deep Neural Networks                                  | 1    |

| 1.2         | Perception Processing                                 | 3    |

| 1.3         | Chiplet Technology                                    | 4    |

| 1.4         | Processing In Memory                                  | 5    |

| 1.5         | Thesis Outline                                        | 6    |

| II. NetFl   | ex: Flexible Chiplet-Based System for Perception Nets | 7    |

| 2.1         | Introduction                                          | 7    |

| 2.2         | Background                                            | 9    |

|             | 2.2.1 DNN-Based SfM Learner                           | 9    |

|             | 2.2.2 Adaptive Layer Skipping for Easy Scenes         | 12   |

|             | 2.2.3 Hardware Implementation Challenges              | 12   |

| 2.3         | NetFlex Architecture                                  | 13   |

|             | 2.3.1 Accelerator Architecture                        | 13   |

|             | 2.3.2 System Architecture                             | 21   |

| 2.4         | Chip Measurement                                      | 23   |

| 2.5         | System Evaluation of 4-Chiplet Package                | 26   |

| 2.6         | Summary                                               | 28   |

| III. AR-P   | IM: PIM with Adaptive Range                           | 30   |

| 3.1         | Introduction                                                                                 |         | . 30  |

|-------------|----------------------------------------------------------------------------------------------|---------|-------|

| 3.2         | SRAM-Based PIM                                                                               |         | . 32  |

| 3.3         | 7nm SRAM PIM Design Considerations                                                           |         | . 35  |

|             | 3.3.1 Input Encoding                                                                         |         | . 35  |

|             | 3.3.2 BL Resolution                                                                          |         | . 36  |

|             | 3.3.3 ADC Resolution and ADC Sharing                                                         |         | . 37  |

|             | 3.3.4 Necessity to Control Resolution                                                        |         |       |

| 3.4         | The AR-PIM Architecture                                                                      |         | . 39  |

|             | 3.4.1 Runtime Density Detection                                                              |         | . 40  |

|             | 3.4.2 Energy Minimization                                                                    |         | . 42  |

| 3.5         | Evaluation                                                                                   |         |       |

|             | 3.5.1 Energy Consumption and Performance                                                     |         | . 44  |

|             | $3.5.2$ Discussion $\ldots$                                                                  |         |       |

| 3.6         | Summary                                                                                      |         |       |

|             |                                                                                              |         |       |

| IV. CASC    | CADE: Chaining PIM in Analog Dataflow                                                        |         | . 50  |

| 4.1         | Introduction                                                                                 |         | . 50  |

| 4.2         | RRAM-Based PIM                                                                               |         | . 54  |

|             | 4.2.1 Workloads and Mapping to RRAM                                                          |         | . 55  |

|             | 4.2.2 In-RRAM Computation                                                                    |         | . 59  |

|             | 4.2.3 A/D Conversion for In-RRAM Computation                                                 | 1       | . 60  |

| 4.3         | The CASCADE Architecture                                                                     |         |       |

|             | 4.3.1 Input Streaming and Weight Mapping in MA                                               | AC RR.  | AM 63 |

|             | 4.3.2 Buffering of Partial Sums in Buffer RRAM                                               |         |       |

|             | 4.3.3 TIA Interface between MAC RRAM and But                                                 | fer RR. | AM 68 |

|             | 4.3.4 Final Accumulation and A/D Conversion .                                                |         | . 69  |

|             | 4.3.5 Noise Tolerance                                                                        |         |       |

| 4.4         | Evaluation                                                                                   |         | . 71  |

|             | $4.4.1  \text{Methodology}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |         | . 73  |

|             | 4.4.2 CASCADE Design Space Exploration                                                       |         |       |

|             | 4.4.3 Performance and Energy Consumption                                                     |         |       |

|             | 4.4.4 Extension to Spiking Neural Networks                                                   |         |       |

| 4.5         | Summary                                                                                      |         |       |

| V. Caral    |                                                                                              |         | 74    |

| V. Concl    | lusion                                                                                       |         | . 79  |

| BIBI IOCD A | РНҮ                                                                                          |         | . 81  |

| DIDUIUGITA  | <b>1 11 1</b>                                                                                | • • • • | . 0.  |

# LIST OF FIGURES

# Figure

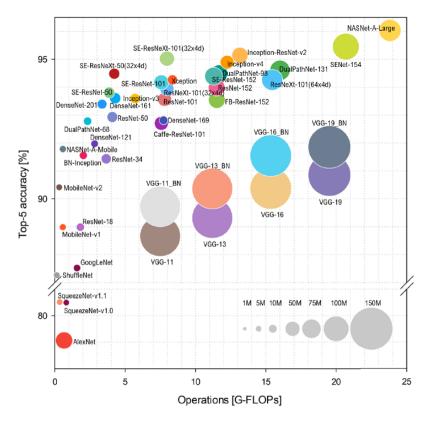

| 1.1  | Complexity represented by circles and operations of DNN models [1]. 2                                              |

|------|--------------------------------------------------------------------------------------------------------------------|

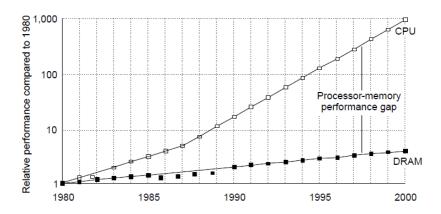

| 1.2  | The performance gap between processor and memory $[2]$ 5                                                           |

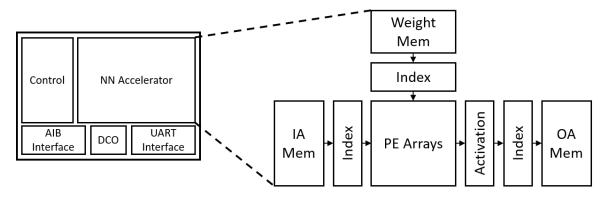

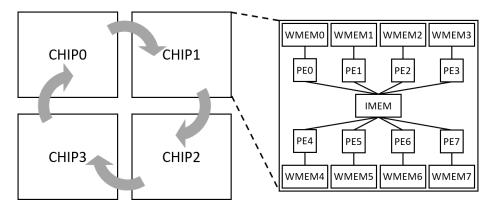

| 2.1  | The NetFlex block diagram                                                                                          |

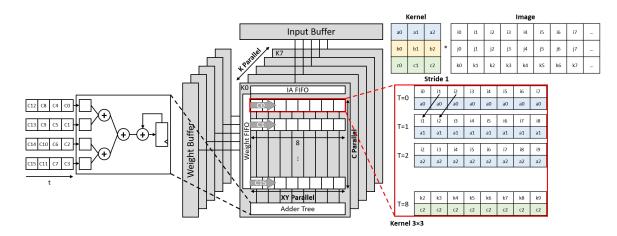

| 2.2  | The convolver design. The zoom in view on the left shows the adder                                                 |

|      | tree design. The zoom in view on the right shows the convolution                                                   |

|      | operation over cycles                                                                                              |

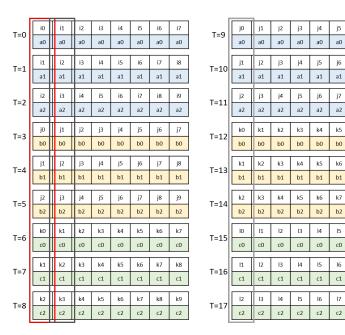

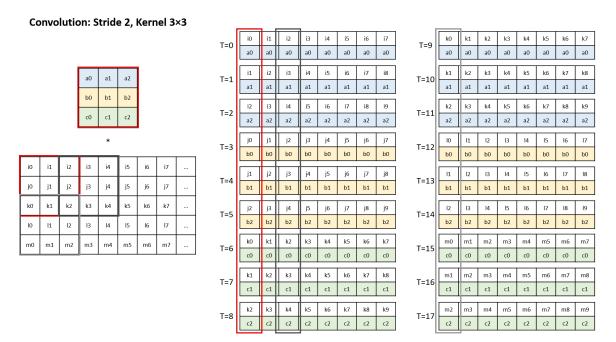

| 2.3  | A convolution operation example of the convolver over cycles for the                                               |

|      | $3 \times 3$ kernel with the stride 1                                                                              |

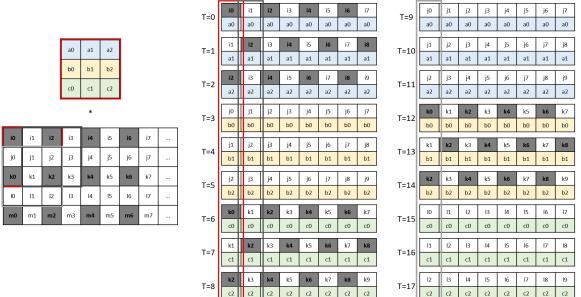

| 2.4  | A convolution operation example of the convolver over cycles for the                                               |

|      | $3 \times 3$ kernel with the stride 2                                                                              |

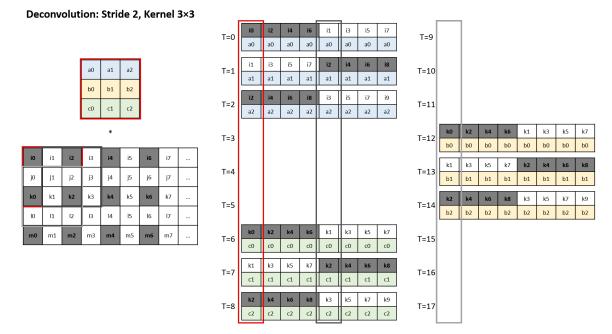

| 2.5  | A deconvolution operation example of the convolver over cycles for                                                 |

|      | the $3 \times 3$ kernel. $\ldots$ |

| 2.6  | A re-organized deconvolution operation example of the convolver over                                               |

|      | cycles for the $3 \times 3$ kernel. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $17$                     |

| 2.7  | The star topology of the core accelerator                                                                          |

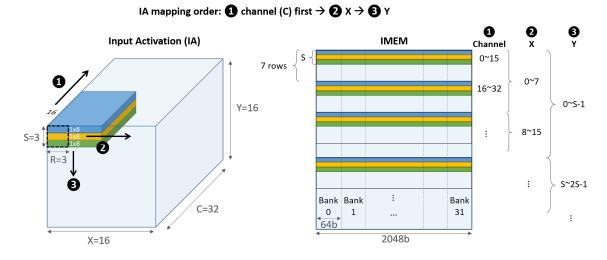

| 2.8  | IA memory mapping                                                                                                  |

| 2.9  | Weight memory mapping                                                                                              |

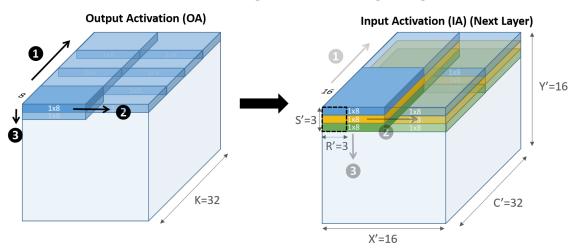

| 2.10 | The OA order from the convolver output                                                                             |

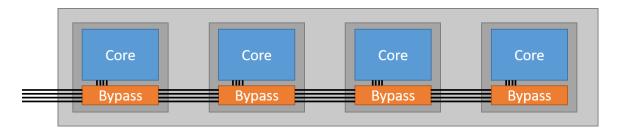

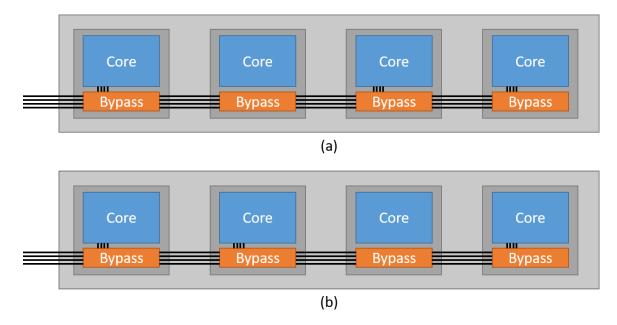

| 2.11 | The 4 chiplet streaming topology in the normal mode                                                                |

| 2.12 | The 4 chiplet streaming topology in the bypass mode                                                                |

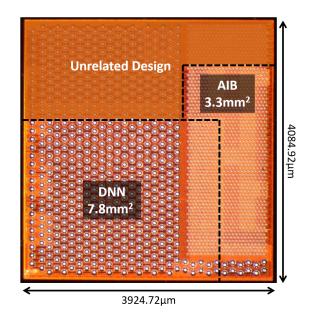

| 2.13 | Die photo. $\ldots \ldots 23$         |

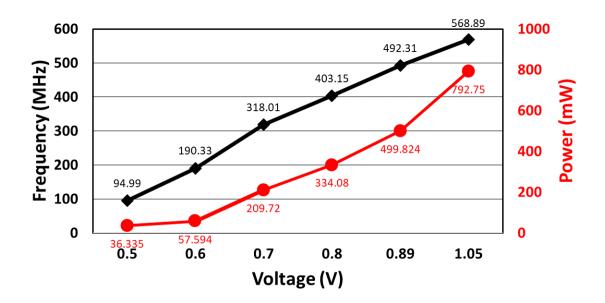

| 2.14 | Frequency and power consumption with the voltage scaling 24                                                        |

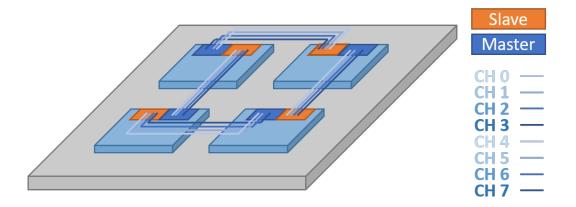

| 2.15 | Package photo of the 4-chiplet system                                                                              |

| 2.16 | A face to back connection of 4 chiplets                                                                            |

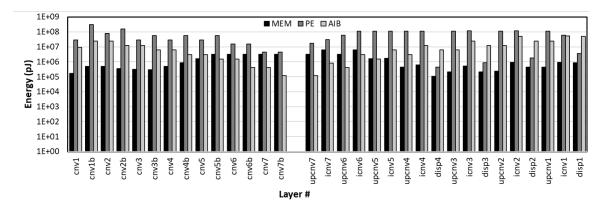

| 2.17 | Energy consumption of SfM depth net                                                                                |

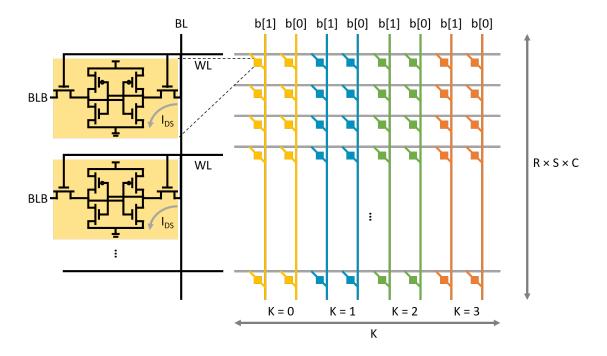

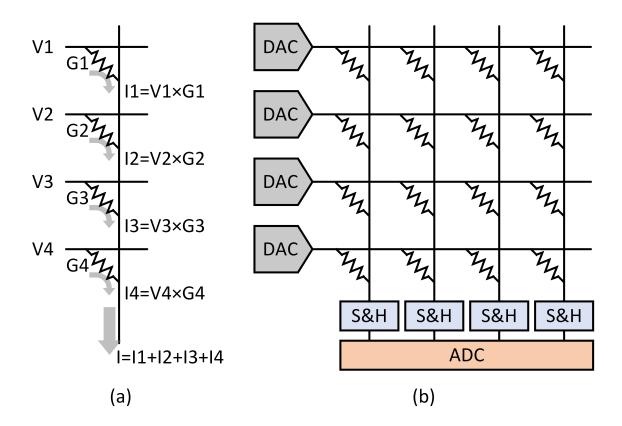

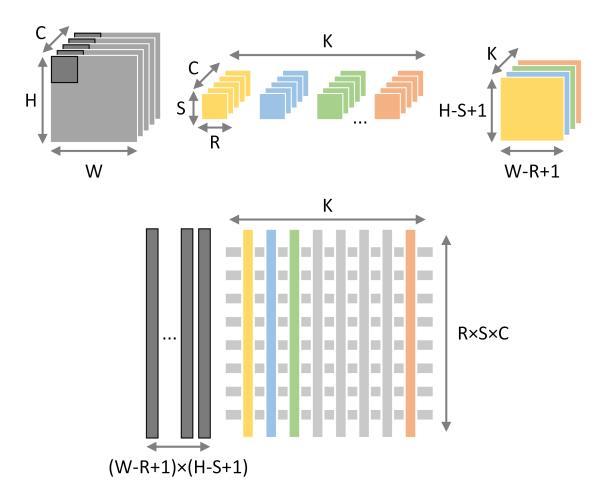

| 3.1  | The PIM mapping of the convolution operation where $R \times S$ is the                                             |

|      | kernel size, $C$ is the input channel and $K$ is the output channel.                                               |

|      | The 2b weight in the example is stored in two columns. The zoom-in                                                 |

|      | view shows the 6T SRAM and current $I_{DS}$ discharged by each bitcell.                                            |

|      | Both baseline PIM and AR-PIM adopt this mapping for convolution                                                    |

|      | operation. $\ldots \ldots 33$                       |

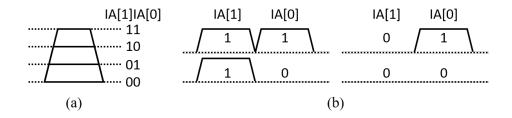

| 3.2         | The multi-bit (2b in the example) input representation of (a) WL pulse level and (b) WL pulse train                                                                                                                                                                        | 9        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <u></u>     | pulse level and (b) WL pulse train.                                                                                                                                                                                                                                        | $3_{4}$  |

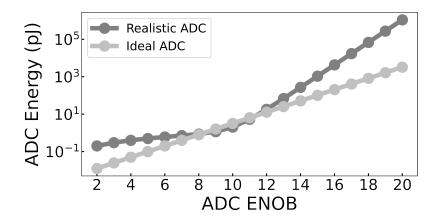

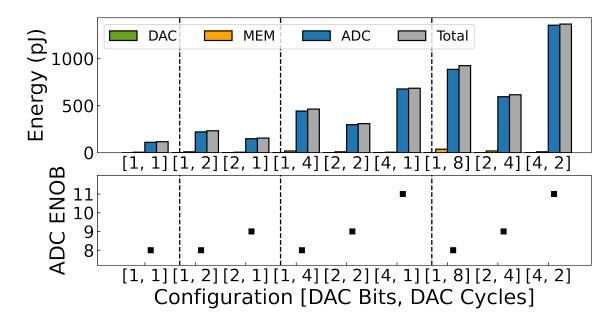

| 3.3         | ADC energy consumption with effective number of bits (ENOB) from [3]                                                                                                                                                                                                       | 3.       |

| 3.4         | Energy efficiency of 1b, 2b, 4b, 8b input activation. The different                                                                                                                                                                                                        |          |

|             | input encoding for each configuration is implemented by DAC bits                                                                                                                                                                                                           |          |

|             | and DAC cycles with the corresponding ADC resolution                                                                                                                                                                                                                       | 30       |

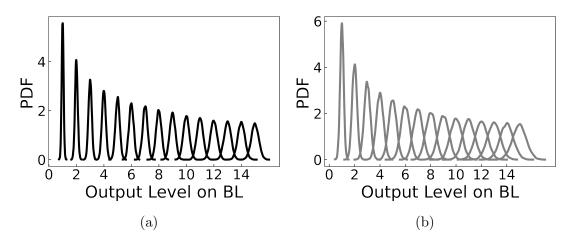

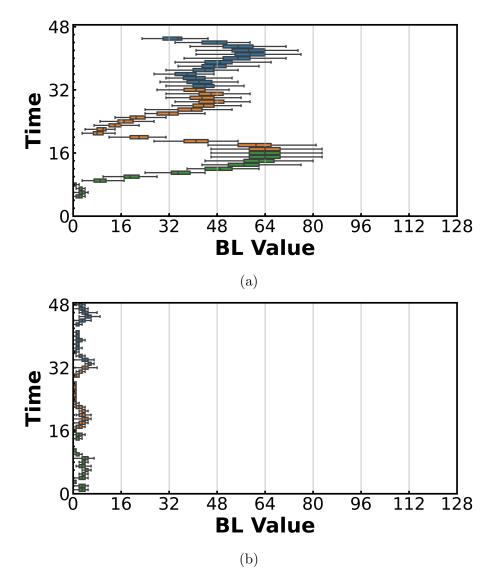

| 3.5         | SRAM BL current levels from SPICE simulation for WL voltage of<br>(a) 0.8V and (b) 0.6V. Each Gaussian distribution represents one<br>output level. The less overlap between two distributions means the                                                                   |          |

|             | better sensing margin for distinguishing two output levels                                                                                                                                                                                                                 | 3'       |

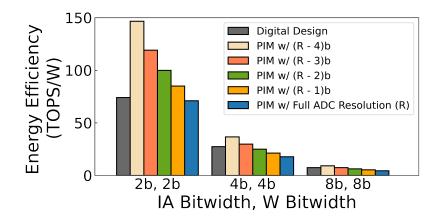

| 3.6         | The energy efficiency comparison for synthesized digital design and                                                                                                                                                                                                        | 0        |

| 5.0         | PIM design with different BL resolutions and 3 Input Activation (IA)                                                                                                                                                                                                       |          |

| ~ -         | and Weight (W) bitwidth combinations.                                                                                                                                                                                                                                      | 38       |

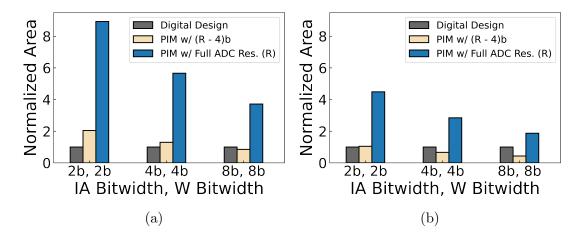

| 3.7         | Area comparison between synthesized digital design and PIM design                                                                                                                                                                                                          | 0        |

| 2.0         | for (a) 1 ADC per BL and (b) 1 ADC shared by 2 BLs                                                                                                                                                                                                                         | 38       |

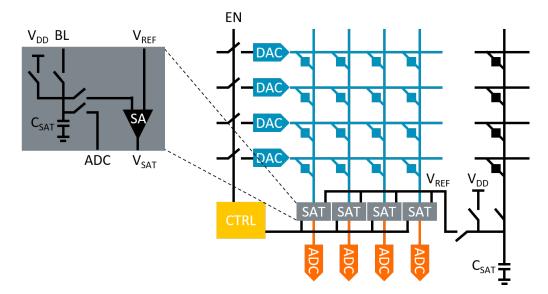

| 3.8         | AR-PIM architecture with BL detection circuitry.                                                                                                                                                                                                                           | 40       |

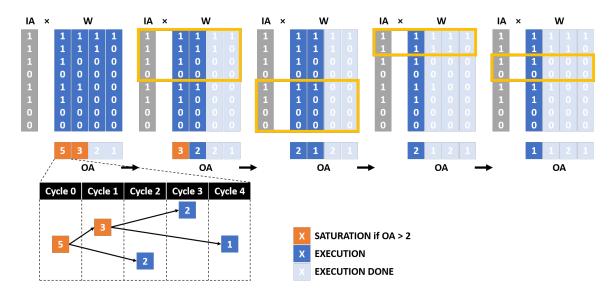

| 3.9         | Example of runtime density detection and adaptation.                                                                                                                                                                                                                       | 4        |

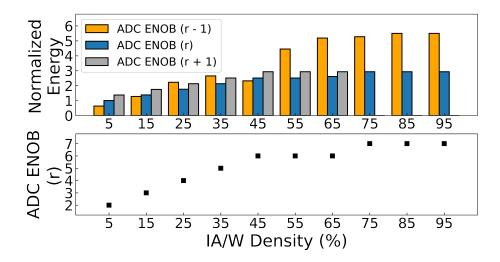

| 3.10        | Energy of AR-PIM for IA/W density from $5\%$ to $95\%$ with conditions of ADC ENOB r-1, r, r+1 (top) and ADC ENOB r for IA/W density                                                                                                                                       |          |

|             | from 5% to 95%. $\ldots$                                                                                                                                                                                                                                                   | 42       |

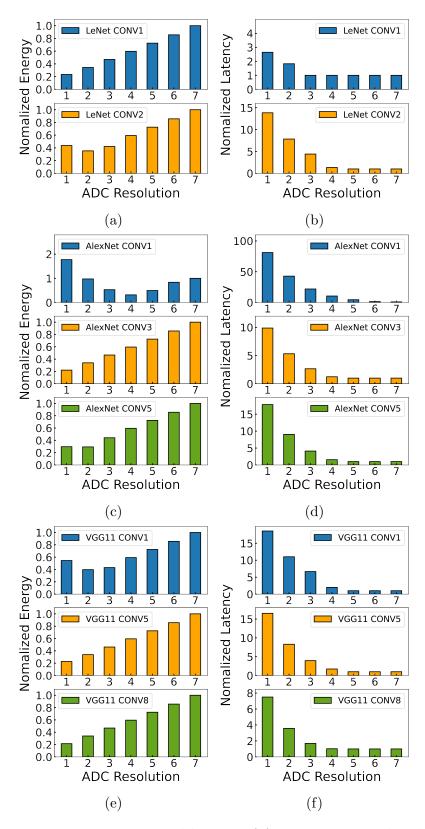

| 3.11        | Energy consumption and latency of AR-PIM compared and normal-<br>ized to the baseline PIM with 7b ADC resolution (the rightmost bar<br>in each figure) for each layer running (a)(b) LeNeT using MNIST<br>dataset, (c)(d) AlexNet using ImageNet dataset, and (e)(f) VGG11 | 4        |

| 0.10        | using ImageNet.                                                                                                                                                                                                                                                            | 48       |

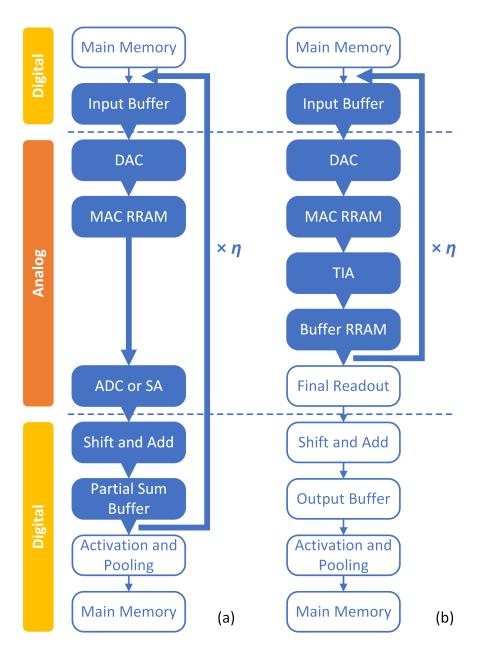

| 3.12<br>4.1 | Latency overhead                                                                                                                                                                                                                                                           | 49<br>54 |

| 4.2         | Mapping of convolution operation on an RRAM crossbar array                                                                                                                                                                                                                 | 50       |

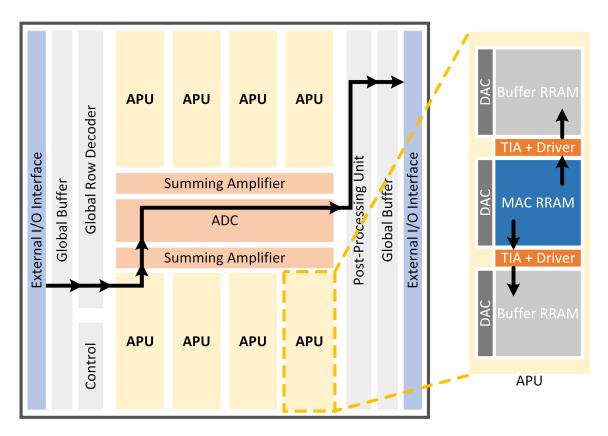

| 4.3         | Illustration of the CASCADE architecture. The bold lines indicate<br>the proposed dataflow. The zoom-in view shows an analog processing                                                                                                                                    | 0        |

| 4.4         | unit (APU). $\dots$ DDAM MAC $\dots$ $\dots$ $\dots$ $\dots$ $\dots$                                                                                                                                                                                                       | 65       |

| 4.4         | Comparison of (a) in-RRAM MAC and digital accumulation of par-<br>tial sums, and (b) in-RRAM MAC and in-RRAM buffering and ac-<br>cumulation of partial sums. The dashed lines indicate D/A and A/D                                                                        |          |

|             | boundaries. The inner loop is highlighted in blue.                                                                                                                                                                                                                         | 6        |

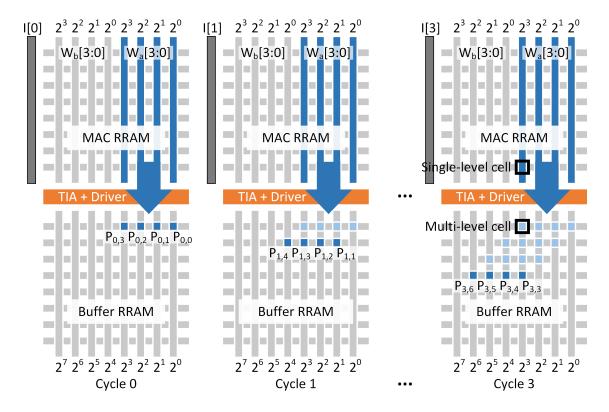

| 4.5   | Illustration of R-Mapping for 4-bit weights and 4-bit inputs. The inputs are serially streamed in with LSB first. The MAC RRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | stores two sets of 4-bit weights $W_a$ and $W_b$ . The arrows indicate the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|       | align and store of partial sums through TIAs and input drivers. The partial sum $P_{i}$ is stored in the <i>i</i> th row and <i>i</i> th column in cucle <i>i</i> of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|       | partial sum $P_{i,j}$ is stored in the <i>i</i> th row and <i>j</i> th column in cycle <i>i</i> of the buffer RRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66 |

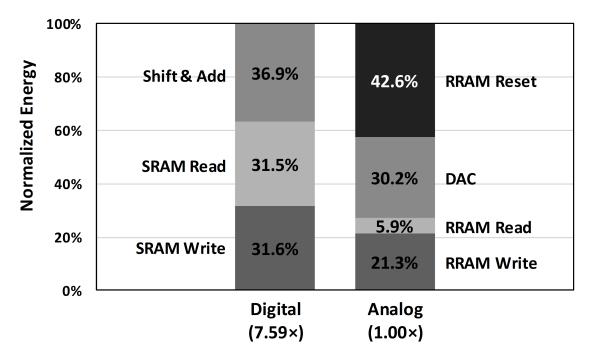

| 4.6   | Normalized energy consumption of digital partial-sum accumulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00 |

| 4.0   | and analog in-RRAM partial-sum buffering and accumulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67 |

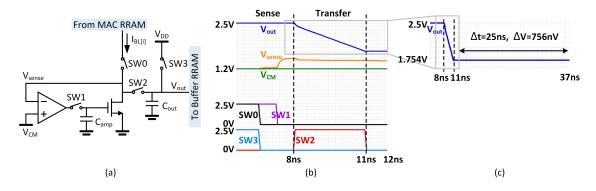

| 4.7   | (a) Schematic of TIA for converting an input current to a propor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01 |

|       | tional output voltage; (b) simulation waveforms of the TIA designed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|       | in a 65nm CMOS technology and the charge leakage of the output ca-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|       | pacitor over 25ns of the buffer RRAM write period; and (c) zoom-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|       | view of the TIA sensing and transfer phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69 |

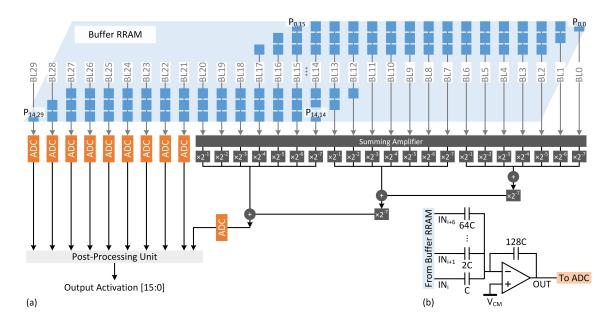

| 4.8   | (a) Illustration of the final accumulation; and (b) schematic of a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|       | summing amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

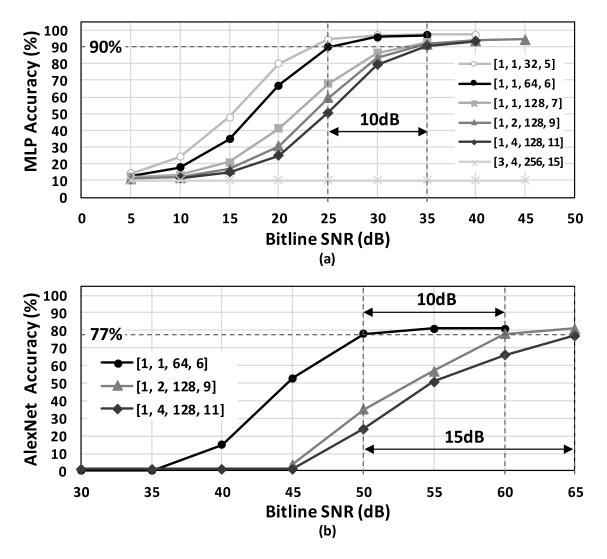

| 4.9   | (a) Two-layer MLP classification accuracy for different configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|       | noted by $[b_{WL}, b_{cell}, N_{rows}, b_{BL}]$ , and (b) AlexNet top-5 classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|       | accuracy for CASCADE and configurations based on ISAAC and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 4.10  | PipeLayer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

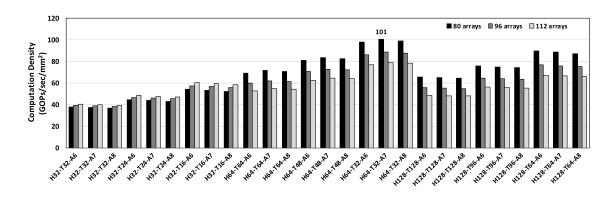

| 4.10  | Computation density across the design space. A notation, e.g., H64-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|       | T32-A7 R80, represents 80 $64 \times 64$ RRAM arrays with 32 TIAs per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 1 1 1 | array and 7 ADCs shared by the arrays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

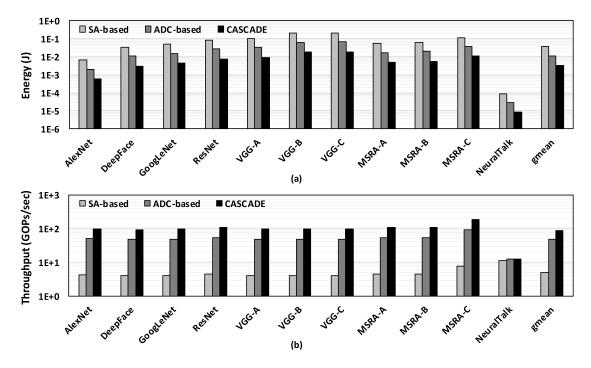

| 4.11  | (a) Energy consumption of CASCADE compared to reference archi-<br>tectures running DNN and RNN benchmarks; (b) Throughput of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|       | CASCADE compared to reference architectures running DNN and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|       | RNN benchmarks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

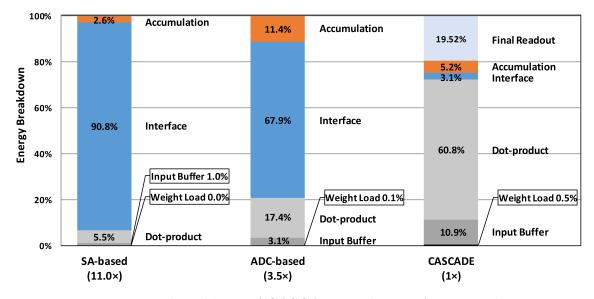

| 4.12  | Energy breakdown of CASCADE and two reference architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

|       | Lines J stream of on some and the reference dream of the stream of the s |    |

# LIST OF TABLES

## <u>Table</u>

| 2.1 | The detailed configuration of depth net                                 | 11 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | The detailed configuration of pose net.                                 | 12 |

| 2.3 | Measurement results for various configurations                          | 24 |

| 2.4 | Comparison with prior works for perception.                             | 25 |

| 2.5 | Microarchitecture parameters of NetFlex. The package-level results      |    |

|     | are from $[4]$                                                          | 27 |

| 2.6 | Comparison of chiplet-based prototypes.                                 | 27 |

| 3.1 | Mean and standard deviation of BL density numbers. (The maximum         |    |

|     | BL density is 128 for a $128 \times 128$ array.)                        | 43 |

| 4.1 | In-RRAM MAC architecture comparison                                     | 59 |

| 4.2 | Configurations of the CASCADE, ADC-based and SA-based refer-            |    |

|     | ence architectures                                                      | 73 |

| 4.3 | Benchmarks for evaluation. Convolution layers are denoted as $R \times$ |    |

|     | S, K/D (L), where R, S and K correspond to the notations used in        |    |

|     | Figure 4.2, and $L$ denotes the number of such layers                   | 74 |

|     |                                                                         |    |

#### ABSTRACT

Machine learning is a key application driver of new computing hardware. Designing high-performance machine learning hardware requires a large number of operations and a high memory bandwidth. The energy efficiency of the hardware is often limited by the data movement and the memory access bottleneck. As the machine learning models evolve to become even larger and more complex over time, it is also a constant challenge to meet the computational requirements of these new models. In this work, we investigate processing in memory (PIM) approaches to overcome the memory access bottleneck and a chiplet-based integration approach to efficiently scale up machine learning hardware by reusing chiplets.

DNN model size and complexity growths have already outpaced the DNN chip upgrades. Making monolithic chips to keep up with the model evaluations is challenging. We demonstrate a chiplet-based approach to designing DNN hardware. The proposed chiplet is called NetFlex – a modular design that can be connected together to build larger DNN hardware. NetFlex is designed to support various layers, including convolutional layer, deconvolutional layer, and fully connected layer, and multiple configurations. The deconvolution dataflow is optimized by removing computation of both row-wise and element-wise 0s. In the PE arrays, spatial processing with three dimensional parallelism is implemented for data reuse and temporal processing is chosen to adapt to different kernel sizes. The processing scheduling and memory mapping are designed for streaming activations without extra data rearrangement. The chiplets are connected to form a ring topology and can be gated by the skipping module to reduce the computation and memory accesses of simple scenes for perception. An Advanced Interface Bus (AIB) and an Advanced eXtensuble Interface (AXI)-compatible protocol enable data streaming from one chiplet to another chiplet. The chiplets are integrated on the interposer using a 2.5D fan-out wafer level packaging (FOWLP) technology. NetFlex is compared with recent silicon prototypes for perception application. The multi-chiplet system is evaluated and compared with recent chiplet-based designs. The results shows NetFlex achieves a higher throughput with competitive energy and area efficiency and can potentially expand to larger-scale systems.

PIM approach has gained significant attention due to its potential of high energy efficiency for DNN workloads. However, key challenges remain: the overhead of high-resolution ADCs and degraded sensing margin when a large number of bitcells are activated together. We propose adaptive-range PIM (AR-PIM) to take advantage of sparsity to relax the need for high-resolution ADCs and improve the sensing margin. The evaluations, performed using a commercial 7nm FinFET PDK, show that AR-PIM increases the energy efficiency by  $1.7 \times$  and reduces the area by  $4.3 \times$ over a baseline PIM architecture for DNN workloads while maintaining the inference accuracy.

PIM is a concept to enable massively parallel dot products while keeping one set of operands in memory. PIM is ideal for computationally demanding deep neural networks (DNNs) and recurrent neural networks (RNNs). Processing in resistive RAM (RRAM) is particularly appealing due to RRAM's high density and low energy. A key limitation of PIM is the cost of multi-bit analog-to-digital (A/D) conversions that can defeat the efficiency and performance benefits of PIM. We demonstrate the CASCADE architecture that connects multiply-accumulate (MAC) RRAM arrays with buffer RRAM arrays to extend the processing in analog and in memory: dot products are followed by partial-sum buffering and accumulation to implement a complete DNN or RNN layer. Design choices are made and the interface is designed to enable a variation-tolerant, robust analog dataflow. A new memory mapping scheme named R-Mapping is devised to enable the in-RRAM accumulation of partial sums; and an analog summation scheme is used to reduce the number of A/D conversions required to obtain the final sum. CASCADE is compared with recent in-RRAM computation architectures using state-of-the-art DNN and RNN benchmarks. The results demonstrate that CASCADE improves the energy efficiency by  $3.5 \times$  while maintaining a competitive throughput.

These three parts, NetFlex, AR-PIM and CASCADE demonstrate more energyefficient and scalable solutions for future machine learning hardware designs.

## CHAPTER I

## Introduction

Machine learning algorithms demonstrate remarkable successes in recent years and open a new era of artificial intelligence (AI). The supervised learning is conducted with the labeled inputs and the unsupervised learning for non-labeled inputs. The advances in hardware such as GPUs to deal with the large amount of computations boost the growth of the field. The other hardware options including CPUs, FPGAs, and ASICs are also proposed for different use cases. However, key bottlenecks and challenges still persist. One is the memory wall bottleneck that limits the performance and processing efficiency improvement. The other is the scalability of the current hardware in handling fast evolving model of larger sizes as shown in Figure 1.1.

#### 1.1 Deep Neural Networks

Neural networks are one subset of machine learning algorithms, and they have evolved to be one primary workload for new computing hardware. A neural network layer consists of the input layer, the hidden layers, and the output layer. In a fully connected layer, the neurons of one layer are fully connected to all neurons of previous layer. The weights of each layer are trained using gradient descent. The error of the last layer from forward propagation and the label is required for backpropagation during training. The weights can be used to predict the classification class of the

Figure 1.1: Complexity represented by circles and operations of DNN models [1].

unseen data during inference.

A convoluational layer can be represented in 3D volumes of neurons in 3 dimensions, width, height, and depth. Only a small number of neurons in one layer are connected to the layer before it. Convolutional neural networks (CNNs), and generally deep neural networks (DNNs), typically have convolution layers, ReLU layers which apply the non-linearity, pooling layers, and fully-connected layer. DNN computation consists of a large number of matrix multiplication operations with plenty of opportunities to compute in parallel.