## Wide Bandgap Semiconductor-Based Power Converters for Electric Vehicle Applications

by

## Guanliang Liu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan-Dearborn 2022

#### **Doctoral Committee:**

Associate Professor Mengqi Wang, Chair Assistant Professor Junho Hong Assistant Professor Zhen Hu Associate Professor Wencong Su

#### Acknowledgements

During my whole Ph.D period, I received lots of help from my advisor, department, my family, and ECE department. Without all these help, I cannot get my Ph.D degree. Thanks to all the people who helped me in my Ph.D period. First of all, Thanks to my advisor Prof.Mengqi Wang in my Ph.D period She were always ready to help me on any academic questions.

Meanwhile, thanks to my master advisor Dr.Bai Hua. He trained me how to do a outstanding research in USA.Also, thanks to my undergraduate advisor Dr.Xiaofeng Ding, He is the first person who guided me to begin my research life. I would like to express my gratitude to my parents Wei Liu and Haiying Leng. Without their tremendous understanding and encouragement in the past few years, it would be impossible for me to complete my study. Finally I would like to thank my my previous lab members. Their help made me have a wonderful time in my Ph.D period.

# **Table of Contents**

| Acknowledgements                                                         | ii  |

|--------------------------------------------------------------------------|-----|

| List of Tables                                                           | vi  |

| List of Figures                                                          | vii |

| Abstract                                                                 | xv  |

| Introduction                                                             | 1   |

| Chapter 1 Introduction to EV and Power Converters                        | 2   |

| 1.1 EV Development                                                       | 2   |

| 1.2 Power Converters in EV                                               | 4   |

| 1.3 On-Board Charger Topologies                                          | 5   |

| 1.4 DC-DC Converter Topology                                             | 7   |

| 1.5 Traction Inverter Topology                                           | 9   |

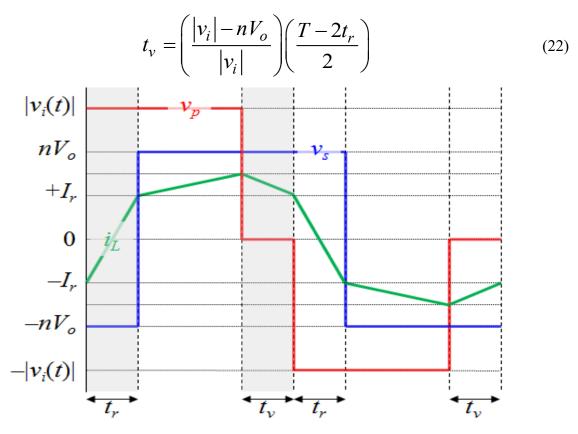

| Chapter 2 Benefits of WBG in EV Power Converters                         | 11  |

| 2.1 Wide Band Gap Devices Material Characteristic                        | 11  |

| 2.2 WBG Device Packages                                                  | 12  |

| Chapter 3 On-Board Charger Design Case with GaN                          | 14  |

| 3.1 GaN Gate and Power Loop Design                                       | 14  |

| 3.1.1 Introduction                                                       | 14  |

| 3.1.2 Modelling Dynamic Behavior of Paralleled Gan Hemts with Parasitics | 19  |

| 3.1.3 Parasitic Optimization of GaN Power Modules                        | 29  |

| 3.1.4 Gate Driver Design                                                 | 32  |

| 3.1.5 Experimental Verification                                          | 34  |

| 3.1.6 Applying Gan-HEMTs Power Modules in High-efficiency Systems                 | 35  |

|-----------------------------------------------------------------------------------|-----|

| 3.1.7 Soft-switched DC/DC Converter                                               | 36  |

| 3.1.8 Hard-switched DC/DC Converter                                               | 40  |

| 3.1.9 GaN Design Prototype and Experiments                                        | 42  |

| 3.2 Control Strategies Optimization of DAB                                        | 51  |

| 3.2.1 Introduction                                                                | 51  |

| 3.2.2 VSF DPS, TPS & MPS                                                          | 53  |

| 3.2.3 TPS for Light-load Operation                                                | 57  |

| 3.2.4 MPS for All Operating Conditions                                            | 63  |

| 3.2.5 Experimental Validation of MPS                                              | 67  |

| 3.2.6 Optimization at Light-load Efficiency                                       | 73  |

| 3.2.7 Conclusion                                                                  | 80  |

| 3.3 GaN and Si Hybrid Switch                                                      | 81  |

| 3.3.1 Introduction                                                                | 81  |

| 3.3.2 Design and Challenges                                                       | 83  |

| 3.3.3 Design Solution and Layout                                                  | 90  |

| 3.3.4 Performance Evaluation                                                      | 93  |

| 3.3.5 Conclusion                                                                  | 99  |

| Chapter 4 Interleaved Boost Converter Design Case with Sic Power Module           | 101 |

| 4.1 Interleaved Boost Converter Hardware and Software Overall Optimization Design | 101 |

| 4.1.1 Introduction                                                                | 101 |

| 4.1.2 Overall System Mathematical Model                                           | 103 |

| 4.1.3 Multiple Objective Optimization                                             | 108 |

| 4.1.4 Hardware Component's Design                                                 | 112 |

| 4.1.5 Multiple Optimization Algorithm NSGA-II Application                         | 115 |

| 4.1.6 Conclusions                                                            | 117 |

|------------------------------------------------------------------------------|-----|

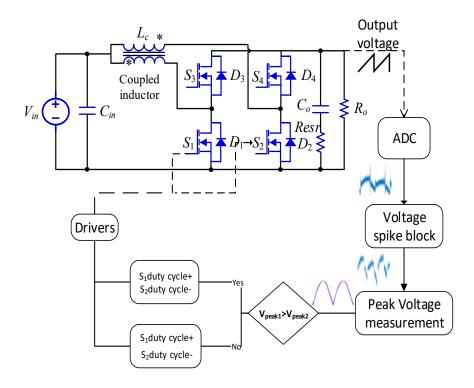

| 4.2 Current Senseless Control for Multiple Phase Interleaved Boost Converter | 118 |

| 4.2.1 Introduction                                                           | 118 |

| 4.2.2 Sensorless Current Control Theory and Calculation Formulas             | 124 |

| 4.2.3 The Proposed Sensorless Control Method                                 | 134 |

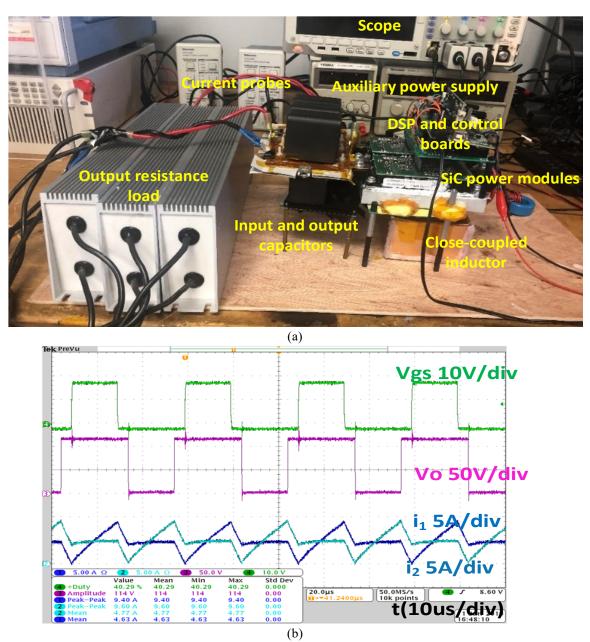

| 4.2.4 Experiment Test Bench and Results                                      | 138 |

| 4.2.5 Conclusions                                                            | 150 |

| Chapter 5 T-Type Traction Inverter Design                                    | 151 |

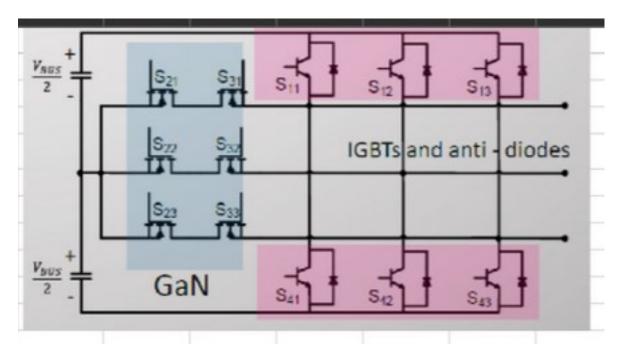

| 5.1 Introduction                                                             | 151 |

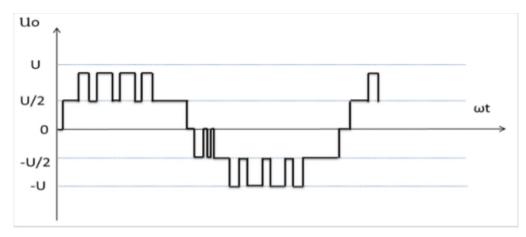

| 5.2 The GaN Application in the T-Type Inverter                               | 153 |

| 5.3 Proposed Hybrid Control Method                                           | 157 |

| 5.4 Conclusion                                                               | 159 |

| Chapter 6 DC Link Capacitor Degradation Investigation                        | 160 |

| 6.1 Introduction                                                             | 160 |

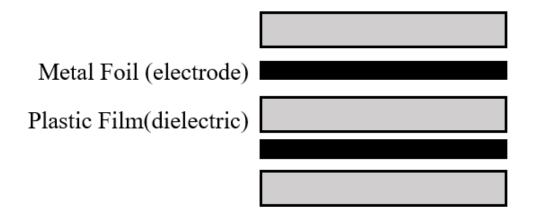

| 6.2 MCF Capacitor Degradation Principle                                      | 161 |

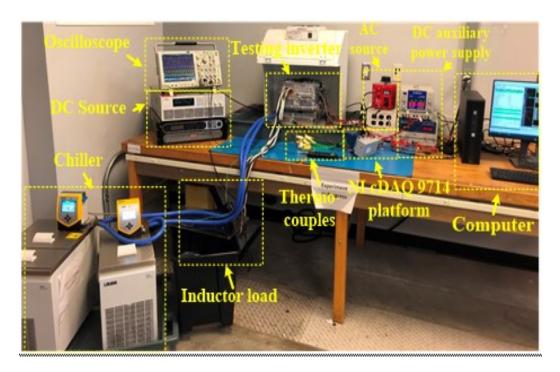

| 6.3 The Test Bench Setup and Operating Conditions                            | 163 |

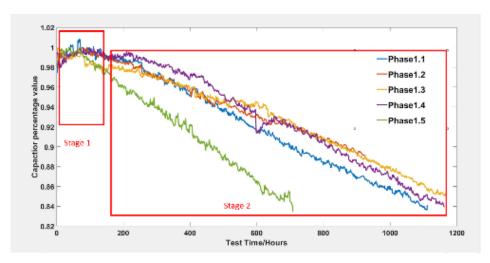

| 6.4 Two-stage Capacitance Degradation Model                                  | 165 |

| 6.5 Test Results and Analysis                                                | 167 |

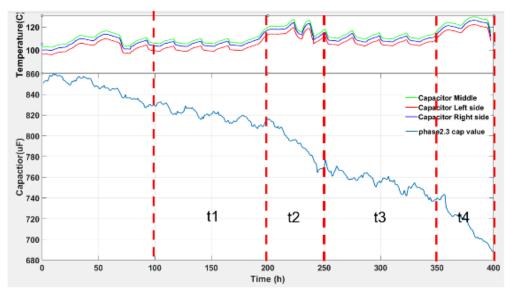

| 6.6 Capacitor Temporary Short Circuit                                        | 169 |

| 6.7 Conclusions                                                              | 171 |

| Chapter 7 Conclusion                                                         | 172 |

| References                                                                   | 173 |

# **List of Tables**

| Table 1 Possible candidates of GaN HEMTs                                | 15  |

|-------------------------------------------------------------------------|-----|

| Table 2 Values of key parameters                                        | 42  |

| Table 3 Comparison of dual, triple, and multiple phase shift strategies | 67  |

| Table 4 SiC-based DAB system parameters & test conditions.              | 67  |

| Table 5 Definition of parameters                                        | 85  |

| Table 6 400V 80A switching simulation table                             | 92  |

| Table 7 600V film capacitors comparison                                 | 113 |

| Table 8 800V film capacitors comparison                                 | 113 |

| Table 9 The MOSFETs' parameters                                         | 114 |

| Table 10 A comparison between different current balancing methods       | 121 |

| Table 11 The test bench components' parameters                          | 139 |

| Table 12 IGBT and MOSFET parameters                                     | 154 |

| Table 13 Environmental tests and number of samples                      | 164 |

| Table 15 DC link capacitor short circuit point value                    | 170 |

# **List of Figures**

| Figure 1 Global EV car sales                                                                          | 2  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2 Global EV sales distribution                                                                 | 3  |

| Figure 3 OEM EV development plan                                                                      | 3  |

| Figure 4 EV circuit diagram                                                                           | 4  |

| Figure 5 Classic boost PFC circuit                                                                    | 5  |

| Figure 6 Full bridge LLC topology                                                                     | 6  |

| Figure 7 DAB topology                                                                                 | 6  |

| Figure 8 Typical boos converter topology                                                              | 7  |

| Figure 9 Interleaved boost converter topology                                                         | 8  |

| Figure 10 Traction inverter topology                                                                  | 9  |

| Figure 11 T-type inverter topology                                                                    | 10 |

| Figure 12 WBG material characterize                                                                   | 11 |

| Figure 13 SiC and GaN structure                                                                       | 12 |

| Figure 14 SiC and GaN device packages (a) Power module (b) through-hole package(c) Surfmount package. |    |

| Figure 15 Structure of E-mode GaN HEMTs.                                                              | 14 |

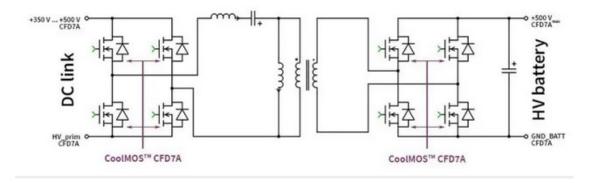

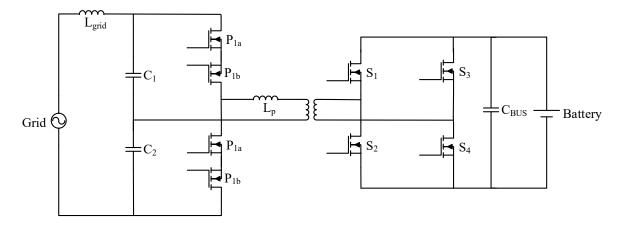

| Figure 16 A conventional single-phase isolated charger                                                | 16 |

| Figure 17 A conventional three-phase isolated charger                                                 | 16 |

| Figure 18 Single-phase single-stage bidirectional isolated ZVS AC-DC converter                        | 18 |

| Figure 19 Charger topology adopted in this on-board charger                                           | 18 |

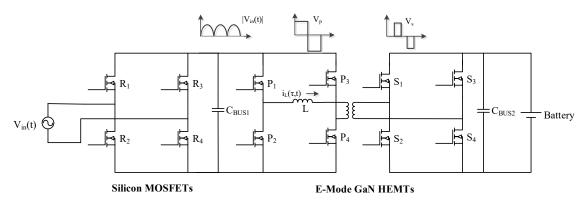

| Figure 20 (a) Switching Energy of GS66516T (b)Leadless Top-Cooled Packaging of GaN HEMTs (GS66516T)   | 19 |

| Figure 21 V-I Curve of GS66516T vs. Temperature                          | 20 |

|--------------------------------------------------------------------------|----|

| Figure 22 A Half Bridge with 2x GaN HEMTs in Parallel                    | 21 |

| Figure 23 V <sub>DS</sub> , I <sub>DS</sub> Waveform During Switching on | 22 |

| Figure 24 State Transition of GaN HEMT During Switching on               | 22 |

| Figure 25 Equivalent Circuit during di/dt Period of Switching on Process | 23 |

| Figure 26 Equivalent Circuit during dv/dt Period of Switching on Process | 25 |

| Figure 27 Waveform During the Switching-off                              | 27 |

| Figure 28 State Trajectory of GaN HEMT During the Switching-off          | 27 |

| Figure 29 Effects and Design Rules of Parasitic Parameters               | 29 |

| Figure 30 Layout of 650V/240A GaN HEMTs based Half Bridge                | 31 |

| Figure 31 GaNpxTM Packaging                                              | 31 |

| Figure 32 Miller Clamp Circuit                                           | 32 |

| Figure 33 Two-gate-terminal Circuit                                      | 33 |

| Figure 34 Gate-Drive Circuit used for GaN HEMTs                          | 33 |

| Figure 35 Prototype of 650V/240A GaN HEMTs based Half Bridge             | 34 |

| Figure 36 Current Balancing Among Four Paralelled Switches               | 35 |

| Figure 37 Double Pulse Test Waveform @400V/240 A                         | 35 |

| Figure 38 Impact of Coss on Zero Voltage Switching Process               | 36 |

| Figure 39 Current Spike Measurement with Double Pulse Test Platform      | 37 |

| Figure 40 Coss Charge @ Different Load Current                           | 38 |

| Figure 41 Switching-loss Comparison w/n Anti-Parallel Diodes             | 39 |

| Figure 42 The Three-level Topology with 650V GaN HEMTs                   | 40 |

| Figure 43 The Conventional Buck Converter with 1200V SiC MOSFETs         | 41 |

| Figure 44 System Loss Breakdown Comparison between Two Solutions         | 41 |

| Figure 45 DPT with four GaN HEMTs in parallel                            | 43 |

| Figure 46 Current Sharing among Paralleled HEMTs @ 400V/56A During the Turn-off Processing and Processing among Paralleled HEMTs and Authority (1984).                                                                    |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 47 Prototype of the Single-phase Charger (left- the charger, right-charger with the enclosure)                                                                                                                     | 44 |

| Figure 48 PCBs of the Whole Charger (from left to right: GaN HEMT PCB, control PCB and rectifier PCB)                                                                                                                     |    |

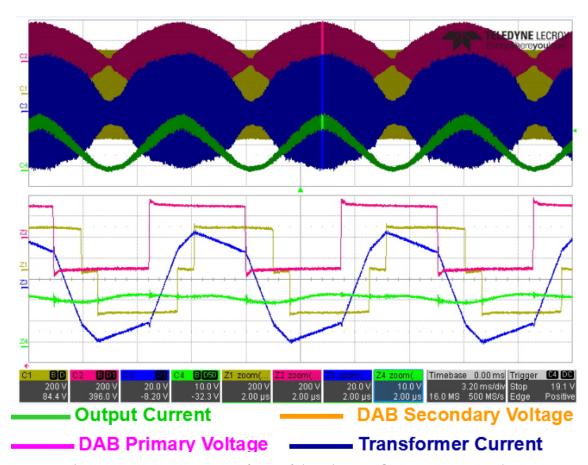

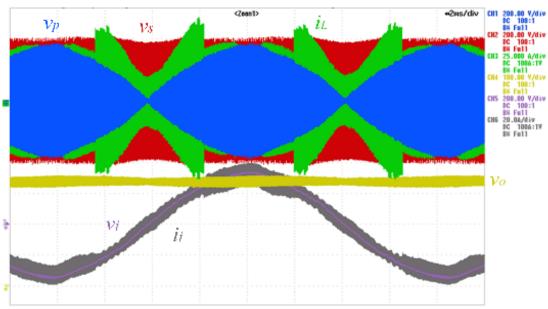

| Figure 49 DAB Stage Waveform of the Charger @Vo=400V, P=7.2kW                                                                                                                                                             | 45 |

| Figure 50 DAB Stage Waveform of the Charger @Vo=200V, P=4kW (yellow-DAB primary voltage, 100V/div; purple-DAB secondary voltage, 100V/div;                                                                                |    |

| Figure 51 TPS control at the 100W (yellow-transformer primary voltage, 100V/div; purple-transformer current, 1A/div; green-transformer secondary voltage, 100V/div; red-grid voltage 100V/div; brown-grid current 1A/div) |    |

| Figure 52 grid-current-harmonics distribution                                                                                                                                                                             | 47 |

| Figure 53 The Three-phase Charger Using Three Single-phase Modules (left) and Its Enclosu (right)                                                                                                                         |    |

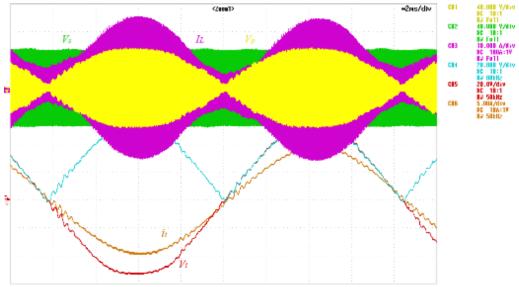

| Figure 54 Three-phase-charger Test Result @5kW (yellow-Io: 3A/div; Ioa, Iob, Ioc: 3A/div; grey&purple-grid phase voltage Vgrid_a&b: 100V/div)                                                                             | 49 |

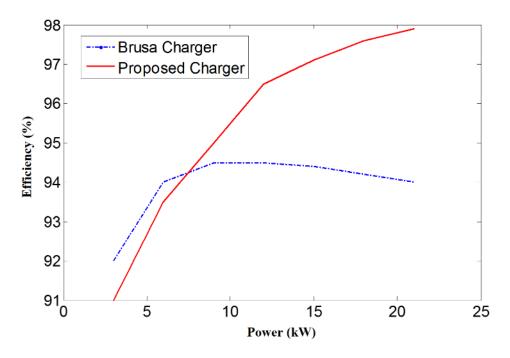

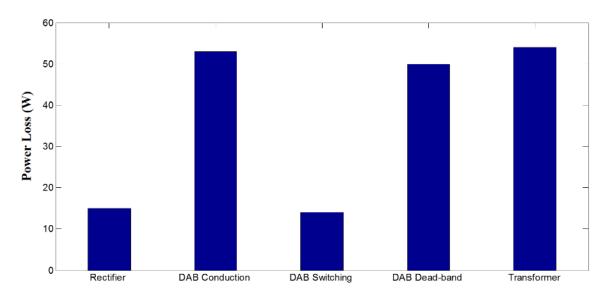

| Figure 55 Efficiency Comparison (GaN vs Si)                                                                                                                                                                               | 50 |

| Figure 56 Power loss breakdown (per phase)                                                                                                                                                                                | 50 |

| Figure 57 Power Density Comparison (left- Si Charger of 2kW/L, right- GaN charger of 3.3kW/L)                                                                                                                             | 51 |

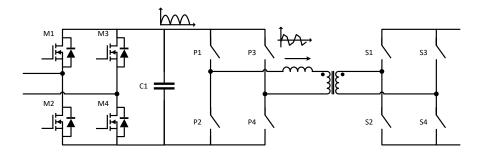

| Figure 58 Topology of the on-board level-2 battery charger used in this paper                                                                                                                                             | 52 |

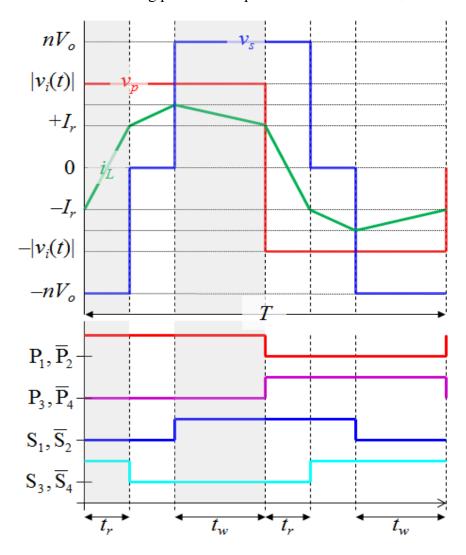

| Figure 59 Output voltage of the DAB primary side and secondary side, current of the primary inductor, and gate signals of all switches during SDPS                                                                        |    |

| Figure 60 Output voltage of the DAB primary side (red) and secondary side (blue) and currenthe primary side (green) during PDPS                                                                                           |    |

| Figure 61 Simulated converter input voltage & current using DPS @ 7.2 kW                                                                                                                                                  | 57 |

| Figure 62 Voltage, current, & switching waveforms of non-overlap TPS.                                                                                                                                                     | 58 |

| Figure 63 Voltage & current waveforms of TPS during the overlap case.                                                                                                                                                     | 59 |

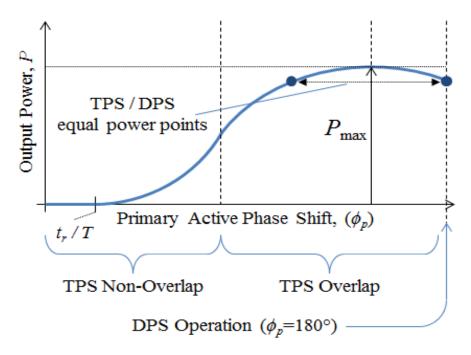

| Figure 64 Output power vs. primary active phase shift when  vi  < Vo                                                                                                                                                      | 64 |

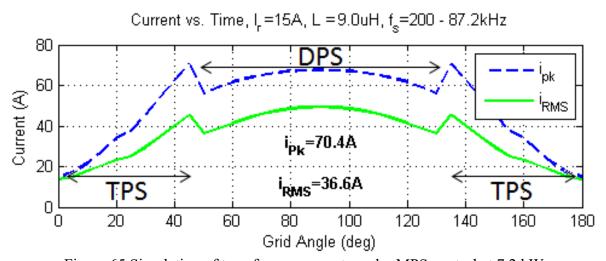

| Figure 65 Simulation of transformer currents under MPS control at 7.2 kW                                                                                                                                                            | . 65 |

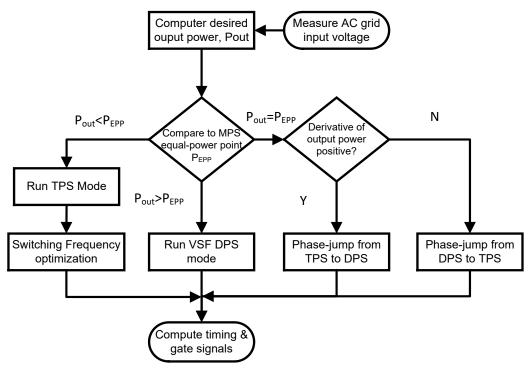

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 66 Flowchart of modulation strategies in a grid side period                                                                                                                                                                  | . 66 |

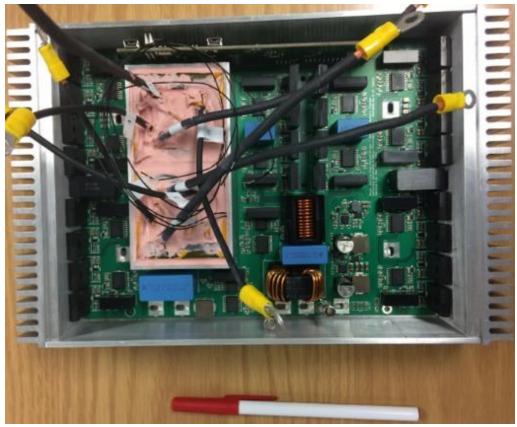

| Figure 67 SiC-based DAB + transformer prototype test bench.                                                                                                                                                                         | . 68 |

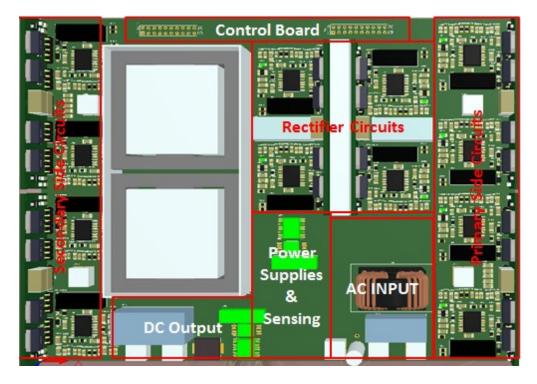

| Figure 68 internal layout of the charger                                                                                                                                                                                            | . 68 |

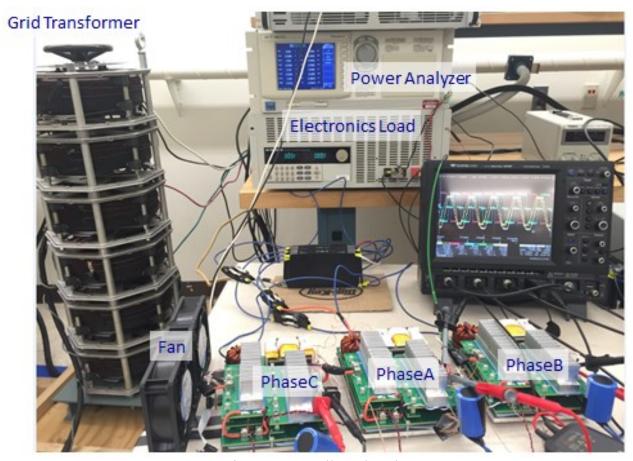

| Figure 69 overall test bench                                                                                                                                                                                                        | . 69 |

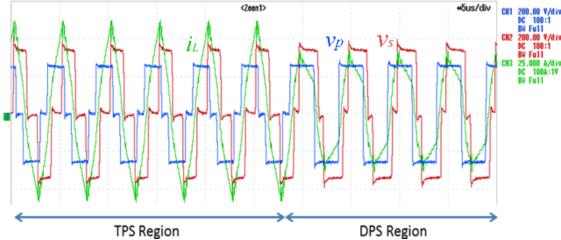

| Figure 70 Experimental DAB waveforms at 100W (yellow-transformer primary voltage, 100V/div; purple-transformer current, 1A/div; green-transformer secondary voltage, 100V/div red-grid voltage 100V/div, brown-grid current 1A/div) |      |

| Figure 71 Experimental DAB waveforms at 5.1 kW (blue-transformer primary voltage; green-transformer current; red-transformer secondary voltage; brown-output voltage, gray-grid side voltage, purple-grid side current)             |      |

| Figure 72 Phase-shift jumping region of Fig.65 (blue- primary voltage, red- secondary voltage green- transformer current).                                                                                                          |      |

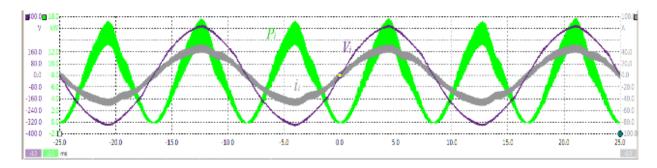

| Figure 73 input voltage and current of EV charger                                                                                                                                                                                   | . 72 |

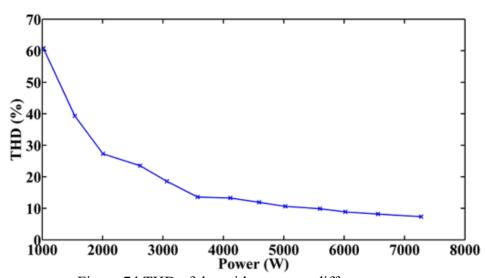

| Figure 74 THD of the grid current at different power                                                                                                                                                                                | . 72 |

| Figure 75 Experimental efficiency of DAB under MPS from 0.5-7.2 kW                                                                                                                                                                  | . 73 |

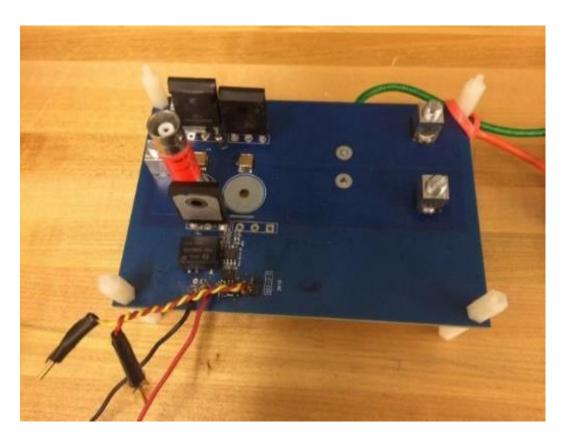

| Figure 76 SiC DPT board                                                                                                                                                                                                             | . 75 |

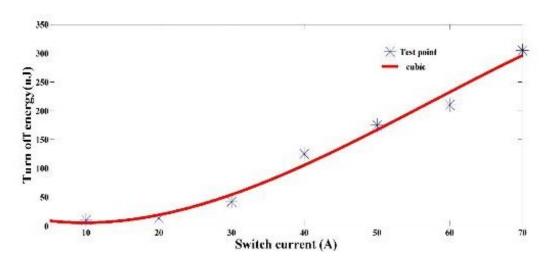

| Figure 77 switching-off loss vs the switching current                                                                                                                                                                               | . 75 |

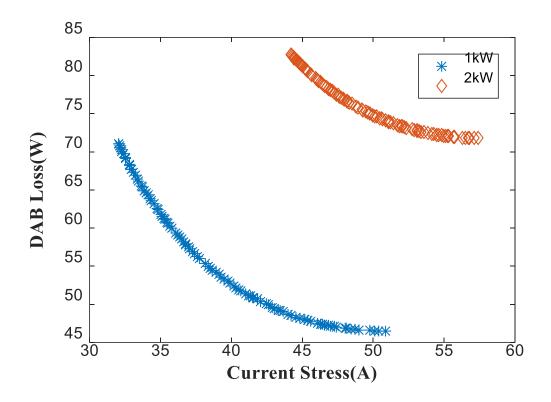

| Figure 78 Optimization process at 1kW and 2kW                                                                                                                                                                                       | . 78 |

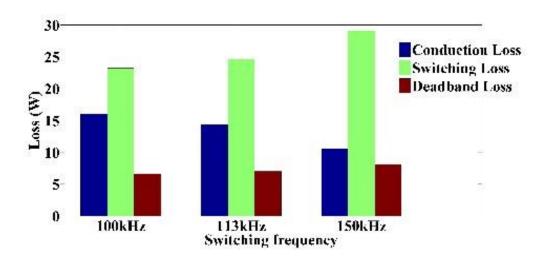

| Figure 79 1kW DAB loss breakdown at (100kHz, 113.6kHz, and 150kHz)                                                                                                                                                                  | . 79 |

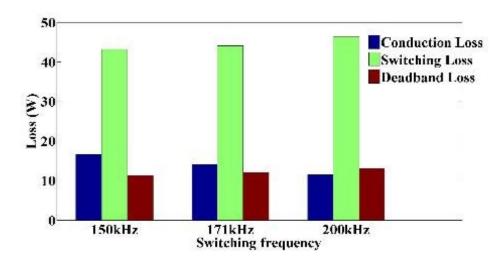

| Figure 80 2kW DAB loss breakdown at (150kHz, 171kHz, and 200kHz)                                                                                                                                                                    | . 80 |

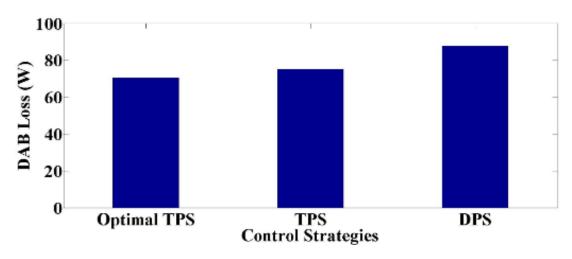

| Figure 81 2kW DAB loss breakdown at different control algorithm                                                                                                                                                                     | . 80 |

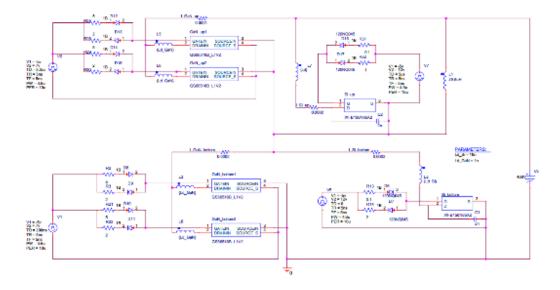

| Figure 82 Schematics of the Hybrid Switching Module                                                                                                                                                                                 | . 83 |

| Figure 83 Leadless Top-Cooled Packaging of GaN HEMTs (GS66516T) and The equivalent circuit of the GaN+Si hybrid module                                                                                                              | . 84 |

| Figure 84 Current changing in switching process                                                                                                                                                                                     | . 86 |

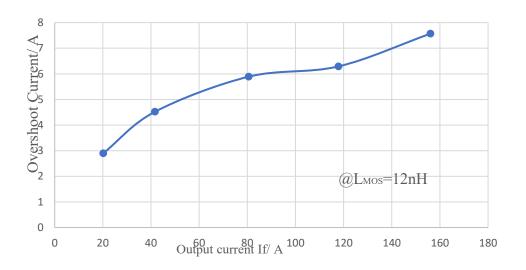

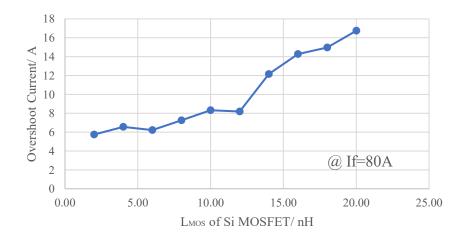

| Figure 85 pspice simulation model                                                                                                                                                                                                   | . 86 |

| Figure 86 GaN overshoot current during Si switching off                                                                                                                                                                             | . 87 |

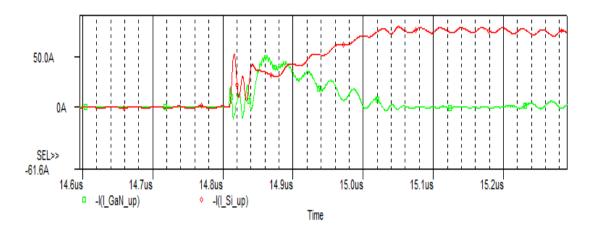

| Figure 87 GaN current during Si switching off (experiments @IL=70A)                             |

|-------------------------------------------------------------------------------------------------|

| Figure 88 Top GaN+Si Current Distribution when Bottom GaN is Switched Off – simulation result   |

| Figure 89 Top GaN+Si Current Distribution when Bottom GaN is Switched Off – experimental result |

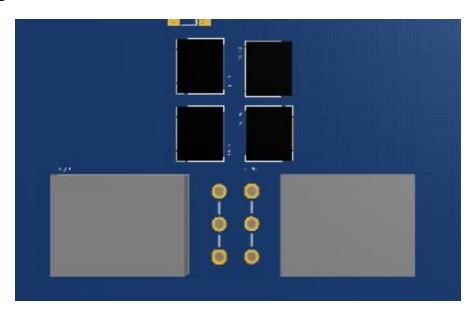

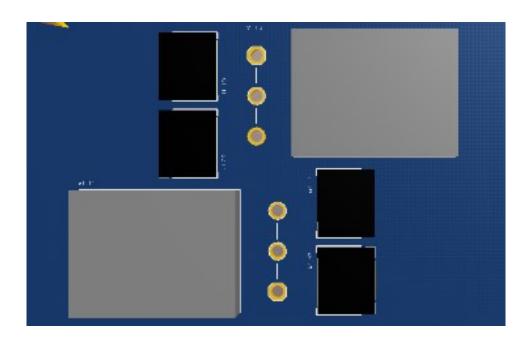

| Figure 90 Hybrid layout plan A                                                                  |

| Figure 91 Hybrid layout plan B                                                                  |

| Figure 92 Hybrid layout plan B                                                                  |

| Figure 93 PCB layout                                                                            |

| Figure 94 Zero-Voltage Switching-on Process                                                     |

| Figure 95 Current Spike Measurement During a Hard-turn-on Process in DPT                        |

| Figure 96 Charge Estimation during a Hard-switching-on Process                                  |

| Figure 97 Extraction of the hybrid-switch Coss                                                  |

| Figure 98 loss breakdown of 4 GaN vs Si+GaN                                                     |

| Figure 99 Conventional design                                                                   |

| Figure 100 Hybrid-switch solution                                                               |

| Figure 101 test waveforms                                                                       |

| Figure 102 Primary side and secondary side's test waveforms                                     |

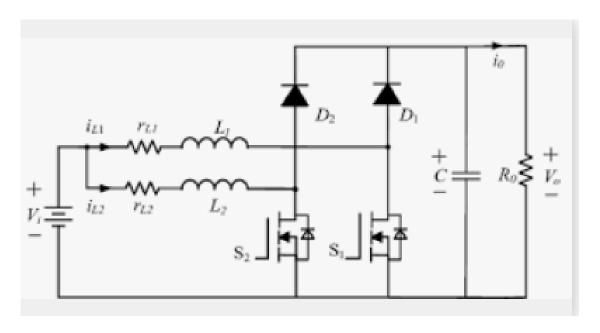

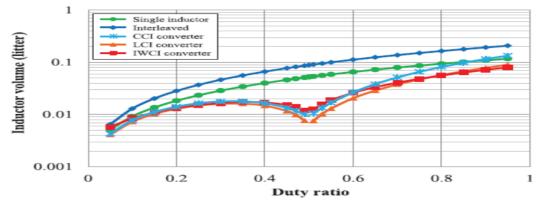

| Figure 103 Two-phase interleaved boost converter circuit topology                               |

| Figure 104 Different inductor converters' volume comparison                                     |

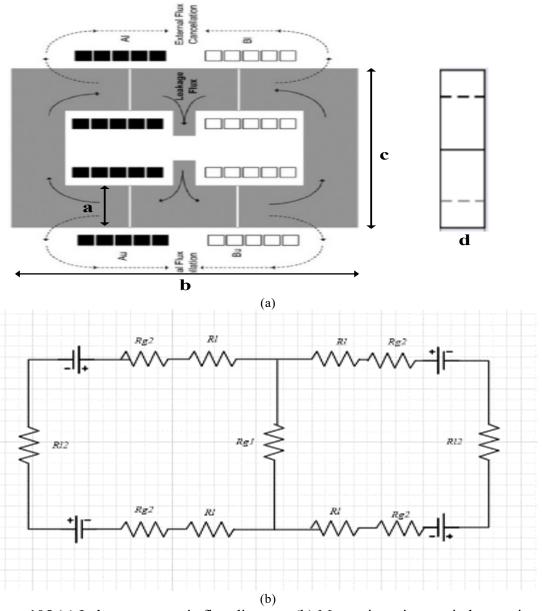

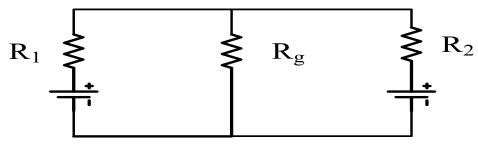

| Figure 105 (a) Inductor magnetic flux diagram; (b) Magnetic resistance inductor circuit 104     |

| Figure 106 Simplified magnetic circuit                                                          |

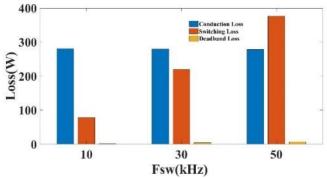

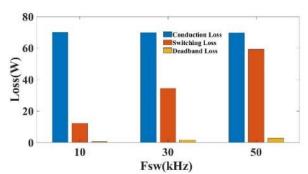

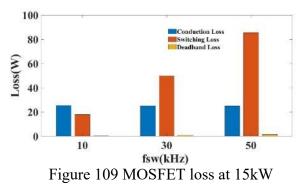

| Figure 107 MOSFET loss at 50kW                                                                  |

| Figure 108 MOSFET loss at 25kW                                                                  |

| Figure 109 MOSFET loss at 15kW                                                                  |

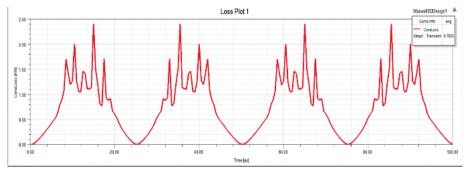

| Figure 110 Inductor loss simulation loss result at 50kW                                         |

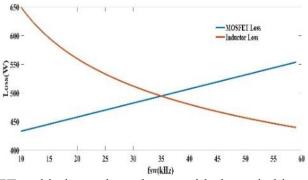

| Figure 111 MOSFET and inductor loss change with the switching frequency at 50kW                                                                                                  | 110 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

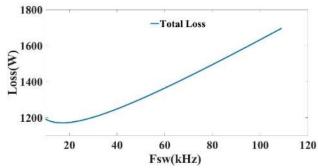

| Figure 112 Total loss change with the switching frequency at 50kW                                                                                                                | 110 |

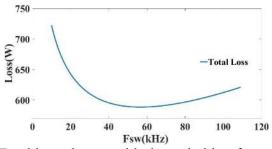

| Figure 113 Total loss change with the switching frequency at 25kW                                                                                                                | 110 |

| Figure 114 Total loss change with the switching frequency at 15kW                                                                                                                | 110 |

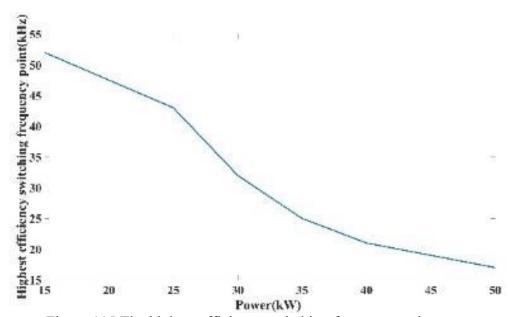

| Figure 115 The highest efficiency switching frequency point curve                                                                                                                | 111 |

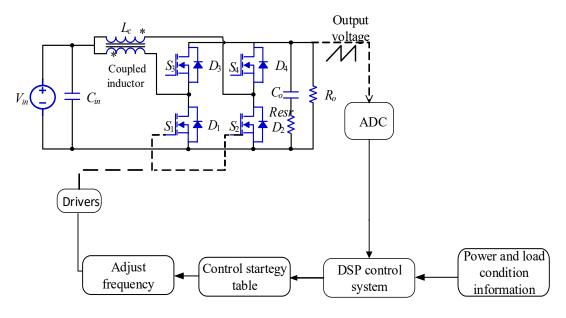

| Figure 116 The control system loop                                                                                                                                               | 112 |

| Figure 117 System power-flow path                                                                                                                                                | 114 |

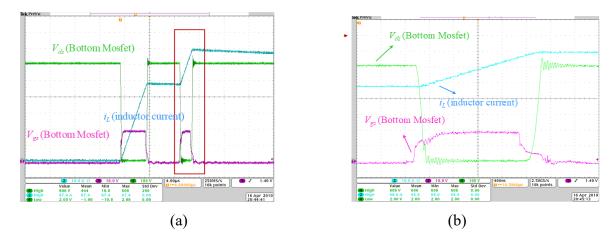

| Figure 118 Double-pulse test waveforms: (a) two pulses test waveform, (b) the second pulse zoom                                                                                  | 115 |

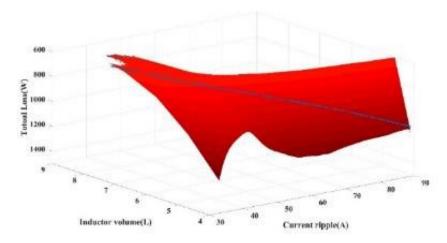

| Figure 119 Optimization result: Pareto front surface                                                                                                                             | 116 |

| Figure 120 (a) The two-phase interleaved boost converter test bench; (b) 70V input voltage test waveform                                                                         |     |

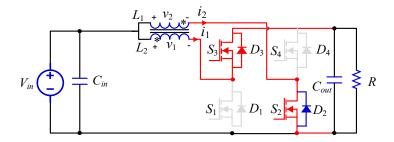

| Figure 121 The topology of the two-phase interleaved converter                                                                                                                   | 122 |

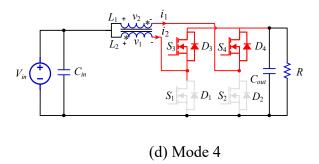

| Figure 122 interleaved boost topology work mode                                                                                                                                  | 123 |

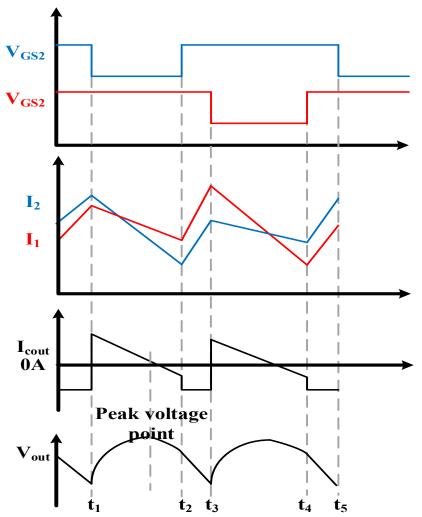

| Figure 123 Imbalanced phase current caused by imbalanced phase inductance when cycle >0.5                                                                                        |     |

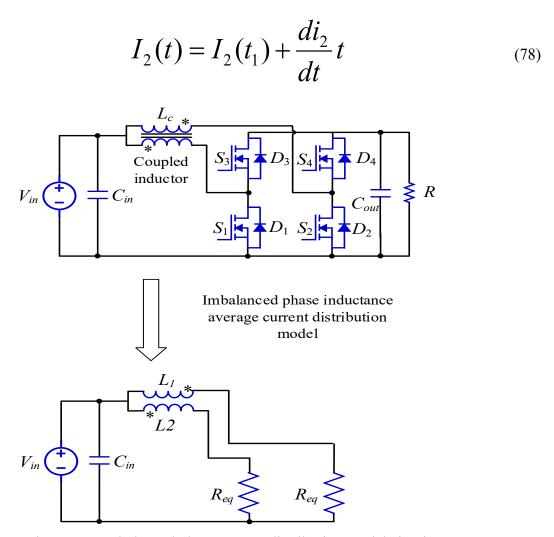

| Figure 124 Imbalanced phase current distribution model circuit                                                                                                                   | 126 |

| Figure 125 Imbalanced phase current caused by imbalanced phase                                                                                                                   | 131 |

| Figure 126 Imbalanced phase current caused by imbalanced phase duty                                                                                                              | 133 |

| Figure 127 Imbalanced phase current caused by imbalanced phase when duty cycle <0.5                                                                                              | 133 |

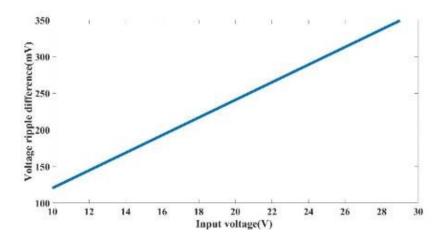

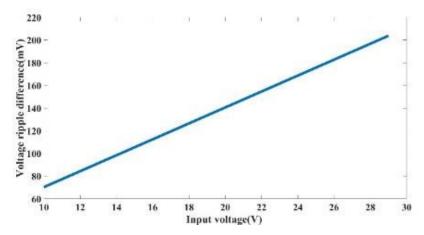

| Figure 128 Voltage ripple difference caused by imbalanced phase                                                                                                                  | 134 |

| Figure 129 Voltage ripple difference caused by imbalanced phase duty                                                                                                             | 134 |

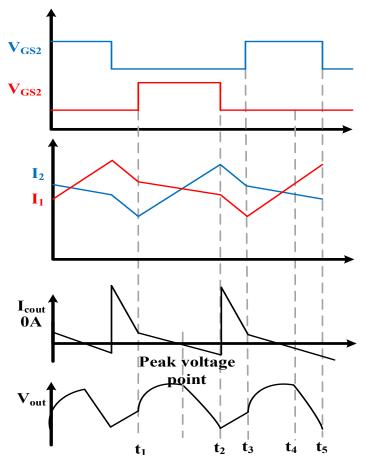

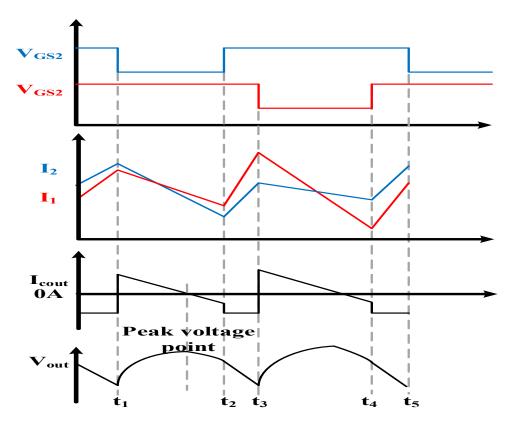

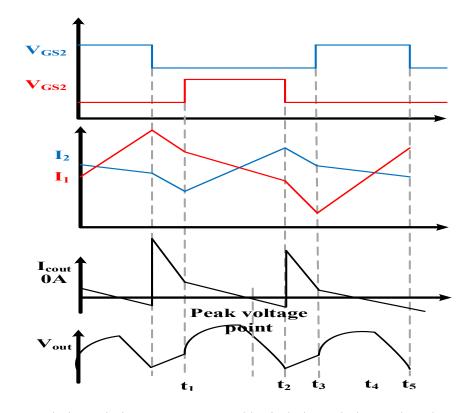

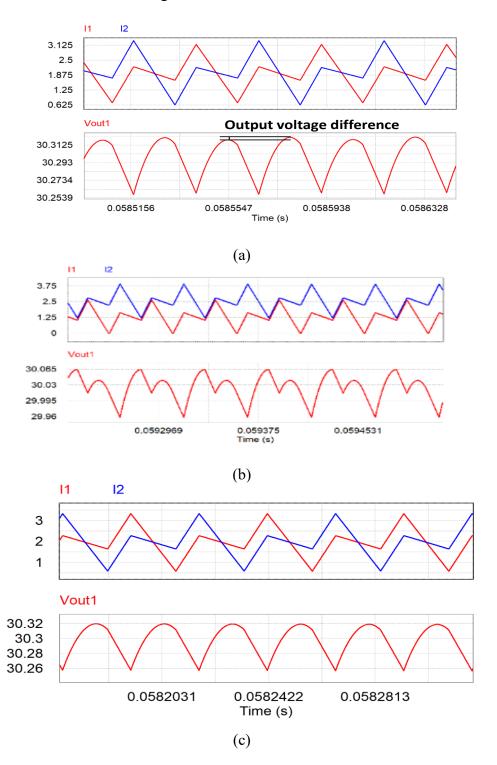

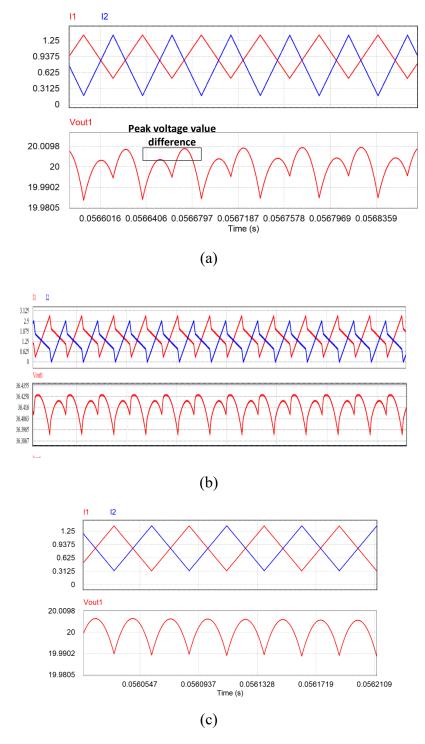

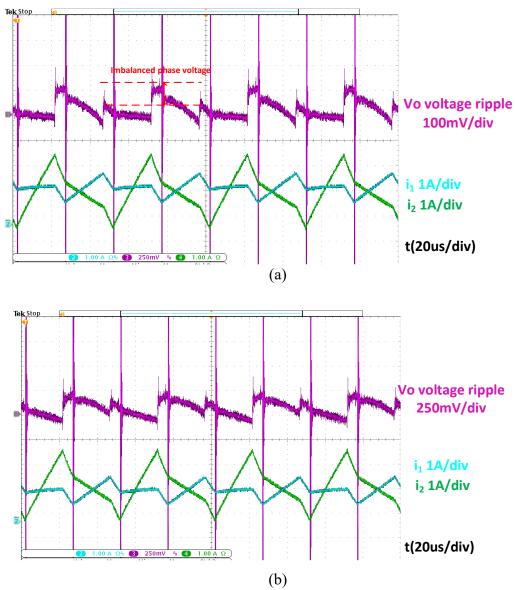

| Figure 130 Phase current and output voltage waveforms when D>0.5 under the conditions of: imbalanced phase inductor, (b) imbalanced duty cycle, (c) balanced phase current       |     |

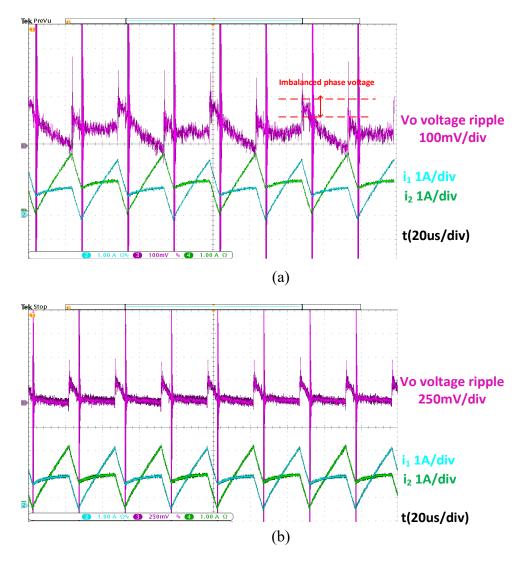

| Figure 131 Phase current and output voltage waveforms when $D \le 0.5$ under the conditions of: imbalanced phase inductor, (b) imbalanced duty cycle, (c) balanced phase current |     |

| Figure 132 Overall sensorless current balanced closed-loop control diagram                                                                                                       | 138 |

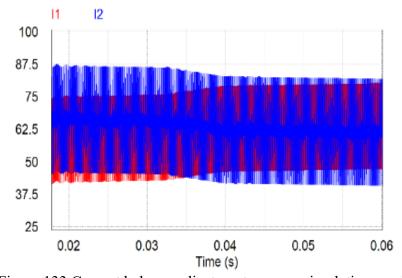

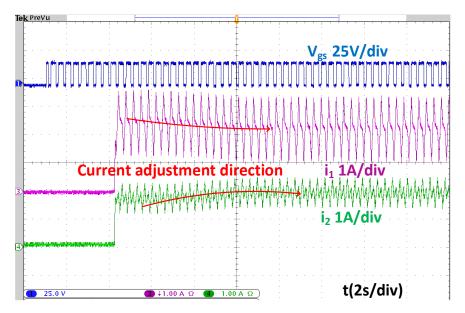

| Figure 133 Current balance adjustment process simulation result                                                                                                     | 138 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

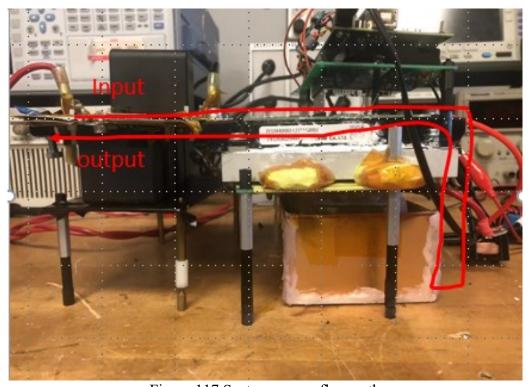

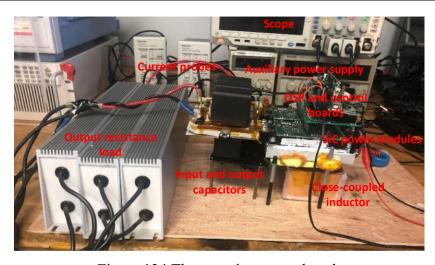

| Figure 134 The experiment test bench                                                                                                                                | 139 |

| Figure 135 Output voltage waveforms under the condition of an imbalanced phase inductance                                                                           |     |

| Figure 136 Output voltage waveforms under the condition of an imbalanced duty cycle                                                                                 | 140 |

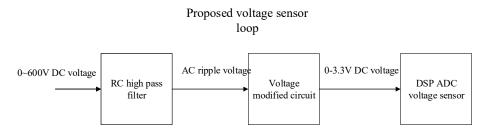

| Figure 137 Proposed voltage sensor loop                                                                                                                             | 141 |

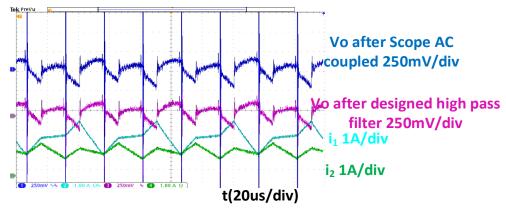

| Figure 138 Proposed voltage sensor output waveforms                                                                                                                 | 141 |

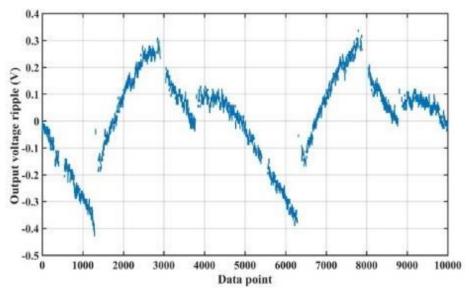

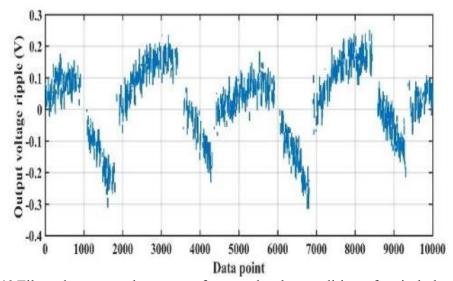

| Figure 139 Filtered output voltage waveform under the condition of an imbalanced duty cycle                                                                         |     |

| Figure 140 Filtered output voltage waveform under the condition of an imbalanced phase inductance when duty cycle is 66%                                            |     |

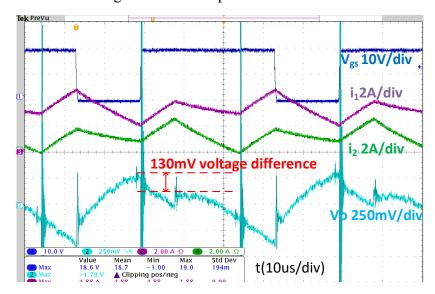

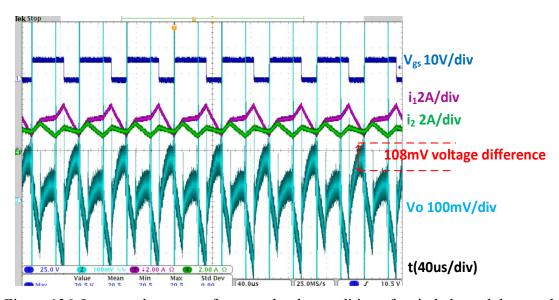

| Figure 141 Dynamic adjustment process of the two-phase currents i1 and i2                                                                                           | 143 |

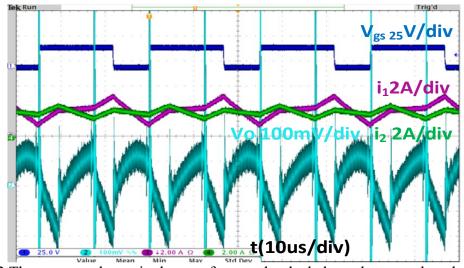

| Figure 142 The output voltage ripple waveform under the balanced status when duty cycle >5                                                                          |     |

| Figure 143 Imbalanced phase inductance output voltage waveforms when the duty cycle is smaller than 50%: (a) imbalanced current status, (b) balanced current status |     |

| Figure 144 Imbalanced phase duty cycle output voltage waveforms when the duty cycle is smaller than 50%: (a) imbalanced current status, (b) balanced current status | 145 |

| Figure 145 Imbalanced phase duty cycle output voltage waveforms when the duty cycle is lar than 50%: (a) imbalanced current status, (b) balanced current status     | _   |

| Figure 146 Output voltage waveforms under a 170hm working condition: (a) imbalanced curr status, (b) balanced current status                                        |     |

| Figure 147 Output voltage waveforms under a 30 kHz switching frequency working condition (a) imbalanced current status, (b) balanced current status                 |     |

| Figure 148 Output voltage waveforms under a 15 V input voltage working condition: (a) imbalanced current status, (b) balanced current status                        | 149 |

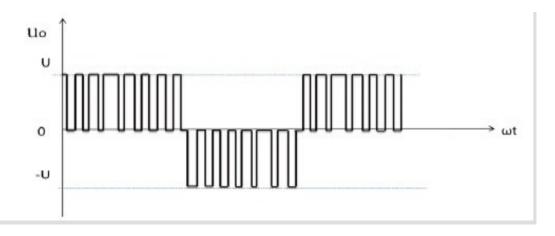

| Figure 149 two level inverter output voltage level                                                                                                                  | 152 |

| Figure 150 T-type inverter five output voltage levels                                                                                                               | 152 |

| Figure 151 T-type inverter topology with GaN                                                                                                                        | 153 |

| Figure 152 IGBT and GaN power MOSFET                                                                                                                                | 153 |

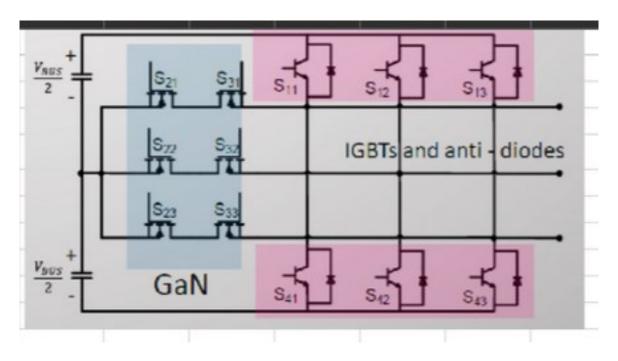

| Figure 153 T-type inverter switching process                                             | 155 |

|------------------------------------------------------------------------------------------|-----|

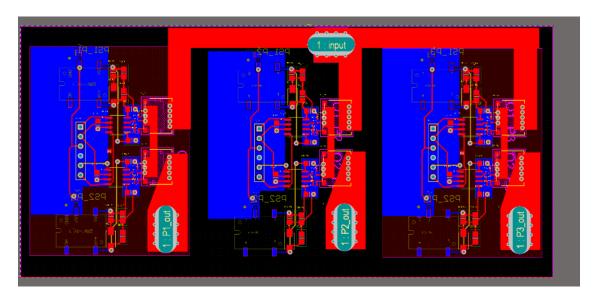

| Figure 154 GaN Three phase layout PCB                                                    | 156 |

| Figure 155 EV traction inverter work mode distribution                                   | 157 |

| Figure 156 Hybrid control mode                                                           | 157 |

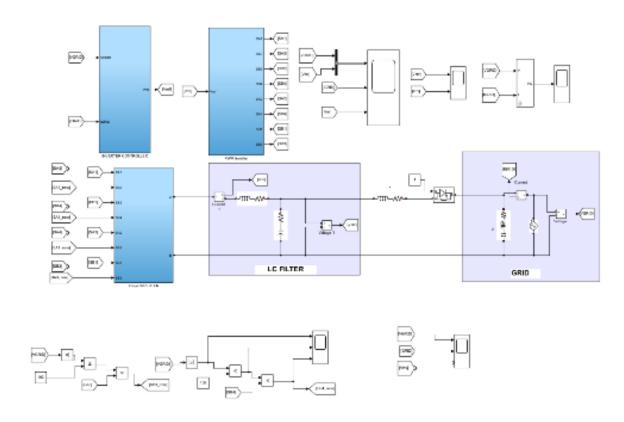

| Figure 157 MATLAB Simulink model                                                         | 158 |

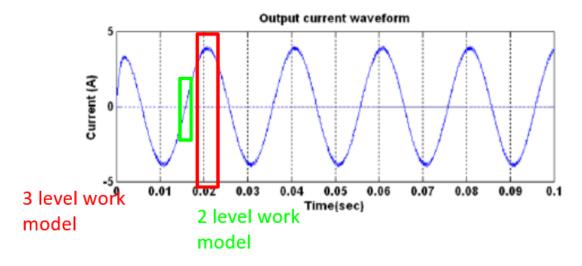

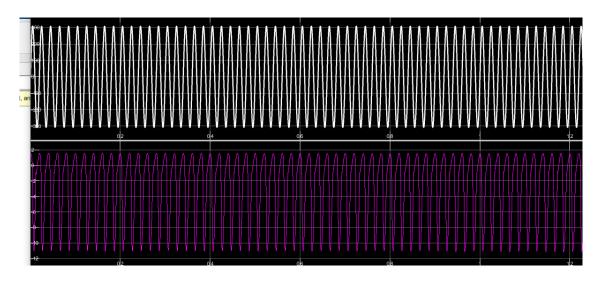

| Figure 158 Simulink simulation waveforms                                                 | 159 |

| Figure 159 Capacitor degradation principle                                               | 161 |

| Figure 160 Test bench overview                                                           | 163 |

| Figure 161 Capacitor temperature test points                                             | 164 |

| Figure 162 two-stage capacitance degradation model                                       | 165 |

| Figure 163 Capacitance changing with temperature                                         | 166 |

| Figure 164 long term test capacitor value degradation curve.                             | 167 |

| Figure 165 Capacitor degradation curves                                                  | 168 |

| Figure 166 degradation curve with temperature changing                                   | 169 |

| Figure 167 Capacitor equivalent paralleled resistance Rp value changing with temperature | 170 |

#### **Abstract**

Wide bandgap (WBG) semiconductor materials allow higher power and voltage, faster and more reliable power electronic devices. These characteristics lead to a massive improvement in power converters, especially for electric vehicles (EV) applications. As a result, new opportunities for high efficiency and power density is coming with the development of WBG power semiconductor. This paper introduces the application of WBG devices in power converters of EV. The EV development trend and the related circuit diagram of an EV system have been introduced. Serval typical power converters' topologies have been discussed.

Meanwhile, WBG devices also bring challenges to a high voltage and frequency design. High current and voltage levels need a more powerful heating system. A higher switching speed requires lower loop parasitic inductance. This paper discusses how to apply WBG devices in the power converter design and address these challenges. Finally, The reliability test method of power converters has been discussed. The lifetime of all components in a power converter has been tested under different voltage and temperature levels. The failure reasons and influences parameters are analyzed.

#### Introduction

Due to an increasing environmental awareness and oil shortage, the EV industry had a huge growth in the past ten years due to a lower CO<sub>2</sub> emission[1-6]. As the International energy agency(IEA) predicted, EVs will contribute to reducing CO<sub>2</sub> emissions by around 30% by 2050. To achieve the proposed target, Industry and academia were keeping trying to improve the performance and efficiency of EVs. An EVs system is mainly composed of three power converters. There are on-board chargers, boost converters, and traction inverters[7-16]. The main power loss of an EV comes from semiconductors in power converters. WBG material semiconductors, especially gallium nitride(GaN) and silicon carbide(SiC), are thought as the most promising alternative to traditional Silicon(SI) devices[17-25].comapred to WBG devices, have higher power and current rate, power density, heating performance and reliability [26-34]. However, WBG devices also bring more critical design challenges. Due to a higher switching speed, lower loop parasitic parameters in both gate drive and power loop are needed in the PCB design. A higher power rate requires a more powerful cooling system. A higher working frequency also could cause more critical EMI problems. Meanwhile, how to evaluate the lifetime and reliability of a power converter is also another essential research topic[35-42]. In this paper, my research contributes to these challenges will be presented

# **Chapter 1 Introduction to EV and Power Converters**

## 1.1 EV Development

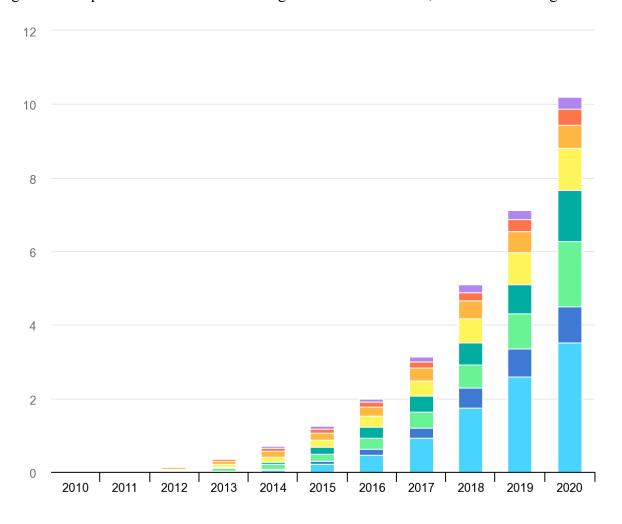

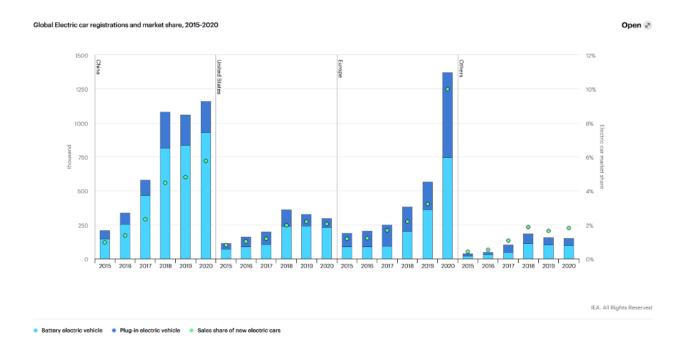

The EV had a decade of rapid growth in the past ten years. In 2020 the global EV stock had hit 10 million marks. Battery electric vehicles accounted for 66% of EV sales, as shown in figure.1. European and China shows faster growth than other areas, as shown in the figure.2

Figure 1 Global EV car sales

Figure 2 Global EV sales distribution

Figure 3 OEM EV development plan

Nowadays, OEMs plan to explore their electric vehicles product line in the next ten years, as shown in figure.3. Most OEMs set that EVs will account for around 50% of their total sale in

2030. Furthermore, some OEMs plan to change their product lines to produce EV only; Volvo will only sell electric cars from 2030; Ford will make only electric car sales in Europe from 2030; General Motors plans to offer only electric LDVs by 2035; Volkswagen aims for 70% electric car sales in Europe, and 50% in China and the United States by 2030; and Stellantis aims for 70% electric cars sales in Europe and 35% in the United States

#### 1.2 Power Converters in EV

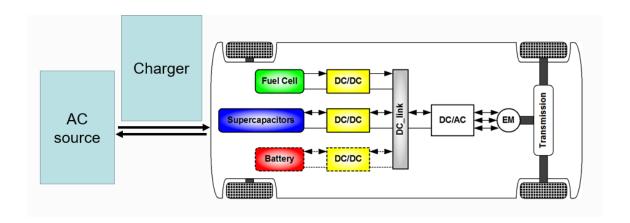

Figure 4 EV circuit diagram

A circuit diagram of EV is shown in figure 4. An electric vehicle could use different power sources: fuel cell, supercapacitor, battery, etc. The battery is usually a Lithium-ion rechargeable battery, which has a higher energy density than a traditional nickel-cadmium or lead-acid material battery. An on-board charger is set between the AC power source and battery. Fuel cell and battery Fuel cells generate energy by fuel chemical conversion. H2 is the current most used chemical fuel for the fuel cell. A Supercapacitor also called an ultracapacitor, is an extremely high capacitance value capacitor. Capacitors can store energy in a static state rather than in the form of chemicals. Which makes the charging and discharging speed much higher than the traditional battery source. A DC-DC boost/buck converter will be applied between the

power sources and DC-link to adjust the DC-link voltage to 200V~800V. A traction inverter will be used to transform DC voltage into multiple phase AC voltage as the drive power for the electric motor.

#### 1.3 On-Board Charger Topologies

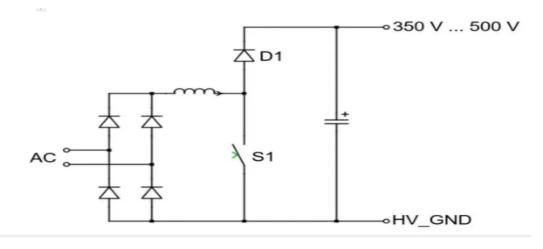

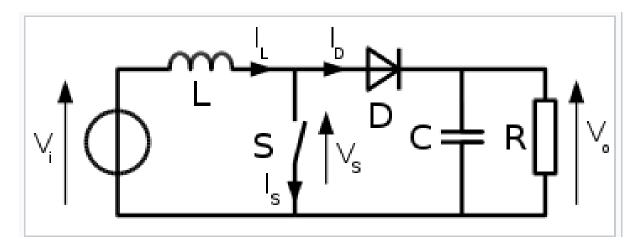

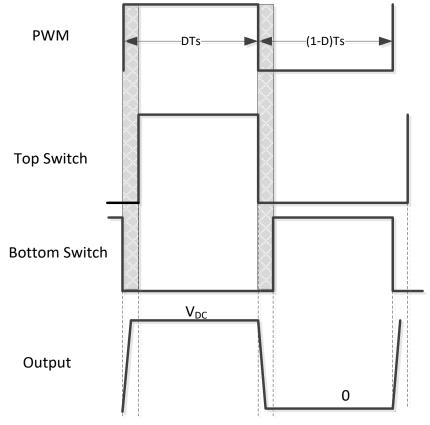

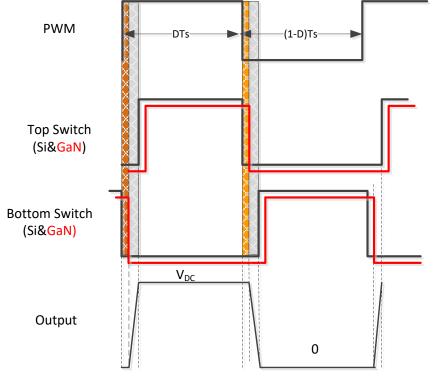

An on-board charger is a battery charger for the EV's batteries. The primary function is to realize the power factor correction function and transform the AC voltage into a steady DC voltage. The most common topologies are shown in Figure-Figure The classic boost PFC topology is the simplest on-board charger topology. This topology is a unidirectional hard switching topology. By controlling the duty cycle of the bottom power switch, the circuit can control the output voltage at a set voltage. However, hard switching makes it hard to reach a high efficiency, which increases the cooling system's requirement. Meanwhile, a high-power current increases the power loop inductor value and volume.

Figure 5 Classic boost PFC circuit

LLC topology is a single directional soft-switching topology, as shown in figure.6. A capacitor and inductor reason tank is put at the primary side to realize ZVS soft switching. ZVS Soft switching can reduce hearing loss and cooling system volume to realize higher efficiency

and power density. One drawback of the LLC topology is that the power is controlled by a variable frequency rather than the PWM duty cycle. A comprehensive working frequency range could challenge the EMI filers design.

Figure 6 Full bridge LLC topology

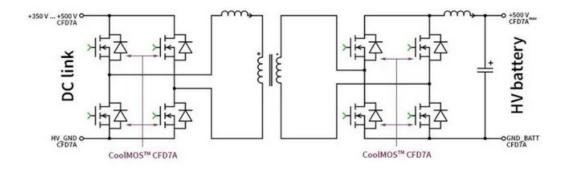

DAB topology is a bi-directional ZVS soft-switching topology for the on-board charger. The leakage inductor on the primary or secondary side can realize ZVS soft switching on both the primary and secondary sides. Compared to LLC topology, the power level is controlled by the phase shift angle between the primary side and secondary side rather than a variable frequency. So, the software control could be easier in the DAB topology. Meanwhile, ZVS soft switching on both sides can also reduce heating loss and cooling system volume to realize higher efficiency and power density.

Figure 7 DAB topology

#### 1.4 DC-DC Converter Topology

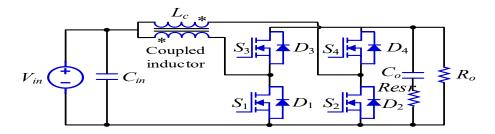

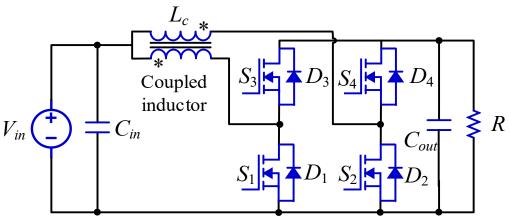

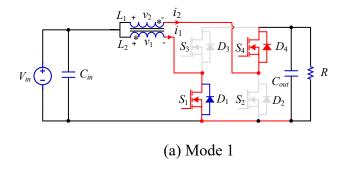

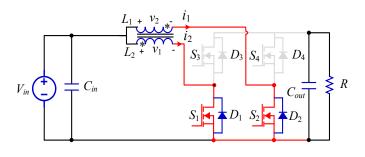

A boost converter is usually between the power source output and the traction inverter input sides. A traditional boost converter topology is shown in fig 8. In EV application, due to the high power application, traditional boost converter topology goanna has a large DC current in the power loop, which results in a high requirement on power switches. So an interleaved boost converter could improve the above issue. The interleaved boost converter topology is shown in figure.9. Compared to the traditional interleaved boost converter, it has more phase leg to undertake high current. Meanwhile, a coupled inductor can also avoid magnetic saturation.

Figure 8 Typical boos converter topology

Figure 9 Interleaved boost converter topology

#### 1.5 Traction Inverter Topology

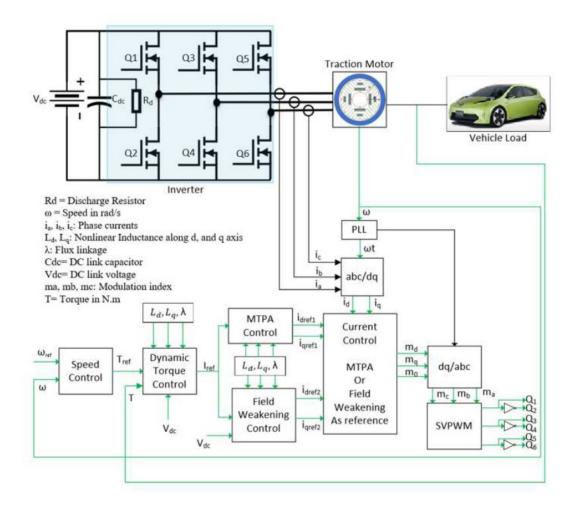

Figure 10 Traction inverter topology

A traction inverter is a high-power level inverter to provide drive power for the traction motor in an EV. The most common three-phase inverter topology is shown in fig.10. Three power MOSFETs consist of the main power loop of an inverter. The output is a three-phase AC voltage with a 120-degree phase shift. Usually, an SPWM or SVPWM control method will be used to control the output AC voltage and frequency. The closed-loop control system is made of a speed loop and a current loop. However, a typical traction inverter will work under hard switching mode. It brings higher power loss and cooling requirements. In order to improve the above issues, a T-type inverter topology is proposed to realize soft-switching, as shown in

figure.11. Meanwhile, a T-type inverter could also reduce the output three-phase AC voltage THD.

Figure 11 T-type inverter topology

## **Chapter 2 Benefits of WBG in EV Power Converters**

#### 2.1 Wide Band Gap Devices Material Characteristic

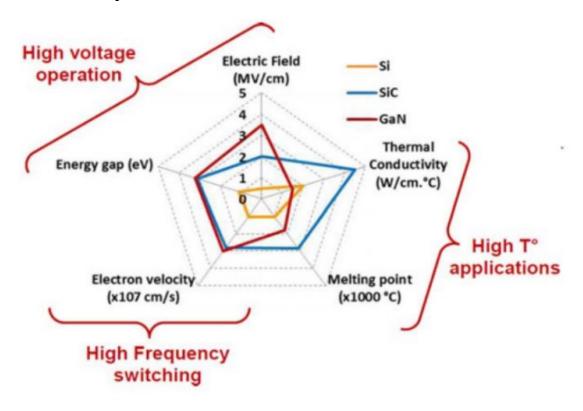

Figure 12 WBG material characterize

Wide-bandgap semiconductors are semiconductors that have a larger bandgap than traditional Si semiconductors, as shown in figure.11. Usually, Si devices' bandgap falls in the range of 1~1.5 electronvolt. However, the WBG devices could have above 2 eV bandgap (2.86ev for SiC,3.4 for GaN). Bandgap means the minimum energy gap between the conduction band and dielectric band. As for semiconductors, a small amount of energy could push more electrons into the conduction band, making devices work in a conduction state. Meanwhile, due to the material charsets, WBG materials also have a high electronic moving speed which makes WBG

devices could have a higher switching speed than traditional Si devices. Two Main Band Gap Devices: Sic and Gan.

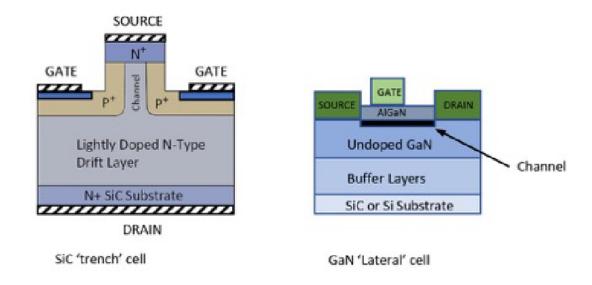

Figure 13 SiC and GaN structure

SiC and GaN both have a similar structure to Si Devices as shown in figure.12. Due to Pure GaN being hard to yield, there is always a SiC/Si substrate in GaN. Substrate mismatch makes GaN breakdown voltage drop around 1000VSo GaN is applied in a low voltage and high switching frequency application (power supply, adaptor). SiC is applied in high voltage and power applications.

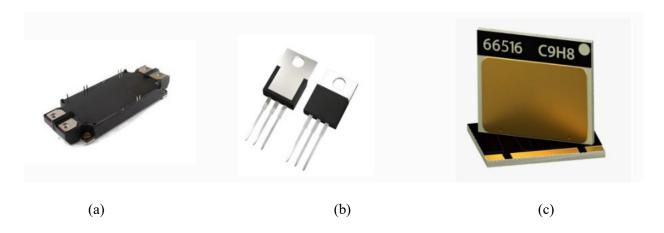

#### 2.2 WBG Device Packages

Most of the wideband gap MOSFET packages are shown in figure.13. There are three main package types. The power module package is used for the highest power and current application(up to 500 hundred amperes or even higher), as shown in (a). The TO-247 package, as shown in figure 14(b) is used for the lower current application. Usually, the highest current rate for one To-247 package is around 100A. Surface-mount package, as shown in Figure 14.(C),

has the lower parasitic parameters. It is usually applied in a high switching frequency (over 500k) application with a lower current rate(smaller than 100A).

Figure 14 SiC and GaN device packages (a) Power module (b) through-hole package(c) Surface mount package.

## Chapter 3 On-Board Charger Design Case with GaN

#### 3.1 GaN Gate and Power Loop Design

#### 3.1.1 Introduction

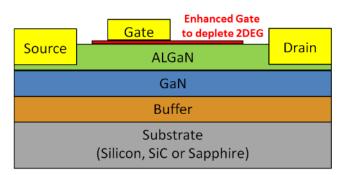

Wide-bandgap (WBG) devices attract more and more attention in recent days as the promising alternative of Si devices. It is witnessed that in the past several years high-current GaN devices have been emerging quickly and applied in various power electronics applications, e.g., travel adapters, wireless chargers, smart home appliances, high efficiency AC-DC datacenter power supplies, industrial motor drives and on-board EV battery chargers. Different from Si/SiC MOSFETs, GaN HEMTs are essentially hetero-junction devices, relying on the two-dimensional electron gas (2DEG) formed between GaN and AlGaN to conduct the current, shown as Fig.15. When imposing zero or negative voltage on the gate, the 2DEG will diminish thereby turning off the switch. Since electrons are travelling laterally between the drain and the source, the GaN HEMT is a typical lateral switch.

Figure 15 Structure of E-mode GaN HEMTs.

Presently available GaN HEMTs are shown as Table. I. Among which, Transphorm and ON Semiconductor use the cascode design, i.e., employing a Si MOSFET to control of gate of the GaN JFET thereby forming a normally off device. EPC, Panasonic and GaN Systems use theenhancement-mode (E-mode) devices without any extra silicon gate. GaN Systems provides so-far the highest current rating of all GaN HEMTs, which is the study object of this paper.

Table 1 Possible candidates of GaN HEMTs

| PartNumber    | Manufacturer     | V <sub>DS</sub><br>/V | Ids<br>/A | Rdson/<br>mΩ | Package                     |

|---------------|------------------|-----------------------|-----------|--------------|-----------------------------|

| GS66516T      | GaN Systems      | 650                   | 60        | 27           | GaN <i>PX</i><br>9x7.6x0.45 |

| TPH3205WS     | Transphorm       | 600                   | 36        | 52           | TO247                       |

| EPC2034       | EPC              | 200                   | 31        | 7            | Passivated Die              |

| PGA26E08BA    | Panasonic        | 600                   | 15        | 56           | DFN 8x8 (BV-<br>Typ)        |

| NTP8G206N     | ON Semiconductor | 600                   | 17        | 150          | TO 220 Style 10             |

| QFN8-HB2-1D   | Sanken Electric  | 600                   | 20        | 50           | QFN 8x8x0.85<br>(mm)        |

| AVJ199R06060A | Avogy            | 650                   |           | 200          | TO 220                      |

| MGG1T0617D    | MicroGaN GmbH    | 600                   | 30        | 170          | Die                         |

The impact of parasitics on a single device has been thoroughly discussed [43-46], however, there is very little work focusing on the dynamic performance of paralleled GaN HEMTs [47-48], no mention paralleling more than 2 GaN HEMTs, which is thought to be extremely difficult [49]. Previous work is mainly focused on the inductance reduction [50-52] and loss modeling [53]. In addition, it is still recommended to adopt zero-voltage-switching (ZVS) technology to eliminate its switching-on loss to further enhance the efficiency. Such attempt has been implemented in [54], where a 7.2 kW on-board charger has been developed with >97% efficiency and ~4kW/L power density. Four GaN(GS66516T) have been paralleled to undertake 400V/92A hard switching-off reliably. Based on previous literatures, this paper aims to 1) further extend GaN application from the soft-switching to the hard-switching applications, given in some applications such as DC/AC inverters the hard switching is inevitable, and 2)

realize more switch paralleling (>2) given that 60A is not enough for some high-power applications. An analytical model to facilitate the understanding of switching process especially for paralleled GaN HEMTs is built in following section.

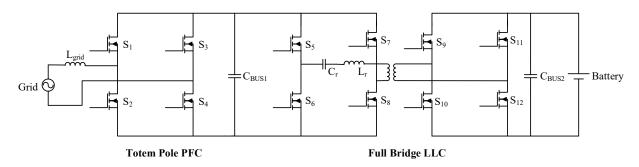

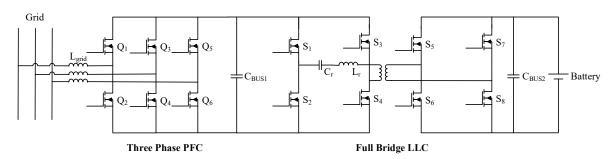

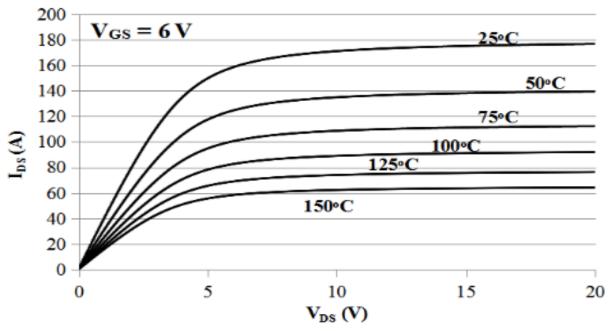

There is a growing interest in high-power-density and high-efficiency battery chargers for electric vehicles (EVs)[55-56], most of which adopt three stages [57-59], i.e., an AC/DC stage to convert the grid voltage to a DC voltage and realize the power factor correction (PFC), a DC/AC stage to transform the DC to a high-frequency AC (hundreds of kHz) on the primary side of the transformer, and an AC/DC stage to rectify the induced high-frequency AC to a DC voltage to charge the battery. Shown in Fig. 1a is a typical single-phase charger using resonance technology. The grid-side AC/DC employs the totem-pole boost-type PFC. Lr and Cr form a resonance circuit to realize the zero voltage switching (ZVS)[60]. Shown in Fig.1b is a typical three-phase charger using the full-bridge LLC resonance [61]. When using MOSFETs, all switches have body diodes.

Figure 16 A conventional single-phase isolated charger

Figure 17 A conventional three-phase isolated charger

All chargers above need bulky DC-bus capacitors and have a relatively high power loss. Assume each stage (AC/DC, high-frequency DC/AC, transformer and AC/DC) has 1~2% power loss. This yields ~94% efficiency and ~2kW/L power density, such as Brusa 22kW charger (NLG664) based on Si devices. Various bidirectional isolated AC/DC converters were investigated in previous literatures [62-64]. In [62], a single-phase bidirectional isolated ZVS AC-DC converter was proposed, as shown in Fig.16. Such topology decreases the stage numbers and eliminates the massive DC-bus capacitor. By using back-to-back switches, the transformer primary voltage follows the envelope of the grid input. It needs vary the phase-shift and switching frequency to secure the power delivery and the power factor simultaneously. Instead of using the back-to-back switches, a circuit in [65-66] is a better candidate. As shown in Fig. 17, the front-end rectifier stage (R1~R4, here R stands for "rectifier") is operated at the line frequency, simply converting the sinusoidal waveform to a double-line-frequency DC voltage. Therefore for the grid-side H-bridge, using conventional Si MOSFET is enough. It meanwhile saves back-to-back switches, eliminates the switching loss, and shrinks the DC-bus capacitance to  $\sim \mu F$  level, given there is no need to keep the DC-bus voltage constant. The DAB stage needs realize both PFC and battery charging. To build a three-phase charger, e.g., 380VAC/20kW for European and Asian markets, three such single-phase modules could be connected as Fig. 18. The overall charger follows the exact power density and efficiency of each single-phase charging module and offers high tolerance, i.e., providing the power even when two phases fail.

Figure 18 Single-phase single-stage bidirectional isolated ZVS AC-DC converter

Figure 19 Charger topology adopted in this on-board charger

For the DAB stage (P1~P4, S1~S4), wide-bandgap (WBG) devices such as GaN HEMTs and SiC MOSFETs are excellent candidates to enhance the efficiency and power density, due to their ultra-fast switching transitions and ultra-low gate-drive power [67]. Some attempts have been carried on for EV chargers using GaN for high-switching-frequency applications [68-70]., showing superior efficiency or power density. Different from the previous literature mostly using cascode GaN devices, this paper adopt Enhancement mode (E-mode) GaN HEMTs, GS66516T from GaN Systems Inc, as shown in Fig.3(a). Its no-lead, top-cooled package significantly facilitates the parasites reduction. Compared with silicon and other GaN counterparts, its much smaller size

makes it more appealing. Along with the topology shown in Fig.2b

Figure 20 (a) Switching Energy of GS66516T (b)Leadless Top-Cooled Packaging of GaN HEMTs (GS66516T)

It is also possible to use SiC devices [71-72], which represents another type of WBG devices. Whatever devices preferred, the following issues need be resolved, i.e., 1) ZVS turn-on has to be true within all output-voltage range (200~450VDC), given that both SiC and GaN have much higher switching-on loss than switching-off loss, as shown in Fig.20(b), and a systematic integration of the three single-phase charging modules, not only at the package level but also at the control level, e.g., a closed-loop control to balance each-phase power even when the grid voltage is imbalanced.

#### 3.1.2 Modelling Dynamic Behavior of Paralleled Gan Hemts with Parasitics

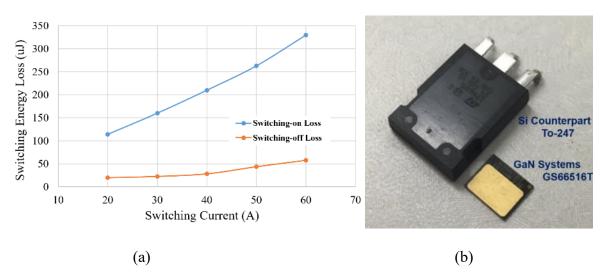

Take GS66516T(650V/60A) as an example. Its I-V curve at different temperature is shown in Fig.21, indicating an obvious positive correlation between the channel resistance and the temperature. Such characteristics guarantee the current balancing among paralleled switches in the steady state.

Figure 21 V-I Curve of GS66516T vs. Temperature

The main challenge for the parallel operation, however, lies in the switching process, during which parasitic parameters and gate driver circuits play critical roles. Different from most of Si MOSFET, E-mode GaN has relatively low turn-on gate-voltage threshold, e.g., ~2V, making it very sensitive to the high di/dt and dv/dt during the dynamic process. When VGS exceeds 10V, such device will be destroyed. Therefore the electrical stress caused by parasitics need more attention than conventional Si devices. Any attempt of swapping Si with GaN without optimizing the circuit layout will result in the system failure.

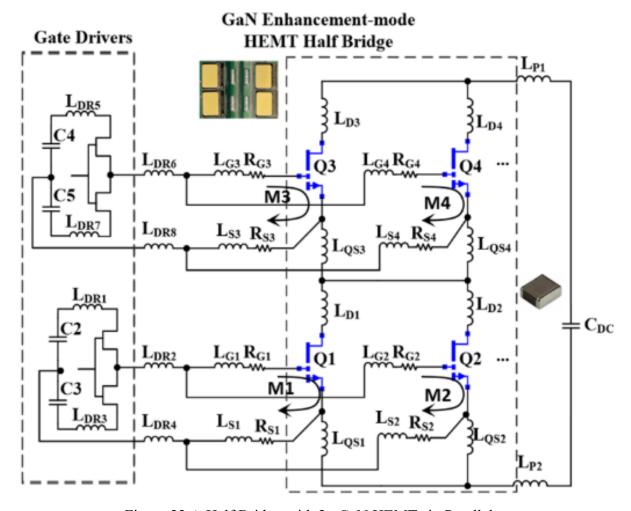

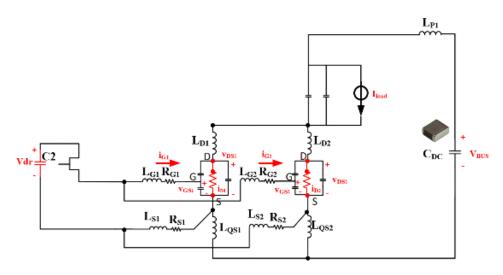

In this section, we will first study two GaN HEMTs in parallel, locate potential influential factors and model their dynamic behaviors, which provides effective guidance for paralleling more GaN HEMTs in Section III. A half bridge consisting of two high-side and two low-side GaN HEMTs in parallel is shown as Fig.22, in which all parasitics are considered, and C2~C4 is the gate driver capacitors, CDC is the decoupling capacitor, and RG1~RG4 and RS1~RS4 are the gate driver resistors.

Figure 22 A Half Bridge with 2x GaN HEMTs in Parallel

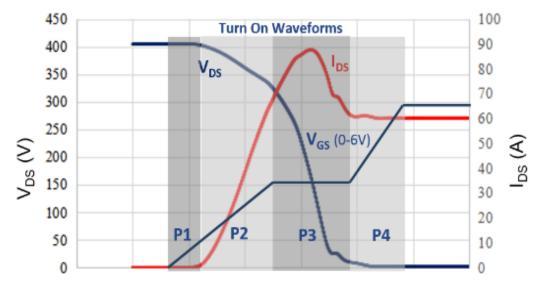

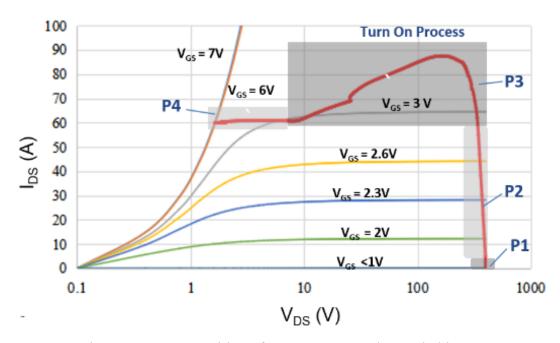

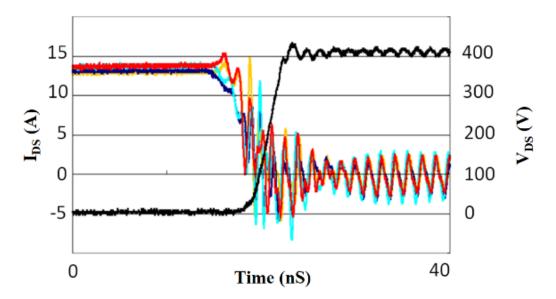

Fig.23 shows the switching-on process of paralleled GaN HEMTs. Here we divide the whole process into four intervals, i.e., P1-delay period, P2-di/dt period, P3-dv/dt period and P4-remaining switching period. Particular attention needs be paid to P2 and P3 since such periods bring the majority of current and voltage stresses to GaN HEMTs. Fig.24 shows the state trajectory of the switch during the turn-on process.

Figure 23 V<sub>DS</sub>, I<sub>DS</sub> Waveform During Switching on

Figure 24 State Transition of GaN HEMT During Switching on

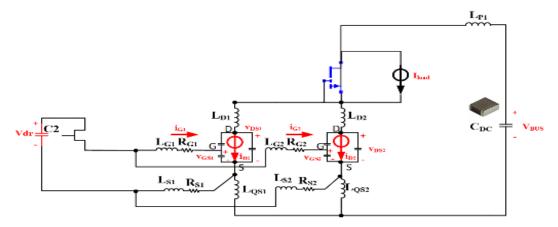

As for the P2:di/dt period, after the gate-source voltage of any of paralleled HEMTs reaches the threshold, the impedance of 2DEG begins to decrease. In this mode, the HEMT is operated in the saturation region, drain current  $(i_{D(t)})$  is controlled by gate-source voltage  $(v_{GS(t)})$  i.e.,

$$i_{D(t)} = \mathbf{g} \cdot (v_{GS(t)} - V_{th}) \tag{1}$$

Here g is trans-conductance, and  $V_{th}$  is threshold voltage. As  $v_{GS(t)}$  increases,  $\frac{di_{D(t)}}{dt}$  starts to affect the gate voltage through the common-source inductance between gate-drive loops and power loops. To mitigate such cross talking, the Kelvin terminal is usually employed to bypass the common source inductance, as shown in Fig.25. Even so, such interaction between the gate and power loop has not fully resolved yet due to the existence of the quasi-common-source inductance ( $L_{QS_1}$  and  $L_{QS_2}$  as shown in Fig.19). The imbalanced quasi-common source inductance and high di/dt together will eventually cause a feedback voltage across gate source voltage as shown in (2). Such feedback voltage is regarded as the disturbance on gates of paralleled switches, which will be minimized if the layout is optimized ( $L_{QS_1} \approx L_{QS_2}$ ) and current is evenly distributed among switches ( $t_{D_1(t)} \approx t_{D_2(t)}$ ).

$$v_{QS_{1}(t)} = (L_{QS_{1}} \cdot \frac{di_{D_{1}(t)}}{dt} - L_{QS_{2}} \cdot \frac{di_{D_{2}(t)}}{dt}) \cdot \frac{Z_{s_{1}}}{Z_{s_{1}} + Z_{s_{2}}}$$

(2)

Here,  $v_{QS_1(t)}$  is the voltage across  $L_{S_1}$  and  $R_{S_1}$ ,  $Z_{S_1}$  and  $Z_{S_2}$  are the impedance of  $L_{S_1}$ ,  $R_{S_1}$  and  $L_{S_2}$ ,  $R_{S_2}$  respectively.

Figure 25 Equivalent Circuit during di/dt Period of Switching on Process

Based on KCL and KVL,

$$C_{GD_1} \cdot \frac{dv_{GS_1(t)}}{dt} + C_{GS_1} \cdot \frac{dv_{GS_1(t)}}{dt} = \frac{1}{R_{G_1} + R_{S_1}} (V_{dr} - v_{GS_1(t)} - v_{QS_1(t)} - M_1 \cdot \frac{di_{D_1(t)}}{dt} - (L_{G_1} + L_{S_1}) \cdot \frac{di_{G_1(t)}}{dt}$$

(3)

$$v_{DS_{1}(t)} = V_{BUS} - L_{P} \cdot \left(\frac{di_{D_{1}(t)}}{dt} + \frac{di_{D_{2}(t)}}{dt}\right) - M_{1} \cdot \frac{di_{G_{1}(t)}}{dt} - (L_{D_{1}} + L_{QS_{1}}) \cdot \frac{di_{D_{1}(t)}}{dt}$$

(4)

$$i_{G_1(t)} = C_{ISS_1} \cdot \frac{dv_{GS_1(t)}}{dt} + C_{RSS_1} \cdot \frac{dv_{GD_1(t)}}{dt}$$

(5)

Here  $V_{dr}$  is the gate-drive voltage generated by the gate-drive ICs,  $M_1$  is the mutual inductance between the gate-drive loop and power commutation loop.

When P2 period ends when  $i_{D_1(t)}$  or  $i_{D_2(t)}$  reaches  $I_{load}$ . Assuming  $\frac{di_{D_1(t)}}{dt} = \frac{di_{D_2(t)}}{dt}$ ,  $v_{GS_1}$  is derived as (6).

$$v_{GS_1(t)} = V_{dr} + (V_{dr} - V_{th_1}) \cdot (\frac{s_2 \cdot e^{s_1 t} - s_1 \cdot e^{s_2 t}}{s_1 - s_2}) \tag{6}$$

Here

$$s_{1,2} = \frac{\pm \sqrt{b^2 - 4a} - b}{2a}$$

$$a = (R_{G_1} + R_{S_1}) \cdot C_{GD_1} \cdot \left( L_{D_1} + \frac{L_{P_1}}{2} + M_1 + L_{QS_1} - L_{QS_2} \right) + (C_{GS_1} + C_{GD_1}) \cdot \left( M_1 + L_{QS_1} - L_{QS_2} + L_{G_1} + L_{S_1} \right)$$

$$L_{QS_2} + L_{G_1} + L_{S_1}$$

$$b = 1 + \left(L_{QS_1} - L_{QS_2} + M_1\right)g + \left(R_{G_1} + R_{S_1}\right) \cdot \left(C_{GS_1} + C_{GD_1}\right).$$

A higher gate driver voltage  $(V_{dr})$  or smaller gate resistance  $(R_G + R_S)$  will lead to a faster switching transition, resulting in a lower loss.

Also, in this period, the quasi-common-source inductance ( $L_{QS_1}$ ,  $L_{QS_2}$ ) has a similar effect as the mutual inductance (M1), which might potentially cause overshoot or undamped ringing on  $v_{GS}$ . an unsynchronized gate-drive circuit is proposed, using one switch to fully turn on first before other switches. Its problem is that one switch undertakes majority of the turn-on current, which potentially lowers the system reliability. A symmetric power loop and gate driver loop

layout is a better solution, as proposed and discussed in Section III to achieve the reliable switching.

#### P3:dv/dt Period

During this process, the impedance of 2DEG is controlled by gate-source voltage as shown in (7).

$$R_{2DEG} = \frac{v_{DS(t)}}{g_{\cdot}(v_{GS(t)} - v_{th})}$$

(7)

This period ends when  $v_{ds(t)}$  reaches zero. The circuit behavior could be modelled as (8) & (9). Miller plateau is observed in this period during which  $v_{GS_1(t)} = v_{GS_1\_miller}$ .

Figure 26 Equivalent Circuit during dv/dt Period of Switching on Process

$$C_{GD_1} \cdot \frac{dv_{DS_1(t)}}{dt} = \frac{1}{R_{G_1} + R_{S_1}} (V_{dr} - v_{GS_1\_miller} - v_{QS_1(t)} - M_1 \cdot \frac{di_{D_1(t)}}{dt} - (L_{G_1} + L_{S_1}) \cdot C_{GD_1} \cdot \frac{d^2v_{DS_1(t)}}{dt^2})$$

(8)

$$\left(I_{load} + C_{OSS_{total}} \cdot \frac{dv_{DS_{1}(t)}}{dt}\right) \cdot R_{2DEG} + L_{LOOP} \cdot C_{OSS_{total}} \cdot \frac{d^{2}v_{DS_{1}(t)}}{dt^{2}} = V_{BUS} R_{2DEG} = \frac{v_{DS(t)}}{g \cdot (v_{GS(t)} - V_{th})}$$

(9)

Here  $L_{LOOP}=L_{P1}+(L_{D1}+L_{QS_1})/(L_{D2}+L_{QS_2})$ ,  $C_{oss_{total}}$  is the total output

capacitance of both high-side and low-side transistors and  $R_{2DEG}$  is the 2DEG resistance of low-side transistors. So,  $v_{DS_1(t)}$  and  $v_{GS_1(t)}$  of low-side HEMTs could be derived as (10) and (11).

$$v_{DS_1(t)} = V_{BUS} \cdot (1 - \frac{S_2}{S_2 - S_1} \cdot e^{S_1 \cdot t} + \frac{S_1}{S_2 - S_1} \cdot e^{S_2 \cdot t}) R_{2DEG} = \frac{v_{DS(t)}}{g \cdot (v_{GS(t)} - V_{th})}$$

(10)

$$v_{GS_{1\_miller}} = \frac{1}{R_1} \left( V_{dr} - (R_{G_1} + R_{S_1}) \cdot C_{GD_1} \cdot \frac{dv_{DS_1(t)}}{dt} - v_{QS_1(t)} - M_1 \cdot C_{GD_1} \cdot \frac{d^2v_{DS_1(t)}}{dt^2} - (L_{G_1} + L_{S_1}) \cdot C_{GD_1} \right) \cdot \frac{d^2v_{DS_1(t)}}{dt^2}$$

$$+ \frac{R^2 p_{DG_1 - d} \cdot \frac{L_{LOOP}}{dt}}{R^2 p_{DG_1 - d} \cdot \frac{L_{LOOP}}{dt}} - R_1 p_{DG_1}$$

$$(11)$$

$$\text{Here } v_{QS_1(t)} \text{ follows eqn (2), } s_{1,2} = \frac{\pm \sqrt{R_{2DEG}^2 - 4 \frac{L_{LOOP}}{C_{OSS_{total}}} - R_{2DEG}}}{2 \cdot L_{LOOP}}.$$

According to (7), the miller plateau voltage ( $v_{GS_{1\_miller}}$ ) determines  $R_{2DEG}$  so as to control the slew rate of the drain-to-source voltage. From (7) to (10), the lower the miller plateau, the higher the channel resistance, therefore the longer time for VDS to reach the steady state, representing the higher the switching-on loss. Meanwhile, according to (11), the larger the gate resistance, the lower  $v_{GS_{1\_miller}}$ , which results in a higher switching-on loss. Overall, (11) indicates that increasing the turn-on voltage or reducing the turn-on gate resistance is an effective solution to reduce the switching-on loss.

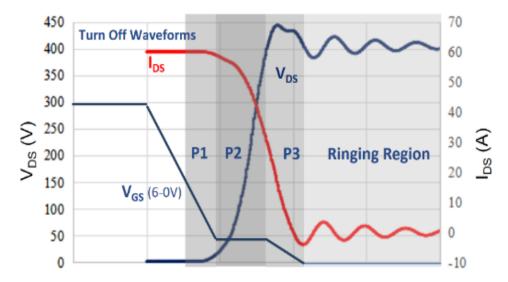

The turn-off process is shown in Fig.21. Three intervals are included, i.e., P1-delay period, P2-dv/dt period, P3-di/dt period.

Figure 27 Waveform During the Switching-off

Figure 28 State Trajectory of GaN HEMT During the Switching-off

P2:dv/dt Period is similar to dv/dt Period of switching on process, miller plateau will also be observed during this period. With the 2DEG impedance increasing, the load current ( $I_{load}$ ) begins to discharge and charge high-side and low-side output capacitance, respectively. Here  $C_{OSS_{total}}$  represents the overall output capacitance of the whole leg.  $v_{DS_1(t)}$  and  $v_{GS_1(t)}$  of the low-side HEMT are derived as

$$v_{DS_1(t)} = V_{BUS} \cdot (1 - e^{\frac{-t}{R_{2DEG} \cdot C_{OSS_{total}}}}) R_{2DEG} = \frac{v_{DS(t)}}{g \cdot (v_{GS(t)} - V_{th})}$$

(12)

$$v_{GS_{1\_miller}} = \frac{1}{R_1} (V_{dr\_off} + R_1 \cdot C_{GD_1} \cdot \frac{dv_{DS_1(t)}}{dt} + v_{QS_1(t)} + M_1 \cdot C_{GD_1} \cdot \frac{d^2v_{DS_1(t)}}{dt^2} + L_1 \cdot C_{GD_1} \cdot \frac{d^2v_{DS_1(t)}}{dt^2})$$

(13)

According to (7), (12) and (13), the gate resistance determines the miller plateau voltage  $(v_{GS_{1\_miller}})$  then further impacts the slew rate of the drain-to-source voltage. The larger the gate turn-off resistance, the lower  $v_{GS_{1\_miller}}$ . When the miller plateau voltage is lower than the threshold voltage, the 2DEG is pinched off. Adding a negative switching-off voltage, e.g., Vdr\_off=-5V, expedites such switching process thereby reducing the switching loss. This period ends when the drain-source voltage reaches the bus voltage.

#### P3:di/dt Period

In this mode, the high-side transistors begin to freewheel the current. The low-side GaN HEMTs are shutting down. The  $v_{GS_1(t)}$ ,  $i_{D_1(t)}$ , and  $v_{DS_1(t)}$  is derived as (14), (15) and (16) assuming  $\frac{di_{D_1(t)}}{dt} = \frac{di_{D_2(t)}}{dt}$ .

$$v_{GS_1(t)} = V_{dr\_off} - (V_{dr\_off} - v_{GS_1_{miller}}) \cdot (\frac{s_2 \cdot e^{s_1 t} - s_1 \cdot e^{s_2 t}}{s_1 - s_2}) R_{2DEG} = \frac{v_{DS(t)}}{g \cdot (v_{GS(t)} - V_{th})}$$

(14)

$$i_{D_1(t)} = g \cdot (V_{dr\_off} - (V_{dr\_off} - v_{GS_{1_{miller}}}) \cdot (\frac{s_2 \cdot e^{s_1 t} - s_1 \cdot e^{s_2 t}}{s_1 - s_2}) - V_{th_1})$$

(15)

$$v_{DS_{1}(t)} = V_{BUS} - L_{P_{1}} \cdot \left(\frac{di_{D_{1}(t)}}{dt} + \frac{di_{D_{2}(t)}}{dt}\right) - M_{1} \cdot \frac{di_{G_{1}(t)}}{dt} - (L_{D_{1}} + L_{QS_{1}}) \cdot \frac{di_{D_{1}(t)}}{dt}$$

(16)

Here

$$s_{1,2} = \frac{\pm \sqrt{b^2 - 4a} - b}{2a}$$

,

$$a = (R_{G_1} + R_{S_1}) \cdot C_{GD_1} \cdot \left(L_{D_1} + \frac{L_{P_1}}{2} + M_1 + L_{QS_1} - L_{QS_2}\right) + (C_{GS_1} + C_{GD_1}) \cdot (M_1 + L_{QS_1} - L_{QS_2} + L_{G_1} + L_{S_1})$$

$$,b = 1 + \left(L_{QS_1} - L_{QS_2} + M_1\right)g + \left(R_{G_1} + R_{S_1}\right) \cdot \left(C_{GS_1} + C_{GD_1}\right).$$

Very similar to the di/dt period of switching on process, a higher gate driver voltage  $(V_{dr})$  or smaller gate resistance  $(R_G + R_S)$  will lead to a faster switching transition, and the quasi-

common-source inductance  $(L_{QS_1}, L_{QS_2})$  has a similar effect as the mutual inductance (M1). If 2DEG is shut off in P2, P3 does not exist.

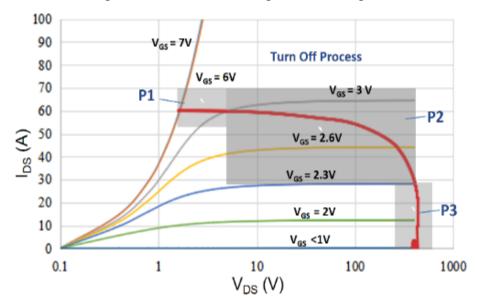

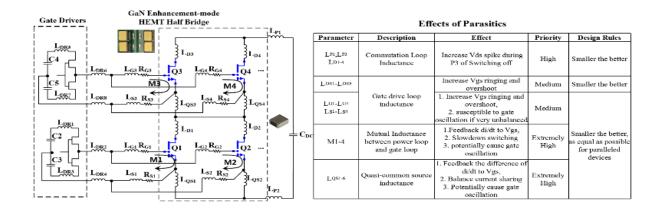

## 3.1.3 Parasitic Optimization of GaN Power Modules

Figure 29 Effects and Design Rules of Parasitic Parameters

The fast switching transition of GaN HEMTs results in a high di/dt, which further causes a voltage spike when coupled with the stray inductance in the power loop. Because of the extremely small input capacitance ( $C_{\rm ISS}$ ) of GaN HEMTs, a large gate-resistor sometimes is applied to slow down the switching transition thereby eliminating the voltage spike across the switch, which however increases the switching loss. To maximize GaN's advantage, minimizing the parasitic inductance is the ultimate solution.

The parasitic inductance is a function of the magnetic flux generated by current, as shown in (17).

$$L = \frac{\Psi}{I} = \frac{\int B^{\otimes *} dS^{\otimes}}{I} \tag{17}$$

A multi-layer PCB could significantly reduce parasitics of both the gate-drive loop and power loop by the magnetic-flux-canceling technique, i.e., the direction of the commutation

current on two adjacent layers are opposite so that the generated flux outside the loop gets cancelled. Compared to the direct-bonded-copper (DBC) substrate, the PCB design could easily adopt the multi-layer structure with smaller loop area to achieve an excellent magnetic flux canceling effect.

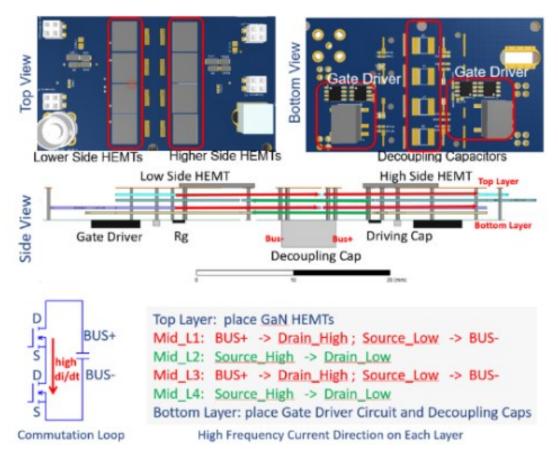

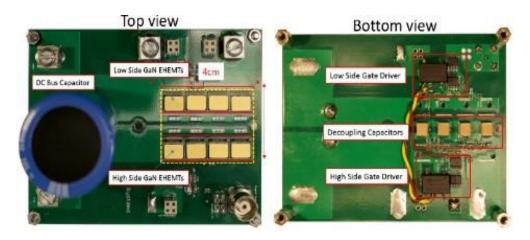

A half-bridge power module consisting of four high-side and four low-side GaN HEMTs in parallel is shown in Fig.30. Such model is rated at 650V/240A@25oC. The decoupling cap in located under the top and bottom switches to minimize the loop area, which in return reduces the loop inductance. On the other hand, the GaN package of such GaN Systems' devices with no leads or bonding wires, as shown in Fig.25, also tremendously facilitates the parallel connections. Compared with traditional TO-247 package, the stray inductance is reduced by >80%.

Such a half bridge with four GaN HEMTs in parallel is modeled in ANSYS Q3D, and the power-loop and gate-drive-loop inductance are evaluated by Finite Element Analysis (FEA). The power-loop inductance of the proposed design is only 0.7 nH. For each paralleled GaN HEMT, its quasi-common source inductance is <0.2 nH, and the gate-drive-loop inductance is 4.2 nH. Effectiveness of such parasitics reduction will be verified later on the double-pulse tester (DPT).

Figure 30 Layout of 650V/240A GaN HEMTs based Half Bridge

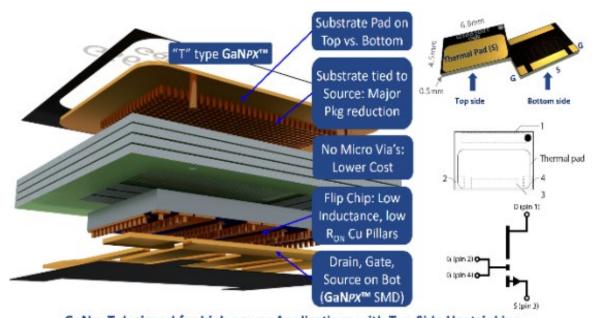

GaNPX T designed for high power Applications with Top-Side Heatsinking

Figure 31 GaNpxTM Packaging

## 3.1.4 Gate Driver Design

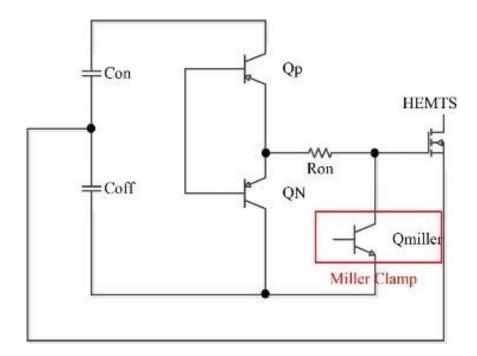

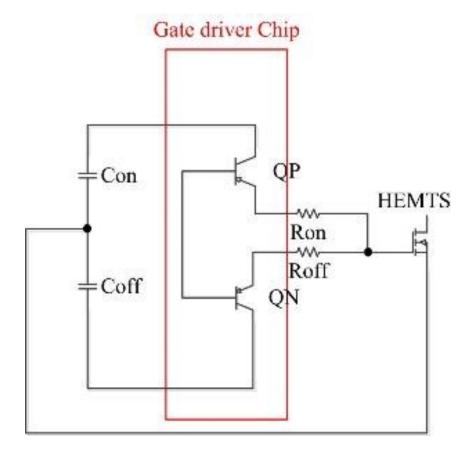

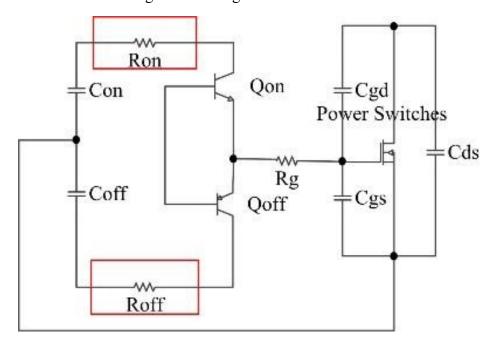

Candidates of the gate-drive circuit are shown in Fig.32. To mitigate the miller affect, a miller clamp circuit is proposed as Fig.32. When the device is fully switched off, the miller clamping transistor is on to bypass the miller charge. Fig.33 is using different gate parameters to vary the switching-on/off speed. It requires two separate output terminals though. The gate-drive circuit in our system is shown in Fig.34. Changing Ron and Roff will alter the switching on and off speed.

Figure 32 Miller Clamp Circuit

Figure 33 Two-gate-terminal Circuit

Figure 34 Gate-Drive Circuit used for GaN HEMTs

Compared to other approaches, the gate-drive circuit shown in Fig.10c has the potential to integrate the gate-drive chip (Qon, Qoff and Rg) with GaN devices on the same substrate, further reducing the gate-loop inductance. To vary the switching speed, only changing the two external resistors (Ron and Roff) is required, providing a very high flexibility.

## 3.1.5 Experimental Verification

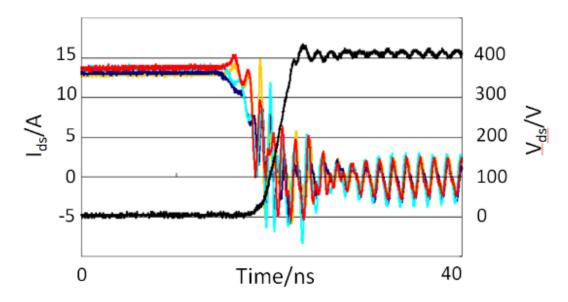

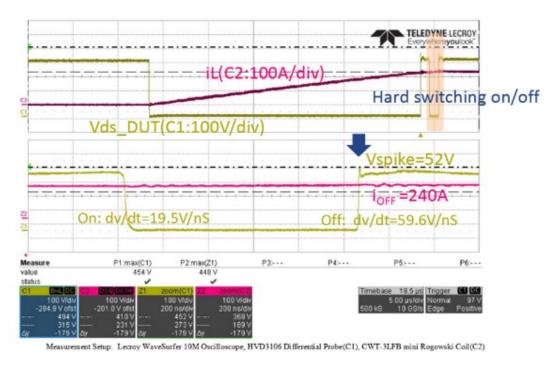

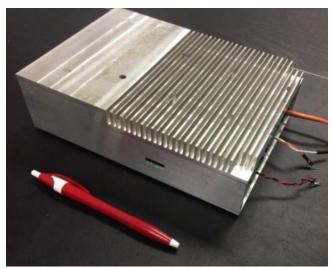

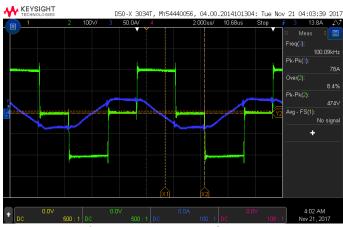

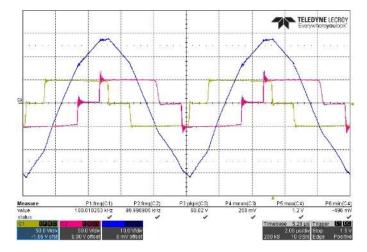

A half bridge power module using four GaN HEMTs in parallel is shown in Fig.35. Test carried out on the DPT at ~60A shows the perfect balancing between GaN HEMTs in both steady state and switching process, as shown in Fig.30. This verifies the effectiveness of the gate-loop circuit design. We further pushed the turn-off current up to 240A, as shown in Fig.31. The observed voltage spike is only 52V, validating the effectiveness of reducing the power-loop inductance.

Figure 35 Prototype of 650V/240A GaN HEMTs based Half Bridge

Figure 36 Current Balancing Among Four Paralelled Switches.

Figure 37 Double Pulse Test Waveform @400V/240 A

## 3.1.6 Applying Gan-HEMTs Power Modules in High-efficiency Systems

The above effort is to minimize the harmful effect of parasitics. In this section, focus will be shifted to increasing the system efficiency. GaN HEMTs will be applied to two DC/DC converters, one is using the ZVS turn-on technique, the other is using the hard switching-on. Both

converters adopt paralleled GaN HEMTs. The goal is to further investigate the interaction between GaN and peripheral circuits during the transient processes in the actual system.

## 3.1.7 Soft-switched DC/DC Converter

Even though GaN HEMTs have superior performance over Si devices, it still has much more switching-on loss than switching-off loss. When possible, ZVS turn-on is still preferred even when using GaN.

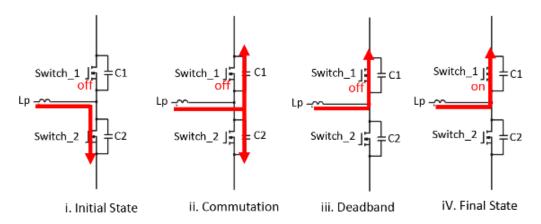

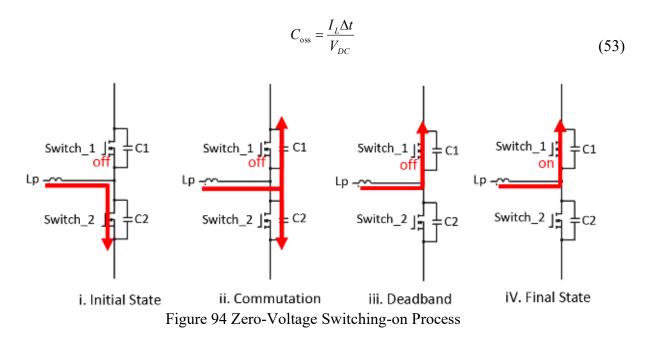

As shown in Fig.38, when switches in the same leg are both off, the energy stored in the external inductor begins to discharge C1 and charge C2. Here C1 and C2 are the switch output capacitance. Once C1 is fully discharged, Switch\_1 is ZVS on, resulting in no switching-on loss.

Figure 38 Impact of Coss on Zero Voltage Switching Process

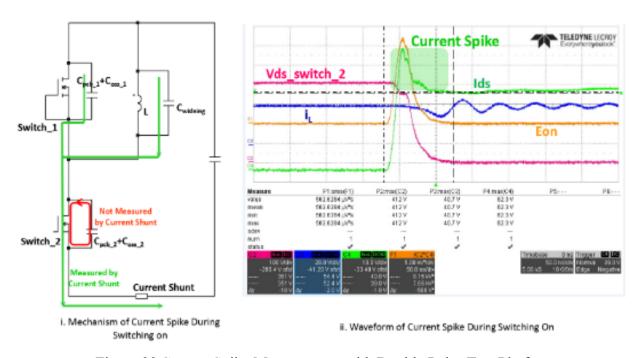

To secure ZVS, the inductor current must be high enough to deplete the overall output capacitance (GaN HEMTs + PCB board) within the dead time. Determination of the dead time and minimum required load current requires an accurate extraction of parasitic capacitance. Note when placed on the PCB, parasitic capacitance introduced by the PCB and other components is not negligible, given that Coss of the GaN HEMT is ultra-small. Such parasitic capacitance could be extracted after modelling the whole PCB in ANSYS Q3D. More accurately, an experimental method using the DPT is preferred, shown as Fig.39. The current spike measured during hard

switching on lower switches is contributed by charging the output capacitance of top switches. The integral of such a spike current divided by the DC-bus voltage indicates that equivalent capacitance is about 2nF for top switches. Therefore, the overall capacitance of the whole H-bridge is 4nF. Note such method is only effective to GaN instead of Si/SiC. Since no body diode exists inside GaN HEMTs, such current spike is solely introduced by charging the Coss without including the diode reverse-recovery current.

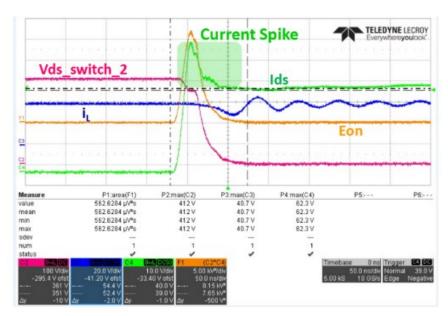

Figure 39 Current Spike Measurement with Double Pulse Test Platform

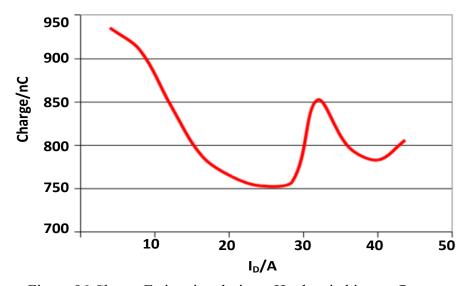

Figure 40 Coss Charge @ Different Load Current

In the reverse conduction mode, the drain will behave as the source and the source will act as the drain. When VGD is higher than Vth\_GS, the switch turns on. The voltage drop across the switch is

$$V_{SD} = V_{th GD} - V_{GS off} + I_D * R_{DSon}$$

$$\tag{18}$$

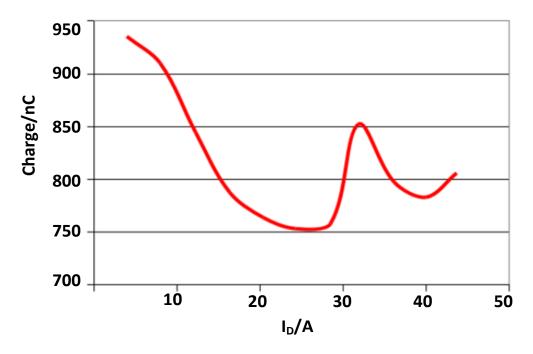

Since the gate threshold of GaN HEMTs is ~2V while a negative VGS\_off = -5.2V is added to reduce the switching loss, (18) indicates a voltage drop of ~7V in the reverse conducting mode, much larger than Si devices. A large dead time for GaN HEMTs will certainly result in the increment of the dead-band loss. On the other hand, if the dead time is too small, the switch will lose ZVS since no enough time is given to deplete the top-switch Coss, as shown in Fig.40, which results in the increment of the switching-on loss.

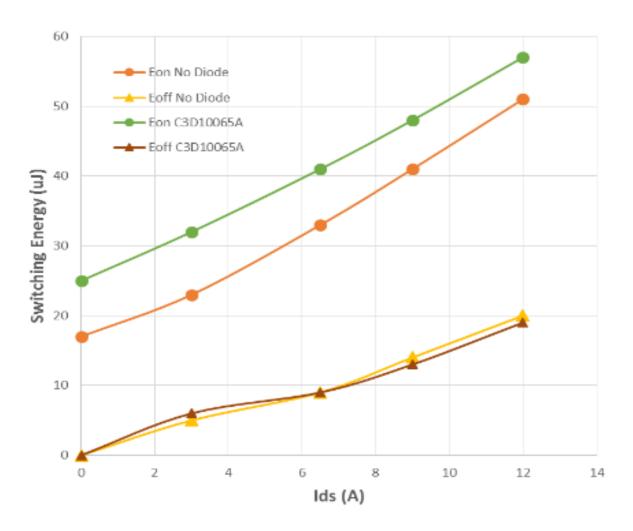

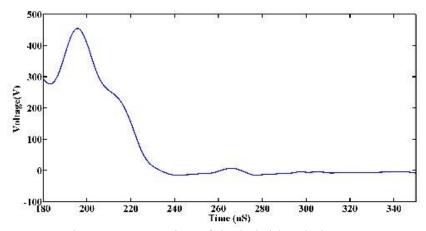

One argument is the possibility to drop the dead-band loss by anti-paralleling a SiC Schottky diode to the GaN HEMT. Firstly, such an external diode will bring additional junction capacitance and introduces the reverse-recovery current in hard switching applications. An

experimental comparison between w/n anti-parallel diode C3D10065A to GaN HEMTs is shown as Fig.41. Obviously adding an anti-paralleled diode will result in the significant increment of the switching-on loss, unless the ZVS turn-on is adopted.

Figure 41 Switching-loss Comparison w/n Anti-Parallel Diodes

Secondly, even with ZVS turn-on, the TO-247/220 packaged diodes are much bulkier than HEMTs, which will complicate the heat sink design and obstruct the reduction of the loop inductance.

#### 3.1.8 Hard-switched DC/DC Converter

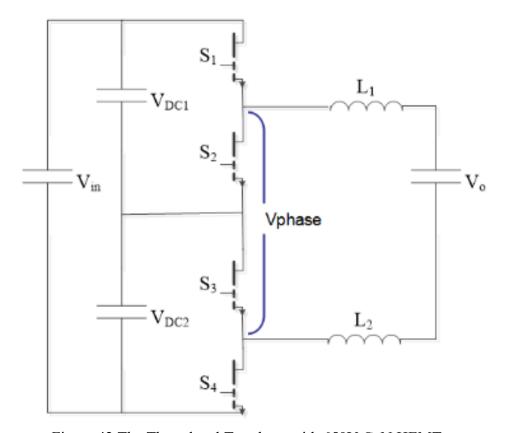

To apply 650V GaN HEMTs to an 800V/400V DC-DC converter, a multi-level topology is an excellent candidate, as shown in Fig.42. When S1 and S4 are turned on, the power is flowing from Vin to Vo. When S1 and S4 are off, the inductor current will freewheel through S2 and S3. Essentially this circuit acts as a hard-switched bidirectional buck/boost converter. Two 30A switches are paralleled.

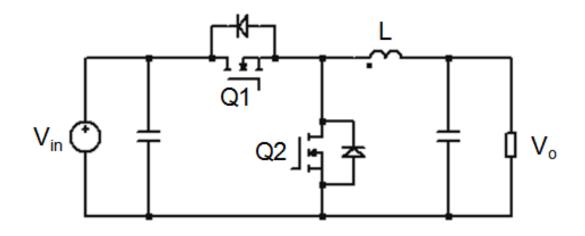

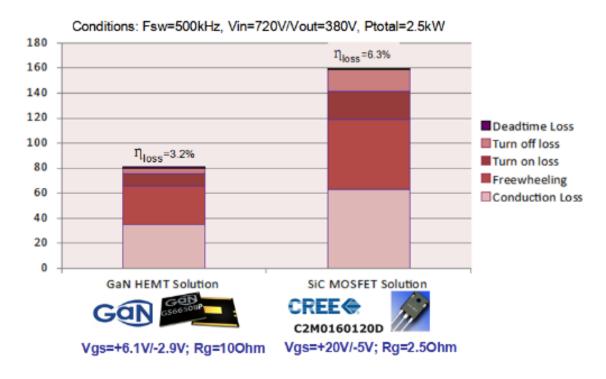

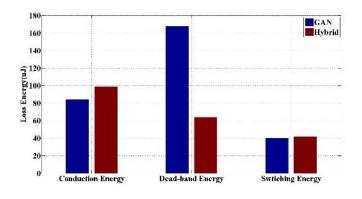

In addition, a conventional buck converter using 1200V SiC MOSFETs is the backup candidate, as shown in Fig.43. Assume all converters are running at 500kHz. The system loss breakdown of two different systems is shown as in following figure, indicating that the 650V GaN HEMT has great advantages on both the conduction and switching performance.

Figure 42 The Three-level Topology with 650V GaN HEMTs

Figure 43 The Conventional Buck Converter with 1200V SiC MOSFETs

Figure 44 System Loss Breakdown Comparison between Two Solutions

Such comparison of these two hard-switching converters is not aiming to compare these two types of WBG devices, given 1200V devices usually have much worse conducting and switching performance than low-voltage switches. This case validated that 1) GaN HEMTs could be used in hard switching, 2) external diode will increase the switching loss. Shown in Fig.44, the

increment of the switching-on loss is due to the reverse recovery current of Q2 being added to the Q1 turn-on current.

# 3.1.9 GaN Design Prototype and Experiments

Table 2 Values of key parameters

| Symbol    | Definition                                              | Values     |

|-----------|---------------------------------------------------------|------------|

|           | Switch equivalent capacitance                           | 2nF        |

|           | DC-bus capacitance                                      | 10μF       |

| L         | Transformer leakage inductance reflected to the primary | 11.5μΗ     |

| n         | Transformer turn ration                                 | 1:1        |

| $f_{sa}$  | Ceiling switching frequency                             | 500kHz     |

| $V_{in}$  | Nominal input voltage                                   | 208VAC     |

| $V_{out}$ | Output voltage                                          | 200~450VDC |

| P         | power                                                   | 0~7.2kW    |

| Io        | Nominal output current of each module                   | 20A        |

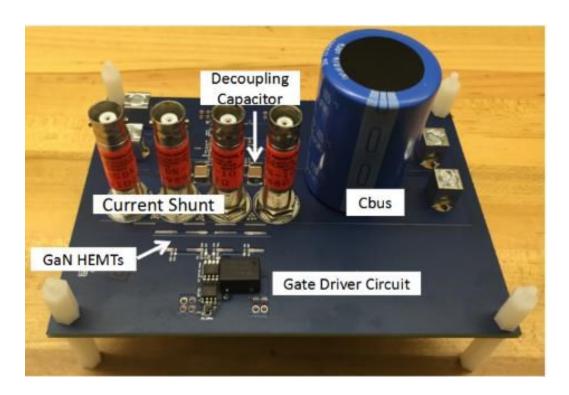

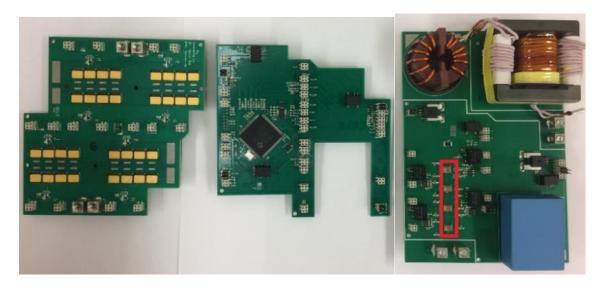

A. Switch Test. As shown in Fig.45, a DPT system with four GaN HEMTs in parallel was built with exactly the same parasitics as the final charger. Additional current shunt resistors are applied to measure the switching off current. The experimental waveform with Ioff=56A @VDC=400V is shown as Fig.46, indicating the currents are balanced well with a small voltage spike.

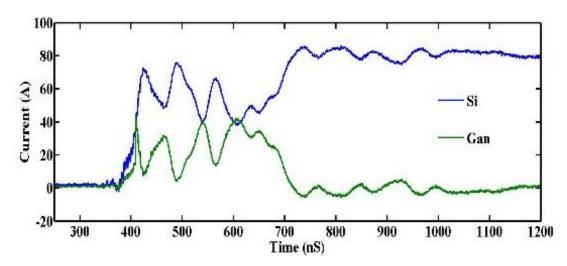

Figure 45 DPT with four GaN HEMTs in parallel

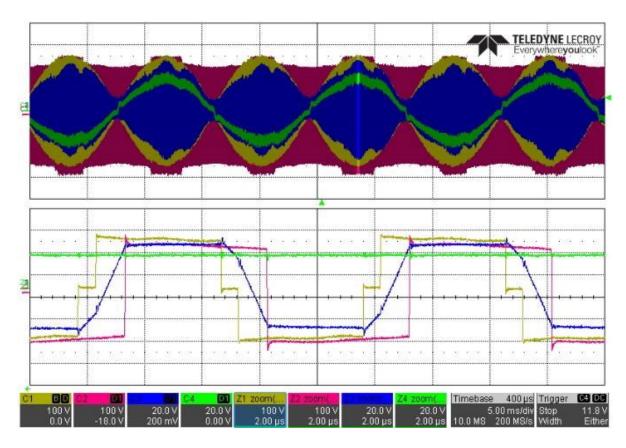

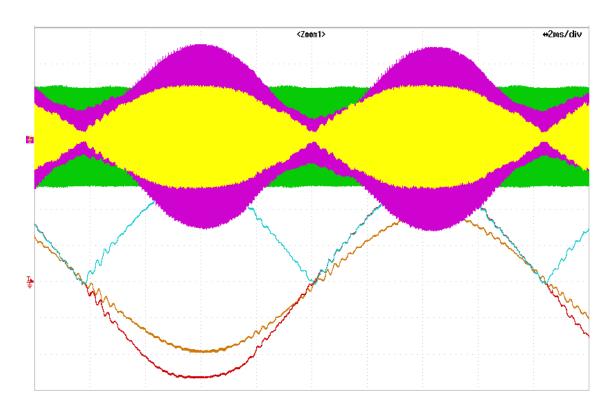

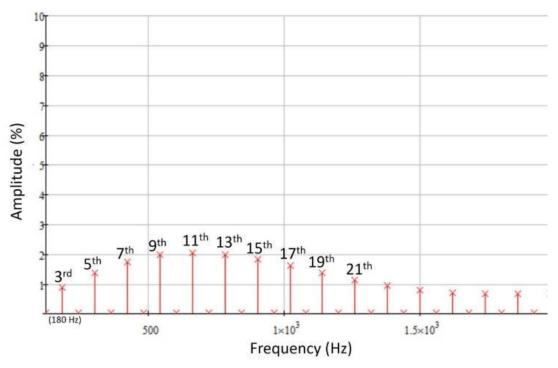

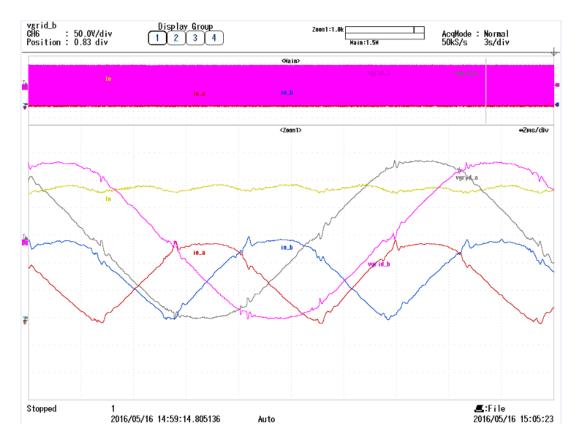

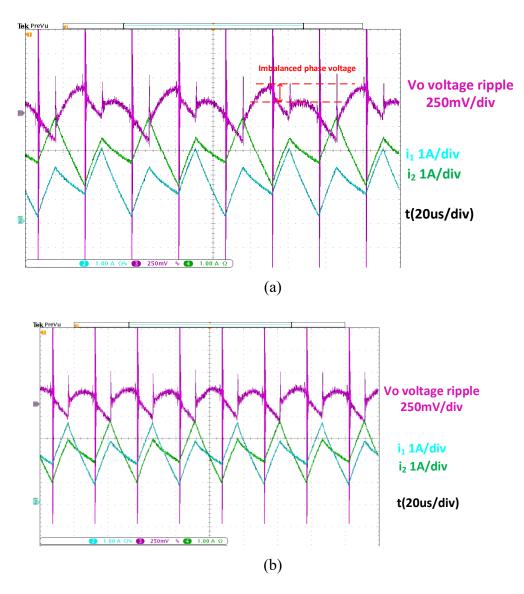

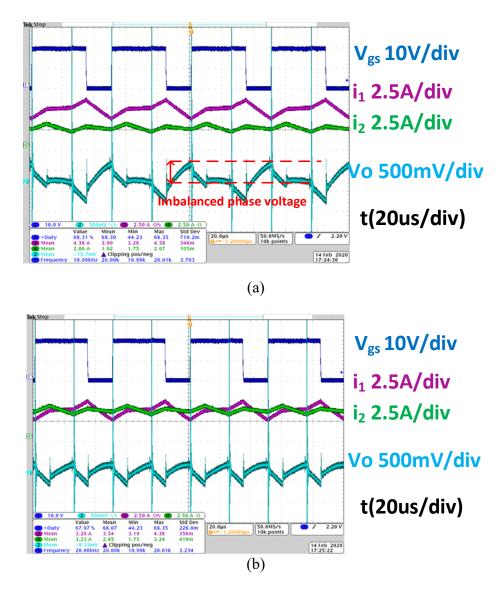

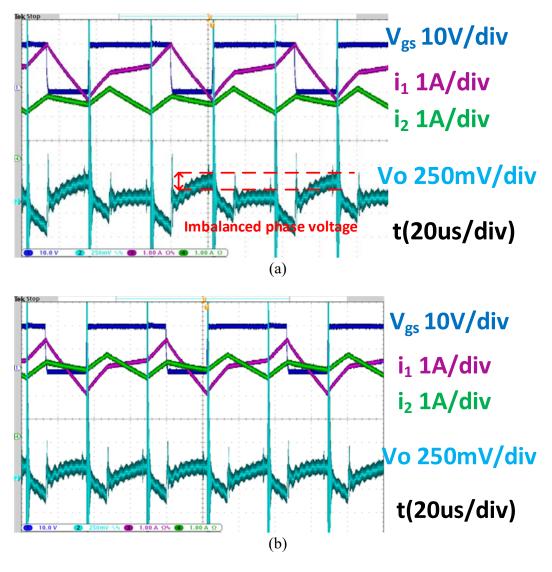

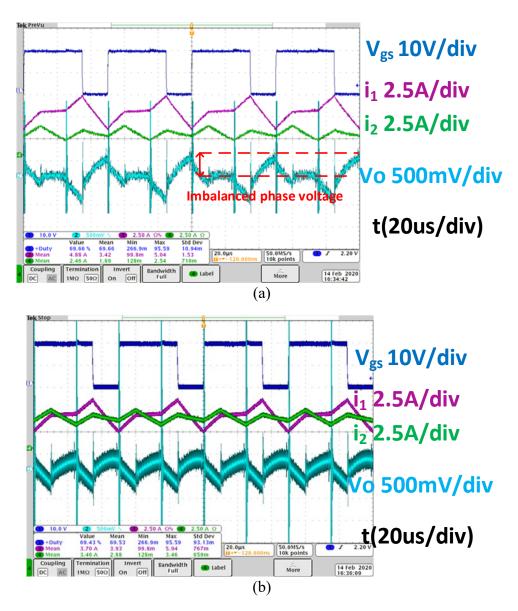

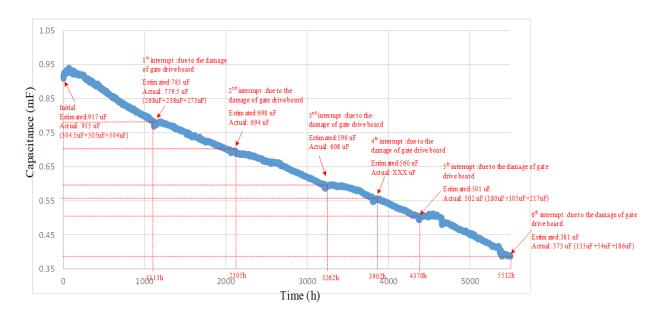

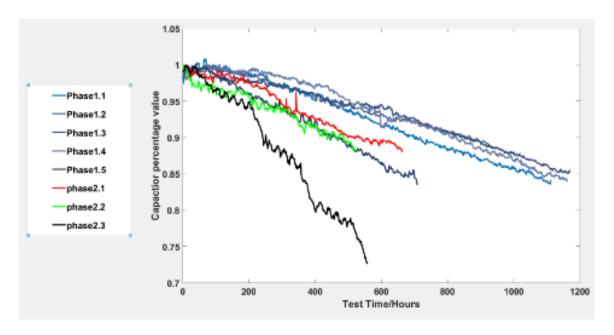

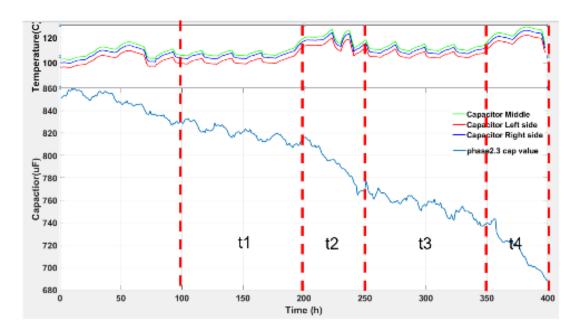

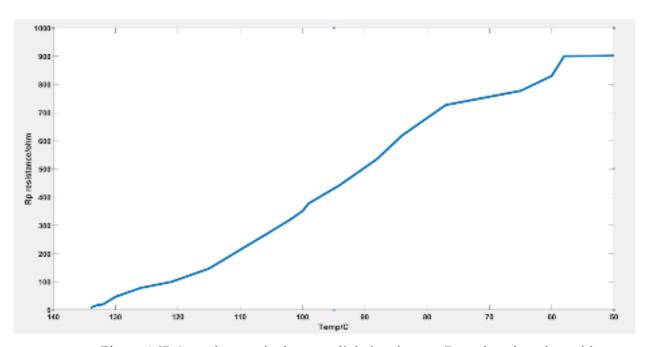

Figure 46 Current Sharing among Paralleled HEMTs @ 400V/56A During the Turn-off Process