#### Efficient, Reconfigurable, and QoS-Aware Systems for Deep Neural Networks

by

Xiaowei Wang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2022

Doctoral Committee:

Associate Professor Reetuparna Das, Chair Professor Scott Mahlke Associate Professor Lingjia Tang Professor Zhengya Zhang Xiaowei Wang xiaoweiw@umich.edu ORCID iD: 0000-0002-5883-7327

© Xiaowei Wang 2022

## DEDICATION

To my family.

#### ACKNOWLEDGMENTS

It would not be possible for me to finish this dissertation without the help of many people. First and foremost, I would like to express my sincere gratitude to my Ph.D. advisor and the dissertation committee chair, Reetuparna Das. She led me into the world of conducting research projects systematically, provided a tremendous amount of guidance to me on research with her insights in the field, and encouraged me to pursue intriguing and impactful research directions. I would also like to thank my dissertation committee members, Scott Mahlke, Lingjia Tang, and Zhengya Zhang. They provided many useful suggestions to improve the quality of dissertation. I would like to thank my collaborators for their inputs and brainstorming sessions that help to shape and improve the works in the dissertation: Jiecao Yu, Vidushi Goyal, Charles Eckert, Arun Subramaniyan, Jingcheng Wang, Valeria Bertacco, David Blaauw and Dennis Sylvester from University of Michigan; Andrew Boutros, Eriko Nurvitadhi, Charles Augustine and Ravi Iyer from Intel; Li Zhao from Alibaba. I would like to thank my fellow research group members and labmates for inspiring discussions and fun times. Thank you Daichi Fujiki, Arun Subramaniyan, Vidushi Goyal, Charles Eckert, Jack Wadden, Subarno Banerjee, Harisankar Sadasivan, Tim Dunn, Kush Goliya, Yufeng Gu and Alireza Khadem. I would also like to thank my fellow graduate student friends and the staff members at CSE for the conversations and help. I would like to thank the first responders who made it possible to conduct research activities throughout the pandemic times.

Finally, I would like to thank all my family members for their support. I would like to express my special thanks to my beloved wife, Yuqi Gu, who accompanied me, shared my happiness, and constantly gave me advice and encouragement throughout my Ph.D. journey.

# TABLE OF CONTENTS

| DEDICATION      | ii  |

|-----------------|-----|

| ACKNOWLEDGMENTS | iii |

| LIST OF FIGURES | vii |

| LIST OF TABLES  | x   |

| ABSTRACT        | xi  |

## CHAPTER

| 1 Introd                                  | luction                                                             | 1  |  |  |

|-------------------------------------------|---------------------------------------------------------------------|----|--|--|

| 1.1                                       | Improving Compute-in-Cache DNN Accelerator with Model Compression . | 3  |  |  |

| 1.2                                       | Reconfigurable In-Memory Computing for DNN Acceleration             | 5  |  |  |

| 1.3                                       | Efficient Cache Data Compression                                    | 7  |  |  |

| 1.4                                       | Satisfying QoS of Collocated DNN Service                            | 9  |  |  |

| 2 Backg                                   | round and Related Works                                             | 12 |  |  |

| 2.1                                       | The Computation Pattern of DNNs                                     | 12 |  |  |

| 2.2                                       | In-Memory Computing for DNN                                         | 14 |  |  |

|                                           | 2.2.1 Overview of In-Memory DNN Acceleration                        | 15 |  |  |

|                                           | 2.2.2 In-SRAM Bit-Serial Computing with CPU Cache                   | 17 |  |  |

| 2.3                                       | Sparsity and Quantization in DNNs                                   | 22 |  |  |

|                                           | 2.3.1 Sparsity in DNNs                                              | 22 |  |  |

|                                           | 2.3.2 Quantization in DNNs                                          | 23 |  |  |

|                                           | 2.3.3 Hardware Adaptations                                          | 24 |  |  |

| 2.4                                       | FPGAs for DNN                                                       | 25 |  |  |

|                                           | 2.4.1 FPGA Architecture                                             | 26 |  |  |

|                                           | 2.4.2 DNN Acceleration on FPGA                                      | 27 |  |  |

| 2.5                                       | DNNs on CPU                                                         | 29 |  |  |

|                                           | 2.5.1 Cache Data Compression                                        | 30 |  |  |

|                                           | 2.5.2 QoS for Collocated and DNN Workloads                          | 31 |  |  |

| 3 Efficient In-Cache Acceleration of DNNs |                                                                     |    |  |  |

| 3.1                                       | Sparsity-Aware Architectures                                        | 33 |  |  |

|            | 3.1.1  | Coalescing Channels                                   |     |   |     |   | 35        |

|------------|--------|-------------------------------------------------------|-----|---|-----|---|-----------|

|            | 3.1.2  | Overlapping Filters                                   |     | • |     |   | 41        |

| 3.2        | Reduce | ed Precision Architecture                             |     | • |     |   | 44        |

|            | 3.2.1  | Ternary Networks                                      |     |   |     |   | 44        |

|            | 3.2.2  | Binary Networks                                       |     |   |     |   | 46        |

| 3.3        |        | tion Methodology                                      |     |   |     |   | 46        |

| 3.4        | Result | S                                                     |     | • |     |   | 48        |

|            | 3.4.1  | Latency                                               |     |   |     |   | 48        |

|            | 3.4.2  | Accuracy                                              |     |   |     |   | 50        |

|            | 3.4.3  | Energy                                                |     |   |     |   | 52        |

|            | 3.4.4  | Model Size                                            |     |   |     |   | 55        |

| - <b>-</b> |        | Comparing to ASICs                                    |     |   |     |   | 55        |

| 3.5        | Summ   | ary                                                   | • • | • | • • | • | 57        |

| 4 DNN      | Accele | ration with Compute-Capable BRAM                      |     | • |     |   | <b>58</b> |

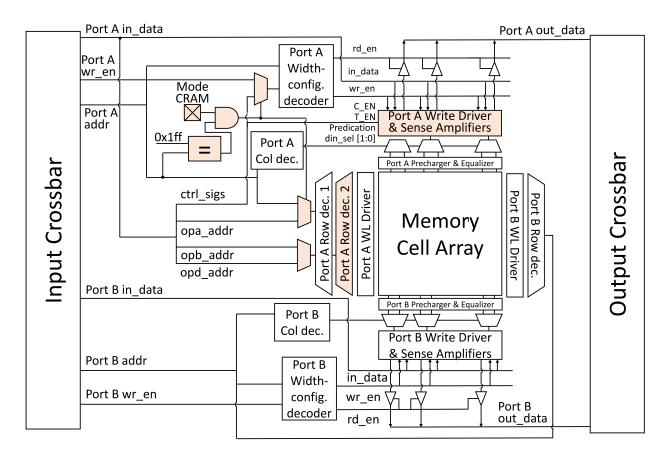

| 4.1        | Compi  | ıte-Capable Block RAMs for FPGAs                      |     |   |     |   | 60        |

|            | 4.1.1  | Enhanced BRAM Architecture                            |     | • |     |   | 60        |

|            | 4.1.2  | Peak MAC Throughput Gain                              |     | • |     |   | 62        |

|            |        | Area Overhead and CAD Support                         |     |   |     |   | 63        |

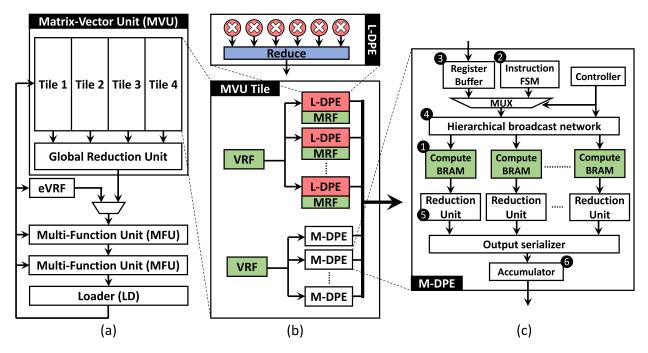

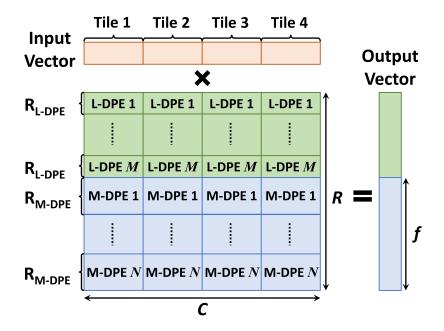

| 4.2        | RIMA   | : DNN Reconfigurable In-Memory Accelerator            |     |   |     |   | 64        |

|            | 4.2.1  | Target DNN Workloads                                  |     |   |     |   | 64        |

|            | 4.2.2  | Accelerator Architecture                              |     |   |     |   | 65        |

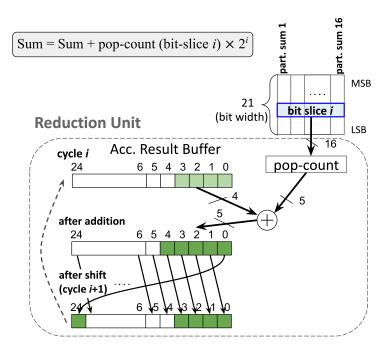

|            | 4.2.3  | Memory Dot-Product Engines                            |     |   |     |   | 67        |

|            | 4.2.4  | Transposed Integer Arithmetic                         |     |   |     |   | 67        |

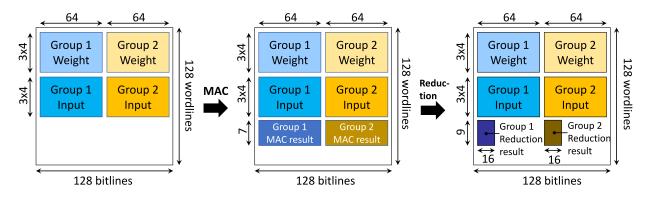

|            | 4.2.5  | Transposed Block Floating-Point Arithmetic            |     |   |     |   | 70        |

| 4.3        |        | ecture Modeling & Customization                       |     |   |     |   | 71        |

|            |        | Load Partitioning and Execution                       |     |   |     |   | 71        |

|            | 4.3.2  | Design Space Exploration & Architecture Customization |     |   |     |   | 72        |

|            |        | Reconfiguration Process of FPGA                       |     |   |     |   | 74        |

| 4.4        |        | tion Methodology                                      |     |   |     |   | 74        |

|            |        | Platforms and Benchmarks                              |     |   |     |   | 74<br>75  |

|            |        | Performance Modeling                                  |     |   |     |   | 75<br>76  |

| 4.5        |        | s                                                     |     |   |     |   | 76        |

| 4.0        | 4.5.1  | RIMA Architecture Design Space Exploration            |     |   |     |   | 76        |

|            |        | RIMA FPGA Implementation Results                      |     |   |     |   | 80        |

|            |        | Performance Results                                   |     |   |     |   | 80        |

| 4.6        | Summ   |                                                       |     |   |     |   | 82        |

|            |        | ression with In-SRAM Data Comparison                  |     |   |     |   | 84        |

|            | _      |                                                       |     |   |     |   |           |

| 5.1        |        | Organization and Data Addressing                      |     |   |     |   | 84<br>87  |

| 5.2        |        | ression Design                                        |     |   |     |   | 85<br>85  |

|            | 5.2.1  | 1 11 5                                                |     |   |     |   | 85<br>87  |

|            | 5.2.2  | Compressed Data Format and Decompression Procedure    |     |   |     |   | 87        |

|            | 5.2.3  | Compression Procedure: Data Matching                  | • • | • | ••• | • | 89        |

|                  | 5.2.4 Data Replacement Procedure                                                                                  | 90  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 5.3              | Evaluation Methodology                                                                                            | 92  |  |  |  |

| 5.4              | Results                                                                                                           | 93  |  |  |  |

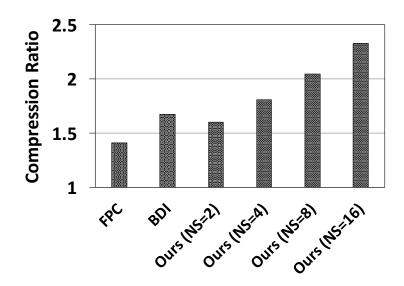

|                  | 5.4.1 Compression Ratio $\ldots$ | 93  |  |  |  |

|                  | 5.4.2 Miss Rate $\ldots$                                                                                          | 95  |  |  |  |

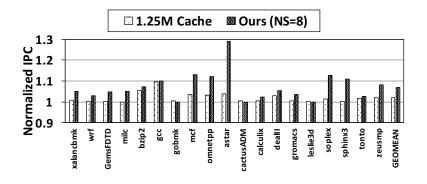

|                  | 5.4.3 Performance $\ldots$       | 95  |  |  |  |

|                  | 5.4.4 Discussion $\ldots$        | 95  |  |  |  |

| 5.5              | Summary                                                                                                           | 97  |  |  |  |

| 6 QoS-A          | ware Collocation for Deep Neural Networks                                                                         | 98  |  |  |  |

| 6.1              | Opportunity for Collocated DNN to Satisfy QoS                                                                     | 98  |  |  |  |

| 6.2              | Design of DQG                                                                                                     | 100 |  |  |  |

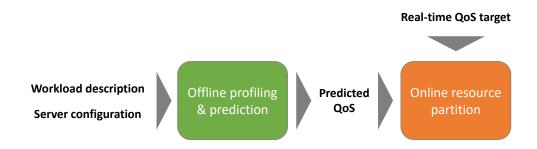

|                  | 6.2.1 Offline Performance Prediction                                                                              | 100 |  |  |  |

|                  | 6.2.2 Online Resource Partition                                                                                   | 101 |  |  |  |

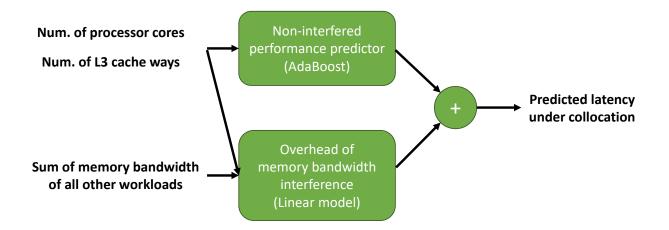

| 6.3              | Predictor for Latency                                                                                             | 102 |  |  |  |

|                  | 6.3.1 Prediction Model                                                                                            | 102 |  |  |  |

|                  | 6.3.2 Training Procedure                                                                                          | 104 |  |  |  |

| 6.4              | Evaluation Methodology                                                                                            | 104 |  |  |  |

|                  | 6.4.1 Hardware and Software Framework Setup                                                                       | 104 |  |  |  |

|                  | 6.4.2 Workloads                                                                                                   | 105 |  |  |  |

|                  | 6.4.3 Settings for Profiling and Partitioning                                                                     | 106 |  |  |  |

| 6.5              | Results                                                                                                           | 107 |  |  |  |

|                  | 6.5.1 Collocation with Other DNN Workloads                                                                        | 107 |  |  |  |

|                  | 6.5.2 Collocation with Core Stressing Microbenchmarks                                                             | 107 |  |  |  |

|                  | 6.5.3 Collocation with Memory-Bandwidth Stressing Microbenchmarks .                                               | 108 |  |  |  |

| 6.6              | Summary                                                                                                           | 109 |  |  |  |

| 7 Conclu         | usion                                                                                                             | 110 |  |  |  |

| . 201101         |                                                                                                                   |     |  |  |  |

| BIBLIOGRAPHY 113 |                                                                                                                   |     |  |  |  |

# LIST OF FIGURES

#### FIGURE

| 2.1  | Computation of a Convolutional Layer.                                                                         | 14 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Overview of the algorithm for a LSTM layer. The computation bottleneck is in                                  |    |

|      | the Matrix Vector Multiplication (MVM).                                                                       | 15 |

| 2.3  | Neural Cache Architecture Overview.                                                                           | 18 |

| 2.4  | Steps for different in-SRAM bit-serial (a) addition, (b) multiplication operations.                           |    |

|      | Green and blue shades correspond to read and write activated wordlines at each                                |    |

|      | time step. The bits from a single data word are marked with the same color                                    | 19 |

| 2.5  | Neural Cache Data Mapping of a 2.5MB Slice.                                                                   | 20 |

|      |                                                                                                               |    |

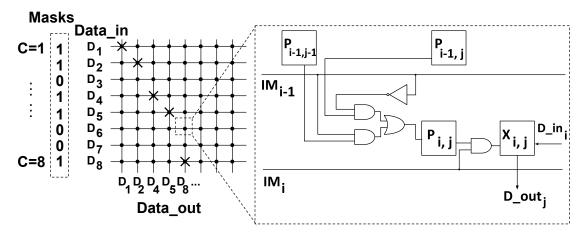

| 3.1  | Sparse Convolution with Coalescing.                                                                           | 34 |

| 3.2  | Architecture of Coalescing Unit (CU). Left: Crossbar and example data before                                  |    |

|      | coalescing (eight channels - $D_1$ to $D_8$ ) and after coalescing ( $D_1$ , $D_2$ , $D_4$ , $D_5$ , $D_8$ ). |    |

|      | Right: Reconfiguring Peripheral for one switch connectivity. $X_{i,j}$ : Output of                            |    |

|      | RP to Crossbar, whether the switch at $(i, j)$ is connected. $P_{i,j}$ : Boolean value                        |    |

|      | of whether the position $(i, j)$ is on the "path." $IM_i$ : Channel mask for the <i>i</i> -th                 |    |

|      | channel.                                                                                                      | 35 |

| 3.3  | Sparse Convolution with Overlapping.                                                                          | 42 |

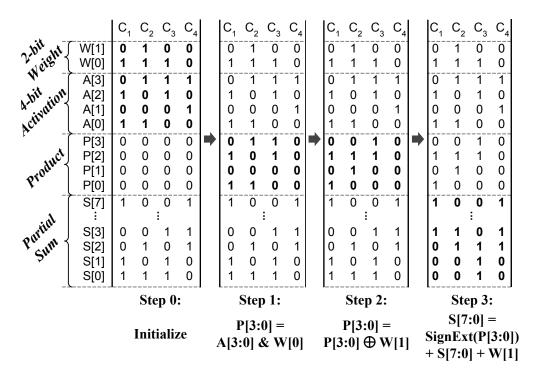

| 3.4  | MAC step of Ternary Network.                                                                                  | 45 |

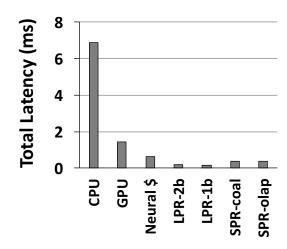

| 3.5  | Total Convolution Latency Across Layers                                                                       | 49 |

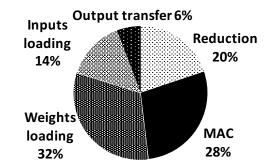

| 3.6  | Latency Breakdown of SPR-Coal Configuration.                                                                  | 49 |

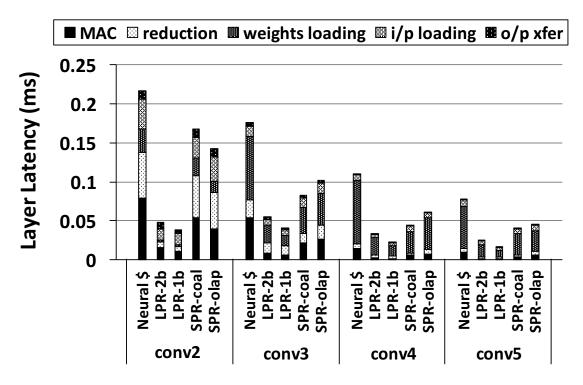

| 3.7  | Latency of Each Convolutional Layer.                                                                          | 50 |

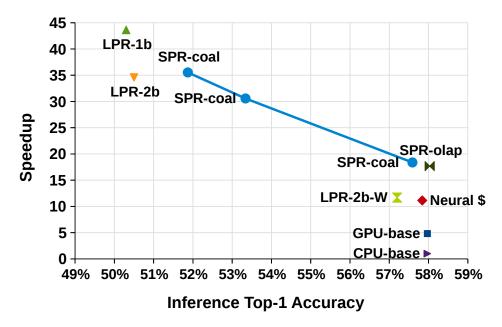

| 3.8  | Accuracy vs Performance for AlexNet                                                                           | 51 |

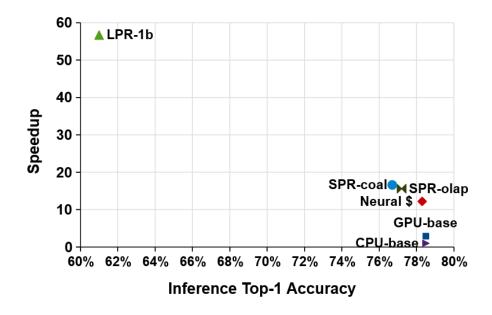

| 3.9  | Accuracy vs Performance for Inception V3                                                                      | 52 |

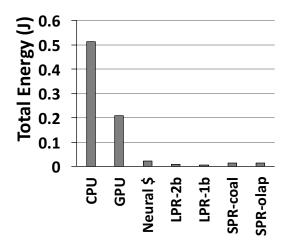

| 3.10 | Total Energy for Convolution                                                                                  | 53 |

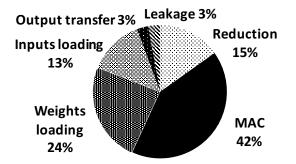

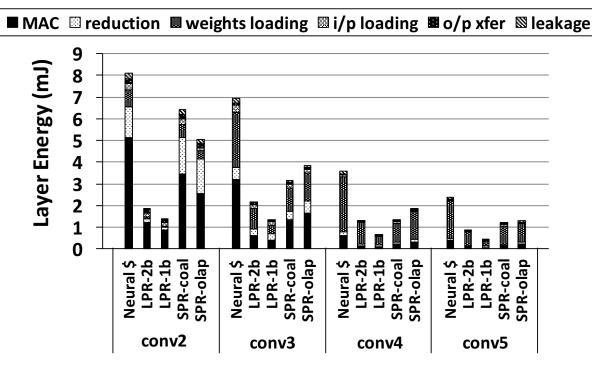

| 3.11 | Energy Breakdown of SPR-Coal Configuration.                                                                   | 53 |

| 3.12 | Energy of Each Convolutional Layer                                                                            | 54 |

| 4.1  | Block diagrams for internal architecture of the compute-capable dual-port single-                             |    |

| 1.1  | bank BRAM. The added/modified circuitry is highlighted in color.                                              | 59 |

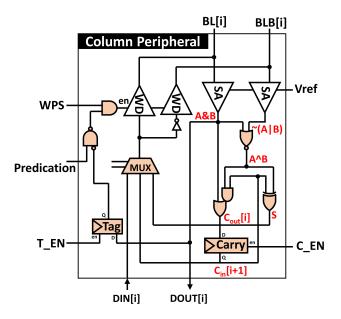

| 4.2  | Block diagrams for peripheral logic circuitry added for each bit-line of the mem-                             | 05 |

| 1.4  | ory cell array. The added/modified circuitry is highlighted in color.                                         | 59 |

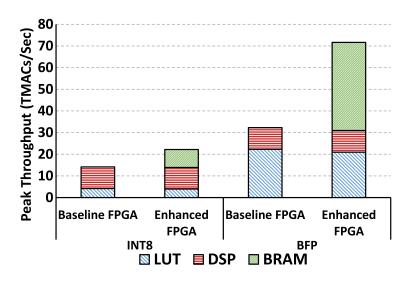

| 4.3  | Peak MAC throughput gains when enhancing a baseline Stratix 10 GX2800                                         | 09 |

| ч.J  | FPGA with compute-capable BRAMs for 8-bit integer and block floating-point                                    |    |

|      |                                                                                                               | 62 |

|      | precisions                                                                                                    | 02 |

| 4.4  | Block diagrams showing: (a) overview of the RIMA architecture, (b) our pro-<br>posed hybrid MVU tile, and (c) the architecture of an M-DPE, with compute-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cc       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.5  | capable BRAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66       |

| 1.0  | from all values is accumulated with pop-count, addition, and shift.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69       |

| 4.6  | In-memory operations for dot-product with block floating-point in a compute-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|      | capable BRAM. Vector has 512 elements and is partitioned into 2 exponent-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -        |

| 4.7  | sharing groups in BFP. $\dots$ Partitioning of a matrix-vector multiplication operation to an example RIMA architecture with 4 tiles, $M$ L-DPEs and $N$ M-DPEs. $\dots$ $\dots$ $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70<br>73 |

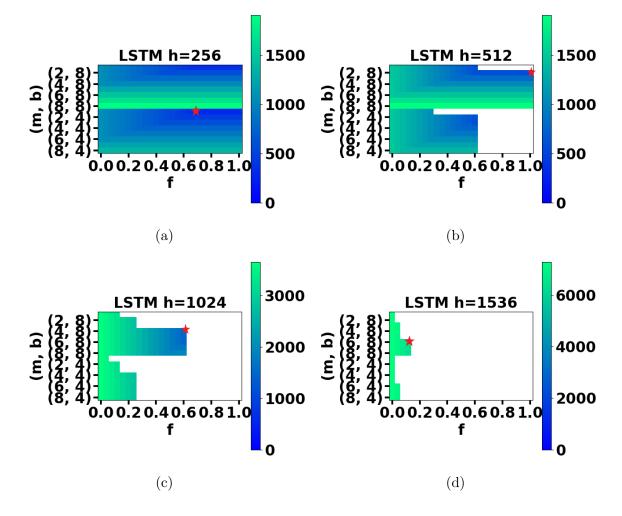

| 4.8  | Design space exploration for the RIMA architecture parameters with number<br>of tiles and L-DPE lanes fixed at 4 and 40, respectively. Each pixel is one<br>architecture configuration and the color represents the processing latency. White                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 4.9  | points are invalid configurations violating the resource constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77       |

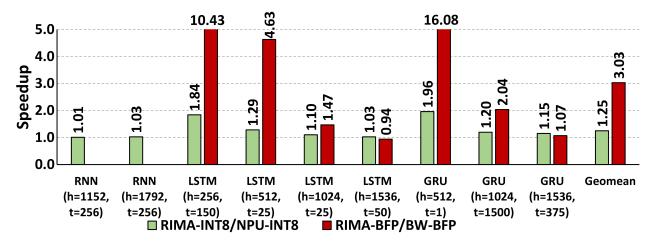

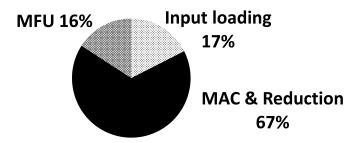

| 4.10 | BFP, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80<br>81 |

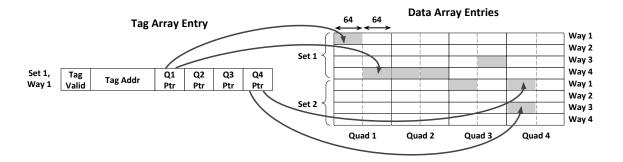

| 5.1  | Cache slice organization for 1MB Intel Xeon LLC (Huang et al., 2013). (a) High<br>level structure of the ways, banks and data arrays. Data bus connects banks in<br>different ways of the same quad. (b) The set mapping and data accessing logic<br>within a bank. The sets are interleaved within an array, and the data of a cache<br>line is distributed. The row column and left right array collector chooses the                                                                                                                                                                                                                                                                                                                  |          |

| 5.2  | line is distributed. The row, column, and left-right-array selector chooses the accessed data location for a given Set ID. Seg ID is a 1-bit value to select one of the two 32-bit segments of the 64 bits from the same cache line in an array The mapping from tag entry to data arrays after compression. Left: The format of an entry in the tag array (Set 1, Way 1) with the proposed compression method. Right: Logical structure of the partial data array that the tag entry may point to. Each cache line is partitioned into 4 quads, each further partitioned into 2 segments of 64 bits. The pointers for each quad include the address of the two segments in the pointer. The pointers for quad 2 and 3 are not shown for | 86       |

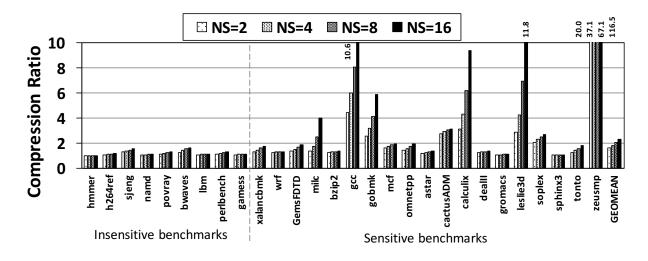

| 5.3  | simplicity. The shaded boxes represent the actual data segments that correspond<br>to this tag entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 86       |

|      | with compression. For each benchmark the compression ratio is an average over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|      | the entire program execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91       |

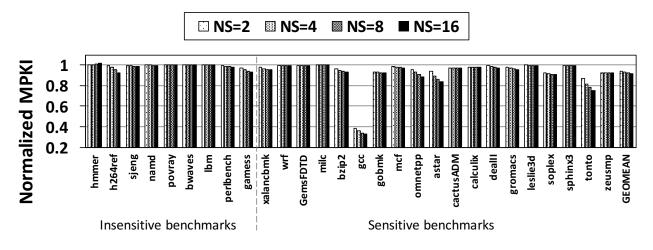

| 5.4  | The relative MPKI (miss per kilo instruction) of the compressed cache, normal-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|      | ized to a baseline conventional cache. Lower is better.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92       |

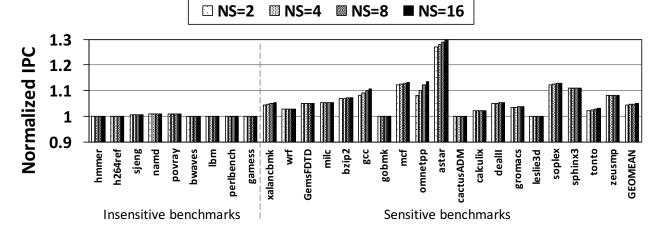

| 5.5  | The relative IPC of the benchmarks with the compressed cache, normalized to a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.5      |

| 5.6  | baseline conventional cache. Higher is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93       |

| 5.7  | compression method, all with 2048-set 1MB data array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94       |

| 0.1  | pression method (NS=8).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 94       |

| 6.1 | Overview of the Workflow of DQG                                        | 100 |

|-----|------------------------------------------------------------------------|-----|

| 6.2 | Performance predictor for a DNN workload                               | 102 |

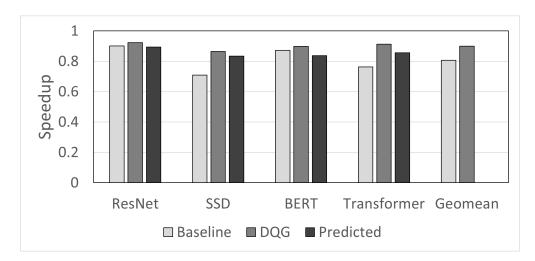

| 6.3 | DQG Result with DNNs as BE workloads                                   | 108 |

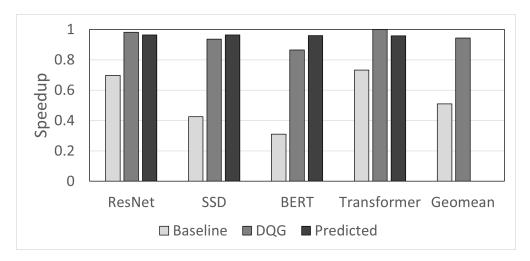

| 6.4 | DQG Result when collocated with core-thrashing microbenchmarks         | 108 |

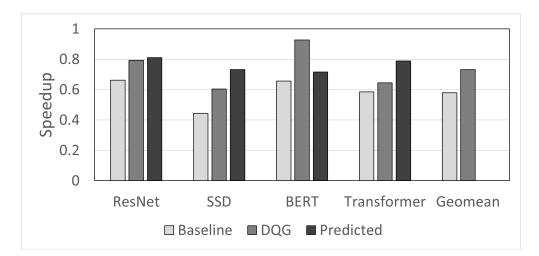

| 6.5 | DQG Result when collocated with memory-bandwidth-thrashing microbench- |     |

|     | marks                                                                  | 109 |

# LIST OF TABLES

### TABLE

| 3.1 | Baseline CPU & GPU Configuration                                               | 47  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.2 | Pruning Rate of SPR-coal and SPR-olap                                          | 55  |

| 3.3 | Model Size Comparison                                                          | 55  |

| 3.4 | Efficiency of Inception v3 Model                                               | 56  |

| 3.5 | Comparison with ASICs. Area scaled to 22 nm                                    | 56  |

| 4.1 | FPGA implementation results of RIMA instances customized for each workload.    |     |

|     | The operating frequencies are for the M-DPE clock domain.                      | 79  |

| 4.2 | Processing latency comparison between RIMA and Nvidia Titan V GV100 GPU.       |     |

|     | All numbers are in milliseconds                                                | 81  |

| 5.1 | Remapping of control signals to retrieve data after compression within Quad 1. | 88  |

| 5.2 | Specification of the Simulated CPU Model                                       | 93  |

| 6.1 | Different types of server resources and their isolation mechanisms             | 99  |

| 6.2 | Server configuration                                                           | 105 |

| 6.3 | List of DNN models as latency-critical workloads                               | 106 |

| 6.4 | Experiment Configuration by BE workloads                                       | 106 |

#### ABSTRACT

Deep Neural Networks (DNN) are an important machine learning application which has high compute and memory bandwidth requirements to the underlying computer systems. Prior works have proposed domain specific accelerators for DNNs, and in-memory computing architectures are especially promising as they can provide high memory bandwidth and computing throughput at the same time.

The first part of the dissertation targets improving the efficiency of a recent SRAMbased in-memory DNN accelerator on sparse and low-bitwidth DNN models. In this system, the last level cache of a CPU is repurposed as a highly parallel bit-serial vector processor, achieved by the circuit modification to the SRAM array peripherals and a transposed data mapping. We propose two hardware/software co-design methods with customized model pruning algorithms to fully utilize the sparsity. A specialized bit-serial algorithm is developed for the operations on low bitwidth data.

While the above in-cache computing system is highly efficient, its hardware architecture lacks the flexibility to be optimally reconfigured for different DNN models. The second part of the dissertation proposes a reconfigurable in-SRAM computing DNN accelerator based on block RAMs (BRAM) on FPGAs. We propose circuit changes to the BRAM to enable bit-serial in-memory computing, which turns BRAMs as both bit-serial vector units and data storage. Building on the compute-capable BRAMs, we further propose customized accelerator instances for different DNN models, which outperforms a state-of-the-art DNN accelerator on FPGA.

DNN workloads can also be run on general purpose CPUs in datacenters. Cache compression is a technique to reduce the cache miss rate on CPU, which benefits DNNs as well as many other applications. In the third part of the dissertation, we present a novel method to compress cache data with efficient in-SRAM data comparison. Further, as datacenters frequently collocate multiple workloads to increase server utilization, the Quality-of-Service (QoS) of DNN workloads, such as latency, can be affected. The final part of the dissertation proposes a systematic approach to achieve the QoS of DNNs under collocation, with resource partition to reduce interference, and a proposed latency prediction model to choose the partition that satisfies the QoS requirement.

## CHAPTER 1

# Introduction

In the last decade, the Deep Neural Networks (DNN) has been pervasively used as a machine learning mechanism to solve many real-world problems that are traditionally difficult tasks for computers. The application domains span from computer vision tasks such as image classification (He et al., 2016) and object detection (Liu et al., 2016), to language processing tasks such as sentimental analysis (Devlin et al., 2018), machine translation (Vaswani et al., 2017), and speech recognition (Rao et al., 2017).

Along with the development of more and more DNN models is the increased attention on how to perform the necessary computation for the DNNs efficiently. DNN models can contain millions to billions of parameters and the computation is usually in vectors or matrices so the total number of arithmetic operations is huge. Fortunately, as there is a high level of parallelism in the operations, vector processor architectures can speed up the DNN computation. Further, as there are several key kernel operations that takes up most of the computation time such as convolution and matrix-vector multiplication, many works have analyzed the common computation and data movement pattern of such operations and built domain specific accelerators for DNNs, implementing the kernels in custom hardware (Chen et al., 2016, 2014). The TPU (Jouppi et al., 2017) is an example DNN accelerator, where the matrix-matrix multiplication kernel is implemented with a non-traditional hardware architecture of systolic arrays that has a high effective computing throughput.

An important and rapidly evolving technique for DNN hardware acceleration is in-memory

computing. The main idea of in-memory computing is to perform computation near or within the memory structure. In-memory computing essentially improves the data movement bandwidth between the computing units and the data storage. As the DNN models usually have a large model size (more than tens of megabytes), the in-memory computing is helpful in alleviating the data movement bottlenecks. In addition, the large number of computing units can also speed up the parallel computing instructions of DNN. One recent work, Neural Cache (Eckert et al., 2018), utilizes the last-level cache of CPUs for SRAM-based in-memory computing to accelerate DNN. Their approach achieves a high overall computing unit. In first part of the dissertation, we aim at improve the above in-cache DNN accelerator with two model compression techniques, weight pruning and ultra-low precision quantization. We propose software/hardware co-designing methods to achieve this goal.

DNNs can also be accelerated on FPGAs, which offer a balance of adequate efficiency and high reconfigurability and therefore can adapt to new computation needs quickly. We observe that the in-memory computing opportunities on FPGAs have not been explored despite the large on-chip SRAM memory available. In the second part of the dissertation, we propose methods to adapt the on-chip memory of FPGA for in-SRAM computing, resulting in a boost of total computing throughput. We further show how this enhanced FPGA can improve RNN latency against Brainwave, a popular DNN accelerator on FPGA.

Multi-core CPUs can also serve as the platform for DNN computation, as this is the costsensitive option or where machine homogeneity is preferred in some datacenters. In the third part of the dissertation, we explore a specific type of microarchitectural optimization, cache compression, which helps improve the performance of cache-sensitive workloads. Specifically, we propose an efficient cache deduplication method based on in-memory data comparison. In datacenters, there are cases where the DNN workloads need to be collocated with other workloads on the same server during periods with high service request rates. Such collocation can negatively affect the Quality-of-Service (QoS) for the DNN workloads. In the final part of the dissertation, we propose a method to protect the QoS of DNNs under collocation based on workload latency prediction and resource partition.

In the remaining part of this chapter, we will provide a more detailed introduction on each of the research questions and the proposed solution.

# 1.1 Improving Compute-in-Cache DNN Accelerator with Model Compression

Neural Cache (Eckert et al., 2018), is one example of demonstrating the in-memory processing techniques for DNN inference. Neural Cache utilizes the SRAM arrays of last level cache of general purpose CPU and turn them into massively parallel computing units. The key idea is to map the data in a transposed way in the SRAM arrays, and then performing bit-serial operations on all the bit-lines in the SRAM arrays in parallel. The bit-serial operations are implemented with in-array dual-row simultaneous sensing and extra logic at the bit-line peripherals. Data on all the bit-lines can be processed in parallel, so the entire cache can be turned into a vector processor. In Convolutional Neural Networks (CNN), there are a massive number of Multiply-Accumulate (MAC) operations that can be parallelized, and they are mapped to the more than one million bit-lines on a 35 MB last-level cache. Thus the CNN inference is accelerated by the high throughput and the convolution specific data reuse strategy. Compared to other custom accelerators, the above solution is based on cache in general purpose processors, and the cache can still improve the performance of many other applications when not functioning as a CNN accelerator.

However, previous works have not explored the opportunity to leverage two important model compression techniques in CNN. First, the weight pruning technique for DNN can reduce the number of weights and thus the computation involving the pruned weights can be left out (Han et al., 2015; Yu et al., 2017). But the existing Neural Cache architecture is unable to skip such computation. This is because with the individually pruned weights scattered in location, the vector processor architecture cannot skip computation for a pruned weight when there are unpruned weights being processed at the same time. Second, lowprecision values in DNN can also reduce computation time (Rastegari et al., 2016; Zhou et al., 2016; Zhu et al., 2016). Although the bit-serial algorithms can naturally take advantage of the low-precision formats, it is observed that bit-serial multiply-accumulate is inefficient when weights are ultra-low precision such as ternary or binary.

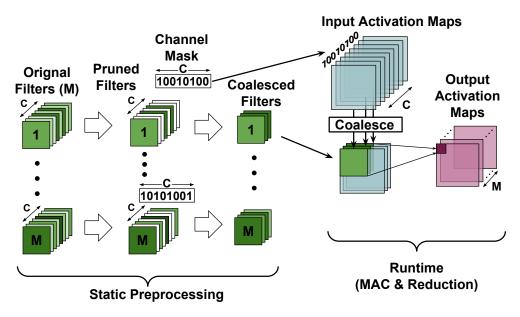

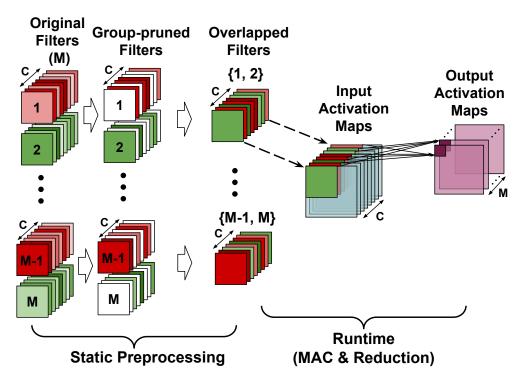

In the first part of the dissertation (Chapter 3), we present the solutions for accelerating DNNs with sparsity and low-precision values with in-SRAM bit-serial computation. For leveraging the data sparsity, the dissertation proposes two novel hardware/software co-design techniques. The first technique proposed is to create dense computation amenable for vector processors, by pruning the model by filter channels and then coalescing the non-zero filter channels. All the weights in a filter channel are mapped to one bit-line, so an entirely pruned filter channel may spare one processing unit. As coalescing the channels may complicate the input loading process, the dissertation proposes a second technique, which custom prunes the model so that several pruned filters can overlap with each other without location-conflicted non-zero values. Overall the above techniques skip the computation as well as data movement on the pruned weights, so as to improve the performance. For low-precision values, the dissertation redesign the process of multiply-accumulate for ternary/binary weights to combine the multiplication and accumulation in fewer cycles using logical operations.

The proposed sparsity-aware architecture achieves a  $17.7 \times /3.7 \times$  speedup over server class CPU/GPU, and a 1.6× speedup compared to the relevant in-cache accelerator, with 2% area overhead each processor die, and no loss on top-1 accuracy for AlexNet. With a relaxed accuracy limit, the tunable architecture with data sparsity and low-precision values achieves higher speedups. This piece of work is published in Wang et al. (2019b).

# 1.2 Reconfigurable In-Memory Computing for DNN Acceleration

Reconfigurability of hardware is a desirable feature that amortizes the fabrication cost as reconfigurable hardware can usually be reused for a wide variety of applications efficiently. The in-cache DNN accelerator described in the previous chapter does not satisfy the reconfigurability as the hardware architecture of the cache is fixed.

In searching for the potential possibility of a reconfigurable in-memory DNN accelerator, a promising choice of the base hardware platform is FPGA. FPGAs have been widely deployed as domain-specific computation device (AWS; Caulfield et al., 2016), and they are known for their flexibility and reconfigurability.

The basic structure of FPGA hardware consists of several different types of building blocks serving different functions, including lookup tables (LUT) for building customized logic, block RAMs (BRAM) to store data, and digital logic processing (DSP) blocks for efficient arithmetic operations. We observe that state-of-the-art FPGA architectures have high capacity on-chip BRAMs, which, although are not conventionally used to form computation logic, provides opportunities for building compute-capable memory on FPGAs. For example, the largest monolithic Intel Stratix 10 device has 11,721 BRAMs that collectively provide 229 Mb of distributed on-chip memory (Int, 2019). Future generations of FPGA devices are also expected to have higher density of on-chip BRAMs to satisfy the ever increasing demands of memory-intensive datacenter workloads (Putnam et al., 2014).

If we apply the similar idea of bit-serial in-SRAM computing to the BRAM blocks, they can be turned into a total of about 1.5 million bit-serial compute units. Such computecapable BRAM blocks would become an important computing resource in addition to the existing LUT and DSP blocks. In FPGAs, the gains of compute-capable BRAMs are compelling for these main reasons: (1) The large number of distinct memory blocks in an FPGA enables a significantly higher degree of parallelism. The BRAMs in the largest monolithic Intel Stratix 10 FPGA can be re-purposed to over 1.5 million bit-serial SIMD compute lanes when enhanced with compute-capable peripherals. When not computing, BRAMs can still function as normal memory units. (2) The in-fabric distributed nature of the FPGA on-chip memory enables tighter integration of the compute-capable memories with the rest of the design logic. For operations that cannot be computed in-memory, the data from a computecapable last-level cache in a CPU would still need to go through the different levels of the memory hierarchy and the fixed processor pipeline to reach the compute units, which is not the case for compute-capable FPGA BRAMs. (3) Performing the compute in BRAMs eliminates the data movement between memory and compute units which reduces the competition over the fabric's precious routing resources. This can potentially alleviate congestion and increase the routability of FPGA designs.

In the second part of the dissertation (Chapter 4), we demonstrate how to make modifications to the BRAMs to support the in-memory computing, tackling the challenge that the interface of BRAM to FPGA is different from the SRAM array's interface to the CPU cache. We present designs for the block-floating-point arithmetic with compute-capable BRAMs, dot-product acceleration modules built from an integration of compute-capable BRAMs and LUTs. We also show how to perform architectural customization when the DNN model varies.

In contrast to prior in-SRAM computing architectures which use fixed hardware, the proposed system fully utilizes the reconfigurability of FPGAs. The enhanced FPGA architecture can be reconfigured optimally for different DNN models, with the compute-capable BRAM being flexibly used as computing units or data storage. Further, the control structures are reconfigurable to support both fixed-point and block-floating-point numerical precision.

Our evaluation shows that enhancing a modern Stratix 10 FPGA architecture with compute-capable BRAMs can result in  $1.6 \times$  and  $2.3 \times$  increase in the device's peak multiplyaccumulate (MAC) throughput for 8-bit integer and block floating-point precision, respectively. These gains are achieved with no change to the modes of operation or routing interface of existing BRAMs and at a minimal cost of 1.8% increase in the FPGA die size. We then evaluate the performance gains of our proposed architectural modification when accelerating a variety of real-time DNN workloads. Compared to Brainwave (Fowers et al., 2018), a state-of-the-art DNN accelerator on FPGA, the proposed architecture achieves an average  $1.25\times$  and  $3\times$  speedup for 8-bit integer and block floating-point numbers. In addition, the proposed accelerator can achieve an order of magnitude higher performance compared to a same-generation GPU. This piece of work is published in Wang et al. (2021b).

## **1.3** Efficient Cache Data Compression

During DNN computation, there can be a lot of duplicated values either due to the large number of zeros after model compression or because of quantization to a small number of bits leading to a small set of possible data values. In either case, an efficient way for data compression is crucial to improve the performance of DNNs running on CPUs.

Cache compression is an architectural optimization topic that has been extensively studied. In general, cache compression leverages the data redundancy within the cache, and stores the data in relatively fewer bits to increase the effective cache capacity. More cache lines can be cached and kept on chip with compression. The cache hit rate and the overall program performance, especially for the programs with a large working set, improve as a result. Cache compression also avoids adding more data arrays to the cache which is more energy-consuming.

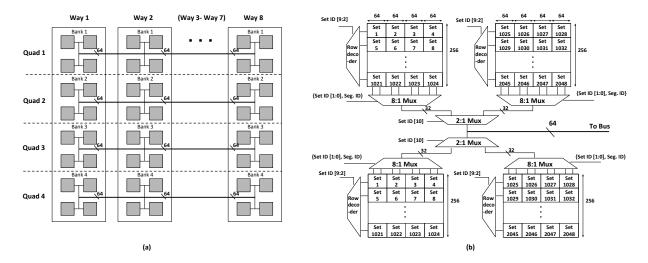

Recently, compression methods that leverage the similarities across cache lines have been proposed (Tian et al., 2014; Ghasemazar et al., 2020). It is observed that duplicated or highly similar cache lines exist in the last level cache, leading to compressing opportunities where the duplicated part can be stored with one data copy and multiple pointers for the distinct tags. Such inter-cache-line compression exploits the data redundancies at a wider range across all the cache lines and therefore provide additional opportunity for compression beyond the data similarity within a cache line. However, these works treat the cache data array as a scratchpad and thus indexing the data is complicated. This causes delays in the decompression process, which is on the critical path of the memory read instructions in the case of cache hit. We discover that the above problem can be alleviated by storing the compressed data in segments that are conveniently indexed, with a case study on Intel Xeon last-level cache.

We also observe the cache organization in today's processors for more efficient compression. More specifically, in the last-level cache for a multi-core Xeon E5 processor (Huang et al., 2013), each core is connected to a cache slice. Within each slice, the SRAM arrays are arranged in columns, where each column has 16 8kB SRAM arrays and each column corresponds to one way in the set-associative cache. The 16 arrays in a way column are further partitioned into 4 banks, and the arrays within a bank are connected via an H-tree interconnect. Because the 4 banks within a way column all use separate data buses, we may use separate pointers and thus the deduplication compression happens independently for the 4 quads in a cache line, reaching a balance between high compression ratio and fast decompression.

The cache line similarity-based compression methods require comparison of new incoming cache lines with the existing ones to find similar pairs for compression. In a conventional architecture, it is necessary to read out the data in existing cache lines and transfer them to the comparison logic. We observe that a recent work on in-cache computation, Compute Caches (Aga et al., 2017), provides the ability to do data comparison in the data arrays in last-level cache efficiently. In Compute Caches, each SRAM array is equipped with an additional row decoder to activate two wordlines simultaneously. Then the differential senseamplifiers at each bitline pair are modified to sense both bitline and bitline-bar separately, effectively calculating the logical AND and NOR of the two activated bitcells on that bitline. Other logical operations, including comparison, can be supported by a few additional logic gates, and making all the sense-amplifiers work concurrently. For instance, to support XOR operation, a NOR gate is added, taking the results of bit-line and bit-line complement (i.e., AND and NOR results) as inputs. To check whether two words are identical, first XOR is performed on the two data words, and then the XOR results go through a wired-NOR logic, to generate a binary matching result.

With the above in-SRAM comparison operation, the in-array data comparison directly works on the data stored at two word-lines in an SRAM array, without the need of transferring data out of the array. Such word-line level comparison can be done at multiple SRAM arrays in parallel. By comparing the cache line data in arrays, the comparison throughput can be improved thanks to the high parallelism. Further, while reading out a massive amount of data for comparison consumes energy in the data interconnects, the in-array comparison eliminates such energy consumption. We apply this idea and propose a cache compression design with low decompression latency (Chapter 5). We evaluate the proposed compression method on the SPEC2006 benchmarks. We achieve a  $2.05 \times$  compression ratio, and 4.73% of speedup on average, compared to a conventional L3 cache without compression. This piece of work is published in Wang et al. (2021a).

## 1.4 Satisfying QoS of Collocated DNN Service

Now we will consider how to improve the DNN performance from a system perspective in the context of datacenters. In modern datacenters, it is crucial to provide a consistent Quality-of-Service (QoS) to the clients that meets the QoS targets set by the clients. The common QoS metrics are latency and/or throughput, which depend on the nature of the applications.

DNN inference is an important type of service provided by the datacenter servers recently (Hauswald et al., 2015). As DNN is widely used in artificial intelligence applications, a guaranteed QoS for DNN inference is a highly desirable feature in the datacenters, which further contributes to the guaranteed QoS of end-to-end artificial intelligence applications.

Even though many accelerators or customized hardware have been built for the DNN

workloads, the CPU-based servers are still an important type of computing resource for machine learning inference. According to a report on machine learning inference at Facebook's datacenters (Hazelwood et al., 2018), the majority of inference services are run on the single-socket or dual-socket CPU servers, for a wide range of applications such as speech recognition, personalized recommendation, and face recognition. Running the inference on CPUs instead of dedicated accelerators can avoid the overhead of dedicated programming and compilation efforts, and also is favorable for a homogeneous datacenter environment for ease of management. In a datacenter with both CPU and GPU resources, it is more efficient to perform the training tasks on GPUs and assign the inference tasks to CPUs (Hazelwood et al., 2018).

With the DNN inference running on the CPU servers, it is a natural idea to collocate such DNN services with other services on the same multi-core CPU server to increase the overall server resource utilization and improve the request processing throughput. Another scenario where the task collocation would happen is when the request rate is at a high level and the datacenter is designed to avoid over-provisioning. Further, with the widely used software frameworks that can express different machine learning models, multiple machine learning services of different types can be run at the same server node, and thus the concurrent execution of different machine learning applications can also happen.

The workload collocation can have a negative impact on the performance of an individual workload and cause the violation of QoS. This is mainly caused by the contention of resources such as the processor cores, the memory capacity and the memory bandwidth, as well as the interference effects such as the thrashing of the cache contents. Although various previous works have studied the problem of contention caused by collocation of generic workloads on CPU-based servers, none of them directly targets the specific domain of DNN inference services.

In the final part of the dissertation (Chapter 6), we propose a mechanism to protect the QoS of DNN workloads under collocation. We observe that there is determinism in the

computation of DNNs and therefore design a latency predictor. At runtime we generate a partition of different types of server resources across the latency-critical DNN workloads and other best-effort workloads, so that the predicted performance of the DNN workload meets the QoS target. When applied, the proposed approach improves the latency of DNN workloads by 85% and 26% when collocated with core and memory-bandwidth thrashing microbenchmarks, and by 11% when collocated with best-effort DNN workloads.

## CHAPTER 2

# **Background and Related Works**

This chapter describes the background knowledge and related works for the rest of the dissertation. We begin with a general description of the structure and computation pattern of common DNNs (Section 2.1), followed by an introduction to the in-memory acceleration of DNNs (Section 2.2), including an in-SRAM computing example in detail. Then we discuss two important types of algorithmic simplification opportunities in the DNN computation, data sparsity and quantization, and how the hardware can take advantage of them (Section 2.3). After that, we introduce the FPGA architecture and show how DNNs can be accelerated with FPGAs (Section 2.4). Finally, we provide background regarding topics of DNN performance on CPU, including the cache data compression techniques and how the DNN workloads achieve QoS targets (Section 2.5).

## 2.1 The Computation Pattern of DNNs

DNN is a general term for one family of machine learning models, which has many layers stacked together, and the output of one layer becomes the input of the next layer. One DNN layer usually includes a linear transformation on the input, and then is followed by a nonlinear function. There are trainable parameters in the DNN layers, which are also called weights. Usually, the linear transformation step involves a large number of weights and dominates the computation in inference. The common DNN models include Convolutional Neural Networks (CNN), Recurrent Neural Networks (RNN), and Multi-Layer Perceptron (MLP).

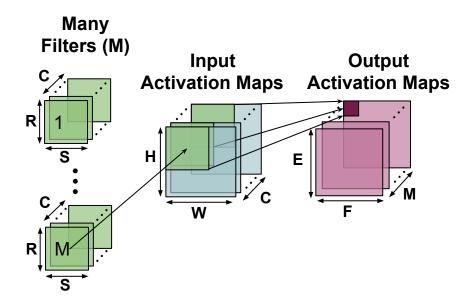

Convolutional Neural Network (CNN) is a machine learning method that takes a 3D-array as input, performs convolution and non-linear functions on the array iteratively, and extracts the array information for further tasks such as classification. A typical CNN consists of many convolutional layers, a few pooling and fully connected layers, and non-linear functions between the layers. The overall procedure of a convolutional layer is shown in Figure 2.1. A convolutional layer takes in C channels of 2D activation maps as input, with activation of each channel having H pixels in height and W pixels in width. A batch of in total M 3Dfilters are the network parameters of the layer. Each 3D-filter has C channels, each channel with  $R \times S$  parameters called weights, where R is the filter height and S is the filter width. At convolution, the C channels of  $R \times S$  filters are overlaid on the C channels of inputs. The  $R \times S \times C$  input pixels are element-wise multiplied with their corresponding filter weights, and then the products are summed up across all C channels to produce one output pixel as shown in Figure 2.1. The  $R \times S$  filter slides over the  $H \times W$ -sized input activation with stride U, generating  $E \times F$  output pixels per 3D filter. Therefore the M filters create a total of  $M \times E \times F$  output pixels for one convolutional layer and these pixels become inputs of the following convolutional layer. It has been shown that among the end-to-end CNN computation, most (90%) of the time is spent on convolutional layers (Chen et al., 2016).

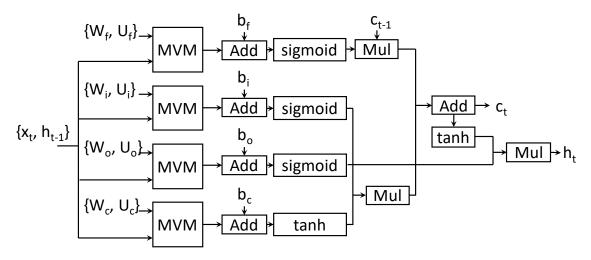

Recurrent Neural Networks (RNN), is a type of DNN that is widely used in AI applications including machine translation and speech recognition. Many types of RNNs have been designed, including vanilla RNN, LSTM and GRU, with the main difference in the dependency of vectors and activation function used. RNNs have one shared major component in inference computation - the matrix-vector multiplication (MVM). For example, Figure 2.2 shows the algorithmic structure of a LSTM layer. The four MVM blocks consume the majority of the compute time. Note that there is no data dependency among the four MVM blocks, thus they can be combined into a larger MVM. This property holds for many different

Figure 2.1: Computation of a Convolutional Layer.

types of RNN. In such a combined MVM, the inputs are a vector with C elements and a weight matrix of size  $R \times C$ . The output is a vector of R elements.

In MLP, the linear transformation is matrix-vector multiplication similar to the RNN. The main difference is that the RNN takes a sequence as an input while MLP has a single input vector.

In a DNN application, there are usually two computation stages, training and inference. The training stage generates the best weights for the given task, and the inference stage provides a prediction for the input with the already trained weights. Training is a onetime cost before the model deployment while inference usually is run many more times than training. In this dissertation, we mostly consider the inference stage as the target application.

## 2.2 In-Memory Computing for DNN

This section mainly discusses the in-memory computing techniques to accelerate DNNs. In fact, the DNN accelerators is a much wider research area than the in-memory DNN accelerations and there are numerous prior works (Chen et al., 2016, 2014; Du et al., 2015;

Figure 2.2: Overview of the algorithm for a LSTM layer. The computation bottleneck is in the Matrix Vector Multiplication (MVM).

Deng et al., 2019; Zhang et al., 2018; Hegde et al., 2018; Jouppi et al., 2017). TPU (Jouppi et al., 2017) is a typical DNN accelerator work that proposes a high-throughput systolic matrix multiply unit. Eyeriss (Chen et al., 2016) is another typical work, which explores different data flow options for CNN acceleration and reduces data-movement by maximizing weight reuse. Discussing all the DNN accelerators is beyond the scope of this work and Sze et al. (2020) provides a summary on this topic.

#### 2.2.1 Overview of In-Memory DNN Acceleration

Many recent works have proposed to accelerate DNN applications with in-memory processing (Li et al., 2017; Seshadri et al., 2017; Li et al., 2018; Imani et al., 2019; Eckert et al., 2018; Ankit et al., 2019; Ji et al., 2019; Shafiee et al., 2016; Chi et al., 2016; Song et al., 2017; Kim et al., 2016). In-memory computing is a good fit for accelerating DNNs for multiple reasons. First, DNN applications usually have a high degree of parallelism as the computation involves large matrices and vectors. The parallelism can be well exploited by the vector-processor style architecture of in-memory processing. Second, in the inference stage of DNN, the model parameters are usually fixed and thus can be pinned to the memory, while the inputs are being streamed in. This is especially a desired behavior of in-memory processing as one

of the operators (weights) is stationary and only the movement of the inputs needs to be orchestrated.

The in-memory DNN accelerators can utilize a range of different types of memory cells, including DRAM, SRAM, and non-volatile memory such as ReRAM. ReRAM-based inmemory DNN accelerators (Shafiee et al., 2016; Chi et al., 2016) use the analog circuit property of the ReRAM memory cells, where the model weights are programmed as memristance values into the cells. Then the inputs are converted into analog voltage values and applied to the ReRAM cells, leading to a generated current that represents the value of a MAC operation. There are other ReRAM-based in-memory computing architectures that stress flexibility with reconfigurable routing architecture (Ji et al., 2019), and support floating point arithmetic with digital in-memory computation (Imani et al., 2019). Overall, computing-in-ReRAM can achieve high compute density for MAC operations. But ReRAM devices are prone to operational variations which might affect its reliability, and the analog/digital converters also take up extra area and energy.

Many DRAM-based in-memory computing DNN accelerators (Kim et al., 2016; Gao et al., 2017) utilizes 3D-stacked memories, where the logic layer and the memory layers are vertically stacked to enable a high data movement bandwidth between these layers. The DNN computation is mapped to the above architecture with the consideration of reducing the data movements within the logic layer. Another line of work (Li et al., 2018) attaches ALU to each bitline in DRAM array for in-memory processing. An example of in-DRAM computing architecture for DNNs that modifies the DRAM array structure is DRISA (Li et al., 2017). The underlying technique is to activate three rows in a DRAM array and then performing bit-wise logic operation by exploiting the changes in capacitor charges. On the architectural level, DRISA builds a vector processor by activating multiple DRAM arrays simultaneously. Overall DRAM-based in-memory computing is a popular design due to the widespread use of DRAM as the main memory device.

The in-SRAM acceleration of DNNs can be based on either digital or analog approaches.

In the digital approach, elementwise logical operations are performed on the data of two rows in the same SRAM array, by activating two wordlines and sensing the currents on each bitline. We will discuss extensively one example of in-SRAM DNN accelerator in Section 2.2.2. The in-SRAM analog computing approach (Valavi et al., 2018; Srivastava et al., 2018) uses a similar approach as used in ReRAMs, where the weights are stored in memory cells and inputs are sent to all wordlines for MAC operations. Overall, in-SRAM computing has faster speed and lower energy consumption for each operation compared to other memory cell types, while its larger cell size makes the total capacity of SRAM smaller, and thus it is more complicated to handle large datasets.

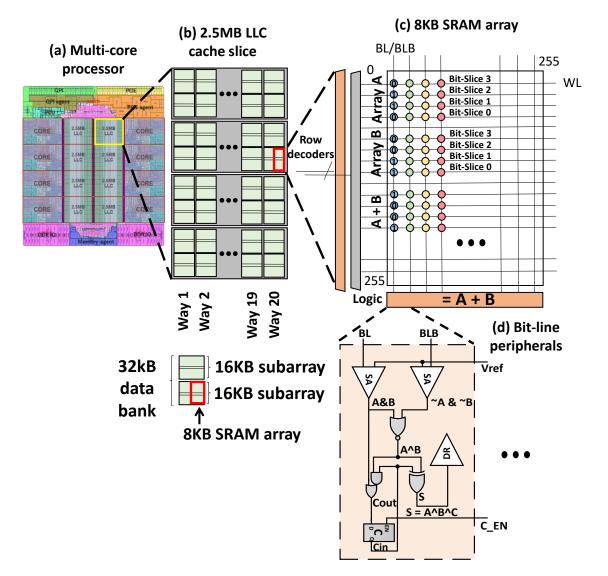

#### 2.2.2 In-SRAM Bit-Serial Computing with CPU Cache

Neural Cache (Eckert et al., 2018) is an architecture which repurposes the last level cache in general purpose processors to perform massively parallel in-SRAM computing for neural networks. Figure 2.3 shows the overall architecture of Neural Cache. The building block of Neural Cache is bitline computing enabled by SRAM array peripherals. In bitline computing, two wordlines of an SRAM array are activated at the same time and by sensing the shared bitline pairs (existing in Xeon LLC), logical operations (and and nor) on the cell data of the two wordlines can be performed (Aga et al., 2017; Jeloka et al., 2016).

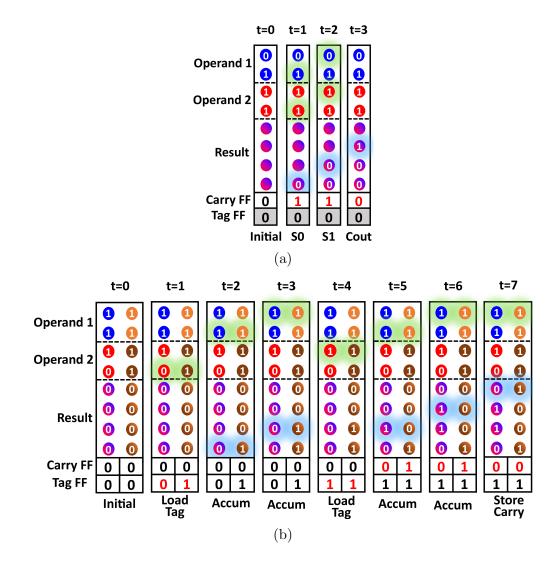

To perform arithmetic operations such as addition and multiplication, a bit-serial architecture is utilized (Figure 2.3 (c)): data are mapped to a transposed layout where different bitlines hold data from different elements in the operand vector. Each *n*-bit element is stored across *n* wordlines, and thus each wordline holds one *bit-slice* from all the vector elements. The bits in each bit-slice are of the same bit position. The arithmetic operation is done bit-slice by bit-slice – for example, to compute A + B, bit-slice 0 of vector *A* and bit-slice 0 of vector *B* are first activated and added by the peripheral logic (generating sum and carry), then the same operation is done to bit-slice 1, 2, ..., n - 1 of the two operand vectors (carry taken from the previous bit-slice step). For *n*-bit integer addition, bit-serial computation

Figure 2.3: Neural Cache Architecture Overview.

takes *n* cycles; similarly, *n*-bit integer multiplication can be done in  $n^2 + 3n - 2$  cycles. A step-by-step illustration of the bit-serial addition and multiplication are in Figure 2.4. The weights and activations are linearly quantized to 8-bit integers for bit-serial computation.

In the above architecture, 256 bitlines in one 8 kB SRAM array are turned into 256 ALUs in a vector unit. Xeon's 35 MB LLC can accommodate 4480 such 8 kB arrays. Thus up to 1,146,880 elements can be processed in parallel, while operating at a frequency of 2.5 GHz at runtime. By repurposing memory arrays, the above throughput is achieved for a cost of 7.5% area increase of an SRAM array and less than 2% area overhead for the entire Xeon

Figure 2.4: Steps for different in-SRAM bit-serial (a) addition, (b) multiplication operations. Green and blue shades correspond to read and write activated wordlines at each time step. The bits from a single data word are marked with the same color.

Figure 2.5: Neural Cache Data Mapping of a 2.5MB Slice.

processor die. Note, while a 35 MB LLC cache access from core takes 20-30 ns, the smaller 8 kB SRAM arrays can themselves operate at a frequency up to 4 GHz (Huang et al., 2013; Chen et al., 2013).

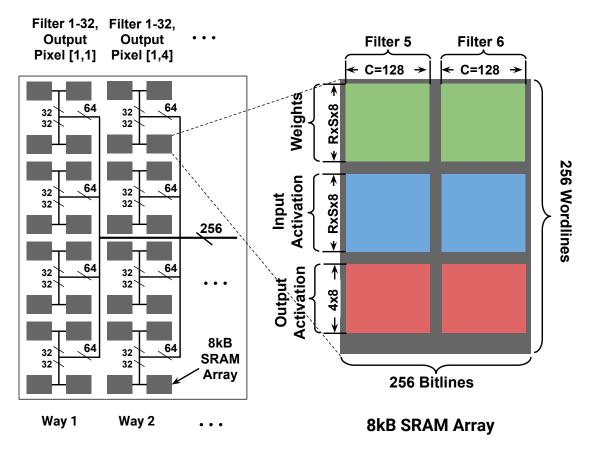

Neural Cache uses the cache structure of 2.5 MB Xeon LLC slice (Huang et al., 2013; Chen et al., 2013; Bowhill et al., 2016) for demonstrating its idea. In such a Xeon processor, multiple slices on a processor die are connected by a ring. Each slice has 20 columns which serve as 20 different ways of the set-associative LLC. Each way consists of 4 banks and each bank has 4 SRAM arrays of 8 kB. The 20 ways are connected by a 256-bit bus within the cache slice. The ways and banks in a slice are shown in the left hand side of Figure 2.5.

Figure 2.5 shows a typical data mapping scheme of one convolutional layer. In each  $256 \times 256$  array, the filter weights are stored in  $R \times S \times 8$  wordlines, and the input activations to be multiplied with weights are loaded to another  $R \times S \times 8$  wordlines; each bitline corresponds

to one input channel. The M filters span multiple arrays in the same or neighboring ways. One way of each slice is reserved for storing the outputs of the previous layer and another way reserved for system background processes. The other 18 ways hold the replicated weights for in-cache computation.

The in-cache convolution is performed in the five successive stages as described below:

1. Weight Loading: At the start of each layer, the filter weights are loaded from DRAM to the cache. Mapping a 2D filter to each bitline does not result in full utilization of all bit-serial compute units. Thus filters are replicated throughout all the ways and then slices to exploit parallelism. The inter-slice and intra-slice interconnect structures allow low-cost replication of weights using broadcasts. The weights from all the M filters are broadcasted to all the slices via the inter-slice ring, and then to all the ways via the intra-slice bus. After filter replication, the output pixels that still cannot be computed in parallel are computed in serial.

2. Input Loading: Each slice computes a tile (subset) of  $E \times F$  output pixel positions across all M channels. The pixel positions with neighboring heights and widths are mapped to the same slice. Therefore, the output activations generated in one slice can be used as the input activation of the next layer. In input loading, the input activations are broadcasted from the reserved way to all the compute ways via the intra-slice bus. A small portion of the activations (at the border of tiles) are transferred through the inter-slice ring.

3. MAC (Multiply-ACcumulation): After data loading, at each array, the  $R \times S$  weights multiply with the  $R \times S$  inputs sequentially; after each multiplication, the product is accumulated into the partial sum in the reserved wordlines in the array.

4. Reduction: To sum up all the input channels of each filter, the partial sums at different bitlines are added up in the reduction stage. In reduction, at each array, partial sums of half the channels to be reduced are copied to another set of wordlines and aligned channel-wise with the other half of channels. Then the second half of partial sums are added into the first half. The copying and addition are called one round of reduction; the reduction rounds are

conducted iteratively until the final reduction result is calculated.

5. Output Transfer: After reduction, the output activation maps at the compute arrays are transferred to the reserved array in the stage of output transfer. Then the inputs at a different height or width are loaded in, and the MAC, reduction, and output transfer repeat.

## 2.3 Sparsity and Quantization in DNNs

DNNs require a large amount of computation performed, as it usually consists of many layers and a large number of total weight parameters to obtain the high accuracy. Take CNN as example, the number of MAC operations required per convolutional layer is proportional to  $R \times S \times C \times E \times F \times M$ . This leads to efforts to reduce the total computation requirements by algorithmic changes to DNN inference itself.

Two types of algorithmic changes have been proposed in literature to reduce the computation requirements: 1) model pruning to reduce total number of weight parameters (Han et al., 2015); 2) represent the weight and/or feature maps with low-precision data formats (Rastegari et al., 2016; Zhu et al., 2016; Zhou et al., 2016).

In this section, we discuss two opportunities in DNN computation that lead to a reduction in total computation requirements, data sparsity and quantization, followed by a survey of hardware designs exploiting such opportunities.

#### 2.3.1 Sparsity in DNNs

Data sparsity in DNNs especially means the zero values in the weight or feature maps. These zero values do not contribute to the result of MAC operation, so theoretically any MAC operations involving these zero values can be skipped.

**Sparsity in weights**: In a trained DNN model, the chance that a weight has exact zero value is low. The majority of the weight sparsity comes from an artificial optimization phase to increase the zero values in weights, called weight pruning.