## Energy-Efficient Circuits and Systems for Powering, Sensing and Actuating the Motions in Internet of Things

by

Yimai Peng

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2022

**Doctoral Committee:**

Professor Dennis Sylvester, Chair Professor David Blaauw Professor Khalil Najafi Professor Henry Sodano Yimai Peng

pyimai@umich.edu

ORCID iD: 0000-0001-9860-0175

© Yimai Peng 2022

## Dedication

To my wife Xingye, my parents Changcao Peng and Xiaolan Zhao, my advisor Dennis Sylvester, and Professor David Blaauw for all your support and care.

# Acknowledgements

The authors would like to thank Robert Gordenker and Professor Khalil Najafi at University of Michigan, for their support and contribution to my research projects.

## **Table of Contents**

| Dedication                                                               | ii   |

|--------------------------------------------------------------------------|------|

| Acknowledgements                                                         | iii  |

| List of Tables                                                           | viii |

| List of Figures                                                          | ix   |

| Abstract                                                                 | xiii |

| Chapter 1 Introduction                                                   | 1    |

| 1.1 Powering Miniaturized IoT Sensor Nodes with Motions                  | 2    |

| 1.2 Sensing Motions with Ultra-Low Power and High Resolution             | 4    |

| 1.3 Creating Motions with Electrostatic Actuation by Nano-Watt Circuit   | 5    |

| 1.4 Dissertation Outline                                                 | 6    |

| Chapter 2 An Efficient Piezoelectric Energy Harvesting Interface Circuit | 9    |

| 2.1 Introduction                                                         | 9    |

| 2.2 Related Works on the PEH Interface Circuit                           | 11   |

| 2.2.1 Modeling of Piezoelectric Transducers                              |      |

| 2.2.2 Baseline Interface: Full-Bridge Rectifier                          |      |

| 2.2.3 Prior State of the Art: Bias-Flip Rectifiers                       | 14   |

| 2.3 Fundamentals of the Sense-and-Set Technique                          | 16   |

| 2.3.1 Sense Phase                                                        |      |

| 2.3.2 Set Phase                                                          |      |

| 2.3.3 Flipping Phase                                                     |      |

| 2.3.4 Calibration Phase                                                  |      |

| 2.4 Circuit Implementation of Sense-and-Set                                                                   |               |

|---------------------------------------------------------------------------------------------------------------|---------------|

| 2.4.1 Inductor-Sharing Circuit                                                                                |               |

| 2.4.2 Clock Generator                                                                                         |               |

| 2.4.3 Pulse Generation and the Clock Counter                                                                  |               |

| 2.4.4 Comparators                                                                                             |               |

| 2.4.5 Switch Controller and Switch Drivers                                                                    |               |

| 2.5 Measurement Results and Analysis                                                                          |               |

| 2.6 Conclusion                                                                                                |               |

| Chapter 3 An Ultra-Low-Power Triaxial MEMS Accelerometer with High<br>and Electrostatic Mismatch Compensation |               |

| 3.1 Introduction                                                                                              |               |

| 3.2 Proposed High-Voltage MEMS Biasing with Electrostatic Mismatch Cor                                        | npensation 40 |

| 3.2.1 Fundamentals of the MEMS Capacitive Accelerometer                                                       |               |

| 3.2.2 Motivation for High-Voltage MEMS Biasing                                                                |               |

| 3.2.3 Electrostatic Feedback of the High-Voltage Biasing                                                      |               |

| 3.2.4 Electrostatic Mismatch Compensation                                                                     |               |

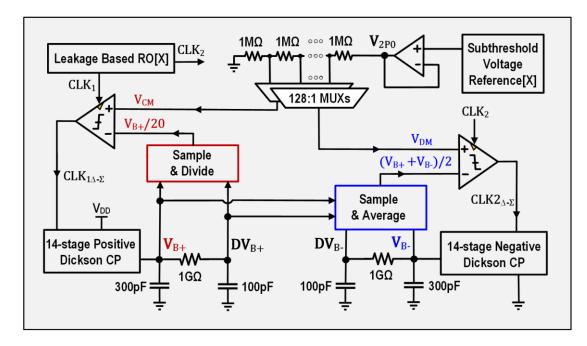

| 3.3 Implementation of the High-Voltage Companion (HVC) Chip                                                   |               |

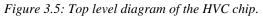

| 3.3.1 High-Precision Bias Voltage Generation for EMC                                                          |               |

| 3.3.2 High Voltage Sampling Circuits for $V_{B+}$ and $V_{B-}$                                                |               |

| 3.3.3 Electrostatic Pull-In Detection and Protection                                                          |               |

| 3.4 Implementation of the MEMS and CMOS Analog Front End Chip                                                 |               |

| 3.5 Measurement Results and Analysis                                                                          | 59            |

| 3.5.1 Accelerometer Performance Measurements                                                                  | 59            |

| 3.5.2 EMC measurement with process variation                                                                  | 64            |

| 3.6 Conclusion                                                                                                |               |

| Chapter 4 A High-Voltage Generator and Multiplexer for Electrostatic Actuation in<br>Programmable Matter | , 66 |

|----------------------------------------------------------------------------------------------------------|------|

| 4.1 Introduction                                                                                         | . 66 |

| 4.2 Programmable Matter with Electrostatic Actuation                                                     | . 68 |

| 4.2.1 Catom Design with Electrostatic Actuation                                                          | . 68 |

| 4.2.2 The Stack: Micro-Controller inside the Catom                                                       | . 70 |

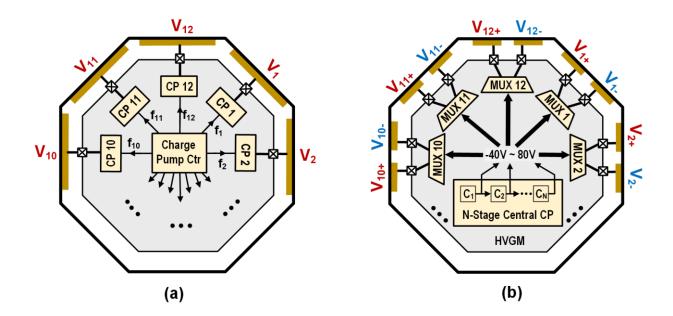

| 4.2.3 HVGM: Energy-Efficient Scheme for Capacitive Actuators                                             | . 72 |

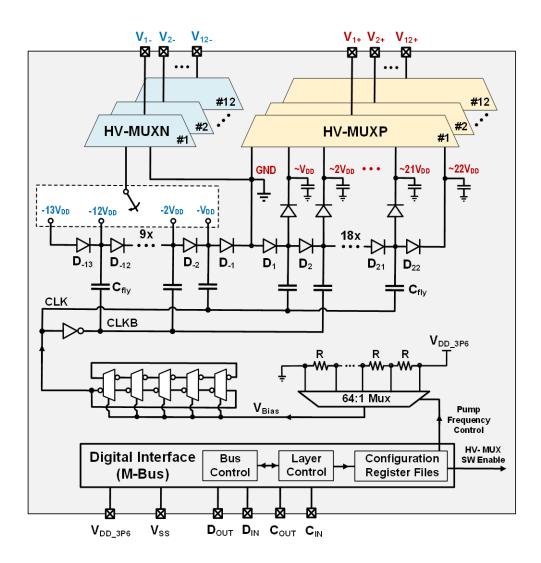

| 4.3 Circuit Implementation of HVGM                                                                       | . 74 |

| 4.3.1 Central Charge Pump                                                                                | . 74 |

| 4.3.2 HV-MUX for Positive Electrodes (HV-MUXP)                                                           | . 76 |

| 4.3.3 HV-MUX for Negative Electrodes (HV-MUXN)                                                           | . 79 |

| 4.3.4 Peripheral Circuits in HVGM                                                                        | . 80 |

| 4.4 Measurement Results and Analysis                                                                     | . 82 |

| 4.4.1 HVGM Measurement Results                                                                           | . 82 |

| 4.4.2 Stack and Catom Integration                                                                        | . 86 |

| 4.5 HVGMv2: Single-Chip μ-Controller for the Catom                                                       | . 87 |

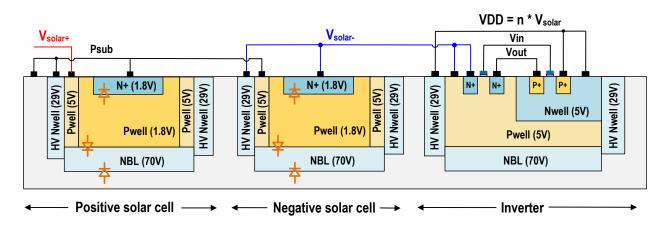

| 4.5.1 Solar Energy Harvesting and Power Management                                                       | . 89 |

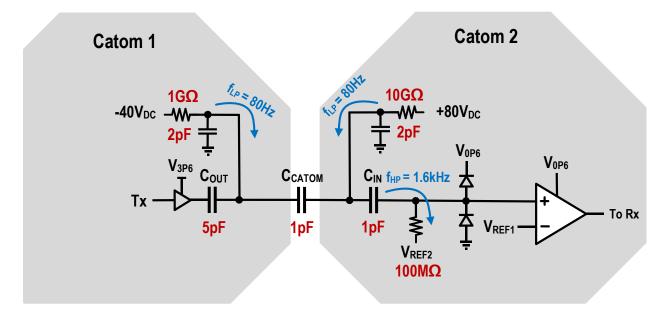

| 4.5.2 Capacitive Coupling Communication                                                                  | . 91 |

| 4.5.3 Rx, Tx and FSM Design                                                                              | . 92 |

| 4.6 Conclusion                                                                                           | . 93 |

| Chapter 5 Conclusion                                                                                     | , 95 |

| 5.1 Summary of Contribution                                                                              | . 95 |

| 5.2 Directions for Future Research                                                                       | . 96 |

| 5.2.1 Sense-and-Set Energy Harvesting                                                                    | . 96 |

| 5.2.2 High-Voltage Biasing Technique for MEMS Capacitive Accelerometers                                  | . 98 |

| 5.2.3 Hardware Design for Future Generations of Programmable Matter                                      | . 99 |

| bliography |

|------------|

|------------|

## List of Tables

| Table 2.1: Circuit Parameters of the Sense-and-Set Circuit                                              | 25 |

|---------------------------------------------------------------------------------------------------------|----|

| Table 2.2: Performance Comparison with State-of-the-Art Piezoelectric Energy Harvester         Circuit. | 35 |

| Table 3.1: Performance Summary of the proposed MEMS accelerometer and comparison with prior works.      |    |

| Table 4.1: Performance Summary of HVGM and comparison with prior works                                  | 85 |

# List of Figures

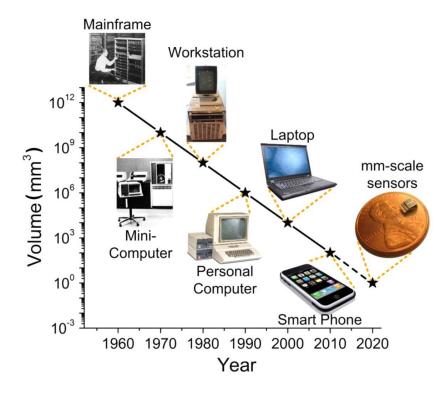

| Figure 1.1: Bell's Law predicts continuous scaling of micro-size computing systems [2]2                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

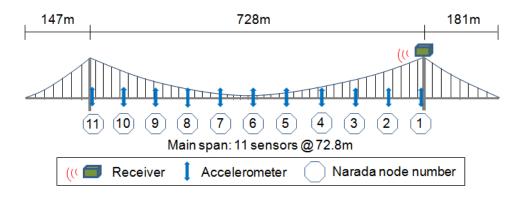

| Figure 1.2: The deployment of the wireless sensors on the bridge (top) and the measured vibration acceleration waveform with its power spectrum density (bottom) [9]                                                                                                                                                                                                                                                                                                  |

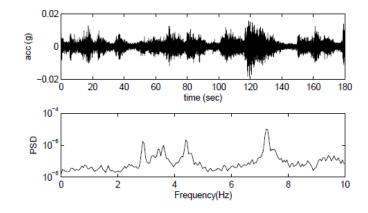

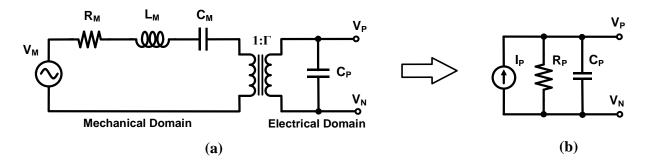

| Figure 2.1: Modeling of piezoelectric transducer. (a) complete model with electromechanical coupling and (b) simplified model on resonant frequency                                                                                                                                                                                                                                                                                                                   |

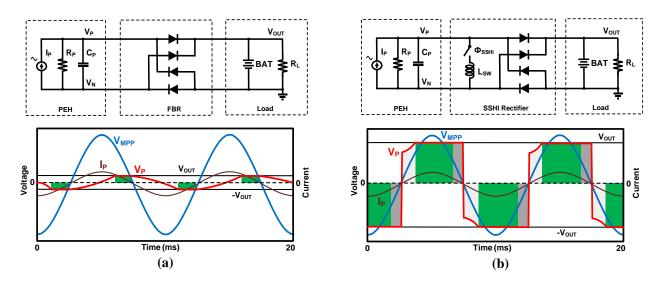

| Figure 2.2: Schematic and waveform for piezoelectric energy harvesting through (a) FBR and (b) SSHI rectifier                                                                                                                                                                                                                                                                                                                                                         |

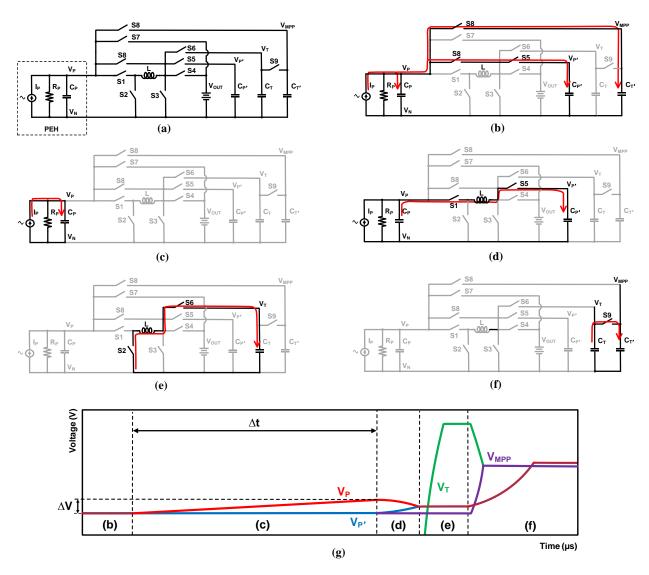

| Figure 2.3: (a) SaS core circuit where $C_P=C_{P'}$ , $C_T=C_{T'}$ , (b) set initial voltage $V_P$ on $C_P$ , $C_{P'}$ and $C_{T'}$ , (c) leave the PEH in open-circuit and let $I_P$ only charge $C_P$ , (d) short $C_P$ and $C_{P'}$ through an inductor until their voltages merge, (e) transfer the energy in the inductor into the smaller capacitor, (f) short $C_T$ and $C_{T'}$ to get $V_{MPP}$ , and (g) waveforms showing the voltages for important nodes |

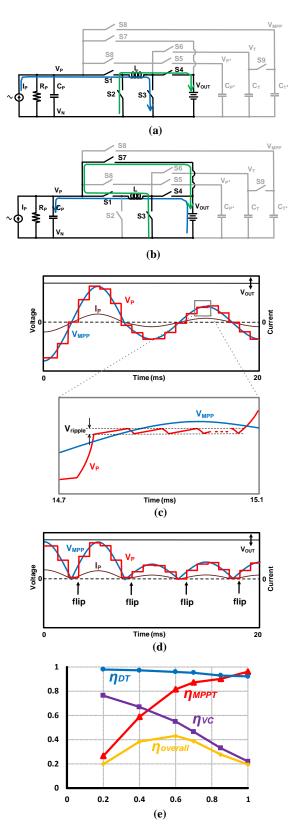

| Figure 2.4: SaS rectifier in set phase. (a) down-convert operation and (b) up-convert operation, (c) SaS waveform (without voltage flip) and its zoomed-in region, (d) SaS waveform with voltage flip, and (e) SaS efficiency with different MPPT ratios                                                                                                                                                                                                              |

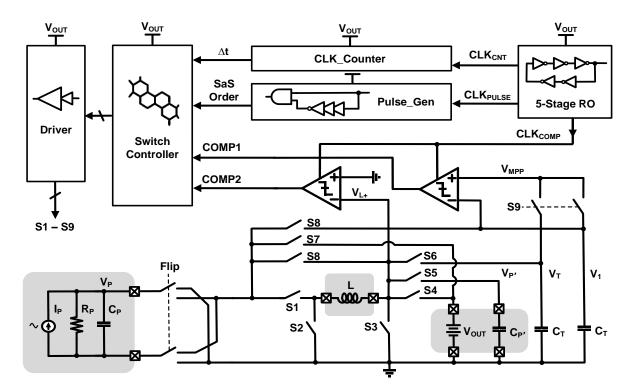

| Figure 2.5: Top-level diagram for the proposed SaS circuit (greyed area indicates components that are off-chip)                                                                                                                                                                                                                                                                                                                                                       |

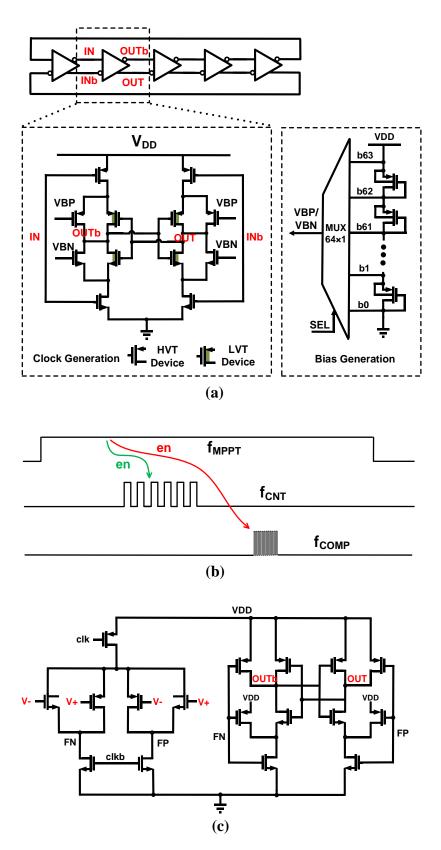

| Figure 2.6: (a) Circuit schematic of the 5-stage ring oscillator and its biasing circuit, (b) $f_{CNT}$ and $f_{CMOP}$ that run at higher frequency are awoken by $f_{MPPT}$ at a specific time, and (c) the 2-stage comparator schematic                                                                                                                                                                                                                             |

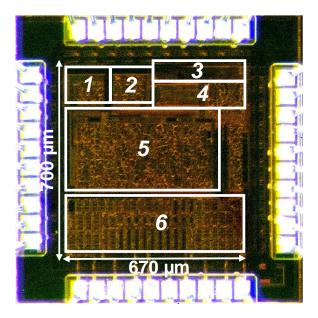

| Figure 2.7: Micrograph of the test chip fabricated in 180-nm CMOS process. The active area of the circuit is 0.47 mm <sup>2</sup> . 1: bias voltage generator; 2: ring oscillators; 3: scan chain for tuning; 4: clocked comparators; 5. Pulse generator; 6: Inductor sharing circuit                                                                                                                                                                                 |

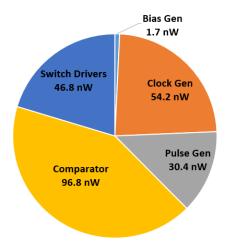

| Figure 2.8: Breakdown of power consumptions of SaS sub-circuit blocks under normal operation. The total power (230nW) is measured in room temperature and the proportion numbers come from post-pex simulation                                                                                                                                                                                                                                                        |

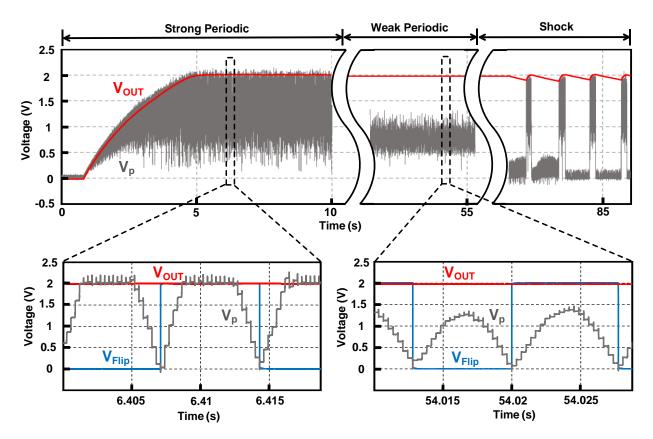

| Figure 2.9: Measured transient waveform of $V_P$ , $V_{OUT}$ and the $V_{Flip}$ (flip control signal) under different vibrations in the long term (top) and its zoom-in regions (bottom). Amplitude/frequency for strong and weak periodical vibrations are 2g/85Hz and 0.2g/85Hz, respectively. The shock vibration has an amplitude of 3g, with a (rough) period of 1 second                                                                                        |

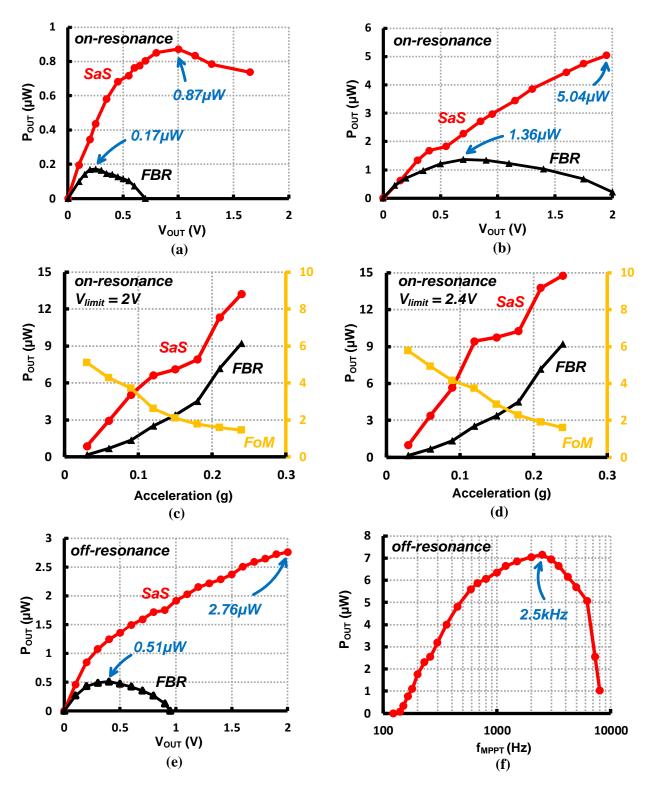

| Figure 2.10: Measured output power of SaS and ideal FBR for (a) different $V_{OUT}$ values with 0.03 g/53 Hz vibration, (b) different $V_{OUT}$ values with 0.09 g/53 Hz vibration, (c) different vibration strengths with $V_{limit}=2V$ , (d) different vibration strengths with $V_{limit}=2.4V$ , (e) different $V_{OUT}$ values with 0.5 g/85 Hz vibration and (f) different f <sub>MPPT</sub> values and (f) different input vibration strengths                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

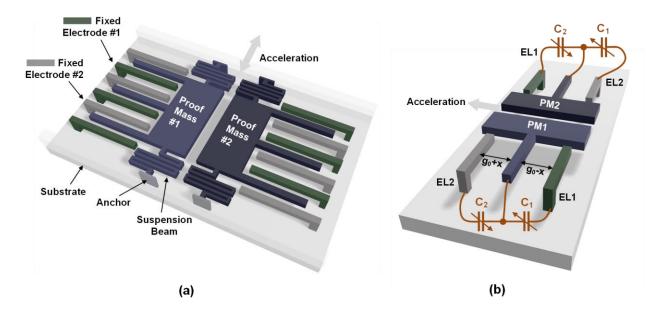

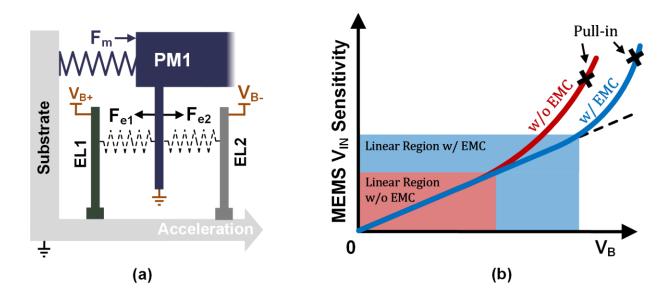

| Figure 3.1: (a) Simplified diagram of a fully differential MEMS capacitive accelerometer; (b) zoomed-in diagram showing the coupling capacitance between the MEMS proof-masses and electrodes. 41                                                                                                                                                                                                                                                                                                                           |

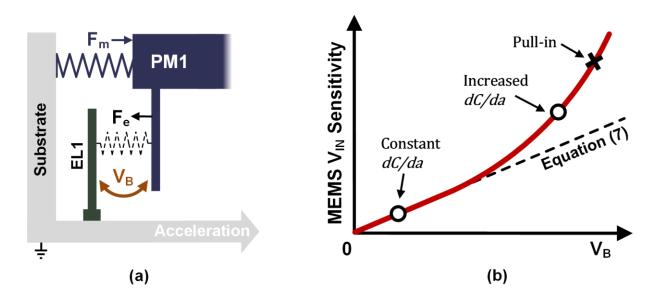

| Figure 3.2: (a) The conventional scheme to readout sensing signals from MEMS capacitive accelerometer; (b) the proposed high-voltage biasing scheme that increases the MEMS signal and relaxes the AFE noise requirement for low power operation                                                                                                                                                                                                                                                                            |

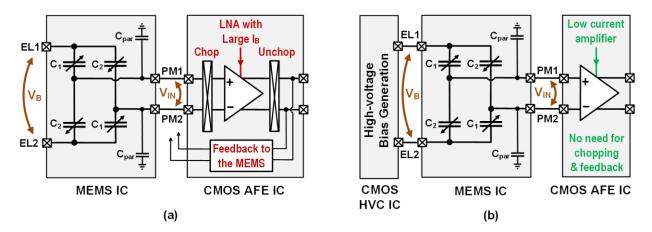

| Figure 3.3: (a) Stress analysis of the proof mass when considering both mechanical force $F_m$ and electrostatic force $F_e$ ; (b) with a fixed acceleration, the change of MEMS signal $V_{IN}$ with increasing bias voltage $V_B$                                                                                                                                                                                                                                                                                         |

| Figure 3.4: (a) The stress analysis of the proof mass in a differential MEMS structure; (b) the change in MEMS sensitivity with bias voltages for systems with/without electrostatic mismatch compensation (EMC).                                                                                                                                                                                                                                                                                                           |

| Figure 3.5: Top level diagram of the HVC chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 3.6: (a) Comparison between the voltage divider of parallel / serial switched capacitors, showing that the serial structure has a better AC path only controlled by $\Phi_2$ ; (b) implementation of the V <sub>B+</sub> sampling and division circuit, with a separated dirty V <sub>B+</sub> to pre-charge the sampling nodes and reduce V <sub>B+</sub> ripples; (c) implementation of the V <sub>B+</sub> and V <sub>B-</sub> average circuit and (d) conceptual waveform showing transient voltages (b) and (c) |

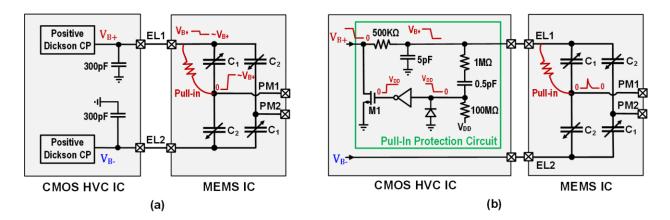

| Figure 3.7: (a) Without the protection circuit, pull-in results in high-voltage stress in PM1 that can damage the AFE circuit; (b) with pull-in protection, the voltage drop in EL1 will ground $V_{B+}$ and prevent damage to the AFE chip                                                                                                                                                                                                                                                                                 |

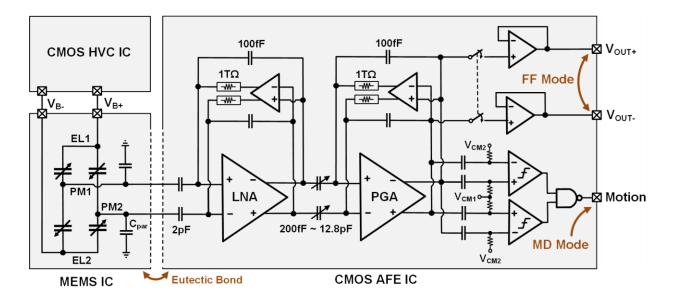

| Figure 3.8: Top-level diagram showing the MEMS + CMOS AFE chip                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

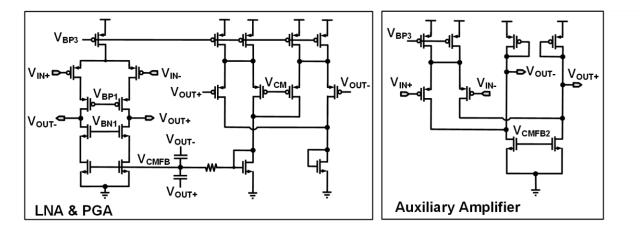

| Figure 3.9: Schematic of LNA/PGA and the auxiliary amplifier shown in Fig. 3.8                                                                                                                                                                                                                                                                                                                                                                                                                                              |

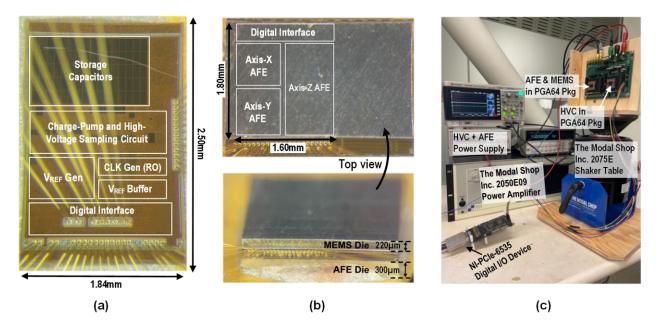

| Figure 3.10: (a) HVC die photo; (b) CMOS die photo and the eutectically bonded MEMS-CMOS die; (c) testing setup for the accelerometer measurement                                                                                                                                                                                                                                                                                                                                                                           |

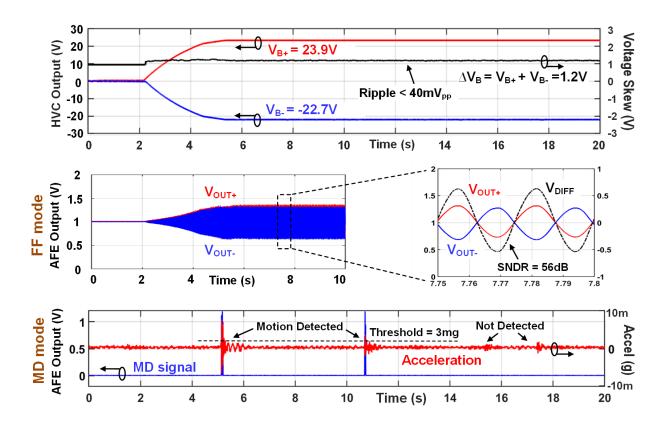

| Figure 3.11: Measured transient waveform showing the HVC bias voltage generation from cold start, and the AFE output voltage in both FF and MD mode                                                                                                                                                                                                                                                                                                                                                                         |

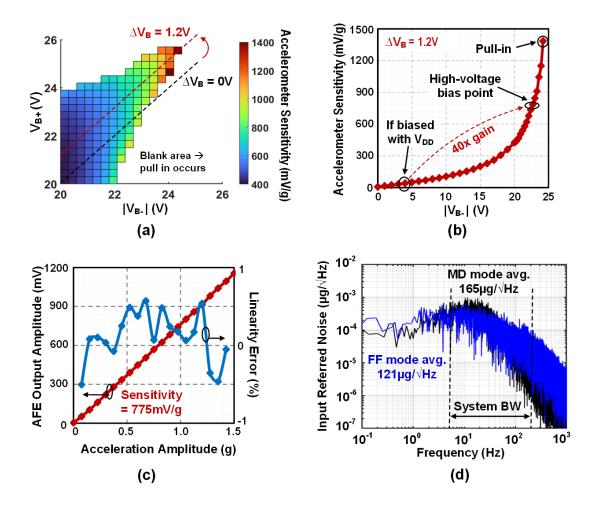

| Figure 3.12: Measured results for (a) the accelerometer sensitivity with >20V V <sub>B+</sub> and V <sub>B-</sub> , showing an optimal 1.2V voltage skew; (b) the accelerometer sensitivity from 0-25V bias maintaining a 1.2V skew; (c) linearity of accelerometer output within the 1.5g full-scale; (d) the accelerometer input-referred noise (determines its resolution) in FF and MD mode                                                                                                                             |

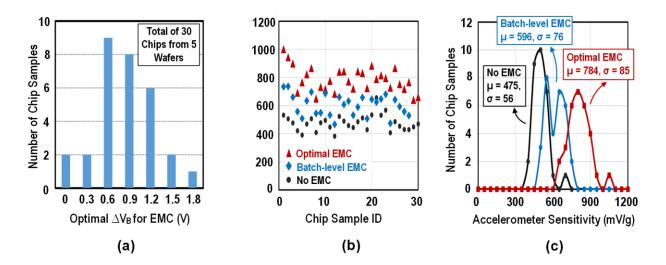

| Figure 3.13: (a) Distribution of the optimal voltage skews $\Delta V_B$ (that achieves the highest bias voltage before pull-in) across 30 different MEMS/CMOS chips; (b) EMC designated accelerometer sensitivity for the 30 chip samples, with individually chosen $\Delta V_B$ (red triangle), wafer-average $\Delta V_B$ (blue diamond) and zero $\Delta V_B$ (black dot); (c) distribution of the results in (b)                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

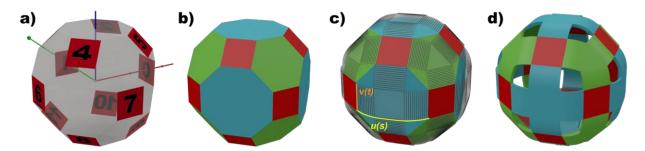

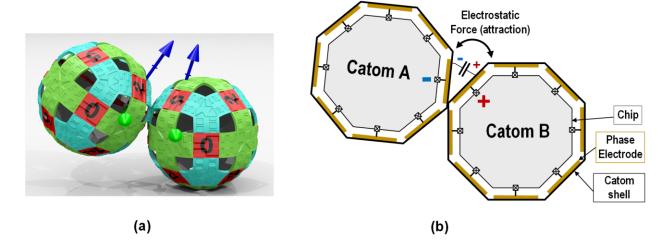

| Figure 4.1: Geometrical design of a Quasi-Spherical Module (Catom) for Building<br>Programmable Matter [2]                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.2: (a) The actuation (rotation) operation shown in [18] and (b) the 2-D diagram showing the electrostatic attraction force generation in this work                                                                                                                                                                                                                                                                                                                                             |

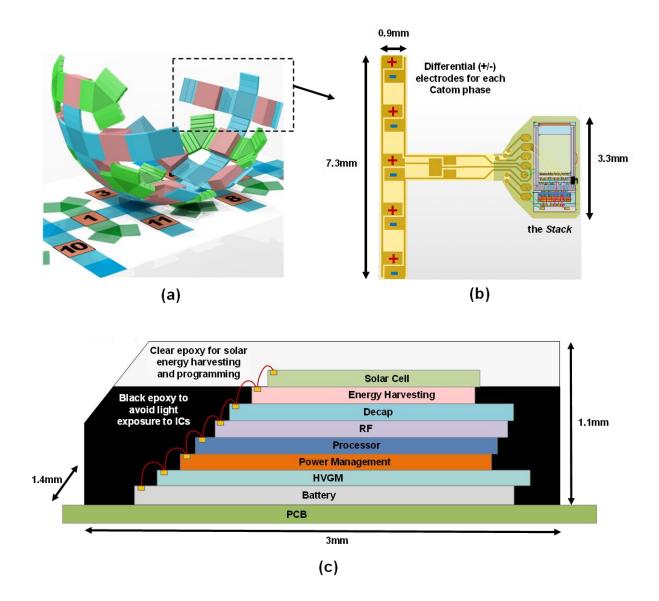

| Figure 4.3: (a) The disassembled view of a Catom [18]; (b) the Flex-board design with the micro-controller stack and differential high voltage electrodes, and (c) the diagram showing the stack design with multiple custom IC layers                                                                                                                                                                                                                                                                  |

| Figure 4.4: (a) The conventional Catom driving circuit that has 12 charge pumps and (b) HVGM with single charge pump and 12 high voltage multiplexers                                                                                                                                                                                                                                                                                                                                                   |

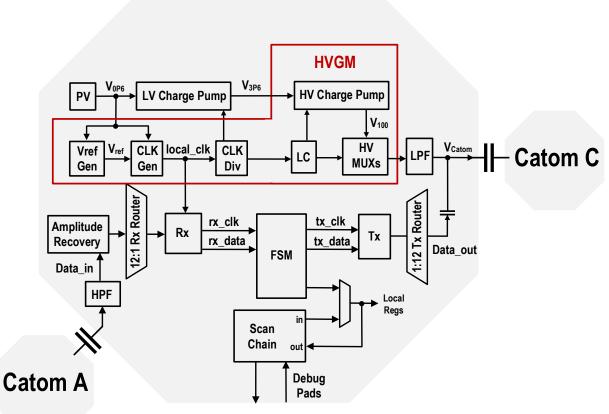

| Figure 4.5: Top-level diagram of the proposed HVGM chip                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

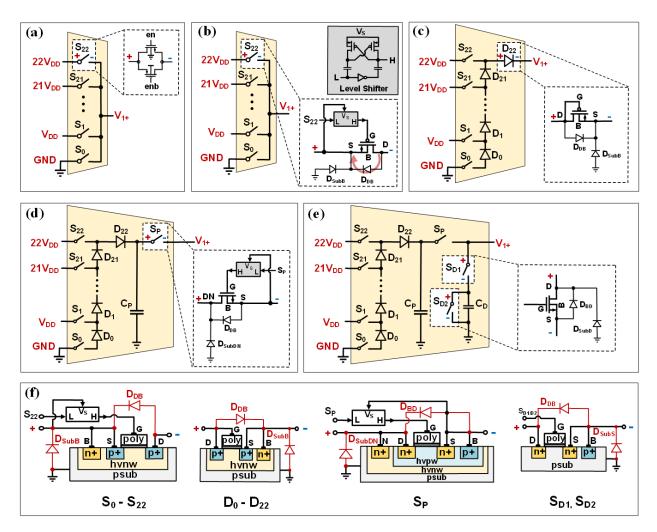

| Figure 4.6: (a) a conventional analog multiplexer with transmission gate; (b) a level-shifted high-voltage analog multiplexer that has a risk of reverse current (red arrow); (c) the improved high-voltage multiplexer with current-blocking diodes; (d) further improved high-voltage multiplexer with switched-capacitor resistance to limit peak current; (e) the final high-voltage multiplexer implementation with controlled discharge path and (f) device details and cross-section view in (e) |

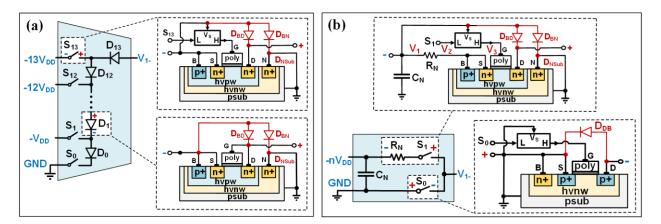

| Figure 4.7: (a) Implementation of HV-MUXN similar to its positive counterpart but with reverse current issue. (b) the actual HV-MUXN implementation with dual voltage selection and polyresistor to limit the current                                                                                                                                                                                                                                                                                   |

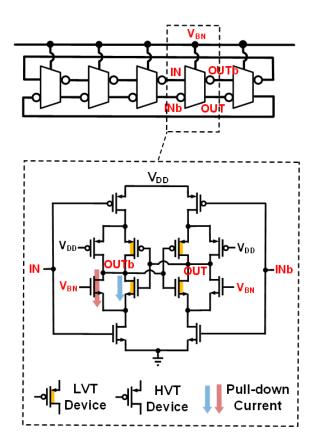

| Figure 4.8: Leakage-based ring oscillator [80] with bias voltage VBN controlling the output frequency                                                                                                                                                                                                                                                                                                                                                                                                   |

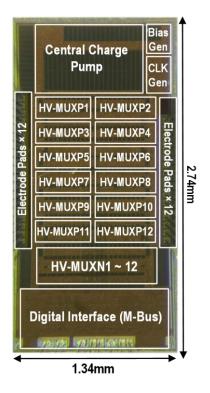

| Figure 4.9: HVGM die photo                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

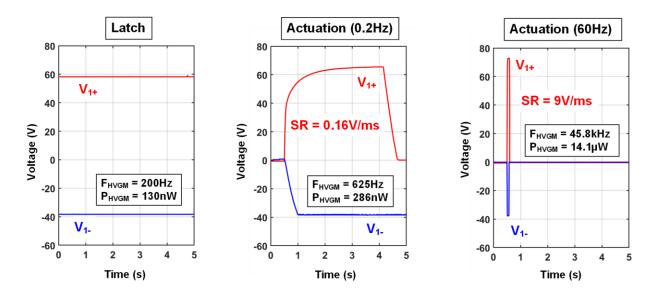

| Figure 4.10: Measured transient waveform showing the electrode voltage to latch (left), slow actuate (middle) and fast actuate (right)                                                                                                                                                                                                                                                                                                                                                                  |

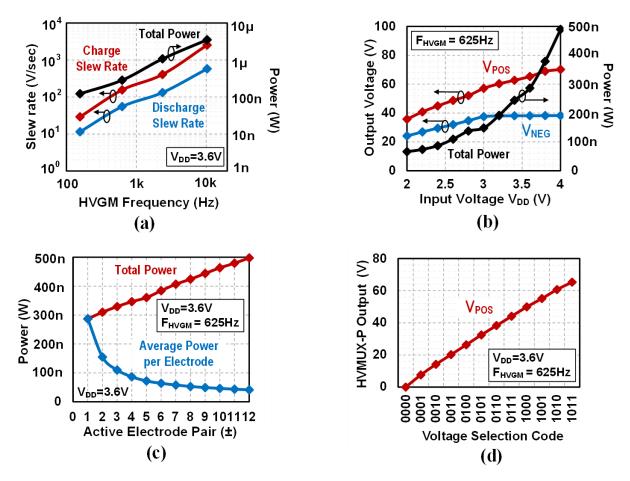

| Figure 4.11: (a) Measured HVGM power versus the electrode slew rate at different clock frequencies; (b) measured HVGM output voltage and power with different supply voltages; (c) measured HVGM power with different number of electrode being activated; (d) measured HVGM output programmability                                                                                                                                                                                                     |

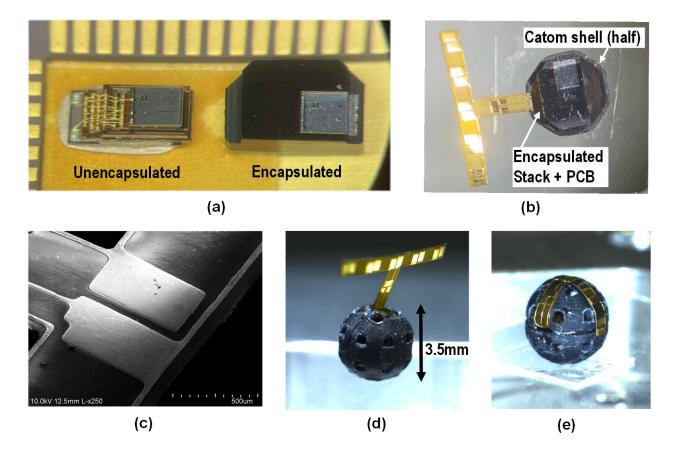

| Figure 4.12: (a) The Stack photo with and without the black epoxy encapsulation; (b) encapsulated Stack fit in a half Catom shell and connected to the flexible PCB; (c) microscope image showing the differential electrode design on the flexible PCB; (d) full Catom with the                                                                                                                                                                                                                        |

| Stack in it and an unattached flexible PCB; (e) full Catom with the Stack and flexible PCB attached to its surfaces.                      | 86 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

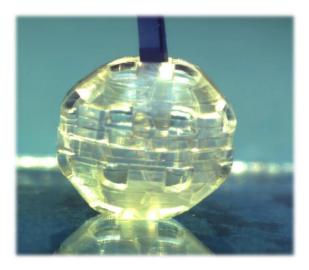

| Figure 4.13: Catom hardware with transparent shell for solar energy harvesting and communication.                                         | 87 |

| Figure 4.14: Top level diagram of HVGMv2.                                                                                                 | 88 |

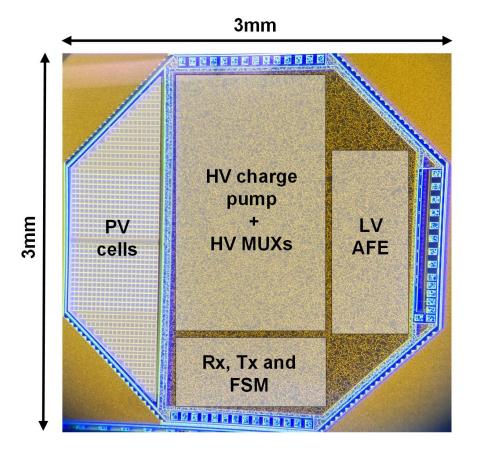

| Figure 4.15: Die photo of HVGMv2                                                                                                          | 89 |

| Figure 4.16: The cross-section view of the stacked PV cell structure in HVGMv2                                                            | 90 |

| Figure 4.17: Analog front end design for the capacitive coupling communication in HVGMv2.                                                 | 91 |

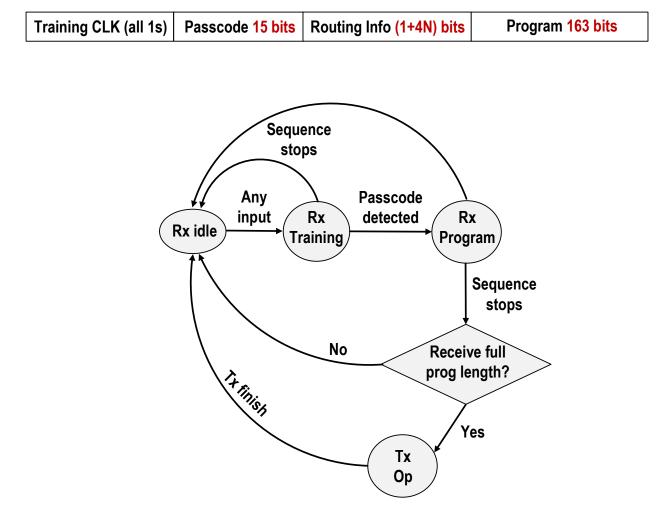

| Figure 4.18: Data package for the HVGMv2 communication (top), and a simplified state transition diagram for the $Tx + Rx + FSM$ (bottom). | 93 |

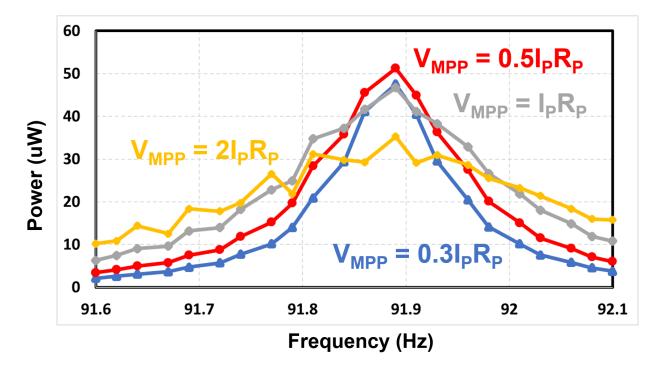

| Figure 5.1: Power extraction from the PEH with different $V_{MPP}$ ratio                                                                  | 98 |

#### Abstract

The Internet-of-Things (IoT) has long been considered the next major computing class that has significant societal benefits on people's lives. With the miniaturization of the sensor nodes, the acquisition and analysis of data can be achieved in a broader range of environments, enabling applications such as precision healthcare, smart buildings, intelligent agriculture, and more. Motions are ubiquitous in these applications and can be utilized as an energy source to mitigate the power constraints associated with the sensor node scaling. Besides, many sensor nodes also acquire motion signals to reveal the information from the ambience, and some may even actively produce motions to achieve a more complex interaction with the environment (e.g., micro-robot). This thesis introduces three major topics on low-power circuit and system designs for IoTs related to motions. The first topic is to harvest kinetic energy from motions with piezoelectric energy harvesters (PEHs). To address the challenges in the impedance matching to PEHs, we present a sense-and-set (SaS) circuit that achieves the optimal energy extraction from the transducer and adapts to environmental variations. The SaS circuit is implemented with a single chip design, achieving a  $5 \times$  power improvement in energy harvesting under periodic and random vibrations. The second topic is about sensing motions with ultra-low power MEMS capacitive accelerometers. To improve the critical trade-off between power and noise in MEMS accelerometers, we present a high-voltage biasing technique that significantly increase the MEMS sensing signal while maintaining mechanical stability with a novel technique called electrostatic mismatch compensation. The proposed accelerometer is implemented with 1 MEMS and 2 CMOS ICs, showing a  $15 \times$  power-noise improvement over the prior state of the art. The third topic is about

generating motions with micro-robot design to achieve the Programmable Matter (PM) that can be configured into any arbitrary 3-D shapes with a program. The motion generation is achieved by the high-voltage electrostatic actuation, and we present a high-voltage generation and multiplexing (HVGM) chip to enable a 100V actuation with 200nW range power. We further integrate HVGM with several other ICs into a complete bare-die system that is placed in each PM unit, and controls its communication, computation, powering and actuation in a PM system. A second version controller is also proposed and implemented to be fully integrated on-chip but maintains the multifunctions that enables an intelligent PM system.

#### **Chapter 1 Introduction**

From the early 1960s, the development of computers has been characterized by computing platforms that emerged and became dominant over time, known as Bell's law [1]. From the huge workstation to personal computers and then to smartphone, a new class of less expensive and much more compact computers is developed approximately every decade to replace its predecessor. The next generation of computing platforms [2] [3] [4] has reached the millimeter scale in terms of system volume and was able to perform a complex function including sensing, computations, and communications in diverse emerging applications. In 1999, Kevin Ashton first used the term "the Internet of Things (IoT)" to describe future computing platforms where the Internet is connected to the physical world through ubiquitous sensors.

Combining the scaling of sensor node hardware, IoT becomes promising in a wide range of applications, such as monitoring the environment for pollutants, assessing water quality, improving agricultural productivity, providing precision healthcare and hence improving quality of life, and many more tasks [5].

Along with these opportunities, miniaturized IoT sensors also brought unique design challenges, which are mainly related to its power constraints from the small battery capacity. Besides, environmental motions results in more design complexities as they may interact with the IoT sensors and change how they acquire data and issue feedbacks [6]. This thesis introduces three projects, from three different angles on the interaction between miniaturized IoT designs and motions: 1) how to power IoTs by harvesting energy from motion; 2) how to sense motion while maintaining both high resolution and low power; and 3) how to generate motions for a complete, intelligent micro-robot system.

Figure 1.1: Bell's Law predicts continuous scaling of micro-size computing systems [2].

### 1.1 Powering Miniaturized IoT Sensor Nodes with Motions

Since IoT sensors work in a wide range of environments, power delivery is often not reliable or even accessible. While sensors can operate with integrated batteries, their battery life is usually limited due to the small battery size. Moreover, as the number of sensors increases in the network, recharging sensor batteries or maintain a wireless power delivery [7] can also be tricky and expensive. Energy harvesting from the ambient environment can significantly extend the lifetime of battery-powered systems, and in energy-autonomous systems it can even eliminate the use of batteries. To perform energy harvesting, a transducer is integrated with the sensor, and it captures energy from one or more renewable energy sources and converts them into usable electrical energy [8]. Kinetic energy harvester is usually deployed in the presence of object motion, including vibrations, pressure and other activities, and the piezoelectric transducers become popular for kinetic energy harvesting due to their high power-density and good sustainability.

An interesting application of the piezoelectric energy harvester (PEH) is introduced by [9], where a series of wireless sensor nodes were attached to a bridge to acquire its vibration signature for structural health monitoring (SHM), as shown in Fig. 1.2. The wireless sensors are integrated with energy harvesting modules made of piezoelectric transducers and the vibration energy is harvested to power the SHM sensor nodes for long period of time (e.g., years) without replacing the batteries. In the energy harvesting module, the authors utilize the *Parametric Frequency Increased Generator* [10] (*PFIG*) technique to up-convert the vibration frequency to a higher value that maximizes the output power of a miniaturized piezoelectric transducer, providing a  $\mu$ W level harvested power from the bridge vibrations.

Figure 1.2: The deployment of the wireless sensors on the bridge (top) and the measured vibration acceleration waveform with its power spectrum density (bottom) [9].

However, there are several challenges associated with the use of piezoelectric energy harvesters in mm-scale sensor nodes. First, the efficiency of the PEH is highly related to the vibration frequency and its own resonant frequency, which is hard to meet in practical applications, since most ambient vibration sources have a relatively unstable, broadband frequency spectrum. Second, the PEH interface circuits that perform impedance matching can significantly impact the charge-extraction efficiency as well, and design challenges exist to compensate the intrinsic PEH parasitics to maximize output power. We present a new energy extraction technique, sense-andset (SaS), to perform maximum-power-point tracking (MPPT) by dynamically sensing and setting the optimal voltage to the transducer. It also adapts to various input vibrations and load changes while maintaining maximum efficiency in extracting power from piezoelectric energy harvesters.

#### **1.2 Sensing Motions with Ultra-Low Power and High Resolution**

Motion detection and classification are becoming crucial for autonomous monitoring systems, including assistive living, rehabilitation, device stabilization and surveillance [11]. While the detection of motion can be achieved remotely via ultrasound motion sensors or image sensors, a directly attached sensor to the object (e.g., an accelerometer in a wearable device) is still preferable because of the high sensitivity and the continuous monitoring of the motion. MEMS capacitive accelerometers have become increasingly popular in motion-detection applications such as object monitoring, gesture recognition and tilt control [12] [13]. Consisting of a micro-mechanical spring-mass system, MEMS capacitive accelerometers are capable of high acceleration sensitivity while maintaining good linearity, low Brownian(mechanical) noise, good temperature consistency and miniaturized volume [14] [15]. An analog-front-end (AFE) interface circuit is

required to amplify the signals generated by the MEMS sensing elements, before it can be read out and utilized by other circuits such as analog-to-digital converters (ADCs).

The AFE circuit, usually implemented with the CMOS process, has its own noise floor that adds up to the readout signal. And since there is a fundamental noise-power trade-off inside the circuit design, it is difficult to achieve both sub-µW power and a mg-level resolution in measuring the acceleration. In Chapter 3, we present a unique accelerometer architecture in which, instead of keeping a good noise floor in the CMOS readout circuit design, we increase the signal amplitude from the MEMS side by applying a higher voltage bias on it. This high voltage bias, while it generates a linearly increase signal at the AFE input, reduces the stiffness of the MEMS accelerometer by electrostatic force to further increase the MEMS sensitivity. The proposed accelerometer achieves 40× signal gain than the conventional MEMS capacitive accelerometers, and it operates with 100nW range power to sense mg-level accelerations, achieving a larger than 10 times improvement on the power and resolution performance.

#### 1.3 Creating Motions with Electrostatic Actuation by Nano-Watt Circuit

The concept of IoT was originally proposed to consist of sensors and computing resources. During its rapid development over the last two decades, actuators are also becoming a significant part of it and evolve more applications with micro-robot design. Recent research has presented an insect-sized robot named RoboBee [16], with wings driven by two alumina-reinforced piezoelectric actuators and integrated together with the electronics required for untethered flight.

Another research has brought the realization of programmable matter consists of tiny, mmscale quasi-spherical robots called Catoms [17]. The concept of programmable matter (PM), defined as matter that can change its physical properties based on a user's input, has been pursued for a long time to achieve the ultimate vision of achieving a universal meta-material for use in daily life. Improved 3D printing and VLSI/MEMS technology have enabled the realization of PM with millimeter-sized intelligent micro-robots [18]. PM consists of tiny, mm-scale quasi-spherical robots called Catoms, which can autonomously attach themselves in different positions to their neighbors using electrostatic forces. When different Catoms make surface contact, the difference in their surface potentials creates an electrostatic force, bonding them together (latching) or causing a rotation/movement (actuation). By combining thousands of Catoms, a morphable 3D structure can be programmed to take arbitrary shapes. The PM hardware structure can also be manipulated and changed externally while the resulting changes are tracked and captured using sensors inside each Catom and synchronized with a simulation/3-D model inside the software environment. Conversely, we can also modify the 3-D model through the software, and the Catoms will be actuated to reform the PM shape and reflect the change. This 2-way interaction induces a scalable, real-time, efficient, and expressive way of implementing a virtual reality. At the same time it creates an ensemble of micro-robots, which can interact with other communicating things through the IoT.

The realization of programmable matter (PM) requires a sophisticated system design, including geometry design, control algorithms, simulation, software-hardware co-design and industrial design [19] [20] [21] [22]. In this thesis we show for the first time a micro-controller design that resides in the Catom and supports its communication, computation, actuation and power management for autonomous operation. While introducing the complete micro-controller system using a chip stack, we focus on the chip layer that is related to actuation of the PM.

#### **1.4 Dissertation Outline**

This dissertation is composed of three chapters introducing the unique circuit and system designs for the above three topics. Chapter 2 presents a new energy extraction technique, sense-

and-set (SaS), to perform maximum-power-point-tracking (MPPT) in harvesting energy from piezoelectric energy harvesters (PEHs). Unlike previous PEH interface designs that relied on calibration to achieve high efficiency, SaS can automatically determine the optimal output voltage through a small "sensing phase" and thus keep maximum power extraction under arbitrary vibrations. The SaS circuit is fabricated with a 0.47 mm<sup>2</sup> single IC, and measured with 5.41× and  $4.59\times$  improvement in harvesting energy from periodic and pulsed vibrations, respectively.

Chapter 3 presents a triaxial MEMS capacitive accelerometer using a high-voltage biasing technique to achieve high resolution with ultra-low-power. The accelerometer system generates a pair of differential high-voltages and utilizes them to bias the MEMS structure, raising the MEMS signal way above the noise floor of the analog front end circuits. With the large signal-to-noise ratio, the proposed accelerometer system eliminates the power hungry low-noise amplifiers and signal chopping, and significantly improves the power-noise trade-off in the conventionally biased MEMS accelerometers. Moreover, the properly generated bias voltages compensate for the electrostatic mismatch on MEMS caused by using high voltages, and show a robust operation against MEMS process variation. The proposed accelerometer is fabricated with 1 MEMS and 2 CMOS chips, achieving a  $121\mu g/ \sqrt{Hz}$  input-referred noise floor with  $\pm 1.5g$  dynamic range, <1% linearity error and 184nW per-axis power (including high-voltage bias generation). Compared to prior arts, it achieves a  $11.7 \times$  FoM improvement considering both power and noise specifications over the sensing bandwidth.

Chapter 4 presents a high-voltage-generation-and-multiplexer (HVGM) chip specially designed for electrostatic actuation of micro-robots for applications such as Programmable Matter (PM). PM consists of tiny, mm-scale quasi-spherical robots that can be combined and programmed to form any arbitrary 3-D shape autonomously. The HVGM individually controls 12 pairs of +/-

electrodes using a positive and negative charge pump and mux-structure, consuming only 286nW power when switching a 10pF electrode at 155V/s, and producing a differential voltage of 103V (29× voltage gain from 3.6V) in measurement. We also show a complete micro-system of stacked dies, measuring 3×1.4×1.1 mm, including the HVGM, a processor, radio, and harvester that achieves energy-autonomous operation, and can be integrated into a micro-robot "Catom" via a flexible PCB. Furthermore, we propose and fabricate the second version of the Catom controller that only consists of one chip, HVGMv2 for lower power and cost, while maintaining similar multi-functions of the stacked dies.

Each of Chapters 2 –4 is organized with first discussing on the design challenges, related previous works, and also the contribution of the proposed work. Then a detailed explanation of the proposed work will be given in the next 2~3 sections, including fundamental analysis and circuit implementation. In the conclusion parts, we will analyze the limitations of our work and propose future work for further improvement.

## Chapter 2 An Efficient Piezoelectric Energy Harvesting Interface Circuit

## **2.1 Introduction**

A piezoelectric energy harvester (PEH) converts mechanical strain into electrical charge by means of the direct piezoelectric effect [23], and the charge can be extracted to generate AC power (usually in the nW to mW range), which can be applied to the electrical load. The output power of a given PEH can be optimized in terms of these two processes. On one hand, the efficiency of the electro-mechanical energy conversion is optimized when the PEH is precisely vibrated at its resonant frequency, matching the natural characteristics of its mass-spring-damping system. This is rarely achieved in practical applications since most ambient vibration sources have a relatively unstable, broadband frequency spectrum [24]. Hence, some prior works have aimed to improve the bandwidth energy conversion, although with limited success [25] [26]. On the other hand, the design of interface circuits that perform impedance matching or maximum-power-pointtracking (MPPT) can significantly improve the charge extraction efficiency and thus increase the output power of the PEH. Most of the circuit techniques discussed in this thesis aim to improve the efficiency of this process rather than control the electro-mechanical conversion.

Among various interface circuits, full-bridge rectifiers (FBRs) are the most commonly used for their simplicity and stability [27] [28]. However, their power efficiencies are usually low since most of the PEH-generated charges are not extracted but remain within the large intrinsic capacitors of the PEHs. Several different techniques have been proposed to help with energy extraction from PEHs. The bias-flip (BF) technique, proposed by [29], manually sets a high biasvoltage at the PEH's output in order to extract more energy from a certain charge generated by the PEH. When the charge generation (current) changes direction with the input vibration oscillation, the bias-voltage is flipped. This is performed adiabatically to limit the energy loss of the operation. Prior BF-based works generally achieved the highest power efficiency when compared to other energy extraction techniques, and they can be divided into two categories, synchronized switch harvesting on inductor (SSHI) [30] [31] [32] and synchronized switch harvesting on capacitor (SSHC) [33] [34] [35], depending on whether an inductor or a capacitor array is used for the voltage flip. Other charge extraction techniques, such as synchronous electric charge extraction (SECE) [36] and energy pile-up resonant circuit [37], are generally less power efficient than the BF-based circuits but offer other advantages such as being more suitable for non-periodic vibrations.

However, all the above techniques have disadvantages for maximum-power-point tracking (MPPT) while extracting energy from PEHs. Theoretically, SSHI and SSHC can achieve near-MPPT in energy harvesting, but they usually do not adapt to various input-vibration types (periodic or shock) and amplitudes, which decreases their power efficiencies in practical applications. SECE automatically adapts to different vibration amplitudes, but its efficiency is significantly degraded by the large intrinsic capacitor CP, and it generates unregulated output voltage for non-periodic vibrations.

In this chapter we present a sense-and-set (SaS) interface circuit for PEHs, which is fundamentally different from prior techniques and achieves MPPT for arbitrary input vibrations. The proposed SaS technique has the following advantages over prior art:

SaS dynamically senses the PEH's charge generation and sets the harvesting voltage accordingly. The power efficiency of SaS is thus adjusted to approach the theoretically limit.

- 2. SaS maintains MPPT for different vibration types, strengths/amplitudes and PEH characteristic parameters without the need to manually tune the circuit for each condition.

- 3. SaS produces rectified output voltage without an additional passive rectifier, which eliminates the conduct loss (voltage drop) associated with the rectifier diode and improves the efficiency, especially for low amplitude vibration (low voltage) applications.

- 4. SaS de-couples the output node from the input so that a fixed output voltage does not interfere with the MPPT. In previous techniques V<sub>OUT</sub> needs to change with the vibration strength to achieve high power efficiency which clearly cannot be performed dynamically.

The remainder of this chapter is organized as follows. Section 2.2 presents the background of the PEH model and interface circuit approaches. The operation principle and implementation of the proposed SaS circuit are described in Sections 2.3 and 2.4, respectively. Section 2.5 shows the measurement results and analysis, while a conclusion is drawn in Section 2.6.

#### 2.2 Related Works on the PEH Interface Circuit

#### 2.2.1 Modeling of Piezoelectric Transducers

*Figure 2.1: Modeling of piezoelectric transducer. (a) complete model with electromechanical coupling and (b) simplified model on resonant frequency.*

The PEH or piezoelectric transducer generates electrical charges when the piezoelectric material is compressed or deflected by mechanical stress derived from external vibrations. It can be modeled as an electro-mechanical system as shown in Fig. 2.1(a). The left part of the model

illustrates the mechanical structure of the PEH, in which  $R_M$ ,  $L_M$  and  $C_M$  are the equivalent circuit components for the mass-spring-damping system of the piezoelectric layer. With the electromechanical coupling factor  $\Gamma$ , power generated at the mechanical side is transformed to the electrical side and stored in the PEH intrinsic capacitor  $C_P$ . When the PEH is excited at or close to its resonant frequency,  $L_M$  and  $C_M$  are cancelled out, and the model can be simplified into a model without the transformer, as shown in Fig. 2.1(b), where

$$I_P = \frac{V_M}{\Gamma R_M} \tag{2.1}$$

$$R_P = \Gamma R_M^2 \tag{2.2}$$

$I_P$  defines the charges generated by the PEH in a certain time, and  $R_P$  is the equivalent loss in the electro-mechanical conversion. According to the theory of maximum power transfer, the load receives maximum power

$$P_{max} = \frac{1}{4} I_P{}^2 R_P \tag{2.3}$$

from the current source when

$$V_P = V_{MPP} = \frac{1}{2} I_P R_P$$

(2.4)

However, the impedance of  $C_P$  is usually much smaller than  $R_P$  at the vibration frequency f (or  $\omega$ ). As a result, the  $V_P$  amplitude is much smaller than  $V_{MPP}$  even for the open-circuit condition

$$V_{P-OC} = I_P(R_P || X_{CP}) = \frac{I_P}{\omega C_P}$$

(2.5)

Since  $1/\omega C_P \ll R_P$ ,  $V_{P-OC} \ll V_{MPP}$ . For the same I<sub>P</sub> generated by the vibration, the low V<sub>P</sub> value limits the power efficiency. Furthermore, V<sub>P</sub> will be affected by the impedance-match condition between the PEH and interface circuits. The ideal interface circuit that delivers P<sub>max</sub> to the load should achieve complete impedance matching to the PEH, where the load impedance  $X_L = R_L + \omega L_L$  is given by

$$R_L = R_P, \qquad \omega L_L = \frac{1}{\omega C_P} \tag{2.6}$$

However, the required  $L_L$  value is usually hundreds of Henries, which is impractical for system-on-chip (SoC) or even on-board systems. Thus prior interface circuit designs tend to achieve better impedance match by placing V<sub>P</sub> to be near V<sub>MPP</sub>, which counteracts the negative effect of C<sub>P</sub>. The following paragraphs will continue this discussion in more details.

#### 2.2.2 Baseline Interface: Full-Bridge Rectifier

Figure 2.2: Schematic and waveform for piezoelectric energy harvesting through (a) FBR and (b) SSHI rectifier.

The FBR is the most widely used interface circuit that allows energy harvesting from PEHs. As shown in Fig. 2.2(a), the PEH current  $I_P$  first charges  $C_P$  until  $V_P$  reaches  $V_{OUT}$ . Then all of  $I_P$  will flow through the FBR diodes to the load (represented by the green region) except for the loss by  $R_P$ . When  $I_P$  changes direction with the input vibration, it must first discharge  $C_P$  to 0 and then repeat the voltage build-up process in the other direction. During the charge-discharge operation, no power is transferred through the rectifier.

In FBR circuits, the output voltage  $V_{OUT}$  must be between 0 and  $V_{P-OC}$  in order to harvest energy from the PEH. Assuming ideal diodes (with no voltage drop) are used, the FBR delivers the maximum output power when  $V_{OUT}$  is equal to half of  $V_{P-OC}$ , according to [29].

$$P_{max-FBR} = f C_P V_{P-OC}^{2} = \frac{I_P^{2}}{2\pi\omega C_P}$$

(2.7)

Comparing this to the theoretical maximum power we get

$$\frac{P_{max-FBR}}{P_{max}} = \frac{2}{\pi} \frac{1}{\omega C_P R_P} = \frac{2}{\pi Q_{PEH}}$$

(2.8)

where  $Q_{PEH}$  is the quality factor of the piezoelectric transducer. Since generally  $1/\omega C_P \ll R_P$ , then  $Q_{PEH} \gg 1$  (in the range of 10-100 for most of PEHs), and the maximum output power delivered by a FBR is significantly lower than the theoretical maximum value.

#### 2.2.3 Prior State of the Art: Bias-Flip Rectifiers

One reason for the low power efficiency of the FBR is that  $V_P$  is limited within  $V_{P-OC}$ , which is far below  $V_{MPP}$ , which is shown as the blue line in Fig. 2. 2(a). For the same PEH current  $I_P$ , this much lower voltage results in output power degradation. One effective way to improve is the efficiency is to manually set a bias voltage (usually higher than  $V_{P-OC}$ ) on  $V_P$  so that the same

I<sub>P</sub> produces larger output power. When I<sub>P</sub> changes direction, the bias voltage is then flipped so that no energy is lost due to discharging  $C_P$ . The circuits that utilize such a "bias-flip" operation can be divided into two categories, SSHI [29] [30] [31] [32] and SSHC [33] [34] [35], depending on whether they use an inductor or a capacitor array for the voltage flip.

Fig. 2. 2(b) shows the schematic and waveform of an SSHI circuit. It still has an FBR for rectifying the output, but it has an additional switch-controlled inductor in parallel.  $V_P$  is set manually to be a fixed high voltage, as demonstrated by the red line.  $I_P$  will flow through the FBR to the load without charging  $C_P$ , as indicated by the green region. When  $I_P$  changes direction, discharging  $C_P$  is avoided by turning on the switch and shorting the PEH through the inductor  $L_{SW}$ . By precisely controlling the switch's turn-on period,  $\Phi_{SSHI}$ ,  $V_P$  will be adiabatically flipped to a slightly lower negative value due to the circuit loss during the flip. Then the inversed current IP charges  $V_P$  back to  $V_{OUT}$ , and energy harvesting begins again at this voltage.

From previous discussions, we know that for each interface circuit, the energy extraction from the PEH peaks when  $V_P$  gets closer to  $V_{MPP}$ . In the SSHI circuit, that is when  $V_P = V_{OUT} = Q_{BF}V_{P-OC}$ , and the maximum power delivered by an SSHI rectifier is

$$P_{max-SSHI} = 2fC_{P}V_{P-OC}^{2}Q_{BF} = \frac{I_{P}^{2}Q_{BF}}{\pi\omega C_{P}}$$

(2.9)

where  $Q_{BF}$  is the combination of quality factors of the PEH and the  $C_{P}L_{SW}$  resonant circuit, and thus usually  $1 \ll Q_{BF} < Q_{PEH}$ . Again, we compare it to the theoretical maximum power

$$\frac{P_{max-SSHI}}{P_{max}} = \frac{4Q_F}{\pi} \frac{1}{\omega C_P R_P} = \frac{4Q_F}{\pi Q_{PEH}}$$

(2.10)

Although the power efficiency seems to be much better than that of an FBR, SSHI circuits does not achieve MPPT because the square-wave-shaped  $V_P$  does not track the waveform of  $V_{MPP}$ ,

which is defined by the vibration pattern (normally it will be a sine wave). In addition to the voltage-flip loss, which is shown by the dashed grey region in Fig. 2. 2(b), it also has a "dead time" when  $V_P$  is larger than  $2V_{MPP}$  and all the current will flow through  $R_P$  instead of the FBR (solid grey region). More importantly, in order to achieve the peak output power, SSHI circuits must set the value of  $V_{OUT}$  wisely since it defines the amplitude of  $V_P$ , which further determines the output power. In practical applications, it is hard to predict  $V_{P-OC}$  and set the correct  $V_{OUT}$  before the vibration happens. Also, the system output must be stable, not changing with the vibration's amplitude, and an additional voltage converter will be needed, which further decreases the total power efficiency.

These limitations were partly addressed by some recent energy extraction techniques, such as synchronous electric charge extraction (SECE) [36], which builds  $V_P$  by the input current  $I_P$  and harvests only at the peak value. However, these techniques lack the advantages of using a higher voltage at  $V_P$ , so the overall power efficiency is less than that of the BF-based technique.

### 2.3 Fundamentals of the Sense-and-Set Technique

To achieve MPPT for PEHs,  $V_P$  needs to be equal to  $V_{MPP}$ , whose waveform and amplitude varies with the vibration. Hence, there are two main challenges to dynamically adapt  $V_P$  to  $V_{MPP}$ :

- 1. Determining the value of  $V_{MPP}$ . It is not possible to directly observe  $V_{MPP}$  due to the large intrinsic  $C_P$ . Neither can we measure  $R_P$  in the circuit (and multiply it by  $I_P$  to get  $V_{MPP}$ ) since it is not in the real electrical domain but derived from the electromechanical mode.

- 2. Maintaining  $V_P$  equal to  $V_{MPP}$ . If we determine  $V_{MPP}$  and  $V_P$  is adapted to the  $V_{MPP}$  level, its value will change with the oscillation. Since  $C_P$  is large, keeping  $V_P$  at/near  $V_{MPP}$  requires a large energy transfer to charge or discharge  $C_P$ , which results in

significant power loss.

Our proposed SaS technique addresses these two challenges by adiabatically estimating the value of  $V_{MPP}$  (the "sense" operation) and then adiabatically adjusting  $V_P$  to it (the "set" operation). The operation of sense and set will be introduced in the next paragraphs.

### 2.3.1 Sense Phase

As previously discussed in section II. A, a PEH's open-circuit voltage  $V_{P-OC}$  is far less than  $V_{MPP}$ . The difference comes from the current that flows through  $C_P$ , and, hence, we can recover  $V_{MPP}$  by taking this current into account. Assuming the PEH is left in the open-circuit state, then

$$I_P = I_R + I_C \tag{2.11}$$

where  $I_R$  and  $I_C$  are the current flowing through  $R_P$  and  $C_P$ , respectively.  $I_R$  can be derived by  $V_P/R_P$  in which  $R_P$  is an unknown but fixed value for a given PEH. To measure  $I_C$ , we can wait for a short time period  $\Delta t$  and measure the voltage accumulation  $\Delta V$  on capacitor  $C_P$ .  $I_C$  is approximately constant during  $\Delta t$ , and its value is given by

$$I_P = \frac{V_P}{R_P} + \frac{C_P \Delta V}{\Delta t}$$

(2.12)

Then  $V_{MPP}$  can be recovered by

$$V_{MPP} = \frac{1}{2} I_P R_P = \frac{1}{2} (V_P + \frac{R_P C_P}{\Delta t} \Delta V)$$

(2.13)

Since  $R_P$ ,  $C_P$  and  $\Delta t$  are constant, we can "sense"  $V_{MPP}$  no matter what the current  $V_P$  is by measuring  $\Delta V$ .

Figure 2.3: (a) SaS core circuit where  $C_P=C_P$ ,  $C_T=C_T$ , (b) set initial voltage  $V_P$  on  $C_P$ ,  $C_P$  and  $C_T$ , (c) leave the *PEH* in open-circuit and let  $I_P$  only charge  $C_P$ , (d) short  $C_P$  and  $C_P$  through an inductor until their voltages merge, (e) transfer the energy in the inductor into the smaller capacitor, (f) short  $C_T$  and  $C_T$  to get  $V_{MPP}$ , and (g) waveforms showing the voltages for important nodes.

However, since we want to keep  $\Delta t$  relatively short (for the approximation that I<sub>C</sub> is constant), the resulting  $\Delta V$  is usually in the sub-mV range. In order to operate with such a small signal, it is necessary to design delicate amplification and offset-cancelling circuits, which induce large power overhead. Fortunately, the energy difference from  $\Delta V$  on the capacitor C<sub>P</sub> is not small due to the large value of C<sub>P</sub>. In SaS we use an inductor-based amplification where we transfer the energy difference into a smaller capacitor to generate higher voltage (tens of mV). Then a serial-

to-parallel switched capacitor array is used to further convert it to higher voltage (hundreds of mV).

Fig. 2. 3(a) shows the SaS circuit schematic, which consists of multiple switches, capacitors and a shared inductor. It can be reconfigured to different sub-circuits during the sense phase as shown in Fig. 2. 3(b)-(f); the red curve shows the direction of current flow. Initially, C<sub>P</sub>, C<sub>P</sub>, and C<sub>T</sub> are at the same potential as they are all connected and charged by the PEH (b). When the sense phase begins, the PEH is left in open-circuit mode for the time  $\Delta t$ , and a voltage difference  $\Delta V$ develops between C<sub>P</sub> and C<sub>P</sub> (c). Since C<sub>P</sub> and C<sub>P</sub> have relatively large capacitances, their energy difference is large, and we can use this for charge-based amplification. In Fig. 2. 3(d), we first short C<sub>P</sub> and C<sub>P</sub> through the inductor L to equalize their voltages, energizing L by

$$E_{L} = \frac{1}{2} \left[ C_{P} V_{P}^{2} + C_{P} (V_{P} + \Delta V)^{2} - 2C_{P} \left( V_{P} + \frac{\Delta V}{2} \right)^{2} \right]$$

$$= \frac{1}{4} C_{P} \Delta V^{2}$$

(2.14)

EL is then transferred into a much smaller capacitor CT in (e) to get a higher voltage VT

$$V_T = \sqrt{\frac{2E_L}{C_T}} = \sqrt{\frac{C_P}{2C_T}} \Delta V$$

(2.15)

By replacing the  $\Delta V$  term in (2.13) with VT, we rewrite the VMPP expression as

$$V_{MPP} = \frac{1}{2} I_P R_P = \frac{1}{2} \left( V_P + V_T \frac{\sqrt{2C_T C_P R_P^2}}{\Delta t} \right)$$

(2.16)

If the constant  $\sqrt{2C_T C_P R_P^2}/\Delta t$  is tuned to be 1, then  $V_{MPP}$  is the average of  $V_P$  and  $V_T$ . So in Fig.3 (f) we short  $C_T$  and  $C_T$  to generate  $V_{MPP}$  and we can set  $V_P$  to this value for MPPT operation.

#### 2.3.2 Set Phase

The SaS circuit "sets"  $V_P$  to  $V_{MPP}$  after obtaining its value during the sense phase. The is performed by configuring the SaS circuit into an inductor-based up-down converter, as shown in Fig. 2. 4(a) and (b). Converting the voltage up and down are adiabatic processes; the blue path shows the charging or discharging current that energizes L, and the green path shows the energyrecycle back to the battery.

After converting  $V_P$  to  $V_{MPP}$ , the SaS maintains  $V_P$  around this value by disconnecting itself from the PEH, as shown in Fig. 2. 4(c). Then  $I_P$  gradually charges  $C_P$ , causing  $V_P$  to rise, and when  $V_{P'}$  exceeds the preset threshold, SaS harvests from  $C_P$  by down-converting its voltage back to  $V_{MPP}$  to maintains MPPT. The harvested energy is then transferred to the load (battery), and  $V_{OUT}$ can be arbitrarily set regardless of the input amplitude.

The set phase lasts until  $V_{MPP}$  drifts away after a time period, and the SaS ceases energy harvesting and enters the sense phase again. The new sense phase happens at the old  $V_{MPP}$  value, and error-correction is performed to get the new  $V_{MPP}$ . Then SaS converts  $V_P$  to the new  $V_{MPP}$  and begins another round of harvesting. By re-sensing repeatedly at a higher frequency than the vibration, the SaS technique achieves energy harvesting that tracks  $V_{MPP}$  dynamically, as shown in Fig. 2. 4(c). Also, when the current crosses zero and changes its direction, there is a voltage flipping operation so that VP remains positive, as will be further explained in the next subsection.

Figure 2.4: SaS rectifier in set phase. (a) down-convert operation and (b) up-convert operation, (c) SaS waveform (without voltage flip) and its zoomed-in region, (d) SaS waveform with voltage flip, and (e) SaS efficiency with different MPPT ratios.

Since SaS always performs energy harvesting near the maximum power-point, its power efficiency can approach 100% except for the loss caused by circuit non-ideality, which is given by

$$\frac{P_{SaS}}{P_{max}} = \eta_{MPPT} \eta_{DT} \eta_{VC}$$

(2.17)

In this equation,  $\eta_{MPPT}$  is the MPPT tracking error for V<sub>P</sub> not perfectly following V<sub>MPP</sub>, and  $\eta_{MPT}$  characterizes the dead-time loss since SaS does not harvest energy during the sense phase. There is a trade-off between  $\eta_{MPPT}$  and  $\eta_{DT}$  when choosing the sense-and-set frequency. More frequent SaS operations increases the V<sub>MPP</sub> tracking precision and thus improve  $\eta_{MPPT}$ , but degrades  $\eta_{DT}$  because the circuit spends more time overall in determining V<sub>MPP</sub>.

With the optimal frequency, the efficiency of  $\eta_{MPPT}\eta_{DT}$  is usually around 85% or higher. However, the voltage conversion loss due to the switching and conduction activities usually dominate the total efficiency number. Although the inductor-based voltage converter has a high efficiency itself, it transfers the energy in C<sub>P</sub> ( $\propto$ C<sub>P</sub>V<sub>P</sub><sup>2</sup>) which is several times larger than the energy generated by the PEH in each cycle ( $\propto$ V<sub>P</sub><sup>2</sup>/R<sub>P</sub>). Hence, the energy loss in the voltage conversion is amplified by this ratio, resulting in a low  $\eta_{VC}$ .

Figure 4(e) shows the post-pex simulation result for Equation (2.17). The X-axis is the proportion of  $V_P/V_{MPP}$  and Y-axis as the system overall efficiency. We know from previous sections that the efficiency should be optimized when  $V_P/V_{MPP} = 1$  in the ideal condition. However, larger  $V_P/V_{MPP}$  ratio results in larger amount of energy transfer, which significantly reduce  $\eta_{VC}$  as well as the overall efficiency. Hence, the system efficiency peaks at smaller  $V_P/V_{MPP}$  which means we track  $V_{MPP}$  at a proportion of its exact value. In such cases the overall efficiency is around 42%, mainly due to the low conversion efficiency. To further increase the overall efficiency, we could

probably use low-series-resistance (LSR) inductor or other converter topologies to reduce the conversion loss.

### 2.3.3 Flipping Phase

The advantages of SaS come from its dynamic adjustment of  $V_P$  according to the vibration waveform. However, this restricts the use of conventional rectifiers that handle negative voltages. To address this problem, we implemented a flipping phase which is a special case of the set phase. When the  $V_{MPP}$  generated in the sense phase is negative, it indicates that  $I_P$  has changed direction and  $V_{MPP}$  entered its negative half-cycle.  $V_P$  is then converted to this negative  $V_{MPP}$  as usual in the set phase but followed by a flipping operation where the connections to the two PEH terminals are swapped. As a result,  $V_P$  is flipped to the positive value and future  $V_{MPP}$  will stay positive until the next flipping happens.

The flipping phase happens twice for each vibration cycle and it ensures that  $V_P$  remains positive without use of rectifiers, as shown in Fig. 2.4 (d). Some energy loss may be incurred in the flipping operation, however, since the  $V_P$  values at the time of flipping is near zero the loss is typically negligible.

### 2.3.4 Calibration Phase

As previously mentioned in (2.16), it is necessary to tune the constant  $\sqrt{2C_T C_P R_P^2} / \Delta t$  to be 1 so that V<sub>MPP</sub> can be obtained by averaging V<sub>P</sub> and V<sub>T</sub>. Unlike C<sub>P</sub> and C<sub>T</sub>, the value of R<sub>P</sub> is difficult to measure or control, and it varies among different PEHs. Moreover, there may be mismatches on V<sub>T</sub> due to circuit non-idealities, resulting in inaccurate V<sub>MPP</sub> estimates. To compensate for this, the SaS circuit performs self-calibration by adjusting the sense phase time  $\Delta t$ automatically without knowing the values of these parameters. The calibration process is very similar to the sense phase in terms of obtaining  $V_{MPP}$ . But instead of entering the set phase, SaS converts VP to  $2V_{MPP}$  and performs another sense operation at this voltage. If the voltage  $V_T$  appears to be negative (which means  $V_P$  was over-estimated in the previous sense phase due to a  $V_T$  constant larger than 1), SaS decreases  $\Delta t$  to get a lower  $V_T$ and compensate for the larger constant. The process is repeated, and  $\Delta t$  is adjusted in a digit-step manner until there is a positive  $V_T$ , which indicates over-tuning.

The calibration phase only needs to be performed once when SaS is connected to a new PEH. Once the right  $\Delta t$  value is tuned, the SaS circuit can harvest energy from the PEH with MPPT for arbitrary vibration inputs.

### 2.4 Circuit Implementation of Sense-and-Set

### 2.4.1 Inductor-Sharing Circuit

The top-level schematic of the proposed SaS circuit is shown in Fig. 2.5. The lower part is the inductor-sharing circuit, which performs the adiabatic SaS operations. In addition to what was described in the last section, there is one additional switch pair that connects PEH with the SaS input to assist the flipping phase. By combining the 'flip' switch with the up-down converter that was previously introduced, SaS eliminates the passive rectifier which limits the efficiency for low vibration (voltage) applications.

All switches are implemented with CMOS transmission gates but with different sizing considerations. For switches with only a control purpose, minimum-sized transistors are used for low switching loss. For the switches on the power path between the PEH and the load, the transistor sizes are selected to optimize the total conduction loss and switching loss during voltage conversion. A list of detailed switch sizes and other parameters can be found in Table 2.1.

Figure 2.5: Top-level diagram for the proposed SaS circuit (greyed area indicates components that are off-chip).

| Component               | Parameters                  |  |  |  |  |

|-------------------------|-----------------------------|--|--|--|--|

| S1 - S4, S7             | W/L = 100μm/0.5μm           |  |  |  |  |

| <b>S5 - S6, S8 - S9</b> | $W/L = 0.5 \mu m/0.3 \mu m$ |  |  |  |  |

| Flip Switch             | $W/L = 200 \mu m/0.5 \mu m$ |  |  |  |  |

| $C_P, C_{P'}$           | 10nF                        |  |  |  |  |

| Ст, Ст *                | 1pF                         |  |  |  |  |

|                         | -                           |  |  |  |  |

Table 2.1: Circuit Parameters of the Sense-and-Set Circuit

<sup>\*</sup> In order to increase  $V_T$  we prefer  $C_T$  to be small. However, there is a relatively large parasitic capacitor for the off-chip inductor, so we want to keep  $C_T$  large enough to overcome the parasitic loss during the amplification. The decrease on amplify ratio is then compensated by a parallel-to-serial switched capacitor circuit.

# 2.4.2 Clock Generator

SaS clocks are implemented on-chip and divided into three domains:

- 1. The MPPT clock (fMPPT) defines the frequency of SaS refreshing its VMPP value by performing SaS operations. This clock frequency, which is denoted by fMPPT, is usually in the 1 KHz range, tens of times higher than the vibration frequency.

- 2. The digital counter clock (fCNT) is related to the sense phase time  $\Delta t$ . Since  $\Delta t = N_{CNT}/f_{CNT}$ , a larger fCNT means finer control over  $\Delta t$  but higher power overhead. Hence the clock frequency is choses to be 100 kHz.

- 3. The comparator clock (fCOMP) runs the clocked-comparator and controls the switches for voltage conversion and is implemented to be 10 MHz in order to achieve high power efficiency by decreasing timing errors.

For low power operation, the three clocks are generated with the 5-stage ring oscillators (ROs) proposed by [38] to achieve constant energy-per-cycle across wide frequency range. As shown in Fig. 2. 6(a), the ROs consist of leakage-based inverters with an additional low- $V_{th}$  (LVT) device pair in the middle. When the input voltage flips, the leakage path through the LVT latch controls the delay of output toggling and determines the oscillation frequency. Further tuning on the frequency can be achieved by adding a current path with the parallel transistors. The voltage to bias the parallel transistors ( $V_{BP}$  or  $V_{BN}$ ) are generated by diode-connected transistors and selected with a 64-to-1 Multiplexer.

Among the three clocks,  $f_{MPPT}$  needs to be always-on in order to track  $V_{MPP}$  in real time. It will result in large power overhead if we run the oscillator at 10MHz and divide it to generate  $f_{MPPT}$ . Instead, we implemented three separate ROs in SaS, and the fast ROs ( $f_{CNT}$  and  $f_{COMP}$ ) are only awoken when their controlled blocks are used. Fig.6 (b) shows the duty-cycled clocks for the counter and comparators.

Figure 2.6: (a) Circuit schematic of the 5-stage ring oscillator and its biasing circuit, (b)  $f_{CNT}$  and  $f_{CMOP}$  that run at higher frequency are awoken by  $f_{MPPT}$  at a specific time, and (c) the 2-stage comparator schematic.

### 2.4.3 Pulse Generation and the Clock Counter

The sequential SaS operation is hard-coded in the SaS, and its order is determined by the pulse generation circuit. The circuit takes  $f_{MPPT}$  as input, propagating its rising edge through multiple delay stages, and generates pulses that activate different switches in SaS. The delay cells are similar to what is used in clock generation, with specific bias voltage to control its delay and the pulse width.

Especially, the pulse width that defines  $\Delta t$  cannot be hard-coded as it needs to be adjustable during the calibration phase. So, we implemented a digital counter that counts  $f_{CNT}$  until it reaches a given number N. Then we have

$$\Delta t = \frac{N}{f_{CNT}} \tag{2.18}$$

where  $f_{CNT}$  determines the resolution of  $\Delta t$ , and N gives the range. The value of N is stored in another counter-like structure that is kept tuned during the calibration phase.

# 2.4.4 Comparators

The SaS circuit performs voltage conversion when it changes V<sub>P</sub>. The voltage conversion efficiency  $\eta_{VC}$ , which dominates the overall SaS efficiency as we discussed, is affected by the timing error of the switches. To determine the correct timing signals for the switches, we implemented two comparators in SaS as shown in Fig. 2. 6(c). The first one compares V<sub>P</sub> with the target voltage and produces turn-off signals when V<sub>P</sub> has been converted to the target voltage. The second one performs cross-zero detection for the inductor L's current by measuring its terminal voltage and helps with the energy recycling from L.

In order to control the switching activities for voltage conversion while maintaining high efficiency, the comparator clock signal  $f_{COMP}$  needs to be approximately 10MHz to reduce timing error. We implemented  $f_{COMP}$  in a highly duty-cycled manner where only when a switching activity begins, the fastest oscillator is enabled and provides clocks to the comparator. Since the switching time is only a small portion of the total sense-and-set time, both the comparator and the corresponding oscillator will be idle for most of the time. By this technique we reduced the power consumption of timing control from 14.5 $\mu$ W to 151nW, as shown in Section 2.5.

### 2.4.5 Switch Controller and Switch Drivers