### N-polar GaN HEMT with HfO2 as Gate Dielectric for mm-wave Applications

by

Subhajit Mohanty

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2023

**Doctoral Committee:**

Assistant Professor Elaheh Ahmadi, Chair Professor Cagliyan Kurdak Professor Wei Lu Professor Zetian Mi Professor Umesh K. Mishra Subhajit Mohanty

subhajit@umich.edu

ORCID iD: 0000-0002-1469-5363

© Subhajit Mohanty 2023

## Dedication

To my dad, mom, my wife Ashley and my cat Olivia.

#### Acknowledgements

#### "If I have seen further, it is by standing on the shoulders of giants."

- Sir Isaac Newton

It has been a wonderful five years in the WBME lab. I would like to express my deepest appreciation to my advisor, Prof. Elaheh Ahmadi, for her unwavering support and guidance. I remember the first day when I joined her lab with little knowledge of fabrication, GaN or HEMT. She taught me the concepts and guided me through the process from scratch and after five years I feel much more confident in the field of GaN electronics. She has helped me evolve not only as a researcher, but also as a holistic person. I have been truly fortunate to have Elaheh as my advisor. This endeavor would not have been possible without the inspiration and help of Prof. Umesh Mishra. His insightful suggestions for my research results helped me approach problems in a novel way. I am incredibly grateful to Prof. Wei Lu for introducing me to many new devices and concepts in course EECS 521. I want to thank Prof. Zetian Mi for his encouragement and collaboration work in ScAlN and DLTS. Many thanks to Brian, Onur, and Xun at Prof. Mishra's group for answering my fabrication questions, which helped me establish the fabrication process flow here at UMich. I could not thank Matt Guidry more for guiding me through the network parameter analyzer measurement setup.

I cherish the moments I spent with my labmates at UMich. Kam helped me with regrowth in my fabrication process. Though it is just a small part of the collaboration, it is such a crucial step in my HEMT device. Many thanks to Sandra for preparing all the documents for DC testing lab. I

have always enjoyed the time I spent working with Ashley, Oguz, Stefan, Irfan, Xin, Harsh, Ethan, Christopher, Tomas in cleanroom where I learned many new things at each step of my life. Ashley trained me on various clean room tools and taught me the basics of fabrication. She helped me navigate the initial years of academic life smoothly. Thank you Xin, Ruby and Wen for keeping the dude-vibe in our group. I also learnt a lot working with Prof. Mi's lab members, Ping, Ding, and Ayush.

Lurie Nanofabrication Facility (LNF) has been an important part of my PhD journey for the past five years. The staff members were extremely helpful. There were situations where I had to contact them at night and received a response from the staff. Special thanks go to Shawn for helping me a lot with lithography on stepper and plasma etch with Lam tool. I would also like to thank Matt for helping me with ALD and Vishva for helping me with e-beam lithography.

I am also extremely grateful to the ECE staff, especially Kristen, who has helped me with all the administrative procedures. Radlab staff Michelle and Kim were the most efficient people I have worked with, and they always provided me with fast and accurate solutions to my needs. I also thank John for providing me with an opportunity to represent as an ECE student ambassador.

I would to thank the primary funding agency Office of Naval Research for supporting my research financially. I would also like to thank Rackham which has also extended financial support for conference and fellowships at the time of need.

I would also like to thank my friends from India who has made my stay in the US wonderful. Saket has been a constant part of my life for the past five years. Thanks to Nagesh, Mahitosh and Debu for treating me delicious Indian food at ICC coop.

I would like to express my deepest gratitude to my wife Ashley and cat Olivia who have been always there by my side during PhD journey. Our cat Olivia was a great emotional booster during

iv

the Ph.D.. Lastly, I cannot be more thankful to my parents who have been there with me at each step of my life. Their inspiration and blessings have established me as I am today.

| Table of Contents Dedication               | ii  |

|--------------------------------------------|-----|

|                                            |     |

| Acknowledgements                           |     |

| List of Tables                             | ix  |

| List of Figures                            | x   |

| Abstract                                   | xiv |

| Chapter 1 Introduction                     | 1   |

| 1.1 RF Wireless Communication              | 1   |

| 1.2 Key Performance Index                  |     |

| 1.2.1 High $f_T$ and $f_{max}$             |     |

| 1.2.2 Power and Efficiency                 |     |

| 1.3 Why GaN                                | 5   |

| 1.3.1 High Frequency of Operation          | 5   |

| 1.3.2 High Power and Efficiency            | 6   |

| 1.3.3 Less Design Complexity               | 7   |

| 1.3.4 Wide Temperature Range               |     |

| 1.3.5 Reliability and Robustness           |     |

| 1.4 Why N-polar                            |     |

| 1.4.1 Strong Confinement from Back-barrier |     |

| 1.4.2 Improved Scaling                     |     |

| 1.4.3 Improved Ohmic contact               |     |

| 1.4.4 GaN Cap in Access Region             |     |

| 1.4.5 Reduced Leakages                     |     |

| 1.4.6 Comparison of Device Performance                                               | 17 |

|--------------------------------------------------------------------------------------|----|

| 1.5 Dissertation Overview                                                            | 19 |

| Chapter 2 Investigation and Optimization of HfO2 Gate Dielectric on N-polar GaN      | 21 |

| 2.1 Introduction                                                                     | 21 |

| 2.1.1 Why HfO <sub>2</sub>                                                           | 21 |

| 2.1.2 Characterization Methods of Interface States                                   | 23 |

| 2.1.3 Chapter Overview                                                               | 26 |

| 2.2 As-deposited HfO <sub>2</sub> on GaN HEMT Epi-structure                          | 26 |

| 2.2.1 Device Fabrication                                                             | 26 |

| 2.2.2 Results and Discussion:                                                        | 28 |

| 2.3 HfO <sub>2</sub> Characterization on GaN MOSCAPs                                 | 32 |

| 2.3.1 Device Fabrication                                                             | 32 |

| 2.3.2 Results and Discussion                                                         | 33 |

| 2.4 Conclusion                                                                       | 40 |

| Chapter 3 N-polar GaN MIS-HEMT with High-k ALD HfO2 as Gate Dielectric               | 42 |

| 3.1 Introduction                                                                     | 42 |

| 3.2 Device Fabrication                                                               | 43 |

| 3.3 Results and Discussion                                                           | 44 |

| 3.4 Conclusion                                                                       | 49 |

| Chapter 4 N-polar Deep Recessed (NPDR) HEMT with HfO <sub>2</sub> as gate dielectric | 50 |

| 4.1 Introduction                                                                     | 50 |

| 4.2 Device fabrication                                                               | 51 |

| 4.3 Results and Discussion                                                           | 53 |

| 4.4 HfO <sub>2</sub> Thickness series                                                | 56 |

| 4.5 Conclusion                                                                       | 60 |

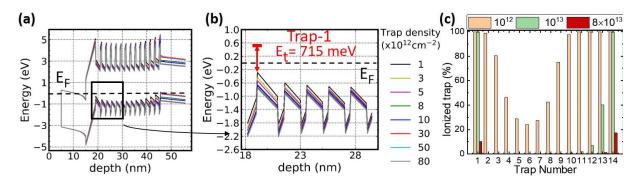

| Chapter 5 Design of Ultra-scaled-channel N-polar GaN HEMTs with High Charge Density: A Study of Hole Traps and Their Impact on Charge Density in the Channel |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 Introduction                                                                                                                                             |

| 5.2 Simulation Framework                                                                                                                                     |

| 5.3 Results and Discussion                                                                                                                                   |

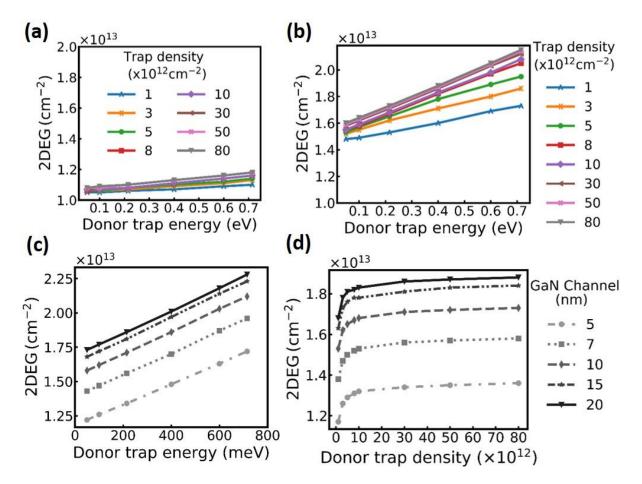

| 5.3.1 Hole Traps and Their Impacts on 2DEG Density                                                                                                           |

| 5.3.2 Estimation of Hole Trap Density and Energy Level at AlN/GaN NPI                                                                                        |

| 5.3.3 Si Doping to Prevent Hole Trap Ionization                                                                                                              |

| 5.4 Conclusion74                                                                                                                                             |

| Chapter 6 Future Work                                                                                                                                        |

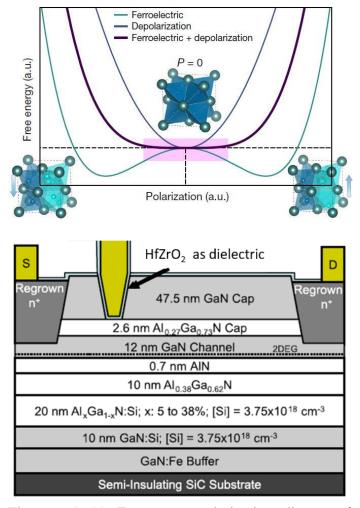

| 6.1 N-polar Deep Recessed HEMT with HfZrO <sub>2</sub> as gate dielectric                                                                                    |

| 6.2 Improvement in HfO <sub>2</sub> leakage:                                                                                                                 |

| 6.3 Regrown Ohmic contact improvement:                                                                                                                       |

| 6.4 Scaled HEMTs for high frequency application:                                                                                                             |

| Bibliography                                                                                                                                                 |

## List of Tables

| Table 1.1 Material properties of various materials [1].                                        |

|------------------------------------------------------------------------------------------------|

| Table 2.1. Summary of the techniques that were employed for surface preparation, in-situ       |

| pretreatment, ALD deposition, and post-deposition annealing                                    |

| Table 2.2 Effect of in-situ TMA/N2 plasma on various bulk and interface characteristics        |

| Table 2.3. Effect of Rapid thermal annealing ambience on bulk and interface characteristics 35 |

| Table 2.4 Effect of various surface cleaning methods on bulk and interface characteristics 38  |

# List of Figures

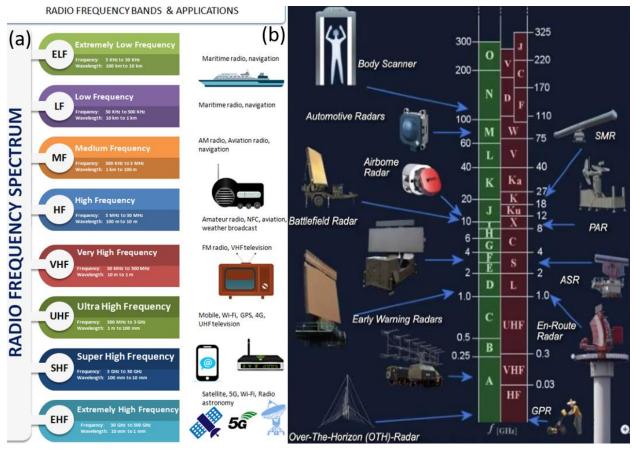

| Figure 1.1 RF frequency range and various applications (a) commercial (b) military applications.                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

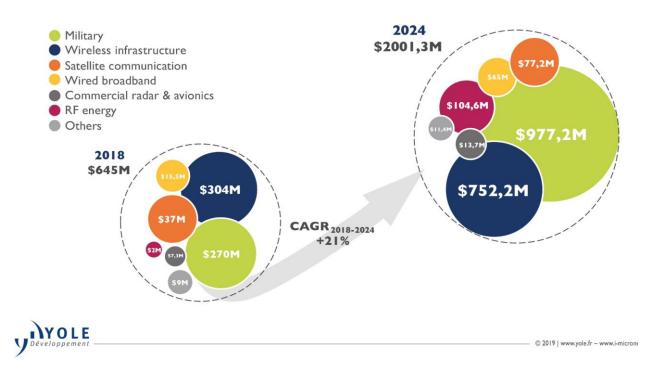

| Figure 1.2 Projected market growth for RF front end                                                                                                                                                                                                                                                                                                                                                             |

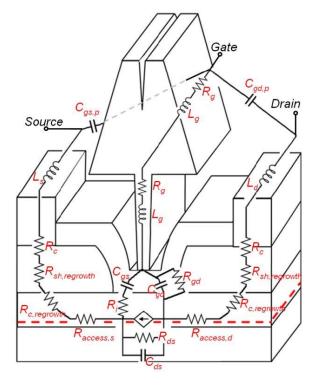

| Figure 1.3 Schematic of HEMT with various device parameters                                                                                                                                                                                                                                                                                                                                                     |

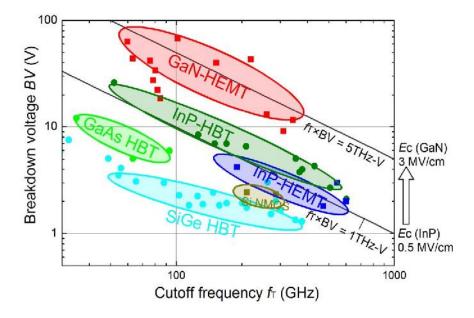

| Figure 1.4 Johnson Figure of Merit (JFoM) for various material systems [1]5                                                                                                                                                                                                                                                                                                                                     |

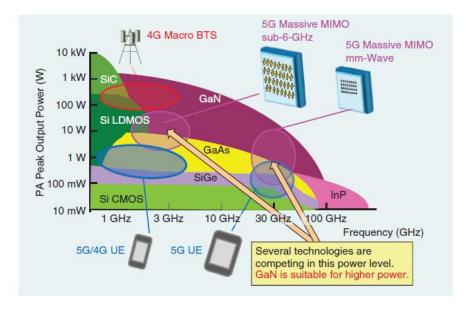

| Figure 1.5 A comparison of output power vs frequency for different material systems [5]                                                                                                                                                                                                                                                                                                                         |

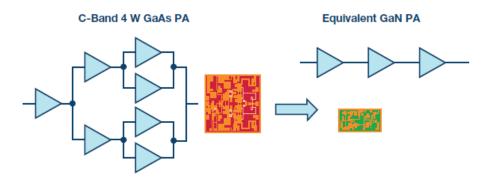

| Figure 1.6 A comparison of multistage GaAs vs GaN Power amplifier (PA) [6]7                                                                                                                                                                                                                                                                                                                                     |

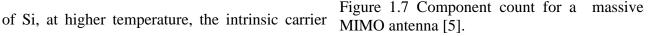

| Figure 1.7 Component count for a massive MIMO antenna [5]                                                                                                                                                                                                                                                                                                                                                       |

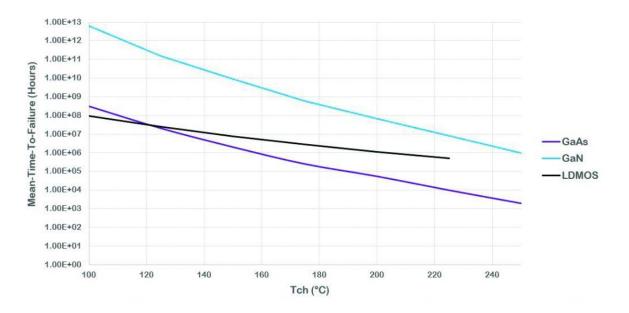

| Figure 1.8 Technology comparison of Mean-Time-To-Failure versus Channel Temperature. https://www.mpdigest.com/2019/10/24/gan-on-sic-is-driving-advances-in-radar-applications/9                                                                                                                                                                                                                                 |

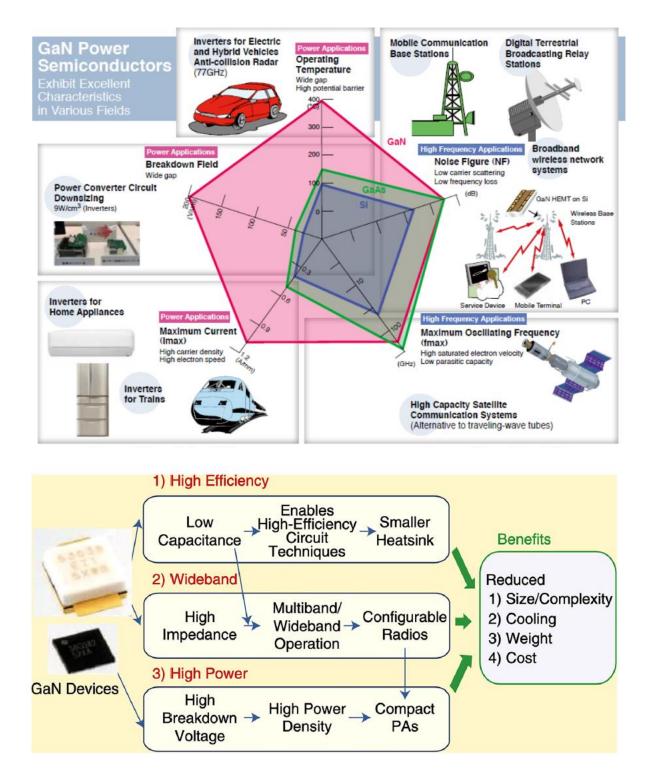

| Figure 1.9 (a) Importance of various material parameters for various commercial applications [8] (b) Impact of GaN device Characteristics on system level advantages [9] 10                                                                                                                                                                                                                                     |

| Figure 1.10 GaN Wurtzite crystal structure in (a) Ga-face (b) N-face, with spontaneous polarization vector                                                                                                                                                                                                                                                                                                      |

| Figure 1.11 Epi-structure, charge profile, and band diagram of typical Ga-polar (left) and N-polar (right) hetero-structures. The 2DEG forms below the barrier in Ga-polar. This is in contrast with N-polar hetero-structures in which the 2DEG forms on top of the barrier and leads to better confinement of the 2DEG, more gate control specially in scaled HEMTs, and lower ohmic contact resistance [17]. |

| Figure 1.12 (a) Band diagram of GaN/InN regrown region in N-polar GaN HEMT. A large bandoffset of 1eV exists at GaN/InN interface. (b) band diagram of GaN/gradedInGaN/InN regrown region [28]                                                                                                                                                                                                                  |

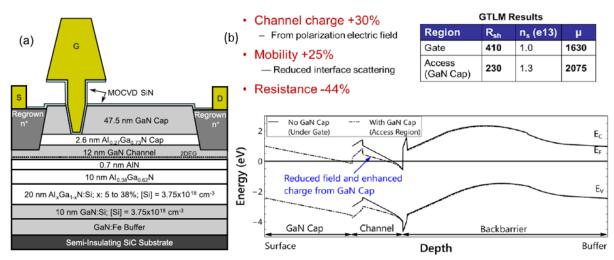

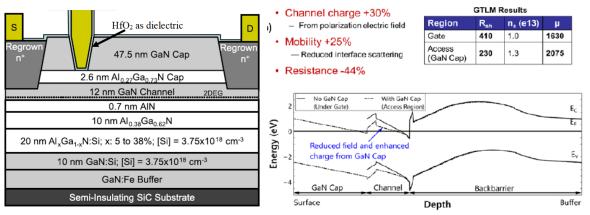

| Figure 1.13 (a) Device cross-sectional schematic (not drawn to scale) and epitaxial layer profile of the N-polar deep recess (NPDR) MISHEMT with the foot-gate self-aligned to the GaN cap recess. (b) Energy band diagram comparing the vertical profiles under the gate electrode as compared to the access region with the addition of a GaN cap layer                                                       |

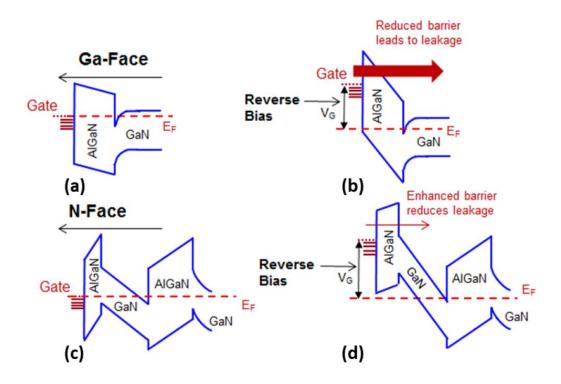

| Figure 1.14 A schematic of a Ga-Polar HEMT band diagram at (a) equilibrium and (b) with a reverse gate-drain voltage applied. (c) and (d) give the energy band diagram of a N-Polar HEMT                                                                                                                                                                                                                        |

| with a thin AlGaN top-barrier at equilibrium and at a reverse gate-drain voltage bias, respectively [31]                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

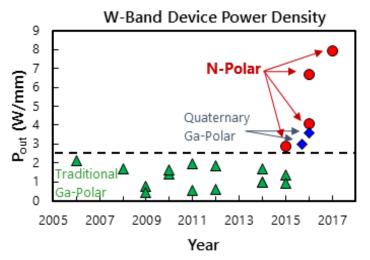

| Figure 1.15 W-Band output power density of various GaN device technologies over time.<br>Traditional Ga-polar AlGaN/GaN HEMTs have saturated around 2 W/mm while N-polar GaN has<br>recently demonstrated 7.94 W/mm [17]                                                                                                                                          |

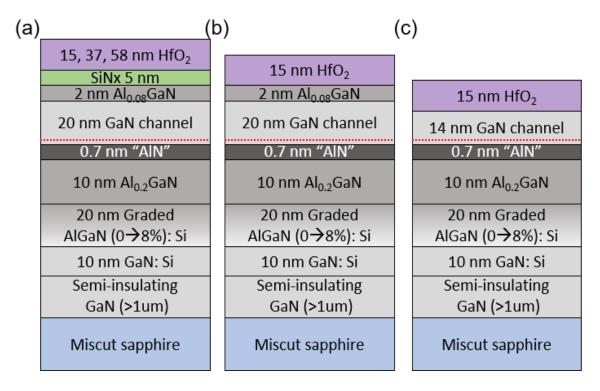

| Figure 2.1 Schematic of the structures studied in this work (a) HfO <sub>2</sub> on SiN (b) HfO <sub>2</sub> on AlGaN after removal of SiN and (c) HfO <sub>2</sub> on GaN after removal of SiN and AlGaN cap layer                                                                                                                                               |

| Figure 2.2CV profile measured at different frequencies on MOSCAP-C with 15nm-thick HfO2which (a) was not annealed and annealed for (b) 1min and (c) 5 min at 400°C in N2                                                                                                                                                                                          |

| Figure 2.3 CV profiles measured at 1 MHz on MOSCAPs with various HfO <sub>2</sub> thicknesses 29                                                                                                                                                                                                                                                                  |

| Figure 2.4 Capacitance measured at 0 V versus HfO <sub>2</sub> thickness                                                                                                                                                                                                                                                                                          |

| Figure 2.5 CV profile measured at different frequencies on (a) MOSCAP-B and (b) MOSCAP-C.                                                                                                                                                                                                                                                                         |

| Figure 2.6 Fabrication process flow of HfO <sub>2</sub> /N-polar GaN MIS structure                                                                                                                                                                                                                                                                                |

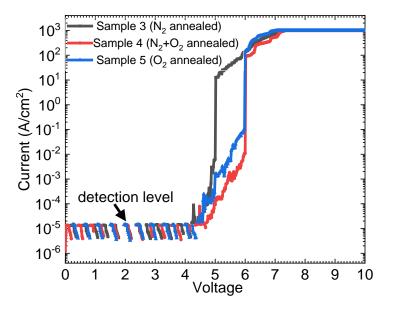

| Figure 2.7 Forward bias Current-Voltage (CV) characteristics of $N_2$ annealed (Sample 3), $N_2+O_2$ annealed (Sample 4) and $O_2$ annealed (Sample 5)                                                                                                                                                                                                            |

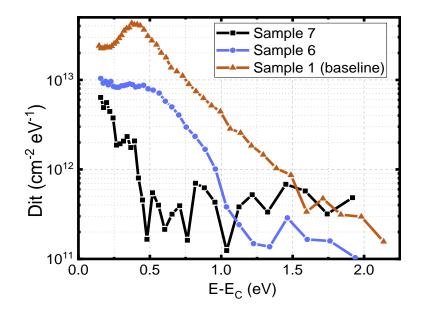

| Figure 2.8 Density of states $(D_{it})$ profile as the function of energy for Sample 1 (baseline), 6 and 7 (UV + Ozone)                                                                                                                                                                                                                                           |

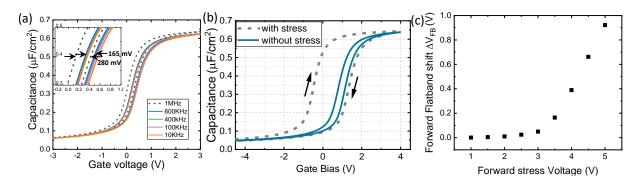

| Figure 2.9 (a) C-V hysteresis (b) HF C-V for fast and slow trap estimation (c) Forward flatband voltage shift for Sample-7                                                                                                                                                                                                                                        |

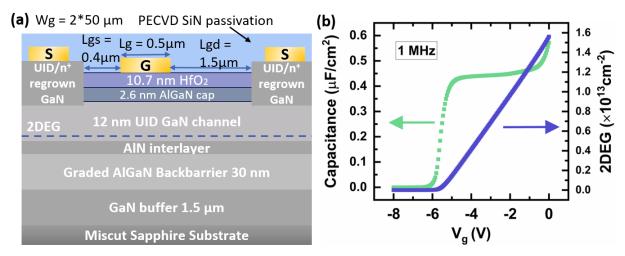

| Figure 3.1 (a) Schematic diagram of N-polar MIS-HEMT with 10.7 nm thick $HfO_2$ as gate dielectric (b) C-V characteristics (green) and 2DEG charge density (green) measured on MOSCAP with 100 $\mu$ m diameter, the blue curve shows the 2DEG concentration with gate bias voltage 42                                                                            |

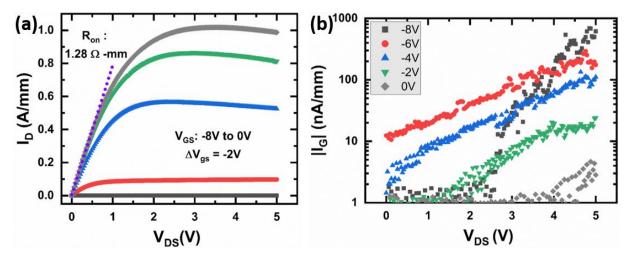

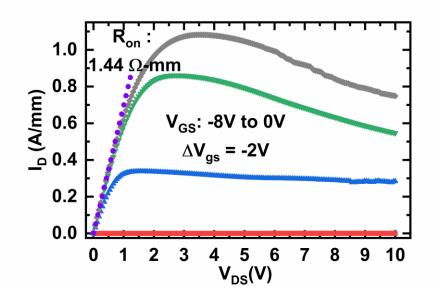

| Figure 3.2 (a) Output characteristics and (b) Corresponding gate leakage current for Vgs from -8 V to 0 V with 2 V increments. The extracted Ron is 1.28 $\Omega$ -mm at Vgs = 0V                                                                                                                                                                                 |

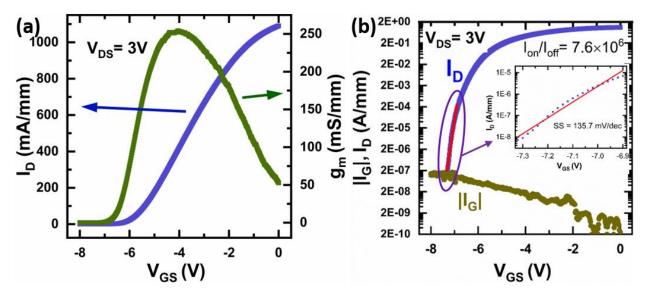

| Figure 3.3(a) Transfer characteristics (blue) and trans-conductance (green) at $V_{DS} = 3 V$ (b) drain current and gate leakage in semi-log scale. The subthreshold slope is 135.7 mS/dec                                                                                                                                                                        |

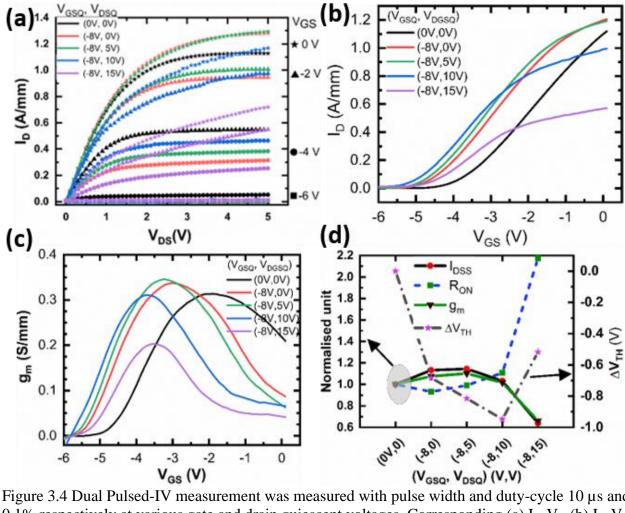

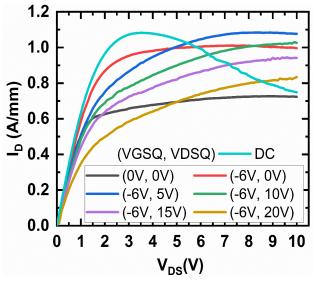

| Figure 3.4 Dual Pulsed-IV measurement was measured with pulse width and duty-cycle 10 $\mu$ s and 0.1% respectively at various gate and drain quiescent voltages. Corresponding (a) I <sub>D</sub> -V <sub>D</sub> (b) I <sub>D</sub> -V <sub>G</sub> (c) g <sub>m</sub> and (d) normalized I <sub>DSS</sub> , R <sub>ON</sub> , g <sub>m</sub> , $\Delta V_{TH}$ |

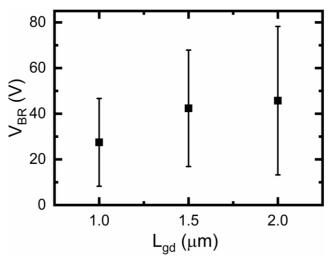

| Figure 3.5 Breakdown voltage (BV) of device with different gate-drain distance (L <sub>gd</sub> ) with various gate lengths and corresponding error in BVs                                                                                                                                                                                                        |

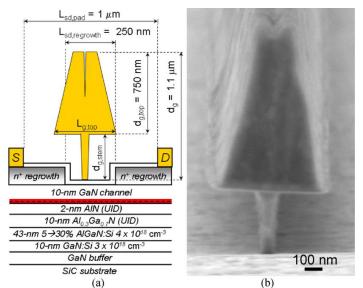

Figure 4.1 Device cross-sectional schematic and epitaxial layer profile of the N-polar deep recess (NPDR) with HfO<sub>2</sub> as gate dielectric (b) Energy band diagram comparing the vertical profiles under the gate electrode as compared to the access region with the addition of a GaN cap layer 50

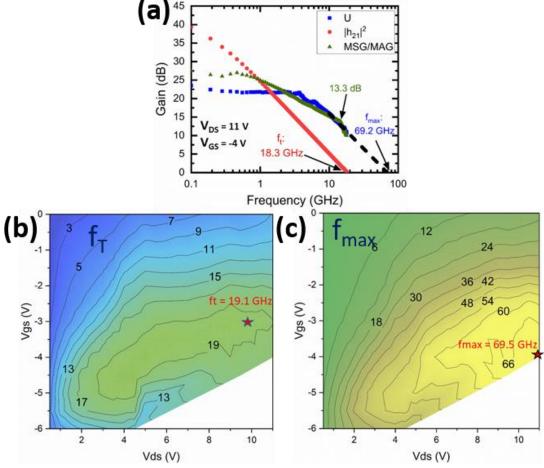

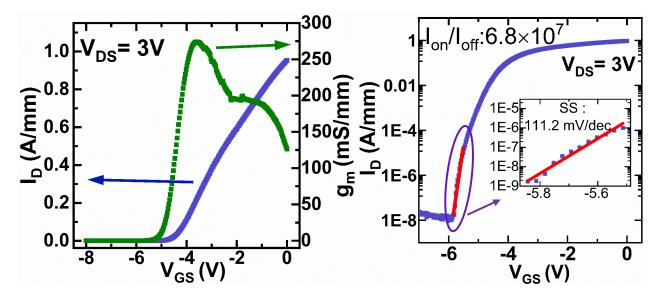

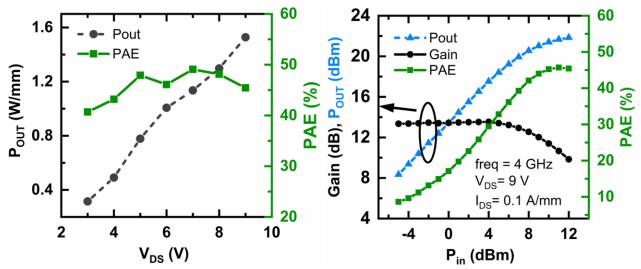

Figure 4.4 (a) RF performance HEMT, Contour plots of fT and fmax w.r.t. VGS and VDS ...... 52

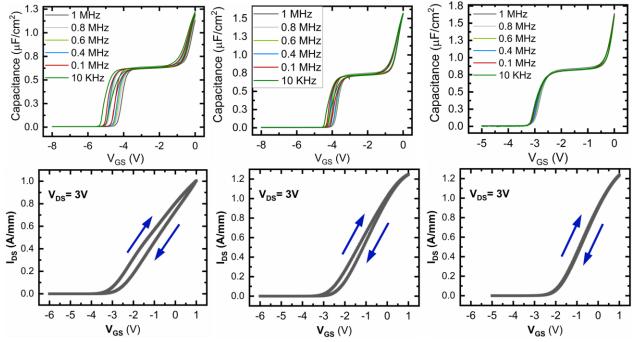

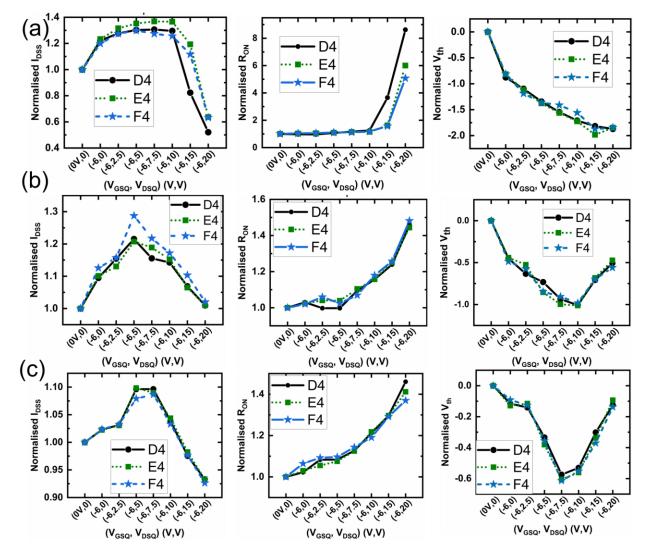

Figure 4.8 Normalized  $I_{DSS}$ , normalized dynamic Ron, and Vth shift was measured for three devices D4, E4, F4 which has  $1\mu$ m,  $1.5\mu$ m,  $2\mu$ m gate-to-drain distance for three samples with three different gate dielectric thickness (a)10.1nm, (b)7.1nm, (c)4.4nm. All the parameters were almost same indicating that traps in the gate-to-drain region does not cause DC-RF dispersion 57

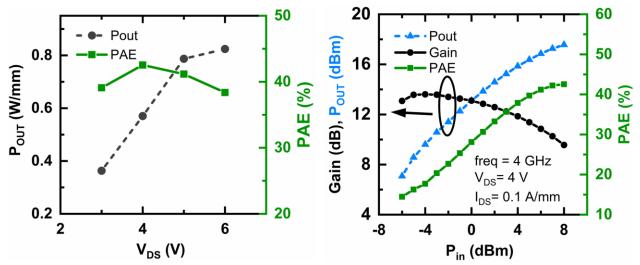

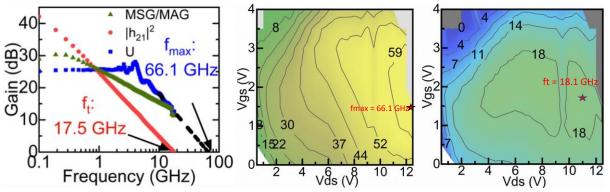

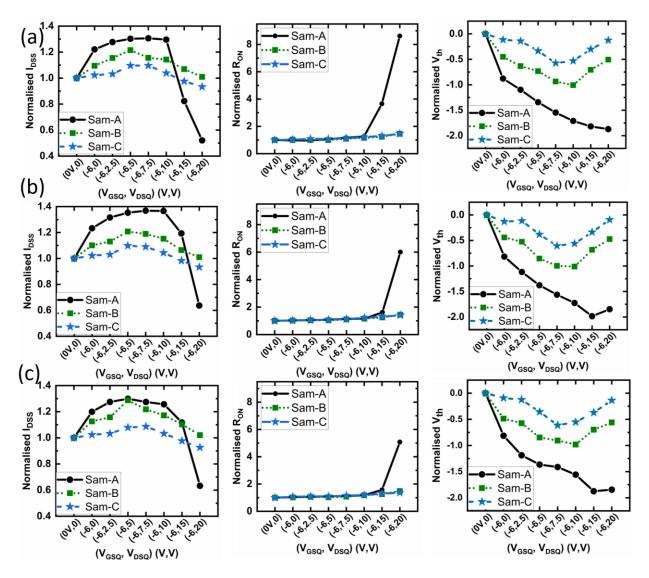

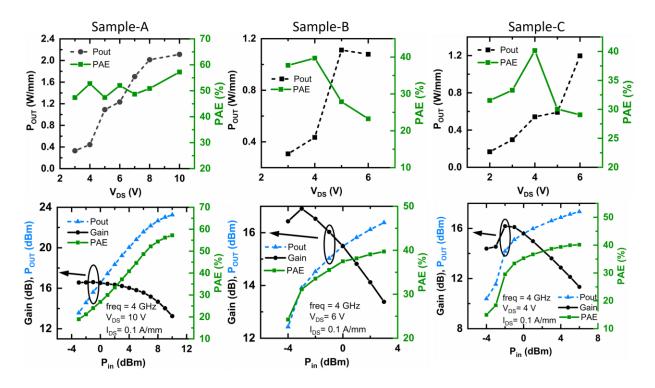

Figure 4.10. Large signal performance at 4 GHz for three samples (Sample-A, B & C) with three different gate dielectric thickness 10.1nm, 7.1nm, 4.4nm respectively for same devices. Dependence Pout and PAE on VDs and Power performance at different VDs, IDSS = 100 mA/mm.59

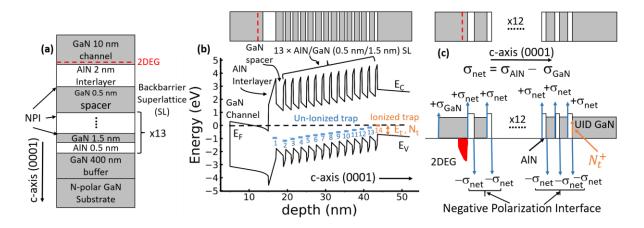

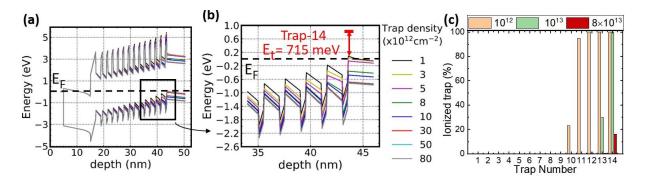

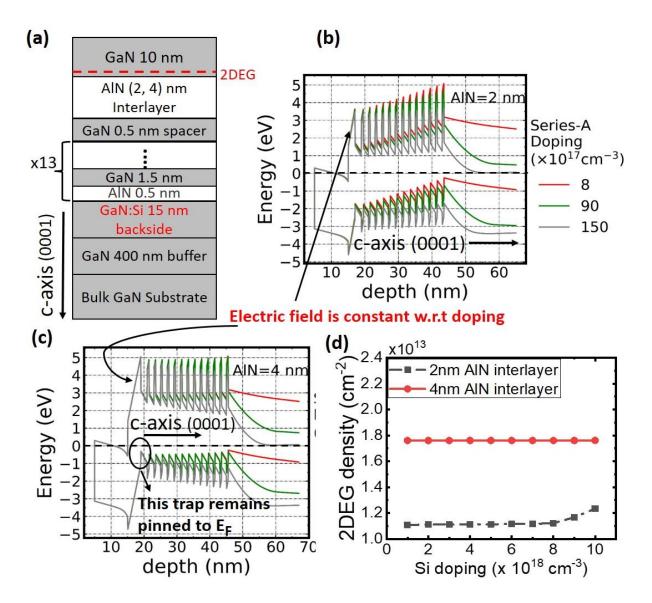

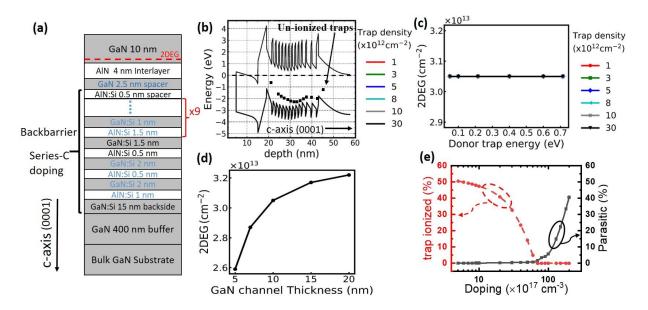

Figure 5.2 (a) Band diagrams for epi-structure described in Fig. 4.1 (a) with 2nm-thick AlN interlayer assuming hole trap with energy of 715 meV and different trap densities at NPIs for barrier height of 0.3 eV at GaN channel surface, (b) magnified band diagram near VB at barrier-

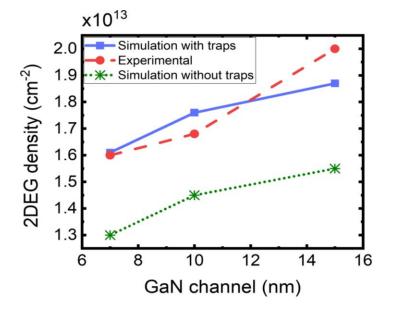

Figure 5.5 2DEG density as a function of GaN channel experimentally measured (red circles), simulated including hole traps with 0.3 eV barrier height, density and energy of  $3 \times 10^{13}$  cm<sup>-2</sup> and 280 meV w.r.t. valence band (blue squares), and simulated without including traps (green stars).

#### Abstract

N-polar GaN-based HEMTs have shown tremendous promises for high-power highfrequency (30-110 GHz) applications due to several advantages such as better pinch-off, low ohmic contact and better gate control. To further achieve higher frequency of operation while maintaining high power, the gate-to-channel distance and gate length need to be scaled down simultaneously to avoid short-channel effects (SCEs). However, extreme scaling of gate-tochannel distance will result in higher gate leakage current which requires thick dielectrics and inturn reduces gate-to-channel distance and gate control. This requires high-k dielectric as gate insulator whose small effective oxide thickness (EOT) can suppress gate leakage while maintaining good gate control.

This dissertation primarily is focused on developing HfO<sub>2</sub> as gate dielectric for ultra-thin N-polar GaN HEMT application.

In the first part of the dissertation, the impact of various surface cleaning, in-situ atomic layer deposition (ALD) pre-treatment, ALD deposition method and post-deposition annealing ambiance on interface properties of HfO<sub>2</sub>/ N-polar GaN was studied via UV-assisted C-V and current-voltage characterization methods. A combination of the BHF and piranha cleaning with UV-ozone pretreatment followed by thermal HfO<sub>2</sub> improved the interface between HfO<sub>2</sub> and N-polar GaN quality significantly. Further annealing in O<sub>2</sub> increased the breakdown voltage, and reduced the interface states compared to annealing in N<sub>2</sub>. The lowest average interface trap density was achieved to be  $1.64 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> with breakdown field of 3.14 MV/cm.

All the processes developed previously were used for fabrication of planar N-polar GaN MIS-HEMTs. The dual pulsed-IV measurements suggest that there are two competing mechanisms at play during device operations resulting in anti-dispersion and dispersion at the same time. Additionally, to reduce the DC-RF dispersion, N-polar deep recess (NPDR) HEMTS with HfO<sub>2</sub> as gate dielectric have been explored. BCl<sub>3</sub>/SF<sub>6</sub> selective dry etch was developed to realize deep-recess structure with thin AlGaN cap as etch stop layer. The HEMTs exhibited a peak saturation current of 1.1A/mm with  $f_T$ =18.1GHz and  $f_{max} = 66.1$  GHz. The HEMTs biased in class AB at  $V_{DS}$ =9 V and  $I_{DS}$ =100 mA/mm at 4 GHz frequency demonstrated a max output power of 1.53 W/mm with associated PAE of 45.4%. Pulsed IV measurements reveal that the deep recess structure did not exhibit DC-RF dispersion from surface traps present in drain access region. Rather the traps present in the gate dielectric cause dispersion which has been shown to depend on the thickness of the dielectric. In fact, the dispersion is less than 10% at a very thin dielectric of 4.4 nm.

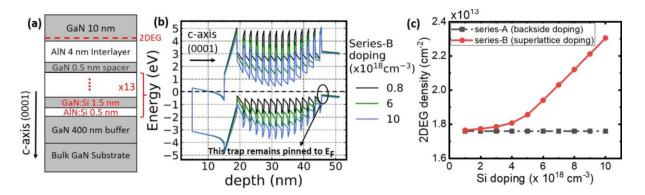

It is reported that interfacial nitrogen vacancies at negative polarization interface (NPI) were the source of these hole/donor traps. Using the Silvaco TCAD simulation platform, for the first time, the effect of hole traps density and energy level on 2DEG density in N-polar HEMT structures was studied. Comparing the calculated 2DEG density with that of experimental results, hole trap density and activation energy were estimated. The results showed that Si doping in both the barrier and at barrier-buffer interface effectively neutralizes the traps present throughout the epi-structure while simultaneously modulating the 2DEG charge density. Moreover, an epi-structure was designed to enable aggressive scaling of the channel (5nm-thick) in N-polar GaN HEMTs while maintaining a large 2DEG density of approximately  $2.6 \times 10^{13}$  cm<sup>-2</sup> with minimal parasitic.

XV

## Chapter 1 Introduction

#### **1.1 RF Wireless Communication**

RF wireless communication is touching every aspect of life such as health, communication, and defense. In the military defense industry, radars in early warning system, counter measure warfare, etc. use a wide range of frequency spectrum from MHz to GHz. Terahertz imaging is used in food and plastic inspection to complex imaging machines used for health monitoring. Mobile communication base stations operate in lower GHz spectrum (~3.5 -25 GHz) with demand to go

Figure 1.1 RF frequency range and various applications (a) commercial (b) military applications.

towards higher frequency. With telecommunication traffic data being projected to grow significantly higher by early 2030, high resolution, faster data and low latency is the need of the hour. This in turn requires advanced electronics with higher frequency of operation and wide bandwidth. Many such electronics operate over a wide range of frequency spectrum and bandwidth and are rapidly evolving. For instance, only a few years ago, the telecommunication industry was debating the feasibility of 5G. In few years span, not only the standards has been decided, but also prototypes and field trials have already been demonstrated successfully. Now it is in use en-masse for commercial mobile communication. There is not a shred of doubt that the next decade belongs to 5G and RF. However, this poses several design challenges to the RF and device engineer. Electronics need to be compatible with a wide range of frequency and bandwidth. Power, efficiency, bandwidth, and speed all need to be taken into account. Emerging segments such as

## GaN RF device market size forecast 2018-2024

(Source: RF GaN Market: Applications, Players, Technology and Substrates 2019 report, Yole Développement, 2019)

Figure 1.2 Projected market growth for RF front end.

satellite communication (SatCom) and consumer handsets present new opportunities as well as challenges. According to the market research, by Yole Développement (Yole), the power amplifier module is poised to grow from US\$5.4 billion in 2019 to US\$8.9 billion by 2025 with CAGR of 11%. The overall RF front end connectivity market will grow to US\$25.4 billion from US\$15 billion with CAGR of 11%.

#### **1.2 Key Performance Index**

### 1.2.1 High fT and fmax

Current gain cutoff- frequency  $(f_T)$  [2] and power-gain cutoff frequency  $(f_{max}$  [3]) are two important parameters for RF application. These two in turn, depend on many device parameters (Fig 1.3). To improve the frequency of operation, it is necessary to increase the trans-conductance of amplifier while reducing parasitic resistances and capacitances.

Figure 1.3 Schematic of HEMT with various device parameters [116].

$$f_{T} = \frac{g_{m}}{2\pi \left\{ \left( C_{gs} + C_{gd} \right) \left( 1 + \frac{R_{s} + R_{d}}{R_{ds}} \right) + C_{gd} \cdot g_{m} \cdot (R_{s} + R_{d}) \right\}} \approx \frac{v_{s}}{2\pi I}$$

$$f_{max} = \frac{\frac{g_{m}}{2\pi (C_{gs} + C_{gd})}}{\sqrt{\frac{4}{R_{ds}} \left( R_{g} + R_{s} + R_{i} \right) + 8\pi \cdot f_{T} \cdot C_{gd} \left( 2R_{g} + R_{s} + R_{i} \right)}}$$

### **1.2.2** Power and Efficiency

RF transistors should be able to produce high power in the intended frequency of operation. For instance, for radar applications, the power requirement depends on the fourth power of distance. Power density is another parameter which impacts the device dimension and subsequent cost. Efficiency is another parameter which is essential for component count and thermal management of the entire system.

|                                                                                 | Si   | GaAs | GaP  | 4H-SiC | Diamond | GaN  | AlN  |

|---------------------------------------------------------------------------------|------|------|------|--------|---------|------|------|

| Band gap (Eg) (eV)                                                              | 1.1  | 1.4  | 2.3  | 3.2    | 5.5     | 3.4  | 6.2  |

| Thermal                                                                         |      |      |      |        |         |      |      |

| Conductivity                                                                    | 1.5  | 0.5  | 1.1  | 4.9    | 20      | 1.3  | 3.9  |

| (W/cm.K)                                                                        |      |      |      |        |         |      |      |

| Melting Point (K)                                                               | 1683 | 1513 | 1740 | 2830   | 3773    | 2791 | 3273 |

| Electron Saturation<br>Velocity (cm/s)                                          | 1    | 2    | 1.25 | 2      | 2.7     | 2.5  | 1.4  |

| Electron mobility<br>(cm <sup>2</sup> /V.s)                                     | 1400 | 8500 | 350  | 950    | 2200    | 1000 | 135  |

| Hole mobility<br>(cm <sup>2</sup> /V.s)                                         | 600  | 400  | 100  | 120    | 1600    | 30   | 14   |

| Dielectric Constant                                                             | 11.8 | 12.5 | 11.1 | 9.7    | 5.5     | 8.9  | 8.5  |

| Breakdown Field $(E_C)$ (MV/cm)                                                 | 0.3  | 0.6  | 1    | 2      | 10      | 2.6  | 2    |

| JFOM $\left(\frac{v_{sat} \cdot E_C}{2\pi}\right)$<br>(normalized to Si)        | 1    | 0.93 |      | 14     |         | 17   |      |

| BFOM $(\frac{\varepsilon_s \cdot \mu \cdot E_g^3}{2\pi})$<br>(normalized to Si) | 1    | 16   |      | 430    |         | 990  |      |

Table 1.1 Material properties of various materials [4].

#### 1.3 Why GaN

So the question is: which material system will dominate the RF market? Gallium Nitride has surfaced as a candidate for high power and high frequency applications due to its unique properties, including a large bandgap of 3.4 eV, large breakdown electric field of 2.6 MV/cm, and high electron mobility and saturation velocity (**Table 1.1** [4]) which provides following advantages:

#### **1.3.1 High Frequency of Operation**

As mentioned before, current gain cut-off frequency ( $f_T$ ) and power gain cut-off frequency ( $f_{max}$ ) are the two most critical parameters for RF applications. High mobility and high 2DEG charge reduce the channel resistance in the device which improves the frequency. High 2DEG charge also improves the semiconductor-metal contact resistance by improving the channel access resistance. Moreover, GaN also possesses comparatively lower dielectric constant which reduces the parasitic capacitances in the device improving  $f_T$  [2] and  $f_{max}$  [3] additionally.

Figure 1.4 Johnson Figure of Merit (JFoM) for various material systems [1].

#### **1.3.2 High Power and Efficiency**

GaN has a larger bandgap and higher breakdown electric field which allows it to operate at significantly higher voltages as compared to other material systems such as Si, GaAs and InP. As device dimensions are scaled smaller to increase the operating frequency, this in turn deteriorates the breakdown voltage (BV) which limits the dynamic range of operation. The product of  $f_{\rm T}$  and BV is commonly referred as Johnson figure of merit (JFoM) which is used to benchmark various high-speed device technologies. GaN-HEMTs demonstrate the highest JFoM almost an order higher than Si and GaAs devices as shown in **Fig. 1.4** [1].

Additionally, power is directly related to breakdown voltage. GaN, due to its wide bandgap, has a high critical electric field, and therefore, a larger breakdown voltage at a given frequency compared to other available high frequency semiconductor materials including Si, InP, and GaAs. Therefore, GaN-based transistors have demonstrated superior power performance over a wide frequency range (**Fig. 1.5** [5]). The emergence of GaN technology operating at 28 V to 50

Figure 1.5 A comparison of output power vs frequency for different material systems [5].

V on a low RF loss, a high thermal conductivity substrate like silicon carbide (SiC) has opened up a range of new possibilities.

#### **1.3.3 Less Design Complexity**

The most power-consuming element of radio transmitter is the power amplifier (PA) (> 60%). Hence any improvement in its power consumption and efficiency will have a significant impact on the entire circuit complexity. Since GaN has a high power density, it requires less number of amplifiers to achieve the same amount of gain and RF power output. For instance, as shown in **Fig. 1.6** [6], in the case of GaAs, multiple amplifier stages and branching with seven amplifiers are required to achieve a specific power level. To do so, RF dividers and combiners are utilized to distribute and combine the output powers of each stage. However, since GaN has a higher power density, hence the same power can be achieved by cascading few GaN PAs. Additionally, GaN is preferable due to the following: (i) simplified circuitry by eliminating peripheral components, reducing power loss, hence improving efficiency (ii) GaN has higher power density, hence requires smaller devices compared to GaAs and thereby providing competitive cost benefits (iii) GaN has a higher thermal conductivity which may simplify the cooling requirements (iv) the high BV of GaN material system eliminates the use of RF limiter

Figure 1.6 A comparison of multistage GaAs vs GaN Power amplifier (PA) [6].

used to protect the LNA from high voltages which reduces overall size and complexity. This can further be seen from **Fig. 1.7** which illustrates the component count in a massive MIMO antenna for various device technologies [5].

#### **1.3.4 Wide Temperature Range**

Low bandgap devices are particularly susceptible to high temperature failure. In the case

1,200 1,049 FPGA + D/A and Number of Components 1,000 A/D Converters VGA + PS SiGe/ 800 PA + LNA CMOS 600 537 GaAs 400 GaN 281 200 153 RC 25 49 0 16 32 128 256 512 1,024 64 Antenna Number ✓ Component count of GaN-based antenna is 89~153, while that of SiGe is 281~537. Only 30% components are required.

concentration exceeds the doping level rendering the device inoperable which limits its operational temperatures below 100 °C. However, the intrinsic carrier concentration is about twelve orders of magnitude lower in GaN [7], which allows them to operate at high temperatures. The lower intrinsic carrier concentration also translates to lower intrinsic leakage current and low noise in GaN HEMTs.

Similarly, at low temperatures, carrier freeze-out effect renders S-based devices inoperable. In contrast, 2DEG forms in the lower bandgap material in a GaN/AlGaN HEMT which does not freeze-out. Moreover, lower temperature improves the mobility of electrons. Deep space applications exploit this low temperature feature to design extremely low noise, high gain microwave devices.

#### 1.3.5 Reliability and Robustness

Mean time to failure (MTTF) is a parameter used to characterize reliability and robustness of a device structure. GaN demonstrates one order higher MTTF compared to Si and GaAs (Fig. 1.8).

Figure 1.8 Technology comparison of Mean-Time-To-Failure versus Channel Temperature. https://www.mpdigest.com/2019/10/24/gan-on-sic-is-driving-advances-in-radar-applications/.

In summary, GaN-based RF and power electronics are going to define many crucial "moreelectric" transportation systems and communication systems in near future. This relies on the enhanced efficiency in conversion processes afforded by wide bandgap materials from kHz to GHz frequency spectrum. In particular, there is a need for efficient solid-state power amplification to replace complex, low-efficiency multi-stage circuits and bulky and fragile vacuum tubes in defense applications. Additionally, in the era of internet of things (IoT), artificial intelligence and autonomous vehicles, there is an urgent need for high-power and high frequency transistors that can facilitate ultra-fast, highly reliable, and low latency wireless networks. To serve these needs, transistors which can provide a combination of high power density and high efficiency at high frequencies are required. **Figure 1.9** summarizes the importance of various material parameters for different applications [8] and illustrates the impact of GaN device characteristics on the PA metrics and system-level advantages [9].

Figure 1.9 (a) Importance of various material parameters for various commercial applications [8] (b) Impact of GaN device Characteristics on system level advantages [9].

#### 1.4 Why N-polar

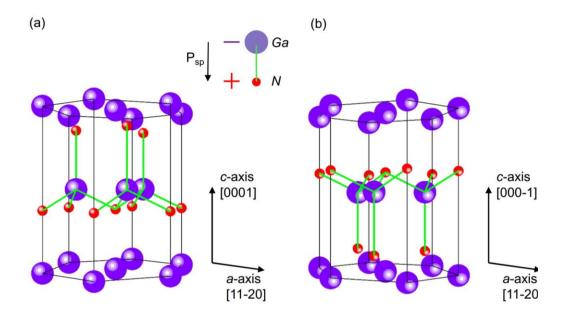

GaN is most stable in a Wurtzite crystal structure as shown in **Fig. 1.10**. This crystal structure lacks inversion symmetry, with the polarization field in the material depending on the crystal orientation. When the crystal is oriented in the [0001] direction, it is terminated with Ga atoms on the surface and has negative net polarization, which is known as Ga-polar or Ga-face. On the other hand, the  $[000\overline{1}]$  orientation is terminated with N atoms and has positive net polarization, which is called N-polar or N-face. GaN-based optoelectronic and electronic devices for commercial applications have been mainly developed on Ga-polar GaN templates due to less complexity of epitaxial growth compared with that on N-polar [10–16]. Nonetheless, N-polar GaN-based HEMTs have several advantages over Ga-polar GaN-based HEMTs that make them a promising candidate for highly scaled devices.

Figure 1.10 GaN Wurtzite crystal structure in (a) Ga-face (b) N-face, with spontaneous polarization vector.

#### 1.4.1 Strong Confinement from Back-barrier

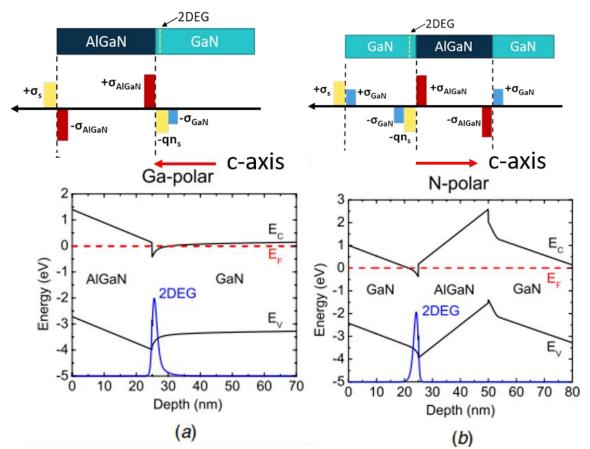

The epi-structure and corresponding band diagram with 2DEG wave-function for Ga-polar and N-polar HEMT is shown in **Fig. 1.11** [17]. As negative gate voltage is applied, it depletes the 2DEG channel and turns off the HEMT. In Ga-polar HEMT, the negative gate bias pushes the electron wave function away from the gate whereas in N-polar it is sandwiched by the underlying back-barrier. This improves confinement results in a sharp pinch-off characteristics in N-polar HEMTs as well as reduces output conductance which improves the short channel effects (SCEs) of HEMTs. Several simulation studies [18,19] supported these predictions.

Figure 1.11 Epi-structure, charge profile, and band diagram of typical Ga-polar (left) and N-polar (right) hetero-structures. The 2DEG forms below the barrier in Ga-polar. This is in contrast with N-polar hetero-structures in which the 2DEG forms on top of the barrier and leads to better confinement of the 2DEG, more gate control specially in scaled HEMTs, and lower ohmic contact resistance [17].

#### **1.4.2 Improved Scaling**

The current gain cut-off frequency depends on gate length (Lg) in the first order which can be enhanced significantly by reducing the gate length. However, this can lead to SCEs such as lowered output resistance, limited benefits in trans-conductance because of diminished charge control and threshold voltage variation with gate length [20][21]. SCEs can be alleviated significantly by proportionately scaling down the gate-to-channel thickness while simultaneously reducing gate length which is referred as high aspect ratio design [22][23][24]. In Ga-polar HEMTs, the 2DEG concentration depends on the AlGaN barrier composition and thickness [25]. Higher the composition and thickness higher the 2DEG. Hence reducing the barrier thickness leads to a reduction in the 2DEG concentration which is not desirable as it increases the sheet and contact resistances. Therefore, a tradeoff exists between barrier thickness and RF frequency in Ga-polar HEMTs.

On the contrary, the 2DEG concentration in N-polar HEMTs depends additionally on the back-barrier thickness, composition and doping [26]. Thus, it is possible to achieve a thinner channel required for high frequency applications while maintaining higher 2DEG by increasing the thickness or polarization of backbarrier. InAIN back-barriers are particularly attractive since it has higher polarization while being lattice-matched to GaN removing upper limit on the thickness of back-barrier due to strain limitation [27]. The additional back-barrier design breaks the trade-off that exists with Ga-polar HEMT and provides designers with an additional knob to improve the HEMTs.

#### 1.4.3 Improved Ohmic contact

As shown in **Fig. 1.11(a)**, the top layer in Ga-polar HEMT is AlGaN which has a higher bandgap making it difficult to achieve a good ohmic contact with the 2DEG. One possible way is

to etch down the barrier layer under the source/drain ohmic contacts selectively. However this reduces the 2DEG concentration as it depends on AlGaN barrier the thickness [25] as discussed previously.

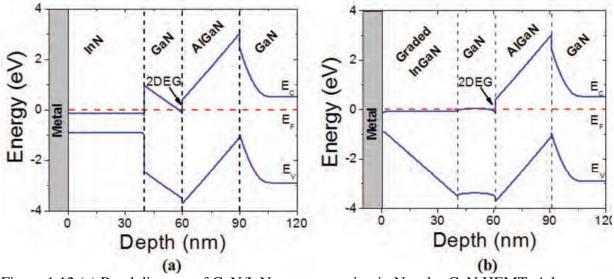

Figure 1.12 (a) Band diagram of GaN/InN regrown region in N-polar GaN HEMT. A large bandoffset of 1eV exists at GaN/InN interface. (b) band diagram of GaN/gradedInGaN/InN regrown region [28].

In contrast, the top layer is low band-gap GaN in N-polar HEMT which results in a lower contact resistance. Moreover, even smaller contact resistance can be achieved by using selective-area ohmic regrowth. A non-alloyed metal–2DEG contact resistance of  $< 0.03 \ \Omega$ ·mm obtained in N-polar GaN HEMTs through selective-area regrowth of graded n<sup>+</sup> InGaN has remained the lowest in III-nitride transistors to date [28]. In this work, an n<sup>+</sup> InN was regrown in source/drain regions on N-polar HEMT structures. A very low Metal-to-InN contact resistance of  $5 \ \Omega$ .µm was achieved, which was attributed to the pinning of the conduction band of InN under the fermi level resulting in a surface accumulation layer with a 2DEG charge density of  $1 \times 10^{13}$  cm<sup>-2</sup>. However, InN on GaN results in the conduction band discontinuity of 1 eV, which can negatively affect metal-to-2DEG contact resistance. This was resolved by introducing a graded n+ InGaN in-between, which brings the conduction band down because of formation of a 3D electron gas due to the positive

polarization of InGaN layer [28] as shown in **Fig. 1.12**. The graded layer was grown by reducing the Ga flux gradually while maintaining the temperature constant. The contact resistance of 23  $\Omega$ µm was achieved with 0-63% InGaN grading with doping 1×10<sup>19</sup> cm<sup>-3</sup> which can be further reduced by increasing final Indium percentage and doping.

For applications that do not need such ultra-low contact resistance, regrown n<sup>+</sup> GaN has been used for non-alloyed ohmic contacts. Regrowth of an n<sup>+</sup> GaN is simpler than a graded InGaN film and can also result in low contact resistances ranging from 0.058  $\Omega$ -mm [29] to 0.16  $\Omega$ -mm [30] depending on the growth quality and doping concentration. It is important to note that nonalloyed ohmic contacts are not only important to obtain low contact resistance, but also to eliminate non-ideal effects such as dispersion observed in N-polar HEMTs with alloyed contacts [31]. A very large degradation in saturation current was observed during pulsed-IV measurements on Npolar HEMTs with alloyed contact due to the combination of a positive *V*<sub>th</sub> shift and a degradation of the trans-conductance whereas non-alloyed contact measured in this study showed negligible dispersion [31].

#### 1.4.4 GaN Cap in Access Region

Planar GaN HEMTs suffer from surface trap related current collapse and knee walkout commonly known as DC-RF dispersion. During device operations, traps present on the surface can capture electrons and become negatively charged. These negatively charged traps act as a virtual gate and deplete the 2DEG channel underneath which increases the on-resistance and reduces the drain current. Traditionally, PECVD SiN passivation or field-plates have been utilized to reduce the dispersion which introduce additional parasitic capacitances rendering them undesirable for mm-wave applications. By introducing a GaN cap in the access region [32], it moves the surface

Figure 1.13 (a) Device cross-sectional schematic (not drawn to scale) and epitaxial layer profile of the N-polar deep recess (NPDR) MISHEMT with the foot-gate self-aligned to the GaN cap recess. (b) Energy band diagram comparing the vertical profiles under the gate electrode as compared to the access region with the addition of a GaN cap layer.

traps away from the channel and makes the pinch-off voltage in the access region more negative (-30V), consequently resulting in less DC-RF dispersion.

Additionally, the GaN cap enhances the conductivity of the access regions for three reasons. The introduction of GaN cap layer reduces the vertical electric field in the access region as shown in the **Fig. 1.13(b)**. This pushes the conduction band downwards in the channel which leads to an increase in 2DEG concentration. Moreover, the reduction in vertical electric field improves the lateral mobility. Third, the surface is moved away from the channel which reduces the surface scattering and further improves the mobility. These combined effects have shown to reduce the sheet resistance from 325  $\Omega$ /sq in the gate region to 220  $\Omega$ /sq in the access region in these NPDR structures.

#### 1.4.5 Reduced Leakages

Since the Schottky barrier to GaN is lower than that on AlGaN, the early N-polar GaN HEMTs suffered from significantly larger gate leakage than that often observed on Ga-polar

Figure 1.14 A schematic of a Ga-Polar HEMT band diagram at (a) equilibrium and (b) with a reverse gate-drain voltage applied. (c) and (d) give the energy band diagram of a N-Polar HEMT with a thin AlGaN top-barrier at equilibrium and at a reverse gate-drain voltage bias, respectively [31].

HEMTs. A 25 nm thick 10% AlGaN cap layer was also introduced in these N-polar HEMTs to increase the Schottky barrier and reduce the gate leakage. This AlGaN cap layer in N-polar HEMT structures reduces the gate leakage not only by increasing the Schottky barrier height, but also by reducing the tunneling current under large reverse gate biases. The latter is a unique feature in N-polar HEMT structures due to the opposite polarization field in these structures compared with that in Ga-polar HEMTs [31] (**Fig. 1.14**). Introducing the AlGaN cap layer resulted in a significantly lower gate leakage current with more than a three-fold increase in breakdown voltage.

#### **1.4.6 Comparison of Device Performance**

Reported Ga-polar HEMTs and monolithic microwave integrated circuits (MMICs) have demonstrated excellent performance from Ka-band (27-40 GHz) through W-band (75-110 GHz).

In Ka-band, HEMT devices offering 9.7 and 10.5 W/mm of output power (*P*o) and power-added efficiencies (PAE) of 43% and 33% at 30 and 40 GHz respectively have been demonstrated [33,34]. Devices have also been demonstrated with output power of 3.1 and 4.3 W/mm at 30-GHz with PAE of 52% by Moon et al [33]. MMICs of highly scaled devices have also been recently reported with a PAE of 59% at 32 GHz but the power density at the output stage was limited to 440 mW/mm [35]. As frequency of operation increases, the output power and efficiency reduce due to trade-off between power and frequency that depends on the semiconductor properties such as bandgap and electron mobility. At 83 GHz, a MMIC with a peak PAE of 27% and *P*o of 1.7 W/mm has been demonstrated [36]. At 94 GHz, a pre-matched device with 24.2% PAE and 1.5 W/mm Po [37] was reported and at 86 GHz, Niida et al. have reported 3.6 W/mm with 12.7% PAE [38].

Alternatively, as discussed before, N-polar HEMT offer additional degrees of freedom to design the devices due to its natural back barrier, inverted polarization and better confinement which is conducive to mm-wave application. Using N-polar GaN with deep recess gate structure,

Figure 1.15 W-Band output power density of various GaN device technologies over time. Traditional Ga-polar AlGaN/GaN HEMTs have saturated around 2 W/mm while N-polar GaN has recently demonstrated 7.94 W/mm [17].

6.7W/mm at 94 GHz with 14.4% associated PAE using a realigned gate process and 27.8% PAE with 8W/mm at 94 GHz using a self-aligned gate process have been reported. This is more than twice of the output power typically measured on conventional Ga-polar GaN HEMTs with more than twice the efficiency as well (**Fig. 1.15**). Romanczyk et al. [39] have reported peak PAE of 55.9% measured at 14 V with an associated *P*o of 5.3 W/mm and 52.5% PAE with 8.08 W/mm at 20 V at 30GHz. No devices to date had demonstrated constant output power density over frequency range as expected in an ideal device (since power density is not a function of frequency; output power is). Romanczyk et al [39] have reported the N-polar device with 7.94W/mm output power at W-Band, Ka-Band and X-Band, the first device to do so.

#### **1.5 Dissertation Overview**

The goal of this dissertation is to explore high-k as dielectric for ultra-thin N-polar HEMT for mm-wave Applications. We have developed high quality thermal HfO<sub>2</sub> ALD films on N-polar GaN and used this as dielectric to fabricate and characterize the N-polar HEMT which has better performance.

Chapter 2 presents the dielectric study of HfO<sub>2</sub> on N-polar GaN. Metal-Oxide-Semiconductor capacitors (MOSCAP) were fabricated to study the interface and bulk properties of HfO<sub>2</sub> using deep UV-assisted capacitance-voltage measurements. Different surface cleaning method, in-situ plasma activation, ALD deposition method and annealing environment was systematically studied to achieve better quality HfO<sub>2</sub>. The HfO<sub>2</sub>/GaN MOSCAPs achieve small hysteresis, low interfacial trap density, low leakage current, and moderate breakdown electric field.

Chapter 3 utilizes the developed HfO<sub>2</sub> dielectric to fabricate N-polar MISHEMT. Several fabrication steps were developed in the cleanroom such as slow GaN etch to reduce the impact of plasma on surface states during etching thin layers, regrown source/drain to achieve low ohmic

contact, HfO<sub>2</sub> etching using BCl<sub>3</sub> plasma. DC, pulsed-IV, BV and small signal RF measurements were carried out to analyze and understand the operation of N-polar HEMT with HfO<sub>2</sub> as dielectric.

In Chapter-4, N-polar deep recessed HEMT (NPDR) were demonstrated with  $HfO_2$  as gate dielectric. Additional fabrication steps were introduced such as selective  $BCl_3/SF_6$  etch to achieve recess under gate and source/drain with smooth surface.  $HfO_2$  thickness series was performed to understand the effect of gate dielectric bulk traps on DC-RF dispersion.

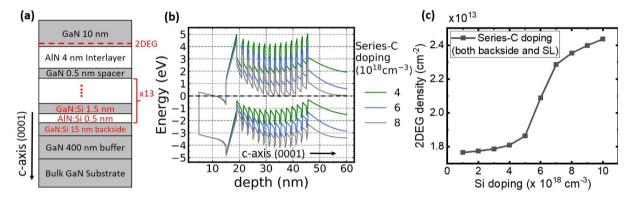

In Chapter 5, an attempt was made to develop a thin channel HEMT epi-layer with large 2DEG concentration using Silvaco TCAD simulation. GaN/AlN digital alloy was used as backbarrier since AlN has higher polarization and digital alloy has better thermal conductivity compared to bulk GaN. Impact hole traps in GaN/AlN HEMT system was studied and various doping scheme with band engineering was used to eliminate its effect. The effect of various interlayer thickness, doping were studied to obtain an optimized structure with minimum parasitic over wide range of doping. 2DEG as high as  $3 \times 10^{13}$  cm<sup>-2</sup> was achieved both from simulation and experimentally. However the mobility was extremely small (~600 cm<sup>-2</sup>/V.s).

### Chapter 2

## Investigation and Optimization of HfO2 Gate Dielectric on N-polar GaN

### **2.1 Introduction**

#### 2.1.1 Why HfO<sub>2</sub>

N-polar GaN HEMT has demonstrated much higher power density and efficiency which has positioned itself as a major contender for RF applications as discussed in the previous chapter. However, the demand for faster data, higher bandwidth is increasing which requires higher and higher frequency of operation. The frequency of operation can be further enhanced significantly by reducing the gate length. This however can lead to short-channel effects (SCEs) such as lowered output resistance, limited benefits in trans-conductance because of diminished charge control and threshold voltage variation with gate length [20][21]. However, SCEs can be alleviated significantly by reducing the gate-to-channel thickness while reducing gate length which is commonly referred as a high aspect ratio design [22][23][24]. This high aspect ratio scaling typically leads to higher gate leakage due to thinner barrier and higher electron tunneling probability. This leakage can be suppressed by a thick insulator layer between channel and gate metal; however, this reduces the gate capacitance. High-k dielectrics such as HfO<sub>2</sub> are particularly advantageous in such scenarios since a thicker dielectric can be deposited without altering the gate capacitance. Hence it is important to develop a high-k dielectric with superior interface states and border traps to enable next-generation high-power high-frequency N-polar GaN-based transistors.

Several groups have studied high-k dielectrics, including HfO<sub>2</sub>, ZrO<sub>2</sub>, and HfZrO<sub>2</sub> on Gapolar GaN HEMTs [40–52]. Saadat et al. [42] compared Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and a stack of Ga<sub>2</sub>O<sub>3</sub>+HfO<sub>2</sub> as gate dielectrics. Their studies revealed that while HEMTs with  $Al_2O_3$  gate dielectric show the best trans-conductance and dispersion performance, the Ga<sub>2</sub>O<sub>3</sub> + HfO<sub>2</sub> combination has the best maximum drain current density, low interface traps, and negligible hysteresis along with transconductance that is comparable to that of standard Ni/Au/Ni Schottky-gated HEMTs because of the high capacitance of the high-k dielectric. Moreover, using  $Ga_2O_3 + HfO_2$  as the gate dielectric reduced the gate leakage by more than five orders of magnitudes compared with the HEMT without any gate dielectric. Chen et al [53] investigated  $ZrO_2$  as gate dielectric in Ga-polar GaN HEMTs and compared dc and RF characteristics of these HEMTs with those with Schottky contact gate. They showed that the MOS-HEMTs with ZrO<sub>2</sub> gate insulator layer significantly reduced the gate leakage current and microwave performance of the devices. The device linearity was also improved due to its flat and wide trans-conductance (gm) distribution. Stoklas et al [54] studied the impact of atomic layer deposition (ALD) deposition technique using photo-assisted capacitance transients (photo-C-t) method and reduced the  $D_{it}$  value from  $1 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> to  $2-3 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> by replacement of thermal-ALD with ozone-ALD. Jung et al [55] demonstrated a surface state density (measured using conventional Terman method) of  $6.77 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> at Ec-0.3 eV by in situ NH<sub>3</sub> ALD plasma passivation. Chang et al [56] reported  $D_{it}$  of 5-10×10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> at mid bandgap at the interface between thermal ALD deposited HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer dielectric and GaN using conventional Terman method which is not accurate for wide bandgap semiconductors.

All the aforementioned studies have focused on depositing the HfO<sub>2</sub> dielectric on Ga-polar GaN. However, the polarity of GaN (Ga-polar vs N-polar) plays an important role in deciding the dielectric-semiconductor interface quality. It has been observed that N-polar GaN surface is more

reactive as compared to Ga-polar resulting in higher incorporation of impurities and higher surface states [57]. A recent study has also showed the GaN polarity impacts the interface sharpness between oxide and GaN, thus resulting in different capacitance-voltage (CV) characteristics [58]. Yang et al [59] have studied the effects of surface pretreatment, dielectric growth, and post deposition annealing on interface electronic structure and polarization charge compensation of Ga-and N-face bulk GaN. Meyer et al [60] is the only report on HfO<sub>2</sub> on N-polar AlGaN-GaN HEMTs, in which they showed that HfO<sub>2</sub>-insulated gate devices improved the reverse-bias gate leakage current as compared to reference Schottky devices, however failed to pinch-off the device even with 1.5 μm gate length.

## 2.1.2 Characterization Methods of Interface States

#### <u>Terman Method</u>

The Terman method compares the ideal capacitance-voltage (C-V) and the low-frequency C-V curves to calculate the interface states density from the deviation of two curves. This method is valid based on the assumption that (i) the semiconductor and dielectric material are both ideal, thus their C-V response can be predicted mathematically; (ii) the low-frequency C-V curve can entirely reflect the information on interface state density. No traps are present in dielectric bulk or near interface. The Terman method has been utilized to characterize the interface state density in silicon based devices for decades. Silicon has relatively small bandgap and relatively large minority carrier concentration which allows both the shallow and deep interface state to be ionized in manageable time scales.

Given the non-ideality of the semiconductor and dielectric materials, the deviations of their material properties from the theoretical values are not avoidable. Thus, the high-low frequency measurement is employed to replace the numerical calculated C-V curve in the Terman method.

However, in the WBG material systems with negligible hole concentration and generation rates, the trap emission time is very long at room temperature. Specifically, previous research showed the electron emission time from the state located around  $E_{C}$ -1.5 eV for GaN is estimated to be 10<sup>7</sup>-10<sup>8</sup> years at room temperature [61]. The high-low frequency method may still be used in the WBG system to a limited extent, as the minority carrier generation rate can increase at elevated temperatures. However, in order to create a comparable quantity of holes, the required high temperature would damage the device being tested.

### AC Conductance method

This method measures the conductance change due to the charging and discharging of traps responding to the Fermi level moving above to below the energy of the trap. This method is very useful when the emission time of the trap is on the order of 10 ms (100 Hz) or shorter. When the time constant of the trap is smaller than that, only shallow traps can respond and the conductance signal becomes noisy. Similar to the Terman method, the temperature is often increased to allow for the measurement of deep traps near mid-bandgap for the WBG material systems with the trap emission time on the order of years.

#### **Deep Level Transient Spectroscopy (DLTS)**

The deep level transient spectroscopy is a very sensitive and accurate technique which measures the change in capacitance due to changes in traps occupancy. The device under test (DUT) is initially placed under reverse-bias (trap emptying pulse) to empty all the traps. Followed by a forward biased pulse (trap filling pulse) which results in traps capturing the carriers and getting filled. The DUT is then again placed under reverse bias (trap emptying pulse) by lowering the voltage to the initial voltage level. However, traps cannot respond to the change immediately due to its slow nature, rather emit electrons slowly over time. This results in a capacitance transient over time which can be accurately measured. By repeating this reverse-forward-reverse pulse sequence over a temperature range for different rate windows, different trap characteristics such as capture cross-section, activation energy level, and density can be extracted using Aarhenius plot. DLTS measurement is spectroscopic in nature such that it can resolve and identify traps present at different energy locations since traps at different energy location emit carriers at different rates. It can also resolve between donor and acceptor traps. Traditional DLTS is typically capacitance based on depletion region (e.g. p-n junction or Schottky diode). However, other electrical parameters such as current (I-DLTS) or voltage (CCDLTS, DDLTS) can be used to monitor the transient response resulting from change in trap occupancy. Another advantage of DLTS over AC Conductance is, while AC Conductance uses an AC frequency at a specific DC bias, DLTS generally pulses from a bias that is significantly higher than the trap energy level to a bias that is significantly lower than the trap energy. However, major disadvantage of DLTS is that it takes a long time to sweep over a large range of temperature especially for wide-bandgap devices. However UV illumination can be used to excite traps in combination with traditional DLTS method which is known as deep level optical spectroscopy (DLOS).

#### Deep UV-assisted Capacitance-Voltage Method

Recently, the deep ultraviolet photo-assisted capacitance-voltage (DUV-assisted C-V) was developed as an alternative technique to extract  $D_{it}$  for wide-bandgap semiconductors [62–65]. This method is utilized in this chapter and will be elaborated in details. Similar to the Terman method, this method tracks the change in the occupancy of the traps, enabled by the capture of electrons first from the conduction band by empty interfacial states and eventually by generated holes that accumulated at the semiconductor/dielectric interface. This technique relies on deep ultraviolet (DUV) illumination applied to devices biased in depletion to ensure all traps can be extracted from the C-V measurements. The energy of the deep UV light should be the same or large than that of the characterized semiconductor materials. The detailed procedure of this measurement will be elaborated in this chapter.

## 2.1.3 Chapter Overview

In the first part of this chapter, we investigated HfO<sub>2</sub> on N-polar HEMT structure by performing frequency dependent capacitance-voltage measurements on metal-oxide-semiconductor capacitors (MOSCAPs). The impact of annealing on the quality of HfO<sub>2</sub> was studied. Moreover, we compared the CV characteristics of MOSCAPs with HfO<sub>2</sub> deposited on GaN channel with that deposited on the AlGaN cap layer.

In the second part of this chapter, the impact of various surface preparations, in-situ ALD plasma pre-treatments, deposition and annealing conditions on the  $D_{it}$  of HfO<sub>2</sub> on N-polar GaN were investigated. Interface trap density ( $D_{it}$ ), border trap density, breakdown voltage (BV) and dielectric constant were measured and optimized for HfO<sub>2</sub>/N-polar GaN MOSCAPs.

# 2.2 As-deposited HfO2 on GaN HEMT Epi-structure

#### **2.2.1 Device Fabrication**

The N-polar HEMT structure used for this study is shown in **Fig. 2.1** and was epitaxially grown by metal-organic chemical vapor deposition (MOCVD) on a miscut sapphire substrate. A graded Si-doped AlGaN backbarrier is typically used in these heterostructures to suppress current dispersion caused by hole traps at the interface with net negative polarization charge [66,67]. The details of growth are discussed elsewhere [68–70]. The 2nm-thick Al<sub>0.08</sub>GaN layer on top is to reduce the gate current leakage. MOCVD grown N-polar HEMT structures are typically capped in-situ with 5 nm-thick SiN<sub>x</sub> dielectric. The SiN<sub>x</sub> cap protects N-polar surface from being

roughened by the developer during the device fabrication [71,72]. It can also function as gate dielectric [32,72,73].

For this purpose, the ohmic contacts were created by E-beam evaporation using a metal

Figure 2.1 Schematic of the structures studied in this work (a) HfO<sub>2</sub> on SiN (b) HfO<sub>2</sub> on AlGaN after removal of SiN and (c) HfO<sub>2</sub> on GaN after removal of SiN and AlGaN cap layer.

stack of Ti/ Al/ Ni/ Au (20/100/10/100 nm), which was then annealed at 820° C for 30 seconds in a N<sub>2</sub> gas atmosphere. HfO<sub>2</sub> was then blanket-deposited over the whole wafer, using plasma enhanced atomic layer deposition (ALD) with the chamber conditioned to 250 °C in Argon ambient. The dielectric thickness was verified using ellipsometry on Si pieces co-loaded as control samples. Sample-A was not annealed after HfO<sub>2</sub> deposition, while sample-B and sample-C were annealed at 400 °C in a N<sub>2</sub> gas atmosphere for 1 min and 5 min, respectively. This was followed by gate metal deposition (30 nm Ti/ 600 nm Au) via E-beam evaporation. Capacitor sizes on each sample ranged in diameter from 50 µm to 800 µm. To investigate the impact of annealing on  $HfO_2$  quality, we first fabricated a set of MOSCAPs with 15 nm-thick  $HfO_2$  deposited directly on MOCVD-SiN<sub>x</sub> as shown in **Fig. 2.1(a)**.

## 2.2.2 Results and Discussion:

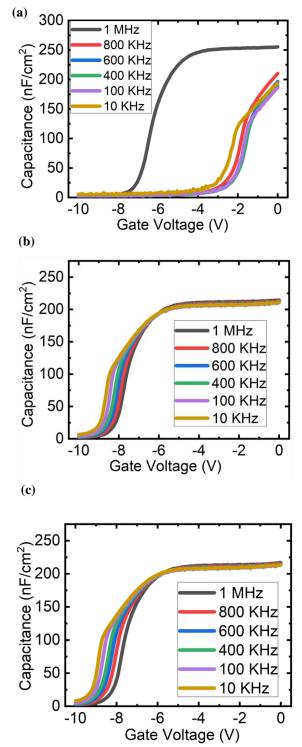

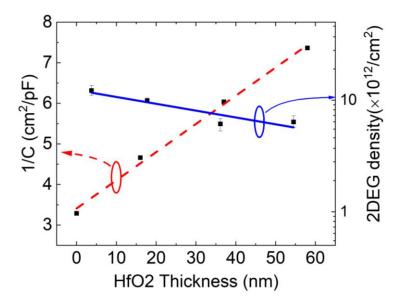

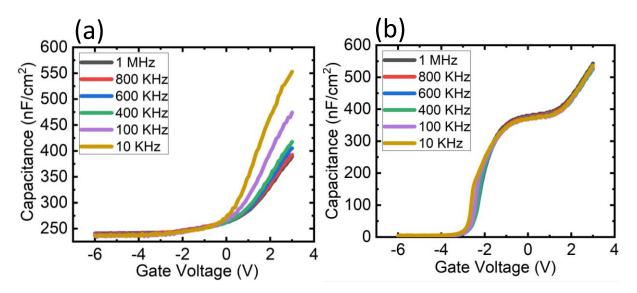

Figure 2.2(a) demonstrates the representative CV profiles measured at different frequencies on Sample-A. CV profiles measured at frequencies below 800 kHz are drastically different from an ideal CV profile expected on a hetero-structure having а two-dimensional electron gas (2DEG). They do not show a saturated capacitance. Attempts to measure these devices at positive voltage were unsuccessful due to high ac current leakage. The 2DEG density extracted from these CV profiles is  $\sim 3 \times 10^{12}$  cm<sup>-2</sup> which is much lower than that extracted from Hall measurement ( $\sim 1.1 \times 10^{13} \text{ cm}^{-2}$ ) on this heterostructure. This indicates existence of slow trap states in HfO<sub>2</sub>, which can only respond at

Figure 2.2 CV profile measured at different frequencies on MOSCAP-C with 15nm-thick HfO<sub>2</sub> which (a) was not annealed and annealed for (b) 1min and (c) 5 min at 400 °C in N<sub>2</sub>.

frequencies below 800 kHz. The positive shift in threshold voltage compared to the expected value of ~8V also points to negative charges in dielectric. At 1 MHz, these traps can no longer respond and therefore the CV profile looks closer to an ideal one. By annealing HfO<sub>2</sub> at 400 °C in N<sub>2</sub> ambient before gate metal

Figure 2.3 CV profiles measured at 1 MHz on MOSCAPs with various HfO<sub>2</sub> thicknesses.

deposition, the CV profile measured at 1 MHz remained unchanged, whereas the other CV profiles measured at lower frequencies become closer to an ideal curve (**Fig. 2.2 (b) and (c)**). As the measurement frequencies reduces, the pinch-off voltage of these MOSCAPs move toward more negative values. Annealing for 5 min did not change the MOSCAP characteristics significantly, and therefore, we annealed  $HfO_2$  for 1 min for all other devices discussed in this work.

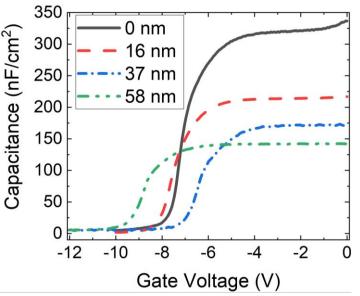

To determine  $HfO_2$  dielectric constant, a set of MOSCAPs were then fabricated varying  $HfO_2$  thickness from 0 nm to ~57 nm. Figure 2.3 shows CV profiles measured at 1MHz on these MOSCAPs. Figure 2.4 depicts 1/C as a function of  $HfO_2$  thickness, in which C is the capacitance density at 0V measured at 1MHz on these MOSCAPs. A dielectric constant value of 17 was extracted for  $HfO_2$  via linear fit to this plot which is close to the dielectric constants reported in the literature for  $HfO_2$  [74,75]. Using a linear fit to 1/C on MOSCAPs with different  $HfO_2$  thicknesses, which are otherwise fabricated identically, allows us to identify dielectric constant accurately

without making assumptions for dielectric constants of other underlying layers including GaN, AlGaN, SiN<sub>x</sub>, and the non-idealities at their interfaces.

The 2DEG density was also extracted on these MOSCAPs by integrating the CV profile and is plotted as a function of HFO<sub>2</sub> thickness. As depicted in **Fig. 2.4**, the 2DEG density decreases as the HfO<sub>2</sub> thickness increases. This behavior can be explained by assuming fixed negative charges uniformly distributed in the HfO<sub>2</sub>. As HfO<sub>2</sub> thickness increases, the total negative charge in HfO<sub>2</sub> increases which results in 2DEG depletion. The  $\Delta V_{th}$  due to the fixed negative charge in dielectric and reduction in 2DEG density is a positive value. On the other hand, increasing HfO<sub>2</sub> thickness leads to reduction of the capacitance density, and consequently,  $\Delta V_{th} < 0$ . Due to these opposite effects, the variation of threshold voltage as a function of HfO<sub>2</sub> thickness is not monotonic.

Figure 2.4 Capacitance measured at 0 V versus HfO<sub>2</sub> thickness.

For ultra-scaled HEMTs, it is desirable to reduce the distance from gate to the channel as much as possible to eliminate short channel effects [22,76]. For this purpose, it is advantageous to deposit HfO<sub>2</sub> directly on the HEMT structure and remove any dielectric with lower dielectric

constant. Therefore, in the next step, we studied the impact of  $HfO_2$  deposited directly on the AlGaN cap (MOCVD-SiN<sub>x</sub> was removed) and GaN channel (MOCVD-SiN<sub>x</sub> and AlGaN cap were removed). For this purpose, MOCVD-SiN<sub>x</sub> was etched by diluted hydrofluoric acid (1:1 HF:DI) after formation of Ohmic contact, followed by  $HfO_2$  deposition on AlGaN cap (**Fig. 2.1(b)**). The sample was then annealed at 400 °C, followed by gate metal deposition as discussed earlier. To fabricate MOSCAPs with  $HfO_2$  deposited directly on the GaN channel (**Fig. 2.1(c)**), SiN was first removed using diluted hydrofluoric acid (1:1 HF:DI). We then removed the AlGaN cap and part of GaN channel using a low-etch-rate (~0.5 nm/min) chlorine-based inductively coupled plasma etching, resulting in a 14 nm-thick GaN channel. After dry etch, the surface was exposed to UV-Ozone for an hour and then etched in HF for 30 sec to help remove surface damage caused by dry etching.

Figure 2.5 CV profile measured at different frequencies on (a) MOSCAP-B and (b) MOSCAP-C. As depicted in **Fig. 2.5** (a), it was not possible to pinch-off MOSCAPs with HfO<sub>2</sub> deposited on AlGaN cap and applying voltages beyond -6V led to very high leakage which made capacitance measurements beyond this voltage impossible. This could be due to reaction of oxide in HfO<sub>2</sub> with Al in AlGaN cap and formation of a poor-quality Al<sub>2</sub>O<sub>3</sub> interface during the annealing at 400°C.

This poor-quality interlayer is full of traps which leads to the pinning of the fermi level. Therefore, by applying gate voltage, the fermi level in the channel does not move. On the contrary, when AlGaN cap layer was removed by low etch rate/low damage dry etching technique and HfO<sub>2</sub> was deposited directly on GaN, normal CV profiles were measured. These MOSCAPs showed much lower pinch-off voltage which is due to a combination of higher gate capacitance, because of lower distance between gate and the channel, and a thinner GaN channel which leads to lower 2DEG density in the channel. A charge density of  $4.9 \times 10^{12}$  cm<sup>-2</sup> was calculated on these MOSCAPs.

## 2.3 HfO<sub>2</sub> Characterization on GaN MOSCAPs

#### **2.3.1 Device Fabrication**

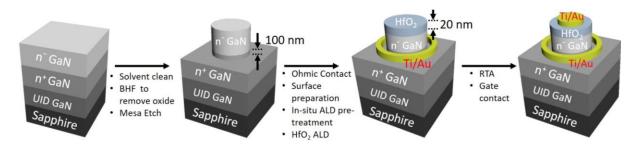

Figure 2.6 Fabrication process flow of HfO<sub>2</sub>/N-polar GaN MIS structure.

Metal-insulator-semiconductor (MIS) capacitors were fabricated to characterize the interface states between HfO<sub>2</sub> and N-polar GaN. The fabrication process is shown in **Fig. 2.6**. The N-polar epitaxial layers were grown by metal organic chemical vapor deposition (MOCVD on  $4^{\circ}$  miscut c-plane sapphire substrates). From bottom to top, the epitaxial layers included 660 nm unintentionally doped GaN, 660 nm n+ GaN:Si with a doping concentration of  $3.5 \times 10^{18}$  cm<sup>-3</sup> and 530 nm n-GaN with a doping concentration of  $2 \times 10^{17}$  cm<sup>-3</sup>. Chlorine-based mesa etch was performed till n+ GaN layer was exposed, followed by evaporation of ohmic metal stack Ti/Au (30/200 nm). Several samples were fabricated with various surface pretreatments using wet

chemical etching combinations and UV-ozone prior to ALD deposition. The samples were loaded immediately into ALD chamber to minimize any native oxide formation and surface contamination. Various in-situ plasma treatments in the ALD chamber were implemented prior to deposition of 20 nm-thick HfO<sub>2</sub>. The HfO<sub>2</sub> was deposited via thermal- or plasma- ALD in a Veeco Fiji ALD reactor and the thickness was measured using ellipsometer on a co-loaded Si sample. After dielectric deposition, rapid thermal annealing (RTA) at 400°C was performed for 1 min on all the samples, followed by deposition of a gate metal stack (Ti/Au :20/200 nm). **Table 2.1** summarizes the techniques that were employed for surface preparation, in-situ pretreatment, ALD deposition, and post-deposition annealing.

#### 2.3.2 Results and Discussion

UV-assisted CV measurement was employed to calculate the interface state density following the methodology developed by Swenson et al [62]. CV measurements were taken at room temperature using a Keysight B1500 semiconductor parameter analyzer. The frequency and amplitude of AC signals were 1 MHz and 30 mV, respectively. The DC voltage sweep was set with a step voltage of 30 mV and a sweep rate of 0.6 V/s. A 365 nm lamp with an optical power

Table 2.1. Summary of the techniques that were employed for surface preparation, in-situ pretreatment, ALD deposition, and post-deposition annealing.

|             | Sample #                    | 1            | 2                     | 3            | 4            | 5            | 6            | 7            |