# Overcoming the Performance and Security Challenges of Building Highly-Distributed Fault-Tolerant Embedded Systems

by

Andrew Loveless

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2023

Doctoral Committee:

Associate Professor Ronald Dreslinski, Co-Chair Associate Professor Baris Kasikci, Co-Chair Assistant Professor Jean-Baptiste Jeannin Associate Professor Linh Thi Xuan Phan, University of Pennsylvania Andrew Loveless loveless@umich.edu ORCID iD: 0000-0003-0627-5702

© Andrew Loveless 2023

To my lovely partner Lisa, who has provided me with unrelenting support for the past 13 years.

#### ACKNOWLEDGMENTS

Completing a Ph.D. has been one of the most difficult challenges of my life, and it would not have been possible without the support of many generous people. In particular, I would like to thank the following individuals.

Ron, my co-advisor, and the first person to contact me from the University of Michigan. His kind and relaxed disposition was a major factor in me choosing to attend the university. While academia can be a pressure cooker, Ron was never a source of that pressure, and he always encouraged me to prioritize my own happiness and health. Ron liked to remind students that a Ph.D. is a training exercise, and that their best work will come after their Ph.D. This perspective helped me through multiple challenging times.

Baris, my other co-advisor, who shaped me more as a researcher than anyone during my Ph.D. In particular, Baris taught me the importance of thinking outside the box and pursuing only the most interesting research ideas. His feedback early in my Ph.D. led to me abandoning several research directions, which ultimately saved me time and led to more exciting work. Baris also taught me the craft of technical writing with more patience than I would expect from any advisor.

Linh, my closest external collaborator, who was a source of constant inspiration throughout my Ph.D. Before a few overnight editing sessions with Linh, I had no idea anyone could operate at such a high level for such long periods of time. I hope I picked up even a small part of her work ethic and attention to detail. Despite my attending a different university, Linh also acted as my unofficial third advisor. Her guidance was essential to making much of my research successful, and I hope we continue working together.

Thank you additionally to the other amazing researchers who influenced my research trajectory. These include Jean-Baptiste Jeannin, who exposed me to his work early in my Ph.D. and provided valuable feedback on this thesis, Chris Peikert, who helped me navigate my early work using errorcorrecting codes, Allen Clement, who suggested I target real-time systems venues, and Mosharaf Chowdhury, who suggested I investigate reducing latency in embedded systems. Thank you also to my labmates in EfesLab and CADRE Lab, who are some of the brightest people I have ever met. I would be fortunate to work with any of them again in the future.

Thank you also to my colleagues at NASA for all their support. Jim Ratliff and Adam Schlesinger for encouraging me to pursue a Ph.D., even though it meant leaving their projects. My

branch and division management, Bruce Manners, Steven Fredrickson, Paul Delaune, Susan Morgan, and Rafael Munoz for helping me receive fellowships that allowed me to continue working at NASA while in school. Brendan Luksik, Cody Hodges, and Paul Muri, who graciously helped take on my NASA tasks whenever I was overloaded. Brendan Hall, Todd Smithgall, Paul Miner, and Wilfredo Torres-Pomales for insightful conversations that contributed to my work. Also, thank you to NASA's Artemis Network Validation and Integration Lab, which let me use lab space and equipment to conduct many of my experiments.

Thank you to my parents, Tom and Kathy, and sisters, Amanda and Meredith, who have always been encouraging and eager to hear about my research. Thank you also to my partner Lisa, who knows more about my research than anyone else. She is my biggest supporter, and this dissertation would not be possible without her help.

Lastly, thank you to the National Science Foundation Graduate Research Fellowship Program (award DGE 1256260), which partly supported this work. Note that any views expressed in this dissertation are my own and not necessarily those of NASA or any funding agencies.

# TABLE OF CONTENTS

| EDICATION      |

|----------------|

| CKNOWLEDGMENTS |

| IST OF FIGURES |

| IST OF TABLES  |

| BSTRACT        |

### CHAPTER

| 1 | Introdu | lection                                                     |

|---|---------|-------------------------------------------------------------|

|   | 1.1     | Background and Trends                                       |

|   | 1.2     | Thesis Statement                                            |

|   | 1.3     | Dissertation Contributions                                  |

|   |         | 1.3.1 Leveraging Hardware Trends to Reduce Latency          |

|   |         | 1.3.2 Compromising Safety in Mixed-Criticality Networks     |

|   | 1.4     | Road Map                                                    |

| 2 | IGOR:   | Accelerating Byzantine Fault Tolerance with Eager Execution |

|   | 2.1     | Introduction                                                |

|   | 2.2     | Background and Challenges                                   |

|   |         | 2.2.1 Overview of a BFT SMR System                          |

|   |         | 2.2.2 Drawbacks of the Agree-Execute Approach               |

|   | 2.3     | Models                                                      |

|   |         | 2.3.1 System Model                                          |

|   |         | 2.3.2 Fault Model                                           |

|   | 2.4     | Design                                                      |

|   |         | 2.4.1 Optimizing Eager Execution for the Single-Fault Case  |

|   |         | 2.4.2 Scaling Eager Execution for the Multi-Fault Case      |

|   | 2.5     | Prototype Implementation                                    |

|   | 2.6     | Evaluation                                                  |

|   |         | 2.6.1 Latency                                               |

|   |         | 2.6.2 Schedulability                                        |

|   |         | 2.6.3 Computation Overhead                                  |

|         | 2.6.4    | Communication Cost                               | 29       |

|---------|----------|--------------------------------------------------|----------|

|         | 2.6.5    | Case Study: Orion Ascent Abort-2                 | 30       |

| 2.7     | Related  | l Work                                           | 32       |

| 2.8     | Conclus  | sion                                             | 33       |

| 3 CROSS | TALK: N  | Making Low-Latency Fault Tolerance               |          |

|         |          | oiting Redundant Networks                        | 34       |

| 3.1     |          | ction                                            | 34       |

| 3.1     |          | ound: Redundant Switched Networks                | 34<br>37 |

| 3.2     | -        |                                                  | 38       |

| 5.5     | 3.3.1    |                                                  | 38       |

|         |          | Fault Model   Fault Model                        | 39       |

| 3.4     |          |                                                  | 40       |

| 5.4     | 0        |                                                  | 40       |

|         | 3.4.1    | Agreement and BFT SMR Protocols                  | 42<br>43 |

|         | 3.4.2    | The Trouble with Timing Faults                   | 45<br>45 |

|         | 3.4.5    | e                                                | 45       |

| 25      |          | Overcoming the Impossibility Result              | 40<br>49 |

|         | • •      | pe Implementation                                | 49<br>50 |

| 3.6     |          | Lion                                             |          |

|         |          | Latency                                          | 50<br>53 |

|         | 3.6.2    | Schedulability                                   | 55<br>54 |

|         | 3.6.3    | Cost Trade-off of Cross-Links                    | -        |

|         | 3.6.4    |                                                  | 57       |

| 27      | 3.6.5    | Case Study: Spaceflight Abort Test               | 58       |

| 3.7     |          | l Work                                           | 59       |

| 3.8     | Conclus  | sion                                             | 60       |

| 4 PCSPO | ooF: Cor | mpromising the Safety of Time-Triggered Ethernet | 61       |

| 4.1     | Introdu  | ction                                            | 61       |

|         | 4.1.1    | Responsible Disclosure                           | 63       |

| 4.2     | Backgro  | ound                                             | 64       |

|         |          | Time-Triggered Ethernet (TTE)                    | 64       |

|         |          |                                                  | 65       |

| 4.3     | Threat I | Model                                            | 66       |

| 4.4     | Design   |                                                  | 68       |

|         | 4.4.1    | Stage 1: Crafting Malicious PCFs                 | 70       |

|         | 4.4.2    | Stage 2: Injecting PCFs into the Network         | 73       |

| 4.5     | Implem   | nentation                                        | 79       |

| 4.6     | -        | tion                                             | 80       |

|         |          | Probability                                      | 80       |

|         | 4.6.2    | Interrupts                                       | 82       |

|         |          | Messaging                                        | 84       |

|         | 4.6.4    | Case Study: NASA Asteroid Redirect Mission       | 86       |

| 4.7     | Mitigati | •                                                | 87       |

|         |          | Prevent Attackers from Crafting PCFs             | 87       |

|         |          | -                                                |          |

|          | 4.7.2 Prevent Attackers from Injecting PCFs                 | 8 |

|----------|-------------------------------------------------------------|---|

|          | 4.7.3 Prevent Devices from Accepting Injected PCFs          | 9 |

|          | 4.7.4 Minimize the Impact of Accepting Injected PCFs        | 0 |

| 4.8      | Related Work                                                | 0 |

| 4.9      | Conclusion                                                  | 1 |

| 5 Conclu | sion and Future Work                                        | 2 |

| 5.1      | Conclusion                                                  | 2 |

| 5.2      | Future Work                                                 | 3 |

|          | 5.2.1 Probabilistic BFT SMR with Eager Execution            | 3 |

|          | 5.2.2 CROSSTALK with Byzantine Switches                     | 4 |

|          | 5.2.3 Optimizing the Network Topology for BFT SMR           | 4 |

|          | 5.2.4 Compromising Security in Mixed-Criticality Networks 9 | 5 |

| BIBLIOG  | RAPHY                                                       | 6 |

# LIST OF FIGURES

### FIGURE

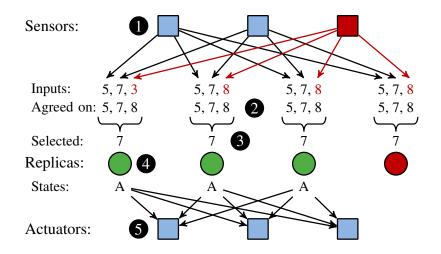

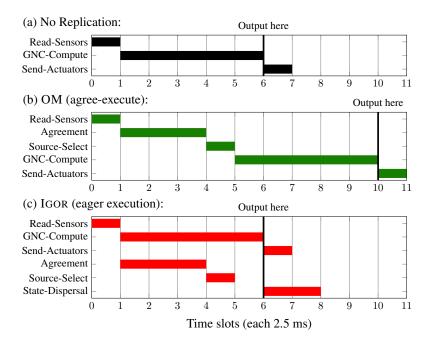

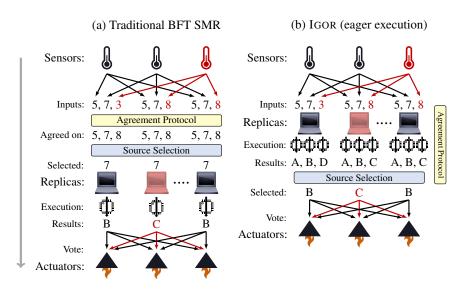

| 2.1 | Traditional BFT SMR — Overview of a traditional agree-execute BFT SMR system.                            |    |

|-----|----------------------------------------------------------------------------------------------------------|----|

|     | Sensor 3 and replica 4 are faulty.                                                                       | 11 |

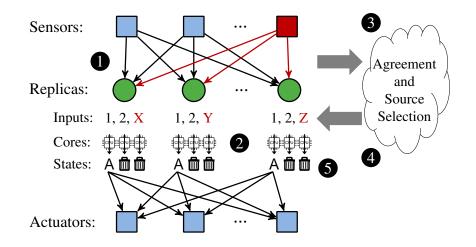

| 2.2 | Overview of IGOR — High-level design of IGOR showing eager speculative execu-                            |    |

|     | tions on data from different sensors. Sensor 3 is faulty                                                 | 15 |

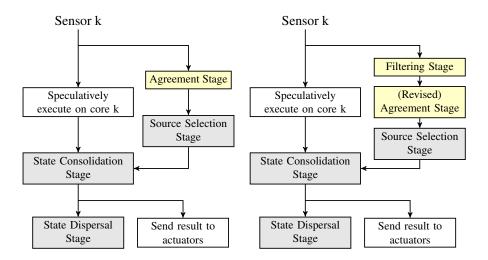

| 2.3 | Stages of IGOR — Stages of IGOR optimized for the single (left) and multiple (right)                     |    |

|     | fault-tolerant cases.                                                                                    | 16 |

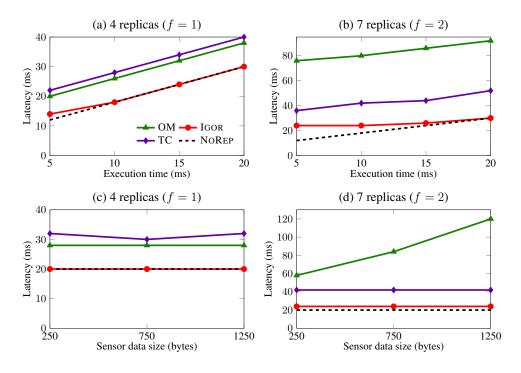

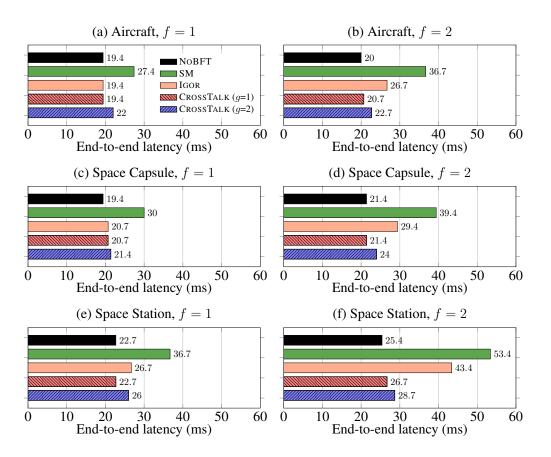

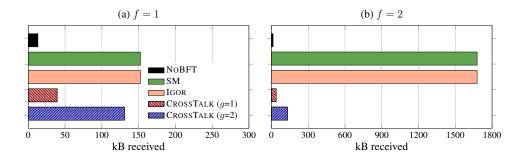

| 2.4 | IGOR's Latency — End-to-end latencies of IGOR and other state-of-the-art protocols                       |    |

|     | compared to a non-replicated system. Plots (a) and (b) use 750 bytes of sensor data                      |    |

|     | with 3 sensors. Plots (c) and (d) use 12 ms execution times with 3 sensors                               | 26 |

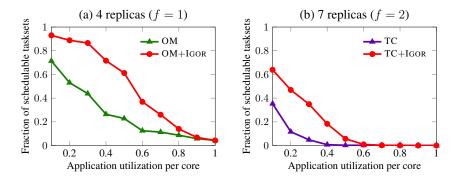

| 2.5 | <b>IGOR's Schedulability</b> — Increase in schedulability when using IGOR. IGOR makes                    |    |

|     | it possible to schedule significantly more tasksets than the state of the art                            | 27 |

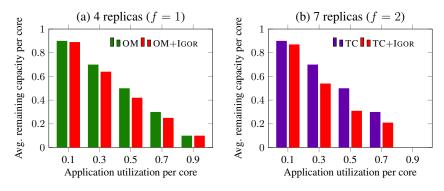

| 2.6 | IGOR's Computation Overhead — Available compute capacity when using IGOR                                 |    |

|     | compared to the best existing protocol alone.                                                            | 29 |

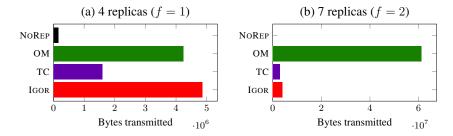

| 2.7 | IGOR's Communication Cost — Total bytes transmitted in IGOR and other state-of-                          |    |

|     | the-art protocols over 100 iterations.                                                                   | 30 |

| 2.8 | IGOR Spaceflight Simulation — Orion AA-2 simulation moments after the crew                               |    |

|     | module (left) separates from the launch abort system (right)                                             | 30 |

| 2.9 | Spacecraft Task Scheduling — Time slot allocations for IGOR and OM when run-                             |    |

|     | ning the AA-2 flight software in the single-fault case.                                                  | 31 |

| 3.1 | <b>Overview of Existing BFT SMR Protocols</b> — Example executions of a traditional                      |    |

|     | BFT SMR protocol (left) and the state-of-the-art IGOR protocol (right). Sensor 3 and                     |    |

|     | replica 2 are faulty. The network is not shown.                                                          | 35 |

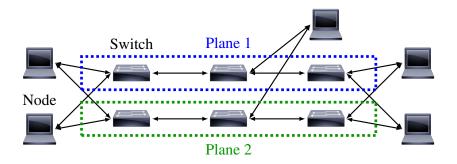

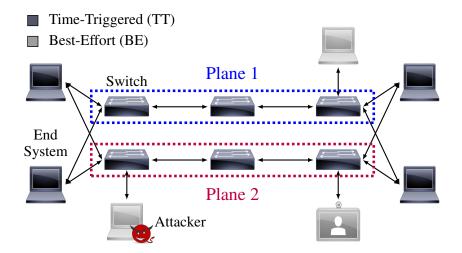

| 3.2 | Redundant Switched Network — Example redundant switched network with two                                 |    |

|     | planes. Nodes here may be replicas, sensors, or actuators. Note that the topology                        |    |

|     | <i>inside</i> a plane can take many different forms, including a star or ring                            | 37 |

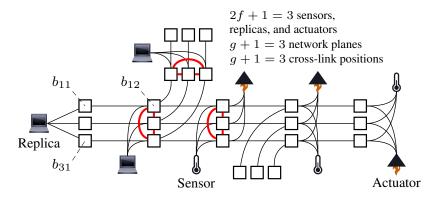

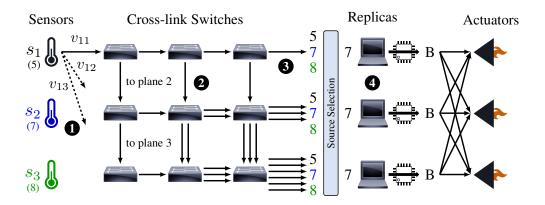

| 3.3 | <b>CROSSTALK's System Model</b> — CROSSTALK's system model when $f = 1$ and                              |    |

|     | g = 2. The squares are switches and the lines are links. The nodes can connect at any                    |    |

|     | position on the network. The <i>only</i> thing we assume that systems in practice may not                |    |

|     | already contain are the cross-links (shown in red).                                                      | 38 |

| 3.4 | <b>Overview of CROSSTALK</b> — Example execution of CROSSTALK ( $f = 1, g = 2$ ).                        |    |

|     | We only show the flow of traffic sent by one sensor to one plane $(v_{11})$ . However, the               |    |

|     | sensor also sends traffic to the other planes ( $v_{12}$ and $v_{13}$ ). Similar traffic flows exist for |    |

|     | each sensor. For clarity we do not depict faults. Note that there may be any number                      |    |

|     | of switches upstream or downstream of the cross-link switches, which are not shown.                      | 41 |

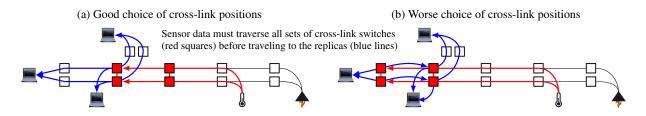

| 3.5                                                                                                   | Choosing Cross-link Positions — Example of strategically choosing cross-link po-                                                                                                                                                                                                                                                                                                                                                                        |                                  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                                       | sitions (red switches) to minimize latency in a system with 3 replicas and 2 planes.                                                                                                                                                                                                                                                                                                                                                                    |                                  |

|                                                                                                       | Only showing one sensor for clarity. Note that in (a), traffic does not deviate from the                                                                                                                                                                                                                                                                                                                                                                | 4.1                              |

| 2.6                                                                                                   | shortest path on its way from the sensor to the replicas.                                                                                                                                                                                                                                                                                                                                                                                               | 41                               |

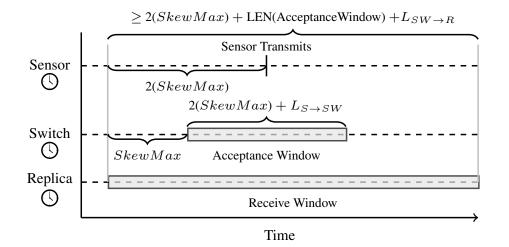

| 3.6                                                                                                   | Suitable Time Bounds — Suitable time bounds for timestamping in CROSSTALK                                                                                                                                                                                                                                                                                                                                                                               | 47                               |

|                                                                                                       | (shown with no skew between devices)                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                               |

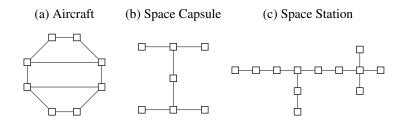

| 3.7                                                                                                   | Network Topologies — Network topologies used in our evaluation. Each figure                                                                                                                                                                                                                                                                                                                                                                             |                                  |

|                                                                                                       | shows the switches in a single network plane                                                                                                                                                                                                                                                                                                                                                                                                            | 51                               |

| 3.8                                                                                                   | <b>CROSSTALK'S Latency</b> — Average worst-case latency of CROSSTALK compared to                                                                                                                                                                                                                                                                                                                                                                        |                                  |

|                                                                                                       | state-of-the-art BFT protocols and NOREP.                                                                                                                                                                                                                                                                                                                                                                                                               | 52                               |

| 3.9                                                                                                   | <b>CROSSTALK's Schedulability</b> — Schedulability improvement when using                                                                                                                                                                                                                                                                                                                                                                               |                                  |

|                                                                                                       | CROSSTALK. Note that IGOR cannot be used on single-core processors                                                                                                                                                                                                                                                                                                                                                                                      | 54                               |

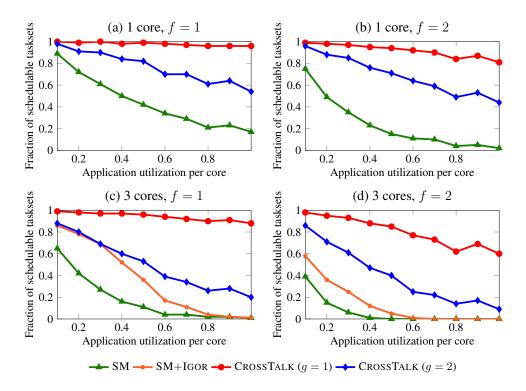

| 3.10                                                                                                  | Impact of Cross-links on Latency — Impact of the total number of cross-link posi-                                                                                                                                                                                                                                                                                                                                                                       |                                  |

|                                                                                                       | tions (the number of switches with cross-links per plane) on CROSSTALK's system-                                                                                                                                                                                                                                                                                                                                                                        |                                  |

|                                                                                                       | wide worst-case latency. We only show up to 7 cross-link positions, since more cross-                                                                                                                                                                                                                                                                                                                                                                   |                                  |

|                                                                                                       | link positions result in no additional latency savings for CROSSTALK. Note that when                                                                                                                                                                                                                                                                                                                                                                    |                                  |

|                                                                                                       | $g = 2$ , CROSSTALK requires $\geq g + 1 = 3$ cross-link positions                                                                                                                                                                                                                                                                                                                                                                                      | 55                               |

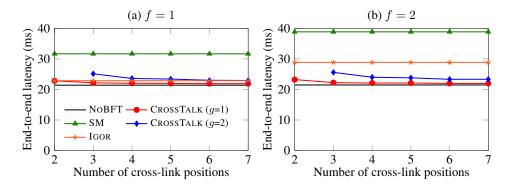

| 3.11                                                                                                  | CROSSTALK'S Communication Overhead — Number of kB received by each                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

|                                                                                                       | replica per plane per sensor in CROSSTALK compared to other protocols                                                                                                                                                                                                                                                                                                                                                                                   | 57                               |

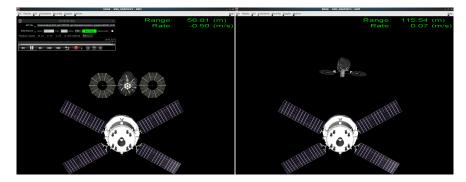

| 3.12                                                                                                  | <b>CROSSTALK Spaceflight Simulation</b> — View from inside and outside the simulated                                                                                                                                                                                                                                                                                                                                                                    |                                  |

|                                                                                                       | capsule after being jettisoned from the rocket.                                                                                                                                                                                                                                                                                                                                                                                                         | 58                               |

|                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| 41                                                                                                    | <b>Example TTE Network</b> — Example of a typical fault-tolerant TTE network with                                                                                                                                                                                                                                                                                                                                                                       |                                  |

| 4.1                                                                                                   | <b>Example TTE Network</b> — Example of a typical fault-tolerant TTE network with redundant planes. The attacker controls a single BE device on a single plane                                                                                                                                                                                                                                                                                          | 64                               |

|                                                                                                       | redundant planes. The attacker controls a single BE device on a single plane                                                                                                                                                                                                                                                                                                                                                                            | 64                               |

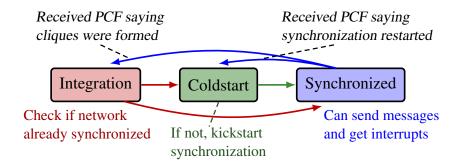

| 4.1<br>4.2                                                                                            | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync                                                                                                                                                                                                                                                                                          |                                  |

| 4.2                                                                                                   | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol                                                                                                                                                                                                                                      | 64<br>66                         |

|                                                                                                       | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol                                                                                                                                                                                                                                      |                                  |

| 4.2                                                                                                   | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol                                                                                                                                                                                                                                      | 66                               |

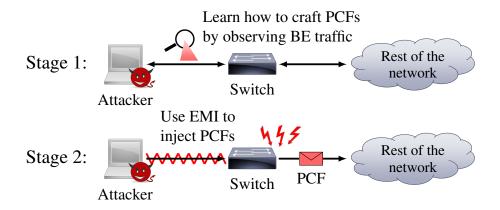

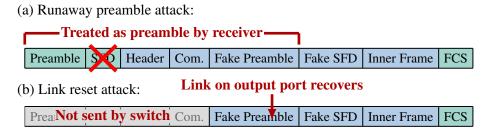

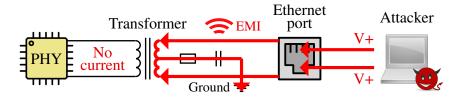

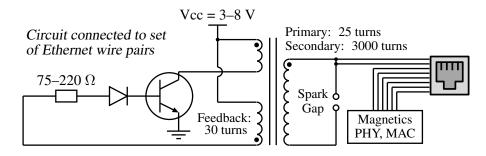

| 4.2<br>4.3                                                                                            | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network |                                  |

| 4.2                                                                                                   | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69                         |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                         | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66                               |

| 4.2<br>4.3                                                                                            | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74                   |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                             | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69                         |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                         | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75             |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                           | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74                   |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                             | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>              | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75             |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                           | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>              | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77<br>78 |

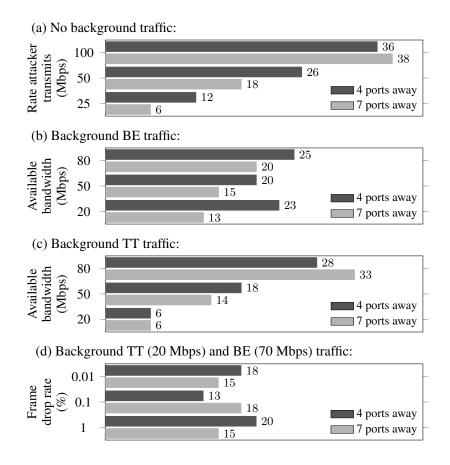

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>              | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77<br>78 |

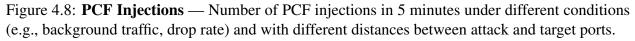

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | redundant planes. The attacker controls a single BE device on a single plane Synchronization State Machine — Simplified version of the state machine that sync masters execute in the TTE synchronization protocol Overview of PCSPOOF — High-level design of PCSPOOF showing the two stages of the attack. First, the attacker learns how to construct malicious synchronization messages. Then, the attacker uses EMI to inject them into the network | 66<br>69<br>74<br>75<br>77<br>78 |

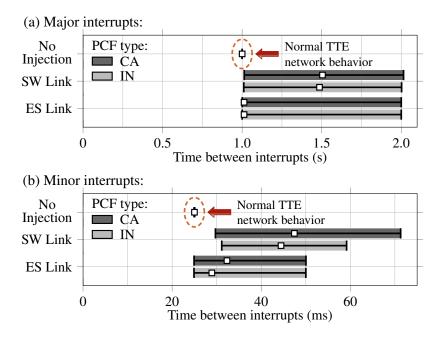

| 4.10 | Impact on Messages — Average-Max-Min charts showing the message delays fol-           |    |

|------|---------------------------------------------------------------------------------------|----|

|      | lowing successful PCF injections on links to switches (SWs) and the sender end sys-   |    |

|      | tem (ES)                                                                              | 85 |

| 4.11 | Asteroid Redirect Mission — NASA spaceflight simulation without (left) and with       |    |

|      | (right) PCSPOOF. PCSPOOF caused a significant deviation in the vehicle's flight path, |    |

|      | which prevented docking                                                               | 87 |

# LIST OF TABLES

### TABLE

| 3.1 | <b>Mass of CROSSTALK</b> — Mass of the replicas and cross-links for each protocol when configured to tolerate different numbers of faults. Results are in kilograms.                                                                                        | 56 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Cost of CROSSTALK — Cost of the replicas and cross-links for each protocol in a                                                                                                                                                                             |    |

|     | typical spaceflight application. Results are in hundreds of thousands of US dollars                                                                                                                                                                         | 56 |

| 4.1 | <b>TTE Device Testing</b> — The table indicates whether TTE switches (SWs) and network cards (NICs) accept PCFs with non-standard preambles. "Too Long, Y, $\leq 11$ bytes" means the device accepts PCFs with longer-than-normal preambles up to 11 bytes. |    |

|     | Devices labeled "1G" are an older generation of devices.                                                                                                                                                                                                    | 76 |

| 4.2 | Successful Injections (Switches) — Percentage of injected PCFs that were accepted on links to switches.                                                                                                                                                     | 83 |

| 4.3 | Successful Injections (End Systems) — Percentage of injected PCFs that were accepted on links to end systems.                                                                                                                                               |    |

| 4.4 | Message Drops — Message drops following successful PCF injections on links to                                                                                                                                                                               |    |

|     | switches and the sender end system.                                                                                                                                                                                                                         | 86 |

### ABSTRACT

Over the past few decades, embedded systems, like those in spacecraft and aircraft, have evolved into complex distributed systems with hundreds of nodes and dozens of network switches. With this shift comes new challenges. One challenge is *performance*. Embedded systems are often required to mask faults. Unfortunately, traditional fault masking approaches, like state machine replication, require nodes to coordinate their actions by exchanging messages over several communication rounds. This means that in modern systems, where these messages often need to traverse multiple switch hops and must compete with hundreds or thousands of other traffic flows, traditional fault masking protocols can have high worst-case latencies that make it difficult or impossible to meet deadlines. For a variety of embedded systems, missing deadlines can be just as dangerous as generating incorrect outputs — potentially even causing system failure. A second challenge is security. As embedded systems have grown, designers have looked for new ways to reduce size, weight, and power. One popular approach is to use mixed-criticality networks, which let systems share a single network between critical and non-critical devices. These networks are designed to ensure that non-critical devices, which often come from unsecured supply chains, have no way to disrupt the critical systems. However, the existence of shared network resources provides a potential means for attackers to bypass these isolation guarantees.

To overcome the performance challenge, I introduce two new Byzantine fault-tolerant (BFT) state machine replication (SMR) protocols that exploit emerging hardware trends in embedded systems. The first, IGOR, exploits the increasing prevalence of multi-core processors. Rather than requiring nodes to agree on a single set of redundant sensor data to execute on, as in traditional protocols, IGOR lets nodes execute on multiple sets of redundant sensor data simultaneously on different cores. A coordination protocol is used in the background to determine which execution will determine the system's final state, reducing the system's latency to the time needed for either execution or coordination — whichever takes longer. The second protocol, CROSSTALK, exploits an increasingly popular network topology, in which messages travel simultaneously through redundant planes of switches. By using novel algorithms to move sensor data back and forth between the redundant planes, CROSSTALK can ensure processing nodes maintain identical state without requiring any communication between the nodes, significantly reducing latency. Moreover, CROSSTALK can be used on even modest single-core embedded processors.

To illustrate the security challenge, I introduce PCSPOOF, a new cyberattack on a popular mixed-criticality network technology called Time-Triggered Ethernet (TTE). TTE is used in a variety of critical systems, including spacecraft, aircraft, and wind turbines. PCSPOOF shows that TTE's switch forwarding rules can allow a malicious non-critical device to infer secret information about the TTE network that can be used to construct fake TTE synchronization messages. By using a small amount of extra circuitry, the malicious device can inject the fake synchronization messages into the network, disrupting the operation of critical systems. Moreover, an attacker can exploit a flaw in the implementation of modern TTE devices to increase the rate of successful injections. PCSPOOF was disclosed to multiple impacted organizations in 2021, including several large spaceflight companies. The disclosure had significant real-world impacts, with multiple organizations acknowledging the attack and implementing defenses. PCSPOOF has also influenced changes to the standard for the TTE synchronization protocol (SAE AS6802).

# **CHAPTER 1**

# Introduction

# 1.1 Background and Trends

Embedded systems are rapidly growing in size, as well as becoming increasingly distributed. For example, the growing complexity of software systems [1, 2], as well as the need for increased onboard autonomy [3], has dramatically increased the number of microprocessors in spacecraft, aircraft, and automobiles [4, 5, 6]. In the past few decades, automobiles have grown from having 15 processors on average [7] to more than 100 [4]. In the same time frame, crewed spacecraft have gone from containing a handful of processors to over 50 [8, 5]. Emerging commercial aircraft are expected to contain hundreds of processors [6]. Similarly, embedded data networks are growing to accommodate the increasing processor counts. Modern commercial aircraft can contain as many as 8 network switches [2], with next-generation aircraft expected to contain more than 10 [6]. Modern spacecraft commonly contain anywhere from 6 to 12 switches [9].<sup>1</sup>

Meanwhile, the importance of fault tolerance in embedded systems is increasing. For example, the growing processor counts in embedded systems mean the probability of a processor fault occurring is increasing, which if not mitigated, could cause a system to fail [12]. Additionally, the desire for faster processing means smaller transistors are being used [13, 14], which are more susceptible to transient upsets from environmental factors like radiation and electromagnetic interference [13, 15]. Moreover, embedded systems are increasingly being asked to autonomously perform safety and mission critical functions that in the past would have been controlled by human operators [3, 16, 17, 18, 19]. For example, crewed spacecraft being developed for deep space missions, such as to asteroids and Mars, will have significant delays when communicating with Earth (e.g., 10–20 minutes [20]) — meaning they cannot be controlled and troubleshooted from Earth like most spacecraft today [3, 21]. Similarly, small modular reactors, which are being developed to reduce the costs and risks of nuclear power production, will be required to operate with near

<sup>&</sup>lt;sup>1</sup>These switch counts do not account for onboard redundancy to tolerate failures, which often doubles or triples the actual number of switches in practice [10, 11].

autonomy to be financially viable [22]. Finally, autonomous automobiles [19] and aircraft [23] will be required to navigate safely without any operator control.

Unfortunately, traditional fault tolerance approaches used in embedded systems scale poorly to large networks. For example, it has been shown that in order for processors to reach agreement on some data in the presence of faults [24] — a common requirement of fault tolerance protocols in practice [25, 26] — the processors must exchange messages with each other over multiple communication rounds [27]. The number of required rounds grows as the number of faults to tolerate increases. This need for multiple communication rounds leads to large system response times [28] — particularly as the number of network hops between processors, as well as the amount of network traffic (which grows with the number of processors), increases. These large response times can make it difficult or impossible for systems to meet certain end-to-end deadlines (i.e., from sensors, to processors, to actuators) [28], which commonly must be on the order of tens of milliseconds to ensure adequate control stability [29, 26]. The problem is compounded by the need for systems to host an increasing number of fault-tolerant functions, which require software tasks be replicated on multiple processors and thus consumes more total processor time — possibly preventing some tasks from being schedulable [28].

Additionally, the growing size of embedded systems, as well as the increasing importance of fault tolerance (and thus need for replication [30]) in these systems, naturally increases size, weight, power, and cost (SWaP-C). In order to counteract this increase, a new trend has emerged in which, instead of using multiple data networks — each optimized for different purposes (e.g., deterministic command and control traffic, high-throughput video streaming), an embedded system will have a single network that is intended to meet the needs of all its subsystems [31, 32, 33, 34]. Such networks are called *mixed-criticality* networks because they allow both highly critical devices and less important commercial-off-the-shelf (COTS) devices to share the same switches [35]. For example, the flight computers and digital engine controllers in an airplane can connect to the same switches as the onboard Wi-Fi access point and passenger entertainment system [35].

The use of a mixed-criticality approach means the network is responsible for isolating critical traffic from non-critical COTS traffic [36]. In other words, even if a COTS device is faulty or compromised by an attacker, it should not be able to interfere with the correct or timely execution of a critical function [36]. This isolation is important, since COTS devices often come from unsecured supply chains and typically do not go through any detailed verification process that would detect tampering [37, 38]. Mixed-criticality networks are rigorously tested and sometimes even formally verified [39] to ensure they provide this isolation under all possible conditions.

# **1.2 Thesis Statement**

At first glance, it appears like the need for coordination between redundant processors [27] means there is no way to avoid the poor performance of traditional fault-tolerant techniques when used in large distributed embedded systems. However, this is not the case. Rather, it is possible to take advantage of recent hardware trends in novel ways in order to counteract large message delays between processors and, as a result, significantly increase performance. Similarly, it appears like mixed-criticality networks are a safe and effective way to reduce the cost of constructing embedded systems. However, even the most rigorously verified network technologies are not infallible. The existence of shared resources means there can still be ways for an attacker to circumvent the isolation guarantees of the network in order to interfere with critical systems.

#### **Thesis Statement**

In this dissertation, I describe new ways to leverage multi-core processors and redundant switched network topologies in order to significantly increase the performance of fault-tolerant embedded systems. In addition, I show how the use of mixed-criticality network technologies can make systems susceptible to a new type of cyberattack from a malicious COTS device.

# **1.3** Dissertation Contributions

### **1.3.1** Leveraging Hardware Trends to Reduce Latency

The first part of this dissertation describes new ways to leverage recent hardware trends to increase the performance of fault-tolerant embedded systems. In particular, I focus on reducing the worst-case latency of Byzantine fault-tolerant (BFT) state machine replication (SMR). BFT SMR is a fault tolerance technique commonly used in critical systems like spacecraft [40, 41], airplanes [26, 42], wind turbines [43], and nuclear reactors [44, 22]. In general, it works by executing identical software simultaneously on multiple processors, or *replicas*. If some of the replicas become faulty — perhaps generating erroneous output — the actuators can perform a majority vote of the outputs of the replicas in order to determine the correct result.

BFT SMR suffers from high latencies due to the need for replicas to reach agreement on sensor data before executing. For example, the replicas may agree to execute on data  $d_1$  from some sensor  $s_1$ , and that  $d_1$  is the median value produced by three redundant sensors. Without agreement, non-faulty replicas could operate on different data and therefore generate different outputs — causing the majority vote at the actuators to fail. Agreement protocols take at least f + 1 communication rounds to tolerate f faults [27], meaning at least f + 1 communication delays are added to the

latency of every execution. Commonly, the agreement process alone can take up more than half the time needed to execute the overall BFT SMR protocol [28].

**IGOR—** Accelerating Byzantine Fault Tolerance with Eager Execution. To address the problem of high latency in BFT SMR, this dissertation introduces the concept of *eager execution*. Eager execution is a speculative computing technique that allows BFT SMR systems to overlay agreement on sensor data with execution, reducing the overall latency to the time taken by the agreement or execution process, whichever is longer. The main challenge of this approach is ensuring nonfaulty replicas operate on the same sensor data. Eager execution overcomes this challenge by exploiting parallelism. Specifically, the approach leverages multi-core processors to allow replicas to execute on data from multiple redundant sensors simultaneously (rather than on data from just one agreed-upon sensor). Each execution is performed on a different core. While these executions are in progress, an agreement process is used to select which sensor's data (i.e., which execution) will determine the system's final state. This dissertation will show that, with this eager execution technique, it is possible to ensure the selected execution was always performed by a majority of non-faulty replicas. Moreover, the selected sensor data is guaranteed to either originate from a non-faulty sensor, or be bounded by data from non-faulty sensors.

The dissertation then describes IGOR, the first BFT SMR protocol to use eager execution. IGOR uses new agreement protocols that work in any network topology (e.g., point-to-point, multidrop bus, switched) and are optimized for the single or multi-fault cases. The standard (single-fault) version of IGOR takes the theoretical minimum number of communication rounds [27] to reach agreement and can use any existing Byzantine agreement protocol [45, 46, 47] as a primitive. Compared to the state-of-the art, it reduces latency by roughly 30% and improves schedulability by  $1.88 \times$  on average. However, it can suffer from large latencies when tolerating multiple faults due to the need to split large messages into fragments. To address this, I introduce a multi-fault optimized version of IGOR that uses a binary reduction technique to convert agreement on arbitrary-length sensor data to agreement on a single bit. This multi-fault optimized protocol can reduce latency by as much as  $1.75 \times$  and improves schedulability by  $3.22 \times$  over the state of the art.

**CROSSTALK**— Making Low-Latency Fault Tolerance Cheap with Redundant Networks. The main shortcoming of IGOR is that, despite its latency and schedulability improvements, it requires execution on multiple cores. This means that it is not possible to use IGOR on low-powered single-core embedded processors [48]. Moreover, even if a multi-core processor is used, the need to perform eager executions on different cores means the capacity for the system to perform other computations is reduced. For example, a taskset that fully utilizes a single core on a non-fault-tolerant system might fully utilize three cores if all tasks were converted to use IGOR.

To overcome this shortcoming, this dissertation presents CROSSTALK, a new BFT SMR protocol that achieves comparable or lower latency than IGOR without requiring multi-core processing. The key insight behind CROSSTALK is that the reason IGOR is potentially expensive is that it makes no assumptions about the network topology — instead treating the replicas as if they are connected by unicast channels. By making *slightly* stronger assumptions about the network topology, it is possible to have significantly lower overheads.

Specifically, CROSSTALK leverages the fact that modern real-time embedded systems are almost universally adopting *redundant switched networks* — i.e., switched networks where fault tolerance is provided by sending messages through redundant planes of switches [49, 11, 50, 51, 52, 53, 54, 55, 56, 57]. CROSSTALK exploits this topology by crossing messages between the planes using special algorithms to ensure no non-faulty replica can receive data from a sensor that other replicas did not also receive. In other words, CROSSTALK solves agreement entirely in the network without requiring communication between replicas. CROSSTALK also leverages special features of modern switches, such as the use of self-checking pairs to mask transmission errors, to avoid the need for voting logic and digital signatures that would otherwise require significant processing time. The result is that CROSSTALK can improve schedulability by  $2.13-4.24 \times$  compared to IGOR, while still staying compatible with networks that systems often use in practice.

In presenting CROSSTALK, this dissertation also proves for the first time the impossibility of tolerating timing faults in synchronous agreement protocols that do not feature any communication between replicas. This proof is important not just for CROSSTALK, but because it shows that some recent results [58] on constructing BFT protocols for embedded systems can actually be incorrect if timing faults are possible.

#### **1.3.2** Compromising Safety in Mixed-Criticality Networks

Like virtually all fault tolerance techniques used in safety and mission-critical real-time systems today [26, 59, 42, 60, 61, 62, 63, 64], IGOR and CROSSTALK make some basic assumptions about the behavior of non-faulty devices. These assumptions include that non-faulty processing nodes are synchronized to one another, and that messages sent over non-faulty network segments will be delivered successfully and by known deadlines.

The second part of this dissertation shifts gears and considers how a malicious actor might break these assumptions in mixed-criticality networks, causing even *non-faulty* processing nodes and network segments to become unpredictable (mimicking the behavior of faulty devices). It specifically focuses on *Time-Triggered Ethernet (TTE)*, a popular technology used in a variety of critical systems, including spacecraft [59, 52, 11], aircraft [65, 66, 67], and wind turbines [68]. The TTE protocol allows safety-critical devices, like flight computers, to communicate with low latency and jitter over multiple redundant planes. TTE's isolation guarantees also allow COTS devices to share the network while ensuring they cannot interfere with the TTE communication.

TTE is perhaps the most well-vetted mixed-criticality network technology in use today, and many of its sub-protocols have been formally verified [39].

**PCSPOOF**— **Compromising the Safety of Time-Triggered Ethernet.** PCSPOOF is the first cyberattack to break TTE's isolation guarantees, allowing a malicious COTS device connected to a TTE network — perhaps compromised by a supply chain attack — to cause resets of the TTE synchronization protocol [32]. Each reset can interfere with the timing of interrupts on critical processors connected to the network, as well as cause TTE messages to be delayed or dropped.

PCSPOOF works by exploiting a weakness in the TTE synchronization protocol, which is that a specific synchronization message, or *protocol control frame (PCF)*, from a trusted switch can cause a processor to detect a clique (a set of processors synchronized to each other, but not to the rest of the system) [69]. Upon detection of a clique, the processor briefly loses synchronization before resynchronizing to the network [32]. Normally, it is impossible for a COTS device to send such a message (it is dropped by the switch). However, by conducting electromagnetic interference (EMI) into the switch through an Ethernet cable, it is possible for a COTS device to send the message and trick the switch into forwarding it to other TTE devices. Moreover, only five circuit components are needed to generate the required EMI, meaning that the current process [37] used for verifying COTS devices for use in critical systems may not detect the malicious circuity.

This dissertation shows that PCSPOOF attacks can be repeated as often as every 10–15 seconds. Each attack can cause TTE devices to lose synchronization for up to a second and drop tens of TT messages — both of which can result in the failure of critical systems like spacecraft or aircraft [26, 29]. It also shows that, in a simulated spaceflight mission, PCSPOOF can cause uncontrolled maneuvers that threaten safety and mission success.

The development of PCSPOOF has had significant impact on real systems. In 2021, the attack was disclosed to multiple organizations, including NASA, ESA, Northrop Grumman, and Airbus, and several have implemented mitigations suggested in this dissertation. The TTE standard, SAE AS6802 [32], is also being updated to enable the use of larger TTE PCFs, which, once incorporated into next-generation devices, will disable the mechanism PCSPOOF uses to trick the switch into forwarding malicious PCFs.

### 1.4 Road Map

The remainder of this dissertation is structured as follows. First, Chapter 2 describes eager execution, a new technique for reducing the latency of BFT SMR in embedded systems, as well as IGOR, the first BFT SMR protocol to use this technique. Next, Chapter 3 describes CROSSTALK, a BFT SMR protocol that improves on the schedulability of IGOR by exploiting common aspects of switched networks used in modern embedded systems. Chapter 4 then describes PCSPOOF, the first attack capable of breaking TTE's isolation guarantees. Finally, Chapter 5 concludes and discusses how future research could build on the work in this dissertation.

# **CHAPTER 2**

# IGOR: Accelerating Byzantine Fault Tolerance with Eager Execution

### 2.1 Introduction

Real-time control systems, such as those in spacecraft and aircraft, often use Byzantine faulttolerant (BFT) state machine replication (SMR) to mask errors due to hardware faults and environmental factors, such as cosmic radiation [62, 63, 61, 70, 71, 64, 44, 42, 72, 14, 73, 74, 75, 40, 26, 76]. In these systems, the same function is performed simultaneously by multiple processors (i.e., *replicas*), each of which receives data from redundant sensors. To ensure that the replicas maintain the same internal state and produce the same output, care must be taken to ensure they operate on the same input data. This is typically accomplished by having the replicas run an *agreement protocol* on the data from each sensor [26, 77, 42]. The replicas then perform a *source selection* to choose a single "best" sensor value as the system input [71, 78, 26]. The source selection step is typically application-specific, and can be as simple as a mid-value selection [71, 26]. Finally, the replicas *execute* on the selected input value.

Unfortunately, this "agree-execute"<sup>1</sup> approach used in traditional BFT SMR systems has a significant drawback: *high latency*. Since any deterministic agreement protocol requires at least f + 1rounds of communication to tolerate f faulty replicas [27], requiring that the replicas reach agreement on inputs *before* executing adds at least f + 1 rounds of communication latency to *every execution* they perform on the incoming data. As we show in §2.6, this additional delay can make it impossible to meet certain hard deadlines. Moreover, even when all deadlines can be met, the added latency results in an unavoidable reduction in real-time control performance and system stability, and thus increases the complexity of the control software to compensate for the extra delay [80].

<sup>&</sup>lt;sup>1</sup>We borrow the term "agree-execute" from [79], but narrow its meaning to refer specifically to BFT systems that agree on inputs before executing.

A standard approach to addressing this challenge in non-real-time systems, such as data centers and blockchains [81, 82, 83, 84, 85, 86], is to adopt *speculative* execution, which forgoes agreement on the inputs altogether and *assumes* the replicas will end up in identical states. In the common case where replicas do not diverge, this approach completely avoids running an agreement protocol. However, when the states do diverge — which can be caused by faulty replicas — the system needs to rollback and repeat previous executions [81, 82, 83, 84, 85]. This outcome is not generally acceptable for real-time systems, since repeating executions can substantially increase worst-case response times, leading to deadline misses.

In this paper, we present IGOR, a novel speculative BFT SMR approach that leverages the increasing prevalence of multi-core processors in real-time embedded systems [14, 48] to enable speculation *without* rollback. The key idea behind IGOR is to *eagerly* execute on the data from redundant sensors simultaneously, without knowing which execution (and thus which sensor) will be used to determine the system's final state. While these executions are underway, the replicas reach agreement on which states to discard and which to keep. As soon as the executions and the agreement process are completed, IGOR can deliver results to the actuators. Thus, when the executions take longer than agreement (which is common in practice, as we show in §2.6), IGOR's end-to-end latency (from sensors to actuators) is the same as that of a non-replicated system — that is, IGOR achieves the *minimum possible latency*. In all other cases, IGOR's ability to overlay agreement and execution inevitably results in latency savings.

It is not sufficient to simply run an existing agreement protocol concurrently with the speculative executions, however. The reason is that, although the source selection algorithm will still select a single "best" sensor value, we cannot guarantee that the selected sensor value has been executed on by enough non-faulty replicas, and thus there may not be enough non-faulty replicas with the same state to out-vote the faulty replicas (c.f. §2.4.1). We solve this problem by introducing new agreement protocols that allow replicas to simultaneously reach agreement on both (1) the sensor values they received *and* (2) how many replicas received each of those sensor values. As such, the protocols are able to guarantee that a given sensor value cannot be selected unless there is a high enough number of replicas claiming to possess the value such that, even if some of those replicas are faulty, a sufficient number of replicas must have executed on the value successfully. Importantly, IGOR can provide this guarantee without sacrificing correctness or using more communication rounds than that of a traditional agreement protocol.

To evaluate IGOR's performance, we implemented a prototype of IGOR in NASA's Core Flight System (cFS) [87], an open-source general-purpose flight software framework used in a variety of real spacecraft, including the Lunar Reconnaissance Orbiter and Parker Solar Probe [88]. Our experimental evaluation shows that, for realistic system configurations, IGOR reduces latency by up to  $1.75 \times$  and improves schedulability by  $1.88-3.22 \times$  compared to the state of the art, and that its latency closely matches the theoretical minimum (produced by a non-replicated system). We also used IGOR to execute simulated guidance, navigation, and control software from a real spacecraft (including multiple genuine flight software components); our evaluation shows that IGOR is able to meet deadlines that existing solutions cannot, leading to improved vehicle stability and performance.

In summary, we make the following contributions:

- IGOR: a speculative BFT SMR system with low latencies in both the presence and absence of faults (§2.4).

- A prototype of IGOR for NASA's cFS framework (§2.5).

- An experimental evaluation of IGOR, including benchmarks (§2.6.1) and schedulability analysis (§2.6.2).

- A case study of IGOR in a spaceflight application (§2.6.5).

# 2.2 Background and Challenges

In this section, we describe how BFT SMR systems are built today and why such a design results in poor performance.

#### 2.2.1 Overview of a BFT SMR System

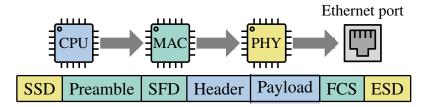

A typical BFT SMR system consists of multiple redundant processors (i.e., replicas) that communicate with a variety of redundant input and output devices [62, 63, 61, 64, 44, 42, 72, 70, 71, 14, 73, 74, 75, 40, 26, 76]. Depending on the application, these devices may include inertial measurement units, star trackers, remote interface units, and engine or thruster controllers. In modern systems, all these devices are connected to a single backbone network [71, 89, 59, 90]. For simplicity, we refer to all input devices as "sensors" and all output devices as "actuators". We refer to each input data item from a sensor as a "value".

To ensure non-faulty replicas never produce conflicting commands, it is necessary to ensure they maintain the same internal state, which in turn requires replicas to operate on the same inputs in the same order. Typically, the *ordering* of the inputs is known a priori (e.g., because system components are synchronized and tasks and traffic patterns are scheduled offline [91]). To ensure that the actual *content* of the inputs is identical, the replicas run an agreement protocol on all inputs before executing [77, 71].

Figure 2.1 illustrates this "agree-execute" approach: ① Each sensor sends its value to each of the replicas; since sensor 3 is faulty, some replicas receive different values from this sensor. ② The replicas then use an agreement protocol to agree on the value from each sensor, and ③ perform

Figure 2.1: **Traditional BFT SMR** — Overview of a traditional agree-execute BFT SMR system. Sensor 3 and replica 4 are faulty.

source selection<sup>2</sup> to choose a single "best" sensor value to use as input for the computation. 4 The replicas then perform the same deterministic computation on the selected input, and thus all non-faulty replicas end up with the same state. The replicas use the state to determine the system output, then send the output to the actuators.<sup>3</sup> 5 The actuators use a majority vote to mask the output of a bad replica.

Notice that if the replicas *did not* run an agreement protocol before executing, then the source selection could result in different non-faulty replicas using different sensor values as their inputs, which would cause their internal states to diverge.

### 2.2.2 Drawbacks of the Agree-Execute Approach

Real-time systems require low latency for tight control loops and hazard response. Unfortunately, traditional BFT SMR systems suffer from high latency, as the replicas must reach agreement before executing and the latency of the agreement protocol is often significant.

The latency of an agreement protocol depends on two factors: the *number* of communication rounds in the protocol and the *length* of each round. A round must be large enough to ensure all messages sent at the start of a round are received by the end of that round [45, 46, 92]. Therefore, the round length must be at least as large as the worst-case traversal time (WCTT) of a message over the network.

In large systems like spacecraft and aircraft, which commonly have thousands of traffic flows and large networks spanning multiple switches [57, 93, 94], the message WCTT — and thus mini-

<sup>&</sup>lt;sup>2</sup>The source selection process is typically application-specific; it could be as simple as a mid-value selection [26].

<sup>&</sup>lt;sup>3</sup>A state change does not always require an output to be sent to the actuators.

mum round length — can be on the order of *several milliseconds* [93, 94, 95, 96, 57]. For example, in deterministic Ethernet (AFDX [31]) networks used in avionic systems, the WCTT can be up to 3–4 ms for individual Ethernet frames [57, 96]. Large messages must be fragmented into multiple frames sent *at least* 1 ms apart [31], and more commonly 4+ ms apart [57], which can result in message WCTTs that are multiple times that of a single frame [31]. We note that since agreement protocols often require replicas to send increasingly larger messages in each round [46, 45, 92, 97, 98], fragmentation is common, even if the data to agree on is small. For example, agreeing on 250 bytes in a typical 1 fault-tolerant BFT SMR system (4 replicas, where 1 replica may be faulty) requires replicas to broadcast 2250 bytes of data in the second round, which must be fragmented across at least 2 Ethernet frames. Agreeing on 1200 bytes would require 8 fragments.

Time-triggered networks [34, 99, 32, 100] can reduce frame WCTTs to hundreds of microseconds [89, 101]. However, if the frame WCTT is short, the round length is then dictated by other factors. For example, each round cannot be shorter than the period at which the network schedule lets devices access the network, which is often on the order of milliseconds to avoid delaying or dropping other traffic [102, 89]. Further, the round length cannot be shorter than what the *soft-ware* schedule allows. For example, replicas typically communicate through a dedicated I/O task or partition that executes with a fixed period [103, 104], which is often 10+ ms to avoid excessive processing overhead [105, 104]. Lastly, large messages still need to be fragmented across multiple time slots [95].