## ELECTROMAGNETIC MODELING OF HIGH-SPEED HIGH-FREQUENCY INTERCONNECTS

by Jong-Gwan Yook

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1996

RL-944 = RL-944

$\bigcirc \qquad \frac{\text{Jong-Gwan Yook}}{\text{All Rights Reserved}} \, \frac{1996}{\text{Supplement of the properties}} \, \frac{1996}{\text{Supp$

This thesis is dedicated to my parents in memory of their devotion and selfless love

#### ACKNOWLEDGEMENTS

This piece of work presented as a form of Ph.D. dissertation would not have been possible without help of many individuals, of whom it is almost impossible to mention all, encountered in my life. Herein, I would like to take a chance to thank those people who have encouraged and cultivated my intellectual growth and enriched my daily life in Ann Arbor for the last five and half years, and hopefully forever.

My first sincere gratitude goes to my advisor, Professor Linda Katehi, since without her support, understanding, and technical expertise, this research would have been a much more difficult and painful journey. Her enthusiasm for research and teaching has made her a symbol for me of a devoted scientist and educator. I would also like to thank all of my committee members: Professor Karem Sakallah for his guidance on the digital circuit aspect of my research, Professor Kamal Sarabandi for his sincere interest in and suggestions on my dissertation, Dr. Rainee Simons in NASA Lewis Research Center for his expertise on high-frequency packages and transitions, and Dr. Hal Marshall for his endless support on parallel computing.

The diversity and abundance of technical facilities and programs at the Radiation Laboratory in the University of Michigan have led me to taste and realize the importance of interdisciplinary educations. In particular, my friends, Dr. Paul Siqueira, Dr. Kazem Sabetfakhri, Messrs. Tayfun Özdemir, Stephane Legault, Sunil Bindiganavale, and many more, too numerous to mention, deserve my deepest thanks for

their close friendship and technical discussions immersed in this thesis. Drs. Yisok Oh and Howard Yoon have to be recognized for their encouragement and support throughout my graduate career.

As a successful graduate student studying far from home, I felt always comfortable and enjoyable with many friends in the church, Ann Arbor Korean Catholic Student Association, and they deserve my warm appreciation. Especially, I wish to thank loving God for letting me know such good friends: Mr. Sang Yeol Park, Dr. Young Ro Byun, Messrs. Jong Yul Choi, Dong Wook Lee, Eun Suk Choi, and their families.

I have received financial support from Intel Co. for the last four and half years, and I would like to thank them for their interest in the research I have done. I always found it helpful and informative to talk to people at Intel, especially Drs. Tawfik Arabi and Tim Schreyer. They have my sincere appreciation. I also wish to express my appreciation to Dr. Rod Johnson for his time and effort to review and correct my dissertation from the acknowledgement to abstract.

Most importantly, I wish to express my deep gratitude to my family members: my father for his intelligence, endurance and patience, my mother for her wisdom and selfless devotion, my elder brother for his humanity, and my younger sister for her understanding and support.

**ABSTRACT**

ELECTROMAGNETIC MODELING OF HIGH-SPEED HIGH-FREQUENCY

INTERCONNECTS

by

Jong-Gwan Yook

Chair: Linda P. B. Katehi

This dissertation develops in detail an approach to a three-dimensional full-wave elec-

tromagnetic field simulator, namely the finite element method (FEM), and applies

it to various high-speed high-frequency interconnects, ranging from a simple via hole

to an entire K/Ka-band MMIC phase shifter package. This approach has several

essential features: the utilization of tetrahedron-based edge basis functions render-

ing spurious-free solutions, a non-uniform structured mesh generator giving flexible

modeling capabilities, and implementation of artificial absorbing layers helping to

simulate open boundary problems. In addition, the FEM is fully parallelized on a

distributed memory machine (the IBM SP2). Two different parallelization strategies

are implemented, among which the task parallelization strategy provides linearly scal-

able performance improvement due to the minimal communication overhead among

the processors.

With all the above features, the parallelized FEM has been successfully applied to the characterization of planar/non-planar high frequency interconnects, hermetic transitions, and K/Ka-band MMIC packages. In particular, the undesirable internal package resonances and energy leakages in the MMIC package are identified, and furthermore, a few mechanisms for the suppression of the above phenomena are suggested, and these are supported by rigorous numerical data. The lumped equivalent circuits for the vertical via holes are utilized in the system level EM modeling to provide appropriate inductances and capacitances. In this dissertation, characterization of various high-frequency interconnects has been stressed as well as parametric study.

Special attention is devoted to development of the system level electromagnetic modeling for high-speed digital circuits and packages. This system level modeling is achieved by combining the FEM and the well known circuit simulator, HSPICE. It is based on the so-called tiling processor, which generates equivalent circuits for PCBs and ICs, and then the circuit simulator is employed for time or frequency domain characterizations. The hybrid approach implemented in this study renders effective simulations in frequency as well as time domain for a given geometry. The detailed derivation and applications of the system level electromagnetic modeling tool are described. Its validity and accuracy are proved by modeling the INTEL P6 board and package containing eight layers of signal, power, and ground planes and hundreds of signal traces.

## TABLE OF CONTENTS

| DEDICATIO         | N                                                                  | i        |

|-------------------|--------------------------------------------------------------------|----------|

| ACKNOWLE          | DGEMENTS                                                           | i        |

| LIST OF FIG       | URES i                                                             | Ż        |

| LIST OF TAR       | BLES                                                               | į,       |

| LIST OF API       | PENDICES                                                           | :3       |

| CHAPTER           |                                                                    |          |

| I. INTR           | ODUCTION                                                           | -        |

| 1.1               | Motivation and Background                                          | -        |

| 1.2               | Objectives                                                         | 4        |

| 1.3               | Overview                                                           | (        |

|                   | ORETICAL METHODOLOGY: 3D VECTOR FINITE EL-                         | í        |

| 2.1               |                                                                    |          |

| $2.1 \\ 2.2$      |                                                                    | 9        |

| $\frac{2.2}{2.3}$ | Vector Wave Equation                                               | 12       |

| $\frac{2.3}{2.4}$ | Basis and Weighting Functions                                      |          |

| 2.5               | Assembly of Matrix Equation and Its Solution Methods               |          |

| 2.6               |                                                                    | 2        |

|                   | 2.6.1 Boundary Conditions                                          | 2        |

|                   | v v                                                                | 2        |

| 2.7               | The Question of Spurious Solutions: A Rationale for Using the Edge |          |

|                   |                                                                    | 28       |

|                   | C 1                                                                | 28       |

|                   | ·                                                                  | 29<br>3: |

| 2.8               | •                                                                  | ).<br>3: |

| $\frac{2.0}{2.9}$ |                                                                    | 3;       |

|                   |                                                                    | 39       |

| = 3 = 0           | -                                                                  | 1;       |

|                   |                                                                    | 15       |

|       | 2.11                                                                 | Passive Lumped Elements                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                  |

|-------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|       |                                                                      | 2.11.1 Volume Current Method                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                                  |

|       |                                                                      | 2.11.2 Surface Impedance Method                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                                  |

| III.  | VALII                                                                | DATION AND PARALLELIZATION                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                  |

|       | 3.1                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                                  |

|       | 3.2                                                                  | Eigenvalue Problems                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                  |

|       |                                                                      | 3.2.1 Lossless Cavities                                                                                                                                                                                                                                                                                                                                                                            | 55                                                                                  |

|       |                                                                      | 3.2.2 Lossy Cavities                                                                                                                                                                                                                                                                                                                                                                               | 60                                                                                  |

|       |                                                                      | 3.2.3 Summary                                                                                                                                                                                                                                                                                                                                                                                      | 62                                                                                  |

|       | 3.3                                                                  | Parallelization                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                  |

|       |                                                                      | 3.3.1 Motivations                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                                  |

|       |                                                                      | 3.3.2 Parallelization Strategies                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                  |

|       |                                                                      | 3.3.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                   | 71                                                                                  |

|       | 3.4                                                                  | Performance of the Artificial Absorbers                                                                                                                                                                                                                                                                                                                                                            | 72                                                                                  |

|       |                                                                      | 3.4.1 Microstrip Thru Line                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                  |

|       |                                                                      | 3.4.2 Microstrip Junction Terminated with Absorber                                                                                                                                                                                                                                                                                                                                                 | 74                                                                                  |

|       |                                                                      | 3.4.3 CPW Series Stub                                                                                                                                                                                                                                                                                                                                                                              | 75                                                                                  |

|       |                                                                      | 3.4.4 CPW Series Stub: Open Structure                                                                                                                                                                                                                                                                                                                                                              | 77                                                                                  |

|       |                                                                      | 3.4.5 Waveguide Absorber                                                                                                                                                                                                                                                                                                                                                                           | 79                                                                                  |

|       |                                                                      | 3.4.6 Summary                                                                                                                                                                                                                                                                                                                                                                                      | 80                                                                                  |

|       | 3.5                                                                  | Conclusions                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                                  |

| 1 V . |                                                                      | JAR/NON-PLANAR HIGH FREQUENCY INTERCON-                                                                                                                                                                                                                                                                                                                                                            | 0.4                                                                                 |

|       |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                                  |

|       | 4.1                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                       | 84                                                                                  |

|       | 4.2                                                                  | Microstrip Short Circuit                                                                                                                                                                                                                                                                                                                                                                           | 84<br>87                                                                            |

|       | 4.2 4.3                                                              | Microstrip Short Circuit                                                                                                                                                                                                                                                                                                                                                                           | 84<br>87<br>93                                                                      |

|       | 4.2                                                                  | Microstrip Short Circuit                                                                                                                                                                                                                                                                                                                                                                           | 84<br>87<br>93<br>98                                                                |

|       | 4.2 4.3                                                              | Microstrip Short Circuit                                                                                                                                                                                                                                                                                                                                                                           | 84<br>87<br>93<br>98                                                                |

|       | 4.2<br>4.3<br>4.4                                                    | Microstrip Short Circuit  Microstrip Ground Pad                                                                                                                                                                                                                                                                                                                                                    | 84<br>87<br>93<br>98<br>98<br>101                                                   |

|       | 4.2<br>4.3<br>4.4                                                    | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition                                                                                                                                                                                                                   | 84<br>87<br>93<br>98<br>98<br>101<br>103                                            |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                      | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole                                                                                                                                                                   | 84<br>87<br>93<br>98<br>98<br>101<br>103                                            |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                               | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole                                                                                                                                                  | 84<br>87<br>93<br>98<br>98<br>101<br>103<br>107                                     |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                      | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions                                                                                                                     | 844<br>87<br>93<br>98<br>98<br>101<br>103<br>107<br>111<br>118                      |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                               | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition                                                                                            | 844<br>87<br>93<br>98<br>98<br>101<br>103<br>107<br>111<br>118<br>118               |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                        | Microstrip Short Circuit Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition                                                                | 844<br>87<br>93<br>98<br>101<br>103<br>107<br>111<br>118<br>118<br>121              |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                        | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition  CPW-to-Waveguide Transition                                  | 84<br>87<br>93<br>98<br>98<br>101<br>103<br>107<br>111<br>118<br>118<br>121<br>123  |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                        | Microstrip Short Circuit Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition  CPW-to-Waveguide Transition  Numerical Convergence            | 844<br>87<br>98<br>98<br>101<br>103<br>107<br>111<br>118<br>112<br>123<br>128       |

|       | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                        | Microstrip Short Circuit  Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition  CPW-to-Waveguide Transition                                  | 844<br>87<br>98<br>98<br>101<br>103<br>107<br>111<br>118<br>112<br>123<br>128       |

| V.    | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Microstrip Short Circuit Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole  Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole  Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition  CPW-to-Waveguide Transition  Numerical Convergence            | 84<br>87<br>93<br>98<br>101<br>103<br>107<br>111<br>118<br>121<br>123<br>128<br>130 |

| V.    | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Microstrip Short Circuit Microstrip Ground Pad  CPW-to-Microstrip Through-Via Transition  4.4.1 Without Via Hole  4.4.2 With Via Hole Channelized CPW-to-Microstrip Transition  Asymmetric 2-port Via with Plated-Through-Hole Double Via Hole  CPW-to-Slotline Transitions  4.8.1 Planar Transition  4.8.2 Non-Planar Transition  CPW-to-Waveguide Transition  Numerical Convergence  Conclusions | 84<br>87<br>93<br>98<br>101<br>103<br>107<br>111<br>118<br>121<br>123<br>128<br>130 |

|      |      | 5.2.1 Open Transition Through a CPW Section                   | 137 |

|------|------|---------------------------------------------------------------|-----|

|      |      | 5.2.2 Closed Transition Through a CPW Section                 |     |

|      |      | 5.2.3 Vertical Wire Grounding                                 |     |

|      |      | 5.2.4 Rectangular Via Hole Grounding                          |     |

|      |      | 5.2.5 Extended Rectangular Via Hole Grounding                 |     |

|      |      | 5.2.6 PEC Wall Grounding                                      |     |

|      |      | 5.2.7 Microstrip-through-CPW Transition With Hermetic Wall    |     |

|      |      | 5.2.8 W-Band Application of the Hermetic Transition           |     |

|      | 5.3  | Inter-Chip Transition: Hermetic Bead Transition               |     |

|      |      | 5.3.1 Squire Dielectric Ring                                  |     |

|      |      | 5.3.2 Circular Dielectric Ring                                |     |

|      | 5.4  | Conclusions                                                   |     |

| VI.  | K/Ka | -BAND MMIC PACKAGE                                            | 159 |

|      | 6.1  | Introduction                                                  | 159 |

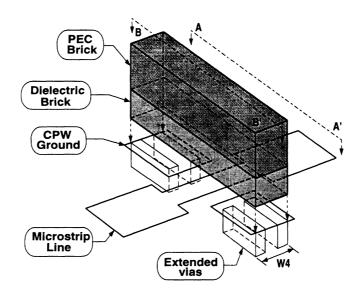

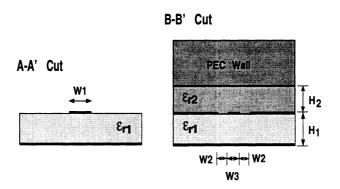

|      | 6.2  | Modeling of the Package                                       | 162 |

|      | 6.3  | Numerical and Experimental Results and Discussions            | 164 |

|      |      | 6.3.1 Modeling of Isolated Symmetric Package                  | 164 |

|      |      | 6.3.2 Modeling of Isolated Asymmetric Package                 | 166 |

|      |      | 6.3.3 Modeling of Asymmetric Package Placed in a Test Fixture | 169 |

|      | 6.4  | Features Which Can Enhance Package Performance                | 170 |

|      |      | 6.4.1 Asymmetric Package with Additional Metal Filled Vias .  | 170 |

|      |      | 6.4.2 Asymmetric Package with Resistive Coated Lid            | 175 |

|      |      | 6.4.3 Asymmetric Package with Lossy Dielectric Frame          | 175 |

|      | 6.5  | Conclusions                                                   | 177 |

| VII. | SYST | EM LEVEL EM MODELING OF DIGITAL ICs AND PACK-                 | •   |

|      | AGES | 3                                                             | 179 |

|      | 7.1  | Introduction                                                  | 179 |

|      | 7.2  | Problem Statement and Previous Work                           |     |

|      | 7.3  | PCB Tiles and their Lumped Equivalent Circuits                |     |

|      |      | 7.3.1 Tiling Procedure                                        |     |

|      |      | 7.3.2 Equivalent Circuits                                     |     |

|      | 7.4  | Simulation Results                                            |     |

|      |      | 7.4.1 Convergence Test: Tiling Optimization                   |     |

|      |      | 7.4.2 Seven Drivers with Decoupling Capacitors                |     |

|      |      | 7.4.3 Modeling of Signal Traces                               |     |

|      |      | 7.4.4 Split PCBs                                              |     |

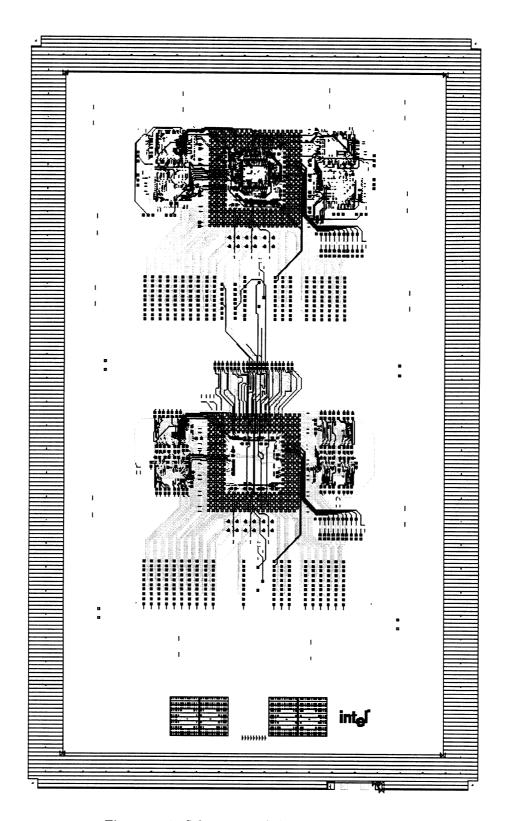

|      |      | 7.4.5 Intel P6 Gadget                                         | 209 |

|      |      | 7.4.6 Summary                                                 |     |

|      | 7.5  | Conclusions                                                   |     |

| III. | CON  | CLUSIONS                                                      | 215 |

|      | Q 1  | Summary of Achievements                                       | 91: |

| 8.2       | Suggested Future Work | 217 |

|-----------|-----------------------|-----|

| APPENDICE | S                     | 219 |

| BIBLIOGRA | PHY                   | 233 |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                |    |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

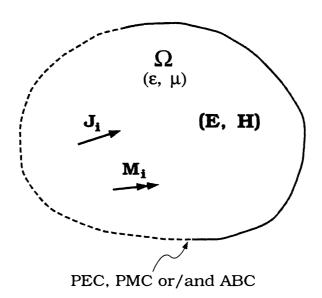

| 2.1    | Geometry of three dimensional volume which has current sources $J_i$ and/or $M_i$ with possible material inhomogeneities and geometrical discontinuities. The boundary of the volume V is closed by some combination of PEC, PMC, and ABC                                                                                                      | 11 |

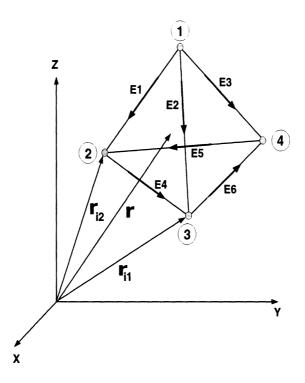

| 2.2    | Tetrahedral element and associated nodes and edges definitions. The circled numbers 1 to 4 represent four node labels and $E1$ to $E6$ six edges associated with those nodes. $\mathbf{r}_{i1}$ and $\mathbf{r}_{i2}$ are node vectors associated with the $i^{th}$ edge and $\mathbf{r}$ is an arbitrary vector which lies in the tetrahedron | 15 |

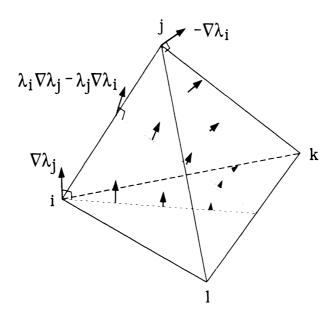

| 2.3    | Behavior of edge element $\mathbf{W}_p^e$ for edge $p=\{i,j\}$                                                                                                                                                                                                                                                                                 | 17 |

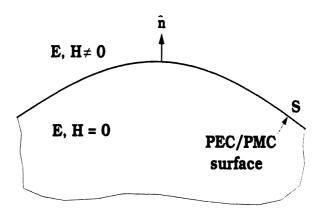

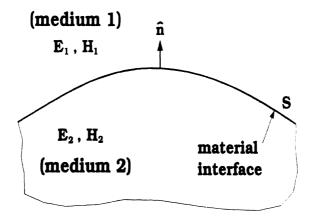

| 2.4    | PEC or PMC surface $S$ with outward unit normal vector $\hat{\mathbf{n}}.$                                                                                                                                                                                                                                                                     | 22 |

| 2.5    | Material interface $S$ with unit normal vector $\hat{\mathbf{n}}$                                                                                                                                                                                                                                                                              | 23 |

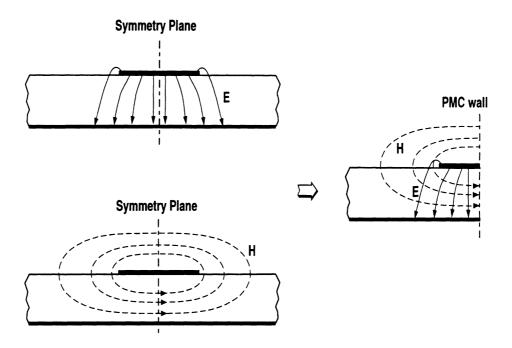

| 2.6    | An example of a circuit configuration (microstrip line) bearing a symmetrical plane at the center and its electric and magnetic field distributions. As presented on the right, the original problem can be replaced with half of the structure, with PMC symmetry condition on one side                                                       | 24 |

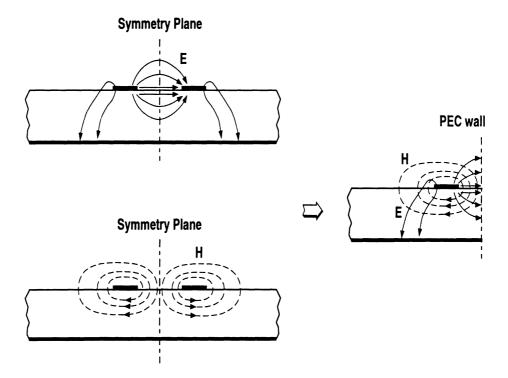

| 2.7    | An example of a circuit configuration (double strip line) containing symmetry at the center and its electric and magnetic field distributions. The original problem can be replaced with the half of the structure with PEC symmetry condition at the center as shown on the right                                                             | 25 |

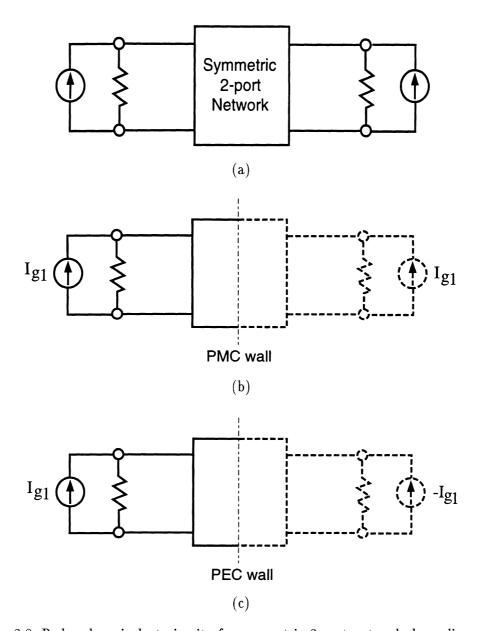

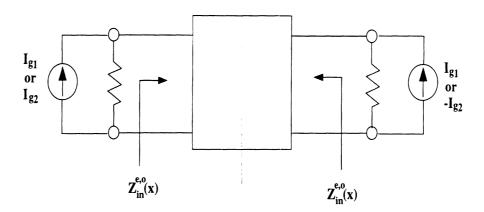

| 2.8    | Reduced equivalent circuits for symmetric 2-port network depending on excitation configurations: (a) original network, (b) reduced equivalent network for even mode excitation, and (c) reduced equivalent network for odd mode excitation.                                                                                                    | 26 |

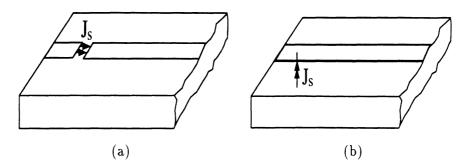

| 2.9    | Two types of ideal excitation configurations: (a) horizontal current source on the transmission line plane. (b) vertical current source                                                                                                                                                                                                        | 35 |

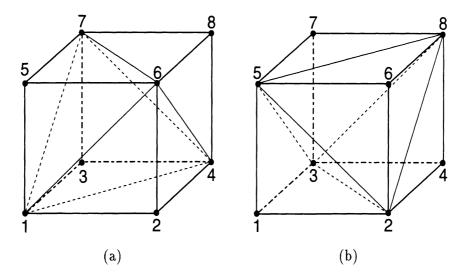

| 2.10   | Two types of rectangular bricks which containing five tetrahedral elements:                                                                                                                                                                                                                                                                    | 26 |

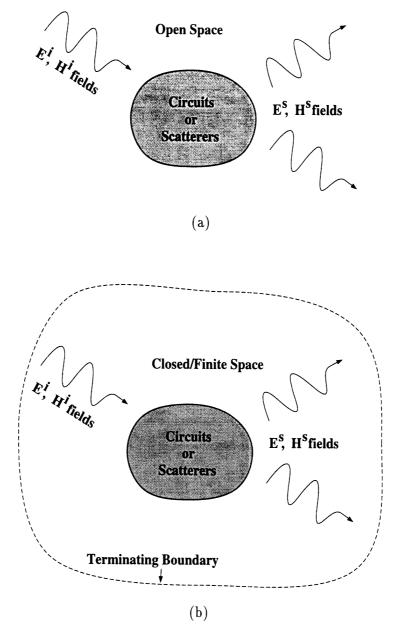

| 2.11 | Treatment of open boundary problem: (a) Original open boundary problem, (b) Equivalent closed/finite boundary problem                                                                                                                                                                                                                                                          | 41 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

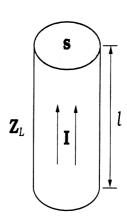

| 2.12 | Impedance load                                                                                                                                                                                                                                                                                                                                                                 | 48 |

| 2.13 | Resistive sheet and equivalent thin dielectric layer                                                                                                                                                                                                                                                                                                                           | 50 |

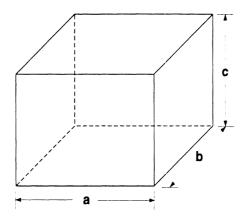

| 3.1  | Rectangular cavity having PEC walls and dimensions a, b, and c in x-, y-, and z-direction, respectively.                                                                                                                                                                                                                                                                       | 56 |

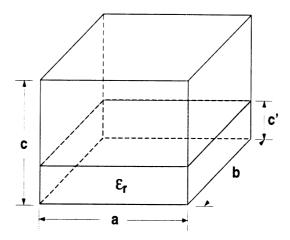

| 3.2  | Partially-filled rectangular cavity having dielectric material with $\epsilon_r$ and thickness $c'$                                                                                                                                                                                                                                                                            | 57 |

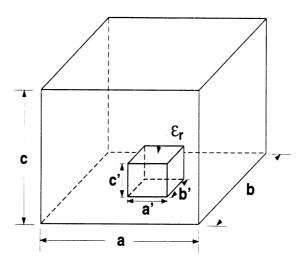

| 3.3  | Rectangular cavity having dielectric cube at the center of the cavity bottom having dielectric constant $\epsilon_r$ and $a'$ , $b'$ , and $c'$ in x-, y-, and z-dimension, respectively                                                                                                                                                                                       | 59 |

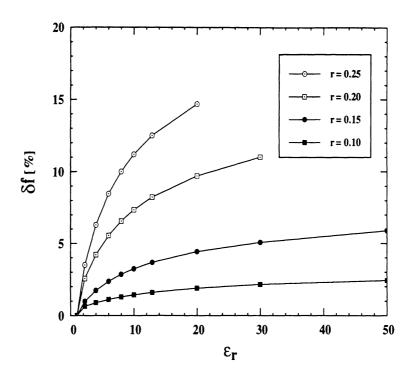

| 3.4  | Variation of the resonant frequency of the dominant mode for various size and $\epsilon_r$ of the dielectric material                                                                                                                                                                                                                                                          | 60 |

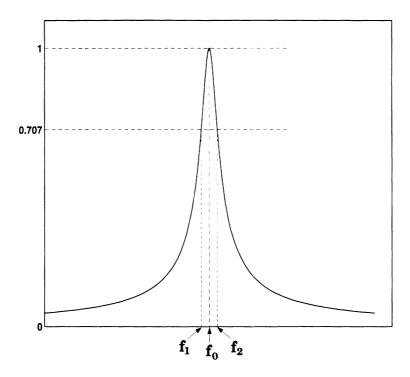

| 3.5  | Typical resonance curve of a lossy cavity. The quality factor $Q$ is defined based on the center frequency, $f_0$ , and two adjacent frequency points, $f_1$ and $f_2$                                                                                                                                                                                                         | 61 |

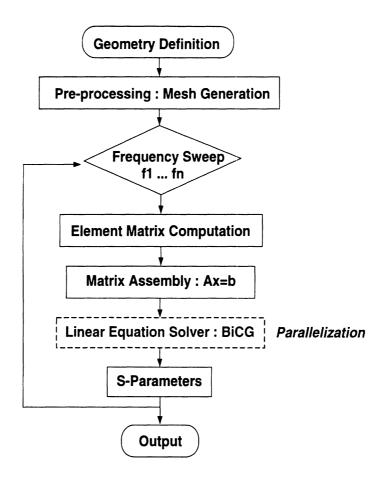

| 3.6  | Parallelization of the linear equation solver, BiCG method, in the FEM scheme.                                                                                                                                                                                                                                                                                                 | 64 |

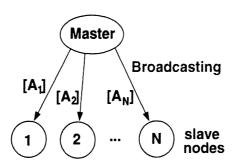

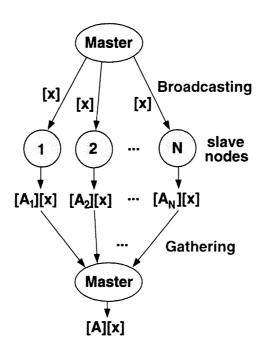

| 3.7  | Parallelization of the matrix-vector multiplication. Step 1: broadcast the partitioned FEM matrix $[A_i]$ . Step 2: broadcast the vector $[x]$ in every iteration. Step 3: perform partial matrix-vector multiplication $[A_i][x]$ on each machine, where $[A] = \cup [A_i]$ for $i = 1, \ldots, N$ . N is the number of slave nodes. Step 4: gather the results to form $[b]$ | 66 |

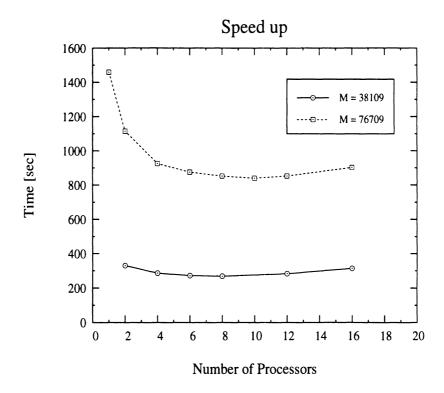

| 3.8  | Speedup curves of the parallel matrix-vector multiplication for two different problem sizes. M indicates the number of unknowns                                                                                                                                                                                                                                                | 68 |

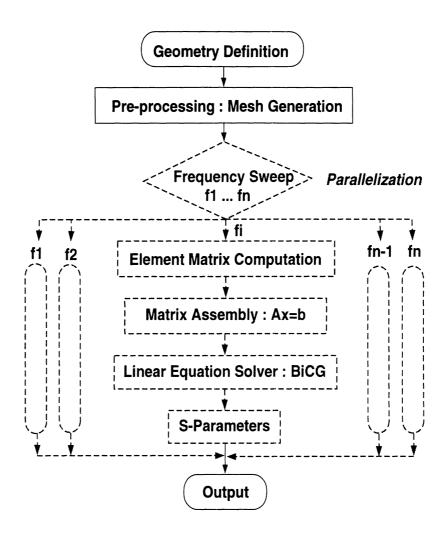

| 3.9  | The concept of the task parallelization.                                                                                                                                                                                                                                                                                                                                       | 70 |

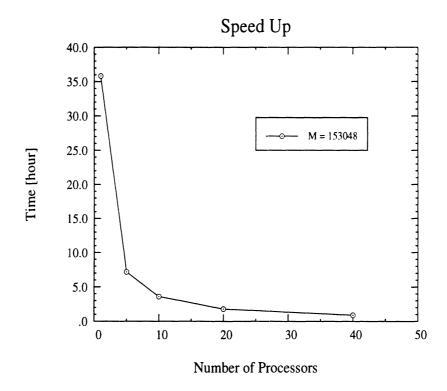

| 3.10 | Speedup curve for the task parallelization.                                                                                                                                                                                                                                                                                                                                    | 71 |

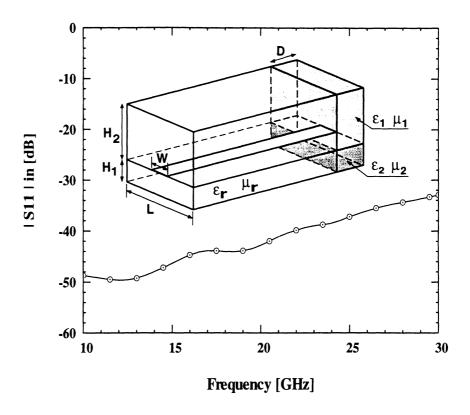

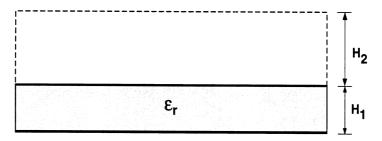

| 3.11 | Computed return loss for the microstrip line terminated with artificial absorbers. Geometrical and material factors: $L=6.38$ mm, $W=1.3$ mm, $D=5.0$ mm, $H_1=0.635$ mm, $H_2=3.365$ mm, $\epsilon_r=3.4$ , $\mu_r=1.0$ , $\epsilon_1=1.0+j3.0$ , $\mu_1=1.0+j3.0$ , $\epsilon_2=3.4+j10.0$ , and $\mu_2=1.0+j2.9412$                                                         | 74 |

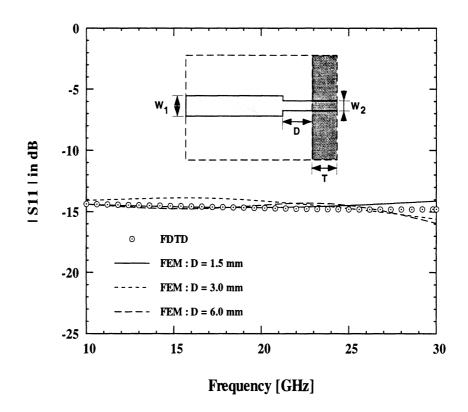

| 3.12 | Computed return loss for the microstrip junction terminated with artificial absorbers. Absorbers are placed at the side and top walls also in addition to the termination end. Geometrical factors: $W_1 = 1.3 \text{mm}$ , $W_2 = 0.6 \text{mm}$ , and $T = 3.0 \text{mm}$ . The thickness and the dielectric constant of the substrate are $H = 0.635 \text{mm}$ and $\epsilon_r = 3.4$ . The absorbers at the end are chosen as: $\epsilon_1 = 1.0 + j15.0$ and $\mu_1 = 1.0 + j15.0$ for the air side and $\epsilon_2 = 3.4 + j15.0$ and $\mu_2 = 1.0 + j4.412$ for the dielectric side. | 76 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

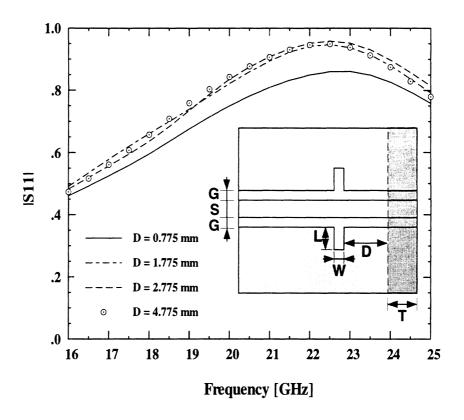

| 3.13 | Computed return loss for the CPW series stub terminated with artificial absorbers (closed structure) at 4 different positions. Geometrical factors: $G=0.225 \mathrm{mm},\ S=0.45 \mathrm{mm},\ L=1.35 \mathrm{mm},\ W=0.225 \mathrm{mm},\ \mathrm{and}\ T=2.0 \mathrm{mm}.$ The thickness and the dielectric constant of the substrate are $H=0.635 \mathrm{mm}$ and $\epsilon_r=9.9$ . The absorbers at the end are chosen as: $\epsilon_1=1.0+j15.0$ and $\mu_1=1.0+j15.0$ for the air side and $\epsilon_2=9.9+j20.0$ and $\mu_2=1.0+j2.02$ for the dielectric side                      | 77 |

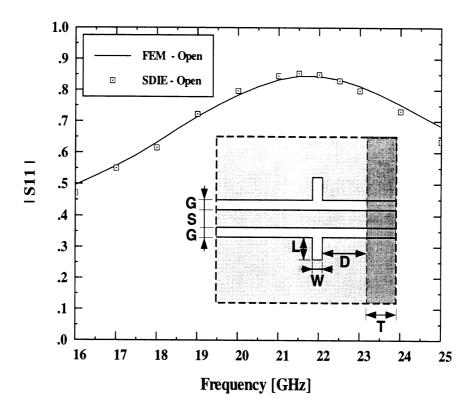

| 3.14 | Computed return loss for the CPW series stub terminated with artificial absorbers (open structure). Geometrical factors: $G=0.225 \mathrm{mm}$ , $S=0.45 \mathrm{mm}$ , $L=1.35 \mathrm{mm}$ , $W=0.225 \mathrm{mm}$ , $D=1.775 \mathrm{mm}$ and $T=2.0 \mathrm{mm}$ . The thickness and the dielectric constant of the substrate are $H=0.635 \mathrm{mm}$ and $\epsilon_r=9.9$ . The absorbers at the end are chosen as: $\epsilon_1=1.0+j15.0$ and $\mu_1=1.0+j15.0$ for the air side and $\epsilon_2=9.9+j20.0$ and $\mu_2=1.0+j2.02$ for the dielectric side                            | 78 |

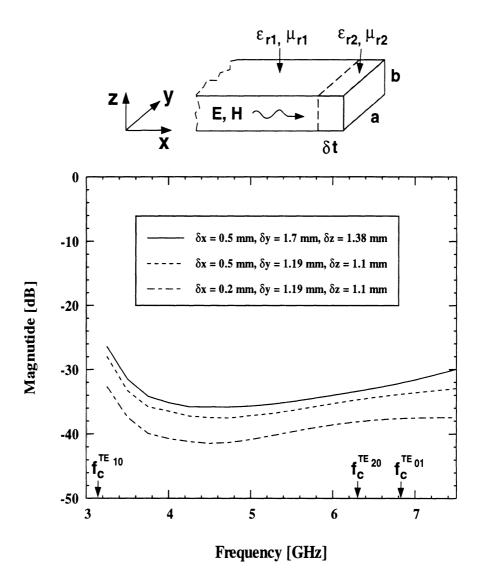

| 3.15 | Computed reflection coefficient of the artificial absorber in a waveguide designed for absorption of the dominant $TE_{10}$ mode as a function of mesh size $(\delta x,  \delta y,  \text{and}  \delta z)$ in the absorber region. Geometrical and material parameters of the waveguide: $a=47.6  \text{mm},  b=22.0  \text{mm},  \epsilon_{r1}=1.0,  \text{and}$ $\mu_{r1}=1.0$ . The thickness of the absorber, $\delta t$ , is $0.041\lambda_g$ (5.0 mm) at 4.0 GHz. $f_c^{TE_{10}}$ , $f_c^{TE_{20}}$ , and $f_c^{TE_{01}}$ are the cutoff frequency of each mode                        | 81 |

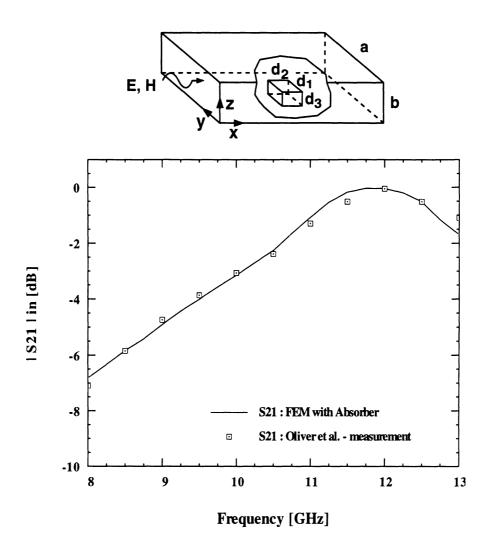

| 3.16 | Computed transmission coefficient for a conducting cube of dimensions $d_1=d_2=9.0$ mm and $d_3=6.0$ mm. The width and height of the waveguide: $a=22.86$ mm and $b=10.16$ mm. The thickness of the absorber at the end of the waveguide is fixed to $5.0$ mm which is $0.06\lambda_g$ at $8.0$ GHz                                                                                                                                                                                                                                                                                          | 82 |

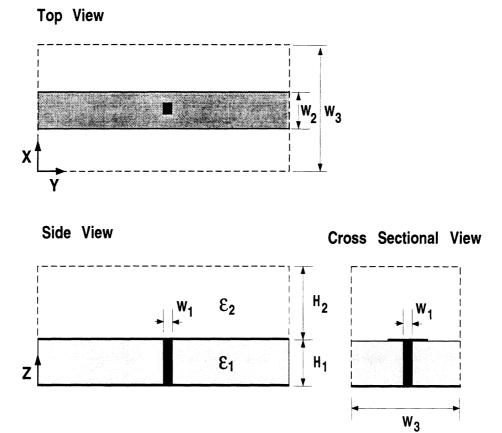

| 4.1  | Geometry of a microstrip short circuit via hole at the center of the line. The dashed lines represent PEC walls to terminate FEM meshes. $W_1=85\mu\mathrm{m}$ , $W_2=600\mu\mathrm{m}$ , $W_3=1785\mu\mathrm{m}$ , $H_1=250\mu\mathrm{m}$ , $H_2=600\mu\mathrm{m}$ , $\epsilon_1=12.9$ , and $\epsilon_2=1$ . The dotted lines around the geometry represent the outer boundaries for FEM mesh termination                                                                                                                                                                                  | 88 |

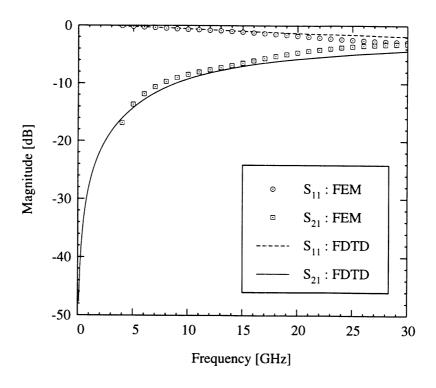

| 4.2  | Scattering parameters for the via                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80 |

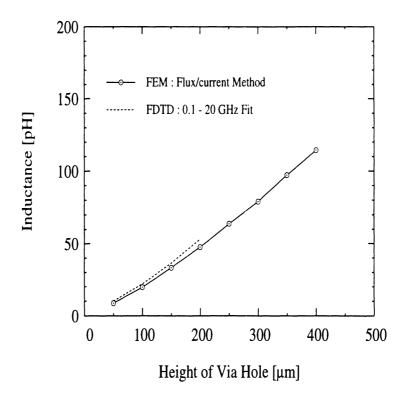

| 4.3  | Inductance of the microstrip short circuit with via hole. The inductance is calculated using two different methods. In FEM, the flux density around the via is used ( $f = 10 \text{ GHz}$ ). In FDTD, however, the via inductance is extracted by fitting the derived S-parameters to a $T$ -equivalent circuit. | 90  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

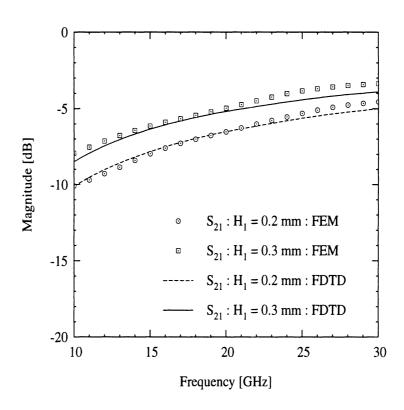

| 4.4  | Scattering parameters of the microstrip short circuit for two different substrate heights ( $H_1 = 0.2, 0.3 \text{ mm}$ ) with via hole grounding at the center of the line.                                                                                                                                      | 91  |

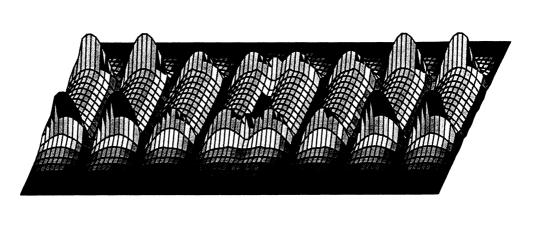

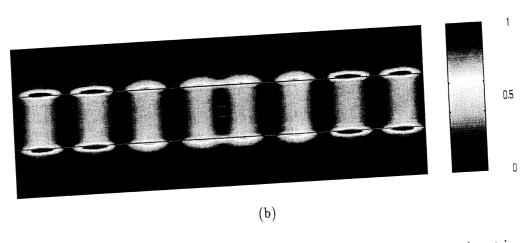

| 4.5  | Magnitude of the electric field distribution at $f=20~\mathrm{GHz}$ under the microstrip short circuit ( $z=0.19~\mathrm{mm}$ plane). The edge singularity and the standing wave patterns of the electric field distribution are clearly revealed.                                                                | 92  |

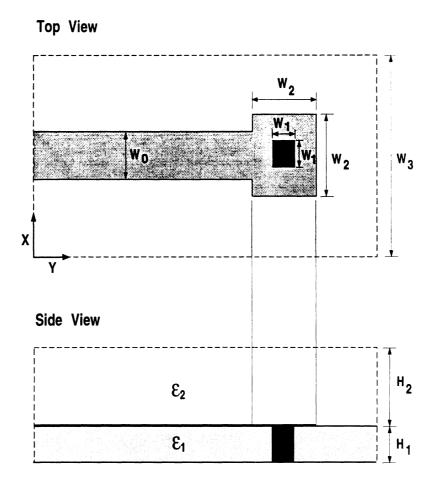

| 4.6  | Geometry of a 1-port microstrip ground pad. This is a board level via. $W_0=2.30$ mm, $W_1=1.15$ mm, $W_2=2.88$ mm, $W_3=10.0$ mm, $H_1=1.0$ mm, $H_2=2.0$ mm, $\epsilon_1=3.4$ , $\epsilon_2=1$ . The dotted lines around the geometry represent the outer boundaries for FEM mesh termination                   | 93  |

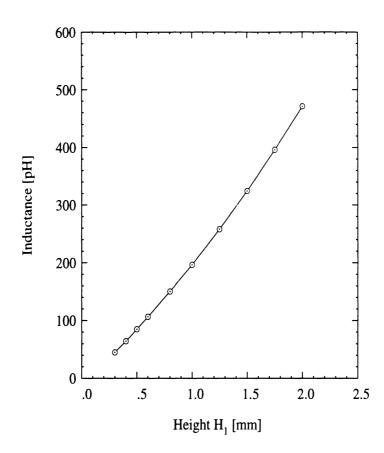

| 4.7  | The via inductance calculated from the flux/current definition at 10 GHz as a function of via height.                                                                                                                                                                                                             | 94  |

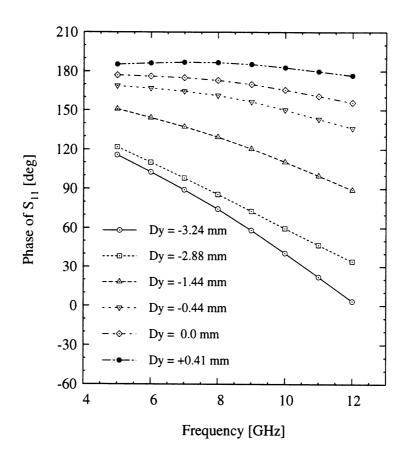

| 4.8  | Phase of the $S_{11}$ of the microstrip ground pad computed using the FEM at several different reference planes ( $D_y = +0.41, 0.0, -0.44, -1.44, -2.88,$ and -3.24 mm from the top to the bottom of the graphs). $D_y$ is 0.0 mm at the geometrical center of the via. $H_1 = 1.0$ mm                           | 95  |

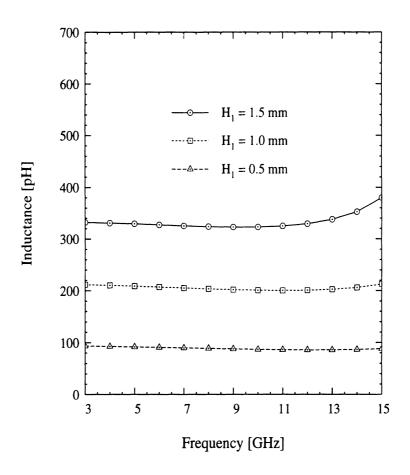

| 4.9  | The via inductance of the microstrip ground pad calculated from the flux/current definition for three different via heights ( $H_1=0.5,1.0,1.5$ mm) as a function of frequency.                                                                                                                                   | 96  |

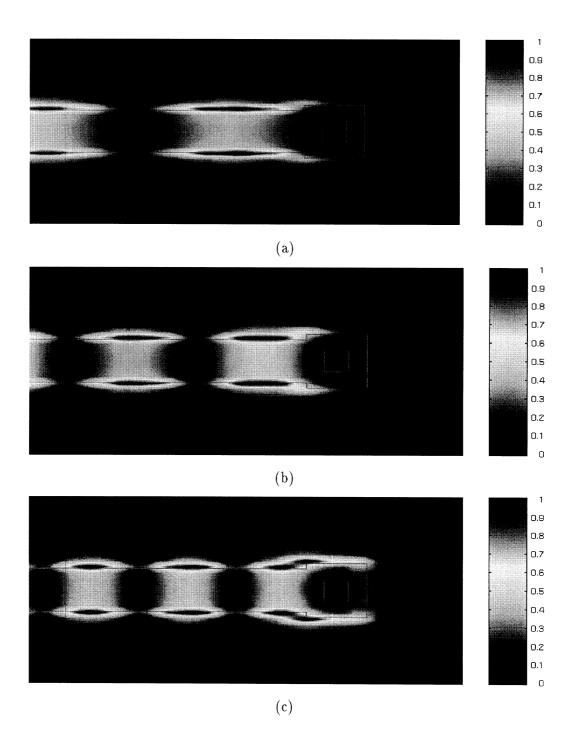

| 4.10 | Magnitude of the total electric field distribution at (a) $f = 10$ GHz, (b) $f = 15$ GHz, and (c) $f = 20$ GHz under the microstrip line at $z = 0.9$ mm plane. The edge singularity and the standing wave patterns of the electric field distribution are clearly revealed                                       | 97  |

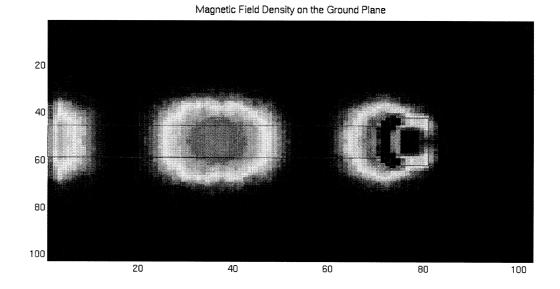

| 4.11 | Magnitude of the magnetic energy distribution on the ground plane at $f=10$ GHz. The via inductance is mainly determined by the magnetic energy surrounding the via                                                                                                                                               | 98  |

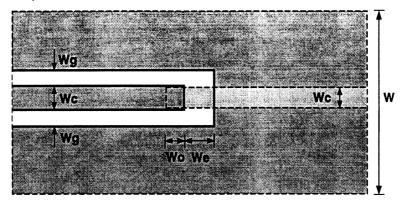

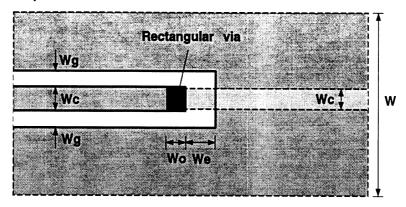

| 4.12 | Geometry of the transition from CPW to microstrip on different layers without via hole. $W_g=50\mu\mathrm{m}$ , $W_c=75\mu\mathrm{m}$ , $W_o=75\mu\mathrm{m}$ , $W_e=200\mu\mathrm{m}$ , $W=1000\mu\mathrm{m}$ , $H_1=100\mu\mathrm{m}$ , $H_2=H_3=400\mu\mathrm{m}$ , and $\epsilon_r=12.9.$                     | 99  |

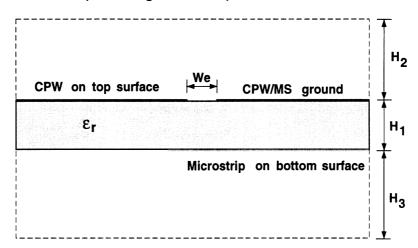

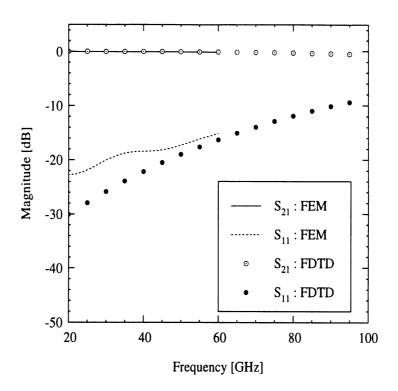

| 4.13 | Scattering parameters for the transition from CPW-to-microstrip on different layers without via hole connection.                                                                                                                                                                                                  | 100 |

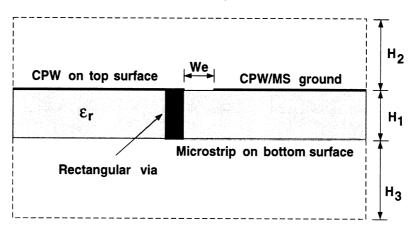

| 4.14 | Transition from CPW to microstrip on different layers through via hole. $W_g = 50 \mu \text{m}$ , $W_c = 75 \mu \text{m}$ , $W_o = 75 \mu \text{m}$ , $W_e = 200 \mu \text{m}$ , $W = 1000 \mu \text{m}$ $H_1 = 100 \mu \text{m}$ , $H_2 = H_3 = 400 \mu \text{m}$ , and $\epsilon_r = 12.9$ . The vertical via is an empty rectangular cavity with PEC walls. | 102 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.15 | Scattering parameters of the CPW-to-microstrip transition with vertical via hole connection.                                                                                                                                                                                                                                                                   | 103 |

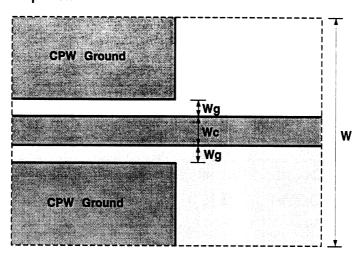

| 4.16 | Geometry of a channelized CPW to microstrip transition. $W_g=50\mu\mathrm{m},$ $W_c=75\mu\mathrm{m},$ $W=1000\mu\mathrm{m},$ $H_1=400\mu\mathrm{m},$ $H_2=500\mu\mathrm{m}$ and $\epsilon_r=12.9.$                                                                                                                                                             | 104 |

| 4.17 | Scattering parameters for the channelized CPW-to-microstrip transition.                                                                                                                                                                                                                                                                                        | 105 |

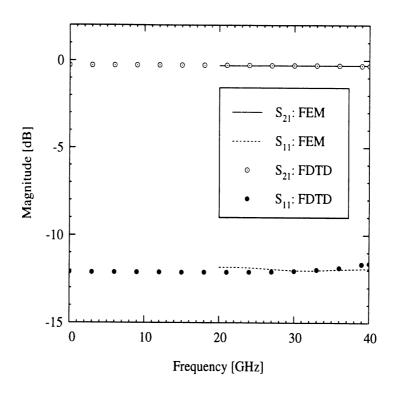

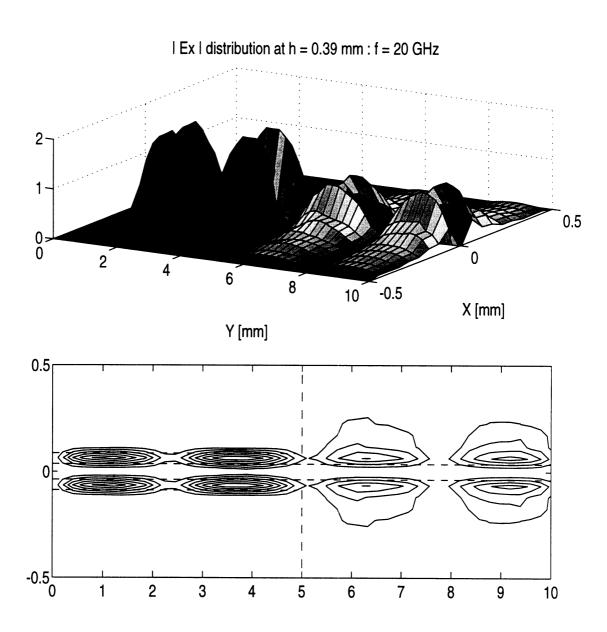

| 4.18 | Magnitude of transverse component of the electric field at $z=390\mu\mathrm{m}$ plane                                                                                                                                                                                                                                                                          | 106 |

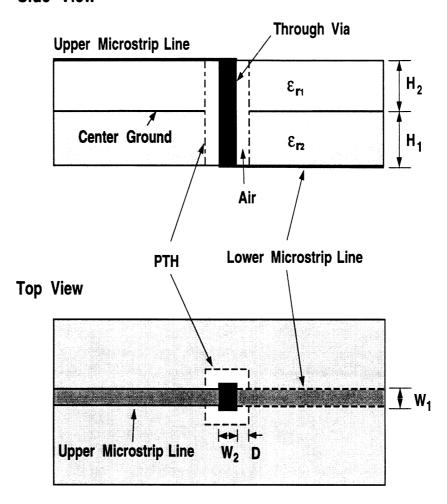

| 4.19 | Geometry of asymmetric two port via hole passing through a plated-through-hole (PTH) in the middle of the substrate. $H_1=H_2=0.2$ mm, $W_1=0.4$ mm, $W_2=0.8$ mm, $\epsilon_{r1}=\epsilon_{r2}=4.5$ , $D=0.2$ , 0.4, 0.7 mm (3 cases).                                                                                                                        | 108 |

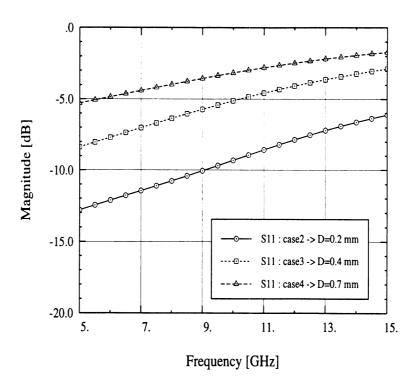

| 4.20 | Comparison of the S-parameters for 3 different PTH sizes                                                                                                                                                                                                                                                                                                       | 109 |

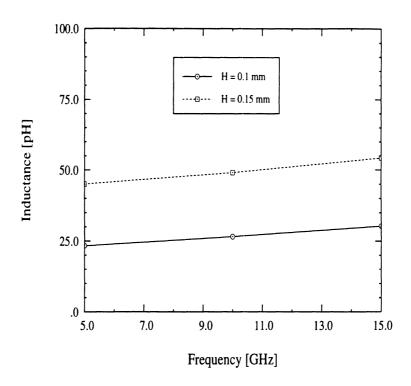

| 4.21 | Via inductances of two different via height: $H_1 = H_2 = 0.1$ and 0.15mm and D = 0.4 mm. Inductances are evaluated from the magnetic flux density surrounding the via                                                                                                                                                                                         | 110 |

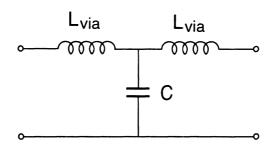

| 4.22 | Type I equivalent circuit used for the asymmetric 2-port via hole geometry. Note that if the PTH opening becomes smaller, $C$ increases and finally becomes a short circuit.                                                                                                                                                                                   | 111 |

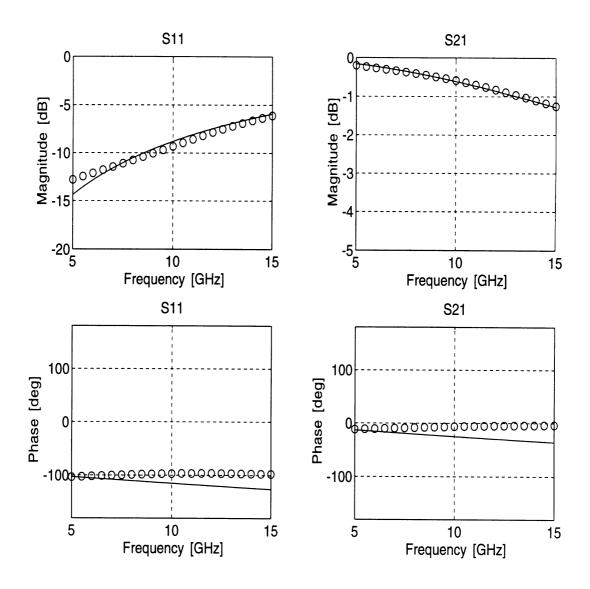

| 4.23 | Matching the S parameters using the type I equivalent circuit (Circle: FEM data, Line: Equivalent circuit). $H_1=H_2=0.1$ mm and $D=0.2$ mm. $L_{via}=25$ pH, $C=0.28$ pF with type I equivalent circuit                                                                                                                                                       | 112 |

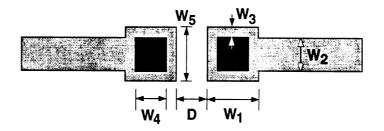

| 4.24 | Geometry of double via hole. H = 1.6 mm, $W_1$ = 1.4 mm, $W_2$ = 1.0 mm (85 $\Omega$ ), $W_3$ = 0.2 mm, $W_4$ = 1.0 mm, $W_5$ = 1.4 mm, $\epsilon_{r1}$ = 4.5, D = 0.2, 0.4, 0.6, 0.8 mm (4 cases)                                                                                                                                                             | 113 |

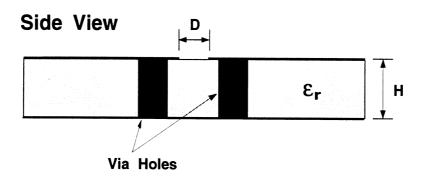

| 4.25 | Comparison of the S-parameters for 4 different separation distances                                                                                                                                                                                                                                                                                            | 114 |

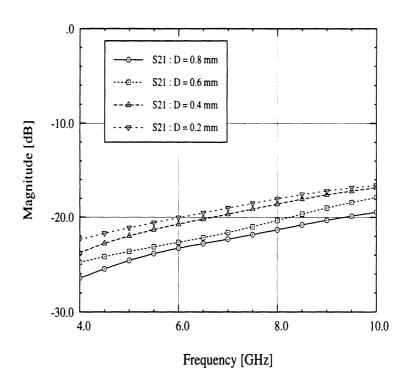

| 4.26 | Magnitude of the total electric field distribution at (a) $f = 4$ GHz and (b) $f = 10$ GHz under the microstrip line at $z = 1.5$ mm plane. The edge singularity and the standing wave patterns of the electric field distribution are clearly revealed.                                                                                                       | 115 |

|      | are clearly revealed.                                                                                                                                                                                                                                                                                                                                          | 110 |

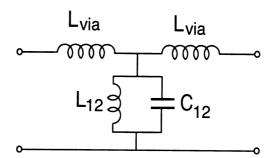

| 4.27 | Type II equivalent circuit used for the double via hole geometry. The $L_{12}$ and $C_{12}$ represent the mutual coupling between the via holes. Note that if the separation distance D increases, the $L$ becomes smaller and finally becomes ideal short circuit                    | 116 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

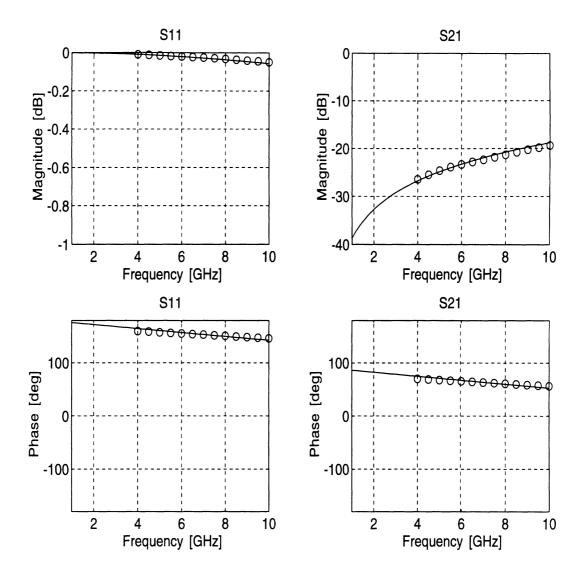

| 4.28 | Matching the S parameters with the type II equivalent circuit. $L_{via}=380$ pH, $L_{12}=80$ pH, and $C_{12}=0.1$ pF. H = 1.6 mm, $W_1=1.4$ mm, $W_2=1.0$ mm, $W_3=0.2$ mm, $W_4=1.0$ mm, $W_5=1.4$ mm, $\epsilon_{r1}=4.5$ , D = 0.8 mm. Circle: FEM data, Line: Equivalent circuit. | 117 |

| 4.29 | Geometry of the CPW-to-slotline planar transition with air bridge: $L_s=4.751$ mm, $S_1=0.114$ mm, $S_2=0.129$ mm, $W_1=0.305$ mm, $W_2=0.254$ mm, $W_3=0.178$ mm, $H=0.635$ mm, and $\epsilon_r=10.5.$                                                                               | 119 |

| 4.30 | Scattering parameters for the coplanar waveguide-to-slotline transition with air bridge.                                                                                                                                                                                              | 120 |

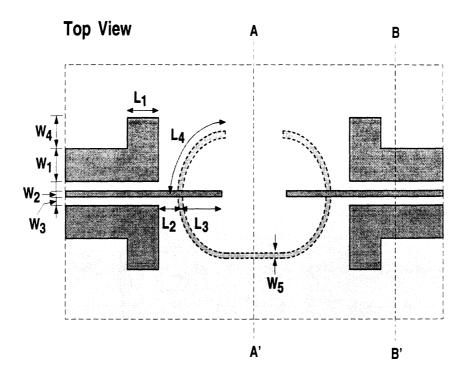

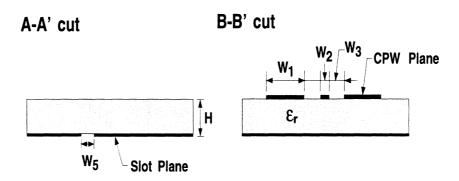

| 4.31 | Geometry of the CPW-to-slotline non-planar transition: $L_1 = 2.54$ mm, $L_2 = 2.54$ mm, $L_3 = 5.0$ mm, $L_4 = 6.229$ mm, $W_1 = 2.54$ mm, $W_2 = 0.152$ mm, $W_3 = 0.318$ mm, $W_4 = 2.54$ mm, $W_5 = 0.178$ mm, $H = 0.635$ mm, and $\epsilon_r = 10.5$ .                          | 122 |

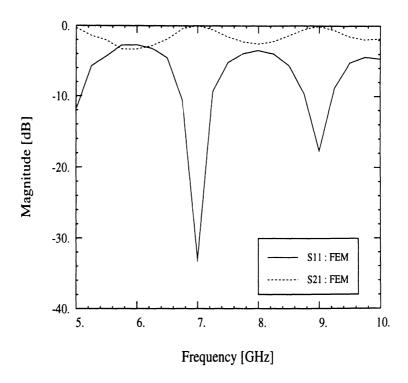

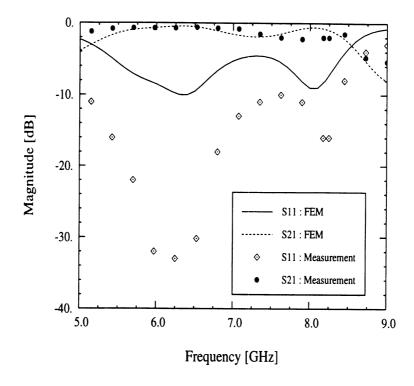

| 4.32 | Scattering parameters for the coplanar waveguide-to-slotline transition under shielding environment. The design frequency is 6 GHz                                                                                                                                                    | 123 |

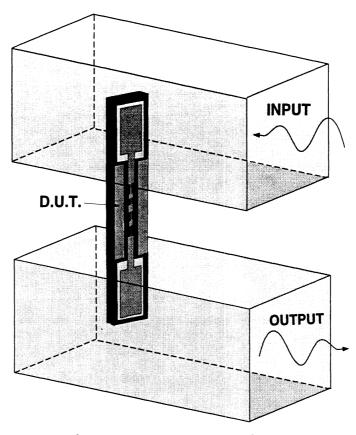

| 4.33 | An example of a CPW-to-waveguide probe station.                                                                                                                                                                                                                                       | 125 |

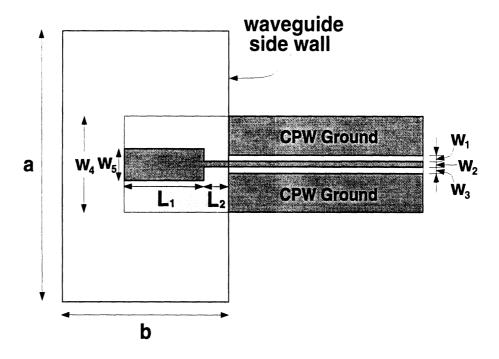

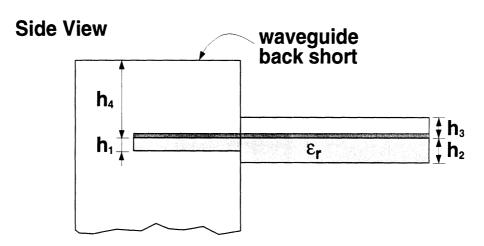

| 4.34 | CPW-to-waveguide transition: a = 47.6 mm, b = 22.0 mm, $L_1$ = 10.8 mm, $L_2$ = 0.8 mm, $W_1$ = 0.5 mm, $W_2$ = 0.8 mm, $W_3$ = 0.5 mm, $W_4$ = 11.8 mm, $W_5$ = 3.8 mm, $h_1$ = $h_2$ = 2.0 mm, $h_3$ = 1.2 mm, $h_4$ = 13.2 mm, and $\epsilon_r$ = 12.0                             | 126 |

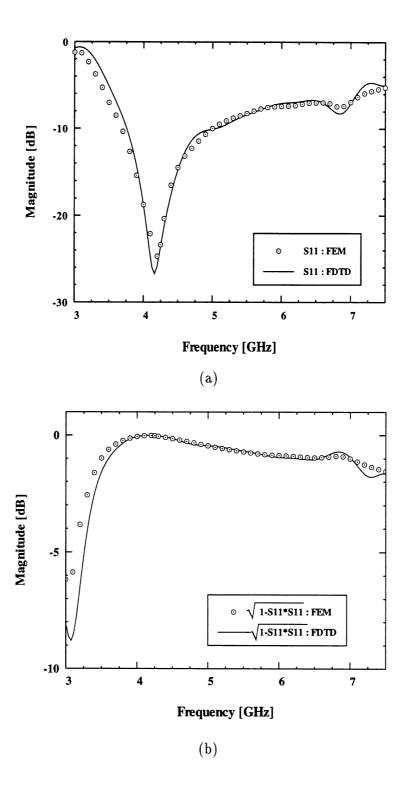

| 4.35 | Scattering parameters of the CPW-to-waveguide transition                                                                                                                                                                                                                              | 127 |

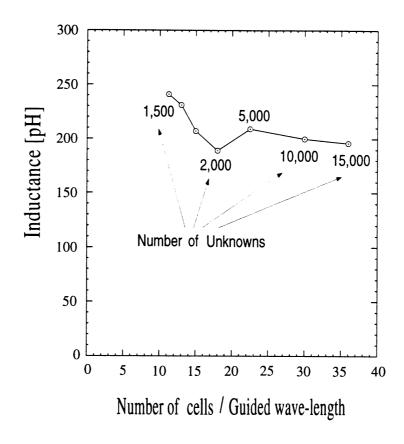

| 4.36 | An example of the convergence test of the FEM. The inductance of the microstrip ground pad shown in Fig .4.6 as a function of the number of cells per guided wavelength.                                                                                                              | 129 |

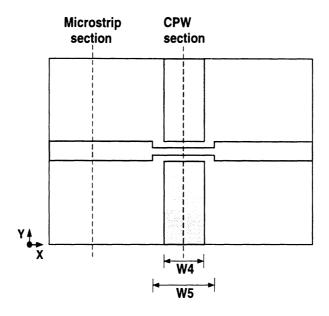

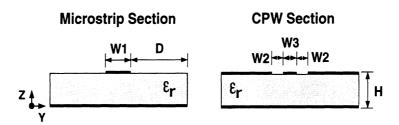

| 5.1  | Geometry of the Microstrip-to-CPW transition without hermetic wall. $W_1=0.48~\mathrm{mm},~W_2=0.14~\mathrm{mm},~W_3=0.2~\mathrm{mm},~W_4=2.0~\mathrm{mm},~W_5=3.0~\mathrm{mm},~H=0.635~\mathrm{mm},~\epsilon_r=12.5.$ Case 1: $D=2.26~\mathrm{mm}.$ Case 2: $D=1.76~\mathrm{mm}.$    | 136 |

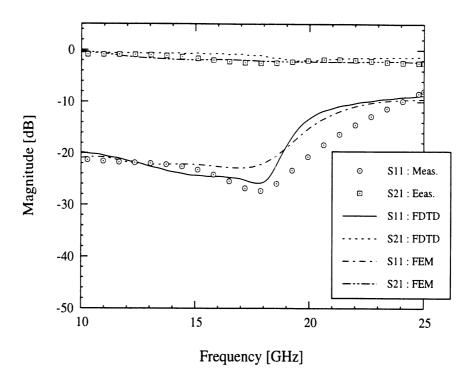

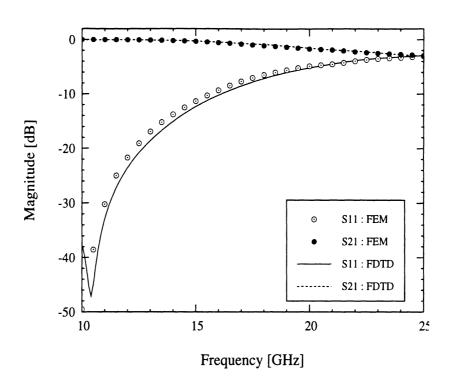

| 5.2  | S-parameters for the open transition shown in Fig. 5.1. In this case, duroid substrate, which has a relative dielectric constant $\epsilon_r$ of 10.8, is used. The CPW ground planes and the PEC underneath the substrate are connected in the measurements.                         | 138 |

| 5.3  | Comparison between FEM and FDTD data for (a) case 1 ( $D = 2.26 \text{ mm}$ ) and (b) case 2 ( $D = 1.76 \text{ mm}$ )                                                                                                                                                                                                            | 139 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

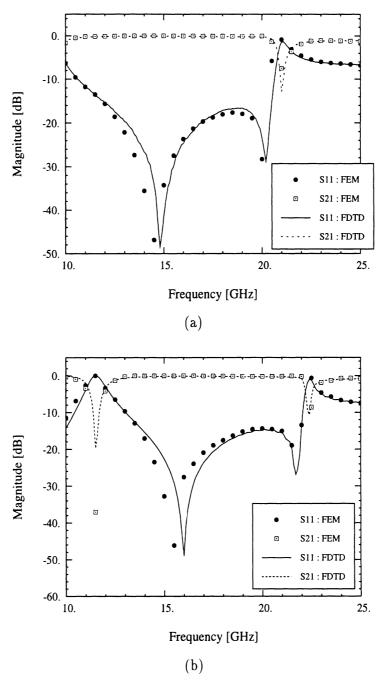

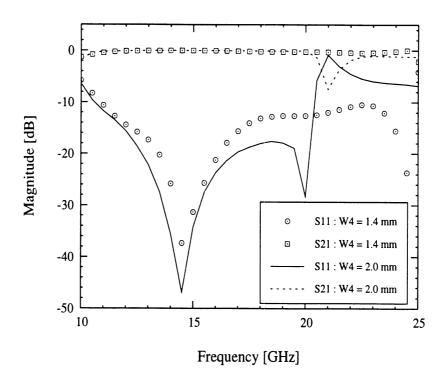

| 5.4  | S-parameters for two different size of CPW ground plane ( $W_4$ in Fig. 5.1). Other geometrical factors are remain the same                                                                                                                                                                                                       | 141 |

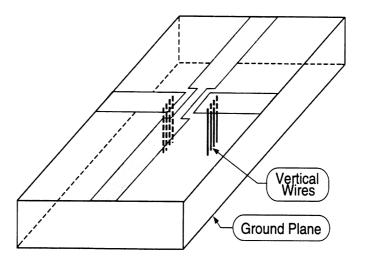

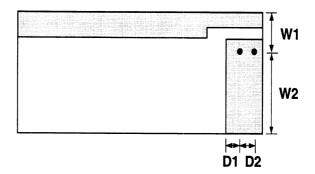

| 5.5  | Geometry of the microstrip-through-CPW transition without hermetic wall: vertical wire grounding. $W_1=0.466~\mathrm{mm},W_2=2.034~\mathrm{mm},D_1=0.40~\mathrm{mm},\mathrm{and}D_2=0.40~\mathrm{mm}.$ Other geometrical factors are the same as those in the previous example.                                                   | 142 |

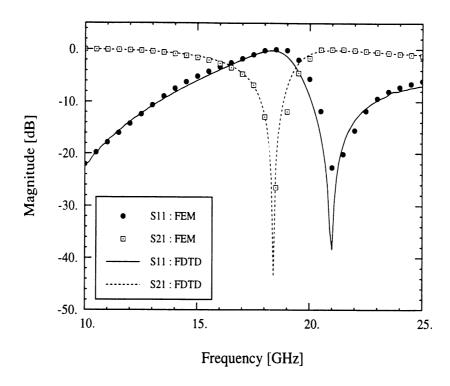

| 5.6  | S-parameters of the vertical wire grounding case                                                                                                                                                                                                                                                                                  | 143 |

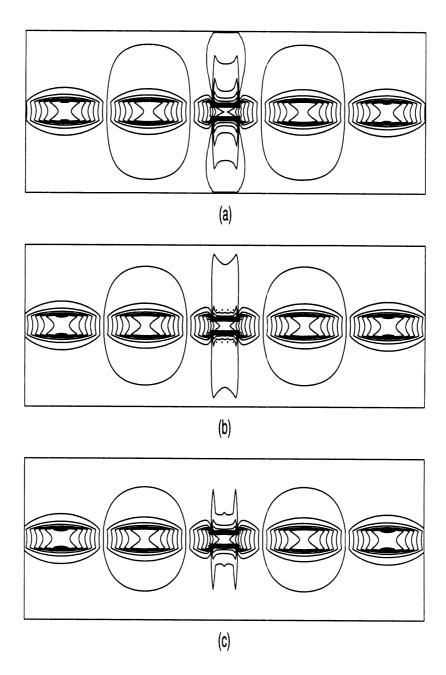

| 5.7  | Electric field $(\mathbf{E}_z)$ distribution around the transition region at f=10 GHz. (a) Microstrip-through-CPW transition, (b) Microstrip-through-CPW transition with vertical grounding wires, and (c) Microstrip-through-CPW transition with extended rectangular vias                                                       | 144 |

| 5.8  | Geometry of the microstrip-through-CPW transition without hermetic wall: Rectangular via hole grounding with finite size CPW ground plane. The size of the via hole is $0.452 \times 0.6$ mm. $W_1 = 0.226$ mm, $W_2 = 0.452$ mm, $W_3 = 0.452$ mm, $W_4 = 1.13$ mm. Other geometrical factors are identical to the first example | 145 |

| 5.9  | S-parameters for the rectangular via hole grounding case                                                                                                                                                                                                                                                                          | 146 |

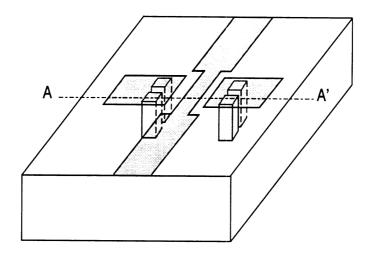

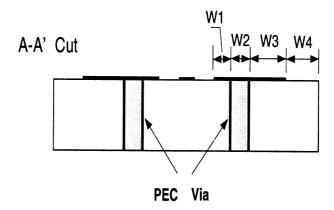

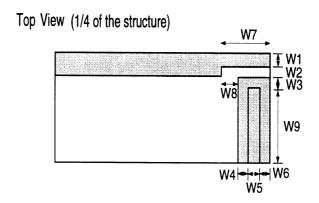

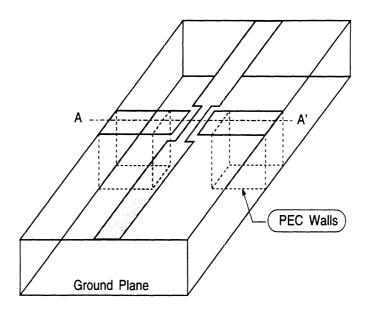

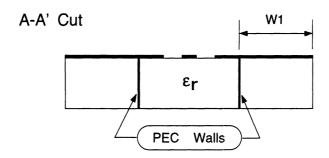

| 5.10 | Geometry of the microstrip-through-CPW transition without hermetic wall : extended rectangular via hole grounding. The top view shows one quarter of the whole geometry. $W_1=0.1$ mm, $W_2=0.14$ mm, $W_3=0.226$ mm, $W_4=0.2$ mm, $W_5=0.6$ mm, $W_6=0.2$ mm, $W_7=1.5$ mm, $W_8=0.5$ mm, $W_9=2.034$ mm                        | 147 |

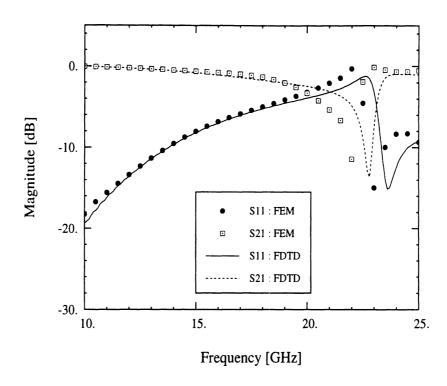

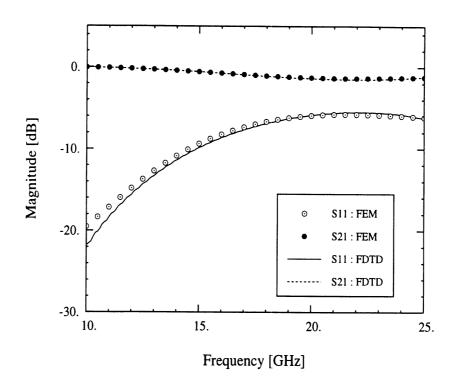

| 5.11 | S-parameters of the extended rectangular via hole grounding case                                                                                                                                                                                                                                                                  | 148 |

| 5.12 | Geometry of the microstrip-through-CPW transition without hermetic wall: PEC wall grounding. $W_1=2.034~\mathrm{mm}$ and other geometrical factors are identical to the first example.                                                                                                                                            | 149 |

| 5.13 | S-parameters of the PEC wall grounding case                                                                                                                                                                                                                                                                                       | 150 |

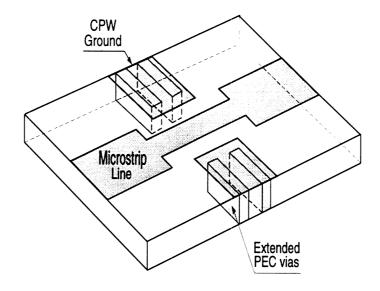

| 5.14 | Geometry of the microstrip-through-CPW transition with hermetic wall on top of the extended PEC via grounding case. The width of the hermetic wall is 1.6 mm. $W_1 = 0.48$ mm, $W_2 = 0.14$ mm, $W_3 = 0.2$ mm, $W_4 = 1.6$ mm, $H_1 = H_2 = 0.635$ mm, $\epsilon_{r1} = 12.5$ , and $\epsilon_{r2} = 2.3$                        | 151 |

| 5.15 | Comparison of the S-parameters for the transition with hermetic wall on top and extended PEC via under the circuit plane.                                                                                                                                                                                                                                                                                                                              | 152 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

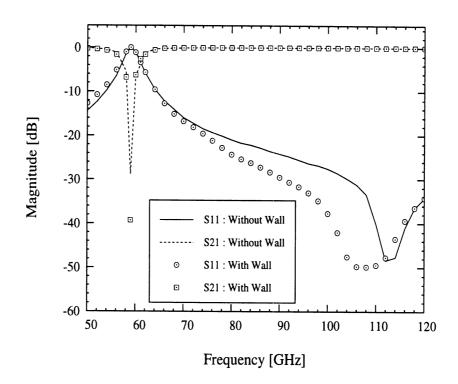

| 5.16 | S-parameters for the transition with and without hermetic wall on top of the CPW section. The geometrical factors : $W_1=70~\mu\text{m}$ , $W_2=30~\mu\text{m}$ , $W_3=40~\mu\text{m}$ , $W_4=300~\mu\text{m}$ , and $W_5=350~\mu\text{m}$ (refer to Figure 2). The width and height of the dielectric brick under the PEC wall are 250 $\mu\text{m}$ and 100 $\mu\text{m}$ , respectively                                                             | 153 |

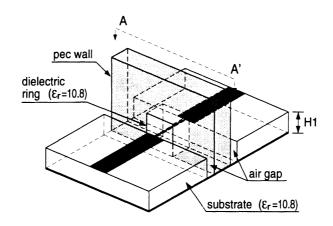

| 5.17 | Geometry of the hermetic bead transition. $W_1 = 0.55$ mm, $W_2 = 0.21$ mm, $W_3 = 1.27$ mm, $W_4 = 2.225$ mm, $W_5 = 5.0$ mm, $H_1 = 0.635$ mm, $H_2 = 4.0$ mm, $L_1 = 1.50$ mm, $L_2 = 0.40$ mm, and $\epsilon_r = 10.8$                                                                                                                                                                                                                             | 155 |

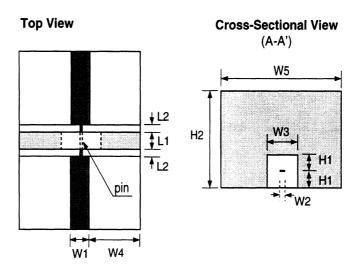

| 5.18 | S-parameters of the hermetic bead transition with square dielectric ring.                                                                                                                                                                                                                                                                                                                                                                              | 156 |

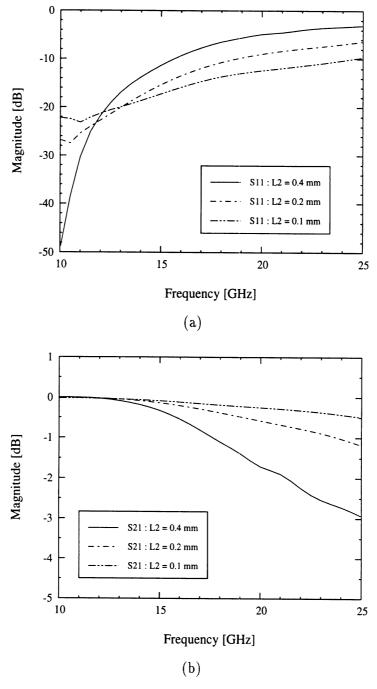

| 5.19 | Comparison of the S-parameters for the hermetic bead transition of three different air gap width $L_2$ . (a) $ S_{11} $ and (b) $ S_{21} $                                                                                                                                                                                                                                                                                                             | 157 |

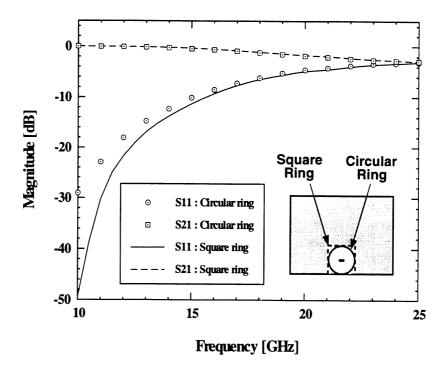

| 5.20 | Comparison of the S-parameters of the hermetic bead transition with square and circular dielectric ring of radius equals $H_1$                                                                                                                                                                                                                                                                                                                         | 158 |

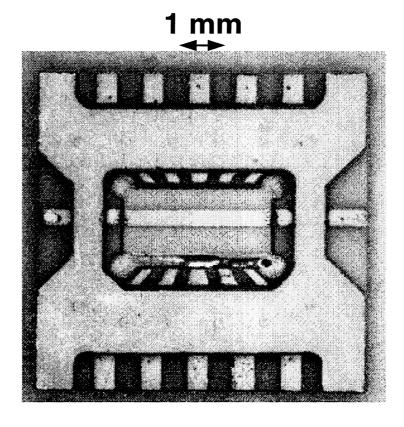

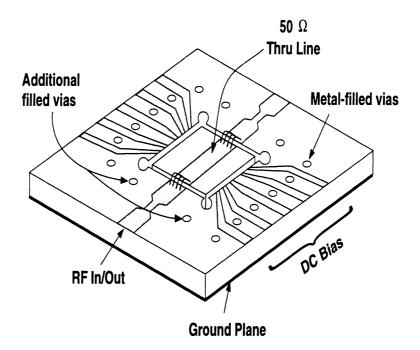

| 6.1  | Top view of the K/Ka-band MMIC package                                                                                                                                                                                                                                                                                                                                                                                                                 | 161 |

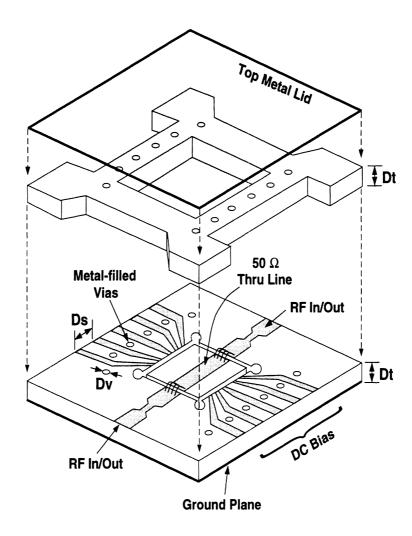

| 6.2  | Schematic diagram of the K/Ka-band hermetic package designed and manufactured for a MMIC phase shifter chip. The diameter of the vertical metal filled vias are $D_v=0.203$ mm and the distance between these vias are $D_s=1.016$ mm. The upper and lower alumina layers are each 0.381 mm thick $(D_t)$                                                                                                                                              | 163 |

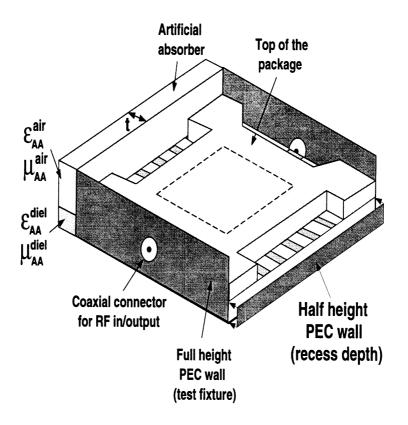

| 6.3  | Schematic showing the location and extent of PECs in addition to the artificial absorbers which simulate the test fixture and open environment. Two different types of absorbers ( $\epsilon_{AA}^{air} = \mu_{AA}^{air} = 1.0 + j10.0$ , $\epsilon_{AA}^{diel} = 9.5 + j15.0$ , and $\mu_{AA}^{diel} = 1.0 + j1.5789$ ) are designed and placed in either side of the package facing the DC bias lines (not fully shown in the figure for simplicity) | 165 |

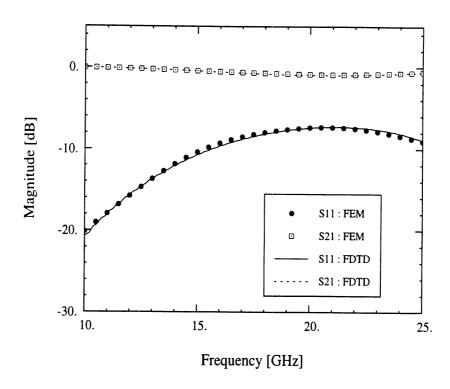

| 6.4  | Computed S-parameters for the isolated symmetric package                                                                                                                                                                                                                                                                                                                                                                                               | 166 |

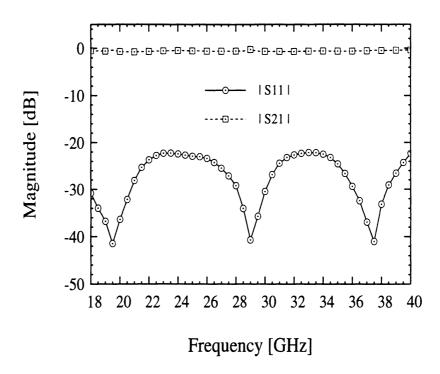

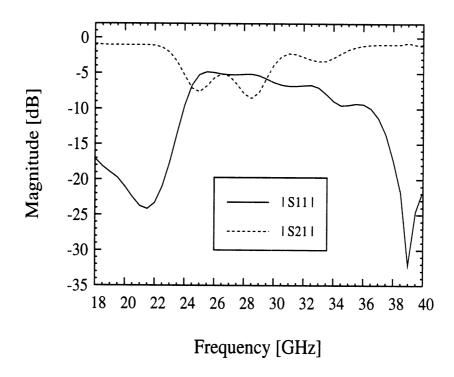

| 6.5  | Computed S-parameters for the isolated asymmetric package                                                                                                                                                                                                                                                                                                                                                                                              | 167 |

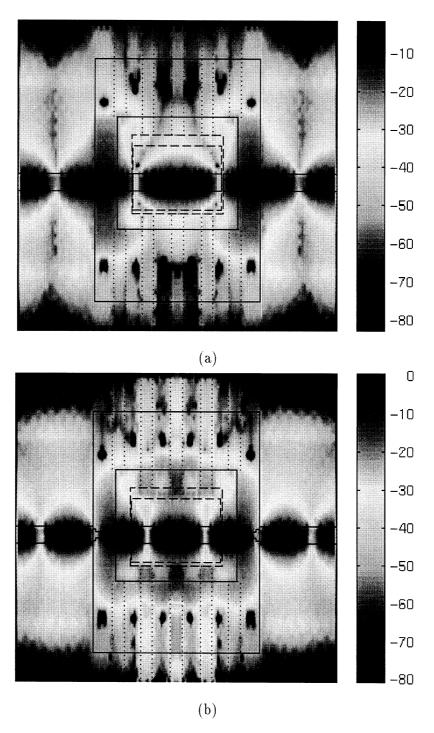

| 6.6  | Computed vertical electric field distribution (dB scale) at (a) $f=20.5~\mathrm{GHz}$ and (b) $f=29.5~\mathrm{GHz}$ in the isolated asymmetric hermetic package                                                                                                                                                                                                                                                                                        | 168 |

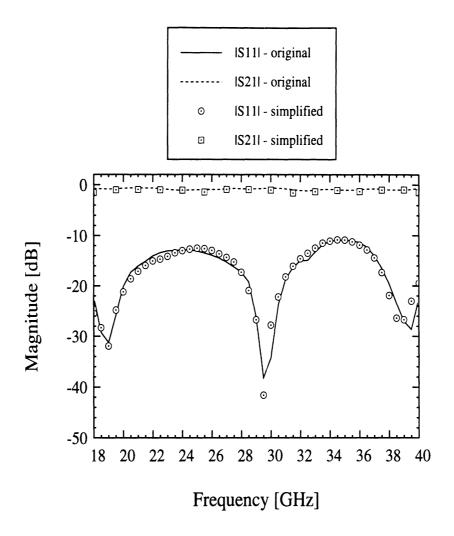

| 6.7  | Comparison between the computed S-parameters for the isolated asymmetric package with (original) and without (simplified) DC bias lines and bond wires                                                                                                                                                                                                                                                                                                 | 169 |

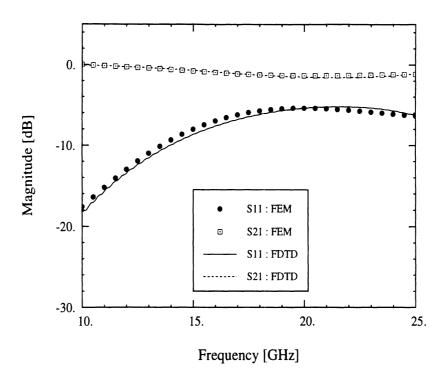

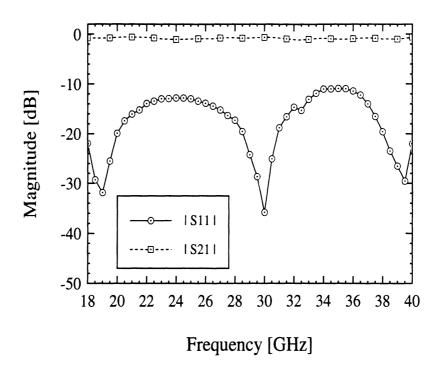

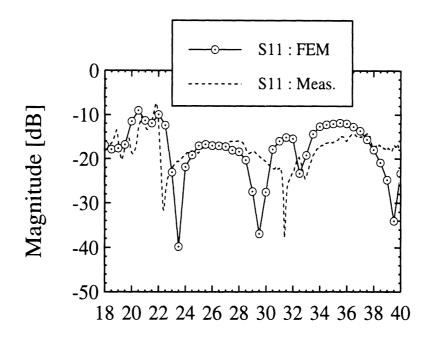

| 6.8  | Measured and computed S-parameters ( (a) $ S_{11} $ and (b) $ S_{21} $ ) for the asymmetric package residing in the test fixture                                                                                                                                                              | 171 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

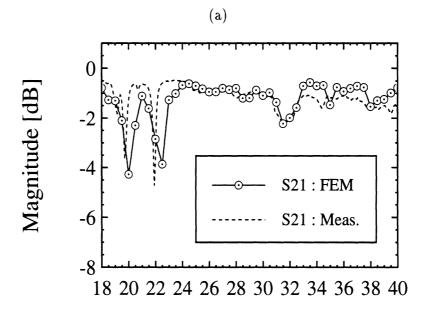

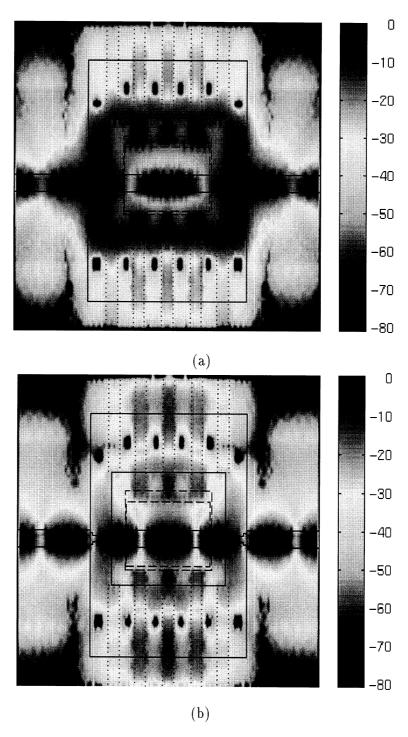

| 6.9  | Computed vertical electric field distribution (dB scale) in the asymmetric hermetic package placed in the test fixture at (a) $f = 20.5 \text{ GHz}$ and (b) $f = 29.5 \text{ GHz}$ in the isolated asymmetric hermetic package                                                               | 172 |

| 6.10 | Schematic diagram of the asymmetric hermetic package showing four additional vias at the input and output ends of the package                                                                                                                                                                 | 173 |

| 6.11 | Computed S-parameters for the asymmetric package with four additional vias at the input and output ends of the package.                                                                                                                                                                       | 174 |

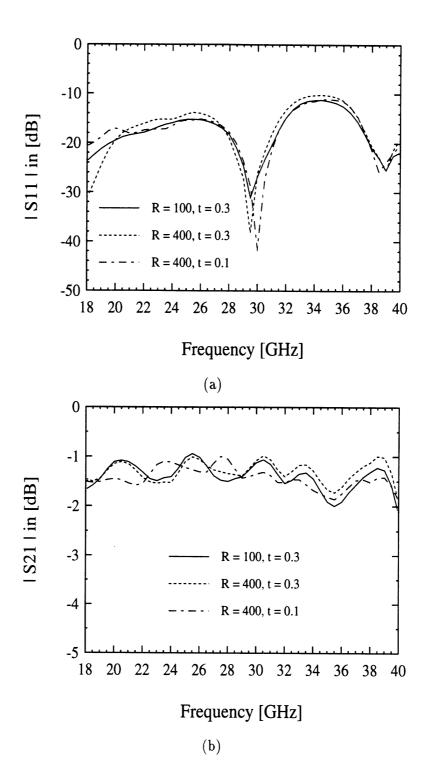

| 6.12 | Computed S-parameters ((a) $ S_{11} $ and (b) $ S_{21} $ ) for the asymmetric package residing in the test fixture with resistive coating on the inside surface of the lid. The resistivity and the thickness of the coating is indicated as R in $[\Omega/\Box]$ and t in [mm], respectively | 176 |

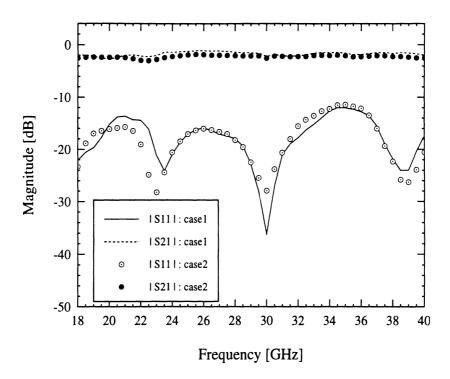

| 6.13 | Computed S-parameters for the asymmetric package with frame constructed from dielectric material with high loss tangent. Case 1: $\epsilon_r = 9.5(1.0+j0.1)$ and $\mu_r = 1.0+j0.0$ . Case 2: $\epsilon_r = 9.5(1.0+j0.5)$ and $\mu_r = 1.0+j0.0$                                            | 177 |

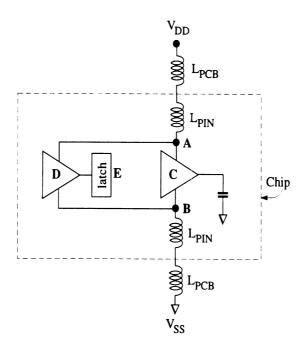

| 7.1  | Traditional way of modeling the inductances of the PCBs and package bonding wires                                                                                                                                                                                                             | 183 |

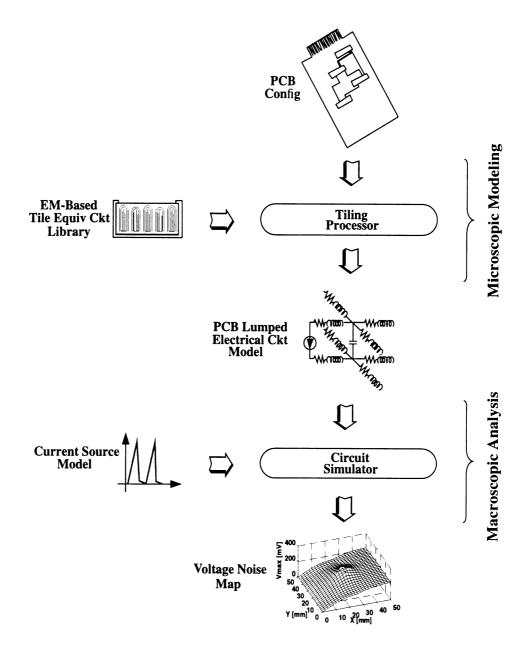

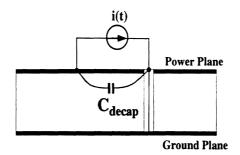

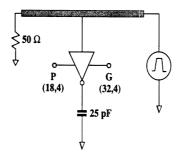

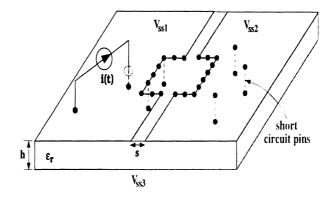

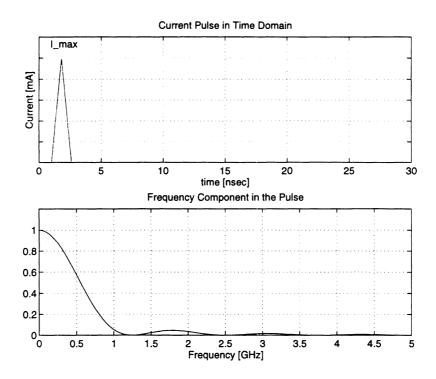

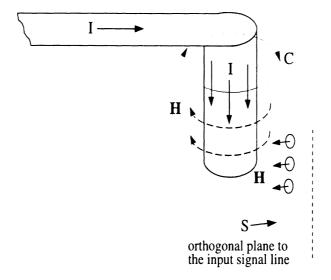

| 7.2  | Modeling of simultaneous switching noise (SSN) and simulation methodology.                                                                                                                                                                                                                    | 186 |

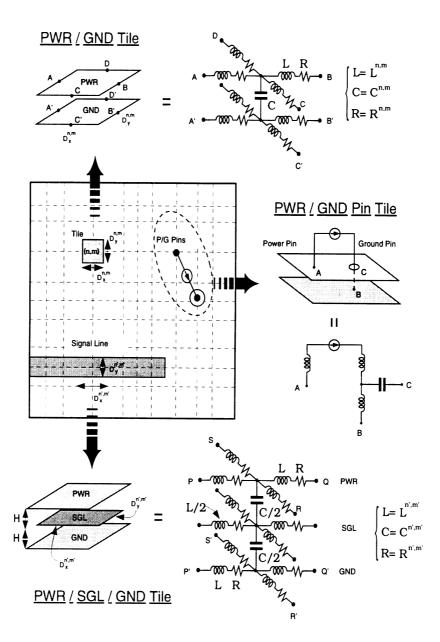

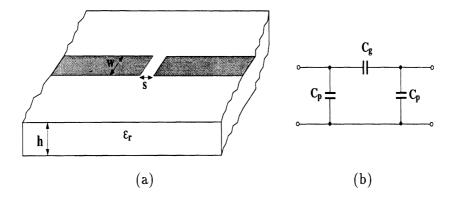

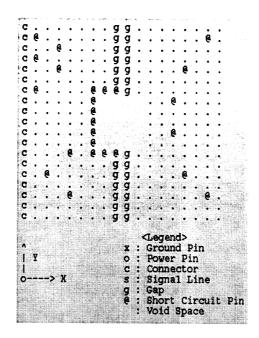

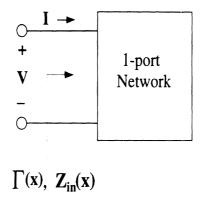

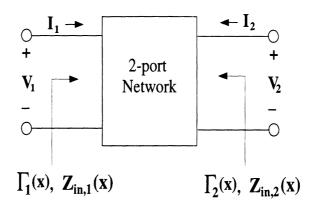

| 7.3  | Equivalent circuits for three different tiles, such as power/ground tile, power/ground pin tile, and power/signal/ground tile                                                                                                                                                                 | 189 |

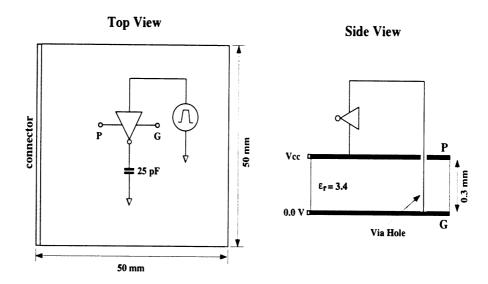

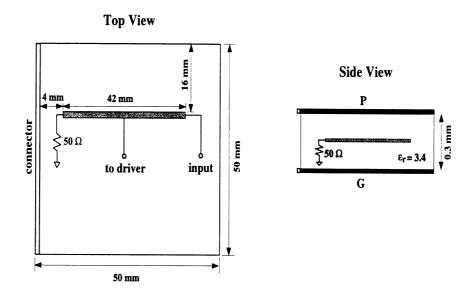

| 7.4  | Example PCB used in the validation experiments                                                                                                                                                                                                                                                | 195 |

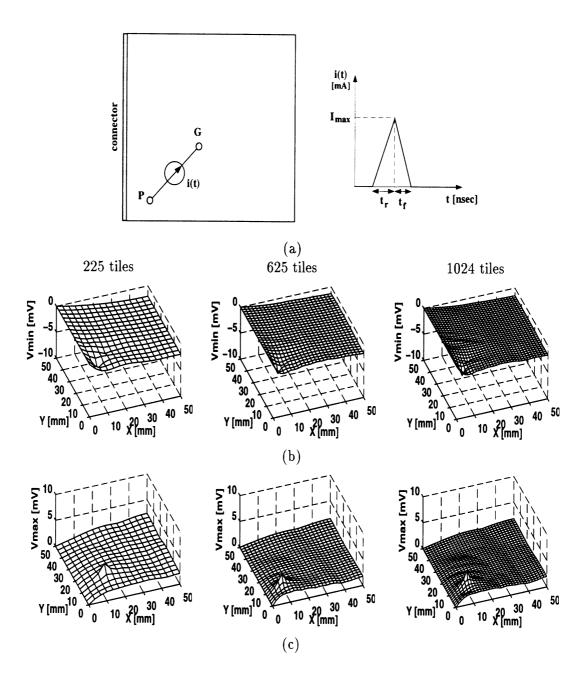

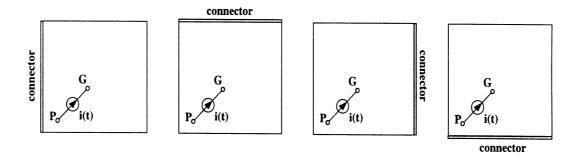

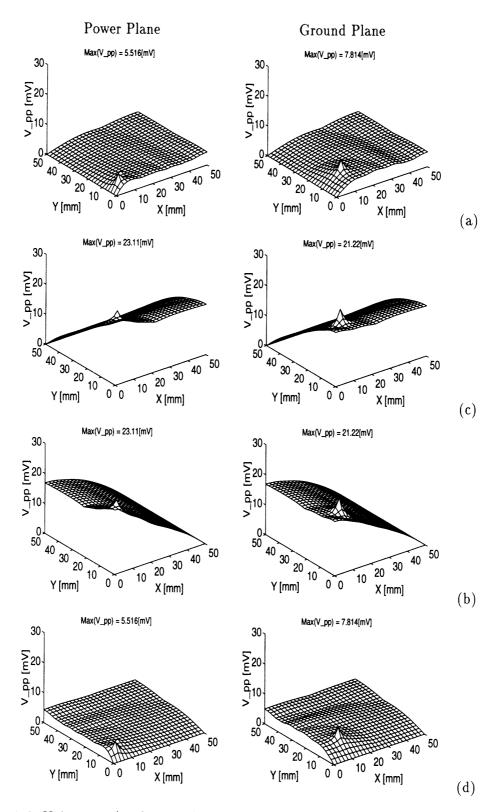

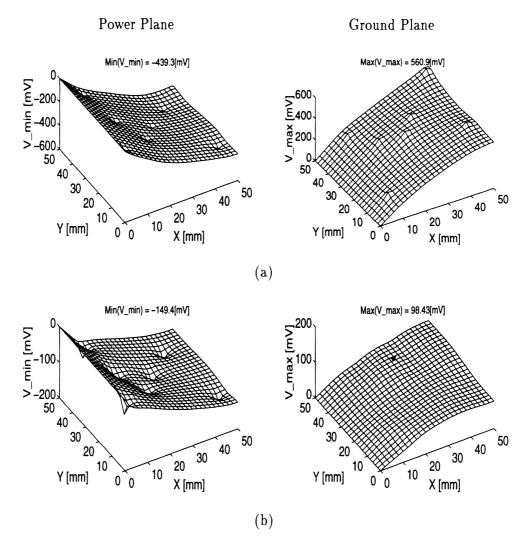

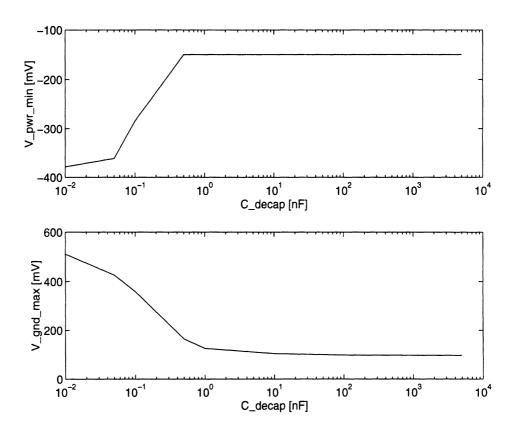

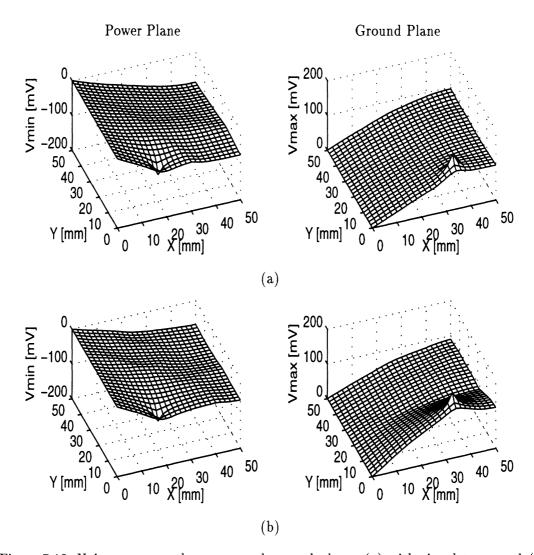

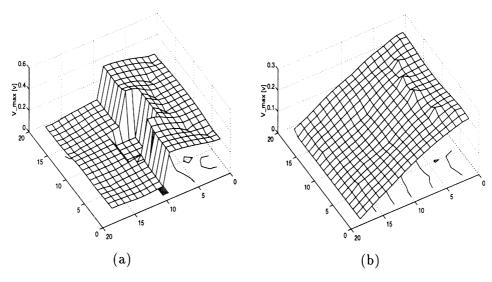

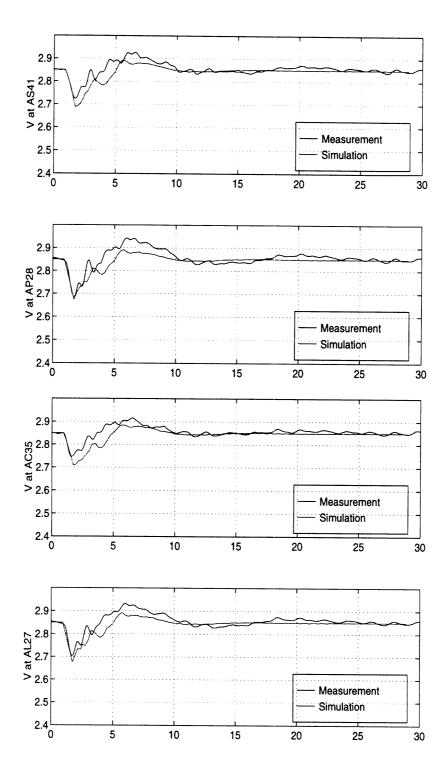

| 7.5  | (a) Board layout and current waveform for validation experiments. Noise maps on the (b) power plane and (c) ground plane for three different number of tiles                                                                                                                                  | 197 |

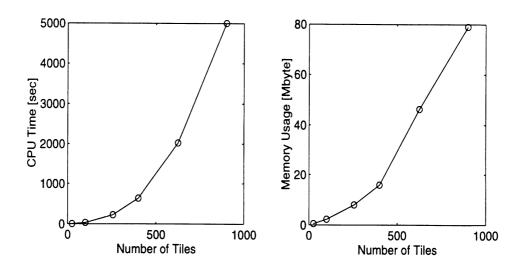

| 7.6  | CPU and memory usage versus the number of tiles                                                                                                                                                                                                                                               | 198 |