# W-BAND THREE-DIMENSIONAL INTEGRATED CIRCUITS UTILIZING SILICON MICROMACHINING

by

## Katherine Juliet Herrick

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2000

#### Doctoral Committee:

Professor Linda P. B. Katehi, Chair Assistant Professor Clark T. C. Nguyen Associate Professor Gabriel M. Rebeiz Associate Professor Michael Thouless Dr. James Harvey, U.S. Army Research Office Dr. Robert T. Kihm, Raytheon Electronic Systems © <u>Katherine Juliet Herrick</u> 2000 All Rights Reserved To my father,

Donald F. Herrick

and my mother,

Sandra K. Blair

## ACKNOWLEDGEMENTS

Completing this dissertation has been a long and arduous process. I could not have accomplished it without the support, guidance, and influence of many people. First and foremost, I would like to thank my advisor, Professor Linda Katehi, for encouraging me to attend graduate school and pursue a doctoral degree. Professor Katehi has provided me with instrumental advice and understanding over the years. I would also like to thank my committee members for their time and support: Professor Clark Nguyen, Professor Gabriel Rebeiz, Professor Michael Thouless, Dr. Jim Harvey, and Dr. Tom Kihm.

Thank you to the students who showed me the way: Professor Tom Weller, Professor Rhonda Drayton, Dr. Steve Gearhart, Dr. Tom Budka, and Professor Sanjay Raman just to name a few. Thank you to my colleagues for your friendship and advice: Dr. Rashaunda Henderson, J.D. Shumpert, Dr. Andy Brown, Sergio Pacheco Dr. John Papapolymerou, Dr. Kavita Goverdhanam, Dr. Scott Barker, Stéphane Legault, Dr. Gildas Gauthier, Dr. Leo DiDomenico, Mark Casciato, Kyoung Yang, and Kevin Lu. As my officemate, I owe J.D. Shumpert a special thank you for always listening and lending valuable perspective and insight. I have also enjoyed working with the new generation: Joe Hayden, Bill Chappell, Lee Harle, Jim Becker, Alex Margomenos, Dimitrios Peroulis, Ron Reano, Jad Risk, Costas Sarris, Tom Schwarz, and Guan Leng Tan. I wish you all the best of luck.

Anyone who processes in the SSEL clean room can appreciate the long tedious hours spent under yellow lighting. The SSEL staff, Jim Kulman, Keith Bowerman, Phil Collica, and especially Tim Brock helped me many times with equipment and processing problems.

I would like to acknowledge the assistance of Tom Ellis in using HFSS and assisting in simulation optimization of the 3-via vertical interconnects. Thank you to Professor Tom Weller for his design assistance with the distribution network components. With regard to the wafer-to-wafer interconnects I would like to acknowledge the discussions and help of Dr. Arturo Ayon at the Massachusetts Institute of Technology, Cambridge, Massachusetts and Ms. Sonbol Ansari at Integrated Circuit Systems, Ann Arbor, Michigan.

The Power Cube project was funded by DARPA/ETO (contract N66001-96-C-8635), and I would like to thank the other University of Michigan team members for their support: Dr. Rashaunda Henderson, Dr. Gildas Gauthier, Dr. Jean-Pierre Raskin, Dr. Steve Robertson, and Dr. Jong-Gwan Yook. My friendship with Dr. Henderson has been invaluable both personally and professionally. I am so happy we had each other to lean on throughout our tenure at the University of Michigan.

Thank you to my family and friends, especially Mark and Zoë Sakalauskas for feeding Jeremy and me after late nights in the lab. I would also like to thank my parents-in-law, Jean and Roger Muldavin, for their kindness. Finally, I would like to thank my mother, Sandra Blair, and my father, Donald Herrick, for their love and support throughout my life. I am grateful to my father for stressing the importance of education and for his constant encouragement.

Lastly, I would like to thank my husband, Jeremy Muldavin, for his unfailing love, support, and strength. He has brightened and enriched my life immeasurably.

# **PREFACE**

This thesis presents several low-loss micromachined W-band circuit components suitable for integration in a multi-layer silicon environment. Some of these components are micromachined finite ground coplanar waveguides, micromachined circuit combining networks, through-wafer vertical interconnects, and wafer-to-wafer vertical interconnects. In addition, this thesis also includes implementation of these novel architectures into the first 94 GHz micromachined silicon multi-layer transmit module. This transmit module is not only a high-density multi-layer circuit, but an integrated conformal package utilizing thermocompression bonding. The multi-layer silicon environment, with appropriate design and packaging, can provide a solution to the low power problems of conventional monolithic microwave integrated circuits (MMICs) by providing more power per unit area. Although this research effort includes a large fabrication effort, the work is presented with equal weighting on design, simulation, fabrication, and measurement. The strong technology base established through this project forms a legacy for future technology maturation and may also be applied at lower frequencies.

# TABLE OF CONTENTS

| DEDICATION                                               | . ii          |

|----------------------------------------------------------|---------------|

| ACKNOWLEDGEMENTS                                         | . iii         |

| PREFACE                                                  | . v           |

| LIST OF TABLES                                           | . ix          |

| LIST OF FIGURES                                          | . xi          |

| LIST OF APPENDICES                                       | . xvii        |

| CHAPTERS                                                 |               |

| 1 INTRODUCTION                                           |               |

| 1.1 Motivation                                           | . 1           |

| 1.1.1 Current Integrated Circuit Applications            | . 1           |

| 1.1.2 Future Integrated Circuit Applications             |               |

| 1.2 Subject Overview                                     |               |

| 1.2.1 High Frequencies                                   |               |

| 1.2.2 Numerical Simulations                              | . 6           |

| 1.2.3 Silicon as a Substrate                             |               |

| 1.2.4 Integrated Circuit Processing                      | . 9           |

| 1.2.5 Measurement and Calibration                        |               |

| 1.2.6 Planar Transmission Lines: Coplanar Versus Microst | <b>rip</b> 15 |

| 1.3 Thesis Overview                                      |               |

| 2 SILICON MICROMACHINED COPLANAR WAVEGUIDES .            |               |

| 2.1 Introduction                                         |               |

| 2.2 Motivation                                           |               |

| 2.3 Micromachined Coplanar Waveguide                     |               |

| 2.3.1 Line Architecture                                  |               |

| 2.3.2 Fabrication                                        |               |

| 2.4 Measurements                                         |               |

| 2.4.1 Effect of Micromachining and Lateral Undercut      |               |

| 2.4.2 Maintaining Characteristic Impedance.              |               |

| 2.4.3 Micromachined Low pass FGC Filter                  |               |

| 2.5 Modeling of Micromachined Coplanar Waveguide         | . 44          |

|   | 2.6  | Conclusions                                   | . 4 |

|---|------|-----------------------------------------------|-----|

| 3 | SING | GLE-LAYER SILICON MICROMACHINED VERTICAL IN-  |     |

| J |      | CONNECTS                                      |     |

|   | 3.1  | Introduction                                  |     |

|   | 3.2  | Motivation                                    |     |

|   | 3.3  | Vertical Interconnect Concept                 |     |

|   | 3.4  | Preliminary Design and Simulation             |     |

|   | 3.5  | Improved Design and Simulation                |     |

|   | 3.6  | Fabrication Technique                         |     |

|   | 3.7  | Measured Results                              |     |

|   | 3.8  | Design                                        |     |

|   | 3.9  | Conclusions                                   |     |

|   |      |                                               |     |

| 4 | TWO  | D-LAYER WAFER-TO-WAFER TRANSITION             |     |

|   | 4.1  | Introduction                                  | . 7 |

|   | 4.2  | Motivation                                    | . 7 |

|   | 4.3  | Design                                        | . 7 |

|   | 4.4  | Fabrication                                   | . 8 |

|   | 4.5  | Wafer Alignment and Thermocompression Bonding | . 8 |

|   |      | 4.5.1 Theoretical Considerations              |     |

|   |      | 4.5.2 Experimental set-up                     |     |

|   | 4.6  | Measurements                                  | 9   |

|   | 4.7  | Bond Evaluation and Analysis                  |     |

|   |      | 4.7.1 Misalignment                            |     |

|   |      | 4.7.2 Contact                                 |     |

|   | 4.8  | Conclusions                                   | 10  |

| 5 | MICE | ROMACHINED CIRCUIT COMBINING NETWORKS         | 10  |

| • | 5.1  | Introduction                                  |     |

|   | 5.2  | Motivation                                    |     |

|   | 5.3  | Components                                    |     |

|   | 5.4  | Interconnects                                 |     |

|   | 5.5  | Fabrication                                   | 11  |

|   | 5.6  | Measurements                                  |     |

|   |      | 5.6.1 Components                              |     |

|   |      | 5.6.2 Interconnects                           |     |

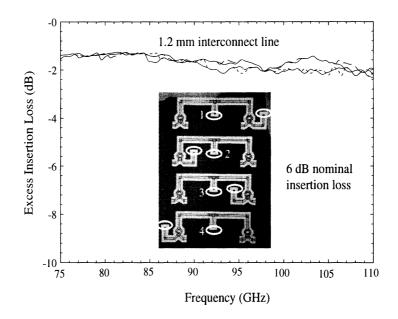

|   |      | 5.6.3 1:2 Combining Network                   |     |

|   |      | 5.6.4 1:4 Combining Network                   |     |

|   |      | 5.6.5 1:8 Combining Network                   |     |

|   | 5.7  | Conclusions                                   |     |

|   |      |                                               | 14  |

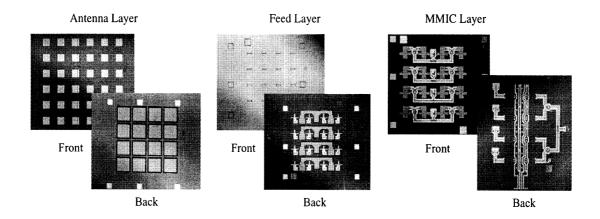

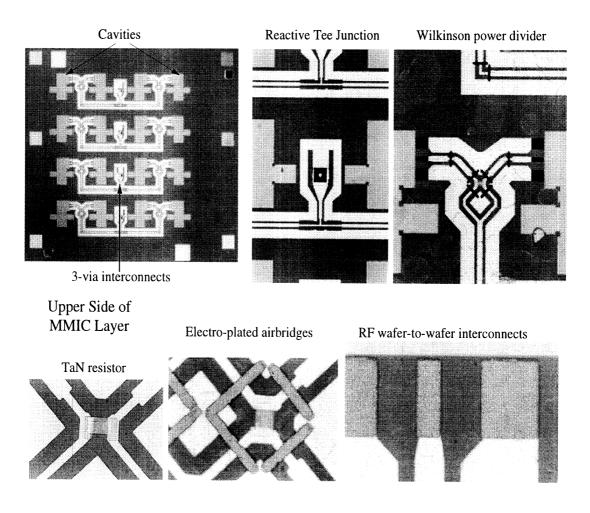

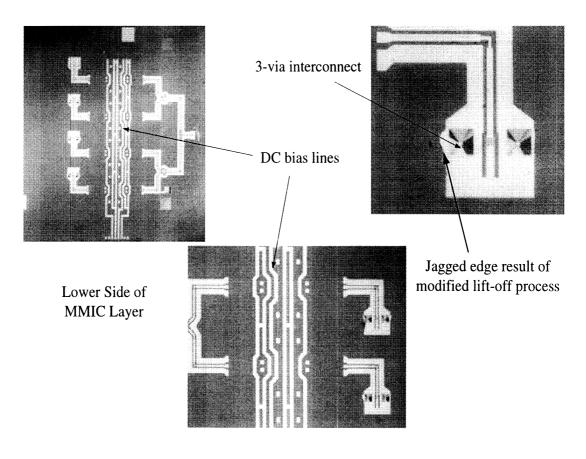

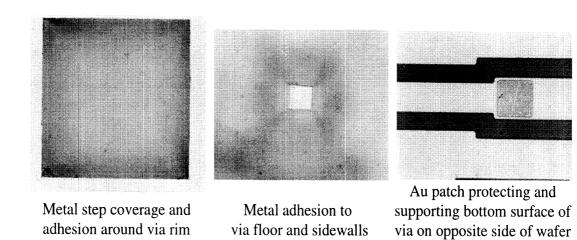

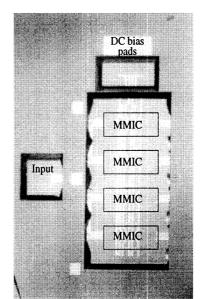

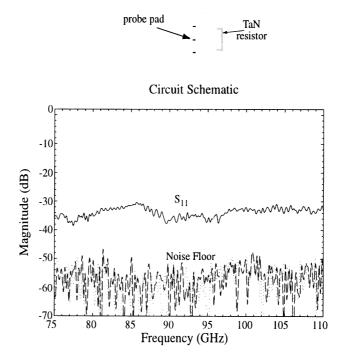

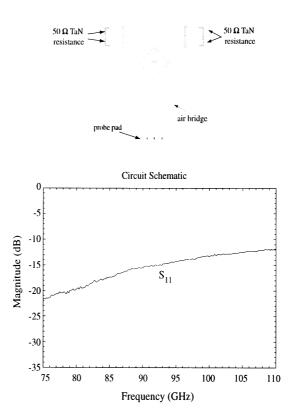

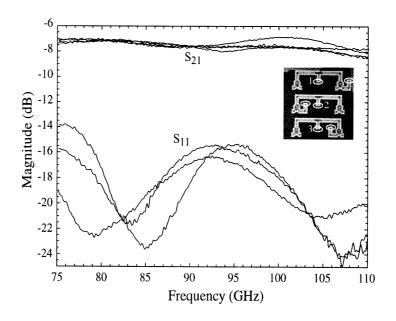

| 6 | MICF | ROMACHINED W-BAND POWER CUBE                  | 12  |

|   | 6.1  | Introduction                                  | 12  |

|   | 6.2  | Power Cube Overview                           | 13  |

|   | 6.3  | Passive Component Integration                 | 13  |

|   |      | 6.3.1 Packaging and Coupling Effects          |     |

|   |      | 6.3.2 Fabrication                             | 1.4 |

| 6.4 Wafer Alignment and Bonding                        | 48 |

|--------------------------------------------------------|----|

| 6.5 Measurements                                       | 53 |

| 6.6 <b>Conclusions</b>                                 | 58 |

| 7 CONCLUSIONS AND FUTURE WORK                          | 60 |

| 7.1 <b>Summary</b>                                     | 60 |

| 7.2 <b>Future Work</b>                                 | 61 |

| 7.2.1 Transmit and Receive Module with Focused, Steer- |    |

| able Array                                             | 61 |

| 7.2.2 Fabrication Enhancements                         | 62 |

| 7.2.3 Adverse Weather UAV 35 GHz SAR Imaging System 1  | 62 |

| APPENDICES                                             | 63 |

| BIBLIOGRAPHY                                           | 30 |

# LIST OF TABLES

| Гable |                                                                                                                                                                   |     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1   | Examples of High Frequency Electromagnetic Simulation Software                                                                                                    | 7   |

| 1.2   | Wet etchants for Si bulk micromachining                                                                                                                           | 9   |

| 1.3   | 50 $\Omega$ Microstrip losses at 30 GHz. [88, 40]                                                                                                                 | 17  |

| 2.1   | Decreasing $\epsilon_{eff}$ , decreasing attenuation (at 94 GHz), and increasing characteristic impedance for three different aspect ratios (AR), with increasing |     |

| 0.1   | undercut.                                                                                                                                                         | 41  |

| 3.1   | Multichip Module (MCM) assembly techniques for X-band frequencies (current state-of-the art)[32, 63]                                                              | 51  |

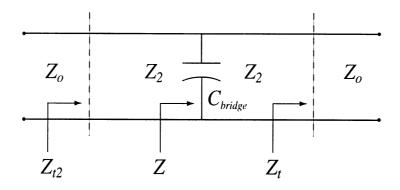

| 3.2   | Results of air bridge capacitive modeling using 2-D static solver [5]                                                                                             | 69  |

| 3.3   | Length of quarter wavelength tuning stub for FGC on Silicon with effective                                                                                        | 09  |

|       | dielectric constant of 6 as a function of frequency                                                                                                               | 70  |

| 3.4   | Anisotropically micromachined via dimensions for different silicon thicknesses                                                                                    |     |

|       | with 10 x 10 $\mu$ m via base                                                                                                                                     | 70  |

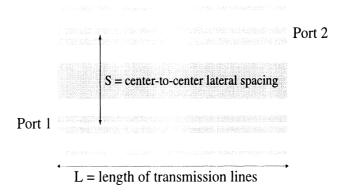

| 4.1   | Characteristics of feed line and transition geometries                                                                                                            | 76  |

| 4.2   | Back-to-back RF wafer-to-wafer transition simulation summary                                                                                                      | 80  |

| 4.3   | Back-to-back wafer-to-wafer interconnect measurement summary from 90-98                                                                                           |     |

|       | $\mathrm{GHz}$                                                                                                                                                    | 94  |

| 4.4   | Wafer-to-wafer interconnect summary from 90-98 GHz                                                                                                                | 100 |

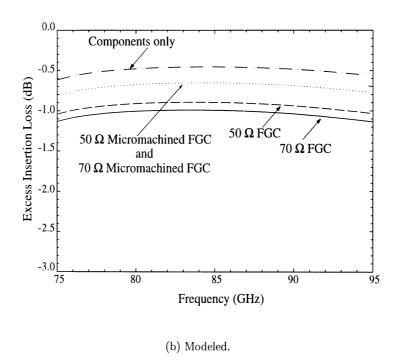

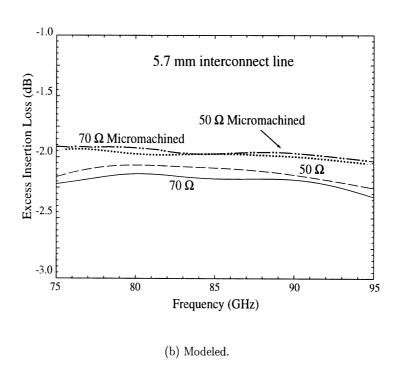

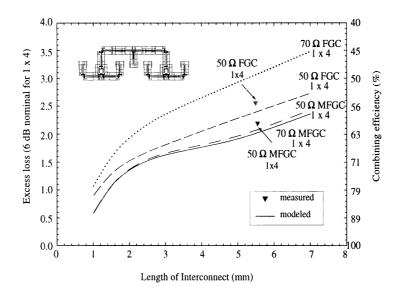

| 5.1   | IE3D estimated loss for 1:2, 1:4, 1:8 circuit networks                                                                                                            | 109 |

| 5.2   | Characteristics of micromachined and unmicromachined lines                                                                                                        | 109 |

| 5.3   | Estimated component insertion loss values at 94 GHz as taken from mea-                                                                                            |     |

|       | surement. The error of the measurement for the 50 $\Omega$ components is $\pm$ 0.03                                                                               |     |

|       | dB, and the error for the 70 $\Omega$ component measurements is $\pm$ 0.07 dB                                                                                     | 113 |

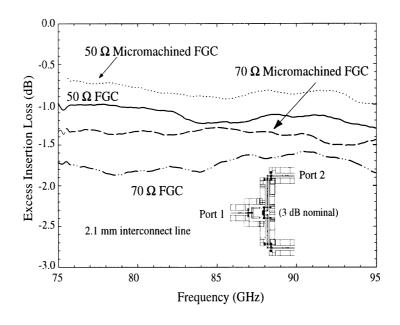

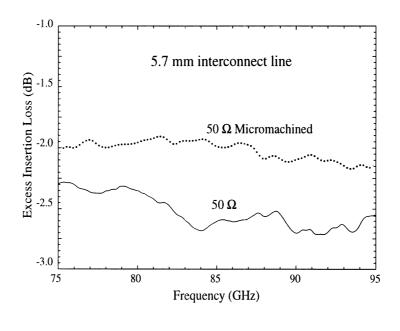

| 5.4   | Measured and modeled attenuation values from 85-95 GHz                                                                                                            | 114 |

| 5.5   | Estimated excess loss for 1:2 circuit networks as compared with measured                                                                                          |     |

|       | results at 85 GHz. Interconnect loss is shown for 2.1 mm, and component                                                                                           |     |

|       | loss is given for 1 Wilkinson and 1 bend. Measurement error is $\pm$ 0.1 dB                                                                                       | 118 |

| 5.6   | Estimated excess loss for 1:4 circuit networks as compared with measured results at 85 GHz. Interconnect loss is shown for 5.7 mm, and component                  |     |

|       | loss is given for 1 Wilkinson, 1 tee, and 2 bends. Measurement error at 85                                                                                        |     |

|       | GHz is $\pm$ 0.1 dB                                                                                                                                               | 123 |

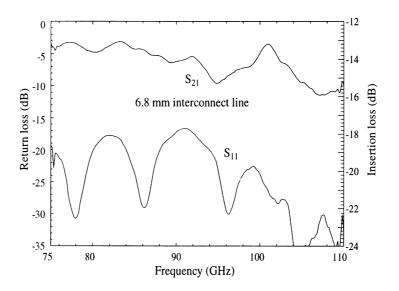

| 5.7 | Estimated excess loss for 1:8 circuit networks as compared with measured                        |     |

|-----|-------------------------------------------------------------------------------------------------|-----|

|     | results at 85 GHz. Interconnect loss is shown for 6.8 mm, and component                         |     |

|     | loss is given for 2 Wilkinsons, 1 tee, and 3 bends. Measurement error for the                   |     |

|     | 50 and 70 $\Omega$ circuits is $\pm$ 0.2 and $\pm$ 0.4 dB, respectively                         | 125 |

| 5.8 | Summary of excess insertion loss for 1:2, 1:4, and 1:8 circuit combining net-                   |     |

|     | works at 85 GHz. Error margins are excluded                                                     | 128 |

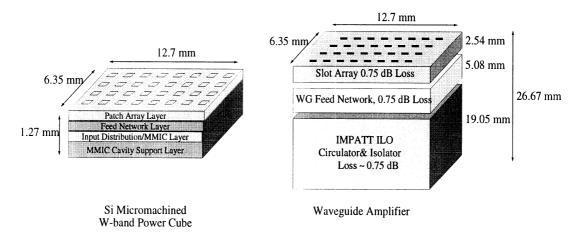

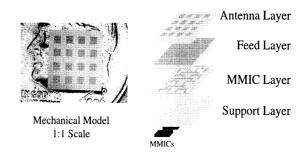

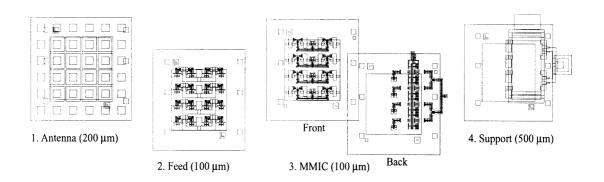

| 6.1 | Comparison of predicted W-band power cube performance and comparable                            |     |

|     | waveguide amplifier (courtesy Dr. Robert T. Kihm)                                               | 130 |

| 6.2 | Amplifier-to-Array loss at 94 GHz                                                               | 158 |

| A.1 | Capacitance per unit length, $\epsilon_{eff}$ , and $Z_o(\Omega)$ for 3 FGC geometries with and |     |

|     | without air bridges                                                                             | 167 |

| A.2 | Capacitance per unit length multiplied by physical width determines capac-                      |     |

|     | itance of air bridges for 3 FGC geometries.                                                     | 168 |

| A.3 | $C$ , $l_1$ , and $l_2$ for different air bridge widths and aspect ratios                       | 169 |

| A.4 | Tabulated results of Figure A.6 averaged from 90-100 GHz                                        | 171 |

| A.5 | Tabulated results of Figure A.7 averaged from 90-100 GHz                                        | 172 |

| A.6 | Tabulated results of Figure A.8 averaged from 90-100 GHz                                        | 173 |

| A.7 | Tabulated results of Figure A.9 averaged from 90-100 GHz                                        | 174 |

| A.8 | Tabulated results of Figure A.10 averaged from 90-100 GHz                                       | 175 |

| A.9 | Tabulated results of Figure A.11 averaged from 90-100 GHz                                       | 176 |

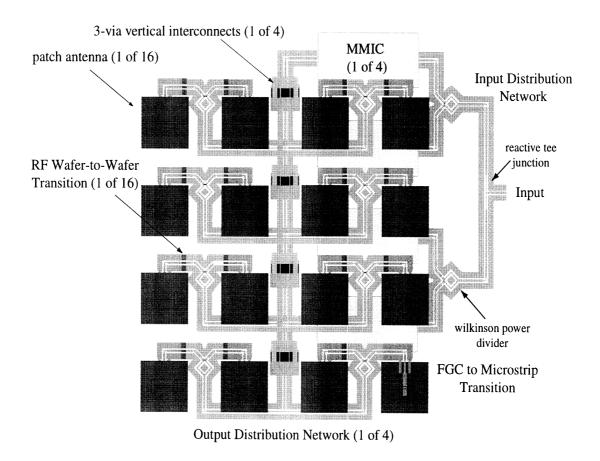

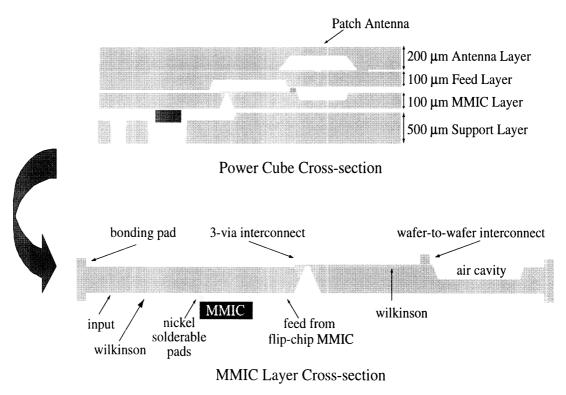

# LIST OF FIGURES

| Figure |                                                                                          |    |

|--------|------------------------------------------------------------------------------------------|----|

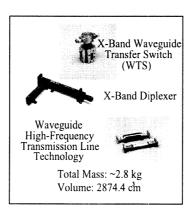

| 1.1    | Traditional waveguide components for satellite communications at X-band                  |    |

|        | (8-12 GHz)                                                                               | ]  |

| 1.2    | Deutche Aerospace T/R MCM radar module [81, 32]                                          | 2  |

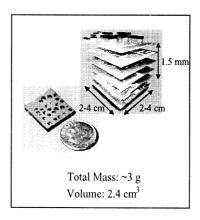

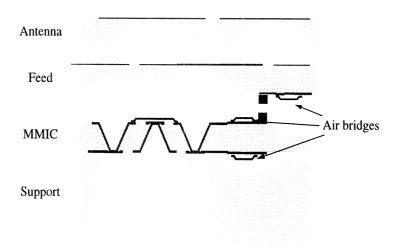

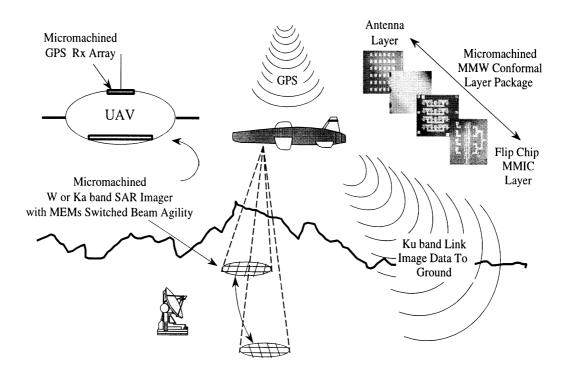

| 1.3    | Silicon multi-layer future technology                                                    | į  |

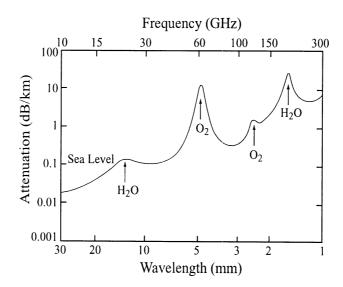

| 1.4    | Average atmospheric absorption as a function of frequency and wavelength [7].            | 5  |

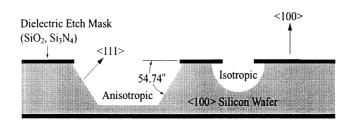

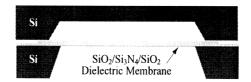

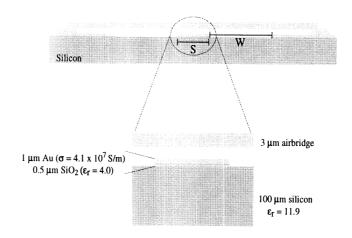

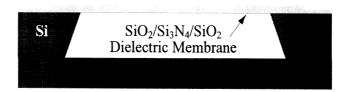

| 1.5    | Cross-section of micromachined Si wafer                                                  | 8  |

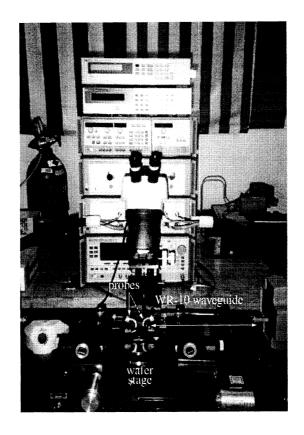

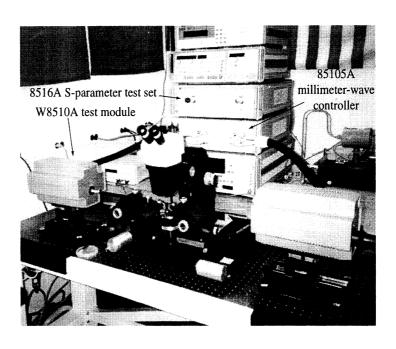

| 1.6    | W-band measurement set-up                                                                | 14 |

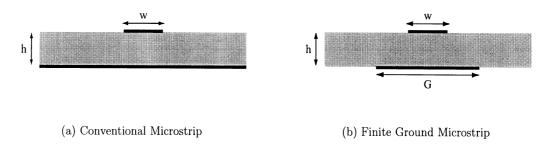

| 1.7    | Microstrip                                                                               | 16 |

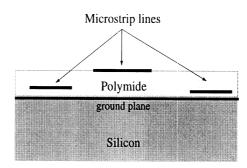

| 1.8    | Schematic of high-density integration(HDI) as applied to microstrip                      | 17 |

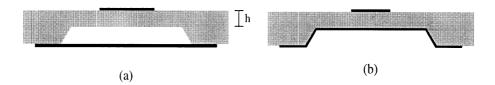

| 1.9    | Alternative microstrip geometries $(h >= 30 \mu \text{m}) \dots \dots \dots \dots$       | 18 |

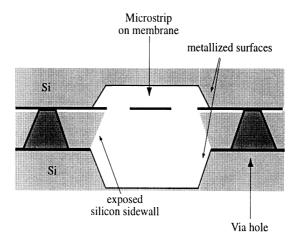

| 1.10   | Membrane microstrip [92]                                                                 | 19 |

|        | Alternative version of membrane microstrip [11]                                          | 19 |

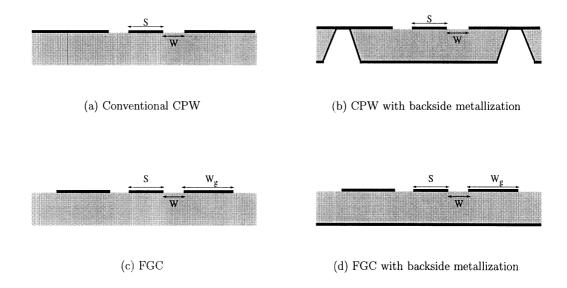

|        | Coplanar waveguide geometries                                                            | 20 |

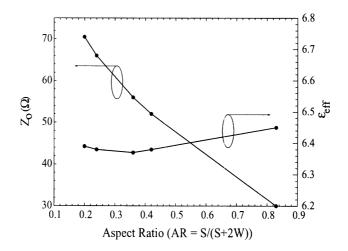

| 1.13   | $Z_o$ and $\epsilon_{eff}$ for various FGC aspect ratios where S is the center conductor |    |

|        | width and W is the aperture width.                                                       | 21 |

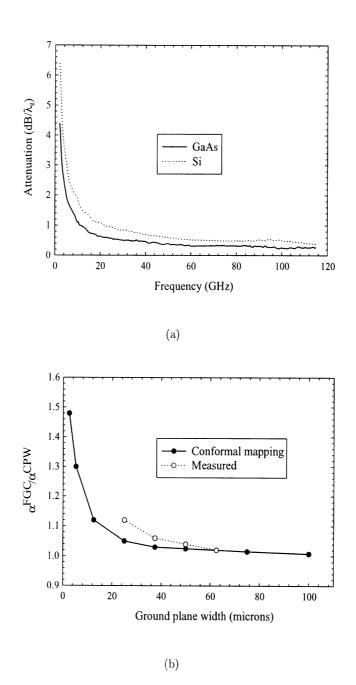

| 1.14   | (a) Attenuation versus frequency for 50 $\Omega$ FGC line on Si and GaAs. (b)            |    |

|        | Attenuation of FGC lines with S=W=25 $\mu$ m normalized to the attenuation               |    |

|        |                                                                                          | 22 |

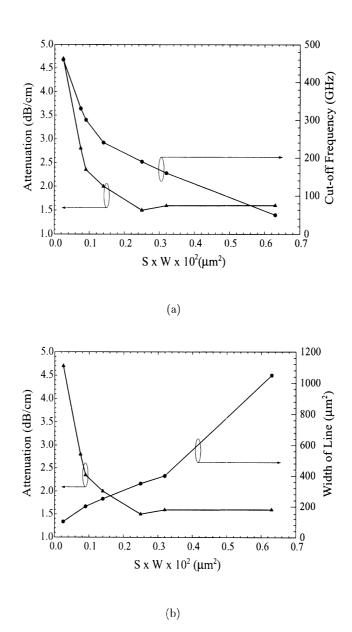

| 1.15   | Attenuation at 40 GHz, (a) cut-off frequency, and (b) line width versus S×W.             |    |

|        | All measurements performed on silicon substrates of various thicknesses                  | 23 |

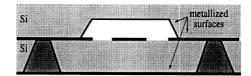

|        | Microshield line.                                                                        | 24 |

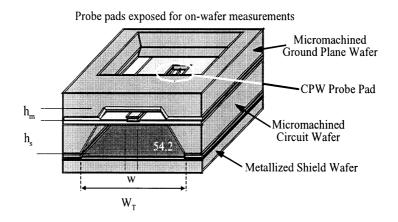

|        | Packaged microstrip line                                                                 | 25 |

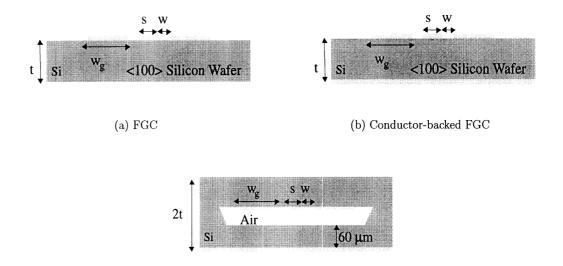

| 2.1    | Finite Ground Coplanar Waveguide: (a) FGC on high-resistivity Si. (b)                    |    |

|        | Packaged FGC                                                                             | 28 |

| 2.2    | State of the Art Low-loss FGC lines (a) Microshield [125, 122, 121] (b)                  |    |

|        | Air-bridge CPW [98] (c) Micromachined CPW for CMOS [73] (d) Trenched                     |    |

| 0.0    | CPW [52] (e) Micromachined FGC presented in this chapter [45, 46]                        | 29 |

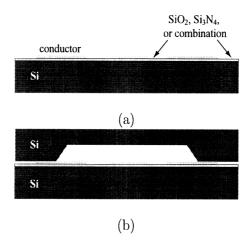

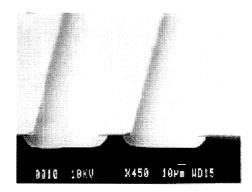

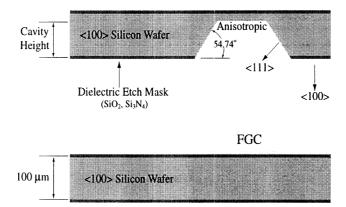

| 2.3    | Anisotropically etched Si                                                                | 32 |

| 2.4    | Isotropically etched Si                                                                  | 32 |

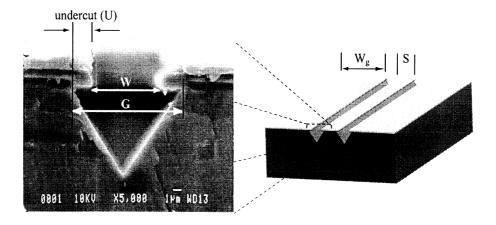

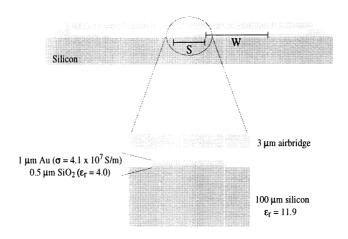

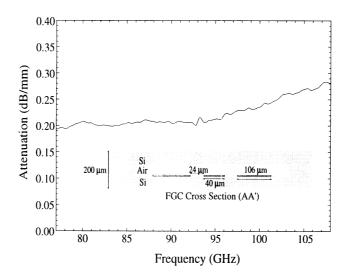

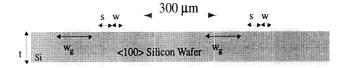

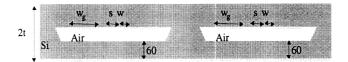

| 2.5    | Cross-section of Micromachined Finite Ground Coplanar (MFGC) line                        | 32 |

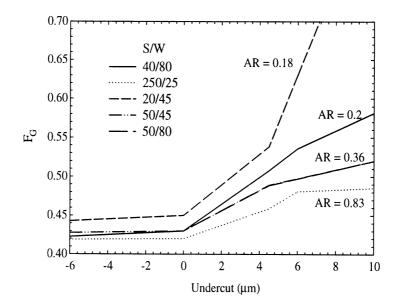

| 2.6    | $F_G$ versus Undercut( $\mu$ m) for five different aspect ratios(AR=S/(S+2W)),           | _  |

| 2.7    |                                                                                          | 34 |

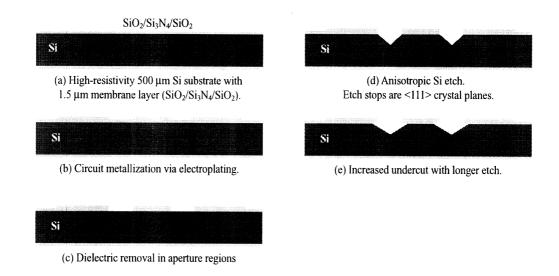

| 4.1    | MFGC process flow                                                                        | 35 |

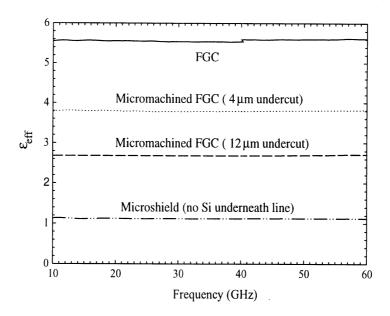

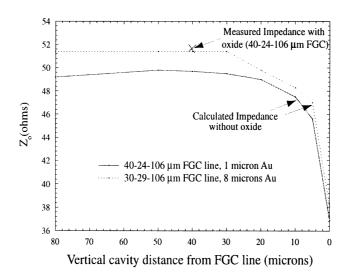

| 2.8  | $\epsilon_{eff}$ vs. frequency for a 80-40-80 $\mu m$ MFGC with 4 and 12 $\mu m$ undercut. Comparison with conventional FGC of same dimensions and 75 $\Omega$ microshield with S/W of 250/25 $\mu m$    | 36 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

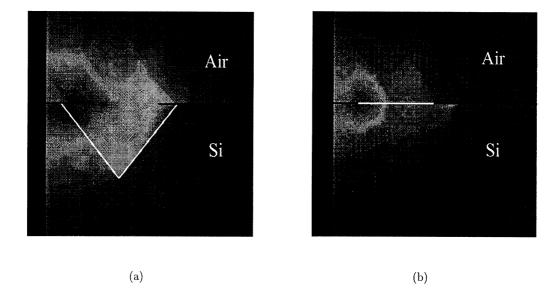

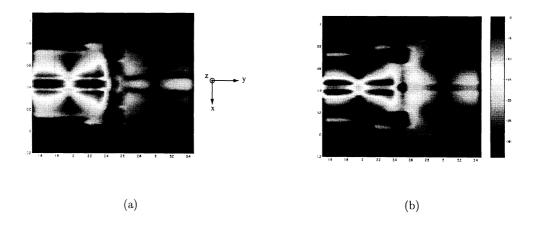

| 2.9  | Simulated electric field distribution of (a) MFGC line (b) conventional FGC.                                                                                                                             | 37 |

| 2.10 |                                                                                                                                                                                                          | 38 |

| 2.11 |                                                                                                                                                                                                          | 38 |

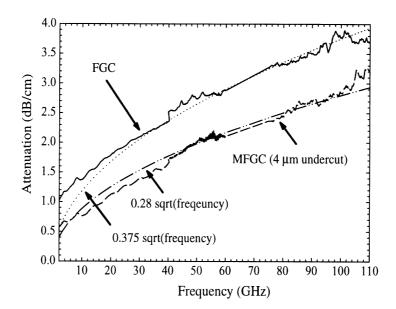

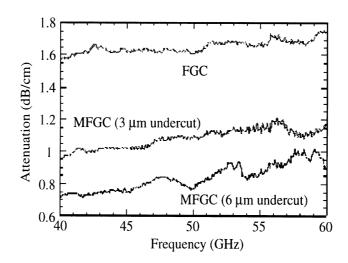

| 2.12 | Loss in dB/cm in FGC and MFGC lines with S=50 and W=45 $\mu$ m at U-band.                                                                                                                                | 39 |

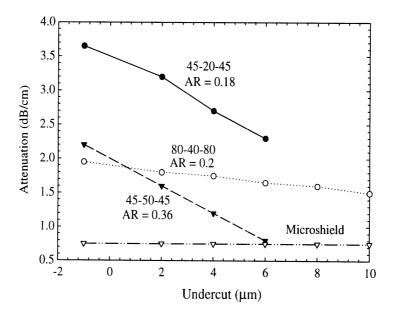

|      | Measured loss versus undercut at 94 GHz                                                                                                                                                                  | 39 |

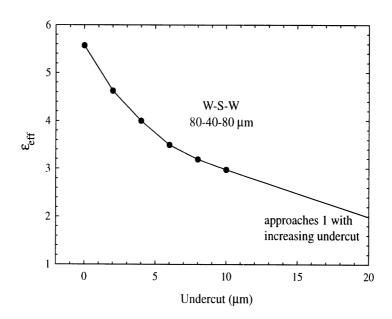

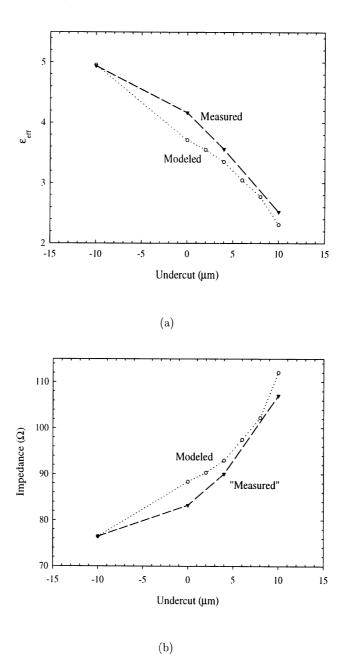

|      | Effective dielectric constant versus. undercut for MFGC with W-S-W equal to 80-40-80 $\mu$ m                                                                                                             | 41 |

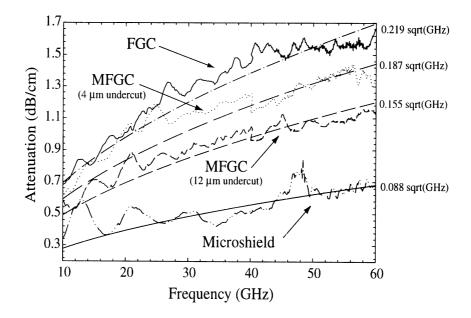

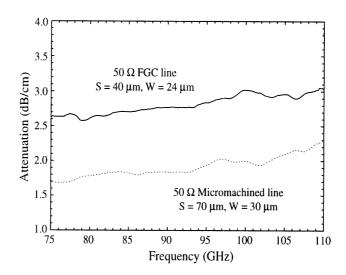

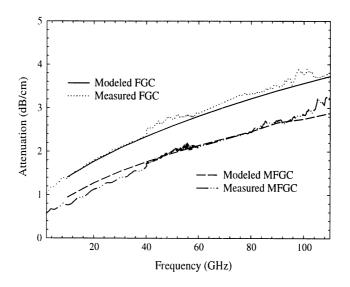

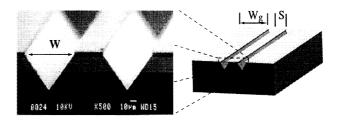

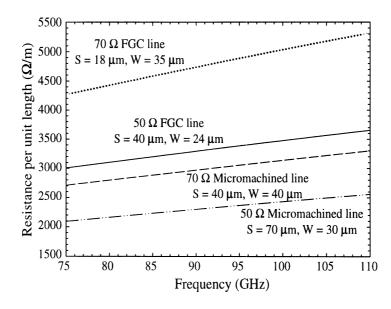

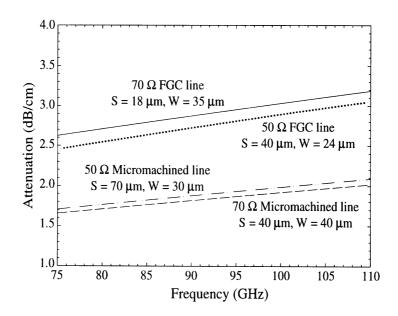

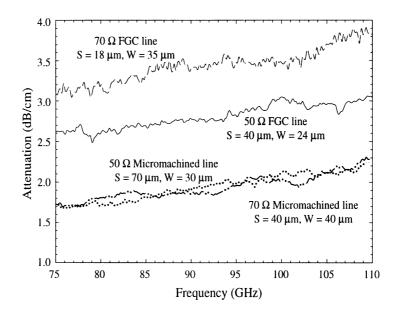

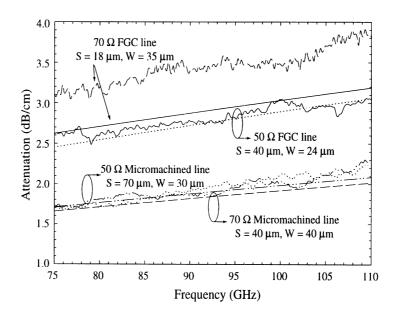

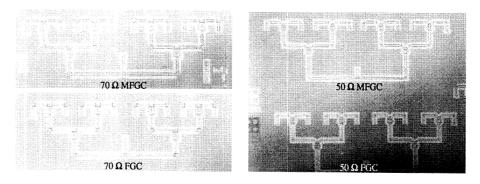

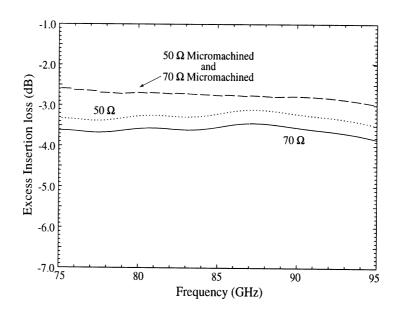

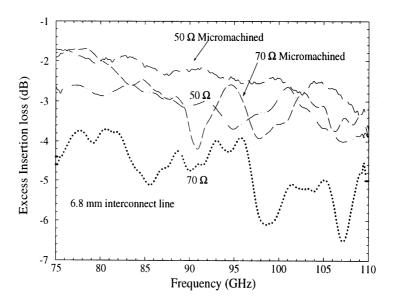

| 2.15 | Measured attenuation versus frequency for 50 and 70 $\Omega$ lines in FGC and MFGC versions showing lower loss in micromachined line                                                                     | 42 |

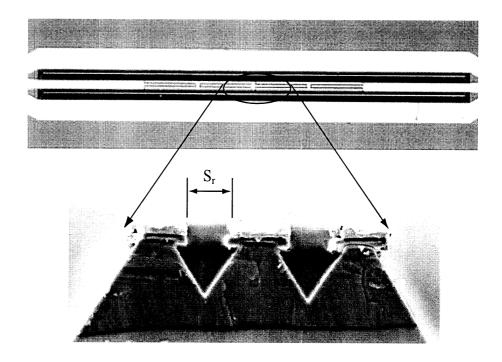

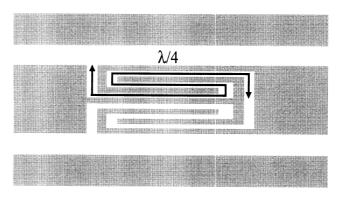

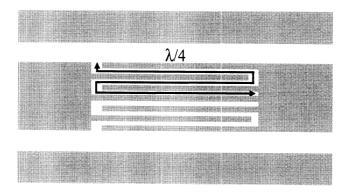

| 2.16 | Micromachined four resonator band-pass filter with W = 45 $\mu$ m, S = 50 $\mu$ m, and 4 $\mu$ m undercut.                                                                                               | 43 |

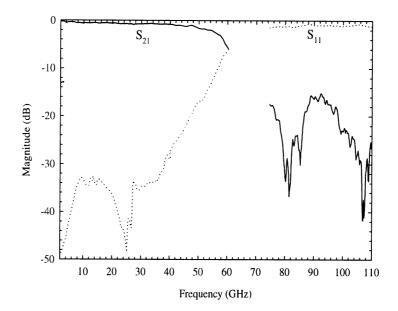

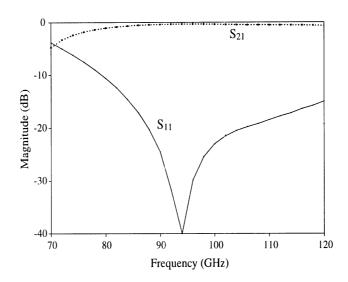

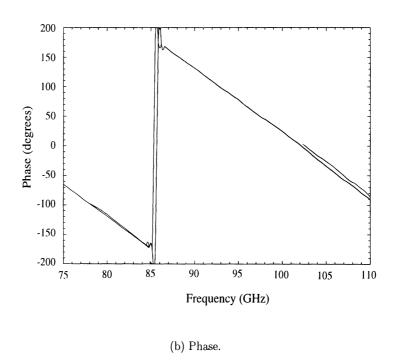

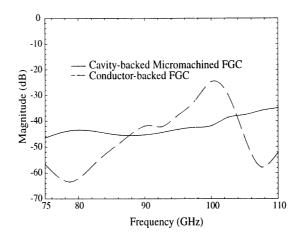

| 2.17 | Measured scattering parameters for the micromachined low pass filter of Figure 2.16                                                                                                                      | 44 |

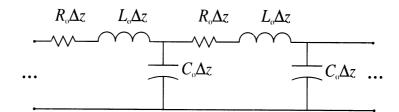

| 2.18 | Lumped-element equivalent circuit for an incremental length of transmission line                                                                                                                         | 44 |

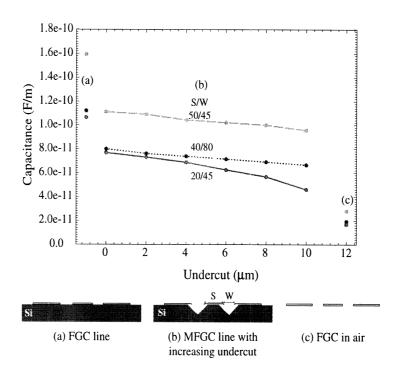

| 2.19 | Capacitance versus undercut for three FGC lines with values for (a) a conventional FGC line (b) a micromachined FGC line with increasing lateral undercut (c) a FGC in air.                              | 44 |

| 2.20 | (a) Effective dielectric constant vs. undercut for FGC and MFGC with W-S-W equal to 45-20-45 $\mu$ m. (b) Characteristic impedance vs. undercut for FGC and MFGC with W-S-W equal to 45-20-45 $\mu$ m    | 46 |

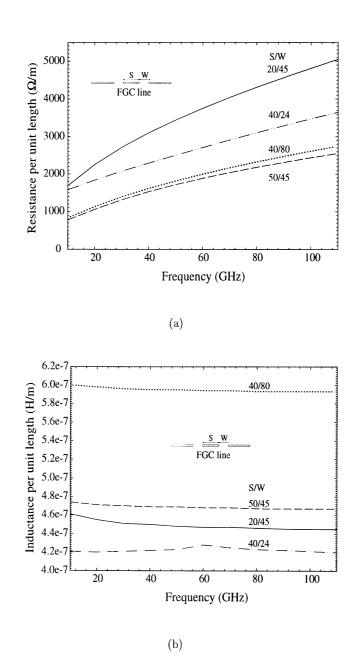

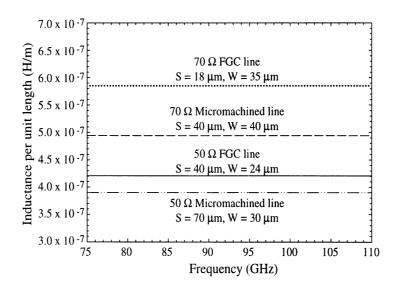

| 2.21 | (a) Resistance per unit length versus frequency for four FGC lines as found using Simian. (b) Inductance per unit length versus frequency for four FGC lines as found using Simian                       | 48 |

| 2.22 | Attenuation vs. frequency for 45-20-45 $\mu m$ line comparing measured and modeled data                                                                                                                  | 49 |

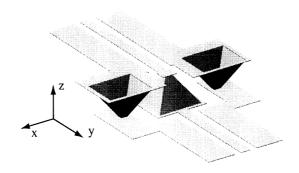

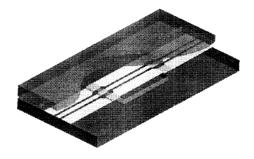

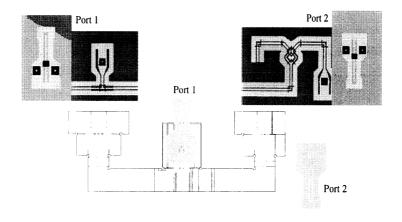

| 3.1  | A vertical interconnect employing three micromachined pyramidal via holes. The vias permeate the Si substrate (not shown) to connect the upper and lower finite ground coplanar (FGC) transmission lines | 53 |

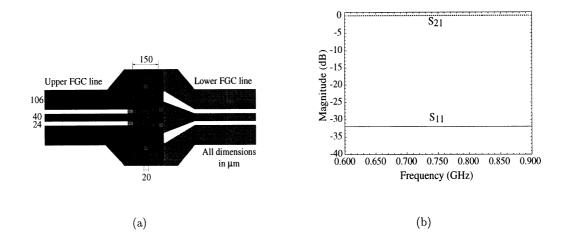

| 3.2  | (a) Schematic. (b) Simulated S-parameters for a single 3-via interconnect from 600-900 MHz.                                                                                                              | 53 |

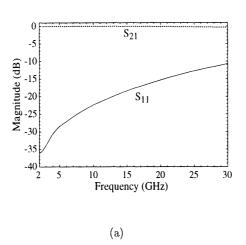

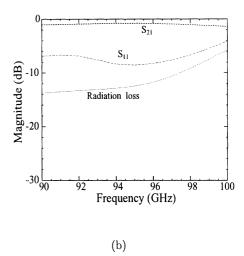

| 3.3  | Simulated S-parameters for single three-via interconnect: (a) 2-30 GHz (b) 90-105 GHz                                                                                                                    | 54 |

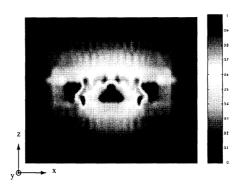

| 3.4  | Electric field distribution for yz-plane of 3.2(a)                                                                                                                                                       | 55 |

| 3.5  | <ul> <li>(a) Z-component of the electric field vector for the transition of Figure 3.2(a).</li> <li>(b) Total electric field distribution for the transition of Figure 3.2(a) showing</li> </ul>         | JJ |

|      | launched horizontal electric field component.                                                                                                                                                            | 55 |

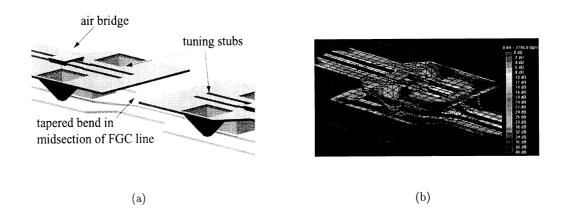

| 3.6  | (a) Schematic of improved design with tuning stub, air bridge, and tapered bend. (b) IE3D plot of current distribution for 3-via interconnect.                                                           | 56 |

| 3.7  | Simulated S-parameters for 3-via vertical interconnect                                                                                                                                                                                                             | 57         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.8  | Schematic of back-to-back vertical interconnect transition                                                                                                                                                                                                         | 58         |

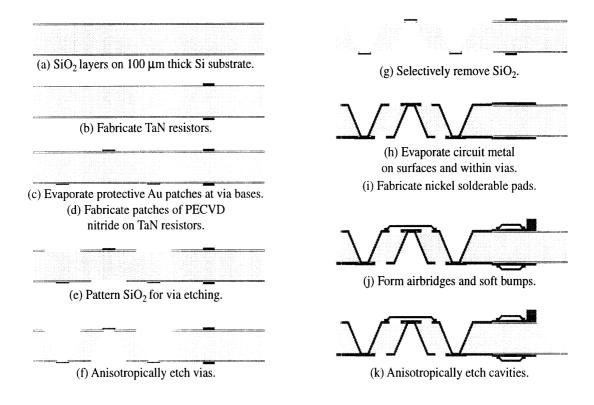

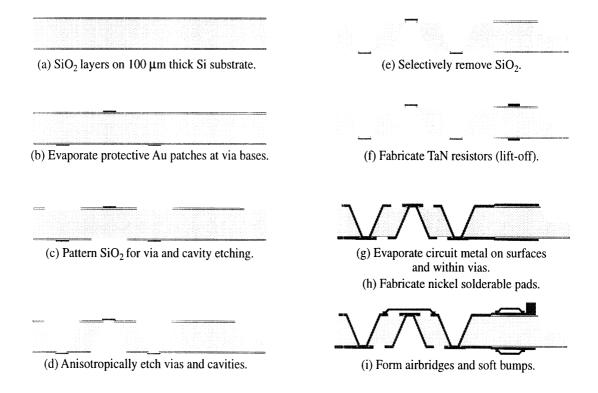

| 3.9  | Initial fabrication process of vertical interconnects                                                                                                                                                                                                              | 60         |

| 3.10 | Illustration of fabrication problems                                                                                                                                                                                                                               | 61         |

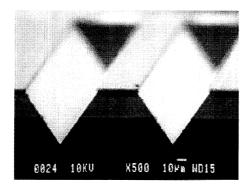

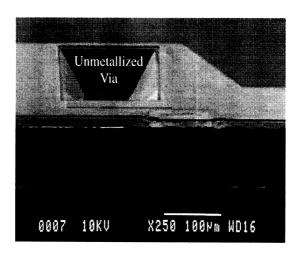

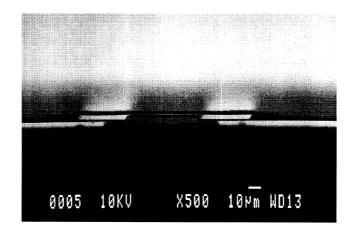

| 3.11 | SEM photographs of three-via cross-sections prior to via metallization                                                                                                                                                                                             | 62         |

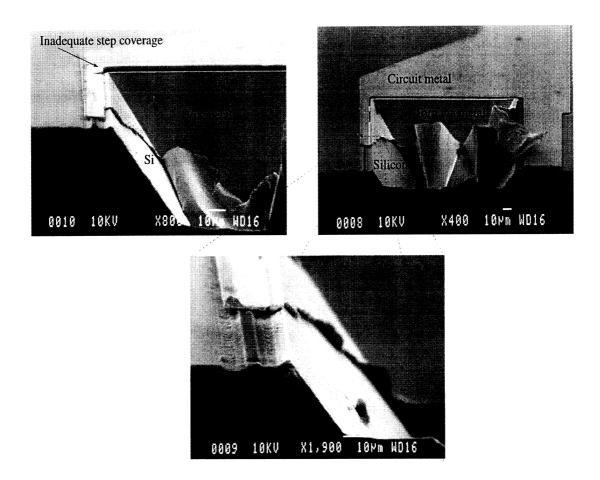

| 3.12 | SEM photographs illustrating step coverage issues with shadow mask method                                                                                                                                                                                          |            |

|      | of via metallization.                                                                                                                                                                                                                                              | 63         |

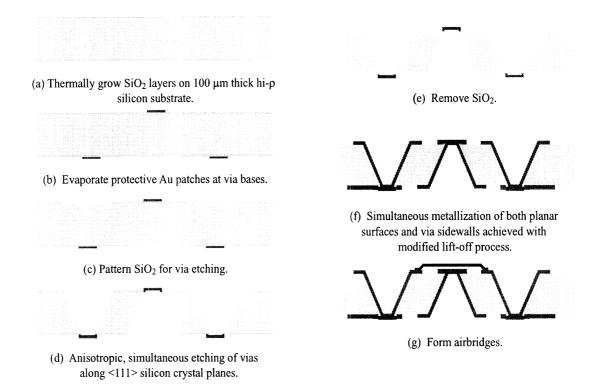

| 3.13 | Final fabrication process for vertical interconnects                                                                                                                                                                                                               | 64         |

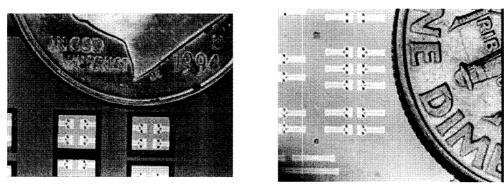

| 3.14 | Top view of fabricated vertical interconnects as compared to a dime                                                                                                                                                                                                | 64         |

| 3.15 | Photo of top and bottom of three-via back-to-back transition                                                                                                                                                                                                       | 65         |

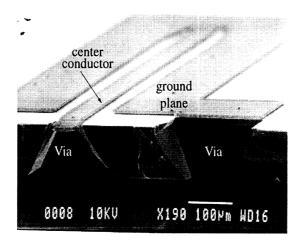

| 3.16 | Close-up within metallized via                                                                                                                                                                                                                                     | 65         |

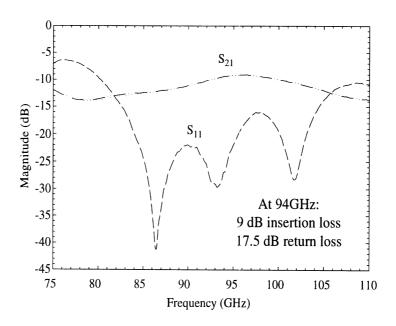

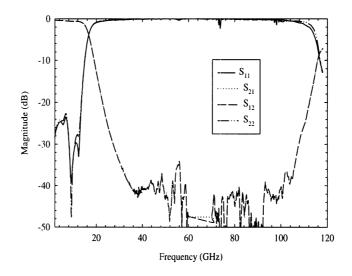

| 3.17 | Measured S-parameters of back-to-back vertical interconnect transition                                                                                                                                                                                             | 66         |

| 3.18 | Measured S-parameters of back-to-back vertical interconnect transition compared with Libra model                                                                                                                                                                   | 67         |

| 3.19 |                                                                                                                                                                                                                                                                    | 68         |

| 3.20 | Measured S-parameters of back-to-back vertical interconnects: a) 934 $\mu$ m midsection, 230 $\mu$ m stub, and 100 $\mu$ m air bridge. b)734 $\mu$ m midsection, 240 $\mu$ m stub, and 130 $\mu$ m air bridge                                                      | 68         |

| 3 21 | Cross section of air bridge over FGC line.                                                                                                                                                                                                                         | 69         |

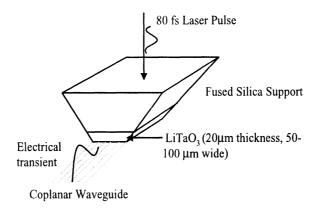

| 4.1  | Three examples of commercial wafer bonding applications a) Sensor Chip for Ford MEMs automotive airbag accelerometer b) Sensor Chip for Motorola micromachined automotive airbag accelerometer c) Micromachined turbine from MIT's Micro gas turbine engine [116]. | 74         |

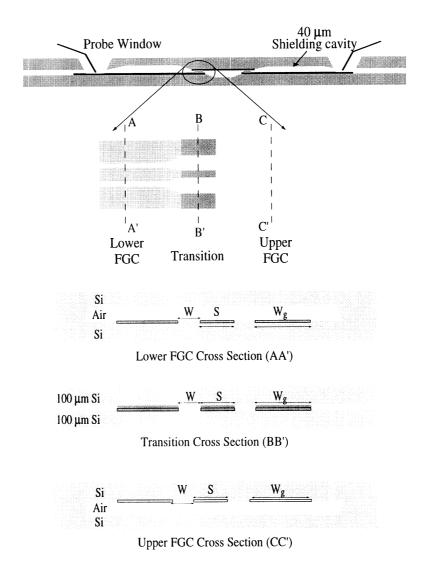

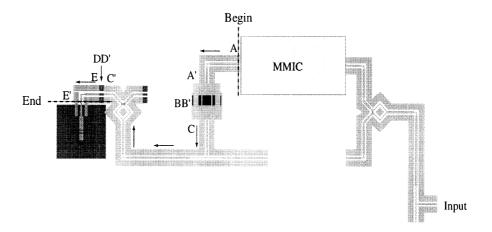

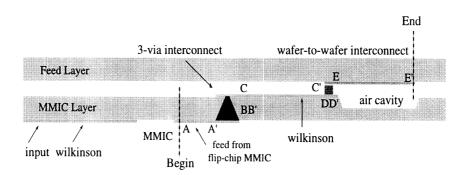

| 4.2  | Illustration of wafer to wafer transition                                                                                                                                                                                                                          | 75         |

| 4.3  | Schematic for Maxwell 2D RF interconnect simulation                                                                                                                                                                                                                | 76         |

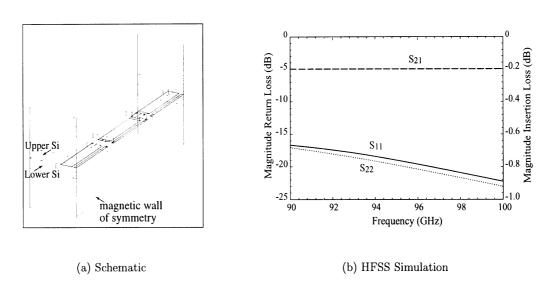

| 4.4  | HFSS simulation results for RF back-to-back interconnect with 30-59-100 $\mu$ m transition. The geometry is cut lengthwise through the center conductor and a magnetic wall is used for symmetry. Perfect conductors are used. (a)                                 |            |

| 4.5  | Schematic (b) Simulated S-parameters                                                                                                                                                                                                                               | 77         |

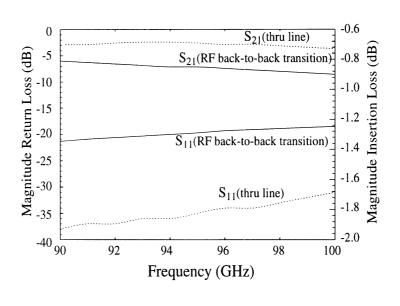

| 4.0  | HFSS simulation results for RF back-to-back interconnect with 30-59-100 $\mu m$ transition as compared with through line of same length. Finite conductivity                                                                                                       |            |

|      | of $4.1 \times 10^7$ Siemens/meter is used. (a) Schematic (b) Simulated S-parameters                                                                                                                                                                               | 70         |

| 4.6  | HFSS simulation results for RF back-to-back interconnect with (a) 20-44-                                                                                                                                                                                           | 10         |

| 1.0  | 100 $\mu$ m and (b) 40-65-100 $\mu$ m transition                                                                                                                                                                                                                   | 79         |

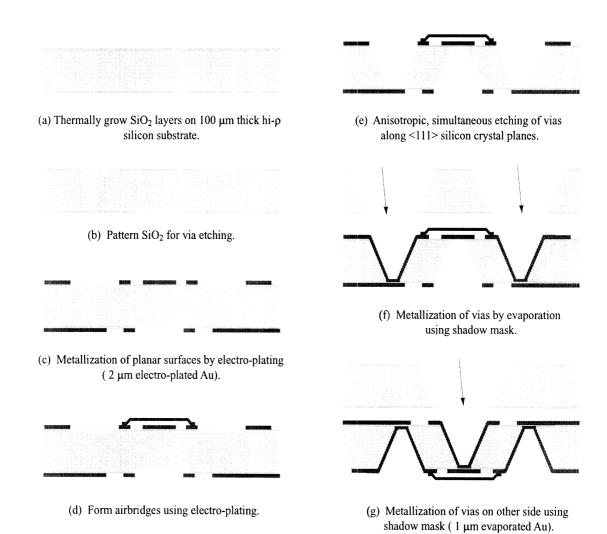

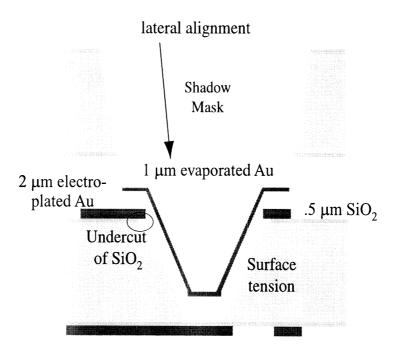

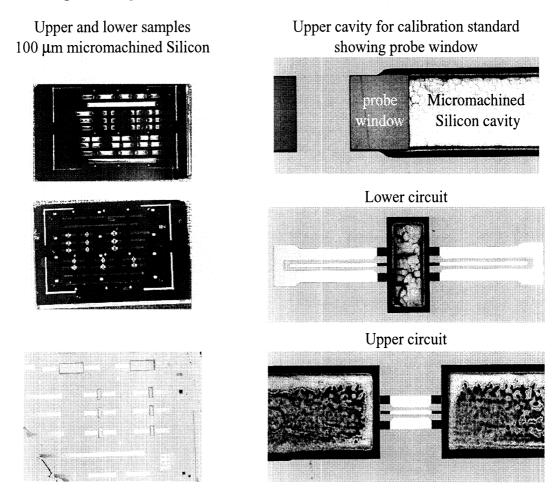

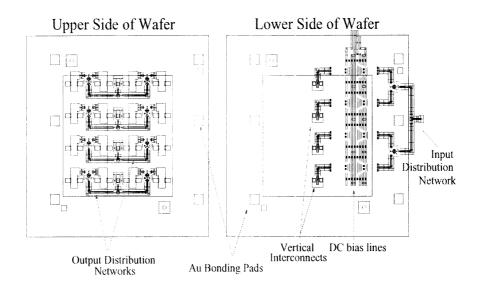

| 4.7  | Fabrication of Upper and Lower 100 $\mu$ m silicon wafers for RF interconnects                                                                                                                                                                                     | 82         |

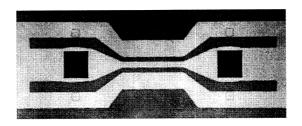

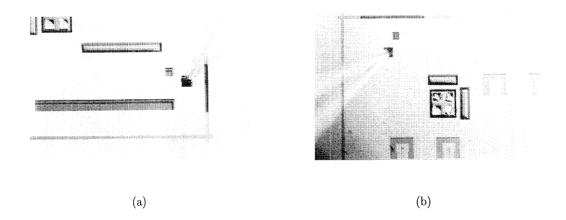

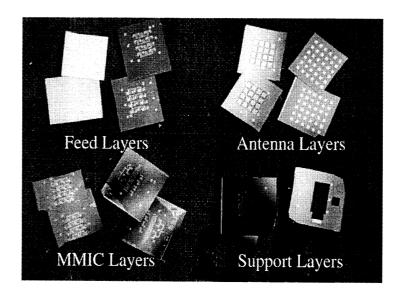

| 4.8  | Photos of fabricated circuits.                                                                                                                                                                                                                                     | 83         |

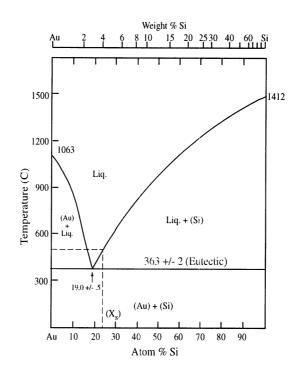

| 4.9  | Phase diagram for Au-Si [37]                                                                                                                                                                                                                                       | 87         |

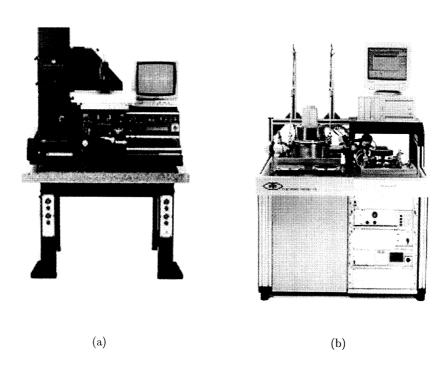

| 4.10 | Electronics Visions Align and Bond Equipment [116]                                                                                                                                                                                                                 | 88         |

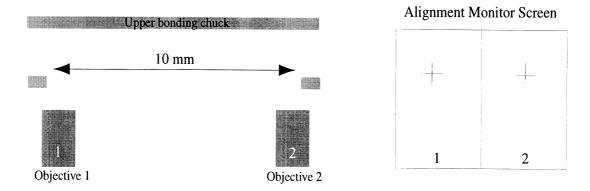

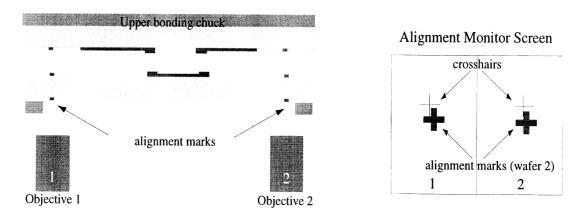

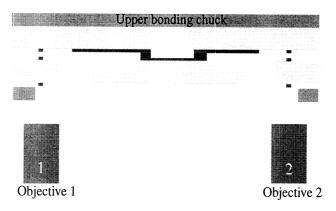

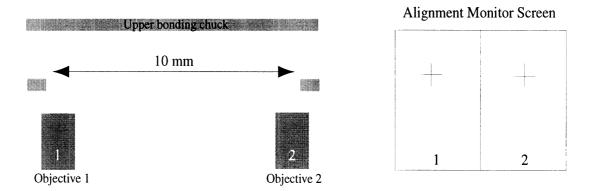

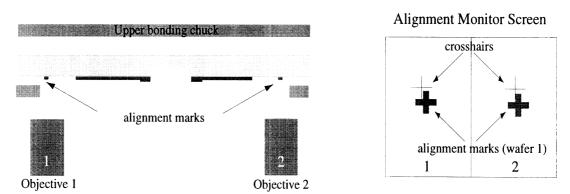

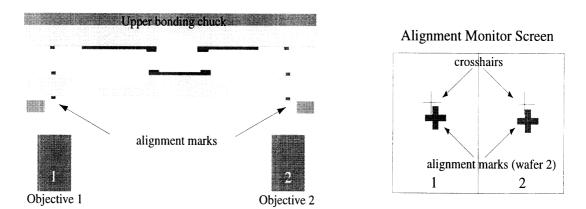

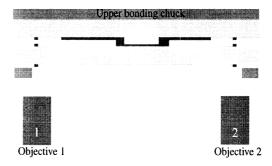

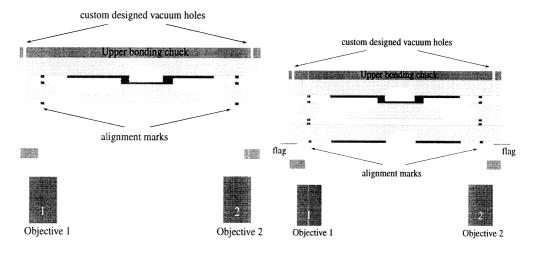

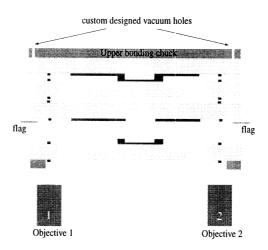

| 4.11 | Method of Alignment for Electronics Visions Equipment (a-c)                                                                                                                                                                                                        | 89         |

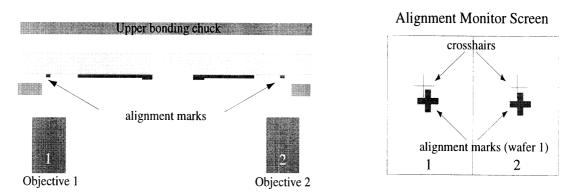

|      | Method of Alignment for Electronics Visions Equipment (d-e)                                                                                                                                                                                                        | 90         |

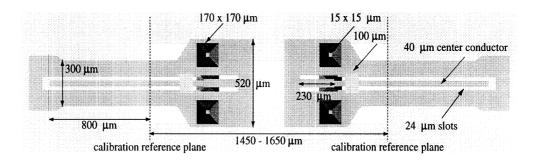

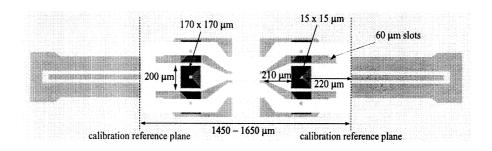

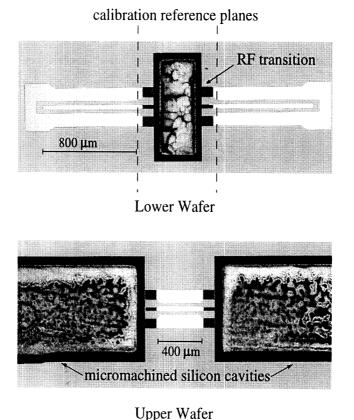

|      | Photograph of RF wafer-to-wafer transition showing placement of calibration                                                                                                                                                                                        | <i>5</i> 0 |

|      | reference planes.                                                                                                                                                                                                                                                  | 92         |

| 4.14 |                                                                                                                                                                                                                                                                    | 93         |

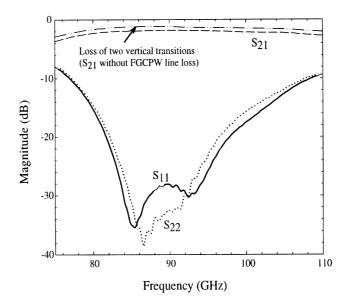

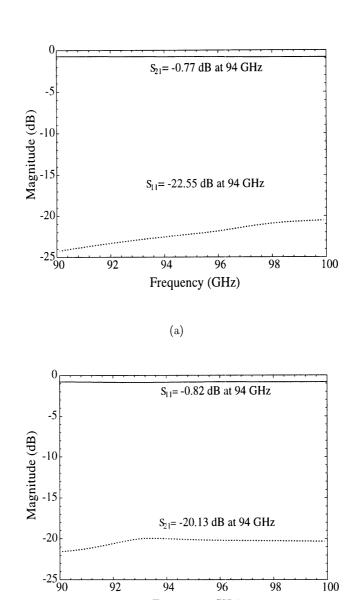

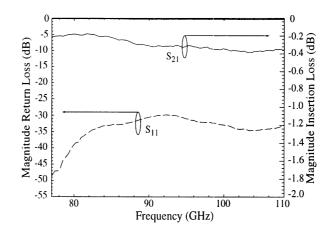

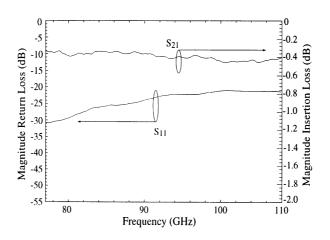

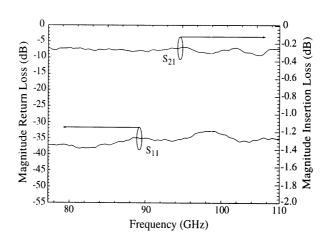

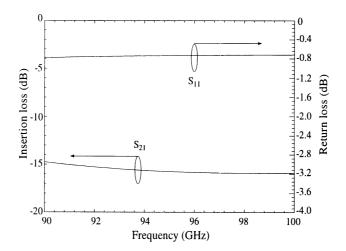

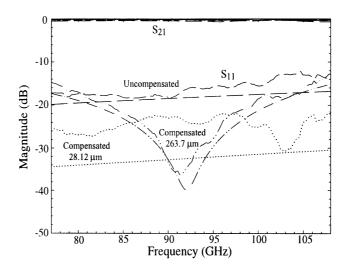

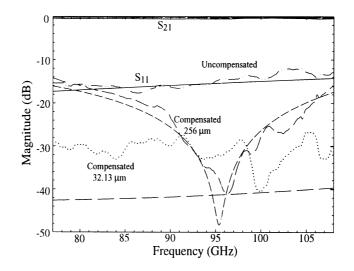

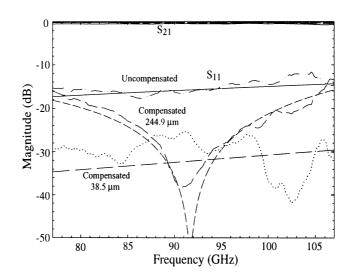

| 4.15 | S-parameters of measured RF wafer-to-wafer transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

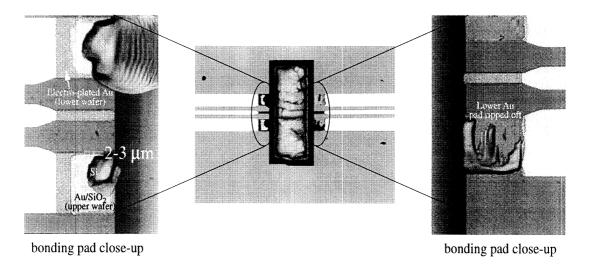

| 4.16 | Photograph of bonded sample after wafers pulled apart showing bonding and alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 96         |

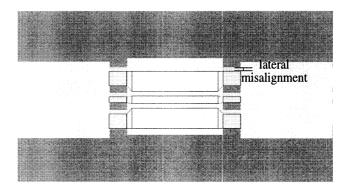

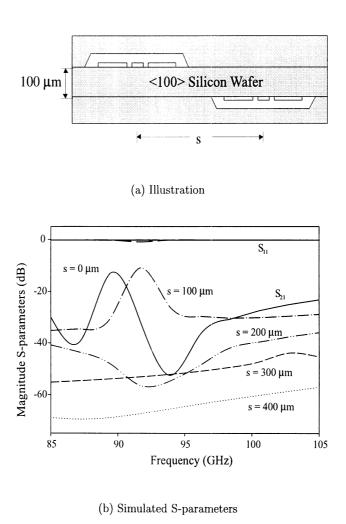

| 4.17 | Schematic of simulated lateral misalignment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97         |

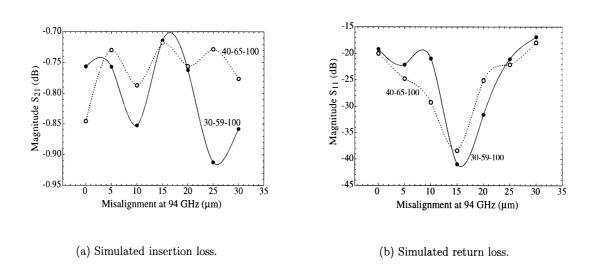

| 4.18 | Simulated scattering parameters as a function of misalignment at 94 GHz for Transitions 2 and 3 (a) Insertion loss (b) Return loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97         |

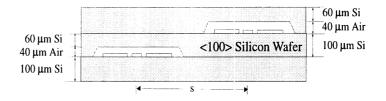

| 4.19 | Photos of 215 $\mu m$ diameter optic fibers threaded through two Si wafers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98         |

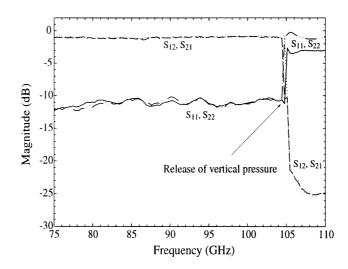

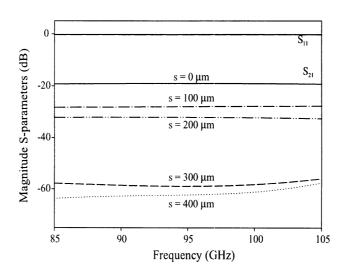

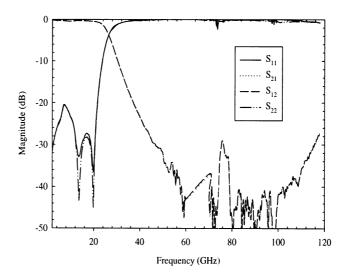

| 4.20 | S-parameter measurements of unbonded RF wafer-to-wafer transition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 99         |

| 4.21 | S-parameter simulations of RF wafer-to-wafer transition with 2 $\mu$ m vertical separation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99         |

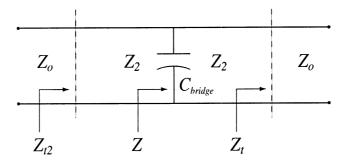

| 5.1  | Equivalent transmission line circuit for Wilkinson power divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103        |

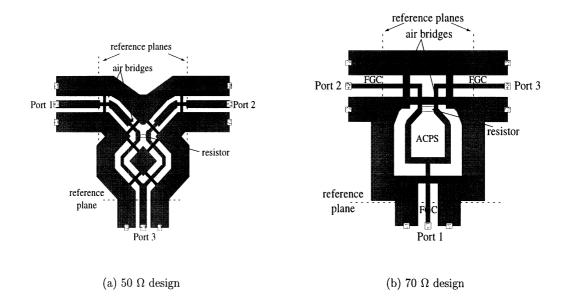

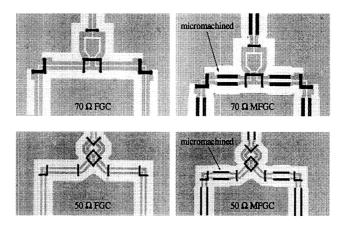

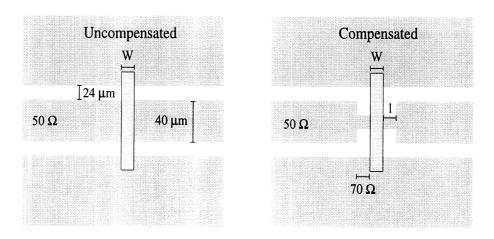

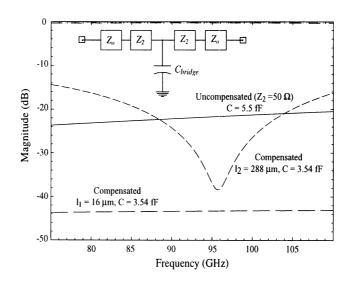

| 5.2  | Schematics of Wilkinson power dividers as simulated in IE3D [132]: a) 50 $\Omega$ b) 70 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104        |

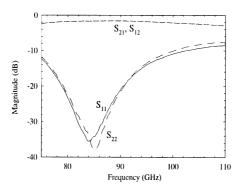

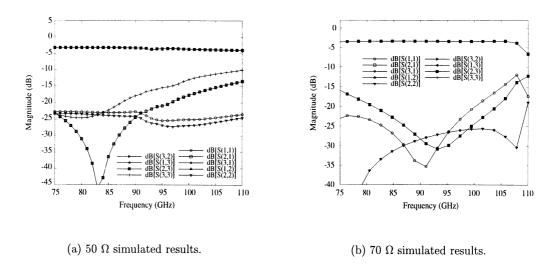

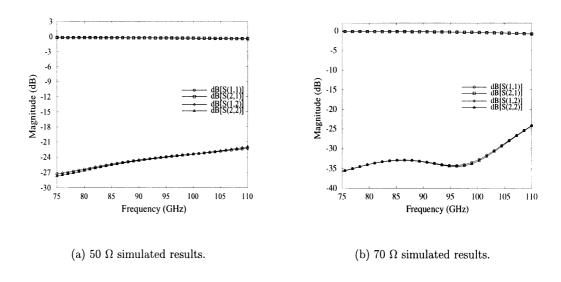

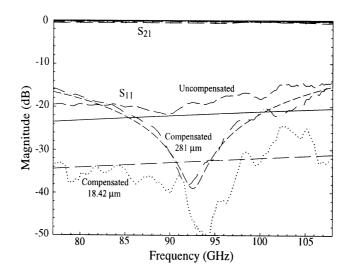

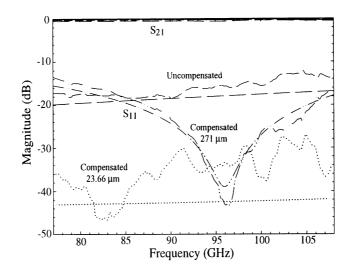

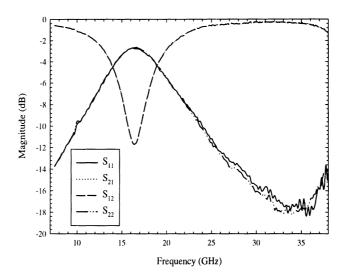

| 5.3  | S-parameters of Wilkinson power dividers as simulated in IE3D [132]: a) 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|      | $\Omega$ b) 70 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 104        |

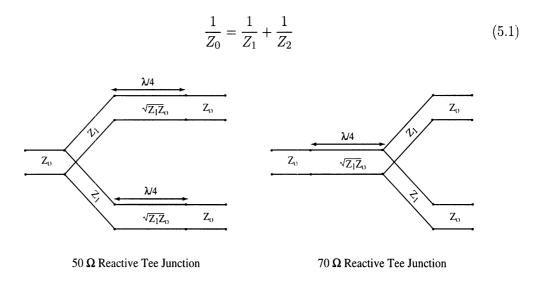

| 5.4  | Equivalent transmission line circuit for reactive tee junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105        |

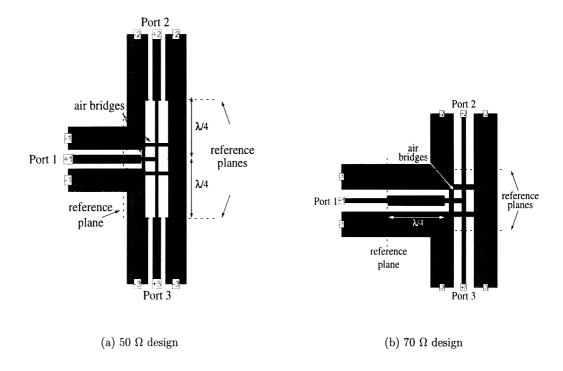

| 5.5  | Schematics of reactive tee junctions as simulated in IE3D [132]: a) 50 $\Omega$ b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|      | $70 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 106        |

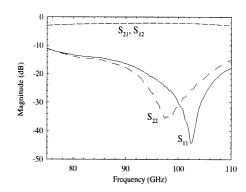

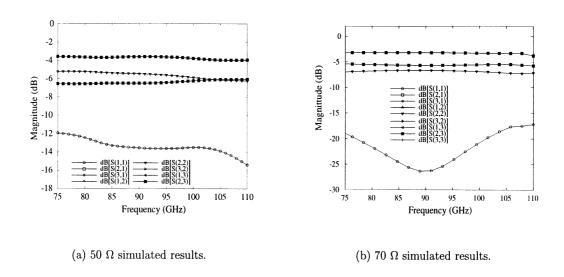

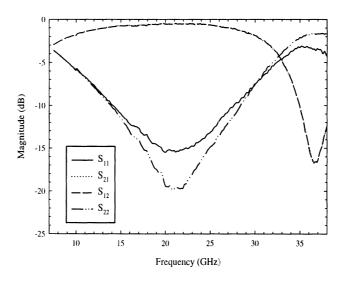

| 5.6  | S-parameters of reactive tee junctions as simulated in IE3D [132]: a) 50 $\Omega$ b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|      | $70 \Omega.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106        |

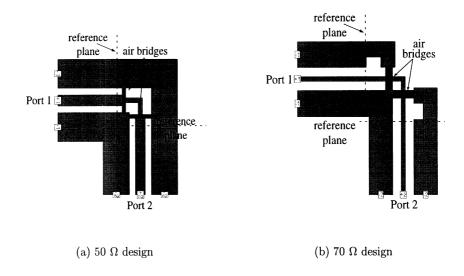

| 5.7  | Schematics of right angle bends as simulated in IE3D [132]: a) 50 $\Omega$ b) 70 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107        |

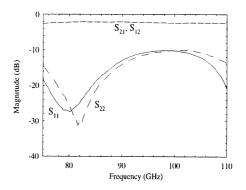

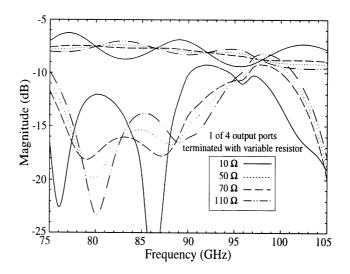

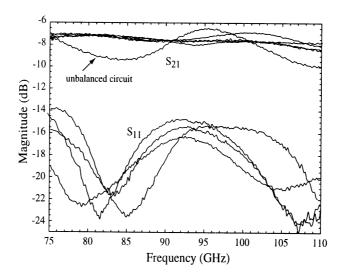

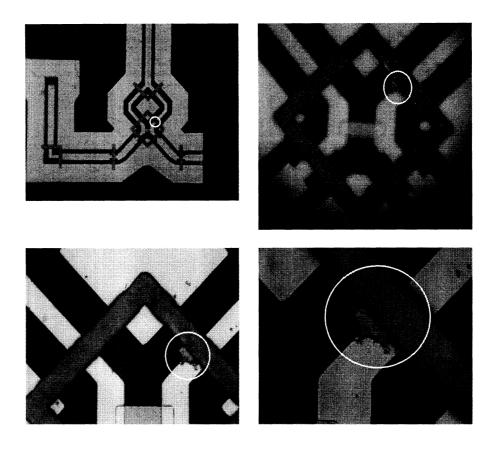

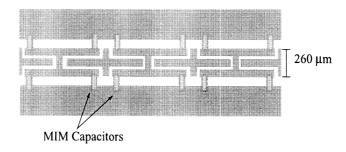

| 5.8  | S-parameters of right angle bends as simulated in IE3D [132]: a) 50 $\Omega$ b) 70 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .107       |