# Micromachined High-Q RF Filters and Resonators for Communication Filters

Annual Report and Final Report to ARO

Attention: Dr. Jim Harvey

ARO AASERT

Ву

Linda P.B. Katehi

The University of Michigan Ann Arbor, MI 48109-2122

July 1999

36963-1-T = RL-2511

Contract Number: DAAH04-96-1-0109

Contract Title: Micromachined High-Q RF Filters and Resonators for Communication

Systems

Final Reporting Period: June 1, 1998- May 31, 1999

#### Graduate Students Partially Funded by this Program:

Lee Harlee John Papapolymerou, Sergio Pacheco Katherine Herrick

Faculty: Prof. Linda P.B. Katehi

Comments: John Papapolymerou received his Ph.D in February 1999. He is now in University of Arizona as an Assistant Professor.

#### **Publications:**

- 1. Lee Harle, John Papapolymerou, Jack East, Linda P.B. Katehi, *The effect of slot positioning on the bandwidth of a micromachined resonator*, 28<sup>th</sup> European Microwave Conference Proceedings, Oct. 1998, vol. 2, pp. 664-668.

- 2. R. F. Drayton, S. Pacheco, J-G. Yook, and L. P.B. Katehi, *Micromachined Filters on Synthesized Substrates*, *IEEE MTT-S International Microwave Symposium Digest*, Baltimore, MD, Vol.3, pp. 1185-1188, 1998.

- 3. Linda P.B. Katehi, *Microtechnology in the Development of Three-Dimensional Circuits*, presented in Microwaves and RF '98, October 1998, London UK.

- 4. Linda P.B. Katehi and Katherine Herrick, *Si Micromachining for High-Frequency Circuits*, Invited paper, ESA Workshop on Millimeter-Wave Technology and Applications, ESPOO, Finland, May 27-28, 1998.

#### Technology Insertion:

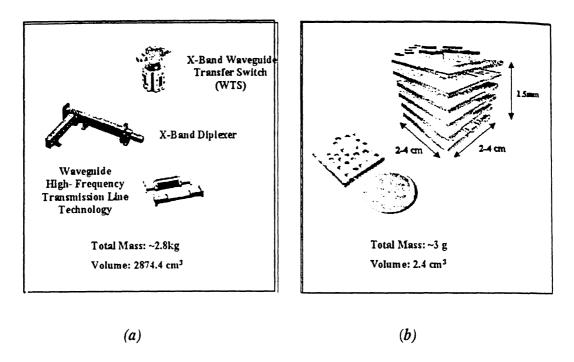

- 1. The concept of High-Q Filters developed under this contract has now been extended to develop multipole filters and diplexers for communication systems. Specifically this concept is further developed for JPL/CISM for the development of the first miniaturized RF Front End.

- 2. The same concept has been extended to the development of Evanescent Mode Filters. This activity is now funded by DARPA.

#### Patents:

This concept has been patented recently. US Patent: 5,821,836

#### Appendices:

1. Appendix A: John Papapolymerou, Ph.D. Dissertation

- 2. Appendix B: Lee Harle, John Papapolymerou, Jack East, Linda P.B. Katehi, *The effect of slot positioning on the bandwidth of a micromachined resonator*, 28<sup>th</sup> European Microwave Conference Proceedings, Oct. 1998, vol. 2, pp. 664-668.

- 3. Appendix C: R. F. Drayton, S. Pacheco, J-G. Yook, and L. P.B. Katehi, *Micromachined Filters on Synthesized Substrates*, *IEEE MTT-S International Microwave Symposium Digest*, Baltimore, MD, Vol.3, pp. 1185-1188, 1998.

- 4. Appendix D: Linda P.B. Katehi, *Microtechnology in the Development of Three-Dimensional Circuits*, presented in Microwaves and RF '98, October 1998, London UK.

- 5. Appendix E: Linda P.B. Katehi and Katherine Herrick, *Si Micromachining for High-Frequency Circuits*, Invited paper, ESA Workshop on Millimeter-Wave Technology and Applications, ESPOO, Finland, May 27-28, 1998.

#### Project Summary

Linda P.B. Katehi

Radiation Laboratory

Department of Electrical Engineering and Computer Science

The University of Michigan

Ann Arbor, MI 48109-2122

#### Summary

The use of millimeter-wave technology in military and commercial applications has drawn the attention of the microwave community for more than three decades due to its advantages over other bands of the electromagnetic spectrum, as well as the lack of frequencies for new services. Since the size of any microwave circuit or component is dictated by the frequency of operation, implementation of the millimeter-wave region (30-300 GHz) can result in very small systems. This is extremely important for airborne and space applications, where launch and deployment costs depend heavily on the volume of the system that is to be deployed. Furthemore, millimeter-waves allow for antennas with high gain and directivity that are essential for point-to-point communication systems (e.g. between a satellite and an earth base station) and radars. For space and airborne applications attenuation through the earth's atmosphere is a major consideration. In general, the attenuation of the microwave energy increases with frequency with the exceptions of a few minima that occur at 35 GHz, 94 GHz, 140 GHz, 220 GHz etc. These "windows" of minimum atmospheric absorption make millimeter-wave, systems ideal for such applications. In addition, millimeter-waves unlike infrared and optical wavelengths have the ability to permeate fog, dust and smoke. Commercial applications of millimeter-wave systems include short-haul line-of-sight transmission links for personal communication networks (PCN's) that operate at 38 GHz, wireless cable at 28 GHz, wireless radio local area networks (LAN's) and mobile broadband systems. In recent years, research reports have also focused on automotive radar sensors for anti-collision radars at 77 GHz, intelligent cruise control and road transport informatics. Aircraft landing systems and earth remote sensing are other areas where millimeter-waves have been employed.

The latter is of major significance due to the intense environmental studies currently under way and the changing conditions of our planet. Of course, military communication systems and radars as well as satellite communications were the first applications of millimeter-wave systems. Until the early 80's most of the millimeter-wave components and systems were built with waveguide technology (rectangular or cylindrical). Waveguides provide very low-loss, high quality factor circuits but are bulky and heavy thus imposing cost limitations on airborne and space systems. In addition, waveguide components are expensive to manufacture since they have to be precision machined one at a time, and at higher operating frequencies their fabrication complexity increases. The bandwidth of such systems is also limited by the operational bandwidth of the waveguides that are used. With the maturity of integrated circuit (IC) fabrication techniques and the increased need for high circuit

integration and compact designs, the microwave community has started focusing its improved reproducibility and reliability. Moreover, MMIC's can allow for broad-band operation if designed properly and easy integration of active devices such as diodes and transistors. As a result, entire communication and radar systems can now be fabricated on a single planar substrate or a multi-layered chip with vertical interconnects connecting the various layers. The operating frequency can also be increased, thus satisfying the high demand for new spectrum bands.

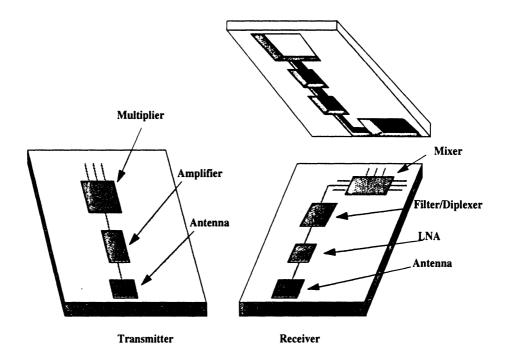

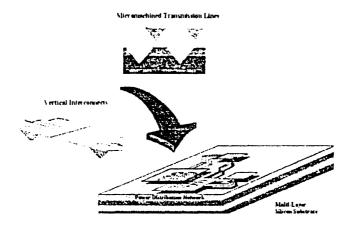

As system requirements for faster data transmission in lighter compact designs drive the technology area, higher frequency design solutions with large density layouts that include radiating elements, passive circuitry, oscillator sources and have light weight, small size and optimum performance, are required. Such a design can be seen in Fig. 1.1 of appendix A and represents a monolithic transmit/receive system that operates at higher frequencies (W-band) and constitutes the RF front end of any communication or radar system. The transmitter includes a frequency multiplier that translates a lower frequency signal into a much higher one, an amplifier that increases the output power of the multiplier and an antenna that radiates the incoming energy. At the receiver, the high frequency signal captured by the antenna is amplified by a low noise amplifier (LNA) and is then down converted to a much lower one by a sub-harmonic mixer. For isolating a particular frequency spectrum, narrow band filters and diplexers can be implemented either right after the antenna or at other stages of the receiver.

On-wafer packaging that reduces interaction between the different components and offers electrical and mechanical protection, as well as a means for heat dissipation, to both the transmitter and receiver can also be achieved. All of the passive and active components, including the package, can be fabricated on Silicon or GaAs substrate with standard integrated circuit fabrication techniques that would significantly lower the total cost. MMICs have the advantage of small size and weight, that further decrease the cost of airborne and space applications, low fabrication cost since they can be batch fabricated using standard IC techniques and MMIC's are designed and fabricated using planar circuit technology that usually implements two types of transmission lines: the microstrip line (Fig. 1.2(a)) and the coplanar waveguide (CPW). The air-dielectric interface that exists in both of these lines introduces several parasitic effects that are pronounced as the operating frequency increases. These effects include increased dielectric loss, substrate moding where the power can propagate inside the substrate in the form of unwanted modes, and dispersion. As a result, MMIC's operating at high frequencies (W band) can have some important limitations. These limitations are augmented by the non-availability of higher frequency solid-state oscillator sources that are difficult to fabricate. These sources are very important for heterodyne receiver applications where an incoming high frequency (RF) signal is down converted to a much lower frequency (IF) signal. The objective of this thesis is to find techniques that address these limitations encountered in planar, monolithically integrated passive and active circuits operating at higher frequencies (W band), with the goal of designing a monolithic One of the solutions to the restrictions imposed in passive MMIC's, makes use of the micromachining techniques. Micromachining is a technology widely used in the development of micro-electro-mechanical systems (MEMS), sensors and actuators and its implementation in the microwave field is relatively new. The first application in microwave circuits was that of membrane supported antennas for imaging arrays. Other developments on antennas reported since then include microstrip patches suspended on a dielectric membrane over air or sitting on a substrate with periodically spaced holes in order to increase the radiation efficiency. Regarding planar resonators and filters, micromachining was used to suspend microstrip and CPW resonators on membrane in order to increase the quality factor and achieve filter designs with very narrow bandwidth and very small loss.

With the trend to incorporate all microwave components on a single chip, as is the case of a monolithic transmit/receive system, there is an increased need to build high-Q resonators that can be monolithically integrated with the rest of the circuitry on the same substrate. High-Q resonators are the building blocks for narrow-band, low-loss filters that are used mainly in communication and radar systems. Traditionally, for microwave frequencies these resonators are made of rectangular and cylindrical metallic waveguides that offer very low loss and flexibility in tuning by inserting backshorts and screws. Waveguides, however, are heavy, large (especially at lower frequencies) and costly to manufacture since each component must be precision machined one at a time. In addition, waveguides do not allow for an easy integration with monolithic circuits and active devices.

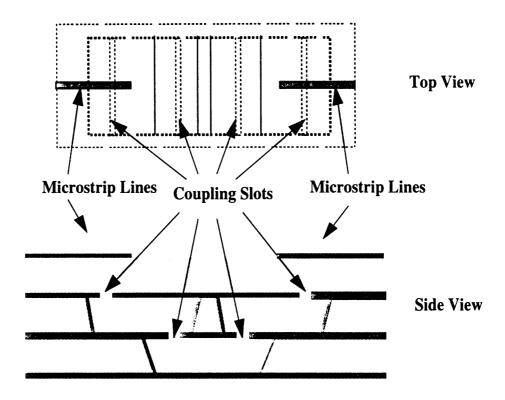

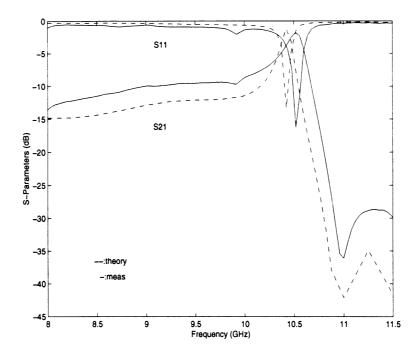

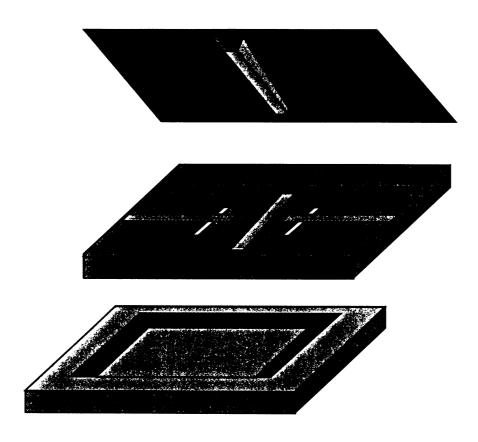

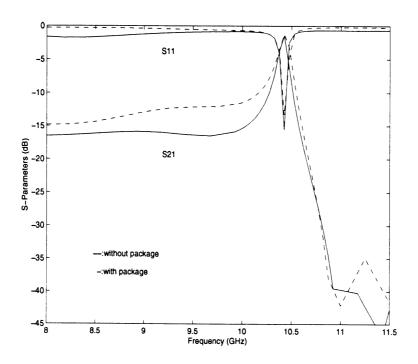

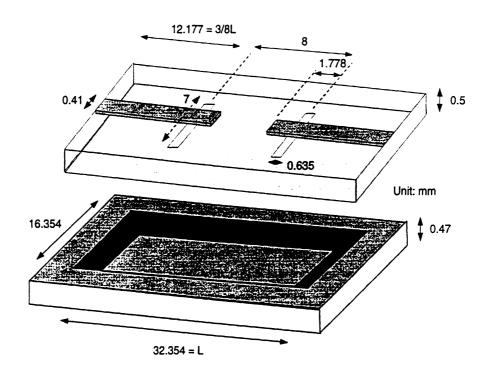

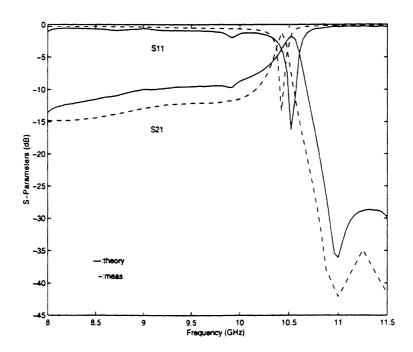

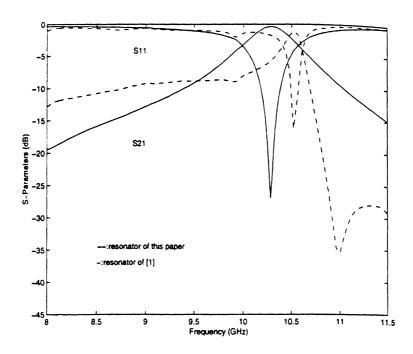

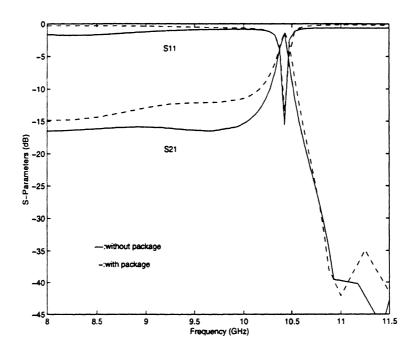

The implementation and maturity of micromachining techniques in the fabrication of microwave and millimeter-wave circuits allows us now to make miniature silicon or GaAs micromachined waveguides or cavities that can be used for the fabrication of high- Q bandpass filters and multiplexers. The quality factor that can be achieved with this technique is much higher than the quality factor of traditional planar microstrip or stripline resonators either printed on a dielectric material or suspended in air with the help of a dielectric membrane. The latter type of resonators can give filters with less than 1 dB insertion loss and bandwidths exceeding 10%. This chapter discusses the development of a silicon micromachined high-Q X-band resonator that consists of a cavity, input and output microstrip lines and coupling slots. Experimental results of the performance of the resonator are shown and compared with simulations performed by Jui-Ching Cheng. In addition, the quality factor of the resonator is evaluated based on s-parameter measurements. The effects of different ambient temperatures and the positioning of the slots relative to the center of cavity on the response of the resonator are also presented and analyzed, as well as some on-wafer packaging considerations. An extensive study of these resonators is presented in Appendices A-E.

# Appendix A:

John Papapolymerou, Ph.D. Dissertation

### MMIC PASSIVE AND ACTIVE STRUCTURES

by

#### Ioannis Papapolymerou

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1999

#### Doctoral Committee:

Professor Linda P.B. Katehi, Chair Associate Professor Kamal Sarabandi Professor Duncan G. Steel Research Scientist Jack R. East © <u>Ioannis Papapolymerou</u> 1999 All Rights Reserved To my beloved mother,

Areti-Eleni Spiliopoulou

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Linda Katehi, for providing me with the opportunity to conduct this Ph.D. research. Her guidance, support, mentoring, encouragement, professionalism and enthusiasm for research made this difficult journey much easier and will always provide a source of inspiration and a guiding light for any future ventures. I am also grateful for her continuous financial support that allowed me to complete my work and attend several conferences. Furthermore, I am grateful to Professor Kamal Sarabandi, Professor Duncan Steel, and Dr. Jack East for serving on my dissertation committee along with Professor Katehi, and for their advice and counsel during this difficult process. I would also like to thank Professor Gabriel Rebeiz for the very useful and enlightening conversations on numerous scientific issues and Professor George Haddad for his moral support all my years at the University of Michigan.

I am deeply indebted to Dr. Imran Mehdi and Lorene Samoska of the Jet Propulsion Laboratory for the generous donations of numerous masks necessary for my projects, as well as for the measurements of the D-band doublers and the long conversations regarding active structure problems.

I would like to express my gratitude to Dr. James Harvey and the Army Reseach Office for sponsoring the major part of my work. Other sponsors include the Office of Naval Research, JPL and Texas Instruments.

During my first years at the Radiation Lab I benefited greatly from the guidance, support and friendship of several "senior" students: Prof. George Eleftheriades, Dr. Walid Ali-Ahmad, Dr. Apostolos Samelis, Prof. Thomas Weller, Dr. Chen-yu Chi, Prof. Rhonda Franklin-Drayton, Dr. Hristos Anastassiou, Dr. Gildas Gauthier, Prof. Sanjay Raman, Prof. Manos Tentzeris, Dr. Jui-Ching Cheng, Dr. Jong-Gwan Yook and Dr. Steven Robertson. Their impact on my life and career will always be remembered. Special thanks go to my officemate, Dr. Rashaunda Henderson, for her friendship all those years and the fruitful conversations on various issues of life and work.

It has also been a privilege and a pleasure to work with so many talented students of Profs. Katehi and Rebeiz: Kavita Goverdhanam, Katherine Herrick, Lee Harle, James Becker, John Shumpert, Sergio Pacheco, Kyoung Yang, Kevin Lu, Costas Sarris, Rob Robertson, Eray Yasan, Bill Chappell, Thomas Schwarz, Saqib Jalil, N. Scott Barker, Tom Ellis, Joe Hayden and Jeremy Muldavin. I have enjoyed their company and learned much from them. I wish them success in their future endeavors. Especially, I would like to thank Leo DiDomenico and Andy Brown for their help and support during the last few weeks of my work.

In addition, I would like to thank all those people in the Solid-State Electronics Lab that provided their technical expertise on several issues and with whom I shared endless fabrication time in the clean room: Dr. Bishnu Gogoi, Prof. Navid Yazdi, Dr. Doug Craig, Egor Alekseev, Don Sawdai, Erik Berg, Cheng-Hui Lin, Herte Gebretsadik, Dimitris Papageorgiou, Tim Brock, Christine Tom, Terre Briggs and James Kempf.

Needless to say, that I would not have been able to finish this long and demanding journey without the administrative and moral support of the Radiation Laboratory staff, past and present: Janice Rosan, Carol Truszkowski, Sharon Ryder, Michelle Shepherd,

Catherine Brown, and Patti Wolfe.

To Peter, Mary and Stacy Karamanos I would like to express my appreciation for their love and support.

To my mother, Areti-Eleni Spiliopoulou, I cannot find the words to express my deepest gratitude and love for devoting her entire life in my up-bringing and well being, teaching me wrong from right, supporting my career plans and encouraging me in difficult times.

Finally, I would like to thank my wife, Jackie Karamanos, who has been a constant source of strength, courage, love and inspiration for all my years as a graduate student, and without whom I would not have fulfilled my dreams.

## TABLE OF CONTENTS

| DEDICATION  | <b>V</b>                                                        |

|-------------|-----------------------------------------------------------------|

| ACKNOWLE    | DGEMENTS iii                                                    |

| LIST OF TAE | BLES vii                                                        |

| LIST OF FIG | URES ix                                                         |

| LIST OF APP | PENDICES xii                                                    |

| CHAPTERS    |                                                                 |

| 1 INTRO     | DDUCTION                                                        |

| 1.1         | Motivation                                                      |

| 1.2         | Silicon Micromachining                                          |

| 1.3         | Schottky Barrier Diode                                          |

| 1.4         | Measurement Techniques                                          |

| 1.5         | Simulation Tools                                                |

| 1.6         | Dissertation overview                                           |

| 2 MICR      | OMACHINED PATCH ANTENNAS                                        |

| 2.1         | Introduction                                                    |

| 2.2         | Reduction of the Effective Dielectric Constant (Technique I) 26 |

|             | 2.2.1 Review of Technique                                       |

|             | 2.2.2 Theory of Radiation Efficiency                            |

|             | 2.2.3 Ku-Band Micromachined Patch Antenna                       |

|             | 2.2.4 Efficiency Measurements                                   |

| 2.3         | Elimination of $TM_0$ Surface Wave (Technique II)               |

|             | 2.3.1 Theoretical Analysis                                      |

|             | 2.3.2 Results                                                   |

| 2.4         | Conclusions                                                     |

| 3 MICR      | OMACHINED RESONATORS                                            |

| 3.1         | Introduction                                                    |

| 3.2         | X-Band Micromachined Resonator                                  |

|             | 3.2.1 Design and Fabrication                                    |

|             | 3.2.2 Theoretical and Measured Results                          |

|        | 3.3   | Thermal Testing                                      | 57  |

|--------|-------|------------------------------------------------------|-----|

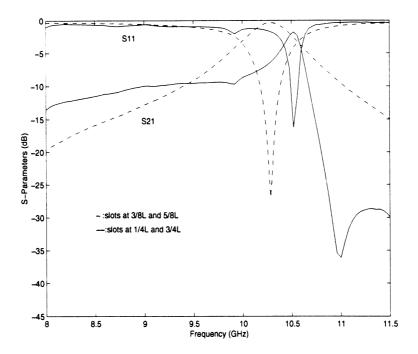

|        | 3.4   | Effects of Slot Positioning on Resonator Performance | 60  |

|        | 3.5   | Conclusions                                          | 62  |

| 4      | GaAs  | MONOLITHIC MULTIPLIERS                               | 65  |

|        | 4.1   | Introduction                                         | 65  |

|        | 4.2   | Study of FGC lines                                   | 67  |

|        |       | 4.2.1 Fabrication                                    | 69  |

|        |       | 4.2.2 Results and Discussion                         | 70  |

|        | 4.3   | W-Band Doublers                                      | 77  |

|        |       | 4.3.1 Analysis and Design                            | 77  |

|        |       | 4.3.2 Measurement System                             | 82  |

|        |       | 4.3.3 Results and Discussion                         | 88  |

|        |       | 4.3.4 A Four Diode Design                            | 99  |

|        |       | 4.3.5 Improved Designs                               | .06 |

|        | 4.4   | Conclusions                                          | 11  |

| 5      | W-BA  | ND MONOLITHIC MIXER                                  | .14 |

|        | 5.1   |                                                      | 14  |

|        | 5.2   |                                                      | 15  |

|        | 5.3   | ·                                                    | 29  |

|        | 5.4   |                                                      | .33 |

| 6      | CONC  | CLUSIONS AND FUTURE WORK                             | .36 |

|        | 6.1   |                                                      | 36  |

|        | 6.2   |                                                      | 39  |

|        |       |                                                      | 39  |

|        |       |                                                      | 39  |

|        |       | ě ·                                                  | 41  |

|        |       |                                                      | 42  |

|        |       |                                                      | .43 |

| APPE   | NDICE | SS                                                   | .45 |

| RIBLIC | OGR A | <b>PHV</b> 1                                         | 67  |

## LIST OF TABLES

| Table |                                                                            |             |

|-------|----------------------------------------------------------------------------|-------------|

| 1.1   | Etch rates of different chemicals for $SiO_2$ and $Si_3N_4$                | 8           |

| 2.1   | Dimensions of the fabricated scaled model and regular antennas             | 33          |

| 2.2   | Input impedance characteristics of the regular and scaled model antennas . | 34          |

| 2.3   | De-embedded efficiency for the scaled model and regular patch antennas at  |             |

|       | resonance                                                                  | 39          |

| 2.4   | Efficiency results and dimensions for two scaled model antennas on duroid  |             |

|       | substrate with $\epsilon_{\tau} = 10.8$                                    | 40          |

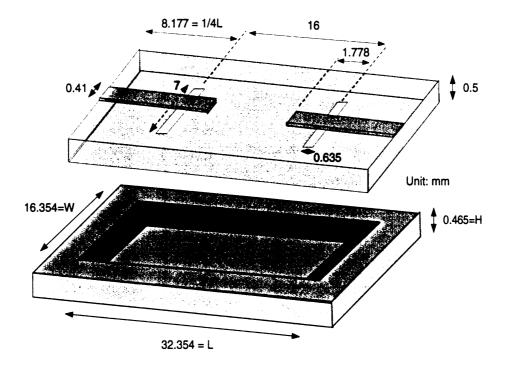

| 2.5   | Dimensions for the cored and conventional patch that were used in the FDTD |             |

|       | simulations                                                                | 44          |

| 3.1   | Comparison of measured Q for several resonators at X-band                  | 57          |

| 4.1   | Geometrical characteristics for the fabricated lines                       | 74          |

| 4.2   | Geometrical characteristics for the Q=2 multiplier                         | 81          |

| 4.3   | Geometrical characteristics for the Q=3 multiplier                         | 81          |

| 4.4   | Measured DC characteristics for the W-band fabricated diodes               | 91          |

| 4.5   | Geometrical characteristics for the Q=2 four diode doubler                 | 102         |

| 4.6   | Measured DC characteristics per diode for the four diode doubler design    | 102         |

| 4.7   | Geometrical characteristics for the improved $Q=2$ multiplier              | <b>10</b> 8 |

| 5.1   | Measured DC characteristics for the mixer diodes                           | 121         |

| 5.2   | Measured characteristics of the shunt stubs used in the mixer design       | 123         |

| 5.3   | Calculated values for the equivalent circuit model of Fig. 5.6(b)          | 128         |

| A.1   | Design parameters for the antennas on Silicon substrate                    | 151         |

| C.1   | PECVD $Si_xN_y$ deposition                                                 | 160         |

### LIST OF FIGURES

| Figure      |                                                                                                                                                                                |                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.1         | Monolithic transmit/receive module for communication and radar systems.                                                                                                        | 4               |

| 1.2         | Planar transmission lines: (a) microstrip and (b) coplanar waveguide (CPW).                                                                                                    | 5               |

| 1.3 $1.4$   | Anisotropic etching profile and geometry for the $\prec 100 \succ$ oriented silicon wafer. Pyramidal pits of a $\prec 100 \succ$ silicon wafer for: a) a rectangular etch mask | 7               |

| 1.4         | pattern and b) a random etch mask pattern and long etching time                                                                                                                | 8               |

| 1.5         | Equivalent circuit for the Schottky-barrier diode                                                                                                                              | 11              |

| 1.6         | I-V characteristic of a Schottky diode on a semi-log plot                                                                                                                      | 12              |

| 1.7         | a) Disk type diode for MMIC applications and b) cross section of diode                                                                                                         | 12              |

| 1.1         | showing different components of the series resistance (from [14])                                                                                                              | 14              |

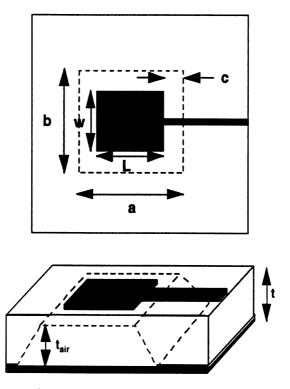

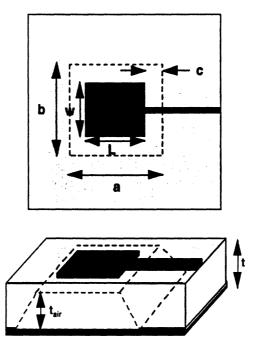

| 2.1         | Geometry of the micromachined patch antenna                                                                                                                                    | 27              |

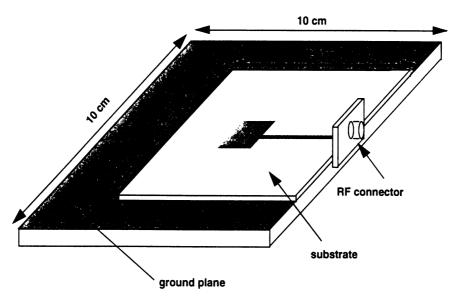

| 2.2         | Text fixture with micromachined antenna mounted                                                                                                                                | 32              |

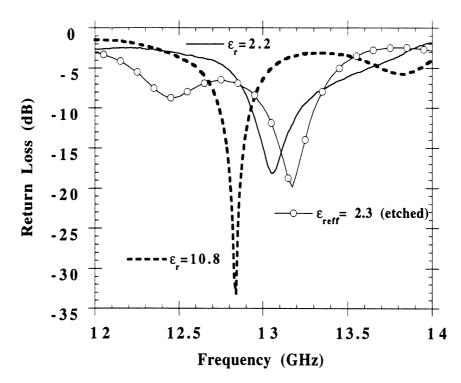

| 2.3         | Measured return loss for the scaled model patch antenna $\epsilon_{reff}$ =2.3 (etched)                                                                                        | -               |

| 2.0         | and regular patch antennas $\epsilon_r = 2.2$ and $\epsilon_r = 10.8$                                                                                                          | 33              |

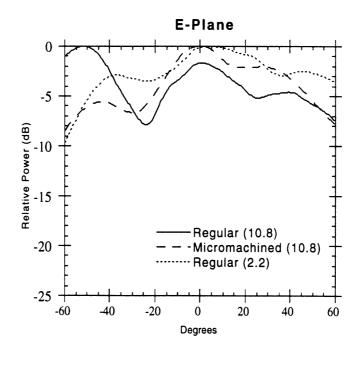

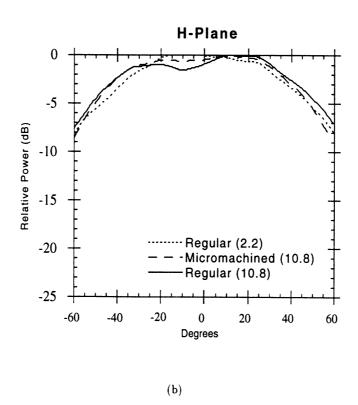

| 2.4         | (a) E-plane and (b) II-plane radiation patterns for the three antennas under                                                                                                   |                 |

|             | test                                                                                                                                                                           | 35              |

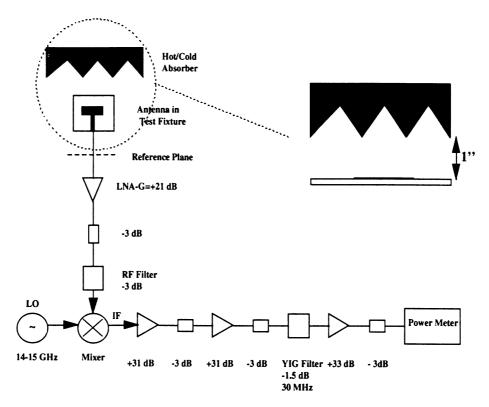

| 2.5         | System diagram of the efficiency measurement setup                                                                                                                             | 36              |

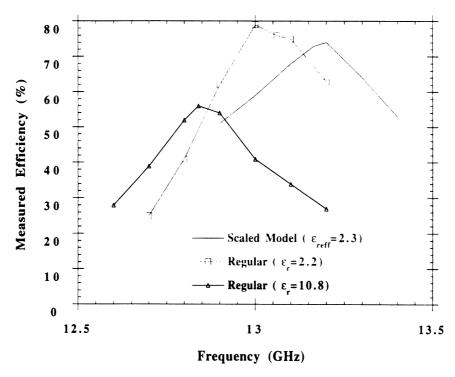

| 2.6         | Measured efficiency for the scaled model and regular patch antenna designs.                                                                                                    | 37              |

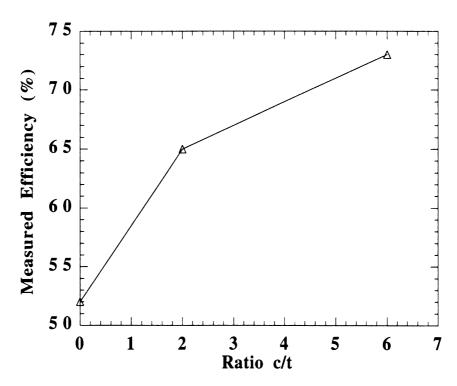

| 2.7         | Measured efficiency versus the ratio of the distance c over the substrate thick-                                                                                               |                 |

|             | ness t                                                                                                                                                                         | <b>3</b> 8      |

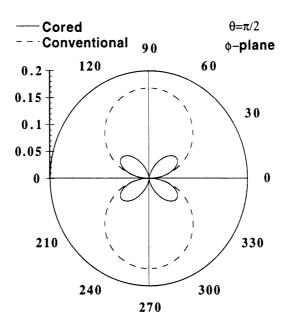

| 2.8         | Micromachined antenna for the elimination of $TM_0$ mode                                                                                                                       | 41              |

| 2.9         | Surface wave field pattern for the regular antenna and the micromachined                                                                                                       |                 |

|             | antenna                                                                                                                                                                        | 43              |

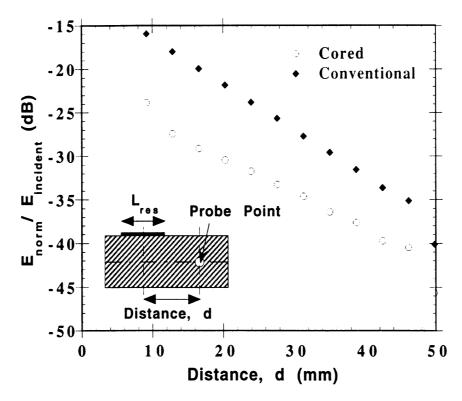

| 2.10        | Normalized electric field inside the dielectric versus distance from the center                                                                                                |                 |

|             | of the antenna for the micromachined (cored) patch and regular patch                                                                                                           | 45              |

| 3.1         | The X-Band micromachined resonator                                                                                                                                             | 49              |

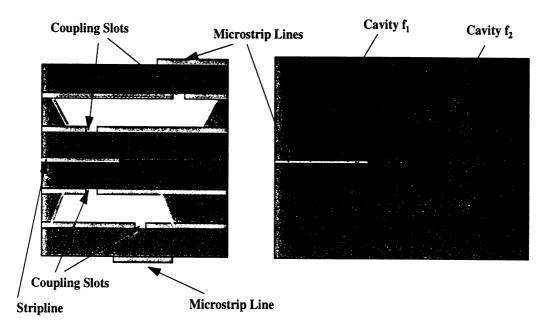

| 3.2         | The structure of the proposed micromachined bandpass filters                                                                                                                   | 50              |

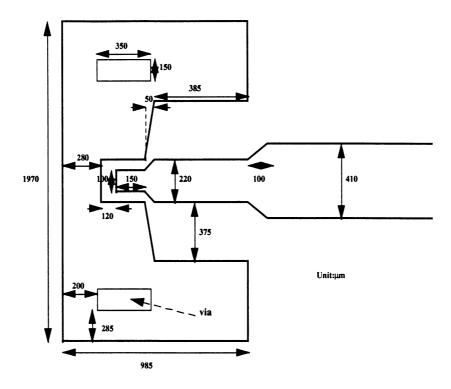

| 3.3         | CPW-to-microstrip transition for $500\mu\mathrm{m}$ thick silicon substrate                                                                                                    | 51              |

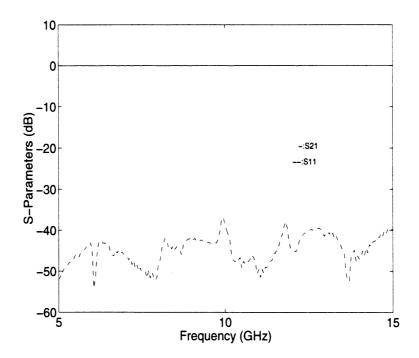

| 3.4         | Measured results for a 50 $\Omega$ microstrip line that implements the transition of Fig. 3.3                                                                                  | 52              |

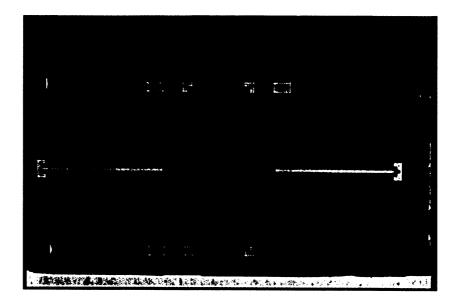

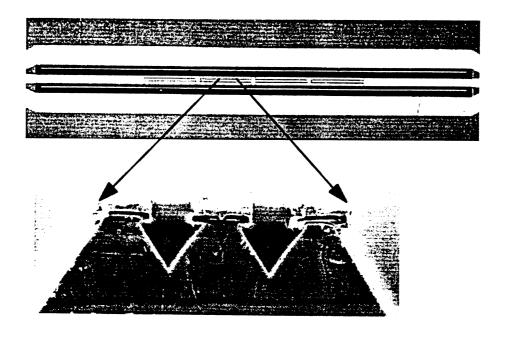

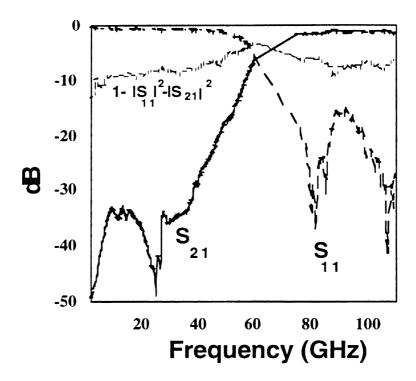

| 3.5         | Fabricated X-band resonator on two 500 $\mu$ m silicon wafers                                                                                                                  | $\frac{52}{53}$ |

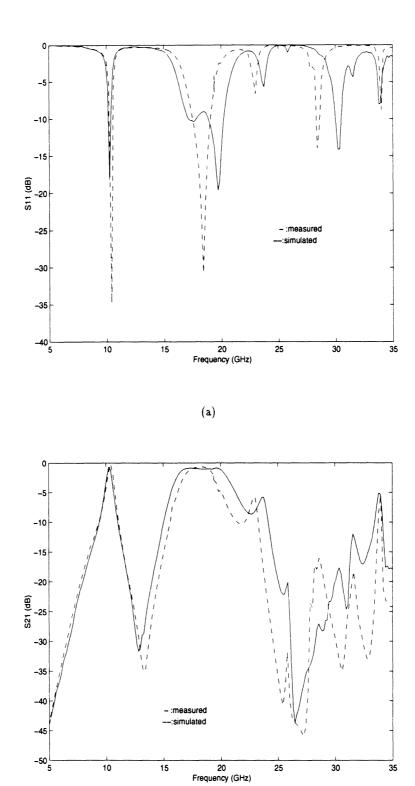

| 3.6         | Simulated and measured results for the resonator of Fig. 3.1: (a) return loss                                                                                                  | აა              |

| <b>J</b> .0 | and (b) insertion loss                                                                                                                                                         | 54              |

|             | (a) modernous room                                                                                                                                                             | 01              |

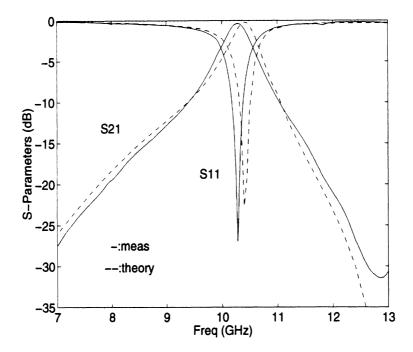

| 3.7   | Measured and simulated S-parameters for the resonator of Fig. 3.1 around resonance                                                                                                                                         | 55 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

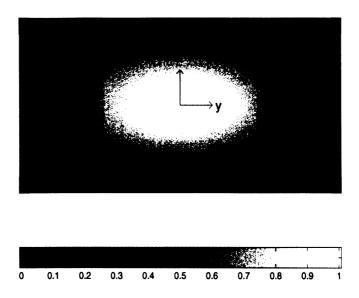

| 3.8   | Computed z-component of the electric field density on the bottom of the cavity (from Jui-Ching Cheng [1])                                                                                                                  | 56 |

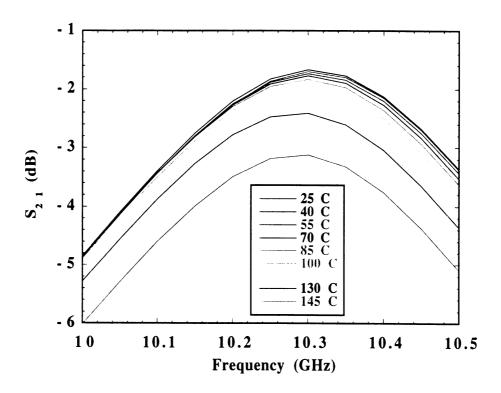

| 3.9   | Measured insertion loss of the micromachined resonator under different temperatures                                                                                                                                        | 58 |

| 3.10  | Measured and simulated results for the resonator with the slots positioned at 1/8L and 3/8L                                                                                                                                | 6  |

| 3.11  | Measured results for the two resonators with different slot positions                                                                                                                                                      | 62 |

| 3.12  | Micromachined resonator with on-wafer packaging                                                                                                                                                                            | 63 |

| 3.13  | Simulation results fot the packaged and non-packaged resonator                                                                                                                                                             | 6  |

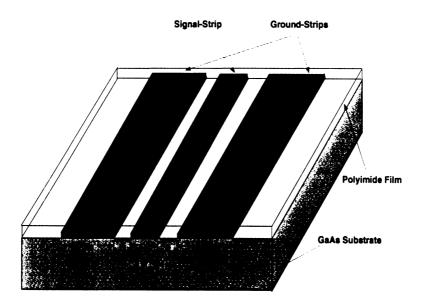

| 4.1   | FGC lines on GaAs with a polyimide overlay                                                                                                                                                                                 | 69 |

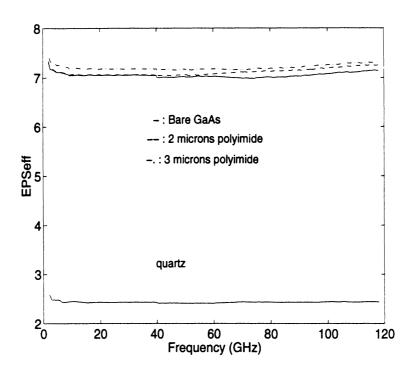

| 4.2   | Effective dielectric constant vs. frequency for the various FGC lines                                                                                                                                                      | 72 |

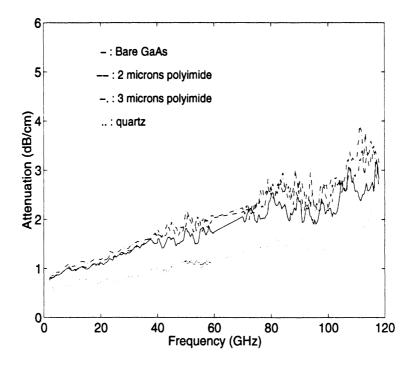

| 4.3   | Attenuation per physical length vs. frequency for the various FGC lines                                                                                                                                                    | 72 |

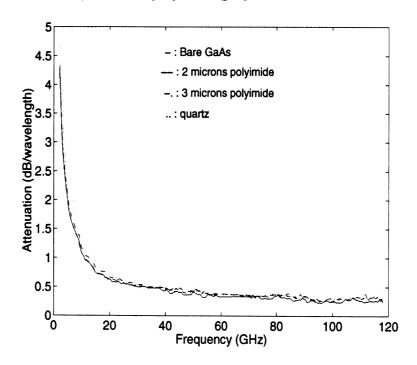

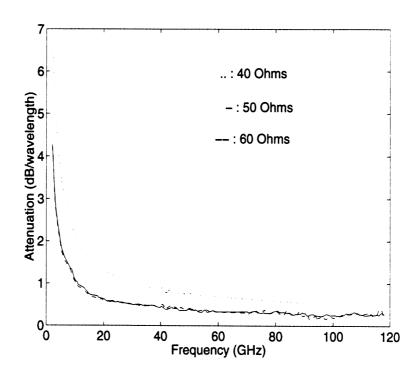

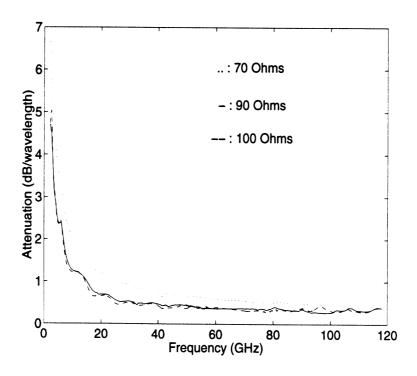

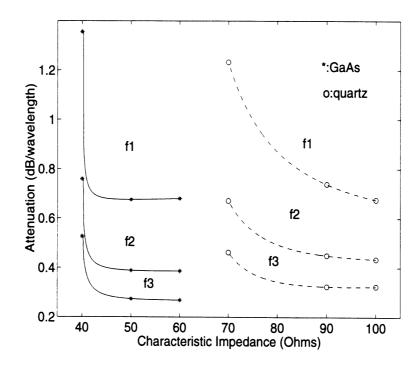

| 4.4   | Attenuation per guided wavelength vs. frequency for the various FGC lines.                                                                                                                                                 | 7: |

| 4.5   | Attenuation per guided wavelength for lines on GaAs with different $Z_0$                                                                                                                                                   | 75 |

| 4.6   | Attenuation per guided wavelength for lines on quartz with different $Z_0$                                                                                                                                                 | 75 |

| 4.7   | Attenuation per guided wavelength vs. characteristic impedance $Z_0$ for lines on GaAs and quartz at three different frequencies: $f_1$ =19.1 GHz, $f_2$ =50 GHz                                                           |    |

|       | and $f_3$ =94 GHz                                                                                                                                                                                                          | 70 |

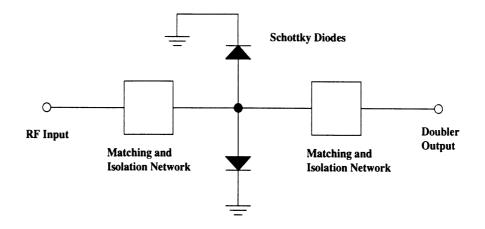

| 4.8   | Block diagram of the doubler configuration (from F. Brauchler [2])                                                                                                                                                         | 7  |

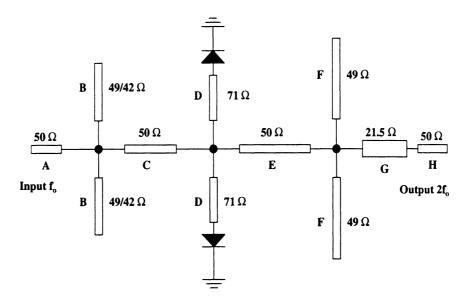

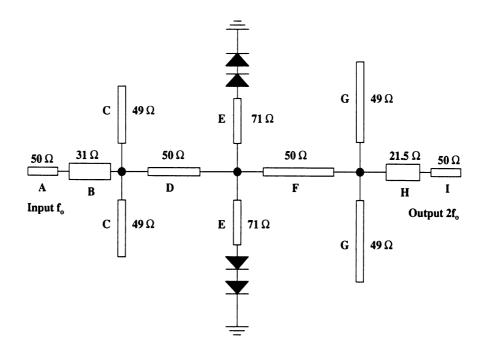

| 4.9   | Multiplier configuration with passive circuits                                                                                                                                                                             | 80 |

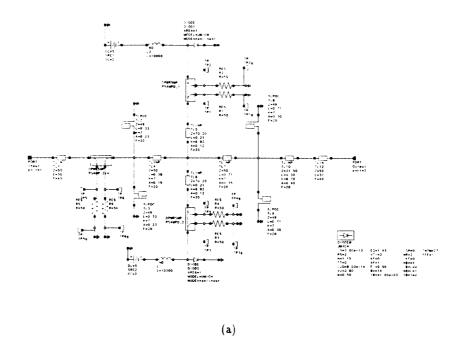

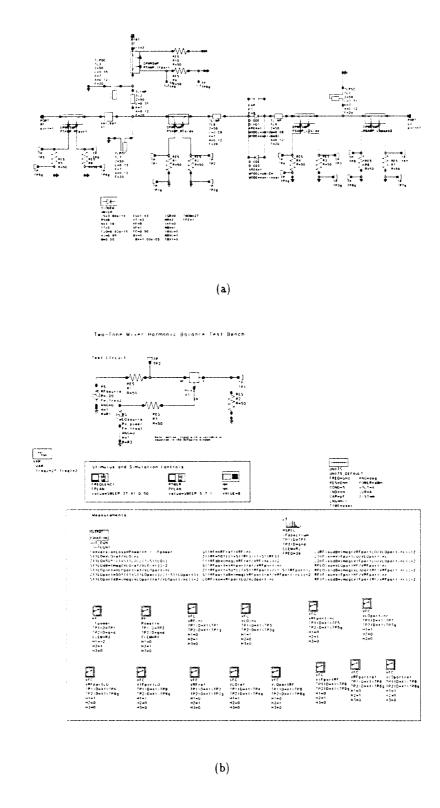

| 4.10  | Libra simulation for the W-band multipliers: (a) circuit schematic and (b) harmonic balance analysis test bench.                                                                                                           | 83 |

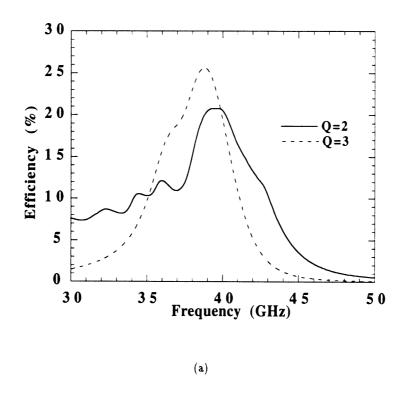

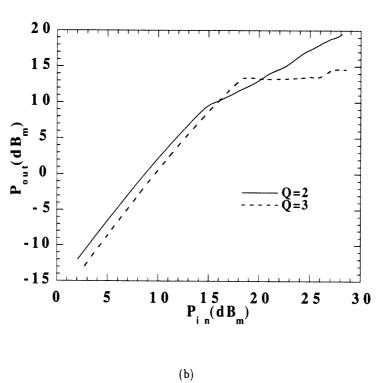

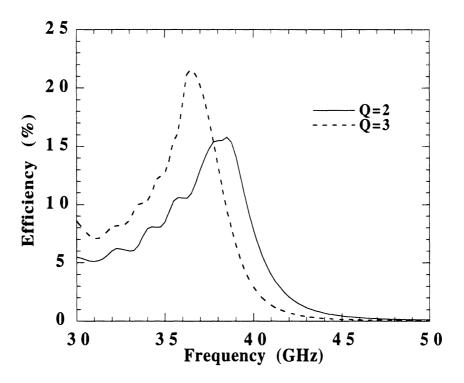

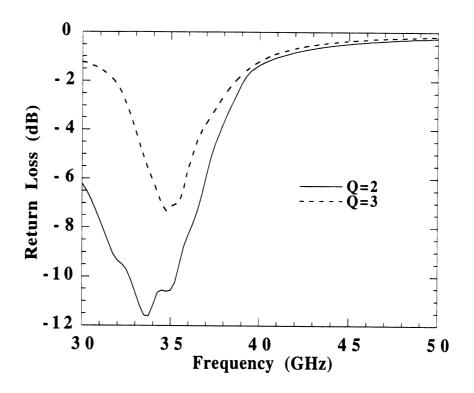

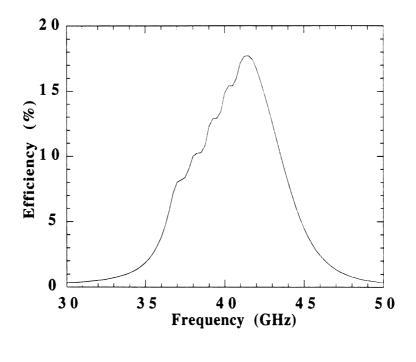

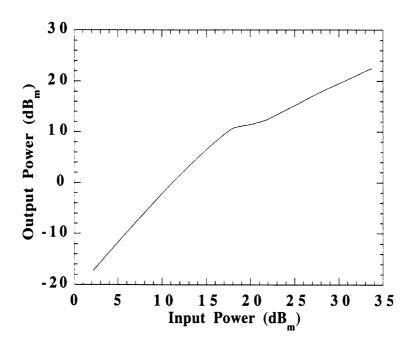

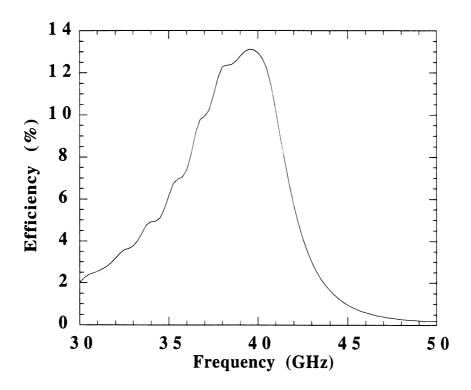

| 4.11  | Simulation results for the W-band multipliers: (a) efficiency vs. input frequency with an input power of 20 and 17 dBm for Q=2 and 3, respectively and (b) output power vs. input power at f=39.7 and 38.7 GHz for Q=2 and |    |

|       | 3, respectively                                                                                                                                                                                                            | 8  |

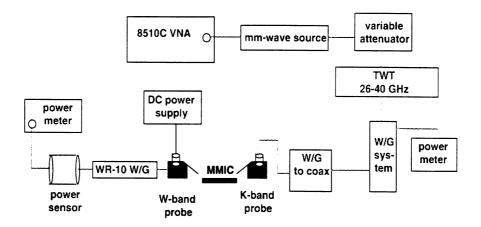

| 4.12  | Block diagram of the measurement system used to evaluate the performance                                                                                                                                                   |    |

|       | of W-band doublers                                                                                                                                                                                                         | 8  |

|       | Photograph of the actual system that was used for the multiplier measurements.                                                                                                                                             | 80 |

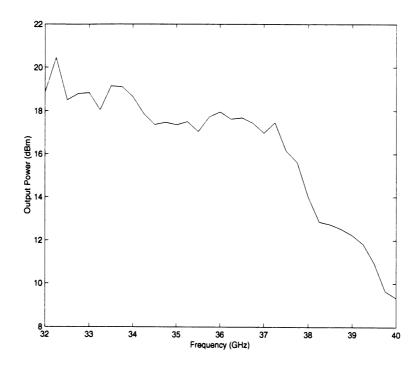

| 4.14  | Output power vs. frequency of the TWT measured at the flange of the                                                                                                                                                        |    |

| 4 1 5 | waveguide system for a fixed position of the attenuator                                                                                                                                                                    | 8  |

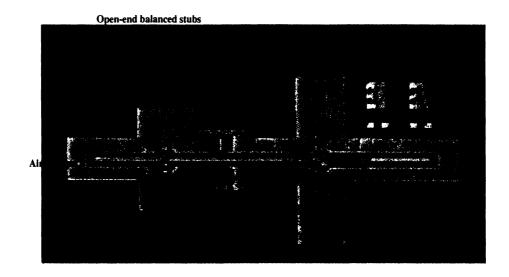

|       | Fabricated Q=3 W-band doubler                                                                                                                                                                                              | 89 |

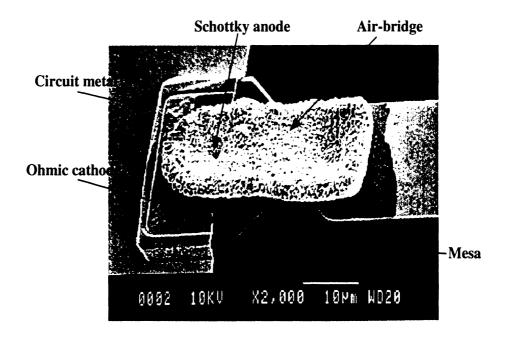

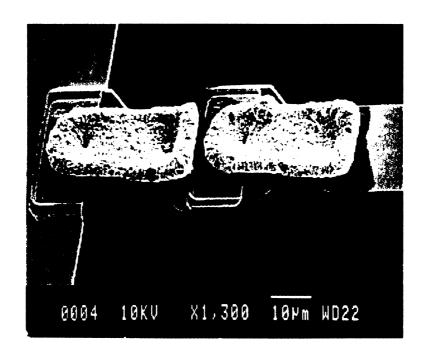

|       | SEM photo of fabricated Schottky diode.                                                                                                                                                                                    | 90 |

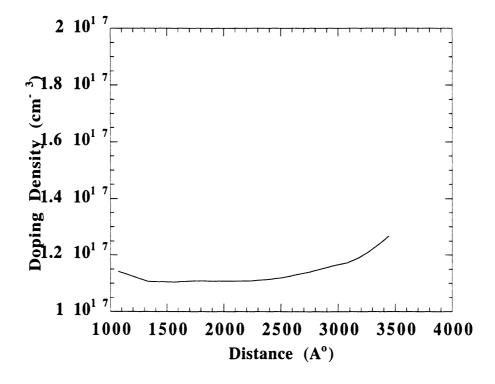

|       | Doping profile for the wafer used to fabricate the W-band doublers                                                                                                                                                         | 9  |

|       | Total capacitance vs. bias voltage for the Q=2 and Q=3 diodes                                                                                                                                                              | 9  |

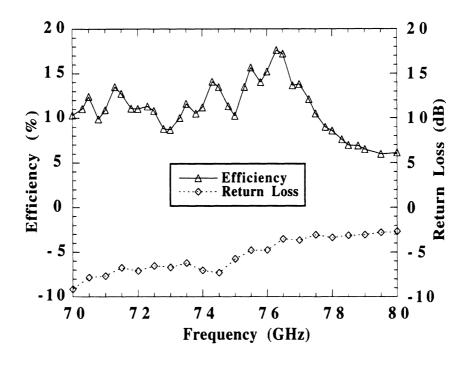

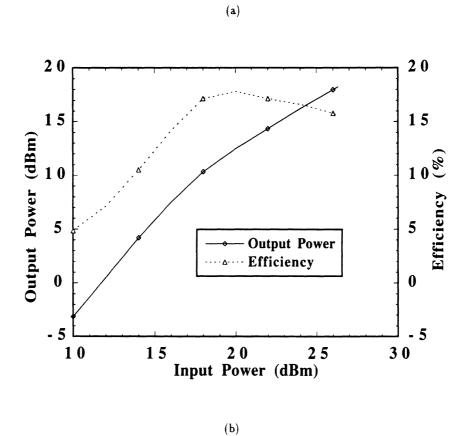

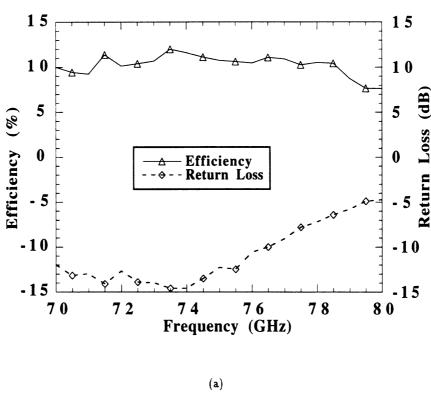

| 4.19  | Measured results for the Q=2 doubler: (a) efficiency and return loss vs. frequency for an input power of 20 dBm and (b) output power and efficiency                                                                        | _  |

|       | vs. input power at 76.3 GHz.                                                                                                                                                                                               | 9  |

| 4.20  | Simulated results for the Q=2 and Q=3 doublers with measured diode DC                                                                                                                                                      | ^  |

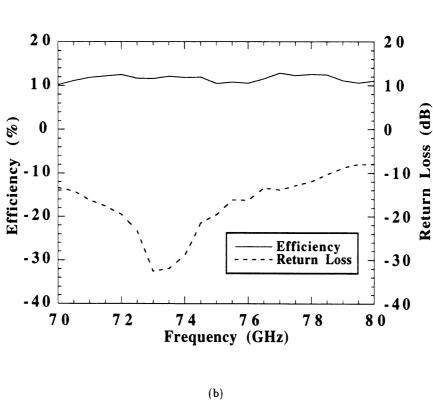

| 4.01  | parameters and input power of 20 and 17 dBm, respectively                                                                                                                                                                  | 9  |

| 4.21  | Simulated return loss for the Q=2 and Q=3 doublers with measured diode DC parameters and input power of 20 and 17 dBm, respectively                                                                                        | 9  |

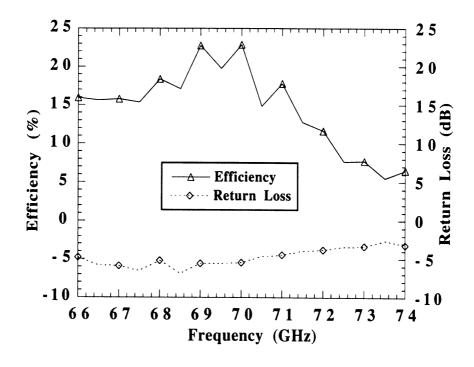

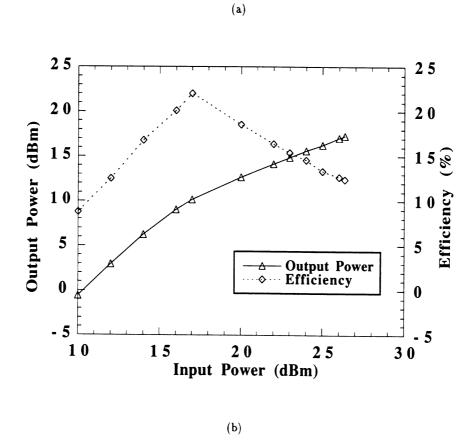

|       | DO PARAMOTOR AND MICHOLOGOUS OF AN ARCHIT ADMIT LESPECTIVELY.                                                                                                                                                              | 0  |

| 4.22 | Measured results for the Q=3 doubler: (a) efficiency and return loss vs. frequency for an input power of 17 dBm and (b) output power and efficiency vs. input power at 70 GIIz | 96    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.23 | Theoretical analysis for the diode bandwidth: a) equivalent circuit model                                                                                                      |       |

|      | and b) results based on equation 4.6                                                                                                                                           | 98    |

| 4.24 | Multiplier configuration with passive circuits and four diodes                                                                                                                 | 100   |

| 4.25 | Simulated results for the four diode doubler: a) efficiency vs. input frequency for an input power of 20 dBm and b) output power vs. input power at 41.25                      |       |

|      | GIIz.                                                                                                                                                                          | 101   |

| 4.26 | Photograph of the fabricated four diode doubler                                                                                                                                | 103   |

| 4.27 | SEM photo of two diodes in series                                                                                                                                              | 103   |

| 4.28 | Efficiency and return loss vs. output frequency of the four diode doubler for an input power of: a) 20 dBm and b) 23 dBm                                                       | 105   |

| 4.29 | Output power and efficiency vs. input power at 74 GHz for the four diode doubler                                                                                               | 107   |

| 4.30 | Simulation of four diode doubler including the measured diode characteristics for an input power of 20 dBm.                                                                    | 107   |

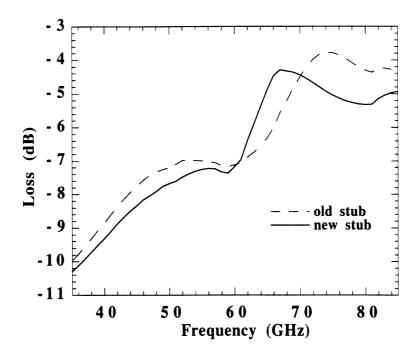

| 4 31 | Simulated results for the output circuit of the doubler with the wide (new)                                                                                                    | 101   |

| 1.01 | and narrow (old) stubs                                                                                                                                                         | 109   |

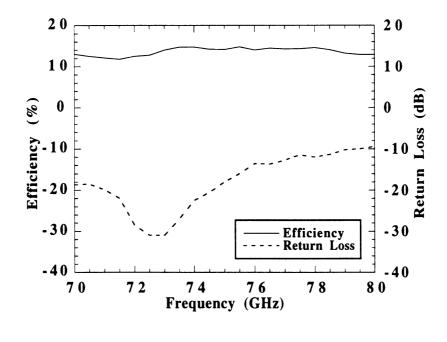

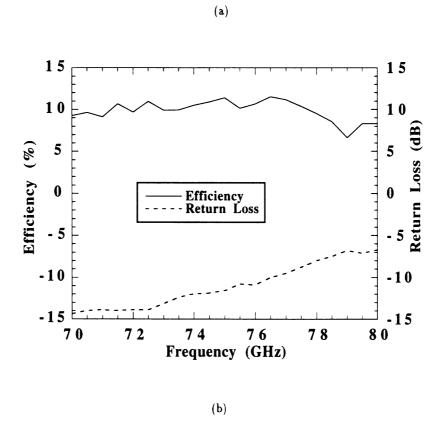

| 4.32 | Efficiency and return loss vs. output frequency for doublers fabricated on a                                                                                                   | 100   |

|      | new wafer and $P_{in}$ =20 dBm: a) improved Q=2 design and b) old Q=2 design                                                                                                   | .110  |

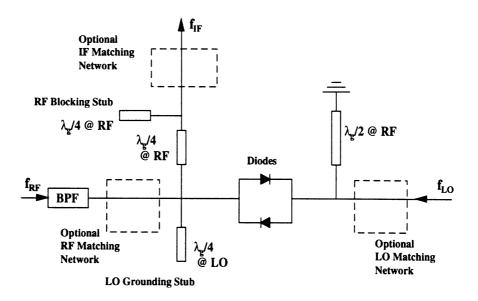

| 5.1  | Schematic of the monolithic FGC based sub-harmonic mixer (from S. Raman                                                                                                        |       |

|      | [93])                                                                                                                                                                          | 116   |

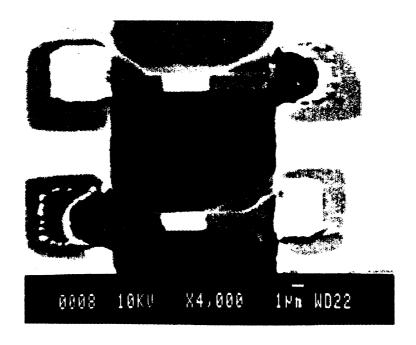

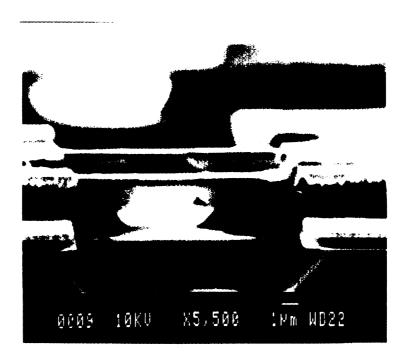

| 5.2  | SEM photograph of: a) back-to-back diodes with $2\mu m$ diameter and b) channel under the diode fingers                                                                        | 119   |

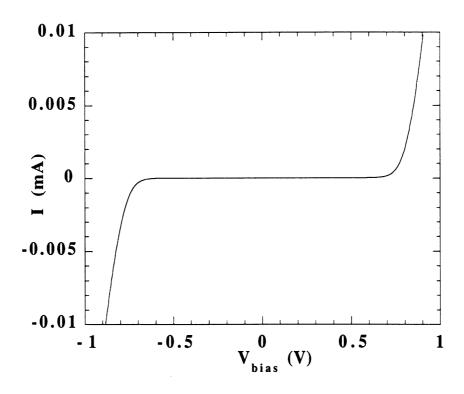

| 5.3  | Current-voltage characteristic of the anti-parallel pair of Schottky diodes used                                                                                               |       |

|      | in the mixer design.                                                                                                                                                           | 120   |

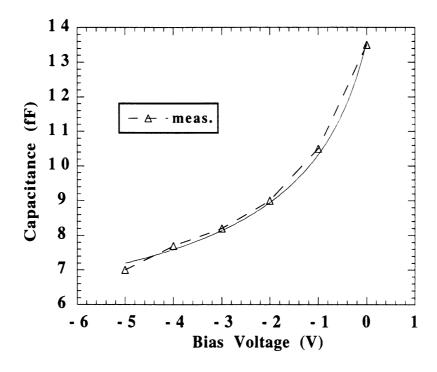

| 5.4  | Measured capacitance versus bias voltage for a single mixer diode with curve-fitted data                                                                                       | 120   |

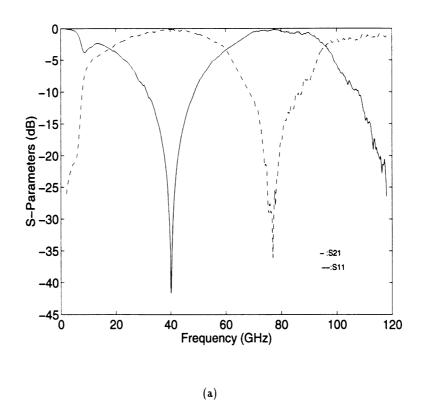

| 5.5  | Measured S-parameters for the: a) LO grounding stub and b) the RF ground-                                                                                                      |       |

|      | ing stub                                                                                                                                                                       | 122   |

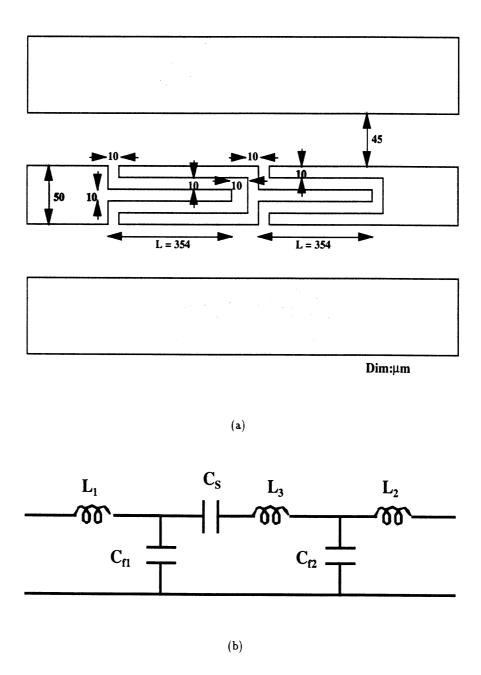

| 5.6  | RF bandpass filter used in the mixer design: a) circuit layout for two stub                                                                                                    |       |

|      | sections and b) equivalent circuit model for one stub section                                                                                                                  | 125   |

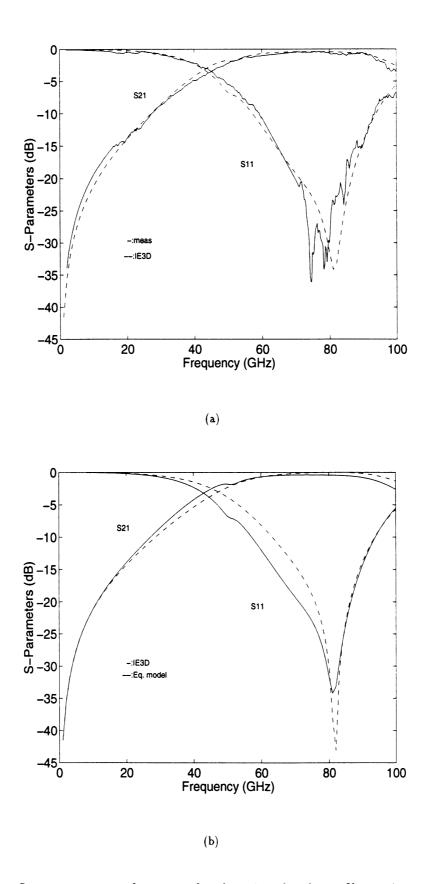

| 5.7  | S-parameters vs. frequency for the mixer bandpass filter: a) measured and                                                                                                      |       |

|      | IE3D simulated data and b) IE3D simulated and Libra equivalent circuit data                                                                                                    | a.126 |

| 5.8  | Libra simulation for the x2 subharmonic mixer: a) circuit schematic and b)                                                                                                     |       |

|      | harmonic balance test bench.                                                                                                                                                   | 127   |

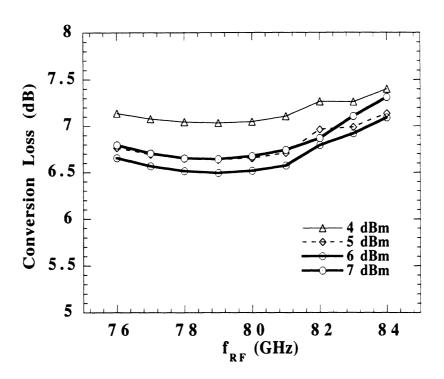

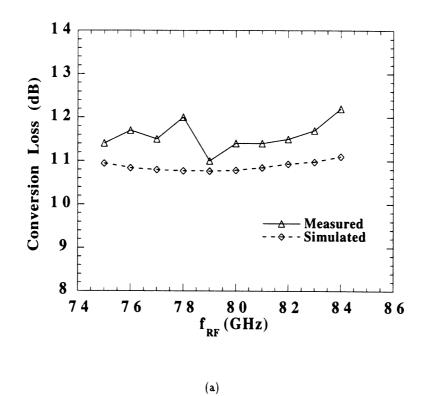

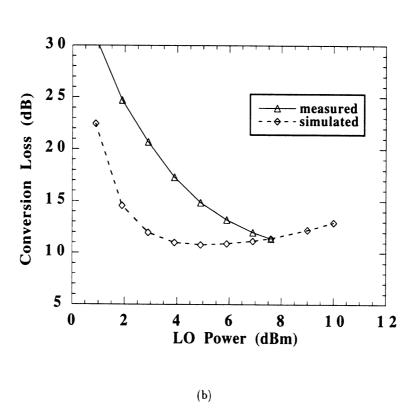

| 5.9  | Conversion loss vs. RF frequency for different LO power levels                                                                                                                 | 129   |

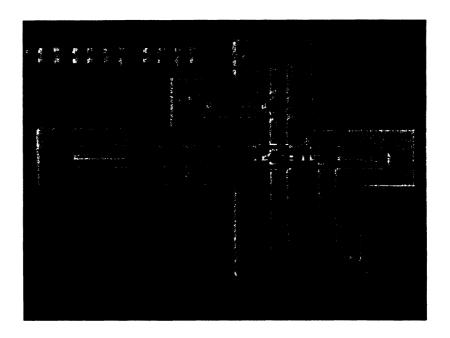

| 5.10 | Fabricated FGC line monolithic mixer                                                                                                                                           | 130   |

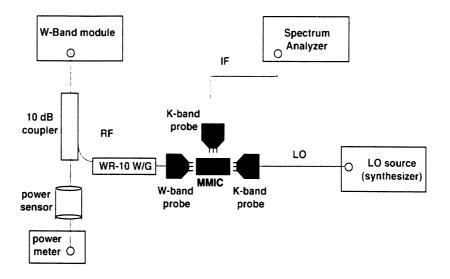

| 5.11 | Block diagram of the system used for the mixer measurements                                                                                                                    | 131   |

| 5.12 | Measured and simulated data for the diode with $R_S=40\Omega$ : a) SSB conversion loss vs. RF frequency for optimum LO power and b) SSB conversion                             |       |

|      | loss vs. LO power at $f_{RF} = 80GIIz$ .                                                                                                                                       | 132   |

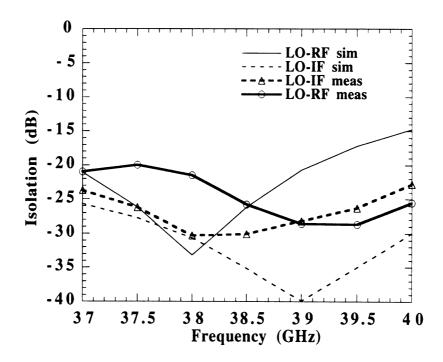

| 5.13 | Simulated and measured results for the RF/LO and LO/IF isolation of the                                                                                                        | 104   |

| G 1  | mixer versus LO frequency.                                                                                                                                                     | 134   |

| 6.1  | Conceptual diagram of a monolithic micromachined diplexer                                                                                                                      | 140   |

| 6.2 | Micromachined FGC lines ([3])                                                                                                                     | 142 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Conceptual block diagram of a monolithic multiplier/mixer pair with FGC                                                                           |     |

|     | line technology for on-wafer measurements                                                                                                         | 143 |

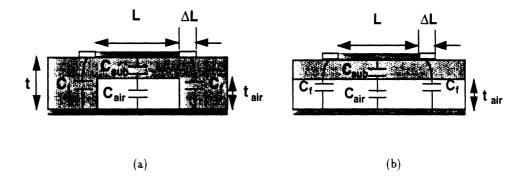

| A.1 | Capacitor model for the micromachined patch with (a) the radiating edges                                                                          |     |

|     | into the high-index substrate and (b) with the radiating edges over the mixed                                                                     |     |

|     | air-substrate region.                                                                                                                             | 147 |

| A.2 | Geometry of the micromachined patch antenna                                                                                                       | 148 |

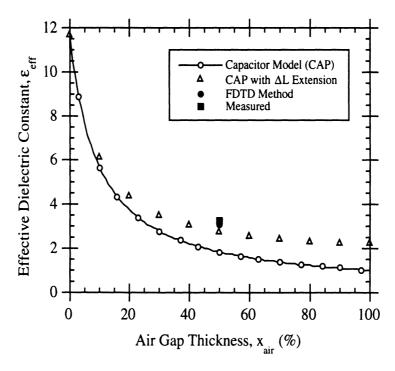

| A.3 | Effective dielectric constant vs. air-gap thickness for the silicon microma-                                                                      |     |

|     | chined patch                                                                                                                                      | 148 |

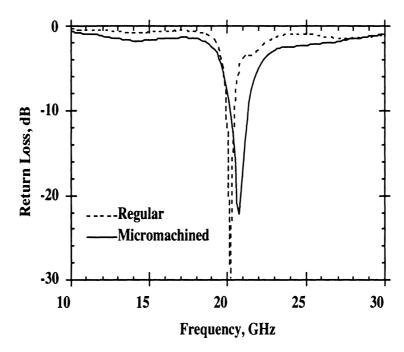

| A.4 | Return loss measurement of the regular and micromachined patch antenna printed on a full thickness substrate and substrate with mixed air-silicon |     |

|     | thickness ratio (1:1), respectively                                                                                                               | 150 |

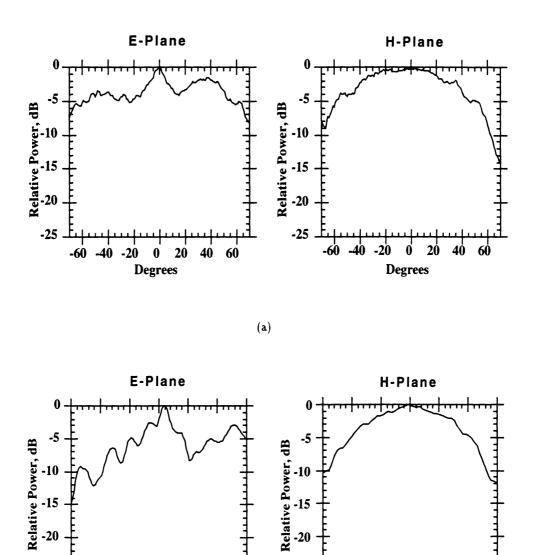

| A.5 | Radiation patterns for (a) the micromachined antenna on Silicon and (b) the                                                                       |     |

|     | regular antenna on Silicon.                                                                                                                       | 152 |

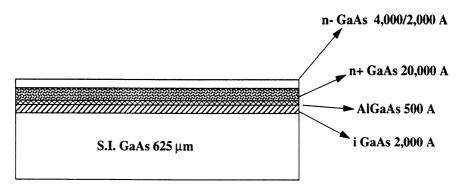

| B.1 | Cross section of the GaAs wafer used for the fabrication of active structures.                                                                    | 153 |

## LIST OF APPENDICES

| APPE         | NDIX                                                    |     |

|--------------|---------------------------------------------------------|-----|

| $\mathbf{A}$ | QUASI-STATIC MODEL FOR THE EVALUATION OF THE EFFECTIVE  |     |

|              | DIELECTRIC CONSTANT AND EXPERIMENTAL RESULTS FOR 2 PATC | H   |

|              | ANTENNAS ON SILICON                                     | 146 |

| $\mathbf{B}$ | FABRICATION PROCESS OF W-BAND AND D-BAND MULTIPLIERS    | 153 |

| $\mathbf{C}$ | FABRICATION PROCESS FOR MONOLITHIC MIXERS AND MULTI-    |     |

|              | PLIERS IN A TRANSMIT/RECEIVE MODULE                     | 159 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

The use of millimeter-wave technology in military and commercial applications has drawn the attention of the microwave community for more than three decades due to its advantages over other bands of the electromagnetic spectrum, as well as the lack of frequencies for new services. Since the size of any microwave circuit or component is dictated by the frequency of operation, implementation of the millimeter-wave region (30-300 GHz) can result in very small systems. This is extremely important for airborne and space applications, where launch and deployment costs depend heavily on the volume of the system that is to be deployed. Furthemore, millimeter-waves allow for antennas with high gain and directivity that are essential for point-to-point communication systems (e.g. between a satellite and an earth base station) and radars.

For space and airborne applications attenuation through the earth's atmosphere is a major consideration. In general, the attenuation of the microwave energy increases with frequency with the exceptions of a few minima that occur at 35 GHz, 94 GHz, 140 GHz, 220 GHz etc. These "windows" of minimum atmospheric absorption make millimeter-wave

systems ideal for such applications. In addition, millimeter-waves unlike infrared and optical wavelengths have the ability to permeate fog, dust and smoke.

Commercial applications of millimeter-wave systems include short-haul line-of-sight transmission links for personal communication networks (PCN's) that operate at 38 GHz, wireless cable at 28 GHz, wireless radio local area networks (LAN's) and mobile broadband systems [4]. In recent years, research efforts have also focused on automotive radar sensors for anticollison radars at 77 GHz, intelligent cruise control and road transport informatics. Aircraft landing systems and earth remote sensing are other areas where millimeter-waves have been employed [5]. The latter is of major significance due to the intense environmental studies currently under way and the changing conditions of our planet. Of course, military communication systems and radars as well as satellite communications were the first applications of millimeter-wave systems.

Until the early 80's most of the millimeter-wave components and systems were built with waveguide technology (rectangular or cylindrical). Waveguides offer low-loss, high quality factor circuits but are bulky and heavy thus imposing cost limitations on airborne and space systems. In addition, waveguide components are expensive to manufacture since they have to be precision machined one at a time, and at higher operating frequencies their fabrication complexity increases. The bandwidth of such systems is also limited by the operational bandwidth of the waveguides that are used. With the maturity of integrated circuit (IC) fabrication techniques and the increased need for high circuit integration and compact designs, the microwave community has started focusing its attention on Monolithic Microwave/Millimeter-wave Integrated Circuits (MMIC's). MMICs offer the advantages of small size and weight, that further decrease the cost of airborne and space applications. low fabrication cost since they can be batch fabricated using standard IC techniques and

improved reproducibility and reliability. Moreover, MMIC's can allow for broad band operation if designed properly and easy integration of active devices such as diodes and transistors. As a result, entire communication and radar systems can now be fabricated on a single planar substrate or a multi-layered chip with vertical interconnects connecting the various layers [6], [7]. The operating frequency can also be increased, thus satisfying the high demand for new spectrum bands.

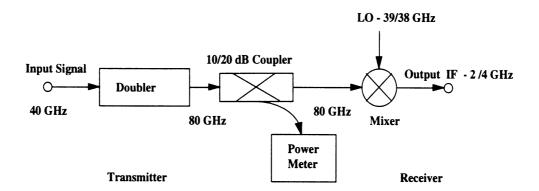

As system requirements for faster data transmission in lighter compact designs drive the technology area, higher frequency design solutions with large density layouts that include radiating elements, passive circuitry, oscillator sources and have light weight, small size and optimum performance, are required. Such a design can be seen in Fig. 1.1 and represents a monolithic transmit/receive system that operates at higher frequencies (W-band) and constitutes the RF front end of any communication or radar system. The transmitter includes a frequency multiplier that translates a lower frequency signal into a much higher one, an amplifier that increases the output power of the multiplier and an antenna that radiates the incoming energy. At the receiver, the high frequency signal captured by the antenna is amplified by a low noise amplifier (LNA) and is then down converted to a much lower one by a sub-harmonic mixer. For isolating a particular frequency spectrum, narrow band filters and diplexers can be imperented either right after the antenna or at other stages of the receiver. On-wafer packaging that reduces interaction between the different components and offers electrical and mechanical protection, as well as a means for heat dissipation, to both the transmitter and receiver can also be achieved. All of the passive and active components, including the package, can be fabricated on Silicon or GaAs substrate with standard integrated circuit fabrication techniques that would significantly lower the total cost.

Figure 1.1: Monolithic transmit/receive module for communication and radar systems.

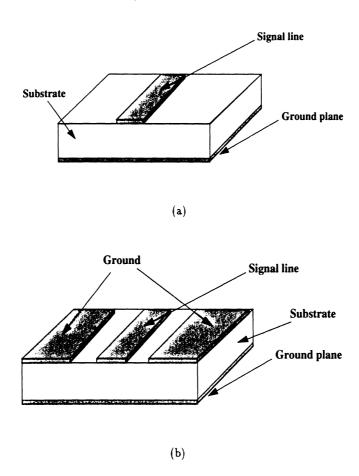

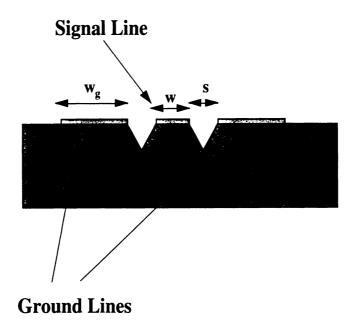

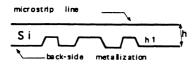

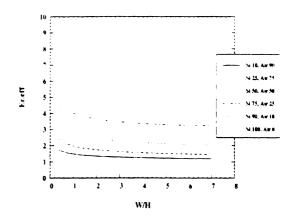

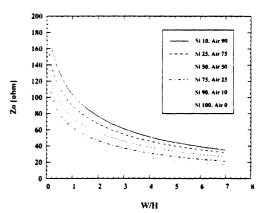

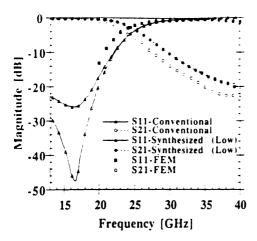

MMIC's are designed and fabricated using planar circuit technology that usually implements two types of transmission lines: the microstrip line (Fig. 1.2(a)) and the coplanar waveguide (CPW) (Fig. 1.2(b)). The air-dielectric interface that exists in both of these lines introduces several parasitic effects that are pronounced as the operating frequency increases. These effects include increased dielectric loss, substrate moding where the power can propagate inside the substrate in the form of unwanted modes, and dispersion. As a result, MMIC's operating at high frequencies (W band) can have some important limitations. These limitations are augmented by the non-availability of higher frequency solid-state oscillator sources that are difficult to fabricate. These sources are very important for heterodyne receiver applications where an incoming high frequency (RF) signal is down converted to a much lower frequency (IF) signal. The objective of this thesis is to find techniques that address these limitations encountered in planar, monolithically integrated passive and active circuits operating at higher frequencies (W band), with the goal of designing a monolithic

transmit/receive module that offers optimum performance and minimum cost.

Figure 1.2: Planar transmission lines: (a) microstrip and (b) coplanar waveguide (CPW).

One of the solutions to the restrictions imposed in passive MMIC's, makes use of the micromachining techniques. Micromachining is a technology widely used in the development of micro-electro-mechanical systems (MEMS), sensors and actuators [8] and its implementation in the microwave field is relatively new. The first application in microwave circuits was that of membrane supported antennas for imaging arrays [9]. Other developments on antennas reported since then include microstrip patches suspended on a dielectric membrane [10] over air or sitting on a substrate with periodically spaced holes [11] in order to increase the radiation efficiency. Regarding planar resonators and filters, micromachining was used to suspend microstrip and CPW resonators on membrane [12]- [13] in order to increase

the quality factor and achieve filter designs with very narrow bandwidth and very small loss. All of the previous mentioned examples illustrate the potential of micromachining to circumvent the problems associated with planar circuits operating at high frequencies.

For active MMIC structures, frequency multipliers and mixers operating in W-band and D-band have been realized. Frequency doublers on GaAs using microstrip line technology with 25% efficiency at 94 GHz and 2.8% efficiency at 320 GHz have been reported [14]-[15]. A modified version of the CPW line, the Finite Ground Coplanar (FGC) line, was used to fabricate a 40/80 GHz doubler with 15-16% efficiency and wide bandwidth [16]. A hybrid x2 subharmonic mixer on silicon with the diodes flip-chip bonded achieved a conversion loss of 7 dB at 94 GHz [17]. The excellent results obtained with all of the above active MMIC structures demonstrate the capability to integrate active devices with passive circuits in planar environments at high operating frequencies with very good performance.

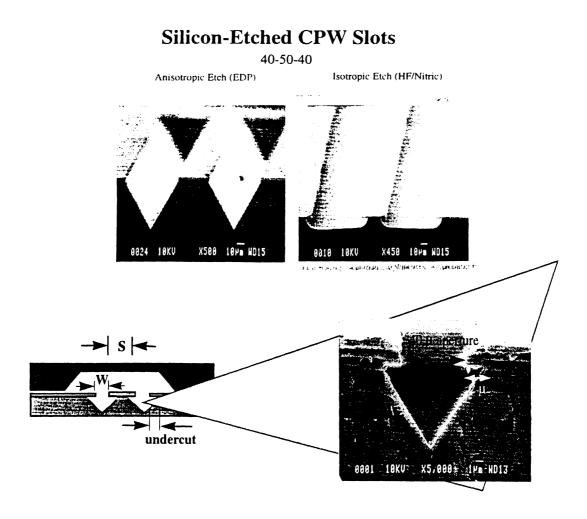

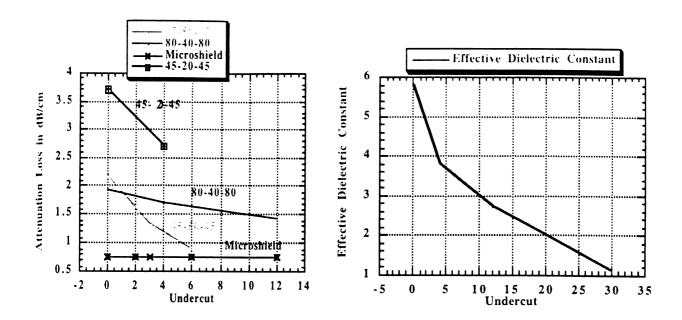

### 1.2 Silicon Micromachining

Silicon has been used as a mechanical material in order to make miniature devices and components since the early 70's, with the first applications in the areas of sensors and transducers. The major process that gives silicon "chips" the various shapes and geometries is micromachining. When a silicon wafer is immersed in an appropriate chemical, then it starts to etch with the process depending on the etchant, the orientation of the wafer and the presence of dopants. The most commonly used etching systems are: a) ethylene diamine, pyrocatechol and water (EDP), b) KOII and water, c) HF, HNO<sub>3</sub> and acetic acid and d) Tetramethyl Ammonium Hydroxide in water (TMAH) [18],[19]. Except for HF-Nitric, all of these chemical etchants are anisotropic. This means that the etch rate strongly depends on the crystallographic orientation of the wafer.

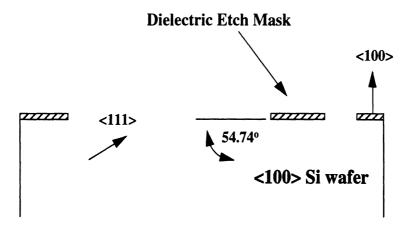

Figure 1.3: Anisotropic etching profile and geometry for the  $\prec 100 \succ$  oriented silicon wafer.

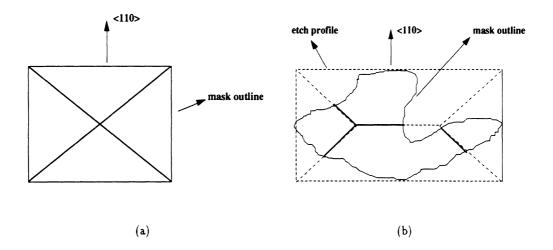

The crystal lattice of the silicon wafer is described by the "Miller indices", which express directions and planes within the crystal using three integer numbers [20]. For EDP, KOII and TMAII the anisotropic behavior is due to the fact that  $\prec 111 \succ$  surfaces are attacked at a much slower rate than all other crystallographic planes (etch-rate ratios as high as 1000 have been reported). Fig. 1.3 shows the etching profile of a standard  $\prec 100 \succ$  oriented wafer, used for all of the work presented in this thesis. In this case, the etchant proceeds rapidly in all directions that are perpendicular and parallel to the surface of the wafer until the  $\prec 111 \succ$  planes become exposed, where the etching effectively stops leaving a sloping side wall in the profile with a 54.74° angle [21]. Any rectangular hole oriented on the surface of the wafer in the  $\prec 110 \succ$  direction, will result in a pyramidal-shaped pit when an anisotropic etchant is used (Fig. 1.4(a)). If the silicon is etched long enough, any randomly shaped closed pattern will also result in a rectangular pit as seen in Fig. 1.4(b). The  $\prec 100 \succ$  silicon etch rate for EDP is approximately 1.2 $\mu$ m/min at 110°C, and for 22% TMAII solution it is 1.0 $\mu$ m/min at 90°C.

An important factor in determining the appropriate etchant is its selectivity towards different masking films. For  $SiO_2$  and  $Si_3N_4$  that are widely used as a mask etch the

Figure 1.4: Pyramidal pits of a <100≻ silicon wafer for: a) a rectangular etch mask pattern and b) a random etch mask pattern and long etching time.

corresponding rates can be seen in Table 1.1 [22], [23]. From this table we observe that for long etches  $Si_3N_4$  is preferred for KOII and IIF-IINO<sub>3</sub>, whereas for EDP and TMAII both dielectric films can be used. In addition, the etch rate for  $SiO_2$  in TMAII is almost four orders of magnitude lower than those of  $\prec 100 \succ$  and  $\prec 110 \succ$  crystallographic directions, depending on the solution temperature and concentration.

| Etchant  | $SiO_2 (nm/min)$ | $Si_3N_4$ (nm/min) |

|----------|------------------|--------------------|

| HF-IINO3 | 10-30            | low                |

| EDP      | 1-80             | low                |

| KOII     | 1-10             | low                |

| TMAII    | 1                | 1-10               |

Table 1.1: Etch rates of different chemicals for  $SiO_2$  and  $Si_3N_4$ .

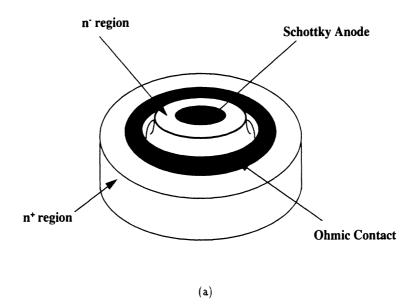

#### 1.3 Schottky Barrier Diode

The Schottky barrier diode has been used in numerous millimeter-wave mixer and multiplier applications since the early 70's. The rectifying or Schottky barrier type junction is formed by placing a metal of higher work function in intimate contact with an n-type semi-conductor of lower work function [2]. Platinum, Ti and gold are the most commonly used anode materials for fabricating GaAs diodes [24]; gold and aluminum have also been used, although these materials have poor reliability. The size and shape of the anode are selected to give the appropriate electrical characteristics (junction capacitance and series resistance) for the intended application. The circular anodes of microwave and millimeter-wave diodes vary in diameter from less than 1.5  $\mu m$  to  $20\mu m$ . For practical reasons a large number of anodes are defined on the surface of a single chip and are isolated from each other by an oxide or nitride layer or by selective etching (mesa) around each diode. An ohmic contact is also formed on the substrate, and for GaAs alloyed gold- germanium is most commonly used.

In thermal equilibrium, a depletion region forms within the semiconductor at the metal interface that is positively charged, since all of the mobile electrons are absent and only the ionized donor atoms are present. The width, W, of the depletion region assuming a uniform doping  $N_D$  can be found by solving Poisson's equation to be [25]:

$$W = \sqrt{\frac{2\epsilon(V_{bi} - V)}{qN_D}} \tag{1.1}$$

where  $\epsilon$  is the dielectric constant of the semiconductor,  $N_D$  is the doping concentration in the  $n^-$  layer, q is the electric charge of the electron,  $V_{bi}$  is the built-in potential and V is the applied voltage at the anode. The charge ,Q, and capacitance ,C, per unit area can be evaluated from:

$$Q = qN_DW = \sqrt{2q\epsilon N_D(V_{bi} - V)}$$

(1.2)

$$C = \frac{\partial Q}{\partial V} = \sqrt{\frac{q\epsilon N_D}{2(V_{bi} - V)}} = \frac{\epsilon}{W}$$

(1.3)

Equation 1.3 can also be written as:

$$C_j = C(V) = \frac{C_{jo}}{\sqrt{1 - \frac{V}{V_{bi}}}}$$

(1.4)

where  $C_{jo}$  is the zero bias capacitance given by:

$$C_{jo} = \sqrt{\frac{qN_D\epsilon}{2V_{bi}}} \tag{1.5}$$

The relationship linking the current, I, through the diode with the applied voltage, V, can be found with the help of thermionic emission-diffusion theory [25]:

$$I = I_s(e^{\frac{qV}{nkT}} - 1) \tag{1.6}$$

where

$$I_s = A^* T^2 S e^{\frac{-q\Phi_b}{kT}} \tag{1.7}$$

In equations 1.6,1.7 n is the ideality factor of the diode, k is Boltzmann's constant, T is the temperature in Kelvin,  $\Phi_b$  is the barrier height, S is the junction area and  $A^*$  is the effective Richardson constant which is approximately 4.4  $Acm^{-2}K^{-2}$  for a metal-GaAs contact. The ideality factor, n, is an indication of how much the diode deviates from the perfect case (n=1) and is a measure of the quality of the junction. It is used to account

Figure 1.5: Equivalent circuit for the Schottky-barrier diode.

for any type of imperfections in the junction and for phenomena that cannot be explained with the thermionic diffusion theory. Typical values of n range from 1.05 to 1.3.

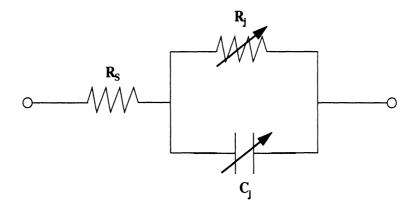

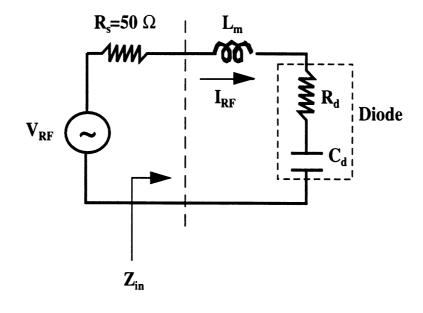

The equivalent circuit of a Schottky-barrier diode can be seen in Fig. 1.5 [24]. The diode consists of three elements, two of which, the junction capacitance and resistance, are non-linear. The junction resistance  $R_j$  accounts for the generation-recombination current, the diffusion current and the surface leakage current. The parasitic series resistance  $R_s$ , which is a result of the undepleted high resistivity epitaxial material, is also non-linear but varies slightly both in forward and reverse bias. In mixers and multipliers  $R_s$  can be a very significant loss mechanism.

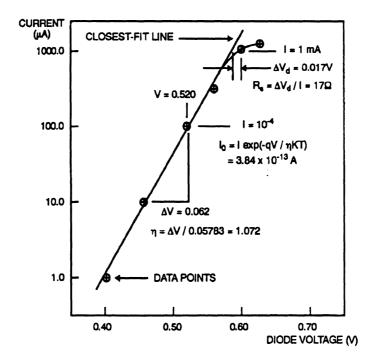

One way to measure  $R_s$  is to plot the diode I-V characteristic on semi-log coordinates. If there was no loss in the junction the I-V would follow the straight line, as indicated by equation 1.6. However, because of the loss (i.e.  $R_s$ ) the I-V characteristic deviates from the ideal line and the difference  $\Delta V$  between the expected and actual voltage for a particular value of current I yields  $R_s$  as follows (see Fig. 1.6):

$$R_s = \frac{\Delta V}{I} \tag{1.8}$$

The capacitance  $C_j$  of the diode can be measured with the help of an LCR meter for

Figure 1.6: I-V characteristic of a Schottky diode on a semi-log plot.

different biasing conditions. Once  $R_s$  and  $C_{jo}$  are found, a figure of merit for the diode, the cutoff frequency  $f_c$  can be evaluated from:

$$f_c = \frac{1}{2\pi R_s C_{io}} \tag{1.9}$$

Usually, for the calculation of the cutoff frequency the dc quantities of the diode are used, without taking into account high frequency skin-effects and parasitics.

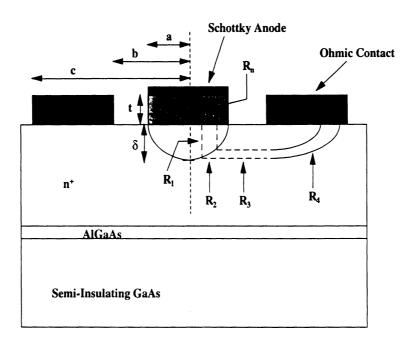

For MMIC applications the planar disk type Schottky diode shown in Fig. 1.7(a) is commonly used (this type of diode was used in the work presented in this dissertation). In this mesa-type diode both contacts (anode and cathode) are on the top surface of the chip and the current through the device flows down from the anode and spreads laterally around the base of the mesa before flowing out of the cathode [14]. Assuming that the current is confined within a skin depth  $\delta$ , the series resistance can be broken in several components

(Fig. 1.7(b)), and the analytical equations for these components are given by the following equations [26], [27]:

$$R_n = \frac{t - W}{\sigma_n \pi a^2} \tag{1.10}$$

$$R_1 = \frac{\delta_s}{2\sigma_s \pi a^2} \tag{1.11}$$

$$R_2 = \frac{1}{4\pi\sigma_s\delta_s} \tag{1.12}$$

$$R_3 = \frac{1}{2\pi\sigma_s \delta_s} ln(\frac{b}{a}) \tag{1.13}$$

$$R_4 = \frac{\rho_m \rho_s}{\rho_m \delta_s + \rho_s \delta_m} \left[ \frac{1}{2\pi} ln(\frac{c}{b}) + \frac{\delta_s}{\rho_s} (AI_o(\beta c) + BK_o(\beta c)) + \frac{\delta_m}{\rho_m} (AI_o(\beta b) + BK_o(\beta b)) \right]$$

(1.14)

where

$$A = \frac{1}{2\pi\beta\Delta} \left[ \frac{\rho_m K_1(\beta b)}{\delta_m c} + \frac{\rho_s K_1(\beta c)}{\delta_s b} \right]$$

(1.15)

$$B = \frac{1}{2\pi\beta\Delta} \left[ \frac{\rho_m I_1(\beta b)}{\delta_m c} + \frac{\rho_s I_1(\beta c)}{\delta_s b} \right]$$

(1.16)

$$\Delta = I_1(\beta c)K_1(\beta b) - I_1(\beta b)K_1(\beta c) \tag{1.17}$$

$$\beta = \sqrt{\frac{1}{\rho_c} (\frac{\rho_m}{\delta_m} + \frac{\rho_s}{\delta_s})} \tag{1.18}$$

$\rho_c$  is the ohmic contact resistance,  $\delta_s$  and  $\delta_m$  are skin depths,  $\rho_s$  and  $\rho_m$  are resistivities,  $\sigma_s$  and  $\sigma_m$  are conductivities, in the substrate and metal regions, respectively.  $I_n()$  and  $K_n()$  are modified Bessel functions of the first and second kind, respectively. The total series resistance, therefore, of the disk-type diode of Fig. 1.7(a) is:

$$R_s = R_n + R_1 + R_2 + R_3 + R_4 \tag{1.19}$$

For a W-band (40 to 80 GHz) multiplier diode with a=4.8  $\mu m$ , b=8.3  $\mu m$ , c=12.3  $\mu m$ , an epi-layer thickness of 4000  $\mathring{A}$  and a doping of  $1 \times 10^{17} cm^{-3}$   $R_s \approx 1.5 \Omega$  from equation 1.19,

Figure 1.7: a) Disk type diode for MMIC applications and b) cross section of diode showing different components of the series resistance (from [14]).

(b)

while for a mixer diode with a=1.1  $\mu m$ , b=3.1  $\mu m$ , c=7  $\mu m$ , an epi-layer thickness of 2000  $\mathring{A}$  and a doping of  $3 \times 10^{17} cm^{-3}$   $R_s \approx 6.4 \Omega$ .

The efficiency of a Schottky-barrier diode that is used as a varactor is expressed as the quality factor, Q, which is the ratio of the energy stored in the junction to the energy dissipated by it [25]:

$$Q = \frac{\omega C_j R_j}{1 + \omega^2 C_j^2 R_j R_s} \approx \frac{1}{\omega C_j R_s} = \frac{X_{in}}{R_{in}}$$

(1.20)

#### 1.4 Measurement Techniques

Measurements on monolithic microwave/millimeter-wave circuits are performed using an IIP 8510C Vector Network Analyzer (VNA). The analyzer is capable of measuring the S-parameters of various circuits from 2 to 118 GIIz, with three different test sets. From 2 to 40 GIIz, the 8516A test set is used with coaxial cables having K-connectors at the end. These cables are connected to model 40A probes from GGB Industries that are designed for on-wafer measurements up to 40 GIIz. From 40 to 60 GIIz, the synthesizer of the VNA drives the 83556A mm-wave source module that uses frequency multipliers (triplers) in order to produce the range of interest. The module is connected to a waveguide system that includes couplers and mixers for sampling the incident/reflected energy and downconverting the measured signals to the 1.2 MIIz baseband. At the end of the waveguide system there is a waveguide-to-coax transition that leads to a 1.89 mm connector where the coaxial cable is attached. The other end of the cable is connected to model 67A probes that are used to measure the planar circuit. The measurement is controlled and recorded with the 85105A millimeter wave controller. The same controller is used for W band measurements from 70 to 118 GIIz. In this case, the W85104A modules are used to produce the frequencies of interest

from those of the synthesizer with the help of quadruplers. The output of the W band test set modules is a WR-10 adaptor that is connected to a long piece of WR-10 waveguide. The waveguide is followed by model 120A-BT probes that have a WR-10 adaptor and a bias-tee network for biasing active structures (such as multipliers and mixers) during measurements without affecting the RF frequencies. All the different models of probes that were mentioned are compatible with coplanar-waveguide transmission lines and consist of three tips, two for the ground and one for the signal, that launch the CPW mode into the planar passive or active structure. The distance between the center tip and each of the outer tips is called the probe "pitch" and is either 150 or 100  $\mu m$  (for most of the measurements in this thesis it is 150  $\mu m$ ). The system available for measurements does not cover the range from 60 to 70 GHz and ,therefore, in the graphs presented herein this band will be presented either with a straight line or a gap in the data.

In order to measure the S-parameters of a circuit, the errors introduced by the various components of the network analyzer, the cables/waveguides, the connectors, the adaptors and the probes must be removed. The process of removing these errors is called calibration or de-embedding. The two methods that are widely used for calibrating the VNA are the Short-Open-Load-Thru (SOLT) and the Thru-Reflect-Line (TRL). In the SOLT method the system is calibrated up to the end of the probe tips and, thus, the errors introduced from the probe to planar circuit transition are not accounted for. For a full two port calibration, error correction is achieved by measuring four standards (open, short,  $50 \Omega$  load and thru line) with known responses. The model that represents the various mechanisms of error in the system and is used for de-embedding, consists of twelve error coefficients (for a one port calibration three standards are used and three error coefficients are calculated). By measuring four known standards a system of twelve equations with twelve unknowns is

formed and solved. The error coefficients are then loaded into the VNA and calibration is achieved on-line.

In the TRL method, the reference planes for the measurement are inside the planar circuit and the errors from the probe-to-circuit transition as well as the transmission lines before the device under test (DUT) can be de-embedded [28], [29]. The standards that are used in this method are fabricated on the same wafer with the DUT and consist of a thru line, one or several delay lines and a short or open. With appropriate selection of the standard dimensions, the designer has the flexibility to define the reference planes anywhere in the circuit before the DUT of interest. The length of the thru line is twice the distance between the point where the probe tips touch the circuit and the reference plane. Usually, the length of the thru line is equal to a wavelength at a particular frequency of interest but any arbitrary length can also be chosen. The length of the reflect standard is half the length of the thru line and depending on the type of line a short or an open is used. For a microstrip configuration an open is much easier to fabricate since a short would require a via hole, while for a CPW configuration a short is usually preferred.

For the delay lines, the lengths are  $\lambda/4$  longer than that of the thru line at various frequencies. These frequencies are determined by the user to ensure a good calibration over the entire band of interest. The delay lines allow the network analyzer to compute calibration coefficients so that the proper phase response of the DUT can be found. For this reason, a delay line is "good" as long as  $0.5 \le |\sin(\beta l)| \le 1$ , where l is the excess length of the delay line, over the frequency range of interest. If the previous relationship is not true for the entire band, then several delay lines that meet the previous criterion must be designed in a way that they overlap and cover all the range. Each delay line will therefore be effective in a sub-region of the entire frequency band. The best phase correction results

are possible when  $\beta l$  is closer to  $90^{\circ}$  or  $270^{\circ}$ . One restriction of the TRL method stems from the maximum length of the delay lines that must fit in the available wafer area. If multiple columns of calibration standards are needed on the wafer, then the length of the lines should be designed to account for the amount of space available. The resonance frequency may have to be altered in order to obtain shorter delay lines, if they are too long for multiple columns.

The National Institute of Standards and Technology (NIST) has developed a program called *Multical* [30],[31], that performs a TRL calibration of the IIP8510C VNA on line and runs under IITBasic in a Windows 3.11 environment. This program makes the TRL calibration faster and more convenient. Rather than defining standards on the IIP8510C VNA, the standards are quickly defined on screen by editing a calibration menu and corrections or alterations can be made rather easily. *Multical* is capable of calculating the error coefficients and loading them in the IIP8510C VNA so that the user can measure the S-parameters of the SUT directly. Besides the scattering parameters, Multical can plot and analyze various data such as propagation constant, attenuation, effective permittivity, characteristic impedance and capacitance of a line.

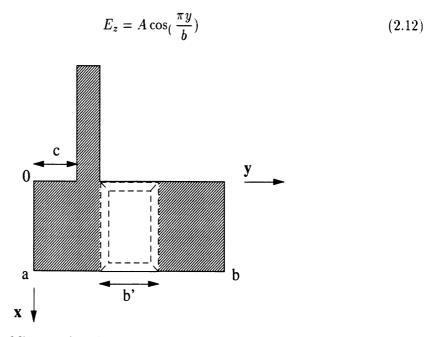

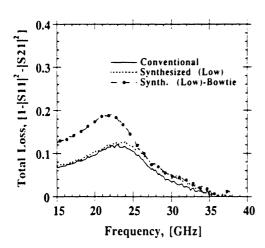

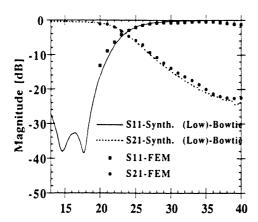

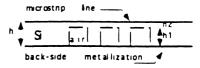

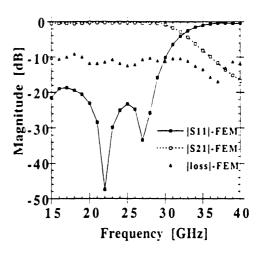

# 1.5 Simulation Tools