# THE BOUND-STATE RESONANT TUNNELING TRANSISTOR (BSRTT): FABRICATION, D.C. I-V CHARACTERISTICS AND HIGH-FREQUENCY PROPERTIES

G. I. Haddad, U. K. Reddy, J. P. Sun and R. K. Mains Center for High-Frequency Microelectronics Department of Electrical Engineering and Computer Science The University of Michigan Ann Arbor, Michigan 48109-2122

(Received: 30 July 1990)

The output characteristics of resonant tunneling transistors with a charge filled bound state quantum well base obtained by a self-consistent solution of Poisson's and Schrödinger's equations show the effect of coupling between the input and output ports of the device and the effect on the current-voltage characteristics. Using a self-aligned process transistors were fabricated which showed a current gain of 3 and transconductances of 30 mS. The output characteristics do not saturate and this is in qualitative agreement with theoretical predictions. The charge and potential distributions obtained from the self-consistent calculations are used in a quasi-static analysis of the small signal parameters for a hybrid- $\pi$ model, and the high-frequency performance of the transistor is analyzed.

#### 1. Introduction

Three terminal devices making use of resonant tunneling<sup>1</sup> have generated considerable interest because of their potential applications in highfrequency/speed applications<sup>2,3</sup> and novel logic circuits<sup>4</sup>. The current transport in all of these devices is controlled by the resonant tunneling phenomenon<sup>5</sup>. There are basically two approaches to the realization of these devices. The first approach involves the use of a traditional double barrier quantum well (DBQW) structure in one of the terminals of a field effect transistor<sup>6</sup> or bipolar junction transistor<sup>3</sup> or even a hot electron transistor<sup>7</sup>. The other approach consists of directly contacting the thin quantum well base region. Although this problem appears simple at first, it presents formidable technological challenges which partly explains the limited number of results obtained so far. It is also very difficult to carry out an accurate theoretical analysis of the device and predict its performance.

A low resistance contact to the quantum well base requires a charge filled quantum well and thus the traditional DBQW is not very suitable for this purpose. Therefore, a modified DBQW structure was proposed independently by Haddad et. al.8 and Schulman and Waldner<sup>9</sup>. The structure makes use of a bound state to store charge in the well, hence the name Bound State Resonant Tunneling Transistor (BSRTT). Haddad et. al.<sup>8</sup> also proposed the utilization of a stepped barrier to improve the device performance. Experimentally, a transistor of similar vintage was realized by Reed et. al.<sup>10</sup> by using a p-type GaAs quantum well and superlattice wide-bandgap emitter and collector layers. Preliminary results on a unipolar version of the device were published earlier by us.<sup>11</sup> We noted that the lack of gain in these devices was explained in terms of strong Fermi pinning in the extrinsic base region. In this paper we present results from a theoretical analysis based on our current understanding of device operation and discuss details of the fabrication technology developed in our Laboratory for the realization of BSRTT. Experimental results will be presented showing a current gain  $(\beta)$  of 3 and a transconductance  $(g_m)$  of 30 mS (40  $\times$  40  $\mu$ m<sup>2</sup> device area) in these transistors. These are preliminary results and improved performance is expected with improvements in fabrication technology.

### 2. Theoretical Model

## 1. Self-Consistent Calculations of Device Characteristics

The calculation of I-V characteristics is carried out by solving Poisson's equation and Schrödinger's equation self-consistently: Poisson's equation is solved for the electrons outside the quantum well treated with the Thomas-Fermi approximation, and the bound-state electron concentration is calculated separately by solving the Schrödinger equation in the quantum well. An interactive scheme is then employed to solve for the charge and the potential distributions for the entire structure within a prescribed tolerance. The details of the formulation are presented elsewhere.<sup>12</sup> Once the charge and potential distribution are found, a quasi-static analysis of the small signal parameters for a hybrid- $\pi$ circuit model is used to evaluate the high-frequency performance of the device, which will be described in the next section.

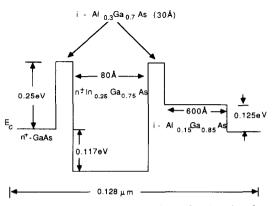

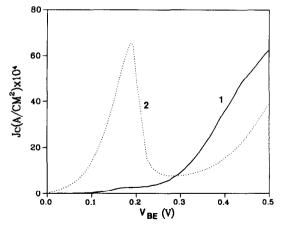

The device structure analyzed here is shown in Fig. 1. It consists of a  $Al_{0.30}Ga_{0.70}As/In_{0.25}Ga_{0.75}As/Al_{0.50}Ga_{0.70}As$  DBQW structure and a flat stepped AlGaAs barrier of 0.125eV (the band edge of GaAs electrode is taken to be at zero potential). The quantum well base is doped at 2 × 10<sup>18</sup> cm<sup>-3</sup>. The effective masses in the GaAs,  $Al_{0.30}Ga_{0.70}As$ and  $In_{0.25}Ga_{0.75}As$  regions are 0.067m<sub>0</sub>, 0.092m<sub>0</sub> and 0.056m<sub>0</sub> respectively. The calculated  $J_c$  vs  $V_{BE}$  characteristics are shown in Fig. 2. For the structure in Fig. 1, the device exhibits a monotonic current increase with increasing base-emitter bias, corresponding to the solid line. This is because, for this particular structure, the second resonant energy level is close to the bandedge in the emitter region

Fig. 1 BSRTT structure and conduction band diagram.

Fig. 2 Collector current  $J_C$  as a function of  $V_{BE}$  for two structures 1) with a 80Å quantum well (solid curve) and 2) with a 70Å quantum well (dotted curve).

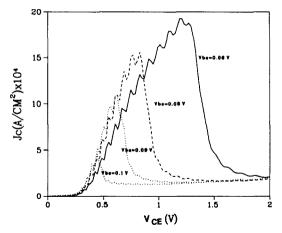

Fig. 3 Theoretical output characteristics of the BSRTT for various values of  $V_{BE}$ .

throughout the bias range. With a modified structure, for example with a narrower 70 Å quantum well, we have obtained negative differential resistance by lifting the second resonant level shown by the dotted curve. The  $J_C$  vs  $V_{CE}$  characteristics obtained for this structure, however, are different compared with the characteristics calculated from previous work without self-consistency.<sup>8</sup> The currents do not saturate with increasing collector - emitter bias voltages with  $V_{BE}$ varying from 0V to about 0.1V as shown in Fig. 3. An examination of the device band structure (not shown here) shows that the second level is close to the breaking point of the stepped barrier for smaller  $V_{CE}$ . When  $V_{CE}$  is increased to 0.8V ( $V_{BE} = 80$  mV), the second level in the well is about at the same level as the onset of the stepped barrier, resulting in a current peak. This is shown in Fig. 3. Further increase of  $V_{CE}$ does not change the effective second barrier width to a significant extent, and the drop of current density is due to an off-resonance condition. It is believed that the inclusion of self-consistency in the calculations has modeled the effect of coupling between the input and output ports of the device. That is, varying  $V_{CE}$  does affect the bandedges in the emitter and base regions and hence  $V_{BE}$ . Therefore the base region is not kept equipotential for an applied base-emitter voltage. To model these effects accurately, a two-dimensional analysis would be required.

Beyond  $V_{BE} = 0.1V$ , the device exhibits monotonic increase in current density with increasing  $V_{CE}$ . This is because the bandedge in the emitter has passed the second level and the emitter electrons will not see a resonant level for this structure below the top of the barrier. The current density ripples in the above I-V characteristics are believed to result from quantum mechanical reflections due to the second and the stepped barrier.

We note that our self-consistent calculations reveal strong feedback effects in the narrow quantum well base transistor, and the stepped barrier and the bound state charge is not adequate to offer good isolation between the emitter and the collector of the transistor. It is further noted that the I-V characteristics of the BSRTT are a very sensitive function of the energy band and geometric structure, as seen from our calculations. More systematic optimizations are to be conducted for the desired I-V characteristics for particular circuit applications.

The  $J_C$  vs  $V_{CE}$  characteristics in Fig. 3 seem to be attractive for a high-frequency negative resistance oscillator, as it presents a large peak to valley ratio (PVR) in current density and a large difference between the peak and valley voltages. However, at higher  $V_{CE}$ , the bound state electrons in the base may have significant tunneling through the effective stepped barrier to the collector. This mechanism should be balanced by scattering of the incoming electrons from the emitter and the base contact to build up a dynamic equilibrium for the steady-state case. Both mechanisms are not yet included in our model. Therefore, it is not possible at this point to determine the magnitude of the maximum voltage swing, which is essential to generate significant amounts of power.<sup>13</sup>

### 2. Evaluation of High-Frequency Performance

The BSRTT has superior high-frequency potential despite the difficulties in the device design and fabrication. In the following, a simplified hybrid  $-\pi$  model is used to estimate the device's current-gain cutoff frequency  $f_T$ . The values of the device transconductance  $(g_m)$  and the capacitances are typical ones obtained for the device calculations described in the previous section.

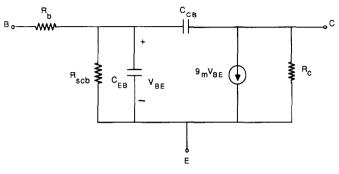

The hybrid- $\pi$  circuit model for the BSRTT is shown in Fig. 4 where  $R_b$  is the small-signal base resistance which accounts for the charging and discharging effects of the capacitance between the emitter and the base. R<sub>scb</sub> is the scattering base resistance, which represents the DC base current due to various scattering mechanisms (R<sub>sch</sub> has been neglected in our calculations, i.e.  $R_{scb} \rightarrow \infty$ ).  $g_m$ is the transconductance  $-\frac{\partial I_C}{\partial V_{BE}}\Big|_{V_{CE}}$ . The current transport in the circuit model is represented by the voltage-controlled current source,  $g_m V_{BE}$ , and the collector resistance  $R_C = \left(\frac{\partial I_C}{\partial V_{CE}}\right)^{-1}$ . Since the BSRTT has bound state charge and a second level in the base,  $g_m$  and the differential capacitances may be negative for certain bias ranges. The negative transconductance is seen from the  $J_C$  vs  $V_{CE}$  curves in Fig. 3. The capacitances are defined as

Fig. 4 Equivalent circuit of the BSRTT.

$C_{BE} = \frac{\partial Q_{BE}}{\partial V_{BE}}$  and  $C_{BC} = \frac{\partial Q_{BC}}{\partial V_{BC}}$

In our calculations of the capacitances,  $\partial Q_{BE}$  and  $\partial Q_{BC}$  include changes of the charge at both sides of the barriers including the bound-state charge. The contact resistances and the electrode resistances are not included in this device intrinsic model.

The  $f_T$  of the BSRTT is calculated to be

$$f_T = \frac{1}{2\pi} \sqrt{\frac{1 - g_m^2 R_{scb}^2}{R_{scb}^2 [C_{BC}^2 - (C_{BE} + C_{BC})^2]}}$$

Assuming negligible scattering in the base,  $g_m^2 R_{scb}^2 >> 1$  and

$$f_T = \frac{|g_m|}{2\pi\sqrt{C_{BE}^2 + 2C_{BE}C_{BC}}}$$

Using the largest value of  $g_m$  calculated for this structure,  $f_T$  is estimated to be about 3 THz.

### 3. Experiment

Epitaxial Growth and Device Fabrication

The device structures were grown by molecular beam epitaxy (MBE) on semi-insulating GaAs substrates at 600° C. The device structure is shown in Table I.

The MBE grown layers were processed into three terminal devices using standard photolithography and a combination of wet chemical and reactive-ion-etching (RIE) for mesa formation. As mentioned in our earlier work<sup>11</sup> Fermi pinning in the extrinsic base region is a major performance limiting factor. To overcome this problem we have developed a self-aligned technology for making the base contact. A highly selective dry etch was developed in our laboratory that allows us to

#### Table I Device Layer Diagram

| 3000Å             | n+-GaAs                 | $1 \times 10^{18} \mathrm{cm}^{-3}$ |

|-------------------|-------------------------|-------------------------------------|

| 500               | n-AlGaAs ( $x = 0.15$ ) | $1 \times 10^{17}$                  |

| 20                | i-AlGaAs (x=0.15)       |                                     |

| 30                | i-AlAs                  |                                     |

| 15                | i-InGaAs(y=0.25)        |                                     |

| 50                | n+-InGaAs(y=0.25)       | $1 \times 10^{19}$                  |

| 15                | i-InGaAs(y=0.25)        |                                     |

| 30                | i-AlAs                  |                                     |

| 600               | i-AlGaAs(x=0.15)        |                                     |

| 20                | i-GaAs                  |                                     |

| 6000              | n+-GaAs                 | $1 \times 10^{18}$                  |

| $50/50 \times 10$ | GaAs/AlAs SL            |                                     |

|                   | S. I. GaAs Substrate    |                                     |

selectively etch GaAs and stop on thin AlGaAs or In-GaAs layers. By carefully controlling the etch parameters we can control the etching in the lateral direction giving desired separation between the emitter mesa and the base ohmic contact, thus reducing surface depletion effects. We have also developed an ohmic process that gives us low resistance contacts and shallow diffusion of ohmic material into the epilayers. The second criterion is very important because of the extremely thin nature of the base. The ohmic metallization consists of Pd(500A)/Ge(1200A)/Ti(500A)/ Al(1000A) and the annealing was done in a N<sub>2</sub> atmosphere at 325°C for 2 minutes.

#### 4. Results and Discussions

We have measured both two terminal and three terminal DC I-V characteristics of the transistors for various values of base doping and extended barrier thicknesses, on the collector side. The doping in the base was varied from nominally undoped to 10<sup>19</sup> cm<sup>-3</sup> and the extended barrier thickness from 300Å - 800Å. Due to limitations of space we limit our discussions to qualitative features of the two terminal measurements. When a bias is applied between the emitter and collector terminals with the base terminal open, most devices exhibit diode behavior showing the characteristic negative differential resistance (NDR) feature. In general, the NDR feature is the strongest in devices with no doping in the base and gradually decreases with increased doping. Also, the NDR is more likely to be seen in a smaller area device on the same wafer. The weakening of the NDR feature with increased base doping may be a result of charge scattering with equilibrium electrons and ionized impurities in the base. The peak to valley ratios (PVR) are always small, the highest PVR measured being 1.8 at room temperature in a device with a base doping of  $10^{19} \text{cm}^{-3}$ .

The two-terminal I-V characteristics have also been studied as a function of extended barrier thickness. In our measurements the emitter is usually grounded and the collector side is biased. A positive voltage on the collector electrode is termed forward bias and a negative voltage is termed reverse bias. By looking at the device band diagram in Fig. 1, one tends to think intuitively that charge injection should be easier under positive bias. Surprisingly, the opposite is observed in our measurements implying easier charge injection from the collector side with a slight negative bias as evidenced by a rather quick current turn-on in the reverse direction. Also, the current turn-on in the reverse direction occurs at a smaller voltage with increasing extended barrier

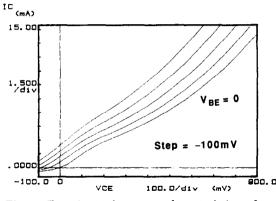

Fig. 5 Experimental output characteristics of the BSRTT for various values of  $V_{BE}$ .

thickness. Our recent theoretical calculations confirm this to be true.

Typical common-emitter characteristics of a BSRTT are shown in Fig. 5. The device structure in this case consisted of stepped barriers on either side of the DBQW structure. The emitter side extended barrier was doped to 10<sup>17</sup> cm<sup>-3</sup> to facilitate the formation of ohmic contact to the base region. About 200Å of this n-AlGaAs was removed chemically before the base contact was made. The output characteristics clearly show the modulation of collector current with changing bias across the emitter-base junction. We measured a maximum current gain of 3 and transconductance  $(g_m)$  of 30 mS. We believe that the performance can be significantly improved if the process parameters are fine tuned. As mentioned earlier we make use of the lateral etching of our selective reactive-ion-etch to achieve desired separation between the base contact and the emitter mesa to overcome Fermi pinning in the extrinsic base. Scanning electron microscope studies of the processed device revealed that this separation was about 0.7  $\mu$ m. much larger than the desired value of about 0.2  $\mu$ m. This also accounts partially for the observed lack of collector current saturation in Fig. 5. As discussed earlier the absence of collector current saturation is also predicted by our theoretical model although for very different reasons. The analysis indicates significant charge movement from the quantum base as a function of collector potential resulting in the suppression of the shielding property of the base. It is highly likely that both the theoretically predicted space-charge effects and fabrication related surface Fermi pinning are responsible for the observed lack of current saturation and relatively low gain.

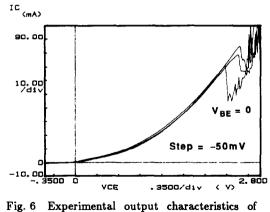

In order to explore these issues further we increased

the BSRTT showing negative differential resistance for large  $V_{CE}$ .

the collector voltage and observed the output characteristics under large bias. If the base were really shielding, one should not observe NDR features in the output curves. But, as can be seen in Fig. 6 strong NDR is seen in the output characteristics of these devices. These curves were obtained from a smaller area device. Although we observe NDR in larger area devices also, the effects were much weaker. This is not surprising since surface Fermi pinning is stronger in small area devices. This is also in agreement with our two-terminal measurements where we observed stronger NDR features in devices with lightly doped quantum wells and smaller areas. This indicates that bound-state equilibrium electron scattering may be a significant factor in electron scattering in the base.

### 5. Conclusions

By using selective reactive-ion-etching and selfaligned technology we have fabricated bound-state resonant tunneling transistors which show a finite current gain ( $\beta = 3$ ) and transconductances in excess of 30 mS. The collector currents do not saturate. This is in agreement with our self-consistent analysis of the device performance which shows that the bound state charge is inadequate for shielding the emitter from the collector side.

Acknowledgements – The authors would like to thank Professor P. K. Bhattacharya, Dr. Wieqi Li and Y. C. Chen for material growth and S. Brown and W. L. Chen for technical assistance. This work was supported by the Army Research Office under the URI program, Contract No. DAAL03-87-K-0007.

Superlattices and Microstructures, Vol. 7, No. 4, 1990

#### References

- 1. R. Tsu and L. Esaki, *Applied Physics Letters*, **22**, 562 (1973).

- E. R. Brown, T.C.L.G. Sollner, C. D. Parker, W. D. Goodhue and C. L. Chen, Applied Physics Letters, 55, 1777 (1989).

- L. M. Lunardi, S. Sen, F. Capasso, P. R. Smith, D. L. Sivco and A. Y. Cho, *IEEE Electron Device Letters*, 10, 201 (1989).

- F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik and A. Y. Cho, *IEEE Transactions on Electronic Devices*, 36, 2065 (1989).

- F. Capasso, K. Mohammed and A. Y. Cho, IEEE Journal of Quantum Electronics, QE-22, 1853 (1986).

- T. K. Woodward, T. C. McGill, R. D. Burhham and H. F. Chung, Superlattices and Microstructures, 4, 1 (1989).

- N. Yokoyama, K. Imamura, H. Ohnishi, T. Mori, S. Muto and A. Shibatoni, *Solid-State Electronics*, 31, (1988).

- G. I. Haddad, R. K. Mains, U. K. Reddy and J. R. East, Superlattices and Microstructures, 5, 437 (1989).

- 9. J. N. Schulman and M. Waldner, Journal of Applied Physics, 63, 2859 (1988).

- M. A. Reed, W. R. Frensley, R. J. Matyi, J. N. Randall and A. C. Seabaugh, Applied Physics Letters, 54, 1034 (1989).

- U. K. Reddy, I. Mehdi, R. K. Mains and G. I. Haddad, Solid-State Electronics, 32, 1377 (1989).

- R. K. Mains, J. P. Sun and G. I. Haddad, Applied Physics Letters, 55, 371 (1989).

- C. Kidner, I. Mehdi, J. R. East and G. I. Haddad, *IEEE Transactions on Microwave Theory and Techniques*, 38, 864 (1990).