# Research and Development Technical Report ECOM-0138-29-T

## Modeling and Analysis of Tuned Power Amplifiers

Technical Report No. 218

by

Ned E. Abbott

November 1971

#### DISTRIBUTION STATEMENT

ECOM

Distribution limited to U.S. Government agencies only; Test and Evaluation; 30 Aug 71 Other requests for this document must be referred to Commanding General, U.S. Army Electronics Command, ATTN: AMSEL-WL-S, Fort Monmouth, N. J. 07703

UNITED STATES ARMY ELECTRONICS COMMAND · FORT MONMOUTH, N.J. CONTRACT DAAB07-68-C-0138

COOLEY ELECTRONICS LABORATORY

Department of Electrical and Computer Engineering

The University of Michigan

Ann Arbor, Michigan 48105

#### NOTICES

#### Disclaimers

The findings in this report are not to be construed as an official Department of the Army position, unless so designated by other authorized documents.

The citation of trade names and names of manufacturers in this report is not to be construed as official Government indorsement or approval of commercial products or services referenced herein.

### Disposition

Destroy this report when it is no longer needed. Do not return it to the originator.

#### MODELING AND ANALYSIS OF TUNED POWER AMPLIFIERS

C.E.L. Technical Report No. 218

Contract No. DAAB07-68-C-0138

DA Project No. 1H021101 A042.01.02

Prepared by

Ned E. Abbott

#### COOLEY ELECTRONICS LABORATORY

Department of Electrical and Computer Engineering

The University of Michigan

Ann Arbor, Michigan

for

U. S. Army Electronics Command, Fort Monmouth, N. J.

#### DISTRIBUTION STATEMENT

Distribution limited to U.S. Government agencies only; Test and Evaluation; 30 Aug 7! Other requests for this document must be referred to Commanding General, U.S. Army Electronics Command, ATTN: AMSEL-WL-S, Fort Monmouth, N. J. 07703

THE UNIVERSITY OF MICHIGAN.

ENGINEERING..LIBRARY.

#### ABSTRACT

The desire to understand and describe the characteristics of tuned power amplifiers has stimulated the research summarized in this report. The principal objective of the research is to provide analytical methods for use in the design of transistorized class C VHF amplifiers. The analysis methods employed are numerical in nature allowing the removal of simplifying assumptions required by purely analytical methods.

Several transistor models compatible with digital computations are introduced to facilitate the study. Experimental techniques for establishing the parameter values for the models are also presented. Each of the model forms is used to study various aspects of class C/D amplifiers.

Basic amplifier characteristics such as output power and efficiency dependencies on frequency, load resistance, supply voltage, nonlinear capacitance, and tuning configuration are investigated with a simple ideal switch representation of a transistor. An intrinsic voltage controlled transistor model and an extended voltage controlled model are used to study several large signal amplifiers. For purposes of comparison these amplifiers are also constructed and investigated experimentally. The intrinsic transistor model is found to provide moderate simulation accuracy for class C amplifiers in which the

ranges of signal swing, load impedance, and supply voltages are limited. For accurate simulations of high frequency, large signal amplifiers over wide ranges of operating conditions a more complete device description such as the extended model is required.

### FOREWORD

This report was prepared by the Cooley Electronics Laboratory of The University of Michigan under United States Army

Electronics Command Contract No. DAAB07-68-C-0138, "Countermeasures Research."

### TABLE OF CONTENTS

|         |                 |                           |                                         | Page     |

|---------|-----------------|---------------------------|-----------------------------------------|----------|

| ABSTRA  | .CT             |                           |                                         | iii      |

| EODEUM  | <b>7DD</b>      |                           |                                         |          |

| FOREW   | JKD             |                           |                                         | <b>v</b> |

| LIST OF | ILLUS           | TRATION                   | NS                                      | X        |

| LIST OF | TABL            | ES                        |                                         | xx       |

| СНАРТЕ  | R 1:            | INTROD                    | UCTION                                  | 1        |

|         | Purpo<br>Staten | se<br>nent of Pr          | oblem                                   | 1<br>5   |

| СНАРТЕ  | SR 2:           | MODEL                     | ING                                     | 12       |

| 2.1     | Introd          | uction                    |                                         | 12       |

| 2.2     | Introd          | uction of                 | Model                                   | 12       |

| 2.3     | Deteri          | mination o                | of Model Parameters                     | 16       |

|         | 2.3.1           | $\alpha_{\mathbf{F}}$ and | $\alpha_{\mathbf{D}}$ From Curve Tracer |          |

|         |                 | Measure                   | $lpha_{f R}$ From Curve Tracer ements   | 17       |

|         |                 |                           | Parameters Determined with              |          |

|         |                 |                           | ransient Measurements                   | 19       |

|         | 2.3.3           | $\lambda$ , $Q_{EC}$ ,    | and $Q_{\mathbf{RS}}$ from DC Behavior  |          |

|         |                 | of Juncti                 |                                         | 24       |

| 2.4     | Numei           | _                         | iculty with Charge Controlled           |          |

|         | Model           |                           | ,                                       | 27       |

|         |                 |                           | al Approximation with Shunt             |          |

|         |                 | Resistan                  |                                         | 28       |

|         | 2.4.2           | Numeric                   | al Approximation with Shunt             |          |

|         |                 | Capacita                  |                                         | 30       |

|         | 2.4.3           | -                         | rmation to Voltage-Control Mod          |          |

| 2.5     |                 |                           | ge Controlled Transistor Model          |          |

|         |                 | -                         | apacitances                             | 36       |

| -       |                 |                           | Package Capacitances                    | 37       |

|         |                 |                           | Diffusion and Depletion                 |          |

|         |                 |                           | Capacitances                            | 40       |

|         |                 | 2.5.1.3                   | Limiting of Depletion                   |          |

|         |                 |                           | Capacitances                            | 40       |

|         |                 | 2.5.1.4                   | Determination of Depletion              |          |

|         |                 |                           | Canacitance Parameters                  | 42       |

### TABLE OF CONTENTS (Cont.)

|          |                                                         | Page      |

|----------|---------------------------------------------------------|-----------|

|          | 2.5.2 Emitter-Base Avalanche Description                | 48        |

|          | 2.5.3 Extrinsic Resistances                             | 51        |

|          | 2.5.3.1 Initial Estimates of $R_{BB}$ and $R_{EE}$      | <b>51</b> |

|          | 2.5.3.2 Initial Estimates of $R_{CC}^{BB}$ and $R_{EE}$ | 53        |

|          | 2.5.3.3 Saturated Resistance Measurements               | 54        |

|          | 2.5.3.4 Experimental Observation of                     |           |

|          | Saturation Characteristics                              | 57        |

|          | 2.5.3.5 Effective Resistances Under                     |           |

|          | Transient Conditions                                    | 62        |

|          | 2.5.3.6 Validation of Multi-Lump Model                  |           |

|          | Transient Behavior                                      | 70        |

|          | 2.5.3.7 Selecting Equivalent Resistance                 |           |

|          | Values for Single Lump Models                           | 74        |

|          | 2.5.4 Emitter Lead Inductance                           | 76        |

|          |                                                         |           |

| СНАРТ    | ER 3: ANALYSES WITH IDEAL SWITCH MODEL                  | 80        |

|          |                                                         | 0.0       |

|          | Introduction                                            | 80        |

| 3.2      | Numerical Analysis With Ideal Switch and Fixed          | 85        |

|          | Capacitance                                             | 87        |

|          | 3.2.1 Effect of Switching Period                        |           |

|          | 3.2.2 Effect of Load Resistance                         | 87        |

|          | 3.2.3 Effect of Switch Conduction Angle                 | 89        |

|          | 3.2.4 Effect of Circuit Capacitance                     | 107       |

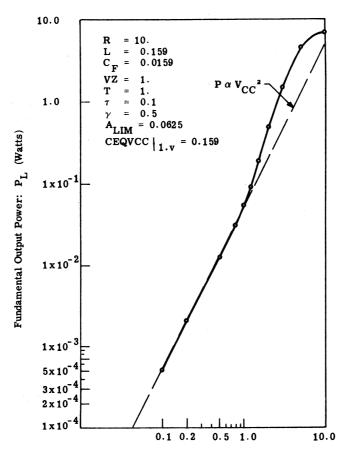

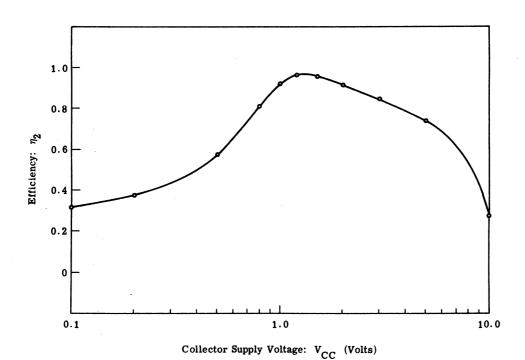

|          | 3.2.5 Effect of Supply Voltage                          | 107       |

|          | Ideal Switch with Nonlinear Capacitance                 | 108       |

|          | Series RL Tuning                                        | 117       |

| 3.5      | 6 Harmonic Tuning                                       | 123       |

| OII A DT | ER 4: CLASS C AMPLIFIER WITH INTRINSIC                  |           |

| CHAPI    | TRANSISTOR MODEL                                        | 131       |

|          |                                                         |           |

| 4.1      | Introduction                                            | 131       |

|          | 2 Computed Behavior of Low Frequency Amplifier          | 131       |

|          | 4.2.1 Numerical Difficulties With Voltage-              |           |

|          | Control Model                                           | 134       |

|          | 4.2.2 Results of Computer Analysis With                 |           |

|          | Voltage-Control Model                                   | 136       |

### TABLE OF CONTENTS (Cont.)

|        |                                                                                                                                                                               | Page              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|        | Experimental Verification of Computer Analysis Experimental 100 MHz Class C Amplifier 4.4.1 Effect of Collector Supply Voltage 4.4.2 Effects of Load Resistance and Period of | 139<br>139<br>142 |

|        | Driving Source                                                                                                                                                                | 145               |

| 4.5    | Computer Analysis of 100 MHz Class C Amplifier                                                                                                                                | 148               |

| 4.6    | Comparisons and Conclusions                                                                                                                                                   | 150               |

| СНАРТЕ | CR 5: CLASS C AMPLIFIER ANALYSIS WITH                                                                                                                                         |                   |

|        | EXTENDED TRANSISTOR MODEL                                                                                                                                                     | 153               |

|        | Introduction                                                                                                                                                                  | 153               |

|        | Experimental Amplifier Amplifier Analysis with Extended Transistor                                                                                                            | 154               |

| 0.0    | Model                                                                                                                                                                         | 154               |

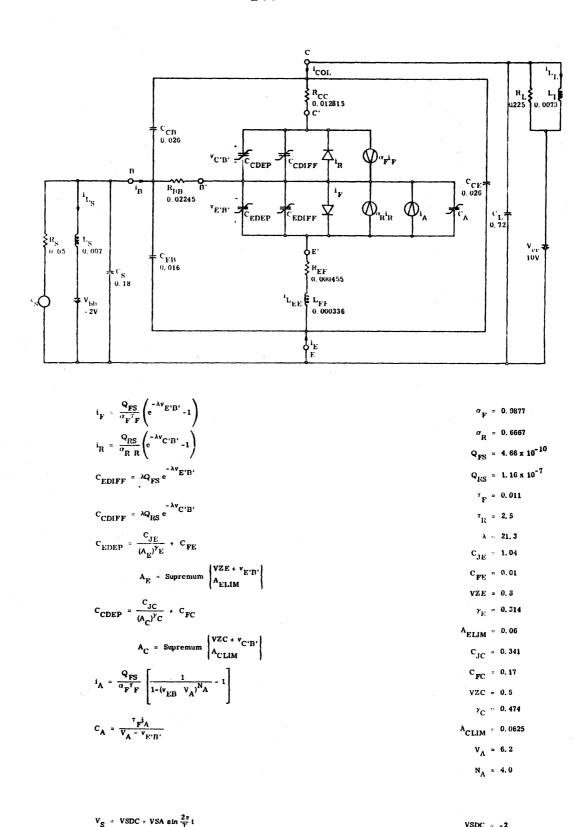

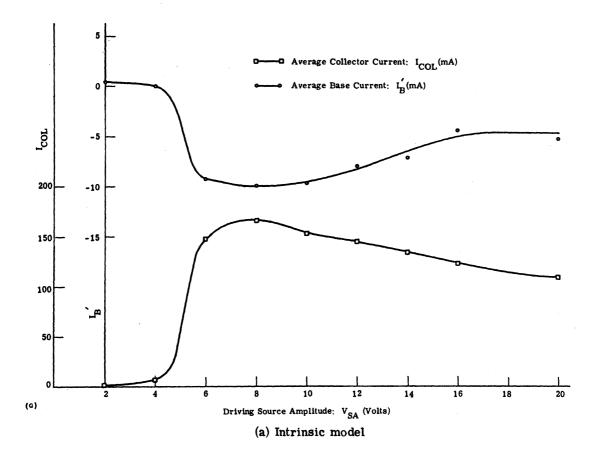

|        | 5.3.1 Effects of Signal Source Amplitude                                                                                                                                      | 165               |

|        | 5.3.2 Computed Performance                                                                                                                                                    | 167               |

| 5.4    | Amplifier Sensitivities                                                                                                                                                       | 175               |

|        | Conclusions                                                                                                                                                                   | 179               |

| CUADTE | R 6: COMPARISON OF AMPLIFIER                                                                                                                                                  |                   |

| CHAPTE | REPRESENTATIONS                                                                                                                                                               | 180               |

| 6.1    | Introduction                                                                                                                                                                  | 180               |

| 6.2    | Waveform Comparisons                                                                                                                                                          | 186               |

| 6.3    | Frequency Response Comparisons                                                                                                                                                | 192               |

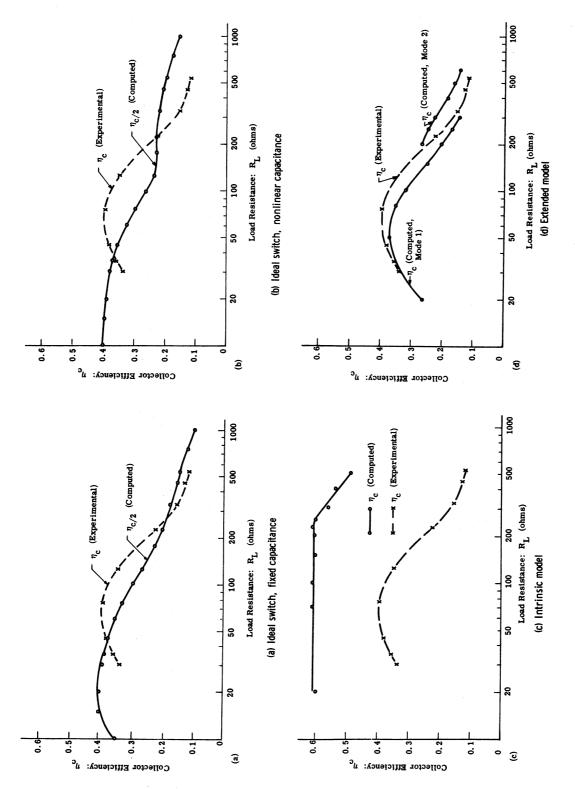

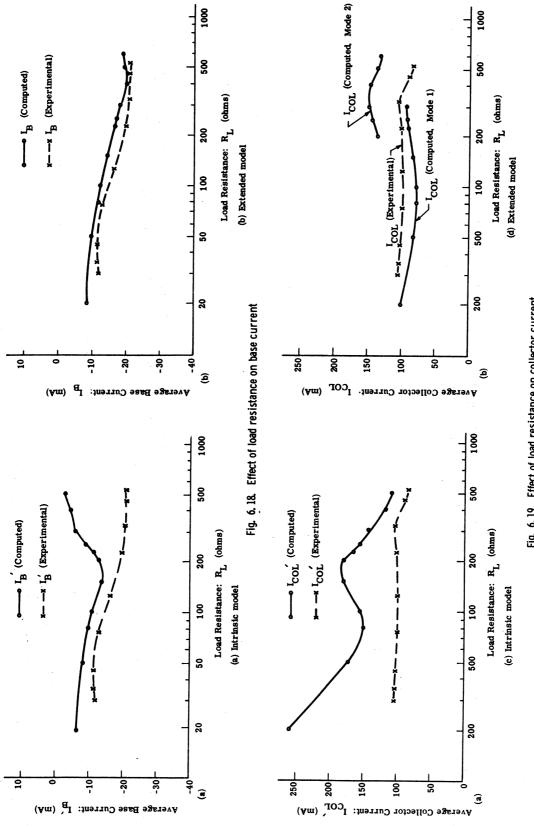

| 6.4    | Comparisons of Load Resistance Effects                                                                                                                                        | 196               |

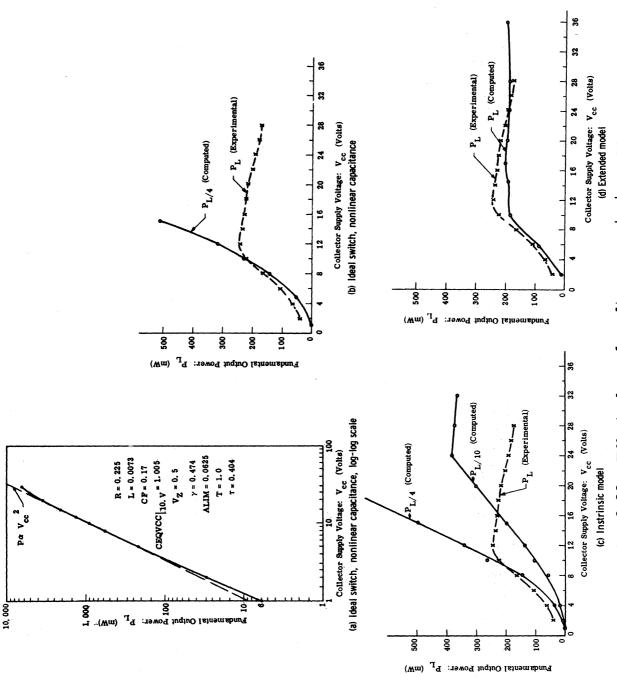

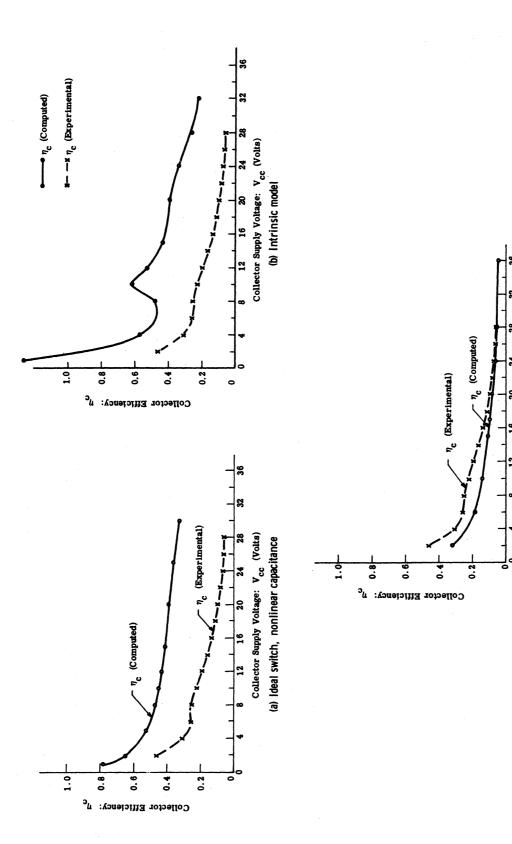

| 6.5    | Comparisons of Supply Voltage Effects                                                                                                                                         | 201               |

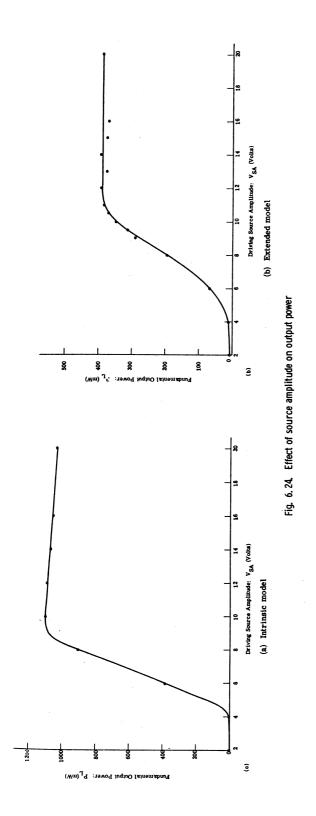

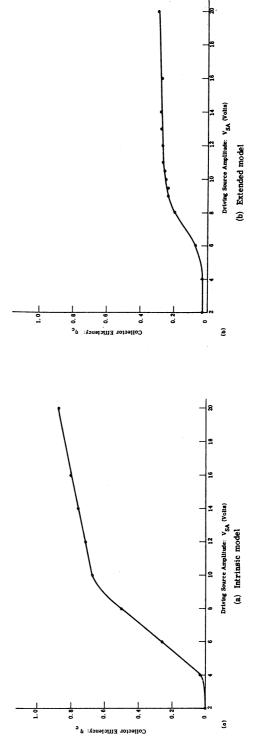

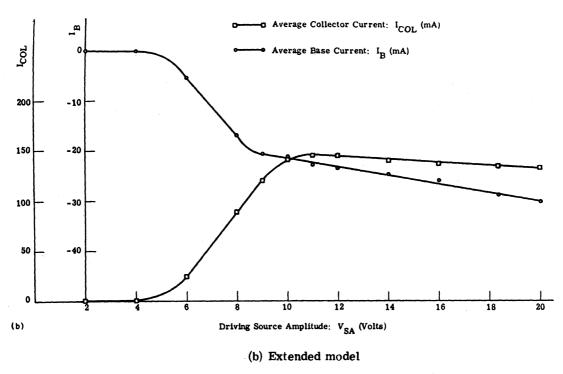

| 6.6    | Computed Effects of Signal Amplitude                                                                                                                                          | 205               |

| 6.7    | Conclusions                                                                                                                                                                   | 205               |

| СНАРТЕ | D 7. DEVIEW CHCCECTIONS AND                                                                                                                                                   |                   |

| CHAPIE | R 7: REVIEW, SUGGESTIONS, AND CONCLUSIONS                                                                                                                                     | 210               |

| 7.1    | Introduction                                                                                                                                                                  | 210               |

|        | Summary of Models                                                                                                                                                             | 211               |

|        | 7.2.1 Ideal Switch Models                                                                                                                                                     | 211               |

### TABLE OF CONTENTS (Cont.)

|                                                           | Page |

|-----------------------------------------------------------|------|

| 7.2.2 Intrinsic Voltage Controlled Transistor Model       | 213  |

| 7.2.3 Extended Voltage Controlled Transistor              |      |

| Model                                                     | 215  |

| 7.3 Computational Costs                                   | 219  |

| 7.4 Improvement to Ideal Switch Models                    | 224  |

| 7.5 Improvements to Intrinsic Model                       | 225  |

| 7.6 Improvements to Extended Model                        | 225  |

| 7.7 Amplifier and Device Optimization                     | 230  |

| 7.8 Conclusions                                           | 232  |

| APPENDIX A: EXPERIMENTAL MEASUREMENT OF CHARGE PARAMETERS | 233  |

| APPENDIX B: TRANSFORMATION FROM CHARGE                    |      |

| CONTROL TO VOLTAGE CONTROL                                | 243  |

| APPENDIX C: ALGORITHM FOR CLASS C AMPLIFIER ANALYSIS      | 246  |

| BIBLIOGRAPHY                                              | 267  |

| Dibliodimi III                                            | 201  |

| DISTRIBUTION LIST                                         | 273  |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                 | Page |

|--------|-------------------------------------------------------|------|

| 1.1    | Circuit configuration for tuned power amplifier       | 6    |

| 1.2    | Progression of device and circuit models              | 8    |

| 2.1    | Intrinsic charge-controlled model of NPN transistor   | 15   |

| 2.2    | Forward current gain                                  | 18   |

| 2.3    | Inverse current gain                                  | 18   |

| 2.4    | Effect of junction potential on forward gain          | 18   |

| 2.5    | Effect of junction potential on inverse gain          | 18   |

| 2.6    | Charge storage measurement                            | 20   |

| 2.7    | Forward charge storage                                | 23   |

| 2.8    | Inverse charge storage                                | 23   |

| 2.9    | Static behavior of junctions                          | 26   |

| 2.10   | Diode with shunt resistance to avoid numerical limit  | 29   |

| 2.11   | Diode with shunt capacitance to avoid numerical limit | 31   |

| 2.12   | Intrinsic voltage controlled model of NPN transistor  | 33   |

| 2.13   | Extended voltage controlled model of NPN transistor   | 35   |

| 2.14   | Components of emitter-base capacitance of 2N3866      | 38   |

| 2.15   | Components of collector-base capacitance of 2N3866    | 39   |

| Figure | Title                                                                                                                                                                | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.16   | Collector-base depletion and case capacitance                                                                                                                        | 44   |

| 2.17   | Emitter-base depletion and case capacitance                                                                                                                          | 44   |

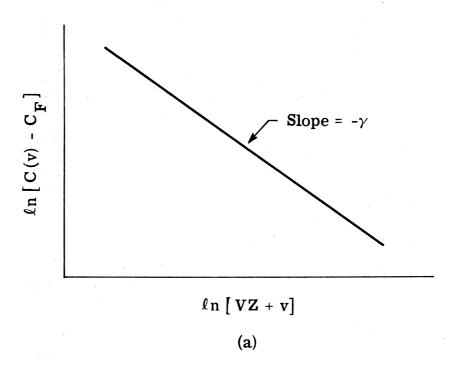

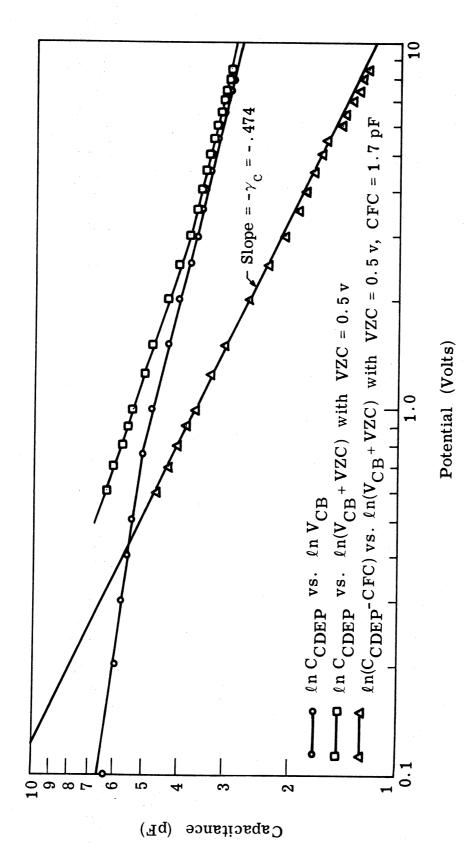

| 2.18   | Logarithmic C-v behavior                                                                                                                                             | 45   |

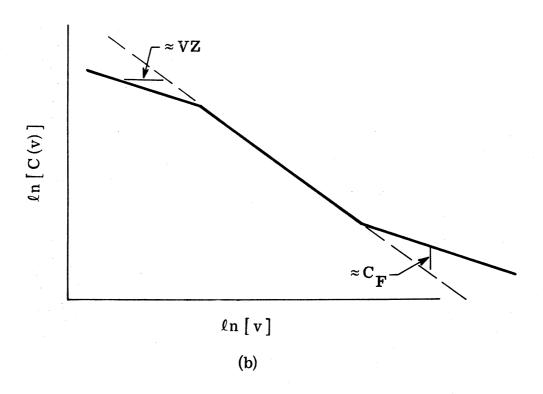

| 2.19   | Graphical determination of collector depletion capacitance parameters                                                                                                | 47   |

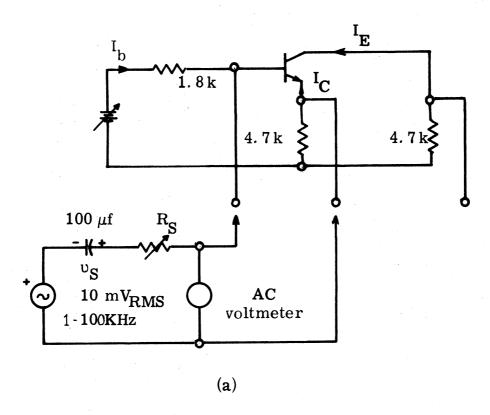

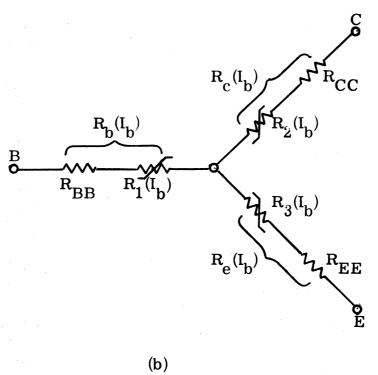

| 2.20   | <ul><li>(a) Measurement circuit - low frequency saturated resistance</li><li>(b) Y connection representation of saturated transistor small signal behavior</li></ul> | 55   |

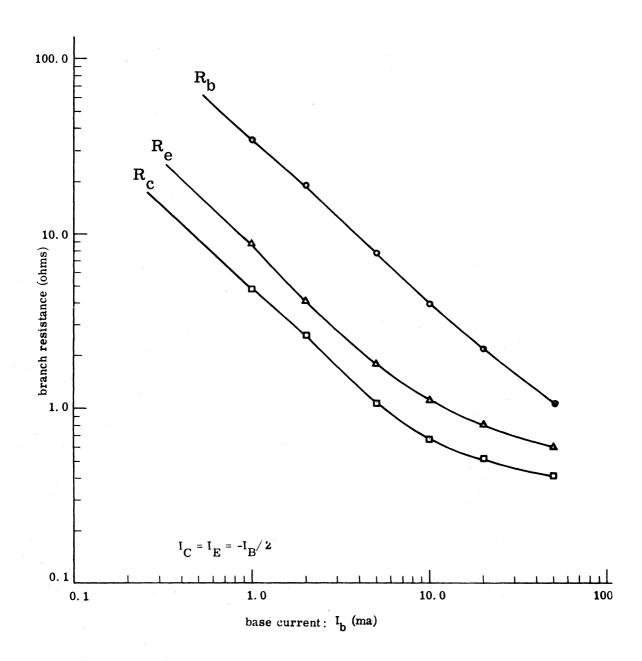

| 2.21   | Low frequency saturated resistance measurements                                                                                                                      | 56   |

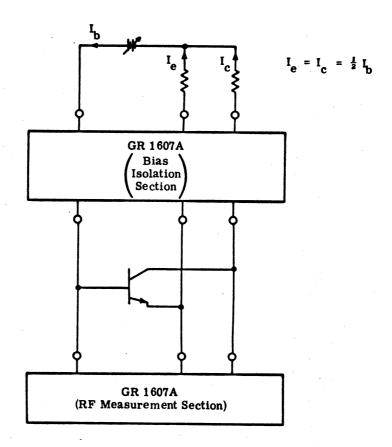

| 2.22   | Measurement circuit for VHF saturated impedances                                                                                                                     | 58   |

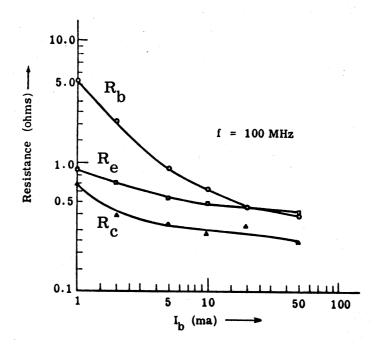

| 2.23   | Real parts of VHF saturated impedances                                                                                                                               | 58   |

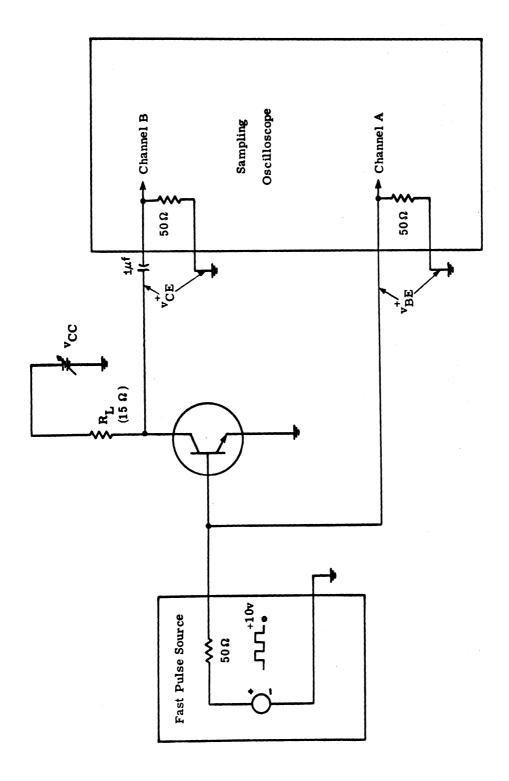

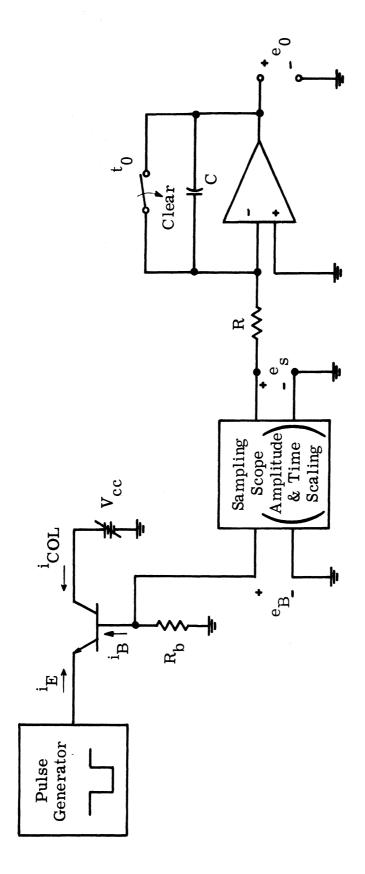

| 2.24   | Switching test circuit                                                                                                                                               | 60   |

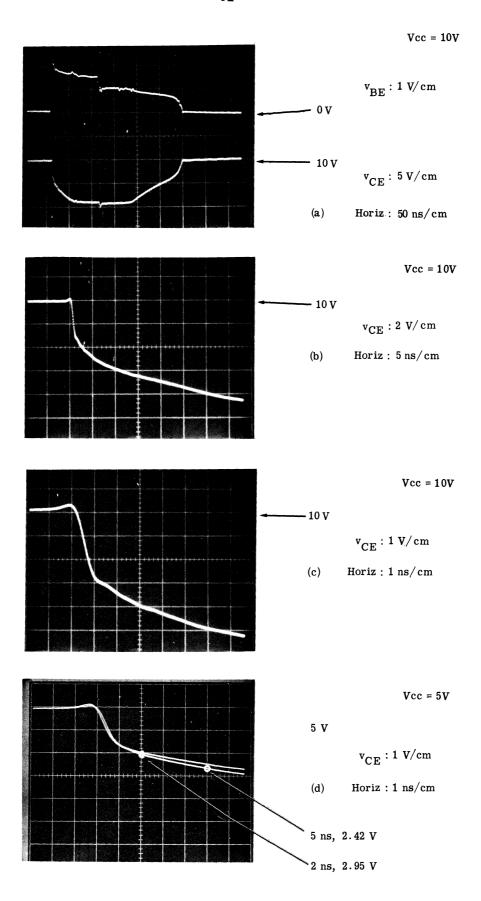

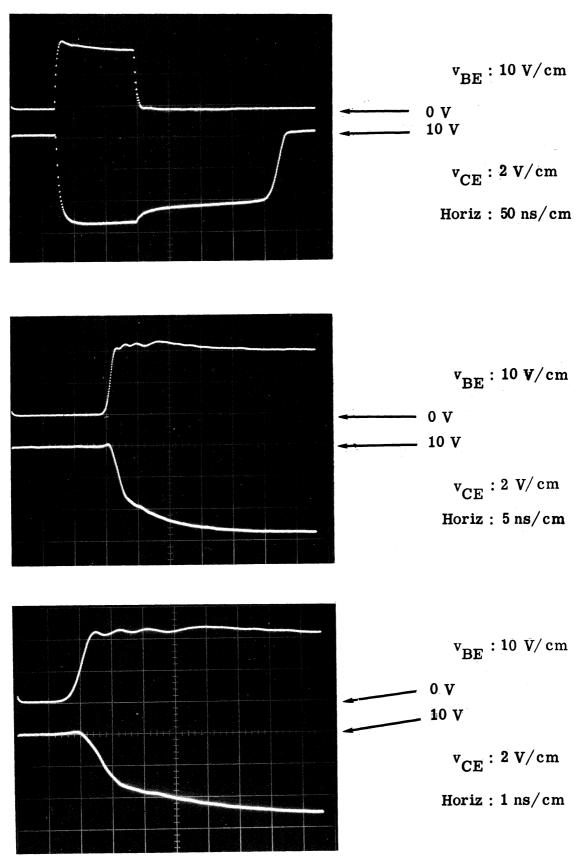

| 2.25   | Turn-on characteristics of 2N3866                                                                                                                                    | 61   |

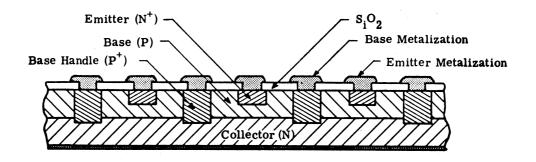

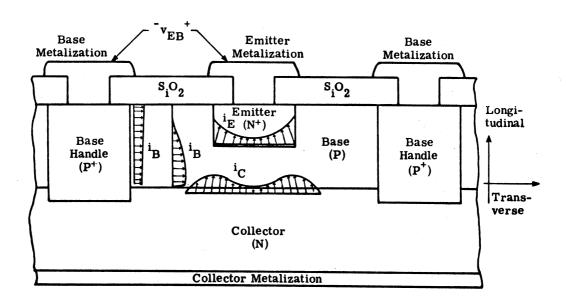

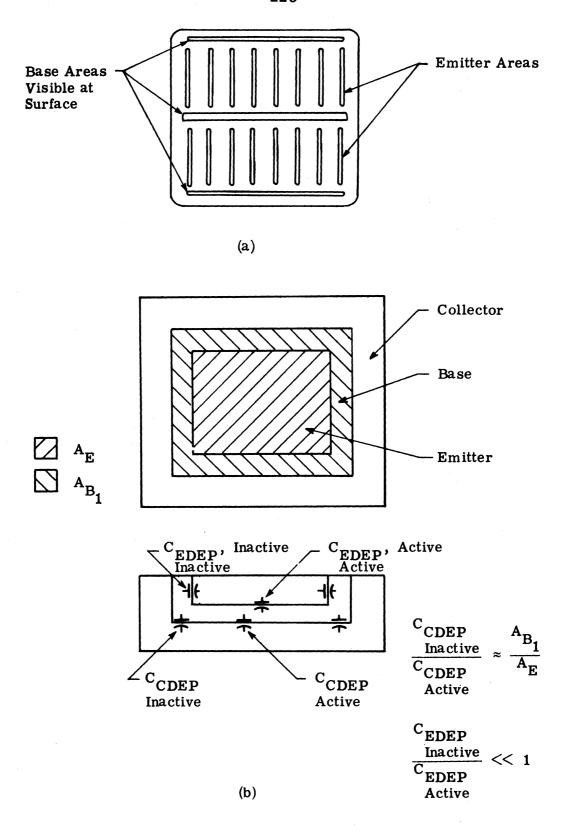

| 2.26   | (a) Cross sectional view of overlay transistor                                                                                                                       |      |

|        | structure<br>(b) Expanded view of overlay transistor                                                                                                                 | 64   |

| 2.27   | Lumped equivalent transistor model                                                                                                                                   | 65   |

| 2.28   | Total 2N3866 representation                                                                                                                                          | 68   |

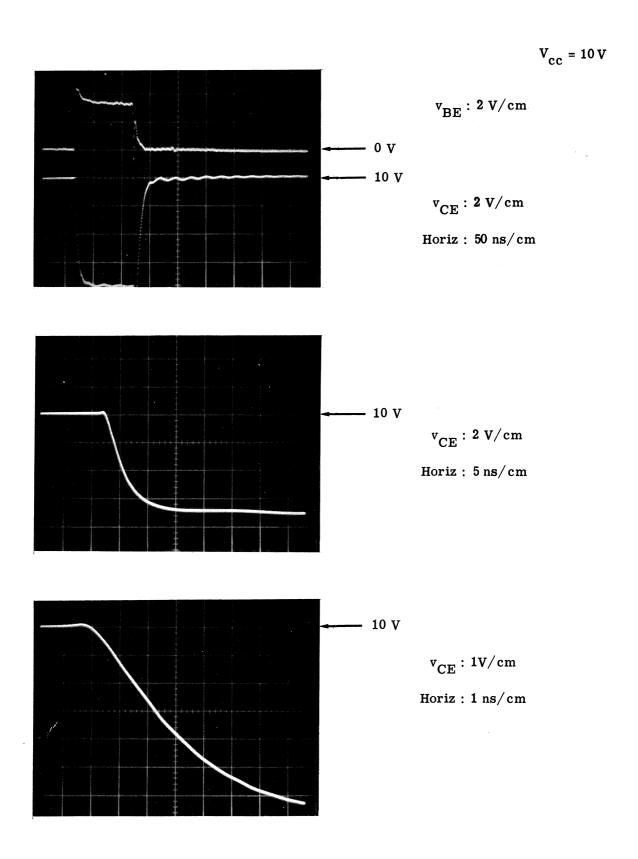

| 2.29   | Turn-on characteristics of 2N918                                                                                                                                     | 71   |

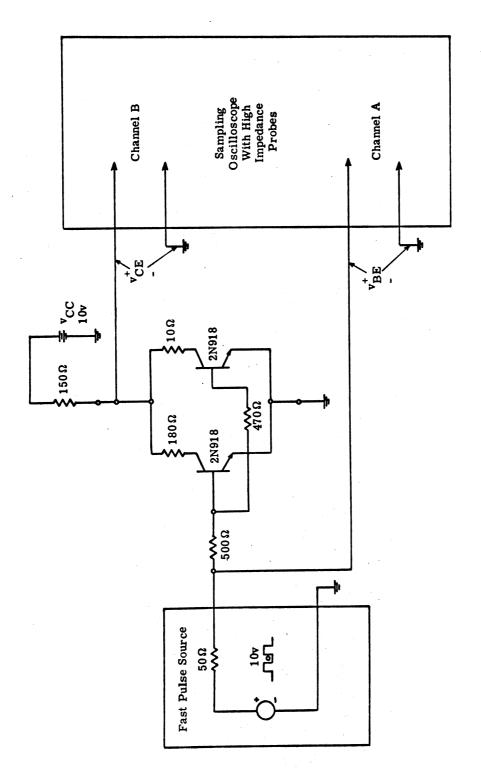

| 2.30   | Two-lump equivalent circuit using 2N918 transistors                                                                                                                  | 72   |

| 2.31   | Turn-on characteristics of two-lump equivalent                                                                                                                       | 73   |

| Figure | Title                                                                               | Page |

|--------|-------------------------------------------------------------------------------------|------|

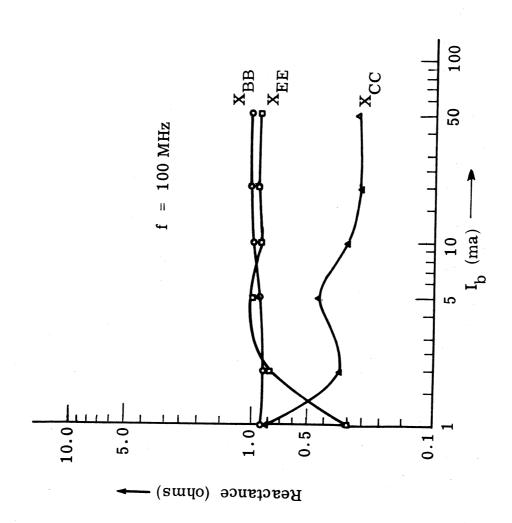

| 2.32   | Reactive parts of VHF saturated impedances                                          | 78   |

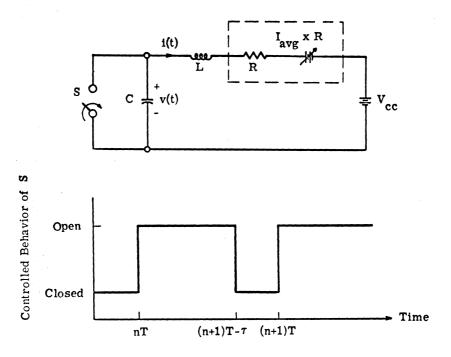

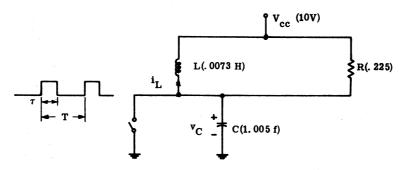

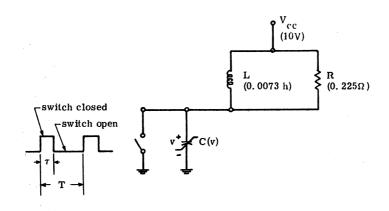

| 3.1    | Idealized class C circuit                                                           | 82   |

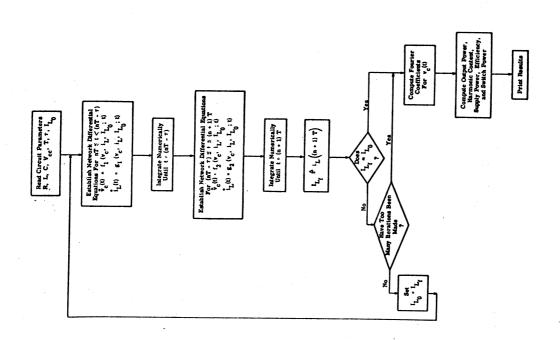

| 3.2    | Flow chart illustrating analysis of ideal switch circuit                            | 86   |

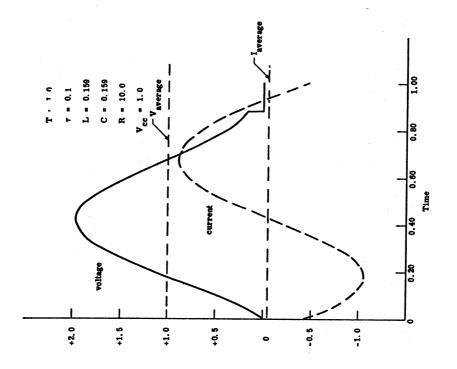

| 3.3    | Output voltage and inductor current waveforms                                       | 86   |

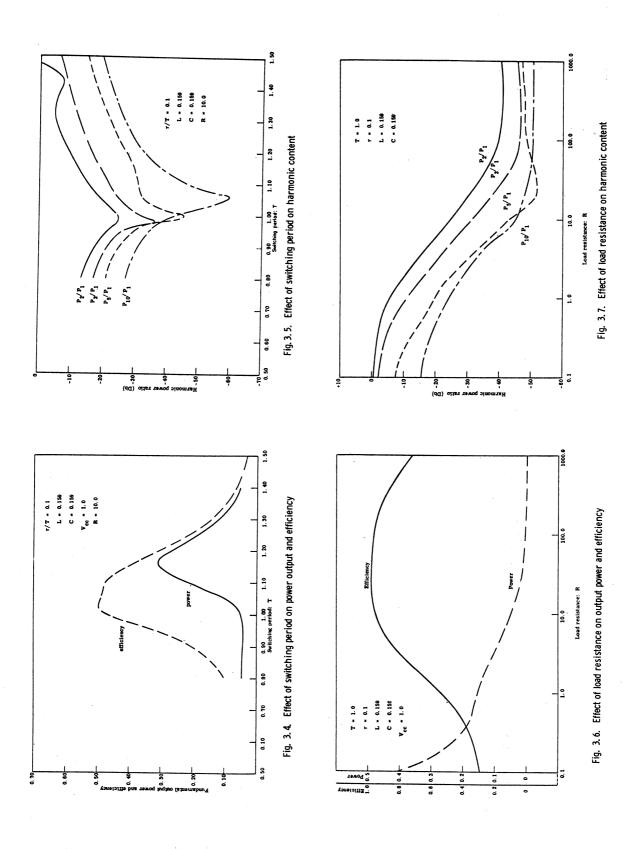

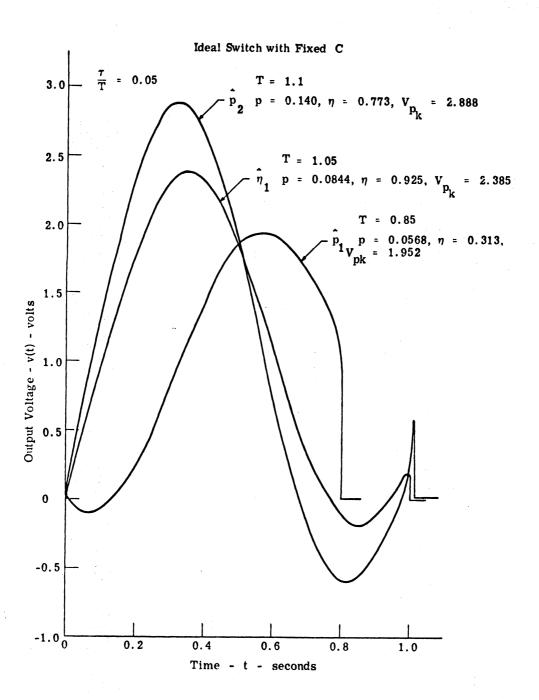

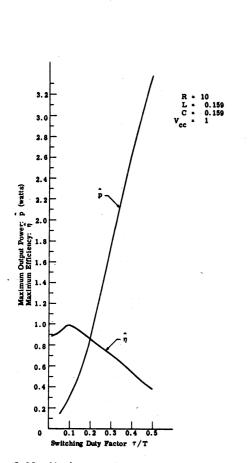

| 3.4    | Effect of switching period on power output and efficiency                           | 88   |

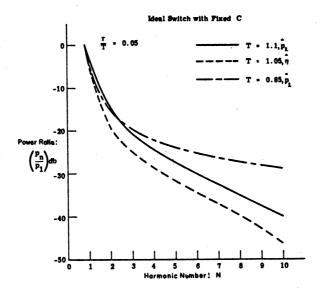

| 3.5    | Effect of switching period on harmonic content                                      | 88   |

| 3.6    | Effect of load resistance on output power and efficiency                            | 88   |

| 3.7    | Effect of load resistance on harmonic content                                       | 88   |

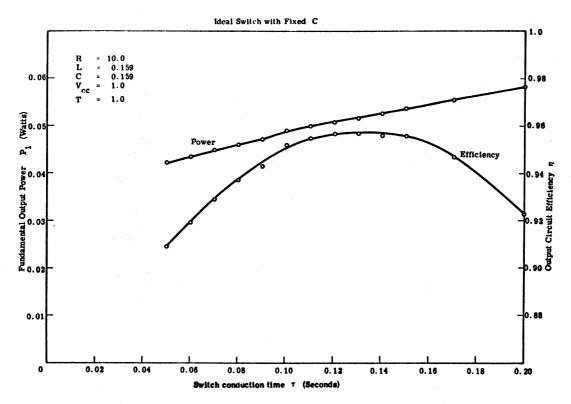

| 3.8    | Influence of switch conduction time on output power and efficiency                  | 91   |

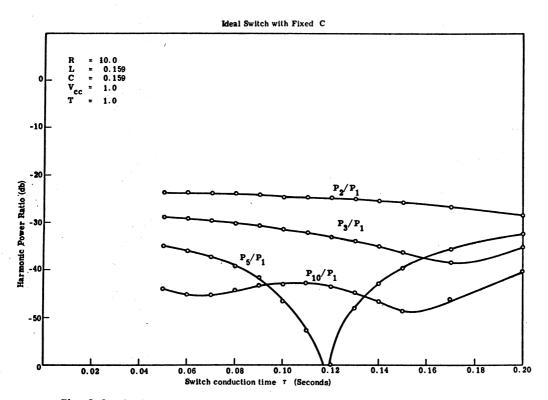

| 3.9    | Influence of switch conduction time on harmonic content                             | 91   |

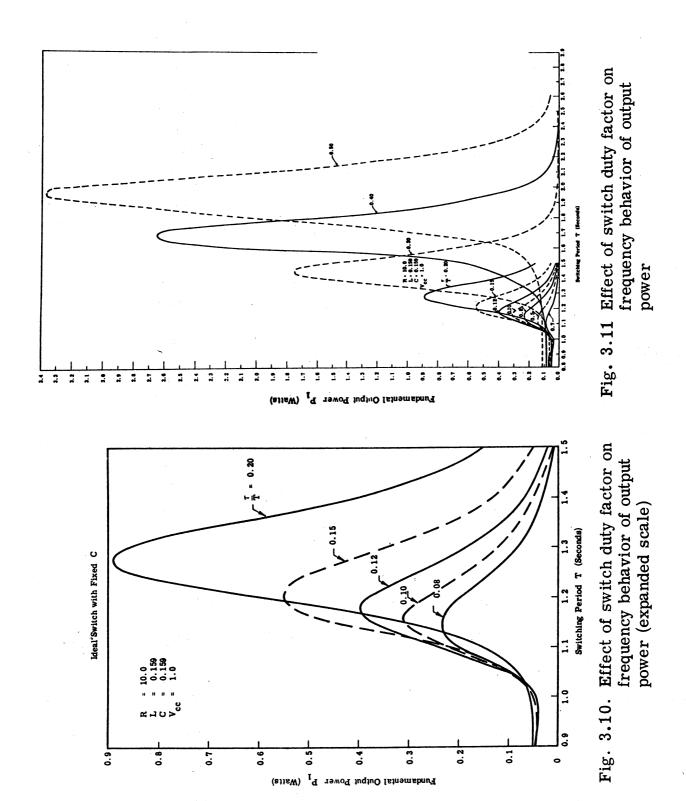

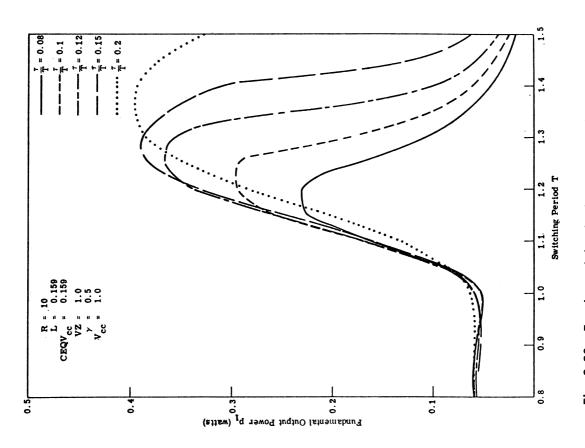

| 3.10   | Effect of switch duty factor on frequency behavior of output power (expanded scale) | 93   |

| 3.11   | Effect of switch duty factor on frequency behavior of output power                  | 93   |

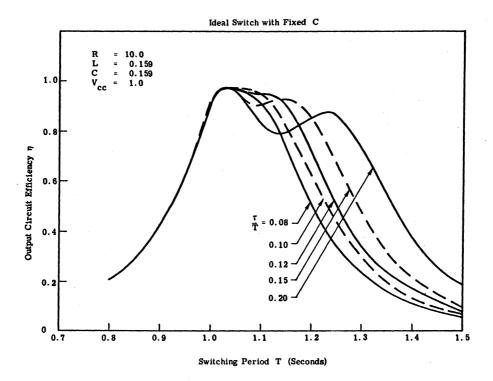

| 3.12   | Effect of switch duty factor on frequency behavior of efficiency (expanded scale)   | 94   |

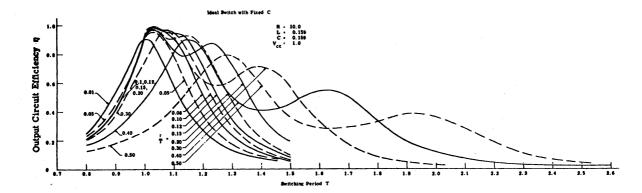

| 3.13   | Effect of switch duty factor on frequency behavior of efficiency                    | 94   |

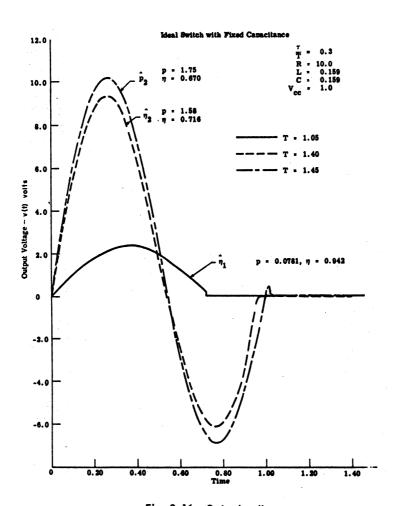

| 3.14   | Output voltage                                                                      | 97   |

| 3.15   | Harmonic content                                                                    | 99   |

| 3.16   | Output voltage                                                                      | 99   |

| Figure | Title                                                                          | Page |

|--------|--------------------------------------------------------------------------------|------|

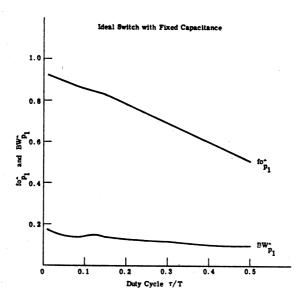

| 3.17   | Center frequency and bandwidth                                                 | 101  |

| 3.18   | Maximum output power and maximum efficiency vs switching duty factor           | 101  |

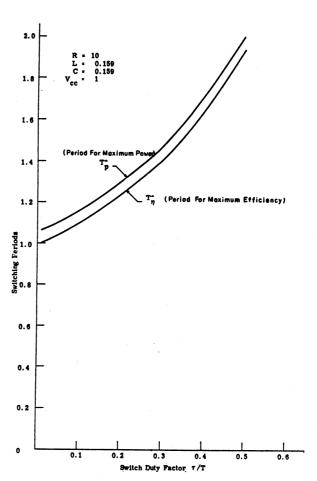

| 3.19   | Switching periods for maximum power and maximum efficiency                     | 101  |

| 3.20   | Scaled output power                                                            | 106  |

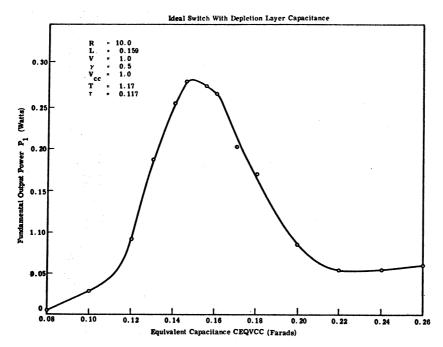

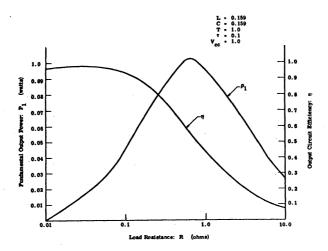

| 3.21   | Selection of nominal value for CEQVCC                                          | 111  |

| 3.22   | Response of nonlinear circuit                                                  | 111  |

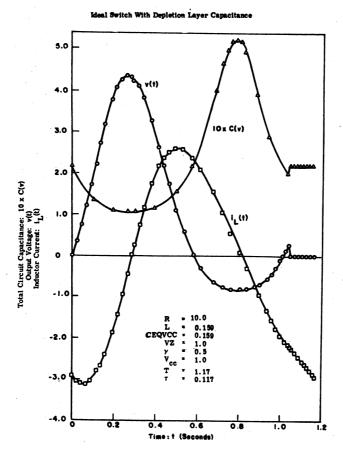

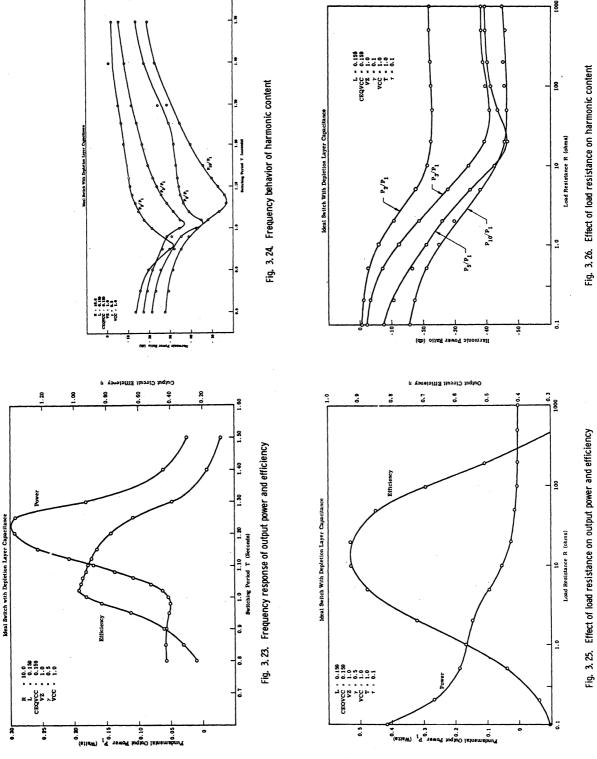

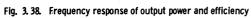

| 3.23   | Frequency response of output power and efficiency                              | 112  |

| 3.24   | Frequency behavior of harmonic content                                         | 112  |

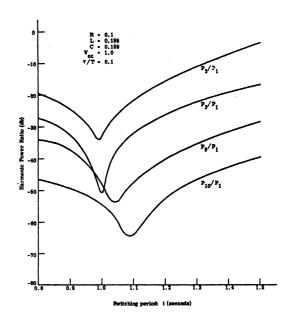

| 3.25   | Effect of load resistance on output power and efficiency                       | 112  |

| 3.26   | Effect of load resistance on harmonic content                                  | 112  |

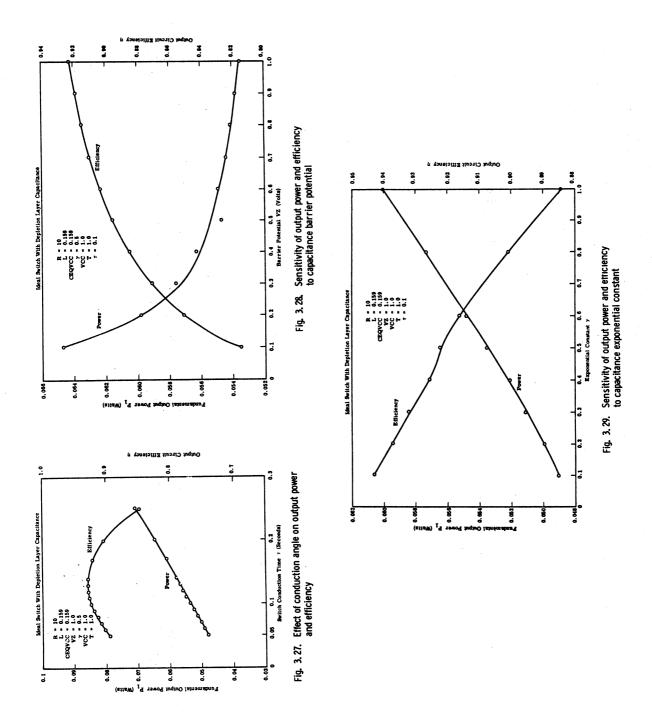

| 3.27   | Effect of conduction angle on output power and efficiency                      | 113  |

| 3.28   | Sensitivity of output power and efficiency to capacitance barrier potential    | 113  |

| 3.29   | Sensitivity of output power and efficiency to capacitance exponential constant | 113  |

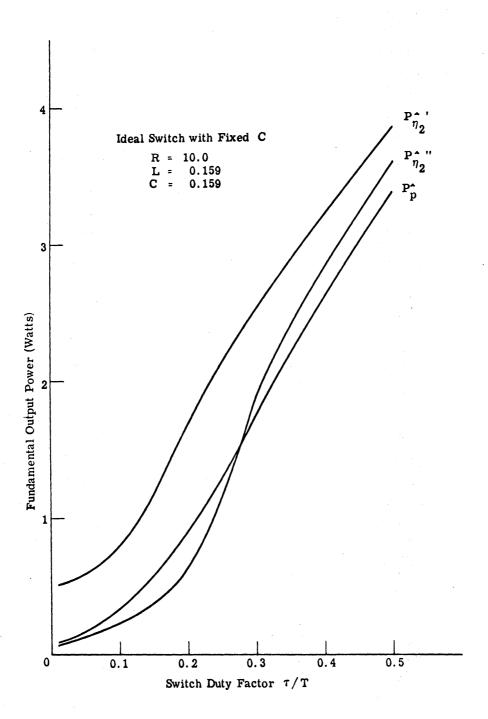

| 3.30   | Fundamental output power vs switching period                                   | 114  |

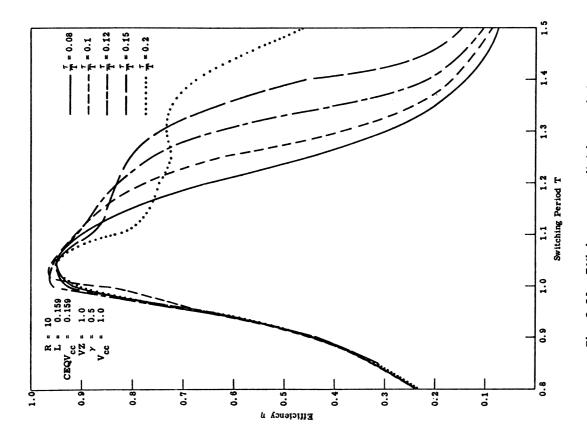

| 3.31   | Efficiency vs switching period                                                 | 114  |

| 3.32   | Effect of supply voltage on output power                                       | 115  |

| 3.33   | Effect of supply voltage on efficiency                                         | 115  |

| Figure | Title                                                                      | Page |

|--------|----------------------------------------------------------------------------|------|

| 3.34   | Classical forms of output matching circuits                                | 118  |

| 3.35   | Idealized output circuit                                                   | 119  |

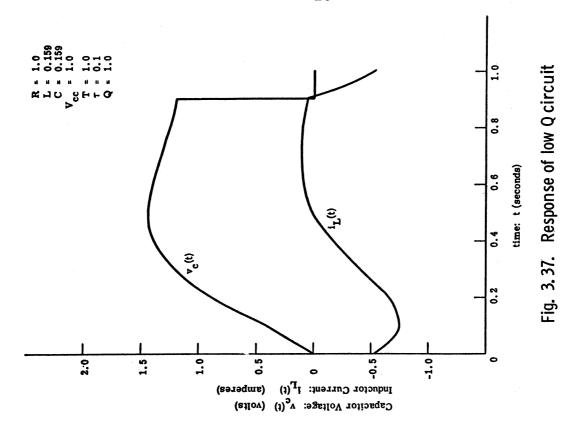

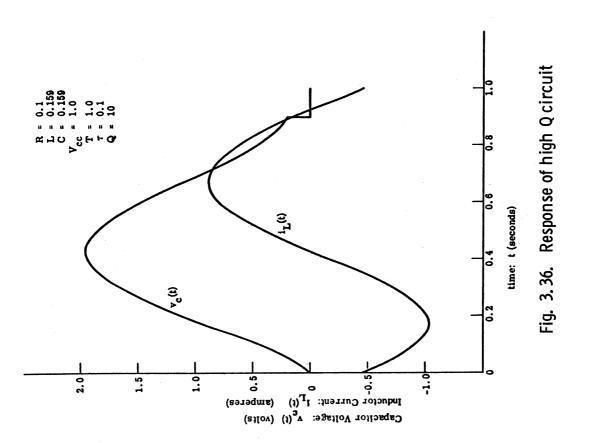

| 3.36   | Response of high Q circuit                                                 | 120  |

| 3.37   | Response of low Q circuit                                                  | 120  |

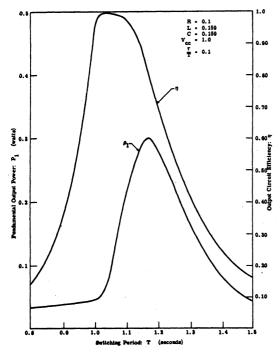

| 3.38   | Frequency response of output power and efficiency                          | 122  |

| 3.39   | Frequency behavior of harmonic content                                     | 122  |

| 3.40   | Effect of load resistance on output power and efficiency                   | 122  |

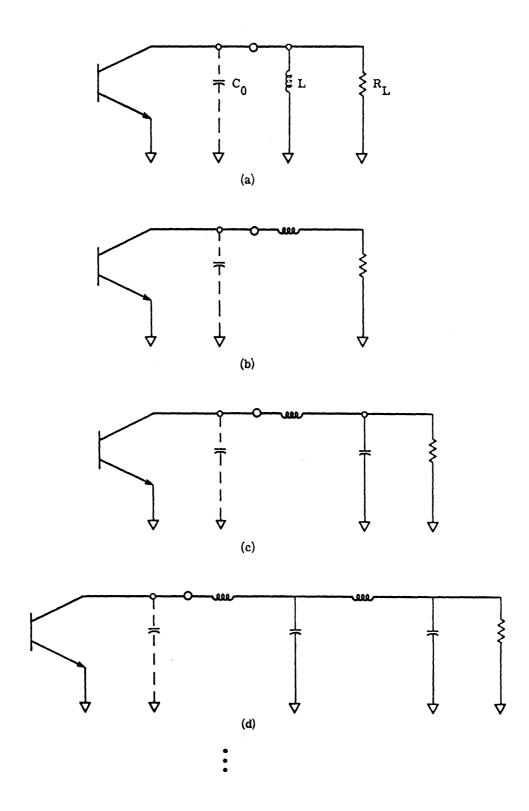

| 3.41   | Equivalent amplifier with harmonic tuning                                  | 125  |

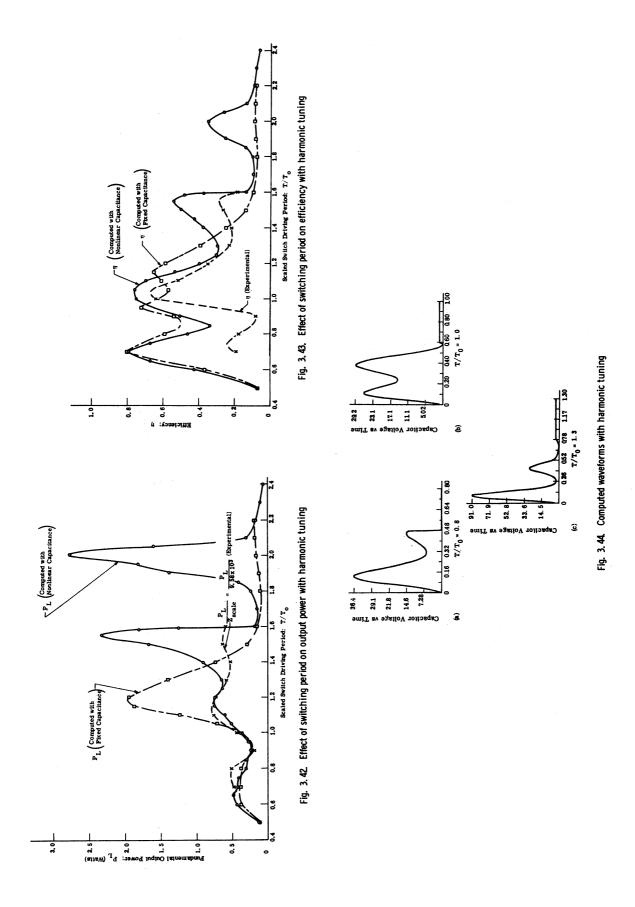

| 3.42   | Effect of switching period on output power with harmonic tuning            | 127  |

| 3.43   | Effect of switching period on efficiency with harmonic tuning              | 127  |

| 3.44   | Computed waveforms with harmonic tuning                                    | 127  |

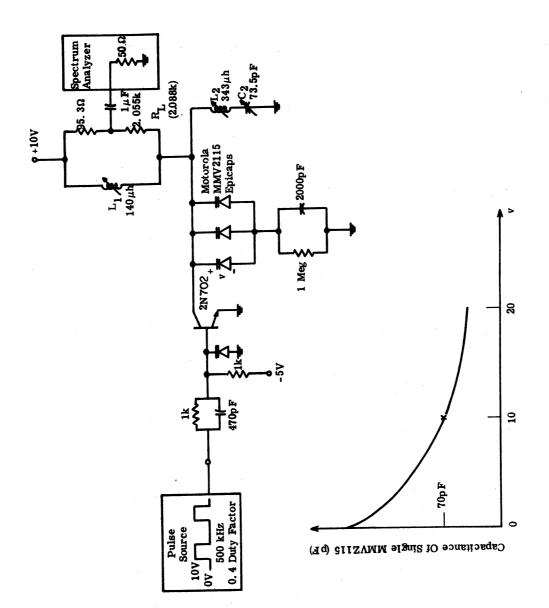

| 3.45   | Experimental amplifier with harmonic tuning                                | 129  |

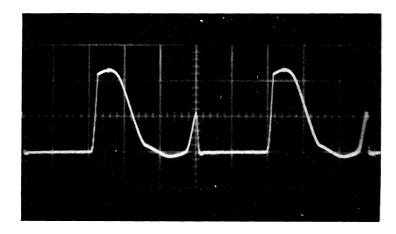

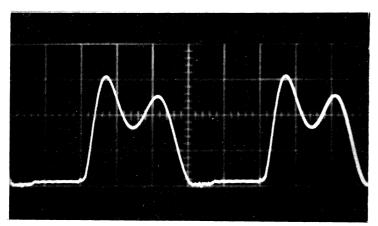

| 3.46   | Experimental collector-emitter voltage wave-<br>forms with harmonic tuning | 130  |

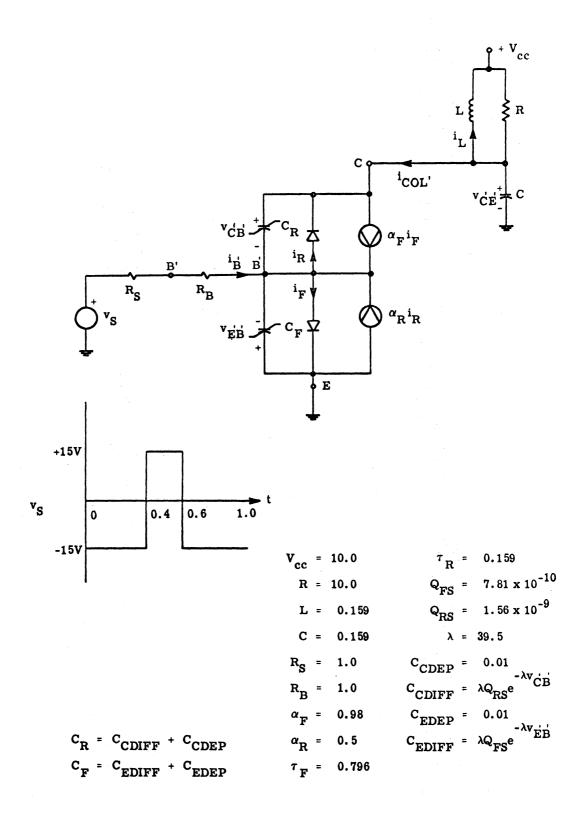

| 4.1    | Amplifier circuit with voltage-controlled model                            | 132  |

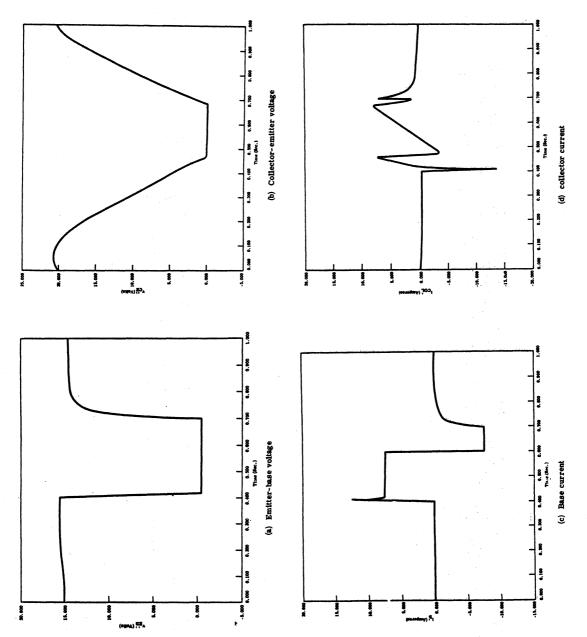

| 4.2    | Waveforms from amplifier analysis                                          | 138  |

| 4.3    | Low-frequency amplifier                                                    | 140  |

| Figure | Title                                                         | Page |

|--------|---------------------------------------------------------------|------|

| 4.4    | Behavior of low-frequency amplifier                           | 141  |

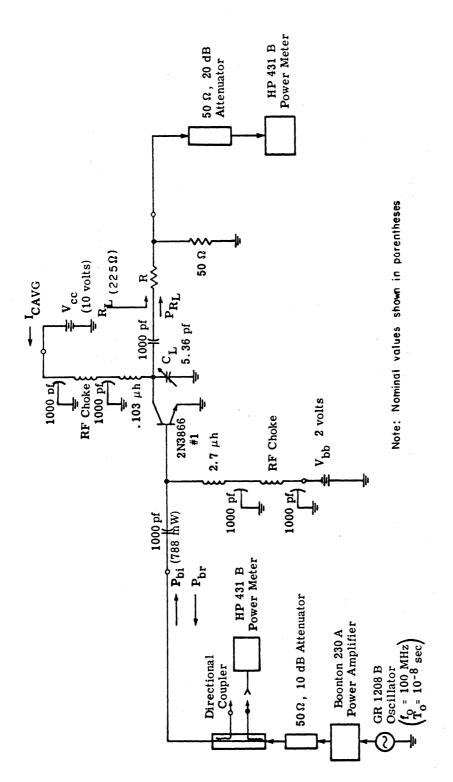

| 4.5    | Experimental amplifier and measurement circuitry              | 143  |

| 4.6    | Collector circuit behavior of low-frequency class C amplifier | 144  |

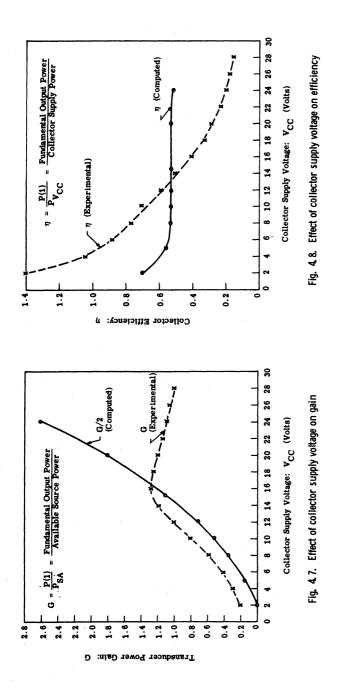

| 4.7    | Effect of collector supply voltage on gain                    | 146  |

| 4.8    | Effect of collector supply voltage on efficiency              | 146  |

| 4.9    | Effect of load resistance on gain                             | 146  |

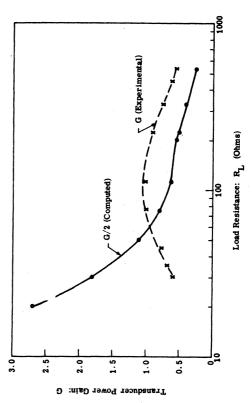

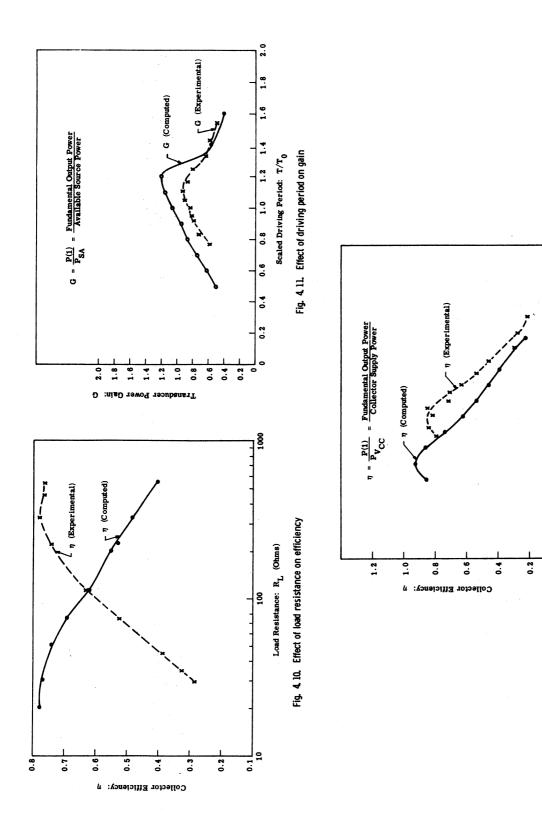

| 4.10   | Effect of load resistance on efficiency                       | 147  |

| 4.11   | Effect of driving period on gain                              | 147  |

| 4.12   | Effect of driving period on efficiency                        | 147  |

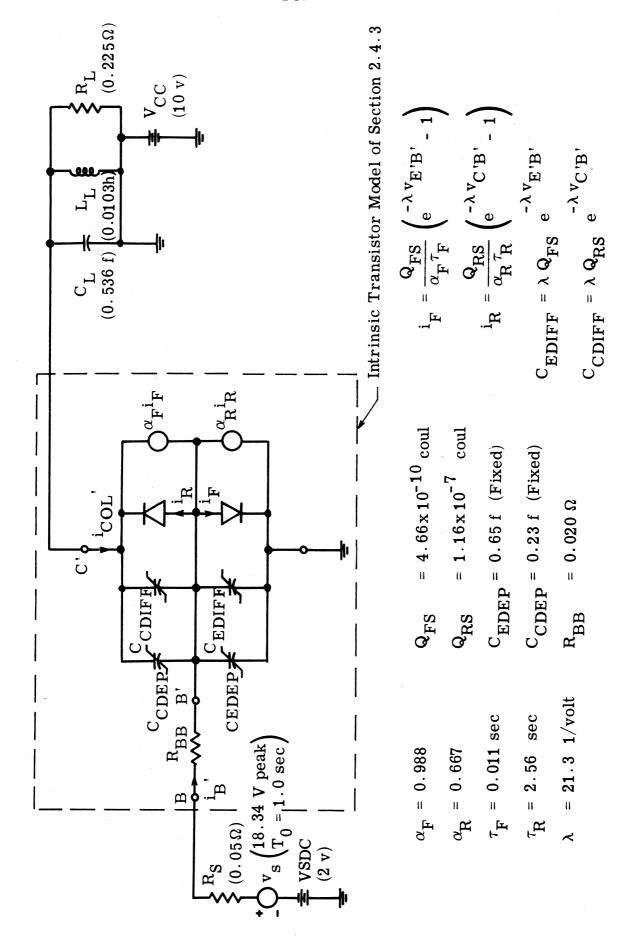

| 4.13   | Equivalent circuit for computer analysis                      | 149  |

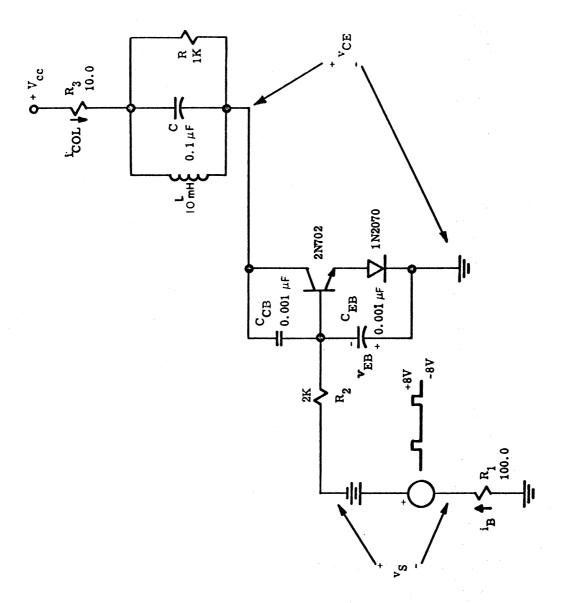

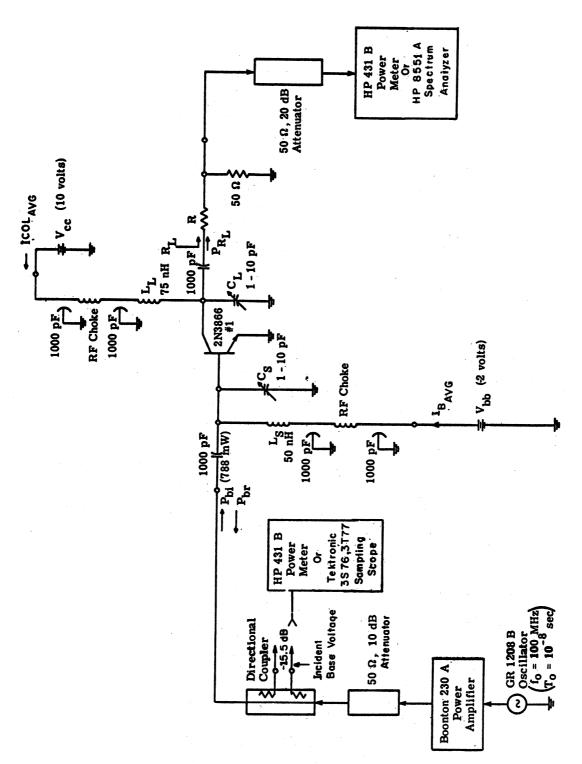

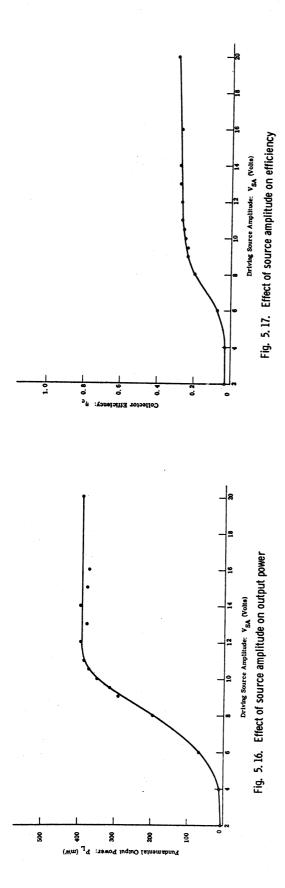

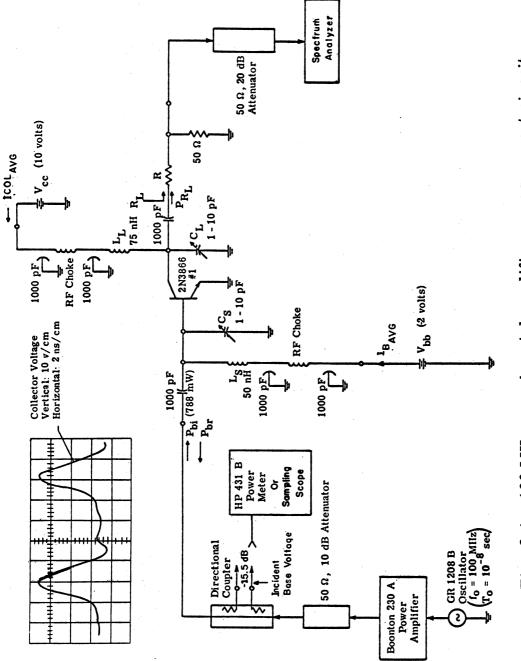

| 5.1    | Experimental amplifier and measurement circuit                | 155  |

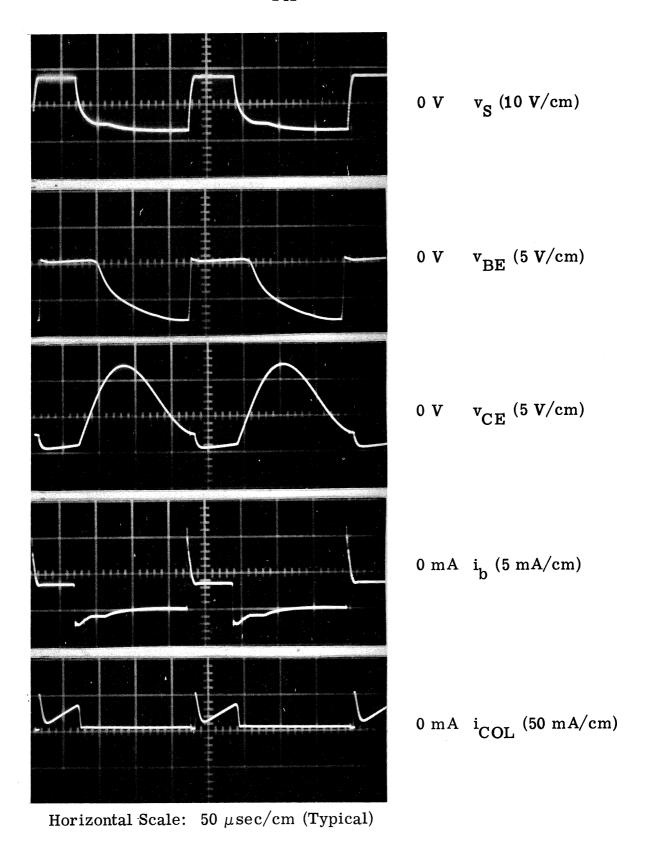

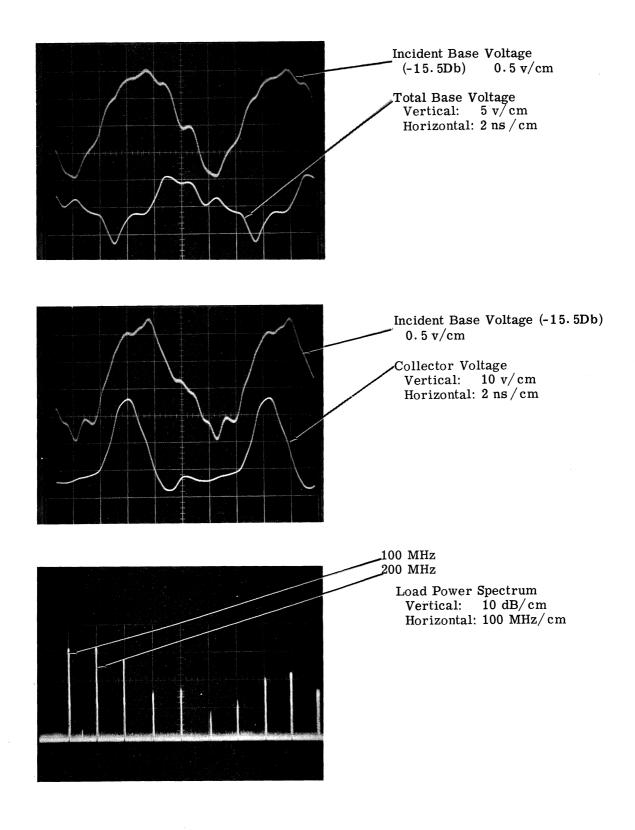

| 5.2    | Waveforms for 100-MHz experimental amplifier                  | 156  |

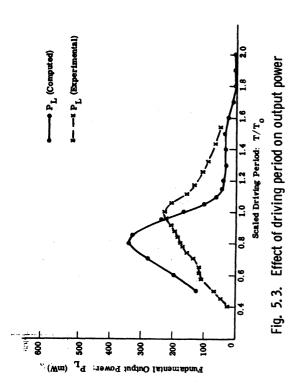

| 5.3    | Effect of driving period on output power                      | 157  |

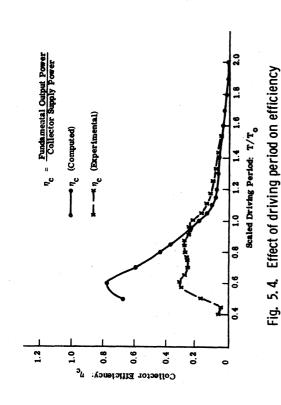

| 5.4    | Effect of driving period on efficiency                        | 157  |

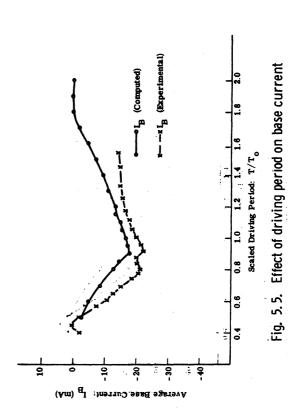

| 5.5    | Effect of driving period on base current                      | 157  |

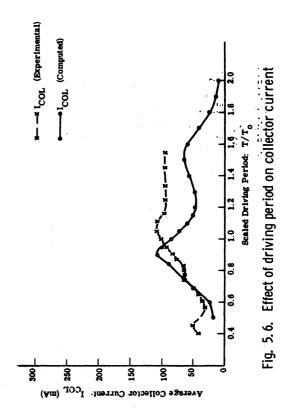

| 5.6    | Effect of driving period on collector current                 | 157  |

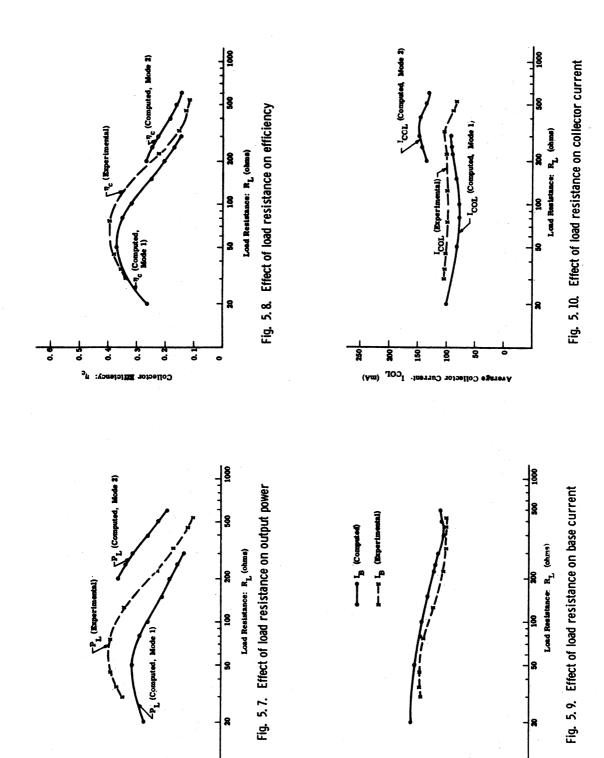

| 5.7    | Effect of load resistance on output power                     | 158  |

| 5.8    | Effect of load resistance on efficiency                       | 158  |

| 5.9    | Effect of load resistance on base current                     | 158  |

| Figure | Title                                                                                                                              | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.10   | Effect of load resistance on collector current                                                                                     | 158  |

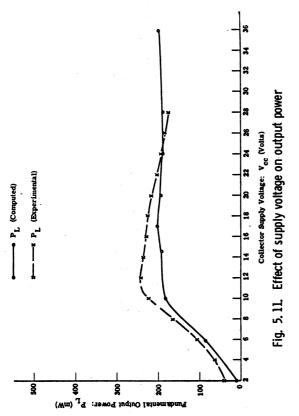

| 5.11   | Effect of supply voltage on output power                                                                                           | 159  |

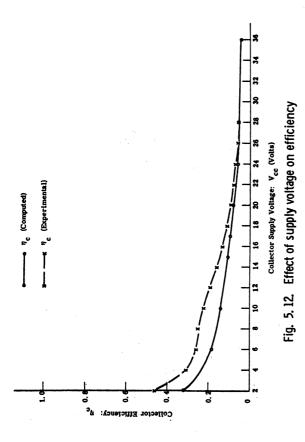

| 5.12   | Effect of supply voltage on efficiency                                                                                             | 159  |

| 5.13   | Effect of supply voltage on base current                                                                                           | 159  |

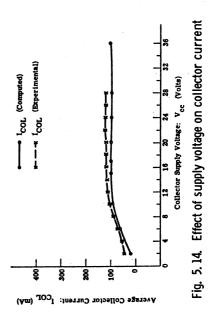

| 5.14   | Effect of supply voltage on collector current                                                                                      | 159  |

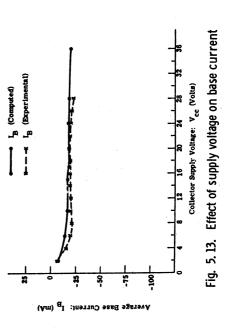

| 5.15   | Scaled equivalent amplifier representation with extended transistor model                                                          | 160  |

| 5.16   | Effect of source amplitude on output power                                                                                         | 166  |

| 5.17   | Effect of source amplitude on efficiency                                                                                           | 166  |

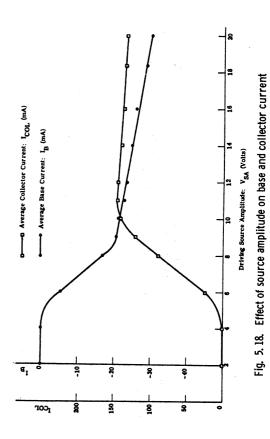

| 5.18   | Effect of source amplitude on base and collector current                                                                           | 166  |

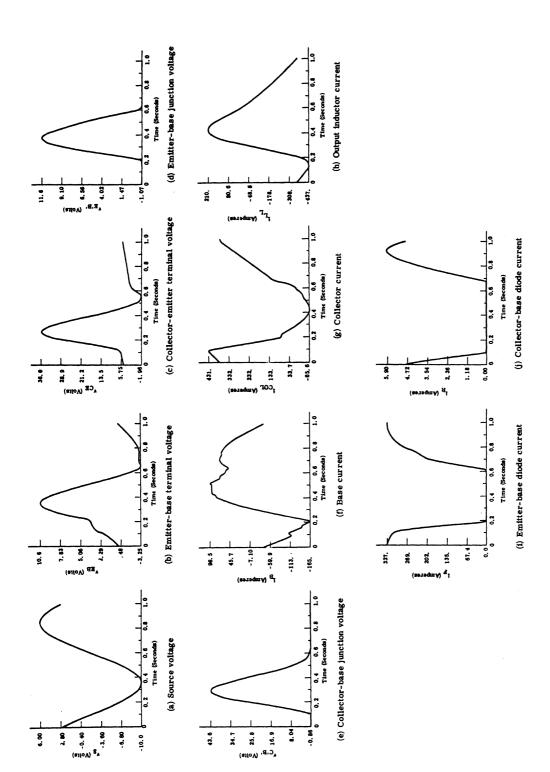

| 5.19   | Typical waveforms with extended model analysis                                                                                     | 168  |

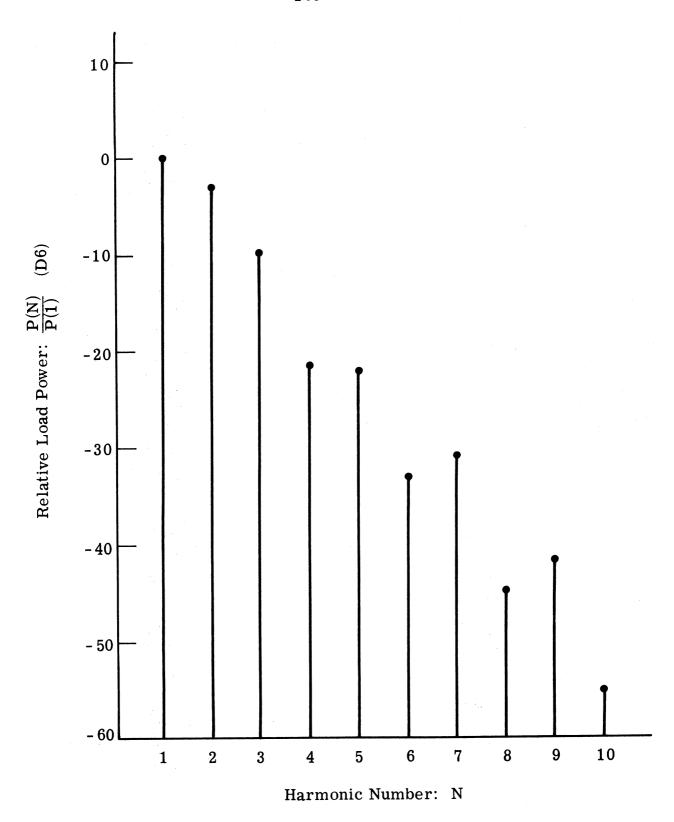

| 5.20   | Computed output power spectrum                                                                                                     | 169  |

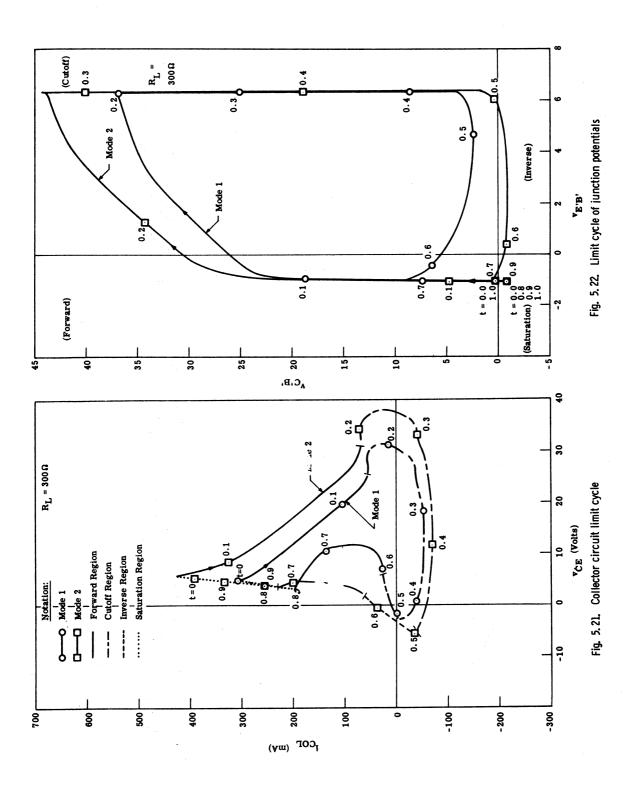

| 5.21   | Collector circuit limit cycle                                                                                                      | 171  |

| 5.22   | Limit cycle of junction potentials                                                                                                 | 171  |

| 5.23   | Experimental class $A_1$ wideband amplifier circuit                                                                                | 173  |

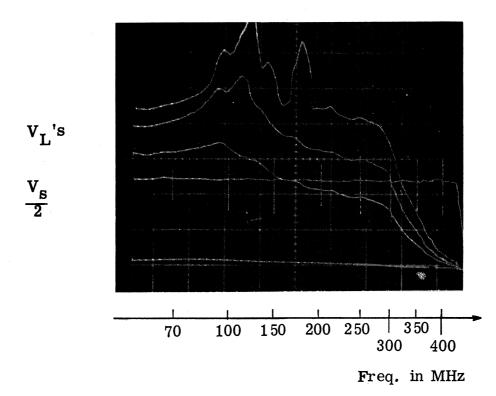

| 5.24   | Swept frequency response of experimental amplifiers; available input powers are 4.23, 2.12, and 0.841 mW                           | 174  |

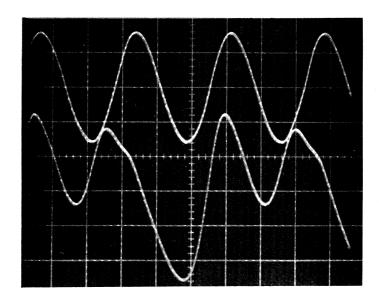

| 5.25   | Output waveform change associated with "mode jump" at 190 MHz. Vertical scale 3 V per division; horizontal scale 2 ns per division | 174  |

| Figure | Title                                                                                | Page |

|--------|--------------------------------------------------------------------------------------|------|

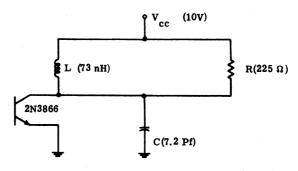

| 6.1    | 100 MHz experimental amplifier, measurement circuit and collector voltage waveform   | 181  |

| 6.2    | Measured equivalent output circuit                                                   | 183  |

| 6.3    | Scaled equivalent output circuit for ideal switch analysis                           | 183  |

| 6.4    | Scaled output circuit for analysis with ideal switch and depletion layer capacitance | 183  |

| 6.5    | Scaled equivalent amplifier representation with intrinsic transistor model           | 184  |

| 6.6    | Scaled equivalent amplifier representation with extended transistor model            | 185  |

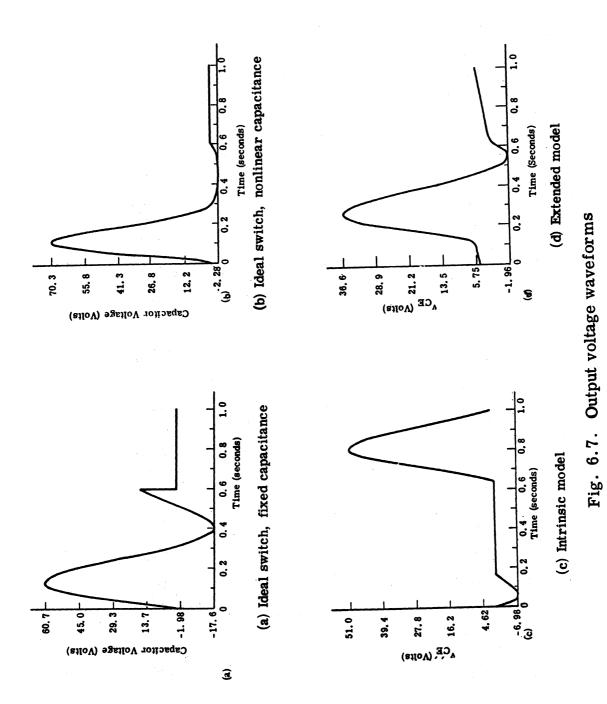

| 6.7    | Output voltage waveforms                                                             | 187  |

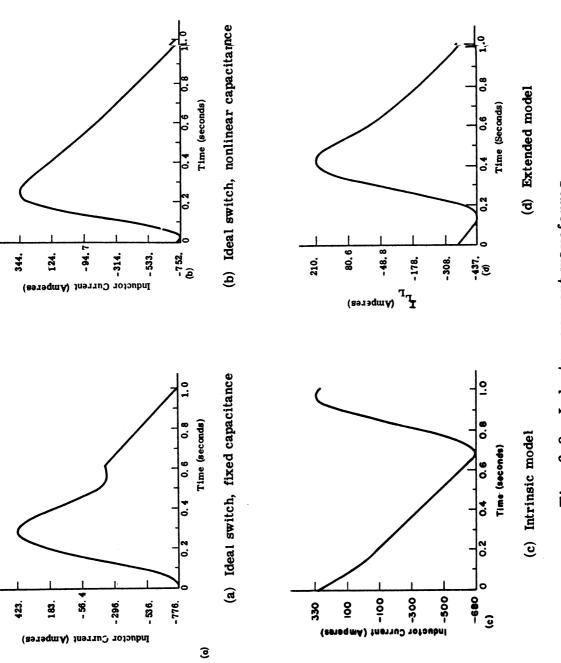

| 6.8    | Inductor current waveforms                                                           | 189  |

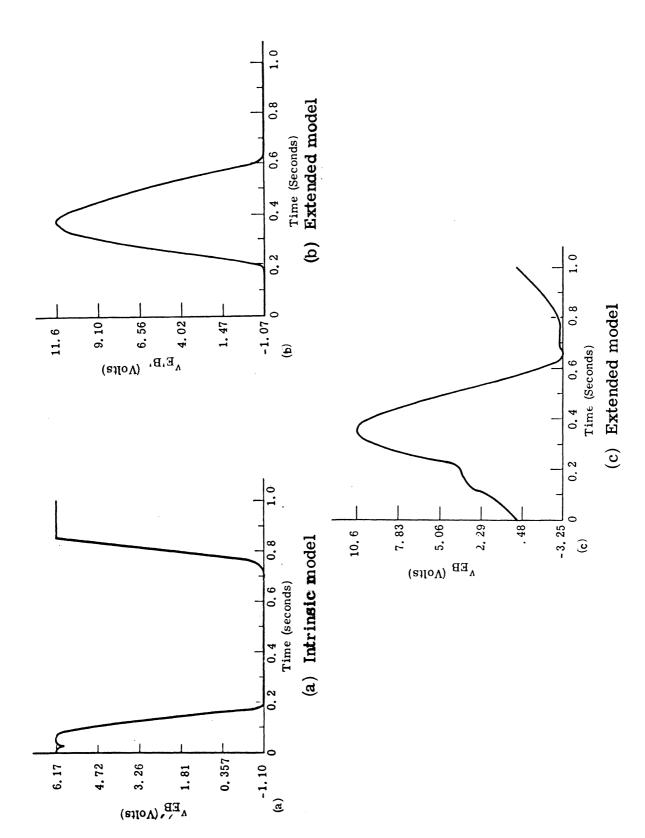

| 6.9    | Emitter-base voltage waveforms                                                       | 190  |

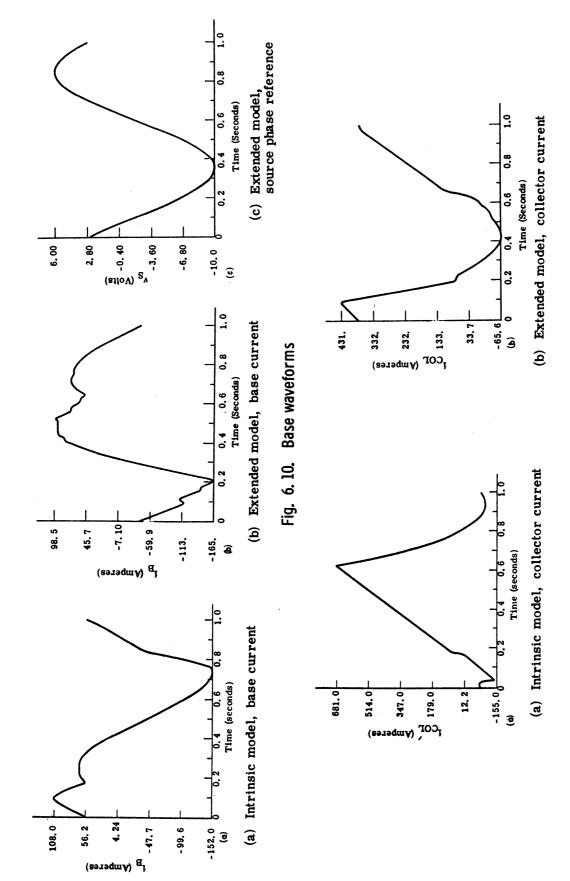

| 6.10   | Base waveforms                                                                       | 191  |

| 6.11   | Collector current waveforms                                                          | 191  |

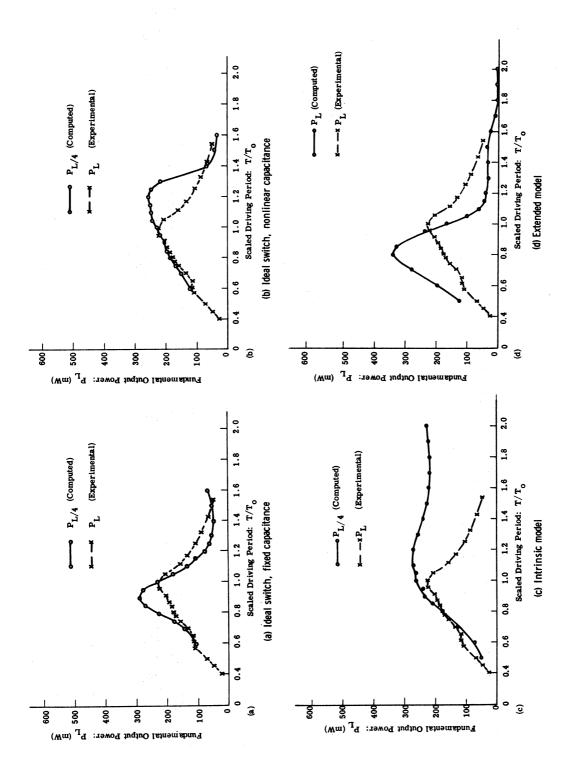

| 6.12   | Frequency response of output power                                                   | 193  |

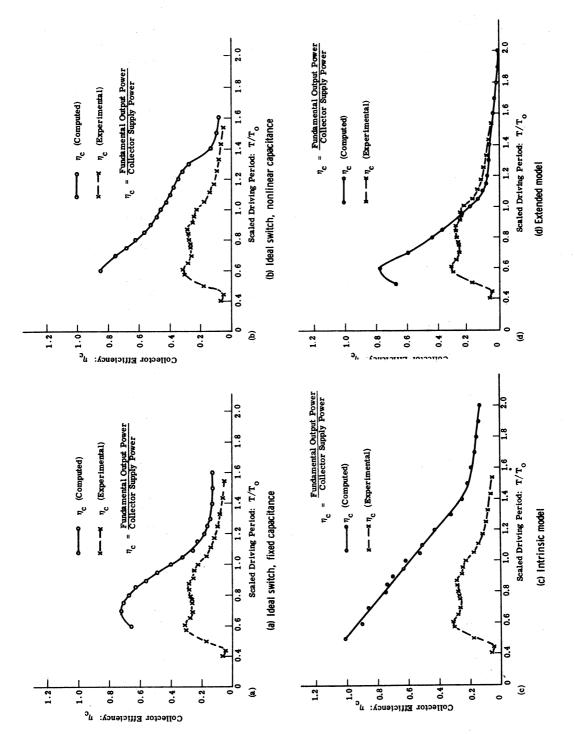

| 6.13   | Frequency response of efficiency                                                     | 195  |

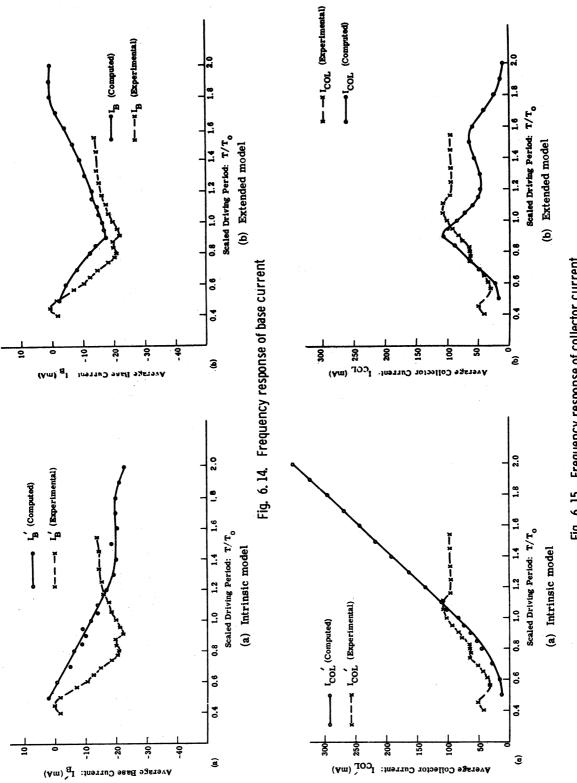

| 6.14   | Frequency response of base current                                                   | 197  |

| 6.15   | Frequency response of collector current                                              | 197  |

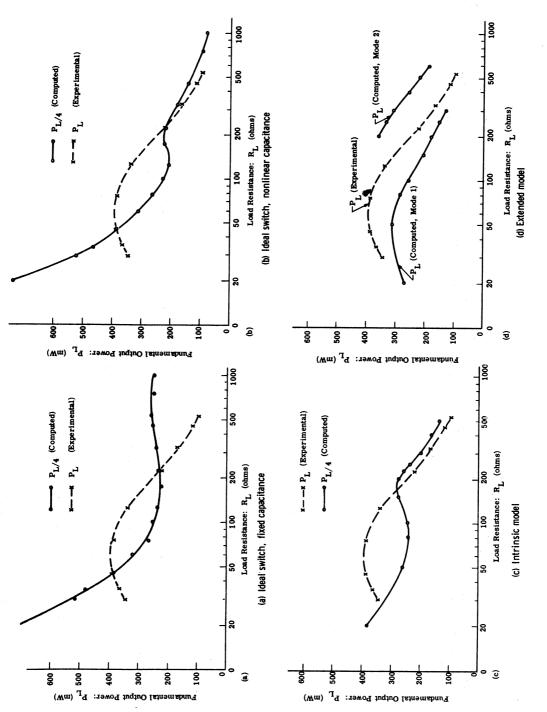

| 6.16   | Effect of load resistance on output power                                            | 198  |

| 6.17   | Effect of load resistance on efficiency                                              | 199  |

| 6.18   | Effect of load resistance on base current                                            | 200  |

| Figure | Title                                                                                                                                                                         | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

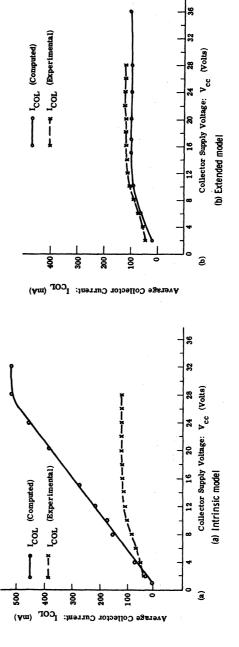

| 6.19   | Effect of load resistance on collector current                                                                                                                                | 200  |

| 6.20   | Effect of supply voltage on output power                                                                                                                                      | 202  |

| 6.21   | Effect of supply voltage on efficiency                                                                                                                                        | 204  |

| 6.22   | Effect of supply voltage on base current                                                                                                                                      | 206  |

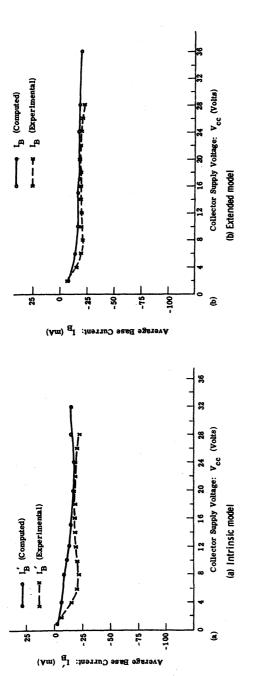

| 6.23   | Effect of supply voltage on collector current                                                                                                                                 | 206  |

| 6.24   | Effect of source amplitude on output power                                                                                                                                    | 207  |

| 6.25   | Effect of source amplitude on collector efficiency                                                                                                                            | 207  |

| 6.26   | Effect of source amplitude on base and collector current                                                                                                                      | 208  |

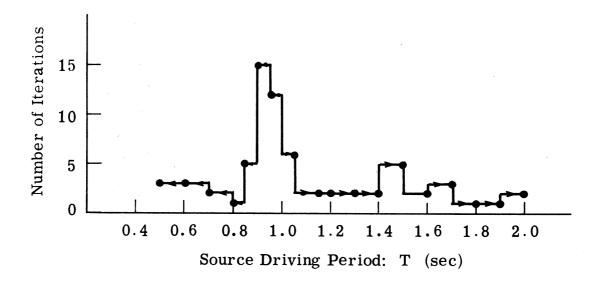

| 7.1    | Convergence behavior with changing excitation period                                                                                                                          | 221  |

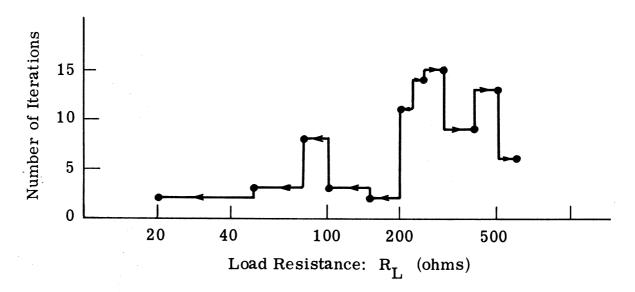

| 7.2    | Convergence behavior with changing resistance                                                                                                                                 | 221  |

| 7.3    | Model with split of depletion capacities                                                                                                                                      | 227  |

| 7.4    | <ul> <li>(a) Photomicrograph of 2N3866 before metallization (from Ref. C4)</li> <li>(b) Example for estimating capacitance split by surface areas of planar device</li> </ul> | 228  |

| A . 1  | Basic circuit for charge storage measurement                                                                                                                                  | 234  |

| A.2    | Typical waveshapes for charge storage measurement                                                                                                                             | 235  |

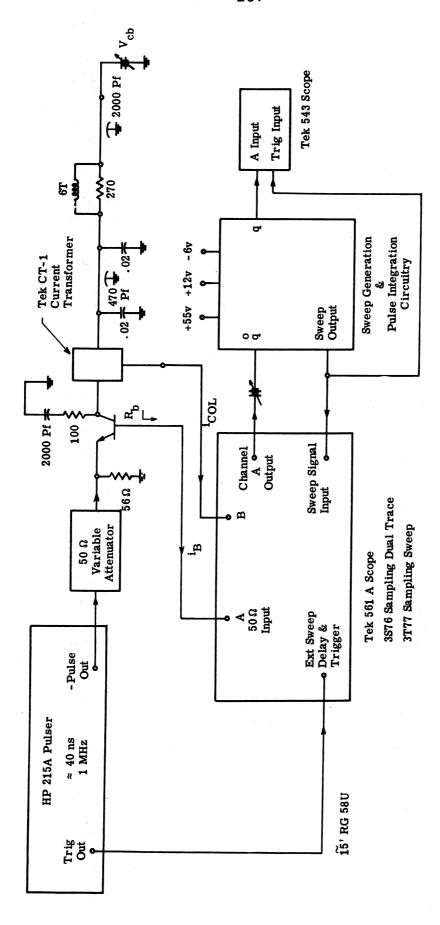

| A.3    | System for $\tau_{ m F}$ charge storage measurements                                                                                                                          | 237  |

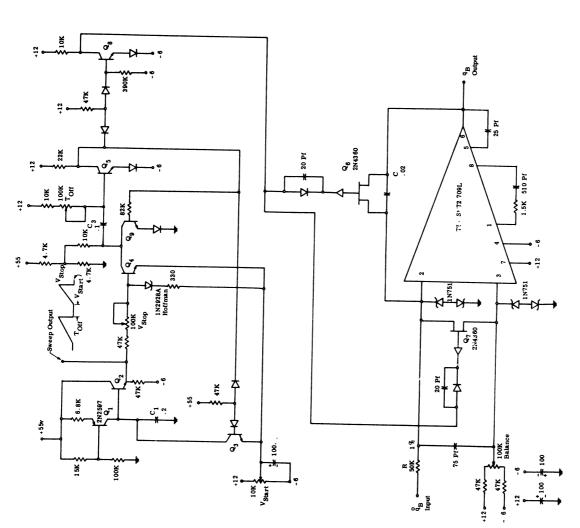

| A.4    | Sweep generation and pulse integration circuitry for charge storage measurement                                                                                               | 240  |

| Figure | <u>Title</u>                                                                            | Page |

|--------|-----------------------------------------------------------------------------------------|------|

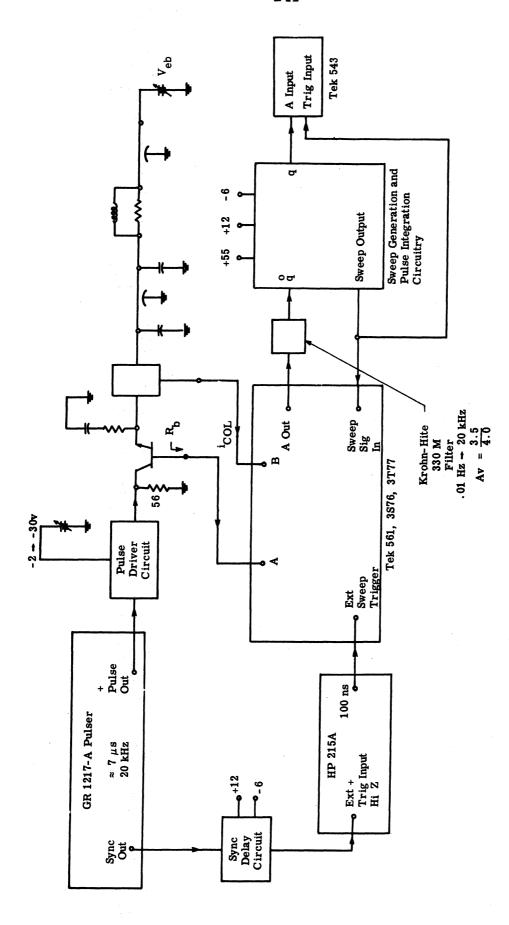

| A.5    | System for $	au_{	extbf{R}}$ charge storage measurement                                 | 241  |

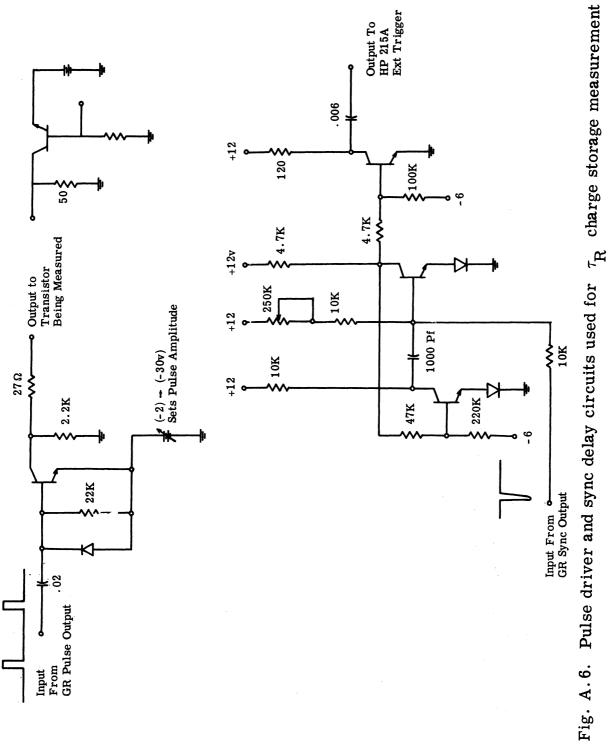

| A.6    | Pulse driver and sync delay circuits used for $\tau_{\rm R}$ charge storage measurement | 242  |

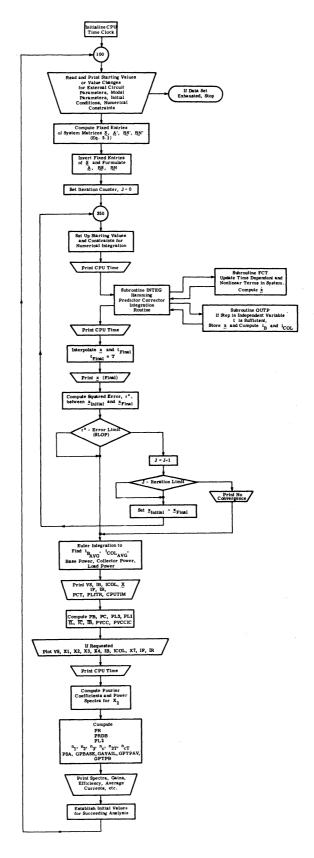

| C.1    | Flow chart for class C amplifier analysis algorithm                                     | 248  |

### LIST OF TABLES

| Table | Title                                                 | Page        |

|-------|-------------------------------------------------------|-------------|

| 2.1   | Summary of extrinsic resistance estimates             | 59          |

| 5.1   | Sensitivities with extended transistor model analysis | 177-<br>178 |

| 7.1   | Averaged sensitivities                                | 217         |

| 7.2   | Guide to model selection                              | 224         |

| C.1   | Program listing for class C amplifier analysis        | 249         |

| C.2   | Sample data set for class C amplifier analysis        | 264         |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Purpose

The desire to understand and design circuits for efficient conversion of electrical energy over a wide frequency range has prompted this study of large-signal high-frequency transistor amplifiers. The problems associated with the design of RF power amplifiers to achieve various performance criteria have received considerable attention in the past. Due to the nonlinear behavior often associated with such large-signal amplifiers, there are very few specific design rules that can be used in their development. At the present time, large-signal RF power amplifiers are typically designed by laboratory determination of "average" large-signal device characteristics, design of simple linear matching circuitry to fit these "average" characteristics, and laboratory cut-and-try procedures to optimize the circuit performance. Unfortunately, the cut-and-try approach is only useful for relatively simple circuits. In addition, such approaches do not allow the engineer to determine what circuit performance could be obtainable if a different device were chosen as a gain element for the circuit.

The rapid development of new devices by the semiconductor industry adds to the design problem. Even as the designer selects an appropriate device for a particular task, he is aware of possible

circuit improvements as new devices become available. When considering complex tuning networks, multiple power stages, strip-line networks and integrated high frequency power stages, the designer needs more analytical methods for predicting, studying and optimizing circuit performance. The use of a high-speed digital computer for analyzing complex nonlinear circuits offers one possible method for aiding the solution of these design problems.

Computer-aided circuit design and analysis is well-developed in problem areas involving linear circuit models for transistors and other active devices. Many automated analysis programs even provide nonlinear device models for determining transient behavior of nonlinear circuits. There is, however, no general nonlinear transistor model stemming from device measurements that adequately incorporates the high-frequency large-signal characteristics of most RF power transistors. It is therefore desirable to develop models and techniques for determining the model parameters that may subsequently be used for computer analysis of high-frequency large-signal circuits.

The main purpose of this research is to further the understanding of high frequency transistorized power amplifiers. This objective involves development of related models and computer analysis techniques. The work is concerned mainly with the behavior

of class C amplifiers operating in the VHF frequency range. Previous analyses of class C amplifiers have been limited by certain assumptions introduced to make hand analysis tractable. The analyses to be presented here are numerical in nature, allowing the power of high speed digital computation to aid in removal of many of the standard assumptions.

Previous analyses typically assume that the operating frequency is low in comparison to the transistor limitations, and low frequency models of the transistor are used (Refs. S3, H5, S2, E3). The Q's of the output tuning networks are normally assumed to be high so that output waveforms can be assumed to be purely sinusoidal. Many analyses make the further assumption that the emitter-base and collectorbase junction potentials are sinusoidal (Refs. H5, S3, S4, W1, S2, E3, P1). In addition, the waveshapes of transistor output current are often assumed to be of some known shape, and the corresponding base currents are calculated by assuming linear or very simple relationships between the two currents (Refs. S2, S3, P1). In keeping with the assumed current waveshapes, the device is assumed always to operate in cut-off or the active region of operation. The device is allowed to approach the edge of saturation but not allowed to enter the saturation region (Refs. H5, S2, S3). For further simplification, extrinsic device resistances and inductances are usually neglected, and depletion capacitances are assumed to be constant or nonexistent (Refs. H5, S2, S3, P1).

Depending on the intended purpose of the amplifier the standard assumptions may or may not be justified. In the class C amplifier design problems to be stressed in this work none of the above assumptions are truly justified. The basic problem to be considered is one of making use of the given device to obtain maximum fundamental output power or maximum efficiency of energy conversion at frequencies near the gain bandwidth limitation of the device. Power gain is of secondary importance, and in general, power gain will be sacrificed to provide operating efficiency and to increase the output power. With such operation in mind the high-frequency characteristics of the transistor must be included in the description of amplifier behavior. Typical values of operating Q lie in the range of 1 to 10, and as a result, considerable amounts of harmonic content will appear in the output voltage waveforms. The harmonic powers must be included for complete characterization of amplifier performance. The relationships between the terminal currents and voltages of a transistor can be expressed in terms of nonlinear differential equations, and the application of digital computation methods allows a rather complete description to be used instead of relying on linearizing assumptions. By using this more complete description, the current waveshapes need not be assumed but can be determined from input excitation and linear network constraints. A standard method of operation of class C power stages is to provide an excess of input power so that the output power

attains a saturation level. Such operation improves the efficiency of operation of the output circuitry and stabilizes the output power with respect to slight variations in input power (Ref. S4). In this mode of operation the transistor is periodically driven into the saturation region, and saturation effects must be included if an accurate analysis is desired. The large signals encountered in tuned power amplifiers can cause avalanche breakdown of the semiconductor junctions, and this effect is also easily included in computer simulations.

#### 1.2 Statement of Problem

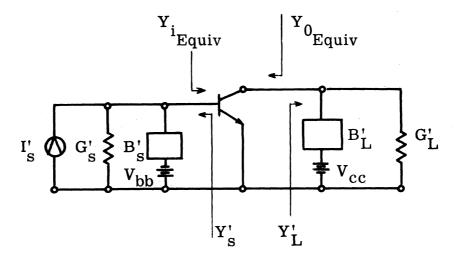

As an introduction to the types of problems to be studied, consider the general circuit configuration for a single stage tuned power amplifier shown in Fig. 1.1. In a strict sense, the concept of admittance does not apply to the nonlinear behavior of the input and output characteristics of the transistor under large signal excitation, but artificial admittances  $Y_i$  and  $Y_0$  are introduced here in a manner consistent with that currently in use by most manufacturers of VHF power transistors (Refs. C5, H7, H9, L2). That is, with the input and output matching networks of a given configuration adjusted for maximizing a given performance criteria (i.e., max power output, max efficiency, etc.) with given bias conditions, signal levels, and frequency; the transistor large-signal equivalent admittances are

<sup>&</sup>lt;sup>1</sup>These adjustments are normally accomplished with low-loss LC networks or double-stub tuners.

Fig. 1.1. Circuit configuration for tuned power amplifier defined in terms of the linear matching networks as:

$$Y_{0_{\text{Equiv}}} = Y_{\text{L}}^{'*}$$

Information about  $Y_i$  and  $Y_0$  as functions of frequency and signal level is useful in the practical sense of designing passive circuitry for obtaining a maximum output power over a selected frequency range; however, there are definite limitations to this information. Since the transistor is operating in a nonlinear mode, the overall behavior depends on the effects of the tuning networks on the harmonic components of the signals as well as the fundamental. Hence it is not possible to predict accurately the behavior of the transistor

when it is imbedded in a network that differs from the networks used for determining Y<sub>i</sub> and Y<sub>0</sub>. In addition, this equivalent Equiv admittance technique does not provide the designer with sufficient information to estimate such characteristics as amplifier bandwidth in wideband situations or the effects of bias conditions on the circuit behavior. It is difficult for the designer to analytically determine the trade-offs possible in power output, bandwidth, and efficiency; and as a result he is often forced into trial-and-error laboratory procedures to determine the level of performance he can expect from a given device in a specified application.

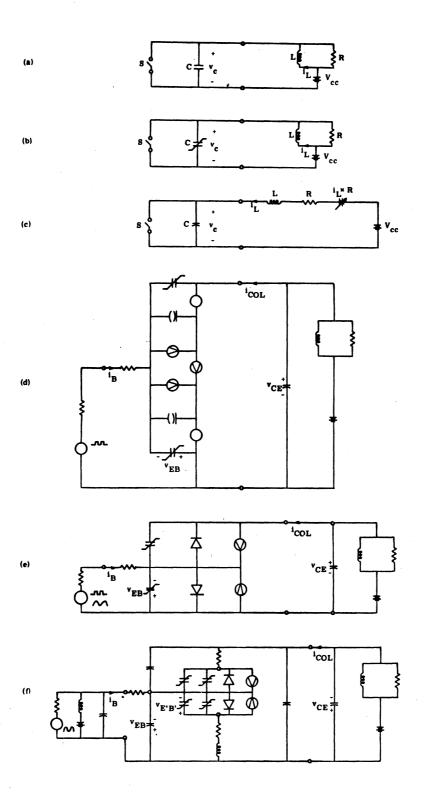

Our objective is to increase the understanding of some of the basic characteristics of class C and class D amplifiers, to develop modeling techniques suitable for describing the large-signal high-frequency effects encountered in VHF power transistors, and to develop computer analysis programs for predicting the performance of class C and D amplifiers. Before analyses of the amplifiers are begun, transistor models are selected to provide descriptions of the major dynamic and nonlinear transistor characteristics. Figure 1.2 provides a brief indication of the progression of the model and circuit forms considered by this study.

The transistor models to be used in the numerical analyses of tuned power amplifiers are presented in Chapter 2. Each of the model forms presented is then used separately in Chapters 3, 4, and 5 to

Fig. 1.2. Progression of device and circuit models

study amplifier behavior. Comparisons of the models is provided in Chapter 6 where they are each used to predict the performance features of a common amplifier. Chapter 7 presents the general conclusions of the study and suggests related areas for further consideration.

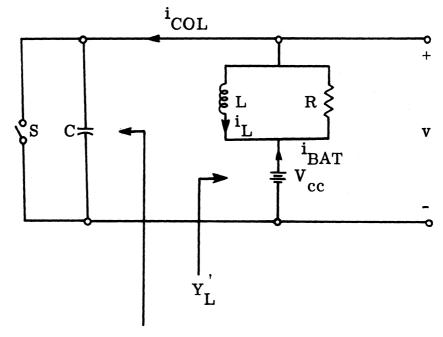

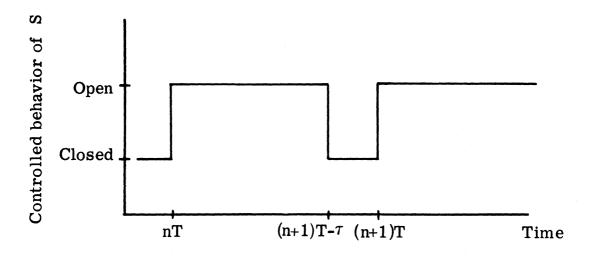

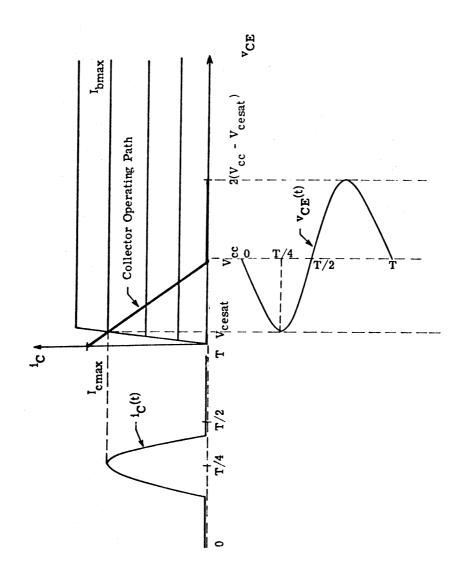

The simplest modeling of class C/D output circuits is shown on Fig. 1.2a where the transistor is modeled as a simple controlled switch with a fixed shunt capacitance, and the output tuning and matching network is taken to be a parallel RL network. As discussed in Section 3.2 a computer analysis program is used to study the effects of switch duty factor, supply voltage, and frequency in determining the  $Y_0$  's for obtaining maximum fundamental output power and for obtaining maximum efficiency. The relationships among output power, efficiency, bandwidth, and harmonic content are also investigated with the ideal switch transistor representation (Section 3.2).

By replacing the fixed shunt capacitance with a nonlinear voltage dependent capacity characteristic of semiconductor junction depletion layers as shown in Fig. 1.2b, the effects of a first order nonlinearity are investigated. In Section 3.3 the results of this investigation are contrasted to those of the fixed capacitance case which forms a reference standard used throughout this study.

The effect of the configuration of the tuning network in determining the equivalent admittances is investigated by changing the output tuning and matching network to a series RL connection again using the ideal switch with fixed capacitance to represent the output characteristics of the transistor (Section 3.4). The ideal switch representation is also used to investigate the effects of harmonic tuning in the output circuits of RF power amplifiers (Section 3.5). This investigation considers both fixed and nonlinear switch capacitances to determine the significance of a nonlinear element to harmonic energy conversion.

With the insight gained through the idealized studies of class C amplifiers, emphasis is directed to predicting behavior of real VHF amplifiers. An intrinsic voltage controlled transistor model (Section 2.4.3) is used to predict the behavior of a low frequency, tuned output, pulsed input amplifier (Section 4.2). This model is also used to analyze a 100 MHz class C amplifier (Section 4.5). Experimental circuits are constructed, and their measured behaviors are used as comparisons to the behaviors predicted with the computed analyses (Sections 4.3 and 4.4).

Another 100 MHz amplifier experiment is performed to add the effects of input circuit tuning (Section 5.2), and this amplifier is modeled (Section 5.3) using an extended voltage controlled transistor model (Section 2.5). Again computed behavior is compared and contrasted to experimentally measured behavior.

A summary of the computational advantages and limitations of

each of the models is presented (Chapter 7). This includes costaccuracy comparisons and computed results for one tuned amplifier example (Chapter 6).

#### CHAPTER 2

#### MODELING

### 2.1 Introduction

Several models used in the computer-aided analysis of VHF power amplifiers will be presented in this chapter together with experimental techniques useful for obtaining the model parameters. Many of the elements present in the models were suggested by observations of experimental amplifier behavior and by computer analysis of tuned power amplifiers. Although the models and modeling procedures will be presented here in a self-contained fashion, it was the interactions with the experimental and computed behaviors that prompted the inclusion of many of the model elements and the experimental techniques that are used for obtaining their quantitative descriptions.

#### 2.2 Introduction of Model

Quantitative analyses of physical processes require mathematical descriptions of the processes. The circuit models and corresponding mathematical expressions chosen for representing the physical behavior of VHF power amplifiers determine the facility with which an analysis can be performed as well as the accuracy of the analysis. Generally, we can expect to improve analytical accuracy by increasing the size of our circuit and mathematical models. The anticipated

price to be paid for improved accuracy is one of increased complexity and time required for the analysis. An apparent practical limit to the maximum size appropriate for a model occurs when further size increases are found to produce insignificant changes in the analytical results, or as a final size limit, when results of further model expansions are lost in computational and measurement noises.

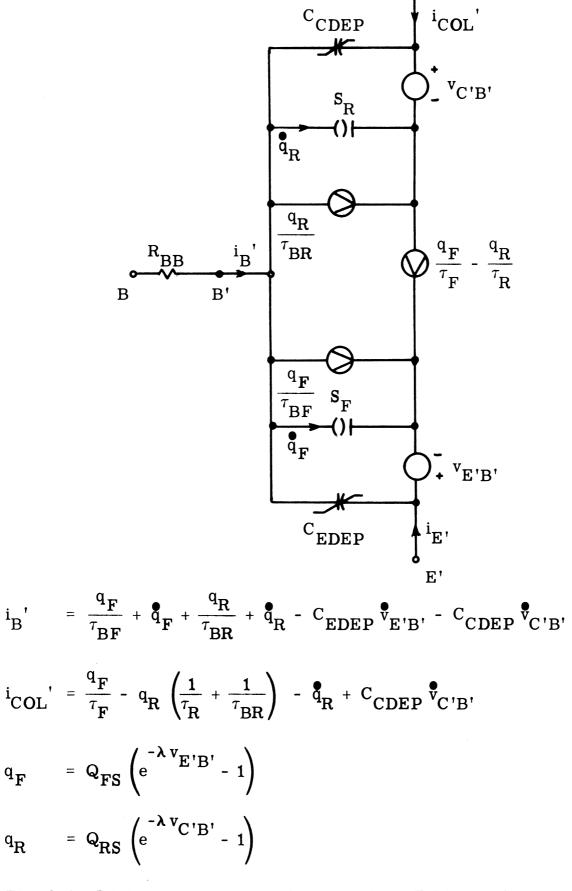

There are several popular large-signal circuit descriptions of intrinsic transistor properties. Notable among these are the classical Ebers-Moll voltage-controlled model (Ref. E1), the physics oriented Linvill voltage-controlled model (Ref. L3), and the mathematical charge-controlled description of Beaufoy-Sparkes (Ref. B1). For a consistent set of approximations, these models can be shown to be mathematically equivalent (Ref. K1); however, because of the different choices in the controlling independent variables, computational differences in dynamic ranges and severities of nonlinearity in various operating regions can affect the computational advantages of one model relative to another (Ref. M1). Neglecting these computational differences between the models, a lumped charge-controlled time-domain model is selected initially because it closely resembles the physical process and also lends itself to a succinct circuit representation. This model can be considered as the basis for the formulation of all the other model forms to be presented. The notation used for the

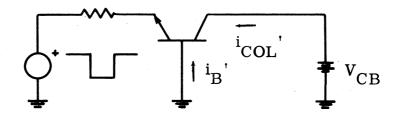

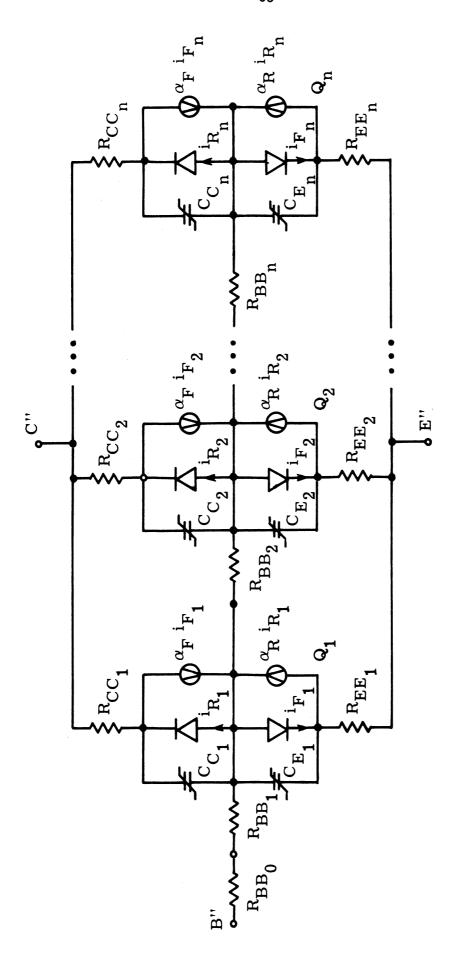

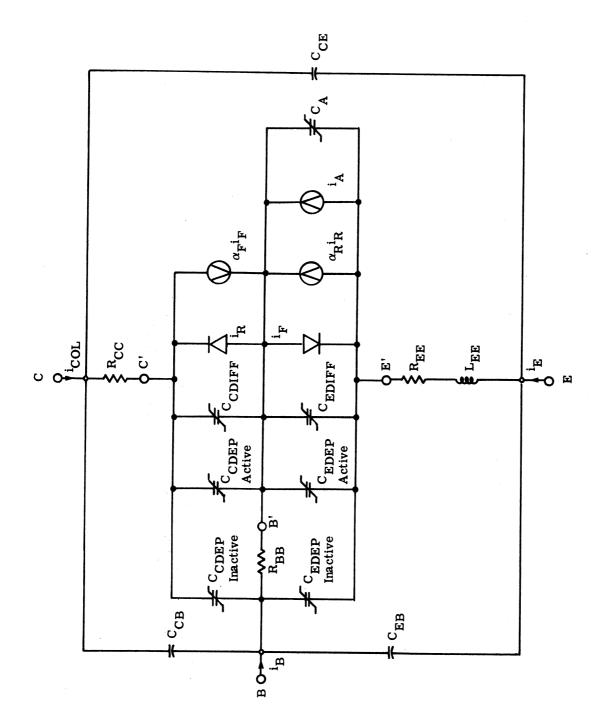

charge-controlled model<sup>1</sup> (Fig. 2.1) of an intrinsic NPN transistor and its defining equations (Eqs. 2.1 - 2.4) are basically those of Ref. P2.

$$i'_{B} = \frac{q_{F}}{\tau_{BF}} + \dot{q}_{F} + \frac{q_{R}}{\tau_{BR}} + \dot{q}_{R} - C_{EDEP} \dot{v}_{E'B'} - C_{CDEP} \dot{v}_{C'B'}$$

(2.1)

$$i'_{COL} = \frac{q_F}{\tau_F} - q_R \left( \frac{1}{\tau_R} + \frac{1}{\tau_{BR}} \right) - \dot{q}_R + C_{CDEP} \dot{v}_{C'B'}$$

(2.2)

$$q_{F} = Q_{FS} \left(e^{-\lambda v_{E'B'}} - 1\right)$$

(2.3)

$$q_{R} = Q_{RS} \left( e^{-\lambda v_{C'B'}} - 1 \right)$$

(2.4)

These equations result from the solution of a lumped representation of a one-dimensional, field-free, diffusion equation approximating minority carrier motion in a narrow base region of a junction transistor. Approximations of space charge neutrality, no carrier recombination or generation in the space charge region, and no potential drops except at the junctions have also been made in the derivation of these charge-controlled equations.

The junction depletion layer capacitances,  $\,^{\mathrm{C}}_{\mathrm{EDEP}}\,$  and

$<sup>^1\</sup>mathrm{The~elements~S_F}$  and  $\mathrm{S_R}$  are termed the forward and reverse charge stores respectively. A charge store is defined as an electrical element with the property that the store potential is always zero and the current through the store is equal to the time rate of change of the stored charge.

Fig. 2.1. Intrinsic charge-controlled model of NPN transistor

$^{\rm C}_{

m CDEP}$  are appended to the intrinsic model after the solution of the diffusion equation to account for the energy stored in immobile charges in the space charge regions (Ref. P2). A base spreading resistance  $^{\rm R}_{

m BB}$  is often added also to simulate ohmic potential drops that result from transverse majority carrier motion in the base region (Ref. P2).

## 2.3 Determination of Model Parameters

In order to make the model useful for numerical computations relating to a given transistor type, experimental methods can be employed to determine the numerical values and behaviors of the model parameters to describe the specific device. The parameters required for completing the intrinsic charge-controlled model description are:

$lpha_{

m F}, \ lpha_{

m R}$ : common base dc forward and reverse current transport factors

${}^{ au}\mathbf{F}$ ,  ${}^{ au}\mathbf{R}$ : recombination time constants for emitter-

$\mathbf{Q}_{\mathbf{FS}},\ \mathbf{Q}_{\mathbf{RS}}$ : saturation charge constants for the emitter-

base and collector-base junction behaviors

$C_{\mbox{EDEP}}$ ,  $C_{\mbox{CDEP}}$ : emitter-base and collector-base depletion

layer capacitances

$\lambda$ : exponential constant  $\frac{mq}{KT}$

$R_{\mbox{\footnotesize{BB}}}$ : base spreading resistance

with

$$\tau_{\rm BF} \stackrel{\Delta}{=} \frac{\alpha_{\rm F}}{1 - \alpha_{\rm F}} \cdot \tau_{\rm F}$$

$$\tau_{\rm BR} \stackrel{\Delta}{=} \frac{\alpha_{\rm R}}{1 - \alpha_{\rm R}} \cdot \tau_{\rm R}$$

There are various methods that can be used to determine the required parameter values from experimental measurements of device behavior. The following techniques have been used to establish parameter values for a type 2N3866 VHF transistor.

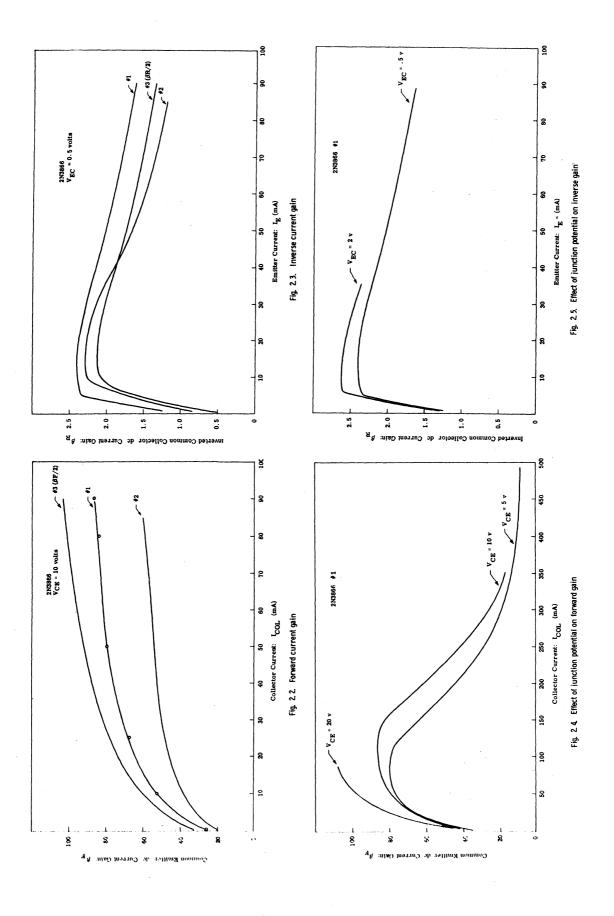

$\frac{2.3.1~\alpha_F~\text{and}~\alpha_R~\text{From Curve Tracer Measurements.}}{\beta_F~\text{and}~\beta_R~\text{can be determined over a wide range of current-voltage operating conditions with conventional curve tracer measurements (Ref. H3, Chapter 7). The common-base current gains are then obtained by applying the simple relationship <math>\alpha = \frac{\beta}{\beta+1} = 1 - \frac{1}{\beta+1}$ . Quite often, however, problems with oscillations, excessive power dissipations, junction temperature variations, and accuracy preclude the use of this simple measurement. In such instances more specialized direct or pulsed measurements may be required, but for present purposes the curve tracer measurements are adequate. Figures 2.2 and 2.3 show the results of forward and inverse beta measurements of three 2N3866 transistors over a wide range of collector and emitter currents. Figures 2.4 and 2.5 illustrate the effects of junction potential variations for one of the transistors.

For transistor #1 in the relatively large region 20 ma <  $I_{COL}$  < 150 ma, 5 volts <  $V_{CE}$  < 15 volts; we find 70  $\lesssim$   $\beta_F$   $\lesssim$  90. Approximating  $\beta_F$  as a constant, 80, in this region leads to the value  $\alpha_F$  = 0.988 which will be used in the computer simulation studies. Similarly for 20 ma <  $I_E$  < 150 ma, 0.5 volts <  $V_{EC}$  < 2.0 volts, we find 1.5  $\lesssim$   $\beta_R$   $\lesssim$  2.0 and approximate  $\alpha_R$   $\approx$  0.667.

$$i'_{B} = \frac{q_{F}}{\tau_{BF}} + \dot{q}_{F} + \frac{q_{R}}{\tau_{BR}} + \dot{q}_{R} - i_{C_{EDEP}} - i_{C_{CDEP}}$$

$$\approx \frac{q_{F}}{\tau_{BF}} + \dot{q}_{F} - i_{C_{EDEP}} - i_{C_{CDEP}}$$

(2.5)

$$i'_{COL} = \frac{q_F}{\tau_F} - q_R \left( \frac{1}{\tau_R} + \frac{1}{\tau_{BR}} \right) - \dot{q}_R + i_{C_{CDEP}}$$

$$\approx \frac{q_F}{\tau_F} + i_{C_{CDEP}}$$

(2.6)

where

$$i_{C_{EDEP}}(t) = C_{EDEP}(v_{E'B'}) \frac{dv_{E'B'}(t)}{dt}$$

$$i_{C_{CDEP}}(t) = C_{CDEP}(v_{C'B'}) \frac{dv_{C'B'}(t)}{dt}$$

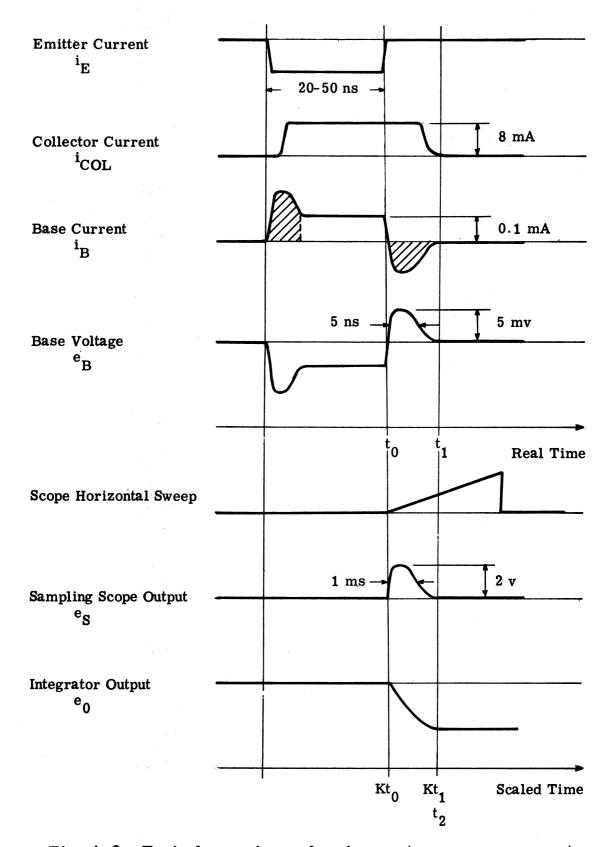

If a pulse of collector current is stimulated by an emitter excitation as indicated in Fig. 2.6, the resulting base current (i'\_B) will be composed of a static term which is the recombination current (q\_F/\tau\_{BF}), and two transient terms: one to build up the stored base charge (q\_F) and a second to charge the depletion layer capacitances (i\_EDEP), i\_CDEP ). Integration of the base current transient terms yields the base charge stored in the base and depletion layer regions, viz.

Fig. 2.6. Charge storage measurement

$$Q_{B_{stored}} = \int_{transient} i_{B}^{\prime} dt^{-1}$$

$$= \int \dot{q}_{F} dt - \int i_{C_{EDEP}} dt - \int i_{C_{CDEP}} dt \qquad (2.7)$$

With the measurement technique used, the collector-base voltage  $(v_{\hbox{$C'$B'$}}) \ \ \text{is held constant so that the} \ \ i_{\hbox{$CDEP$}} \ \ \text{term can be neglected.}$  As a result

$$Q_{B_{stored}} \approx q_F + Q_{C_{EDEP}}$$

(2.8)

with

$$Q_{C_{\mbox{\footnotesize EDEP}}} \stackrel{\Delta}{=} - \int_{\mbox{\footnotesize transient}} i_{C_{\mbox{\footnotesize EDEP}}} dt$$

Combining Eqs. 2.6 and 2.8 results in an expression that relates the stored charge linearly to the collector current.

$$Q_{B_{stored}} \approx \tau_{F} i_{COL}' + Q_{C_{EDEP}}$$

(2.9)

Similarly by reverse biasing the emitter-base junction and exciting a known pulse amplitude of emitter current we get:

i' dt means integrating the two transient terms of the transient

i' dt means integrating the two transient terms of the total base current and excluding the static term. Refer to Appendix A for details of the related experimental technique.

$$Q_{B_{stored}} \approx \tau_{R} i_{E}' + Q_{CDEP}$$

(2.10)

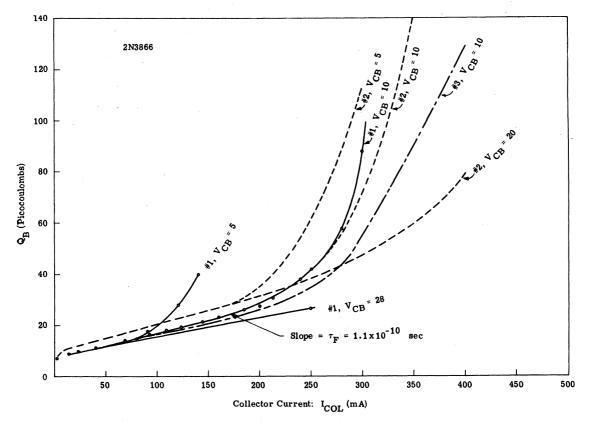

The experimental procedure for determining  $\mathbf{Q}_{B}$  involves electronic integration of the transient base current waveform for various levels of steady state collector current (Appendix A). A plot of this stored charge versus the collector current (Eq. 2.9) will then reveal the time constant  $(\tau_{F})$  as the slope and the depletion capacitance charge  $\left(\mathbf{Q}_{C_{EDEP}}\right)$  as the intercept.

Experimental measurements of stored charge have been taken at various values of current and junction potentials for the three 2N3866 transistors. The results are shown in Figs. 2.7 and 2.8. For the forward bias measurement the straight-line relationship predicted theoretically is seen to occur experimentally in the region of collector currents from 10 to 200 milliamperes. In this region the slope,  $\tau_{\rm F}$ , is found to be  $1.1 \times 10^{-10}$  second. In the region of higher collector currents the value for  $\tau_{\rm F}$  increases rapidly whenever the current exceeds a threshold value dependent on the external collector-base bias potential. This rapid increase in time constant can be attributed to saturation of the intrinsic collector-base junction due to a resistive potential drop in the bulk collector region. For example, the knee of the stored charge curve for transistor #1 with a bias voltage of 10.0 volts occurs at a collector current of approximately 200.00 milliamperes. From this behavior we might infer an effective collector

Fig. 2.7. Forward charge storage

Fig. 2. 8. Inverse charge storage

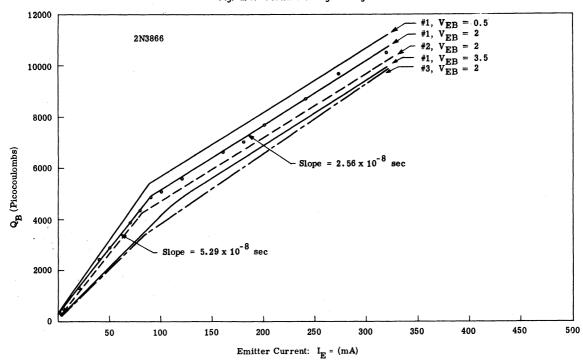

bulk resistance of 50.0 ohms. Conversely, the absence of such saturation effects in the inverse measurement implies that the emitter bulk resistance is less than 0.5 volts/350. mA or 1.4 ohm. Further consideration of these bulk resistances will be given in Section 2.5.3.

From the measurements in the inverse region of transistor operation the reverse charge time constant,  $\tau_{\rm R}$ , appears to be  $5.29 \, {\rm x} \, 10^{-8}$  second for emitter currents less than 80.0 milliamperes and decreases to  $2.56 \, {\rm x} \, 10^{-8}$  second when the emitter current exceeds 100.0 milliamperes. For convenience single values ( $\tau_{\rm F} = 1.1 \, {\rm x} \, 10^{-10}$  and  $\tau_{\rm R} = 2.56 \, {\rm x} \, 10^{-8}$ ) will be taken as representative of the 2N3866 device behavior in the operating regions anticipated for the large signal simulations.

$2.3.3~\lambda$ ,  $Q_{FS}$ , and  $Q_{RS}$  from DC Behavior of Junctions. The steady-state base current  $I_{b'c'}$  resulting from an applied base-collector potential  $V_{b'c'}$  with an emitter current of zero can be expressed from Eqs. 2.1-2.4 as

$$I_{b'c'} \begin{vmatrix} I'_{e} = 0 \end{vmatrix} = \frac{(1 - \alpha_{F} \alpha_{R}) Q_{RS}}{\alpha_{R} \tau_{R}} \left( e^{\lambda V_{b'c'}} - 1 \right)$$

(2.11)

Similarly, for the base-emitter junction

$$I_{b'e'} = \frac{(1 - \alpha_F \alpha_R) Q_{FS}}{\alpha_F \tau_F} \left( e^{\lambda V_{b'e'}} - 1 \right)$$

(2.12)

For forward bias junction potentials greater than 100 millivolts,  $e^{\lambda\,V}>>1$  . In this region, for example,

$$\ell n \left[ \frac{I_{b'c'} \alpha_R \tau_R}{(1 - \alpha_F \alpha_R) Q_{RS}} \right] \approx \lambda V_{b'c'}$$

(2.13)

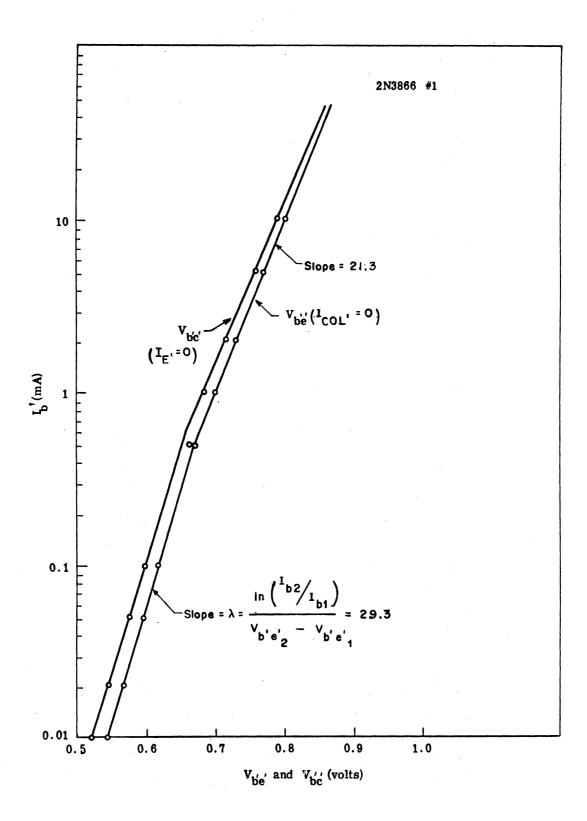

and semi-logarithmic plots of the characteristics for the emitter-base and collector-base junctions are expected to be straight lines with slopes of  $\lambda$  .

Experimental data<sup>1</sup> for a 2N3866 transistor are plotted in Fig. 2.9 and the slopes of both the base-collector and the base-emitter characteristics indicate a  $\lambda$  value of 21.3 (volts<sup>-1</sup>) suitable for base currents greater than 500 microamperes. For base currents less than 500 microamperes, the slope changes to suggest  $\lambda = 29.3$  (volts<sup>-1</sup>).

Evaluation of  $Q_{RS}$  and  $Q_{FS}$  can be made by substitution of experimental I-V data points into Eqs. 2.11 and 2.12.

$$Q_{RS} \approx \frac{I_{b'c'}^{\alpha} \alpha_{R}^{\tau} R}{(1 - \alpha_{F}^{\alpha} \alpha_{R})} e^{-\lambda V_{b'c'}} = 1.16 \times 10^{-18} \text{ coulomb}$$

$$V_{b'c'} = 0.796 \text{ volt}$$

$$I_{b'c'} = 10 \text{ mA}$$

<sup>&</sup>lt;sup>1</sup> For this data it is assumed that the junction potentials were the same as the potentials applied to the device terminals; i.e., for the low current levels involved, ohmic potential drops in the bulk semiconductor material can be neglected.

Fig. 2.9. Static behavior of junctions

$$Q_{FS} \approx \frac{I_{b'c'}^{\alpha} F^{\tau} F}{(1 - \alpha_{F}^{\alpha} R)} e^{-\lambda V_{b'e'}} = 4.66 \times 10^{-21} \text{ coulomb}$$

$$V_{b'e'} = 0.808 \text{ volt}$$

$$I_{b'e'} = 10 \text{ mA}$$

with

$$\alpha_{\rm F}=0.988$$

,  $\alpha_{\rm R}=0.667$ ,  $\tau_{\rm F}=1.1\,{\rm x}\,10^{-10}$ ,  $\tau_{\rm R}=2.56\,{\rm x}\,10^{-8}$ ,  $\lambda=21.3$ .

## 2.4 Numerical Difficulty with Charge Controlled Model

Computer analysis using the charge controlled transistor model of Fig. 2.1 is subject to a numerical difficulty—the dynamic range of the charge variables can exceed the dynamic range of the computer.

This difficulty is easily illustrated by a simple example.

For the IBM 360/67 machine the smallest argument permissible for computing natural logarithms is on the order of  $10^{-70}$ . Recalling the form of an equation for one of the junction potentials, e.g.,  $v_{E'B'} = -(1/\lambda) \ln \left(1 + \frac{q_F}{Q_{FS}}\right)$ , we see that the largest reverse bias potential that can be computed is limited by the argument of the natural logarithm. In this example, the machine limit of  $10^{-70}$  for the argument corresponds to the largest reverse bias potential that can be handled directly. This limit on the potential would be

$$v_{E'B'_{max}} = \frac{\ln(10^{-70})}{-\lambda} = 4.025 \text{ volts}$$

For typical class C amplifiers we expect to encounter reverse

junction potentials well in excess of this 4 volt limit, and some technique must be employed to overcome this limitation. Several circuit modifications and the related numerical modifications to extend the dynamic range of the charge control model are suggested in the following three sections.

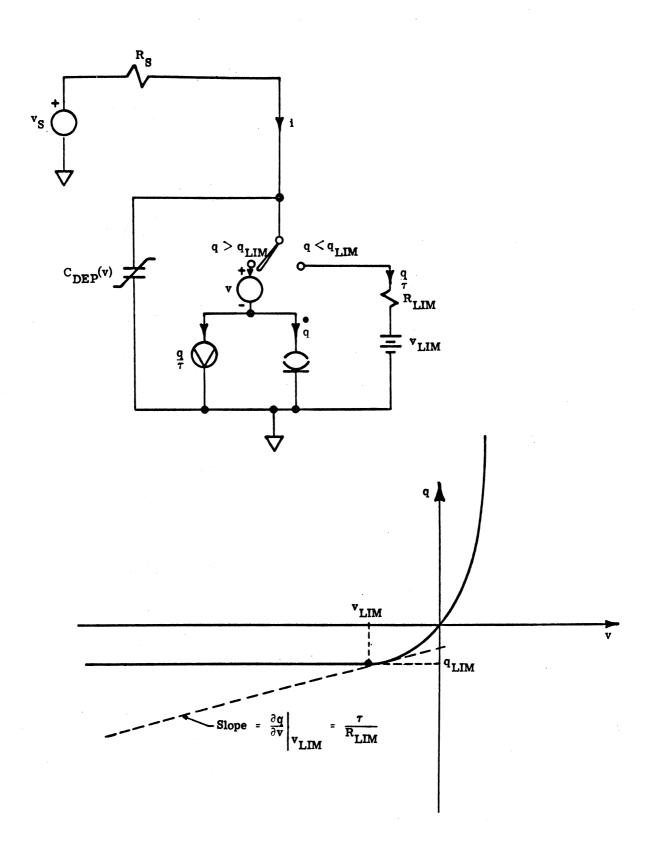

2.4.1 Numerical Approximation with Shunt Resistance. As one possibility for overcoming the numerical limit to the reverse bias potential, consider shunting each semiconductor junction with a large resistance as the numerical logarithmic limit is approached. Using a single diode junction for an example (Fig. 2.10), the equations to be solved under forward bias and small reverse bias conditions would be

$$\left[1 + \frac{C_{DEP}(v)}{\lambda Q_{S}(1 + q/Q_{S})}\right] \dot{q} = -\frac{q}{\tau} + i \qquad (2.14)$$

$$v = (1/\lambda) \ln \left(1 + \frac{q}{Q_S}\right) \qquad (2.15)$$

$$i = \frac{v_S - v}{R_S}$$

(2.16)

Now suppose we choose a small limiting value of the logarithmic argument,  $\epsilon$ , which is slightly larger than the machine limit.

$$\epsilon = 1 + \frac{q_{LIM}}{Q_S} > 10^{-70}$$

This corresponds to determining a limiting value for reverse bias potential.

Fig. 2.10. Diode with shunt resistance to avoid numerical limit

$$v_{LIM} = -\frac{1}{\lambda} \ell n(\epsilon)$$

When this limiting potential is exceeded in the computation, the diode equations can be approximated as:

$$\left(\frac{C_{DEP}(v) \cdot R_{LIM}}{\tau}\right) \dot{q} = -\frac{q}{\tau} + i \qquad (2.18)$$

$$v = \frac{R_{LIM}}{\tau} q + v_{LIM} \qquad (2.19)$$

$$i = \frac{v_S - v}{R_S}$$

(2.20)

where

$$R_{LIM} = \frac{\partial v}{\partial \frac{q}{\tau}} = \frac{\lambda Q_{S}}{\tau} \left(1 + \frac{q_{LIM}}{Q_{S}}\right)$$

(2.21)

and

$$q_{LIM} \stackrel{\Delta}{=} Q_{S}(\epsilon - 1)$$

This procedure is illustrated graphically in Fig. 2.10 and provides an effective method for extending the computational dynamic range of the charge control model.

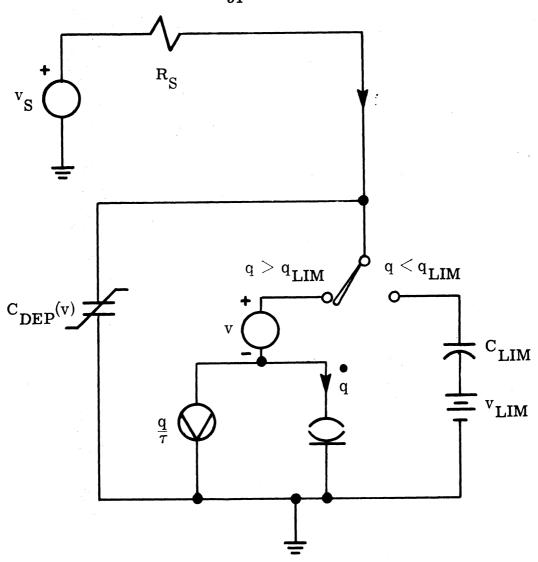

2.4.2 Numerical Approximation with Shunt Capacitance. As an alternate procedure we could switch in a limiting value of shunt capacitance instead of the shunt resistance (Fig. 2.11). In a manner similar to that used for the shunt resistance, we define a capacitance

Fig. 2.11. Diode with shunt capacitance to avoid numerical limit

$$C_{LIM} = \frac{q_{LIM}}{v_{LIM}}$$

(2.22)

and when the limiting potential is exceeded, we are left with the equations

$$\left[\frac{C_{LIM} + C_{DEP}(v)}{\lambda Q_{S} \left(1 + \frac{q}{Q_{S}}\right)}\right] \dot{q} = i \qquad (2.23)$$

$$v = \frac{q}{C_{L,IM}} + V_{L,IM}$$

(2.24)

$$i = \frac{v_S - v}{R_S}$$

(2.25)

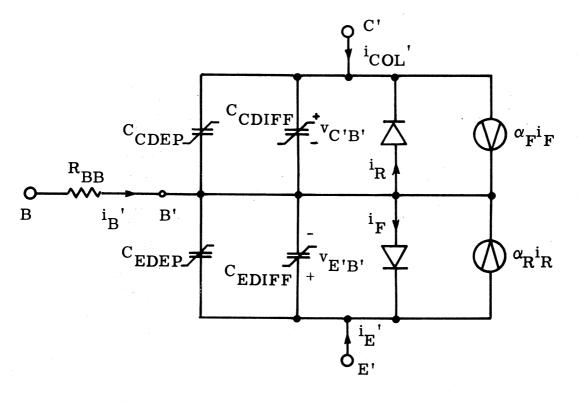

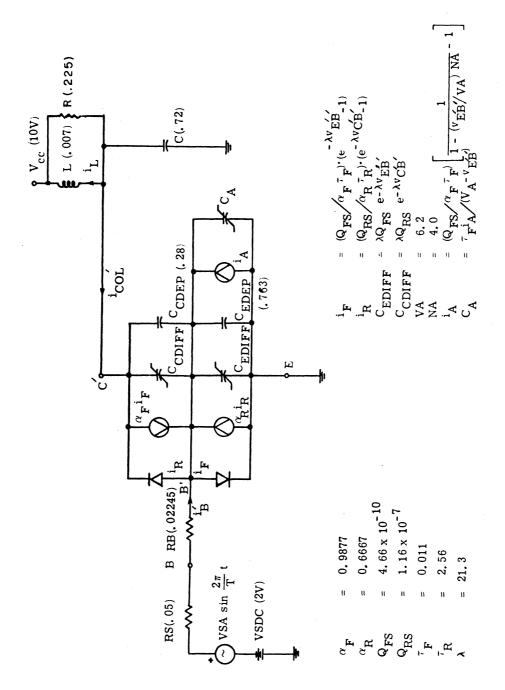

2.4.3 Transformation to Voltage-Control Model. A third approach that can be used to circumvent the numerical difficulties involved in dealing with large reverse-bias potentials with the charge-control model is to transform the charge-control equations to an equivalent set of voltage-control equations and to shift the state variables from charge to voltage. This change of controlling variable from charge to voltage is demonstrated in Appendix B and results in the intrinsic voltage controlled transistor model described by Eqs. 2.26 - 2.31 and illustrated in Fig. 2.12.

$$i'_{B} = (1 - \alpha_{F}) i_{F} - C_{E_{DIFF}} \dot{v}_{E'B'} + (1 - \alpha_{R}) i_{R}$$

$$- C_{CDIFF} \dot{v}_{C'B'} - C_{EDEP} \dot{v}_{E'B'} - C_{CDEP} \dot{v}_{C'B'}$$

(2.26)

$$i'_{COL} = \alpha_F i_F - i_R + C_{CDIFF} \dot{v}_{C'B'} + C_{CDEP} \dot{v}_{C'B'}$$

(2.27)

$$i_{\mathbf{F}} = \frac{Q_{\mathbf{FS}}}{\alpha_{\mathbf{F}} \tau_{\mathbf{F}}} \left( e^{-\lambda v_{\mathbf{E'B'}}} - 1 \right)$$

(2.28)

$$i_{R} = \frac{Q_{RS}}{\alpha_{R} \tau_{R}} \left( e^{-\lambda v_{C'B'}} - 1 \right)$$

(2.29)

$$\begin{split} \mathbf{i_{B}'} &= (\mathbf{1} - \alpha_{\mathbf{F}}) \ \mathbf{i_{F}} - \mathbf{C_{EDIFF}} \ \mathbf{\mathring{v_{E'B'}}} + (\mathbf{1} - \alpha_{\mathbf{R}}) \ \mathbf{i_{R}} - \mathbf{C_{CDIFF}} \ \mathbf{\mathring{v_{C'B'}}} \\ &- \mathbf{C_{EDEP}} \ \mathbf{\mathring{v_{E'B'}}} - \mathbf{C_{CDEP}} \ \mathbf{\mathring{v_{C'B'}}} \\ \mathbf{i_{COL'}} &= \alpha_{\mathbf{F}} \mathbf{i_{F}} - \mathbf{i_{R}} + \mathbf{C_{CDIFF}} \ \mathbf{\mathring{v_{C'B'}}} + \mathbf{C_{CDEP}} \ \mathbf{\mathring{v_{C'B'}}} \end{split}$$

$$i_{\mathbf{F}} = \frac{Q_{\mathbf{FS}}}{\alpha_{\mathbf{F}} \tau_{\mathbf{F}}} \left( e^{-\lambda v_{\mathbf{E'B'}}} - 1 \right)$$

$$i_{R} = \frac{Q_{RS}}{\alpha_{R} \tau_{R}} \left( e^{-\lambda v_{C'B'}} - 1 \right)$$

$$C_{EDIFF} = \lambda Q_{FS} e^{-\lambda v_{E'B'}}$$

$$C_{CDIFF} = \lambda Q_{RS} e^{-\lambda v} C'B'$$

Fig. 2.12. Intrinsic voltage controlled model of NPN transistor

$$C_{EDIFF} = \lambda Q_{FS} e^{-\lambda v_{E'B'}}$$

(2.30)

$$C_{CDIFF} = \lambda Q_{RS} e^{-\lambda v_{C'B'}}$$

(2.31)

This model is essentially a dynamic Ebers-Moll model and as mentioned previously is mathematically (but not computationally) identical to the charge controlled model. The parameters have been left in the form of the charge parameters to enhance the relationship between the two models. This transformation from charge control variables to voltage control variables for the transistor model provides a useful method for achieving the numerical range required for analyses of large signal amplifiers and will be used for the analyses considered in this study.

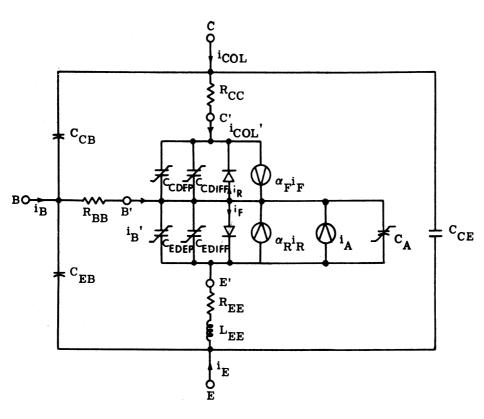

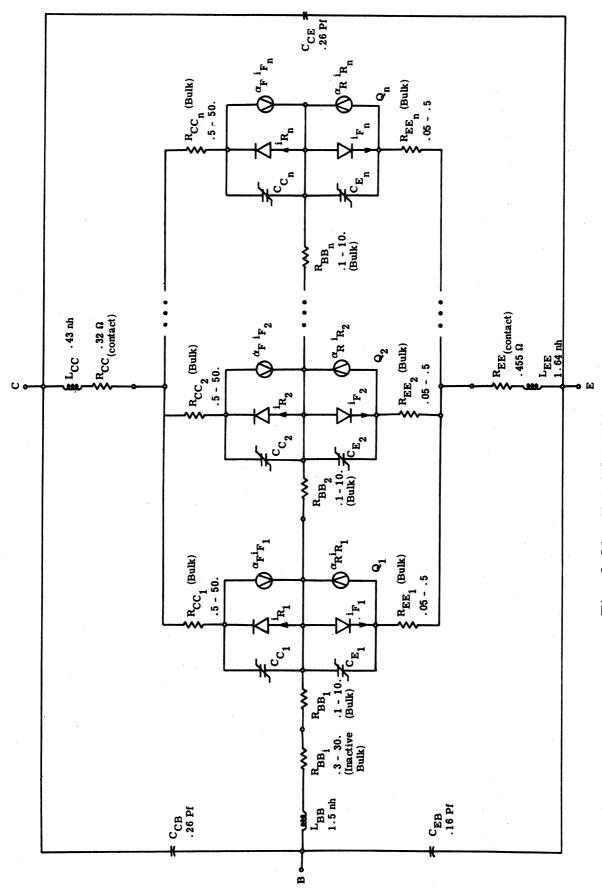

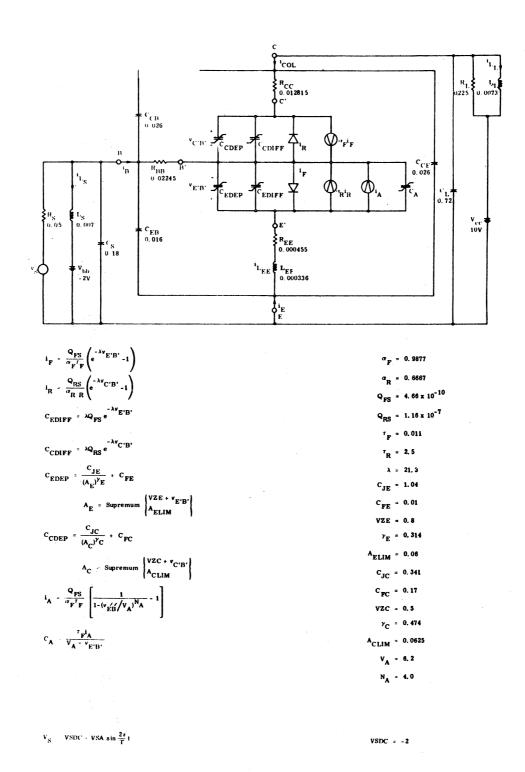

## 2.5 Extended Voltage Controlled Transistor Model

In order to account for several important large-signal and high-frequency characteristics of VHF power transistors not contained in the intrinsic transistor models, the intrinsic model has been extended by the addition of fixed extrinsic elements ( $R_{BB}$ ,  $R_{CC}$ ,  $R_{EE}$ ,  $L_{EE}$ ,  $C_{EB}$ ,  $C_{CB}$ ,  $C_{CE}$ ) and controlled avalanche current elements ( $I_{A}$ ,  $I_{CA}$ ). The resultant extended voltage controlled transistor model (Eqs. 2.26 - 2.35 and Fig. 2.13) is a nonlinear wideband description of a NPN transistor.

$$C_{EDEP} = \frac{C_{JE}}{(VZE + v_{E'B'})^{\gamma_E}} + C_{FE}$$

(2.32)

$$i_{B}^{i} = (1 - \alpha_{F}) i_{F} - C_{E_{DIFF}} \dot{v}_{E'B'} + (1 - \alpha_{R}) i_{R}$$

$$- C_{CDIFF} \dot{v}_{C'B'} - C_{EDEP} \dot{v}_{E'B'} - C_{CDEP} \dot{v}_{C'B'}$$

$$i_{COL}^{i} = \alpha_{F} i_{F} - i_{R} + C_{CDIFF} v_{C'B'} + C_{CDEP} \dot{v}_{C'B'}$$

$$i_{F} = \frac{Q_{FS}}{\alpha_{F} \tau_{F}} \left( e^{-\lambda v_{E'B'}} - 1 \right)$$

$$i_{R} = \frac{Q_{RS}}{\alpha_{R} \tau_{R}} \left( e^{-\lambda v_{C'B'}} - 1 \right)$$

$$C_{EDIFF} = \lambda Q_{FS} e^{-\lambda v_{C'B'}}$$

$$C_{CDIFF} = \lambda Q_{RS} e^{-\lambda v_{C'B'}}$$

$$C_{EDEP} = \frac{C_{JE}}{(v_{ZE} + v_{E'B'})^{\gamma_{E}}} + C_{FE}$$

$$C_{CDEP} = \frac{C_{JC}}{(v_{ZC} + v_{C'B'})^{\gamma_{C}}} + C_{FC}$$

$$i_{A} = \frac{Q_{FS}}{\alpha_{F} \tau_{F}} \left[ \frac{1}{1 - (v_{CPD} / V_{A})^{N_{A}}} - 1 \right], C_{A} = \frac{\tau_{F} i_{A}}{V_{A} - v_{E'B'}}$$

Fig. 2.13. Extended voltage controlled model of NPN transistor

$$C_{CDEP} = \frac{C_{JC}}{(VZC + v_{C'B'})^{\gamma_C}} + C_{FC}$$

(2.33)

$$i_{A} = \frac{Q_{FS}}{\alpha_{F} \tau_{F}} \left[ \frac{1}{1 - (v_{E'B'}/V_{A})^{N_{A}}} - 1 \right]$$

(2.34)

$$C_{A} = \frac{\tau_{F}^{i} A}{V_{A} - V_{E'B'}}$$

(2.35)

The expressions for the depletion capacitances (Eqs. 2.32 and 2.33) apply to the intrinsic model as well as this extended model. Experimental determination of the depletion capacitance and the extrinsic element parameters is considered in the following sections.

2.5.1 Model Capacitances. Neglecting the avalanche capacitance, <sup>1</sup> the emitter-base and collector-base capacitances each consist of three components:

$$C_{E} = C_{EDIFF} + C_{EDEP} + C_{ECASE}$$

(2.36)

$$C_{C} = C_{CDIFF} + C_{CDEP} + C_{CCASE}$$

(2.37)

diffusion components, depletion layer components, and fixed mounting or case components. Small-signal low-frequency measurements of

<sup>&</sup>lt;sup>1</sup>The avalanche capacitance, C<sub>A</sub>, is an artificially introduced element to be discussed in Section 2.5.2, and as such it has no effect on the device capacitances under consideration here.

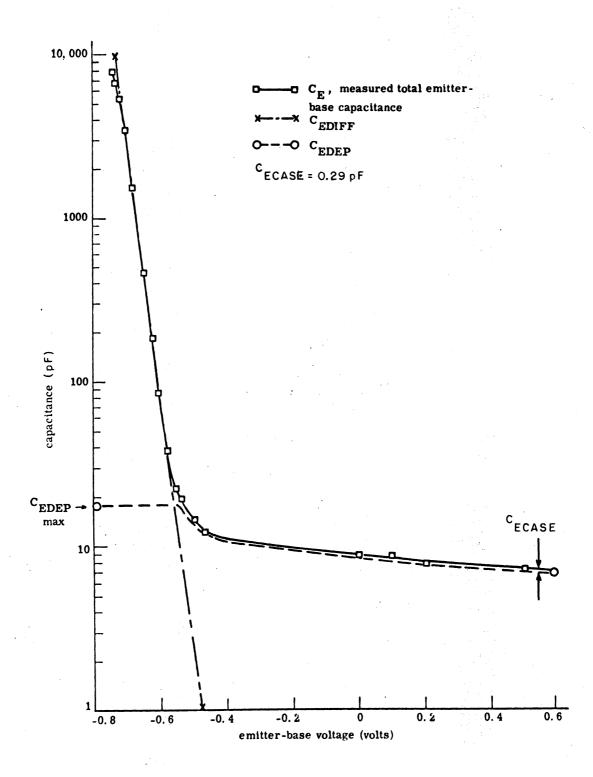

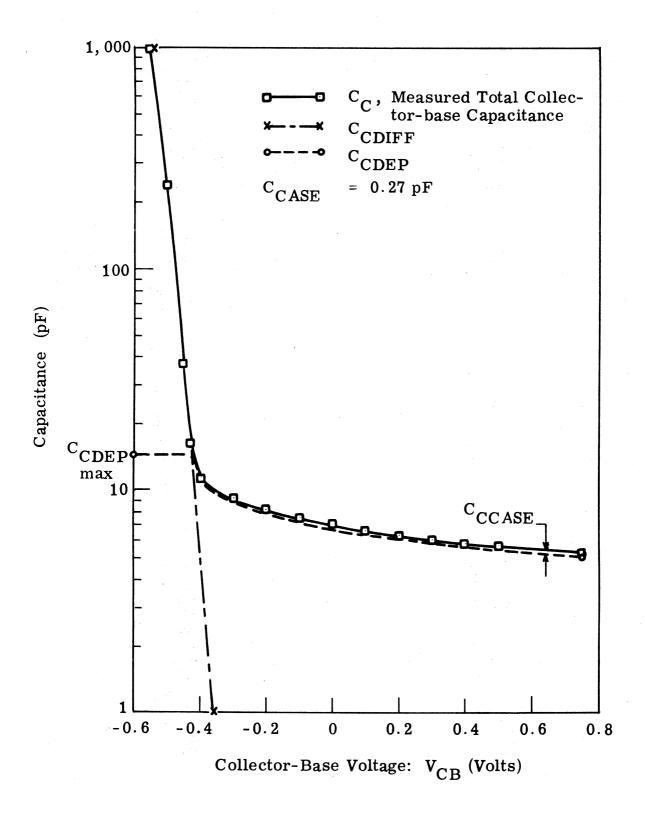

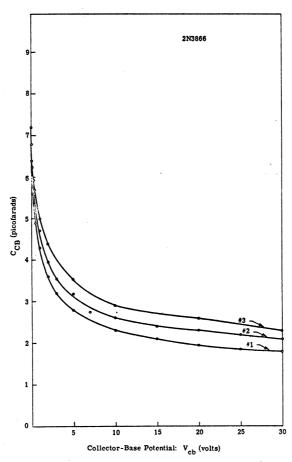

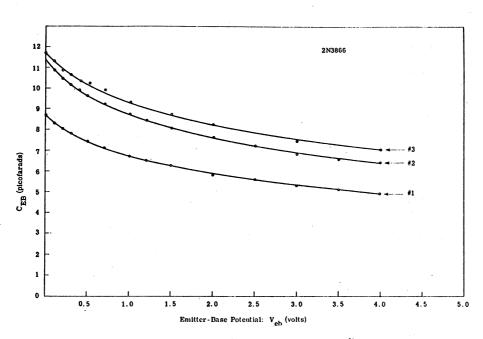

these total capacitances of a 2N3866 transistor as functions of the junction potentials led to the behaviors illustrated in Figs. 2.14 and 2.15.

$$C_{EB} = 0.16 \text{ pF}$$

$C_{CB} = 0.26 \text{ pF}$

$C_{CE} = 0.26 pF$

With the interelectrode capacities determined, equivalent case capacities can be subtracted from the total capacitances as indicated in Figs. 2.14 and 2.15. For this subtraction we have defined

$$C_{\text{ECASE}} \stackrel{\Delta}{=} C_{\text{EB}} + \frac{C_{\text{CE}} C_{\text{CB}}}{C_{\text{CE}} + C_{\text{CB}}} = 0.29 \text{ pF}$$

$$C_{CCASE} \stackrel{\Delta}{=} C_{CB} + \frac{C_{CE} C_{EB}}{C_{CE} + C_{EB}} = 0.27 \text{ pF}$$

Fig. 2.14. Components of emitter-base capacitance of 2N3866

Fig. 2.15. Components of collector-base capacitance of 2N3866