# THE UNIVERSITY OF MICHIGAN COMPUTING RESEARCH LABORATORY<sup>1</sup>

#### OPTIMAL INSTRUCTION SCHEDULING FOR A CLASS OF VECTOR PROCESSORS: AN INTEGER PROGRAMMING APPROACH

Siamak Arya

CRL-TR-19-83

**APRIL 1983**

Room 1079, East Engineering Building Ann Arbor, Michigan 48109 USA Tel: (313) 763-8000

<sup>&</sup>lt;sup>1</sup>Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the funding agency.

VMR3118

### OPTIMAL INSTRUCTION SCHEDULING FOR A CLASS OF VECTOR

PROCESSORS: AN INTEGER PROGRAMMING APPROACH

#### by Siamak Arya

A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer, Information, and Control Engineering) in The University of Michigan 1983

#### Doctoral Committee:

Professor Donald A. Calahan, Chairperson Assistant Professor John R. Birge Assistant Professor Trevor N. Mudge Professor Norman R. Scott Associate Professor Toby J. Teorey

#### **ABSTRACT**

## OPTIMAL INSTRUCTION SCHEDULING FOR A CLASS OF VECTOR PROCESSORS: AN INTEGER PROGRAMMING APPROACH

by

#### Siamak Arya

integer programming model that portrays the architectural features of a class of vector and array processors has been developed. This model is used to produce optimal schedules for low-level-instruction codes of such processors. Optimal schedules are produced for both straight codes and instruction loops. The model is extended to optimally reassign registers to instructions in addition to instruction sequencing. The model is further extended to consider processors with multiple identical functional units. A study of the complexity of the model shows that the scheduling time increases exponentially with the number of instructions. Using the model, a number of experiments have been conducted in optimal scheduling of Cray assembly codes.

• <u>Siamak Arya</u> 1983 All Rights Reserved To

my father, my mother,

Anna, Flooria, and Sohrab

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to thank the members of my committee, my family, and my friends who have provided me with their time, ideas, and support during the course of this research.

I am especially grateful to Professor Donald A. Calahan for providing me with his friendship, guidance, encouragement, and inspiration. He always found the time to helpfully respond to my questions and problems.

I would like to express my appreciation to Professors Birge, Scott, Teorey, and Mudge for the care and wisdom they demonstrated during the supervision of this project. My special gratitude is extended to Professor James C. Bean with whom I have had many inspiring discussions.

My family has played a vital role in encouraging me to pursue a doctorate and in supporting me through out the process. I wish to express my warmest appreciation and love to them for their significant contributions to my progress.

Abundant thanks and love are extended to my friends-- Monica Robinson, Berit Ingersoll, Denise Goulet, Sadegh Moslehi, Khosrow Hadavi, and Tony Da Silva whose friendship and interest in my progress served as a source of

sustenance and enrichment. Special gratitude and love are extended to Monica who contributed indirectly by patiently adjusting her plans to accommodate me and directly by skillfully drawing the graphs for this dissertation.

The personal and intellectual support of each of these individuals has contributed to making this dissertation process an exciting and a pleasant experience.

#### TABLE OF CONTENTS

| DEDICATI | ONS        |       | •   | •  | •   | •   | •   | •   | •          | •    | •    | •        | •           | •   | •   | •        | •     | •     | •      | •  | i                               |

|----------|------------|-------|-----|----|-----|-----|-----|-----|------------|------|------|----------|-------------|-----|-----|----------|-------|-------|--------|----|---------------------------------|

| ACKNOWLE | EDGEM      | MENTS | •   | •  | •   | •   | •   | •   | •          | •    | •    | •        | •           | •   | •   | •        | •     | •     | •      | •  | iii                             |

| LIST OF  | FIGU       | JRES  | •   | •  | •   | •   | •   | •   | •          | •    | •    | •        |             | •   | •   | •        | •     | •     | •      | •  | viii                            |

| CHAPTER  |            | •     |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    |                                 |

| I.       | INTE       | RODUC | rio | N  | •   | •   | •   | •   | •          | •    | •    | •        | •           | •   | •   | •        | •     | •     | •      | •  | 1                               |

|          | A.         | Objec | cti | ve |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 2                               |

|          |            | Reduc |     |    | om  | pu  | ıta | ti  | or         | T    | in   | ie       |             |     | •   | •        |       | •     | •      | •  | 2                               |

|          |            | Limit |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 3                               |

|          | D.         | A Scl | hed | úl | in  | q   | Pr  | ob  | 16         | em   | •    | •        |             |     | •   |          |       |       |        | •  | 2<br>3<br>4<br>5<br>5<br>6<br>7 |

|          |            | A Sci | 1.  | Α  | Jo  | b-  | Sh  | qor | F          | Pro  | bl   | .en      | 1           |     | •   |          | •     | •     |        | •  | 5                               |

|          |            | D.    | 2.  | So | lv  | in  | pı  | Jo  | b-         | -Sh  | op   | F        | ro          | b]  | len | ıs       |       |       |        |    | 5                               |

|          | E.         | Micro |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 6                               |

|          |            |       | 1.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 7                               |

|          |            |       | 2.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 8<br>9<br>9                     |

|          | F.         | Prob. |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 9                               |

|          |            | The 1 |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 9                               |

|          | н.         | Regis | ste | r  | Re  | -a  | 155 | sia | nn         | nen  | t    | •        | •           | •   | •   |          | •     |       | •      | •  | 10                              |

|          |            | Mult  |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 12                              |

|          | J.         | Comp  | lex | it | V   | of  | 7   | 'he | N          | 4od  | le l |          |             |     | •   | •        | •     |       | •      | •  | 12                              |

|          | ĸ.         | Imple | eme | nt | āt  | ic  | n   | of  | 7          | l'he | M    | 100      | le]         | L   | •   | •        | •     | •     | •      | •  | 13                              |

|          |            |       |     |    |     | _   |     | -   | _          |      |      |          |             |     | •   | •        | •     | •     |        | •  |                                 |

| II.      | THE        | MODE  | L   | •  | •   | •   | •   | •   | •          | •    | •    | •        | •           | •   | •   | •        | •     | •     | •      | •  | 14                              |

|          | λ.         | Arch  | ite | ct | ur  | a l | F   | rea | tı         | ıre  | S    |          | _           | _   |     | _        |       |       | _      |    | 15                              |

|          |            | The I |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 17                              |

|          | _,         |       | 1.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 19                              |

|          |            |       | 2.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 22                              |

|          |            |       | 3.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    |                                 |

|          |            |       | ••  |    |     | -   | Ti  | an  | S          | iti  | vi   | t        | , ••••<br>7 |     |     | ,        | _     | _     |        |    | 25                              |

|          | C.         | Elem  | ent | ar | v   | Тi  | m   | no  | ı          | Mod  | اجا  |          |             | •   | •   | •        | •     | •     | •      | •  | 27                              |

|          |            | C.    | 1.  | Mi | ni  | mı  | ım  | Тì  | m <i>e</i> | . F  | 7    | -<br>bbl | en          | n   | •   | •        | •     | •     | •      | •  | 27                              |

|          |            |       | 2.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 28                              |

|          | n.         | Sche  |     |    |     |     |     |     |            |      |      |          |             |     |     | •        |       | •     | •      | •  | 30                              |

|          |            |       | 1.  |    |     |     |     |     |            |      |      |          |             |     |     | •<br>15t | · r = | ir    | •<br>1 | •  | 30                              |

|          |            |       | 2.  |    |     |     |     |     |            |      |      |          |             | •   |     |          |       | if]   |        |    | 30                              |

|          |            |       |     | •  |     |     |     |     |            | rai  |      | - 5      |             |     |     |          |       |       |        |    | 32                              |

|          |            | D.    | 3.  | FU | C   | or. |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 32                              |

|          |            |       | 4.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 33                              |

|          |            |       | 5.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 34                              |

|          |            |       | 6.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       |        |    | 34                              |

|          | F.         | Asyn  |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       | . a . |        | LJ | 35                              |

|          | • ت        |       | 1.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       | •     | •      | •  | 36                              |

|          |            |       |     |    |     |     |     |     |            |      |      |          |             |     | •   |          |       |       |        |    | 38                              |

|          | <b>E</b>   |       | 2.  |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       | •      | •  | 36                              |

|          |            | Glob  |     |    |     |     |     |     |            |      |      |          |             |     |     |          |       |       | •      | •  | 43                              |

|          | <b>G</b> • | Loop  |     |    |     |     |     |     |            |      |      |          |             |     | •   |          |       |       |        | •  |                                 |

|          |            |       | 1.  |    |     |     |     | _   |            |      |      | -        | •           |     |     | •        |       | •     |        | •  | 44                              |

|          |            | G.    | 2.  | TU | ıte | r   | -11 | cer | a          | כוכ  | n    | De       | epe         | enc | aer | IC 1     | es    | 3     | •      | •  | 44                              |

|      |          | G.3.<br>G.4. | Stea  | dy S                                    | Stat       | e           |       | •        | •        | •    | •         | •   | •      | •   |     | 46<br>46 |

|------|----------|--------------|-------|-----------------------------------------|------------|-------------|-------|----------|----------|------|-----------|-----|--------|-----|-----|----------|

|      |          | G.5.         | Exec  | utio                                    | n-T        | 'ime        | of    | tl       | ne       | Lo   | op        |     | •      | •   |     | 48       |

|      |          | G.6.         | Two-  | raoD                                    | 7 Lo       | go          | Sch   | edi      | ıli      | na   | •         |     |        |     |     | 49       |

|      |          | G.7.         | Floa  | ting                                    | Tu         | mn          |       | _        |          |      | _         |     | _      | _   | •   | 50       |

|      | н.       | Integer      | Pro   | gran                                    | nmin       | g           |       | •        | •        | •    | •         | •   | •      | •   | •   | 51       |

| III. | REGI     | STER RE      | -ASS  | I GNN                                   | ŒNT        |             |       | •        | •        | •    | •         | •   | •      | •   | •   | 55       |

|      | A.       | Modifie      | d Ob  | iect                                    | ive        |             |       |          |          |      |           | •   |        |     |     | 55       |

|      | В.       | Result       | Regi  | ster                                    | Re         | ass         | ian   | mei      | nt       | •    |           |     |        | •   | •   | 56       |

|      |          | Complet      |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 56       |

|      | ח.       | Registe      | r Se  | lect                                    | ion        |             |       | - 5.     |          |      | _         | •   | •      | •   | •   | 57       |

|      | F.       | Changin      | c + h | A 01                                    | iai        | na]         | Mo    | å.       | 1        | •    | •         | •   | •      | •   | •   | 60       |

|      | E.       | Changin      | 9 th  |                                         | . 191      | 1101        | . 140 | Tn.      | _<br>~~: | • 1  | •         | : . | •      | •   | •   | 61       |

|      | r.       | Changin      | g th  | של או                                   | :pen       | iaen        | Cy    | T 116    | =qı      | 19 T | ΙL        | тe  | 5      | •   | •   |          |

|      |          | F.1.         | case  | : 1                                     | • •        | •           | • •   | •        | •        | •    | •         | •   | •      | •   | •   | 63       |

|      |          | F.2.         |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 64       |

|      |          | F.3.         | Exam  | ple                                     | • •        | •           | • •   | •        | •        | •    | •         | •   | •      | •   | •   | 65       |

|      |          | Changin      |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 67       |

|      | Н.       | Branchi      | ng C  | omp]                                    | lica       | tic         | ns    | •        | •        | •    | •         | •   | •      | •   | •   | 70       |

| IV.  | MULT     | CIPLE ID     | ENTI  | CAL                                     | FUN        | CTI         | ONA   | L 1      | UNI      | TS   |           | •   | •      | •   | •   | 74       |

|      | Α.       | Multipl      | e-Id  | ent i                                   | ical       | FT          | 1's   |          |          | _    |           | _   | _      | _   |     | 74       |

|      | R.       | The Two      | -Cor  | v Ca                                    | 356        |             |       |          | •        | •    |           |     |        |     | •   | 76       |

|      | ٥.       | B.1.         | Disc  | rim                                     | inat       | inc         | Be    | •<br>+ w | •<br>aar | ``~  | 'n        | ;_  | •      | •   | •   | 77       |

|      |          |              |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 77       |

|      | •        | B.2.         |       |                                         |            |             |       |          |          |      |           |     |        |     |     |          |

|      | C.       | The Gen      |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 80       |

|      |          | C.1.         |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 81       |

|      |          | C.2.         |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 83       |

|      |          | C.3.         | Two-  | ·Copy                                   | y Ve       | ersi        | on    | •        | •        | •    | •         | •   | •      | •   | •   | 84       |

|      | D.       | Global       | Depe  | ndei                                    | псу        | and         | l Mu  | lt       | ip]      | le   | Co        | рi  | es     | C   | Œ   |          |

|      |          |              | -     |                                         | ΙĪ.        |             |       |          |          |      |           |     |        |     |     | 85       |

| v.   | COMI     | PLEXITY      | OF 1  | י ארי                                   | MODE       | ēТ.         |       |          |          |      |           |     |        |     |     | 87       |

| •    | 0011     |              | 0     | · • • • • • • • • • • • • • • • • • • • | 1001       |             | • •   | •        | •        | •    | •         | •   | •      | •   | •   | 0,       |

|      | A.       | NP-Comp      | olete | nes                                     | s of       | Th          | ne M  | fod      | el       | •    | •         | •   | •      |     | •   | 88       |

|      |          | A.1.         | IP M  | <b>leth</b>                             | ods        | •           |       |          |          |      |           |     |        |     |     | 88       |

|      |          | A.2.         | Inte  | ger                                     | Sol        | luti        | ons   |          |          |      |           |     |        |     |     | 89       |

|      | B.       | Complex      |       |                                         |            |             |       |          |          |      |           |     |        |     |     | 92       |

|      |          | B.1.         | Bour  | ide :                                   | for        | the         | Or    | ·ia      | in:      | ונ   | Мо        | Ab  | i      | •   | •   | 93       |

|      |          | B.2.         | Bour  | ido i                                   | for        | Pac         | i ot  | - 9      | 1 1 1 E  | 200  | rio<br>cc | ic  | ~<br>~ | •   | •   | 75       |

|      |          | B.Z.         | BOU!  | ius .                                   | 701        | Rec         | 1150  | .er      |          | Rea  | 55        | 19  | 11111  | E1. | 1 L | 00       |

|      |          | <b>5</b> 2   |       |                                         | ode]       |             |       |          |          |      |           |     |        |     |     | 99       |

|      |          | B.3.         | Bour  | ias_:                                   | ior        | tne         | MU    | ITT      | ıp.      | Le-  | Ιđ        | en  | τı     | Ca  | ΙŢ  |          |

|      |          |              | _     | F                                       | U's        | •           | • •   | •        | •        | •    | •         | •   | •      | •   | •   | 106      |

|      |          | B.4.         | Sumn  | nary                                    | of         | Con         | ple   | Хi       | tie      | 25   | •         | •   | •      | •   | •   | 110      |

| VI.  | IMPL     | EMENTATI     | ON C  | F T                                     | HE N       | MODE        | EL .  | •        | •        | •    | •         | •   | •      | •   | •   | 112      |

|      | λ        | Pre-Pro      | \Cec  | or                                      |            |             |       |          |          |      |           |     |        |     |     | 112      |

|      | p.       | Integer      | . D*/ | )((r)                                   | mmi        | ייי<br>זמיי | <br>  | •        | •        | •    | •         | •   | •      | •   | •   | 114      |

|      | ۵.       | Tureder      | : F1( | Ara                                     | <br>mm T l | 19 I        | ack   | ay       | C        | •    | •         | •   | •      | •   | •   |          |

|      | <u>.</u> | Schedul      |       | Exp(                                    | er II      | nent        | . S . | •        | •        | •    | •         | •   | •      | •   | •   | 115      |

|      | ם.       | Complex      | ııty  | Exp(                                    | erı        | nent        | 5 .   | •        | •        | •    | •         | •   | •      | •   | •   | 117      |

|      | E.       | Non-Lin      | iear  | Pro                                     | gran       | nıng        | •     | •        | •        | •    | •         | •   | •      | •   | •   | 120      |

| F          | F. Conclusion               | •   | • • | •   | •  |     | • | 120 |

|------------|-----------------------------|-----|-----|-----|----|-----|---|-----|

| VII. CO    | ONCLUSION                   | •   |     | •   | •  |     | • | 123 |

| 7          | A. Applications of The Mode | 1   |     |     |    |     | • | 125 |

| I          | 3. Reducing Scheduling Time | •   |     | •   |    |     | • | 126 |

| (          | C. Research Suggestions     | •   |     | •   |    |     | • | 127 |

|            | C.1. Experiments with       | the | Ext | ten | si | ons | • | 127 |

|            | C.2. Specialized IP .       |     |     |     |    |     |   | 128 |

| •          | C.3. Heuristic Schedul      | ing | •   | •   | •  | • • | • | 128 |

| REFERENCES | 5                           | •   |     |     |    |     |   | 129 |

#### LIST OF FIGURES

| 1. | Sample Graph                                       | 24  |

|----|----------------------------------------------------|-----|

| 2. | Cases not Covered by Pairwise Dependency           | 42  |

| 3. | Sample Loop with Floating Jump                     | 52  |

| 4. | Branching Complications in Register Reassignment   | 72  |

| 5. | Totally Dependent and Independent Graphs           | 95  |

| 6. | Complexity of Bounds on Variables and Inequalities | 111 |

| 7. | Timing Results for Sample Experiments              | 118 |

| 8. | Complexity Information for CAL Codes               | 119 |

#### CHAPTER I

#### INTRODUCTION

In recent years, with the increase in available computing power, the size and complexity of scientific simulation problems have increased accordingly. In a large number of such problems, a significant portion of computation time is spent in a relatively small section of the code [AHO]. In these cases, significant efforts to reduce the computation time of such small portions of codes may be worthwhile.

Unfortunately, the optimal control of data flow associated with loops that appear simple in a high level language may be nontrivial for memory-hierarchical functionally-concurrent processors, such the Floating Point System 164 and the CRAY-1. In many important applications, only a fraction of achievable performance is available from a high level language and one must resort low-level-language coding to preserve the efficiency of high performance algorithm development. Indeed, timing simulators have been developed for both of these processors [CSIM] [FSIM], encouraging such programming by algorithm developers. Even with such aids, one is often left with the likelihood that the hand-scheduling of low-level-instruction codes, especially inner loops, is suboptimal. Often one could justify considerable effort in optimal scheduling of only 10-100 low-level instructions.

#### A. Objective

This research is concerned with the minimization of the computation time of low-level instruction codes for the class of register-to-register vector processors (RRVP's). This class of processors is generally defined as processors a) that utilize pipelining to achieve speedups on vector (array) operations and b) for which these vector elements flow from registers through functional units (FU's) and back to registers. Among commercial processors, the CRAY family is the closest to this model, although other vector and array processors share many of the features of this model.

#### B. Reduced Computation Time

Sequential execution of instructions results in maximum computation time. In contrast, minimum time is reached when the maximum number of instructions are executed simultaneously throughout the computation. The latter can be achieved by using RRVP's since these processors may provide a number of FU's that can simultaneously operate on different instructions.

Concurrent use of the FU's of RRVP's can be achieved by a careful arrangement of the instructions of these

processors. Such requirements reduce the ability of the average user of such processors to benefit from their full potential. However, that reduction in benefits may be avoided by using optimal instruction scheduling methods.

To efficiently use the FU's of RRVP's, one can resort to low-level languages that provide the ability to directly manipulate the use of the FU's. Experience has shown that the amount of reduction in total computation time makes it worthwhile to code in low-level languages. Then, the challenge is to find a method that is capable of scheduling the instructions of low-level codes so that maximum FU concurrency and minimum computation time are achieved.

#### C. Limiting the Scope of the Problem

This research has been focused on minimization of total computation times of low-level instruction codes of RRVP's through optimal code scheduling. The reduction in total computation time can be achieved in a number of ways. Such approaches include special considerations during and after the generation phase of the code, [COHA] [NELS]. In this research, it is assumed that a code with a fixed number of instructions is available and its computation time is to be minimized by rearranging the sequence of instructions without changing either the logic or the number of the instructions.

#### D. A Scheduling Problem

The theory of scheduling deals with the proper sequencing of a set of jobs in the presence of a set of constraints to achieve the objective of the problem. sequence of jobs is said to be proper if it satisfies the objective and the constraints of the scheduling problem. Two types of constraints can be imposed on a problem-- 1) precedence constraints and 2) resource constraints. Precedence constraints dictate a specific issue-time order on the pairs of jobs in the sequence, to of the ensure the correctness schedule. constraints impose limits on the number of resources that are available to be used by various jobs. Hence, the theory of scheduling is the subject that deals with proper sequencing of a set of constrained jobs to satisfy a specific objective, using a constrained set of resources.

Scheduling problems can be divided into three classes of problems regarding the constraints imposed on these problems. These three classes are— 1) scheduling with precedence constraints, 2) scheduling with resource constraints, and 3) scheduling with precedence and resource constraints. The problem of this research falls under the third category due to the limitations on the number of available registers and FU's and sharing of data between instructions.

#### D.1. A Job-Shop Problem

Optimal scheduling of low-level instructions for RRVP's is a job-shop problem with resource constraints. Each instruction (a job) enters the CPU (job-shop), which contains a specific number of non-identical FU's (machines), and is processed by only one FU before it leaves the shop. It is a special case of a job-shop problem in which each job has only one operation. As in a job-shop problem, a set of precedence constraints must be enforced between the instructions to ensure the proper sequence of executions that produces correct final results. And, since any RRVP has a fixed number of resources that are available to the instructions, the problem is further constrained by resource limitations.

#### D.2. Solving Job-Shop Problems

In the literature of scheduling, a variety of methods have been introduced to solve job-shop problems. Two main approaches to optimally solve these problems are Active Schedule Generation, [THOM], and Integer Programing (IP) methods, [GREE] [PRIT]. The former approach starts with an empty schedule, considers the next available job, and creates new partial schedules accordingly. This process is repeated for each job to be scheduled. When all of the jobs are considered, a set of active schedules result. Optimal schedules are chosen from the set of active ones. The schedule generation procedure can be either enumerative

or Branch & Bound (B&B) [STIN].

The integer programming approach in solving job-shop problems is a combinatorial one that uses a set of inequalities to represent the problem. A feasible schedule is one that satisfies all of such inequalities. Optimal schedules are selected from the set of feasible ones. The generation of such schedules is often achieved by combined Linear Programming (LP) and B&B techniques.

None of the existing methods can be directly applied to solve the instruction scheduling problem of this research, due principally to the number of various types of constrained resources that must be considered. Nevertheless, Baker's [BAKE] integer programming approach to solve job-shop problems without resource constraints has provided a good starting point.

#### E. Micro-Code Compaction

The instruction scheduling problem of this research is closely related to the problem of micro-code compaction [TRAN]. Both of these studies attempt to distinguish groups of instructions or micro-operations that can be concurrently or must be sequentially processed. This information is used to maximize the concurrent use of the resources of vector- and micro-processors in order to reduce computation time. The main difference between these problems is the issuing of instructions and micro-operations by vector- and

micro-processors, respectively. An RRVP can issue one instruction at a time, in contrast to a micro-processor that can issue a number of micro-operations at once.

In micro-code compaction, data- and resource-independent micro-operations' are grouped into one micro-instruction and are issued simultaneously. In instruction scheduling, no more than one instruction can be issued at any clock-time. And, if two or more instructions compete for a specific issue time, the issue times of all but one of these instructions will be delayed. The issue time delay for some instructions can play a significant role in the arrangement of the rest of the instructions.

The number of papers that have recently been published on micro-code compaction shows a sign of growing interest in this optimization problem. Tokoro et all [TOKO] point out that most of the present compaction methods assume one machine-cycle-time processing time for any micro-operation. They also state that micro-operation execution time in most practical machines requires more than one cycle-time, especially for memory reference operations or operations on pipelined machines.

#### E.1. One Cycle-Time Restriction

The restriction of one cycle-time execution-time for

<sup>&#</sup>x27;Instructions and micro-operations are the lowest-level-language commands that can be issued by vector- and micro-processors, respectively.

each operation provides a simplified version for the compaction problem. Since each resource is reserved for only one cycle-time, all of the resources are available to the micro-operations at the beginning of the next cycle. Therefore, it is sufficient to find the operations that have no precedence constraints or have already satisfied this condition, and combine them into a micro-instruction if they do not require the same resource.

#### E.2. Elimination of the Restriction

To eliminate this restriction, Tokoro et al assume that operations can take longer than one cycle-time from the of issue to the time termination Therefore, to combine micro-operations, these execution. operations should not require a resource which is reserved by a previous operation, in addition to the previous conditions that should be satisfied. The latter condition is stated as a set of "either or" inequalities. If these inequalities are satisfied, that is if the FU required by the operation is not reserved by a previous one, the operations can be combined with the ones that are currently ready to be issued. Otherwise, the issue time of the is delayed. This operation, then, operation can be combined with the succeeding operations when the above This version of conditions are satisfied. compaction is closest to the problem of this research, since the one cycle time execution time does not hold for RRVP's.

#### F. Problem Specification

This research views the problem of scheduling lowlevel instructions for RRVP's as follows.

#### G. The Model

To produce optimal schedules for low-level codes model an integer programming has developed. The model of this research is capable precisely predicting the behavior of such processors and simplifying the complicated job of managing their resources. Resource-management complications arise from the resourcerequirement conflicts that occur between the instructions; Chapter II provides a detailed description of The total computation time is dependent on how conflicts. well these conflicts are resolved. To resolve these conflicts, each instruction is modeled by a set of inequalities that should be satisfied to maintain relationship with the other instructions while avoiding any conflicts that can increase the computation time. feasible schedule is one that satisfies all of these inequalities. An optimal schedule is a feasible one with minimum computation time. Then, the outcome of the model is a set of specific start times at which instructions must be started to realize the minimum computation time.

addition to straight-code scheduling2, optimal instruction-loop scheduling is also included in the model of this research. Scheduling of instructions in a loop differs from straight-code scheduling in that the set of instructions the loop execute repeatedly and of instructions relationships between the of different repetitions must be considered to produce optimal loop schedules. These relationships play a significant role in loop scheduling for processors with more than one pipelined functional units and vector instructions. If none of these resources exist, the execution of each instruction started after the termination of execution of its preceding Therefore. intra-loop relationships between instructions are not important and the attention is focused on reducing loop overhead during code generation [AHO ] to reduce computation time.

#### H. Register Re-assignment

The optimal schedule for the instructions in a code that is produced by applying the model of Chapter II is optimal relative to a specific order of register-

<sup>&</sup>lt;sup>2</sup>Straight-code scheduling refers to scheduling of instructions in a basic-block [AHO], that is a piece of code that can be entered only at the beginning and does not include any branching instructions or entry points.

assignments. Because a limited number of registers are available, each register must be used by a number of instructions. The sharing of registers by instructions can force a delay in the execution of instructions that must wait for specific registers to become available. Such delays that can increase the computation time may be avoided by a change in the register-assignment sequence. Thus, the model of this research is extended to optimally reassign instructions in accordance with optimal registers to instruction sequencing. Hence, the extended model produces optimal-schedules with respect to register assignment and instruction sequencing. The register-reassignment portion of the model is described in Chapter III.

Register reassignment of this research differs from the register allocation problem in that the latter usually a compile time problem to reduce excessive use of Register allocation studies are the storage. concerned with the use of registers to reduce the transfer of data to and from main memory, [FREI] [DAY] [BEAT], in order to reduce the size of the code and/or the use of the memory to minimize the computation time. Study of the number of required registers to avoid memory minimum transfers [SETH] is also categorized as register as allocation problem. However, the allocation problem of this research is concerned with changing the original assignment of registers to instructions so that concurrent execution of higher number of instructions are made possible.

#### I. Multiple-Identical FU's

The model is further extended to deal with the case in which duplicate copies of one or more of the FU's are added to the configuration of the processor. In other words, the processor contains m groups of non-identical FU's where each group is composed of p identical FU's. For  $p \le 2$ , the extension minimally alters the model. However, for p > 2, a more complicated extension is needed. This subject is discussed in Chapter IV.

Scheduling jobs on identical machines has received a great deal of attention in the literature scheduling. This study is mainly concentrated on the scheduling of independent jobs or dependent ones with identical execution times [BAKE] [SAHN]. The problem of this research is a more general one. It is the study of scheduling jobs on identical machines in the presence of precedence constraints where the execution times of instructions are not identical. Again, the goal is to find optimal schedules.

#### J. Complexity of the Model

The problem of optimal scheduling of low-level instructions of RRVP's is NP-complete. That is due to the nature of the problem (job-shop) and use of integer programming. This research has shown that for optimal scheduling of these codes, use of integer programming

cannot be avoided. A study of the complexity of the number of variables and inequalities required for modeling such codes has been conducted to help realize the complexity of time and storage requirements for the implementation of the model. Chapter V deals with these subjects.

#### K. Implementation of The Model

The IP model of this research has been used in optimal scheduling of a number of Cray assembly codes. The scheduling process is composed of three phases: (a) generating the inequalities that model the code, (b) solving the inequalities using an IP, and (c) rearranging the order of instructions according to the optimal sequence. A program that is capable of producing the inequalities of phase (a) has been developed. Using this program and an IP, a number of scheduling experiments have been conducted. The results of the experiments conducted by this research are reported in Chapter VI.

#### CHAPTER II

#### THE MODEL

The scheduling method to be introduced is a general one that can be applied to numerous pipelined RRVP's. The method formulates the sharing of the resources of such processors by their instructions. In turn, this formulation provides a model that can produce optimal schedules for low-level instruction codes of these processors.

To model RRVP's, a detailed description of their architectural features is necessary. An RRVP is specified a vector processor in which each FU receives input from one or more registers and sends its output to register. In addition, in an RRVP, each instruction uses at least one register. These general descriptions that identify a class of RRVP's do not provide sufficient information for their modeling. For a detailed modeling of these processors, the following specifications of resources of RRVP's and the restrictions applied to the of control these resources are necessary. specifications are derived from the CRAY-1 architecture.

#### A. Architectural Features

The following is a list of resources that are included in the model.

- 1- 1 instruction issuer to all Functional Units.

- 2- N register groups. For the convenience of referencing, three special register groups are specified as Address (A), Scalar (S), and Vector (V) registers.

- 3- P<sub>i</sub> identical registers in register group i, for i=1,2,...,N. P<sub>i</sub> is a positive integer, and P<sub>i</sub>=P<sub>j</sub> for some i,j=1,2,...,N is permitted.

- 4- M pipelined non-identical FU's, including the memory. Each pipeline stage is one clock long; one clock is equivalent to one time unit.

- 5- A set of access paths connecting FU's to registers.

The following general restrictions apply to the control of these resources.

- 1- At most one instruction can be issued at any clock period.

- 2- Instructions are issued in a sequential order. i.e. no instruction can be issued before all of the instructions that precede it in the sequential order of the instructions have been issued.

- 3- An instruction can be issued only if the registers and the FU required by the instruction have not been reserved by previously issued instructions.

- 4- At most one register in A register group and one

register in S register group can receive data at any clock period. Each one of these register groups has one update access path.

- 5- Vector instructions are the only instructions that can reserve the FU's, except for memory. The memory is reserved for any instruction type. The memory reservation period is determined by the type of the memory reference instruction.

- 6- Result registers are reserved until the result is received.

- 7- Vector-operand registers are reserved for a known period of time, depending on the vector length.

- 7- Each FU is dedicated to a specific group of instruction types.

- 9- Each instruction can be processed by only one specific FU; i.e. two instructions of the same type compete for the only FU available to that instruction type.

- 10- Execution of an instruction cannot be interrupted after it has been initiated; i.e. when the execution of an instruction is started, it must be fully processed without interruptions.

There are other conditions that control instructionissue that presently are not considered in the model, such

as instruction-buffer-fetch-in-progress, and instructionnot-in-instruction-buffer.

For illustration, the CRAY-1 architecture and

associated assembly language (CAL) [CRAY] will be used throughout the remainder of this dissertation.

#### B. The Method

The following are the definitions of some expressions that are used through out this dissertation.

<u>Definition 1- Issue-time</u> of an instruction  $I_i$  is the time at which all of the resources required by  $I_i$  are available and all of the instructions that precede  $I_i$  in the sequential order of the instructions have been issued.

This definition specifies a sequential order of issue for the instructions. Issue-time of an instruction  $I_i$  can be delayed by the late issue of the preceding instructions or the extension of their reservations of resources.

Definition 2- Start-of-execution-time is the time at which the operand values are transferred to the first stage of the pipelined FU for execution. For vector instructions, this time is the time that the first vector element is transferred for execution.

The start-of-execution-time that succeeds the issue-time is delayed when either the issue-time is postponed or not all of the data items are available. Two types of relationships between these two times can be identified that

are defined as follows.

- <u>Definition 3-</u> <u>Synchronous issue-execution</u> is the relationship between issue-time and start-of-execution-time of an instruction in which the time difference between these times is fixed and predetermined.

- Definition 4

Asynchronous issue-execution is the relationship between issue-time and start-of-execution-time of an instruction in which the time difference between these times is not fixed and is determined at the time of execution.

From Definition 3, it can be concluded that the start-of-execution-time of an instruction can be determined from its issue-time when synchronous issue-execution is enforced. However, such a conclusion is not true when asynchronous issue-execution is utilized. In the remainder of this dissertation, unless otherwise specified, synchronous issue-execution is assumed. The fixed length of time between issue-time and start-of-execution-time is assumed to be equal to the amount of time required for issuing of the instruction, usually one or two clocks.

<u>Definition 5- Termination-time</u> or <u>termination-of-execution-</u>

<u>time</u> is the time at which the last resource reserved by an instruction is released.

Since the result register is usually reserved longer than any other resource, in order to receive the result of the computation, the termination-time is the same as the time at which the result register is freed.

Scheduling of instructions is the act of rearranging the order of instructions in their sequence and determining their issue-times. Given the issue-time of an instruction, the time that its reserved resources will be freed can determined since the length of time that a resource is reserved is known if the instruction type and vector length Given a sequence of instructions, the are specified. issue- and termination-times of all of the instructions determined. The total length of the computation calculated and compared with that of other schedules. Then, the schedule with minimum total computation time is selected as the optimal one.

#### B.1. Inter-Instructional Relationships

Re-ordering of instructions in order to find an optimal schedule must be done so that it does not change the outcome of the computation. During the computation, the result of a calculation by an instruction  $\mathbf{I}_i$  is usually used by some other instructions that succeed  $\mathbf{I}_i$  in the sequential order of the code. If such an order is reversed, the result of the computation may be altered. To preserve the outcome of the computation, any change in the order of

instructions that can alter the correctness of the computation must be avoided.

For optimal scheduling of instruction, a complete understanding of the relationships between the instructions of the code is necessary. The restrictions that are applied to control the resources display a number of possibilities that can delay the execution of an instruction or postpone its issue time. Such delays, in turn, will cause the postponement of the issue and execution of other instructions. Therefore, to optimally schedule a low-level code, inter-instructional relationships that affect their issue-times should be determined.

The following definitions describe the type of inter-instructional relationships that affect the re-ordering of the instructions.

Definition 6- Given two instructions  $I_i$  and  $I_j$ , where  $I_j$  succeeds  $I_i$  in the sequential order of instructions,  $I_j$  is pairwise dependent on  $I_i$  iff at least one of the operand registers of  $I_j$  is the result register of  $I_i$  or the result register of  $I_i$  one of the registers of  $I_i$ .

The pairwise dependency relation, also stated by [TOKO] and [KUCK] in a similar manner, implies that  $I_{\dot{1}}$  should not be

<sup>&</sup>lt;sup>3</sup>Correctness in this context means that the final result or outcome of the code or computation is identical to the outcome of the original code.

issued until  $I_i$  has been issued and the dependency condition has been satisfied. If the issue order is reversed, it may alter the final result of the code. The pairwise dependency between two instructions is displayed by  $\frac{P}{}$ ; e.g. if  $I_2$  is pairwise dependent on  $I_1$ , then  $I_2$   $\frac{P}{}$ > $I_1$ .

<u>Definition 7-</u> Two instructions  $I_i$  and  $I_j$  are <u>globally</u>  $\frac{\text{dependent}}{\text{dependent}} \text{ if there exists } I_{k1}, \quad I_{k2}, \dots, \quad I_{kn}$   $\text{such that } I_j \xrightarrow{P} > I_{kn} \xrightarrow{P} > \dots \xrightarrow{P} > I_{k2} \xrightarrow{P} > I_{k1} \xrightarrow{P} > I_i$

If two instructions are globally dependent, this dependency enforces a specific issue-time-order on them to preserve the correctness of the code. This relation is displayed by  $\frac{G}{}$ ; e.g. if I<sub>2</sub> is globally dependent on I<sub>1</sub>, then I<sub>2</sub>  $\frac{G}{}$ >I<sub>1</sub>.

Two instructions that are neither pairwise nor globally dependent are called pairwise-independent or simply independent and can appear in any relative order with respect to each other. The issue order for two independent instructions is determined by the resource constraints imposed on them. That means that the instruction whose required resources become available prior to the other one's should precede the other instruction in the sequential order of the code. The resource restrictions can occur due to the reservation of resources by preceding instructions or the requirement of one or more resource by both instructions where only one resource of that type is available.

#### B.2. Dependency Graph

The dependency relation is displayed by a directed graph. Each node of the graph represents an instruction. Each edge specifies the dependency between the two nodes connected by that edge. The direction of each edge is from the predecessor to the successor, and the value on each edge represents the amount of time that the successor must wait after the predecessor has been issued, before it can be issued.

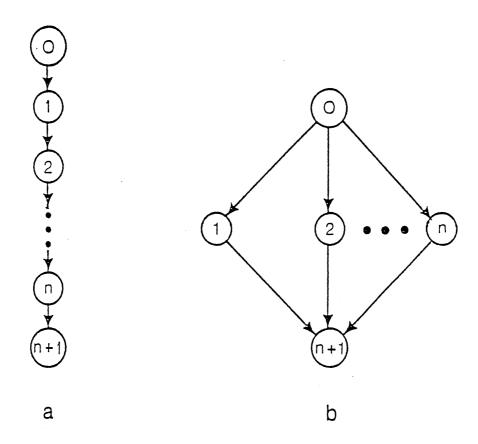

The dependency graph is drawn from the pairwise dependencies between the instructions of the code. The first node of the graph, called the root node, is a null instruction on which any instruction is dependent with a dependency length of zero time units. The instructions the code are, one by one, added to the graph as new nodes, in their sequential issue order. Each new node is connected all of its preceding instructions on which dependent, starting from its immediate predecessor and ending at the null instruction. Any edge created by a pairwise dependency between two instructions that already connected by an edge or a chain of edges need not be drawn. This elimination of edges is necessary to reduce the redundant connections between nodes that are connected by a path. Hence, the root node is the immediate predecessor only to the nodes that do not predecessor by pairwise dependency. This node provides a common time reference to all of the nodes in the graph and prevents the graph from being divided into a number of subgraphs.

After all of the instructions have been added to the graph, a second null node, called the <u>terminal node</u>, is added to the graph in order to succeed all of the nodes that have no successors. This node represents a null instruction that is dependent on any instruction. The issue-time of the terminal node is the termination-time of the code. Then, the total computation time is the time interval between the issue times of the root node and the terminal one.

The following relationships can be determined from a dependency graph.

- a- Two nodes are called <u>adjacent</u> if they are connected by an edge. Two adjacent nodes are pairwise dependent.

- b- A <u>directed path</u> is a set of edges such that for each edge ending at a node, there exists one edge in the same path which starts at that node, except for the nodes that start and finish the path. Each node on the path is connected to only one succeeding node and one preceding node in the same path. Two nodes are globally dependent if there exists a directed path from one node to the other one.

- c- Two nodes are called independent if they are not connected by any directed paths.

- Fig. 1 shows an example of a dependency graph and

S5+FS4

**S**3

**S** 2

, A3

A1+A2

A3

S1+FS1

**S** 5

|       | 2 | 0 |     |

|-------|---|---|-----|

| 4 4 0 |   | 8 | (a) |

S2\*FS1

**S**4

A1+1

Al

/HS3

Fig. 1- Sample Graph

(p)

(b) instructions set for (a). (a) dependency graph.

the set of instructions that it represents. In the sample instruction set of Fig. 1b,  $I_2 \xrightarrow{P} I_1$ ,  $I_6 \xrightarrow{P} I_4$ , and  $I_6 \xrightarrow{P} I_2$ . Therefore, in the dependency graph of Fig. 1a, nodes 2 & 1, 6 & 4, and 6 & 2 are adjacent nodes. The numbers on these edges represent the length of their dependency in time units. Also, since  $I_6 \xrightarrow{P} I_2 \xrightarrow{P} I_1$ , then  $I_6 \xrightarrow{G} I_1$ . Nodes 1 & 3, 1 & 5, 2 & 3, 2 & 4, 2 & 5, 2 & 7, 3 & 4, 3 & 6, 4 & 5, 6 & 5, and 6 & 7 are independent, because none of the pairs are connected by any directed paths.

In general, the dependency graph is neither a branching tree (only one predecessor per node) nor an assembly one (only one successor per node) ([BAKE]). It is a network structure due to the fact that each instruction is allowed more than one predecessor and/or successor.

# B.3. Reflexivity, Symmetry, and Transitivity

To gain more insight into pairwise dependency, global dependency, and independency relations, the following properties of such relations have been investigated.

Reflexivity- Since the execution of an instruction is not delayed by itself, pairwise and global dependencies are not reflexive relations; i.e. no instruction is pairwise or globally dependent on itself. Since no instruction is dependent on itself, it must be independent from itself. Therefore, independency is a reflexive relation.

Symmetry- Because the pairwise and global

dependency relations are defined in one direction and such a direction cannot be reversed, these relationships are not symmetric. In other words, the symmetry property for dependency relations would imply that an instruction can depend on its preceding and succeeding instructions. However, from definitions 6 and 7 these relations are only one directional; an instruction can be dependent on its preceding instructions only. Therefore, dependency relations are not symmetric. Since no direction has been specified for the independency between two instructions, this relation is a symmetric one. It means that the independence of instruction I from I implies that I is also independent from I;

Transitivity- If instruction  $I_j$  is globally dependent on  $I_i$  and  $I_k$  is globally dependent on  $I_j$ , there exists a directed path from  $I_i$  to  $I_j$  and a directed path from  $I_j$  to  $I_k$ . Hence, there exists a directed path from  $I_i$  to  $I_k$  that includes node  $I_j$ . Consequently,  $I_k$  is globally dependent on  $I_i$ . In other words, global dependency is transitive.

Pairwise dependency relation and independency relation are not transitive. The following two examples prove the claim by introducing examples to the contrary. Using the example of Fig. 1, it can be seen that  $I_7 \xrightarrow{P} > I_5$  and  $I_5 \xrightarrow{P} > I_3$ , but  $I_7$  is not pairwise dependent on  $I_3$ . Also,  $I_3$  is independent from  $I_4$  and  $I_4$  is independent from  $I_5$ , but

$I_3$  is not independent from  $I_5$ . Therefore, these relations are not transitive.

# C. Elementary Timing Model

The mathematical scheduling model is developed from inter-instructional relationships that imply restrictions on the order and the time of issue of the instructions. The restrictions imposed on the order of instructions are due to the reservation of the registers, FU's, and other resources. The model is then constrained by other architectural features to produce the complete mathematical programming problem.

The elementary model considers only pairwise dependencies between instructions. Pairwise dependency between two instructions enforces a time distance between the issue times of those instructions, in addition to enforcement of a specific issue order. If such issue time restrictions are satisfied, the availability of proper resources at the time of issue of dependent instructions is guaranteed. This model ensures the proper order and distance of the issue times of the instructions to preserve the correctness of the computation.

#### C.1. Minimum Time Problem

Define the issue distance  $D_{ji}$  as the minimum time between issues of  $I_j \xrightarrow{p} I_i$ . Then, pairwise dependency between instructions  $I_i$  and  $I_j$  can be formulated as follows.

$$T_{j} - T_{i} \ge D_{ji} \tag{1}$$

where  $T_j$  and  $T_i$  are issue times of instructions  $I_j$  and  $I_i$ , respectively. This formulation enforces the issue time of  $I_i$  to precede that of  $I_j$  by at least  $D_{ji}$  time units. Therefore, it preserves the issue order of dependent instructions.

At this stage of the formulation, the formal minimization criterion is the time between the issue of the first instruction and the completion of the last instruction. That is termed the 'minimum time' scheduling problem or minimization of makespan [BAKE]. Since the issue times of instructions are multiples of time units, these times must be specified by integer numbers.

The 'minimum time' problem is a linear programming problem. The problem is to minimize  $T_{last} - T_{first}$  subject to a set of inequalities of type (1). This problem can be solved by using linear programming, except that the LP does not ensure integer solutions. However, since  $D_{ji}$ 's are integers for all i and j, then the  $T_{j}$  and  $T_{i}$  are guaranteed to be integers as well.

#### C.2. Lower Bound

The scheduling of instructions can be viewed as mapping of the dependency graph onto the time axis. Since

<sup>\*</sup>This claim will be justified in Integer Programming section (section H.).

the order and time distance between dependent instructions must be preserved, the minimum amount of time required to issue and execute the instructions is equal to the length of the longest path connecting the root node to the terminal node on the dependency graph. Such a path is called a critical path (CP),[WIES]. Then, the minimum time problem, in which all of the paths can be mapped onto the CP, is the problem of determining the issue times of the instructions such that the total computation time does not exceed the length of the critical path.

The minimum time problem defines a lower the total computation time. Considering the restrictions to be enforced on the instruction issue by the architectural restrictions of the RRVP's, such as single instruction issue per unit time, the issue times of the instructions will delayed with respect to their issue time in minimum time problem. Such delays cause the length of the computation In minimum time problem, a number increased. instructions be can issued simultaneously. instructions must be ordered so that the instructions belonging to the critical path are issued as soon as possible and the rest of instructions are arranged so that their execution times overlap the execution times of the instructions on the CP. In general, it is not likely to comply with the architectural restrictions of RRVP's and map all of the paths onto the CP. In other words, the issue of the instructions on the CP must be delayed beyond their issue times in the minimum time problem due to single issue and resource constraints. Such delays increase the length of the CP and the total computation time. Therefore, the computation time of the minimum time problem is a lower bound for the general problem.

# D. Scheduling With Constraints

To determine the total computation time and issue for the general problem, times of the instructions architectural restrictions and features of the RRVP's must be added to the minimum time problem. The minimum time problem considers only the pairwise dependency relations imposed on the pairs of instructions due to the sharing of the registers. A number of other resource constraints (such as access path conflict, FU conflict, and issue conflict) also exist that should be incorporated in the model. These conflicts will be addressed in following the subsections. In addition to the resource constraints, some architectural features of the RRVP's are considered. Such features include synchronous and asynchronous chaining and asynchronous execution. These restrictions and features are formulated by a set of inequalities that can be added to those represented by (1) to make up a general model.

### D.1. Access Path Conflict Constraints

If both instructions are either A or S type, the

occurrence of access path conflict must be prevented. This conflict occurs when both instructions finish execution at the same time and must deliver the result to two result registers of A or S group at the same clock. Since only one access path is available for result delivery to these register groups, the issue of one of the instructions must be delayed to prevent access path conflict. For pairwise dependent instructions, this conflict is possible only when the number of clocks that the result register of the preceding instruction is reserved is greater than that succeeding instruction plus their issue time of the distance. Hence, to prevent the access path conflict for two pairwise dependent or two independent instructions, one of the following conditions should hold.

or

$$T_{i} + T_{R_{i}} - (T_{j} + T_{R_{j}}) \ge 1$$

$$T_{j} + T_{R_{j}} - (T_{i} + T_{R_{i}}) \ge 1$$

(2)

where  $T_{R_{\dot{1}}}$  and  $T_{R_{\dot{j}}}$  are the number of clocks that result registers of instructions  $I_{\dot{1}}$  and  $I_{\dot{j}}$  are reserved, respectively. For two independent instructions, any one of these inequalities can be chosen depending on the issue order of those instructions. For two dependent instructions, only one of the inequalities of (2) must be used since the order of these instructions is determined by their dependency and this order cannot be reversed.

# D.2. Vector-Operand Conflict Constraints

vector-operand conflict can occur. According to definition 6, two independent instructions can share only their operand registers. For vector instructions, vector-operand registers are reserved and cannot be used by more than one instruction at any time. Therefore, the execution of these instructions cannot be overlapped if they share at least one vector-operand register. However, since the instructions are independent, either one can precede the other one. Hence, this type of conflict is formulated as follows.

or

$$T_{j} - T_{i} \ge T_{OP_{i}}$$

$$T_{i} - T_{j} \ge T_{OP_{j}}$$

(3)

where  $T_{OP_i}$  and  $T_{OP_j}$  are the number of clocks that the operand registers of instructions  $I_i$  and  $I_j$  are reserved, respectively. Depending on the issue order of instructions  $I_i$  and  $I_j$  with respect to each other, one of these inequalities must be satisfied and the other one must be ignored.

#### D.3. FU Conflict Constraints

For independent instructions, <u>FU conflict</u> can occur for either (a) two vector instructions using the same FU, (b) a vector instruction and a scalar instruction using the same FU, or (c) a vector memory reference and any other memory reference. This conflict is similar to vector-

operand conflict, in the sense that the execution of these instructions cannot be overlapped due to sharing of their required FU. Hence, the formulation is the same as (3) with  $T_{OP_i}$  and  $T_{OP_j}$  replaced with  $T_{FU_i}$  and  $T_{FU_j}$ , the number of clocks that the FU is reserved for instructions  $I_i$  and  $I_j$ , respectively. Tokoro [TOKO] also finds it necessary to use similar inequalities to resolve FU conflicts. He uses such inequalities in his micro-code compaction algorithm when he allows the execution time of micro-operations to be longer than unit time.

#### D.4. Issue Conflict Constraints

Since no more than one instruction can be issued at any clock period, it must be assured that independent will avoid issue conflict; i.e. instructions instructions should not be scheduled so that their issue Each instruction requires a fixed and preoverlapped. determined amount of time for issue. Hence, this conflict identical to FU or vector-operand conflict, and it is formulated similarly by replacing  $T_{OP}$ , and  $T_{OP}$ , in (3)  $T_{ISS_i}$  and  $T_{ISS_i}$  that are amounts of time required to issue instructions  $I_i$  and  $I_j$ , respectively. Issue conflict cannot occur for two independent instructions with FU or vectoroperand conflict since the issue-time of one of these instructions must be delayed due to the unavailability of its required resources.

# D.5. Synchronous Chaining Constraints

Synchronous Chaining [CRAY] refers to the immediate transfer of data between pipelines involved in successive vector instructions. Such chaining requires that the second instruction be prepared to issue at the time that the first result emerges from the pipeline. The time at which the first result emerges is called 'chain slot' time [CRAY]. Failure to chain requires that the first vector operation be carried to completion; when the result vector is completely stored in a vector register, the second instruction can issue. Chaining is usually desirable, since both pipelines can be concurrently busied on different parts of a long vector.

Chaining is formulated as follows.

or

$$T_{j} - T_{i} \ge T_{R_{i}}$$

$$T_{j} - T_{i} = T_{CHS_{i}}$$

(4)

where  $T_{CHS_i}$  is the chain slot time and  $T_{R_i}$  is the time to complete the i<sup>th</sup> instruction, when chaining fails. Inequalities of (4) mean that instruction  $I_j$  can be either issued at exactly  $T_i^{+T}_{CHS_i}$  or after  $T_i^{+T}_{R_i}$ . Inequalities of (4) replace (1) for these instructions.

# D.6. Asynchronous Chaining Constraints

Asynchronous chaining refers to the transfer of data between pipelines at or after the chain slot time when the

resources are available. This type of chaining allows the chaining of one or more instructions with the current one. This is not a likely possibility for synchronous chaining, because the instruction to be chained must be issued at the chain slot time of more than one instruction. That requires the chain slot times of two or more instructions to occur at the same time. Since asynchronous chaining can be performed at any clock time at or after the chain slot time, the current instruction does not have to be delayed till the preceding instruction is completed if the chain slot is missed. That allows earlier issue of its succeeding instructions. Asynchronous chaining is formulated as follows.

$$T_{j} - T_{i} \ge T_{CHS_{i}}$$

(5)

Inequality (5) replaces (1) for these instructions.

### E. Asynchronous Issue-Execution

Issuing an instruction requires the availability of the resources needed by that instruction; these resources are the FU, the registers, and the access paths. When all of such resources for the current instruction are available, it will be issued, the resources will be reserved, and the execution of the data element(s) will be started. The length of time that these resources are reserved is determined by the amount of time required for the execution of data element(s) and the type of resources. For scalar

and address instructions, that contain one data element, operand registers are reserved for the duration of issue process. However, the result register of these instructions is reserved throughout the execution. On the other hand, for vector instructions that must process a number of data elements, each one of the required resources is reserved for a number of clocks no less than the vector length. In the previous formulations, it has been assumed that the issue time and the start of execution of data elements are the same, thus only one start time is used in forming the inequalities.

#### E.1. Flexible Issue

To allow the model and RRVP's a higher degree of flexibility, the synchronous issue-execution of instructions can be replaced by asynchronous issue-execution procedures that do not bind the issue-times and the start-ofexecution-times to occur simultaneously. It is still necessary that the resources required by an instruction available at the time of issue. All of A. S. and V instructions utilize synchronous issue-execution, because the availability of the resources at issue time will cause the start of their execution, except for instructions involved in an asynchronous chain. For instructions in an asynchronous chain, it is assumed that the vector registers that provide the chaining are available to the instruction to be chained, but the data elements do not arrive until after the chain slot time. Therefore, an instruction that is to be asynchronously chained to one or more previously-issued instructions can be issued when resource requirements are satisfied, but will not start execution till the chained data elements become available. This procedure also affects the length of reservation interval of the resources used by the chaining instruction. It means that such resources are reserved at the time of issue and will be idle until the start of the execution. From this start time, the time at which those resources must be freed is determined.

Asynchronous issue-execution has an important effect on the total computation time. When an instruction that is to be chained is issued before it can be executed, its succeeding instructions are issued earlier than they would be if the issue of the chaining instruction were to be delayed until the chain slot time. Therefore, the total computation time may be reduced by allowing earlier execution of some instructions.

The length of the chain- the time interval starting at the issue time of the instruction starting the chain and ending at the termination-of-execution-time of the last instruction in the chain- is not altered when asynchronous issue-execution and asynchronous chaining are used. The only effect of such asynchronous issue-execution is the earlier issuing of the instructions involved in a chain.

# E.2. Formulation Changes

To model asynchronous issue-execution, two independent variables are needed to specify the issue-time and the start-of-execution-time independently. Since the only instructions that are affected are the ones which are involved in a series of asynchronous chains, only the inequalities involving these instructions should be modified in the model.

In the preceding sections, the model has used one time variable to specify each instruction. That time variable is the issue time of the instruction. A new variable  $\mathbf{E}_i$  is introduced that represents the time that the execution of instruction  $\mathbf{I}_i$  must be started. For any instruction  $\mathbf{I}_i$  that is not involved in an asynchronous chain, the execution starts at the time of issue; i.e.  $\mathbf{T}_i = \mathbf{E}_i$ . On the other hand, for instructions involved in such a chain, the following changes occur.

1- Change all of the dependency inequalities between the current instruction  $(I_i)$  and the succeeding vector instructions  $(I_j's)$ , except for instructions in the same chain, to the following.

$$T_j - E_i \ge \tau_i$$

(6)

$\tau_i$  is the length of their dependency.

2- If  $I_i$  is a mixed V and S type instruction, the dependency of the succeeding dependent S-type

instruction is not altered.

3- If  $I_{i}$  is asynchronously chained with  $I_{i}$ , then

$$T_{j} - T_{i} \ge T_{ISS_{i}}$$

$$E_{j} - E_{i} \ge T_{CHS_{i}}$$

(7)

4- Since no instruction can be executed before it is issued,

$$E_i - T_i \ge 0$$

5- If  $I_i$  is independent from an instruction in the code, say  $I_j$ , and there exists an FU or vector-operand conflict between them. Then,

or

$$T_{j} - E_{i} + \theta * y_{ij} \ge \tau_{i}$$

$$T_{i} - E_{j} + \theta * (1 - y_{ij}) \ge \tau_{j}$$

(8)

where  $\tau_i$  and  $\tau_j$  are the durations of the conflicts depending on which instruction succeeds the other one. And, if the two independent instructions have only issue conflict, then the original issue conflict based only on issue time inequalities apply.

### F. Global Dependency

Global dependency between two instructions that are connected by a directed path on their dependency graph is

determined from pairwise dependencies between instructions of the path. Pairwise dependency between two instructions forces a minimum time-interval between their Since the global dependency relation can be issue times. represented by a combination of a number of pairwise dependency relations, it also enforces a minimum timeinterval between the issue times of globally dependent instructions; e.g.  $I_k \xrightarrow{G} > I_i$  can be represented by  $I_k \xrightarrow{P} I_i \xrightarrow{P} I_i$ . This minimum time-interval is equal to the longest path connecting two globally dependent instructions where the length of a path is determined by the sum of all edge values of the edges on the path. Since the pairwise dependency ensures the availability of the registers at the time of issue of the dependent instruction, the implicit enforcement of global dependency between two instructions through pairwise dependencies is appropriate, except for some special cases.

Special cases in which global dependencies between instructions cannot be satisfied through pairwise dependencies are caused by instructions that utilize vector registers plus one A or S register. Suppose two independent vector instructions  $\mathbf{I}_i$  and  $\mathbf{I}_k$  with FU or vector-operand conflict use the same A or S register as one of their operand registers; A and S registers are not reserved as operand registers. Now, suppose a scalar or address instruction  $\mathbf{I}_j$  with the result register which is the same register as the one used by the two V instructions separates

those two V instructions. Obviously,  $I_j \xrightarrow{P} > I_i$  and  $I_k \xrightarrow{P} > I_j$ . Therefore,  $I_i$  and  $I_k$  are not considered independent instructions and the FU or vector-operand conflicts are ignored. The dependency between  $I_j$  and  $I_i$  is  $T_{ISS_i}$  clocks since the S or A register is not reserved. And, the dependency between  $I_k$  and  $I_j$  is  $T_{R_j}$ . Therefore, the global dependency between  $I_i$  and  $I_k$  is  $T_{R_j} + T_{ISS_i}$ . However, due to FU or vector-operand conflict  $I_i$  and  $I_k$  should be separated by  $T_{FU_i}$  or  $T_{OP_i}$ . In cases where  $T_{FU_i}$  or  $T_{OP_i}$  is larger than  $T_{R_j} + T_{ISS_i}$ , a dependency inequality is needed to ensure the proper issue time distance between  $I_i$  and  $I_k$ . Hence, the following inequality is added to the model.

$$T_{k} - T_{i} \geq \tau_{i} \tag{9}$$

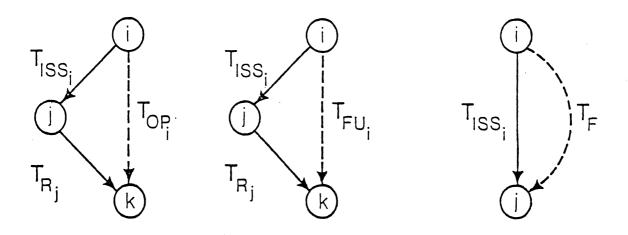

$\tau_i$  represents  $T_{OP_i}$  or  $T_{FU_i}$  depending on vector-operand or FU conflict between  $I_i$  and  $I_k$ , respectively. Fig. 2 (a) and (b) depict examples for vector-operand and FU conflict special cases.